JOURNAL OF APPLIED PHYSICS VOLUME 89, NUMBER 10 15 MAY 2001

# **APPLIED PHYSICS REVIEW**

# High- $\kappa$ gate dielectrics: Current status and materials properties considerations

G. D. Wilka)

Agere Systems, Electronic Device Research Laboratory, Murray Hill, New Jersey 07974

R. M. Wallace<sup>b)</sup>

University of North Texas, Department of Materials Science, Denton, Texas 76203

## J. M. Anthony

University of South Florida, Center for Microelectronics Research, Tampa, Florida 33620

(Received 9 November 2000; accepted for publication 19 January 2001)

Many materials systems are currently under consideration as potential replacements for SiO<sub>2</sub> as the gate dielectric material for sub-0.1 µm complementary metal-oxide-semiconductor (CMOS) technology. A systematic consideration of the required properties of gate dielectrics indicates that the key guidelines for selecting an alternative gate dielectric are (a) permittivity, band gap, and band alignment to silicon, (b) thermodynamic stability, (c) film morphology, (d) interface quality, (e) compatibility with the current or expected materials to be used in processing for CMOS devices, (f) process compatibility, and (g) reliability. Many dielectrics appear favorable in some of these areas, but very few materials are promising with respect to all of these guidelines. A review of current work and literature in the area of alternate gate dielectrics is given. Based on reported results and fundamental considerations, the pseudobinary materials systems offer large flexibility and show the most promise toward successful integration into the expected processing conditions for future CMOS technologies, especially due to their tendency to form at interfaces with Si (e.g. silicates). These pseudobinary systems also thereby enable the use of other high- $\kappa$  materials by serving as an interfacial high-k layer. While work is ongoing, much research is still required, as it is clear that any material which is to replace SiO2 as the gate dielectric faces a formidable challenge. The requirements for process integration compatibility are remarkably demanding, and any serious candidates will emerge only through continued, intensive investigation. © 2001 American Institute of Physics. [DOI: 10.1063/1.1361065]

| I. INTRODUCTION                                        | 5243 |

|--------------------------------------------------------|------|

| II. SCALING AND IMPROVED                               |      |

| PERFORMANCE                                            | 5244 |

| III. METAL-INSULATOR-SEMICONDUCTOR                     |      |

| (MIS) GATE STACK STRUCTURES                            | 5245 |

| IV. SCALING LIMITS FOR CURRENT GATE                    |      |

| DIELECTRICS                                            | 5247 |

| A. Ultrathin SiO <sub>2</sub> properties               | 5247 |

| B. Ultrathin SiO <sub>2</sub> reliability              | 5248 |

| C. Boron penetration and surface preparation           | 5249 |

| D. $SiO_xN_y$ and $Si-N/SiO_2$ dielectrics             | 5249 |

| E. Fundamental limitations                             | 5249 |

| F. Device structures                                   | 5250 |

| V. ALTERNATIVE HIGH- $\kappa$ GATE DIELECTRICS.        | 5250 |

| A. High- $\kappa$ candidates from memory applications. | 5251 |

| B. Issues for interface engineering                    | 5252 |

| C. Recent high- $\kappa$ results                       | 5253 |

|                                                        |      |

| 1. Group IIIA and IIIB metal oxides             | 5254 |

|-------------------------------------------------|------|

| 2. Group IVB metal oxides                       | 5256 |

| 3. Pseudobinary alloys                          | 5262 |

| 4. High- $\kappa$ device modeling and transport | 5265 |

| VI. MATERIALS PROPERTIES                        |      |

| CONSIDERATIONS                                  | 5266 |

| A. Permittivity and barrier height              | 5266 |

| B. Thermodynamic stability on Si                | 5268 |

| C. Interface quality                            | 5269 |

| D. Film morphology                              | 5270 |

| E. Gate compatibility                           | 5271 |

| F. Process compatibility                        | 5272 |

| G. Reliability                                  | 5272 |

| VII. CONCLUSIONS                                | 5273 |

# I. INTRODUCTION

The rapid progress of complementary metal—oxide—semiconductor (CMOS) integrated circuit technology since the late 1980's has enabled the Si-based microelectronics industry to simultaneously meet several technological requirements to fuel market expansion. These requirements in-

a)G. D. Wilk is formerly of Bell Laboratories, Lucent Technologies; electronic mail: gwilk@agere.com

b)Electronic mail: rwallace@unt.edu

clude performance (speed), low static (off-state) power, and a wide range of power supply and output voltages. This has been accomplished by developing the ability to perform a calculated reduction of the dimensions of the fundamental active device in the circuit: the field effect transistor (FET)—a practice termed "scaling." The result has been a dramatic expansion in technology and communications markets including the market associated with high-performance microprocessors as well as low static-power applications, such as wireless systems.

It can be argued that the key element enabling the scaling of the Si-based metal-oxide-semiconductor field effect transistor (MOSFET) is the materials (and resultant electrical) properties associated with the dielectric employed to isolate the transistor gate from the Si channel in CMOS devices for decades: silicon dioxide. The use of amorphous, thermally grown SiO<sub>2</sub> as a gate dielectric offers several key advantages in CMOS processing including a stable (thermodynamically and electrically), high-quality Si-SiO2 interface as well as superior electrical isolation properties. In modern CMOS processing, defect charge densities are on the order of  $10^{10}$ /cm<sup>2</sup>, midgap interface state densities are  $\sim 10^{10}$ / cm<sup>2</sup> eV, and hard breakdown fields of 15 MV/cm are routinely obtained and are therefore expected regardless of the device dimensions. These outstanding electrical properties clearly present a significant challenge for any alternative gate dielectric candidate.

#### II. SCALING AND IMPROVED PERFORMANCE

The industry's demand for greater integrated circuit functionality and performance at lower cost requires an increased circuit density, which has translated into a higher density of transistors on a wafer.<sup>3</sup> This rapid shrinking of the transistor feature size has forced the channel length and gate dielectric thickness to also decrease rapidly. As will be discussed in the next few sections, the current CMOS gate dielectric SiO<sub>2</sub> thickness can scale to at least 13 Å, but there are several critical device parameters that must be balanced during this process.

The improved performance associated with the scaling of logic device dimensions can be seen by considering a simple model for the drive current associated with a FET. The drive current can be written (using the gradual channel approximation) as

$$I_D = \frac{W}{L} \mu C_{\text{inv}} \left( V_G - V_T - \frac{V_D}{2} \right) V_D, \qquad (1)$$

where W is the width of the transistor channel, L is the channel length,  $\mu$  is the channel carrier mobility (assumed constant here),  $C_{\rm inv}$  is the capacitance density associated with the gate dielectric when the underlying channel is in the inverted state,  $V_G$  and  $V_D$  are the voltages applied to the transistor gate and drain, respectively, and the threshold voltage is given by  $V_T$ . It can be seen that in this approximation the drain current is proportional to the average charge across the channel (with a potential  $V_D/2$ ) and the average electric field

$(V_D/L)$  along the channel direction. Initially,  $I_D$  increases linearly with  $V_D$  and then eventually saturates to a maximum when  $V_{D,\mathrm{sat}} = V_G - V_T$  to yield

$$I_{D,\text{sat}} = \frac{W}{L} \mu C_{\text{inv}} \frac{(V_G - V_T)^2}{2}.$$

(2)

The term  $(V_G - V_T)$  is limited in range due to reliability and room temperature operation constraints, since too large a  $V_G$  would create an undesirable, high electric field across the oxide. Furthermore,  $V_T$  cannot easily be reduced below about 200 mV, because  $kT \sim 25$  mV at room temperature. Typical specification temperatures ( $\leq 100$  °C) could therefore cause statistical fluctuations in thermal energy, which would adversely affect the desired the  $V_T$  value. Thus, even in this simplified approximation, a reduction in the channel length or an increase in the gate dielectric capacitance will result in an increased  $I_{D, \rm sat}$ .

In the case of increasing the gate capacitance, consider a parallel plate capacitor (ignoring quantum mechanical and depletion effects from a Si substrate and gate)<sup>6</sup>

$$C = \frac{\kappa \epsilon_0 A}{t},\tag{3}$$

where  $\kappa$  is the dielectric constant (also referred to as the relative permittivity in this article) of the material,  $^7$   $\epsilon_0$  is the permittivity of free space (=8.85×10<sup>-3</sup> fF/ $\mu$ m), A is the area of the capacitor, and t is the thickness of the dielectric. This expression for C can be rewritten in terms of  $t_{\rm eq}$  (i.e., equivalent oxide thickness) and  $\kappa_{\rm ox}$  (=3.9, dielectric constant of SiO<sub>2</sub>) of the capacitor. The term  $t_{\rm eq}$  represents the theoretical thickness of SiO<sub>2</sub> that would be required to achieve the same capacitance density as the dielectric (ignoring issues such as leakage current and reliability). For example, if the capacitor dielectric is SiO<sub>2</sub>,  $t_{\rm eq}$ =3.9 $\epsilon_0(A/C)$ , and a capacitance density of C/A=34.5 fF/ $\mu$ m<sup>2</sup> corresponds to  $t_{\rm eq}$ =10 Å. Thus, the physical thickness of an alternative dielectric employed to achieve the equivalent capacitance density of  $t_{\rm eq}$ =10 Å can be obtained from the expression

$$\frac{t_{\rm eq}}{\kappa_{\rm ox}} = \frac{t_{\rm high-\kappa}}{\kappa_{\rm high-\kappa}}$$

or simply,

$$t_{\text{high}-\kappa} = \frac{\kappa_{\text{high}-\kappa}}{\kappa_{\text{ox}}} t_{\text{eq}} = \frac{\kappa_{\text{high}-\kappa}}{3.9} t_{\text{eq}}$$

. (4)

A dielectric with a relative permittivity of 16 therefore affords a physical thickness of  $\sim$ 40 Å to obtain  $t_{\rm eq}$ = 10 Å. (As noted above, actual performance of a CMOS gate stack does not scale directly with the dielectric due to possible quantum mechanical and depletion effects.)<sup>6</sup>

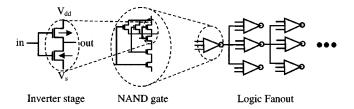

From a CMOS circuit performance point of view, a performance metric considers the dynamic response (i.e., charging and discharging) of the transistors, associated with a specific circuit element, and the supply voltage provided to the element at a representative (clock) frequency. A common element employed to examine such switching time effects is a CMOS inverter. This circuit element is shown in Fig. 1 where the input signal is attached to the gates and the output signal is connected to both the *n*-type MOS (nMOS) and *p*-type MOS (pMOS) transistors associated with the CMOS

FIG. 1. Components used to test a CMOS FET technology.  $V_{DD}$  and  $V_S$  serve as the source and drain voltages, respectively, and are common to the NAND gates shown. Each NAND gate is connected to three others resulting in a fanout of 3.

stage. The switching time is limited by both the fall time required to discharge the load capacitance by the n-FET drive current and the rise time required to charge the load capacitance by the p-FET drive current. That is, the switching response times are given by  $^1$

$$\tau = \frac{C_{\text{LOAD}} V_{DD}}{I_D}, \text{ where } C_{\text{LOAD}} = F C_{\text{GATE}} + C_j + C_i,$$

(5)

and  $C_j$  and  $C_i$  are parasitic junction and local interconnection capacitances, respectively. The "fan out" for interconnected devices is given by the factor "F." Ignoring delay in gate electrode response, as  $\tau_{\text{GATE}} \ll \tau_{n,p}$ , the average switching time is therefore

$$\overline{\tau} = \frac{\tau_p + \tau_n}{2} = C_{\text{LOAD}} V_{DD} \left\{ \frac{1}{I_D^n + I_D^p} \right\}. \tag{6}$$

The load capacitance in the case of a single CMOS inverter is simply the gate capacitance if one ignores parasitic contributions such as junction and interconnect capacitance. Hence, an increase in  $I_D$  is desirable to reduce switching speeds. For more realistic estimates of microprocessor performance, the load capacitance is connected ("fanned out") to other inverter elements in a predetermined fashion. When coupled with other NMOS/PMOS transistor pairs in the configuration shown in Fig. 1, one can create a logic "NAND" gate which can be used to investigate the dynamic response of the transistors and thus examine their performance under such configurations. For example, in microprocessor estimates, a fan out of F=3 is often employed, as shown in Fig. 1.

One can then characterize the performance of a circuit (based on a particular transistor structure) through this switching time. To do this, various "figures of merit" (FOM) have been proposed which incorporate parasitic capacitance as well as the influence of gate sheet resistance on the switching time.<sup>8</sup> For example, a common FOM employed is related to Eq. (6) simply by

$$FOM \approx \frac{1}{\overline{\tau}} = \frac{2}{\tau_p + \tau_n}.$$

(7)

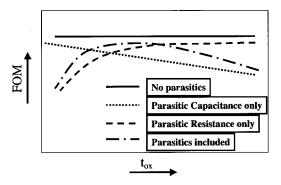

In the case where parasitics are ignored, it is easily seen then that an increase in the device drive current  $I_D$  results in a decrease in the switching time and an increase in the FOM value (performance). Even in this simple model, however, the incorporation of parasitic effects, results in the "clamping" of FOM improvement, despite an increase in the gate

FIG. 2. FOM as a function of equivalent oxide thickness,  $t_{\rm eq}$ . Parasitic capacitances and resistances result in transistor design tradeoffs to optimize performance.

dielectric capacitance. This can be seen in Fig. 2 where various FOM calculations are plotted as a function of an "equivalent oxide thickness,"  $t_{\rm eq}$ , as described earlier.

Each FOM calculation shown in Fig. 2 corresponds to specific assumptions on the values of parasitic capacitance and gate sheet resistance, as indicated (gate length is kept constant in this analysis). Important aspects such as gate induced drain leakage and reliability are ignored in this simple model. Nevertheless, the result of the FOM calculation shown in Fig. 1 indicates that tradeoffs on all aspects of the transistor design and scaling, including parasitics, must be carefully considered in order to increase the circuit performance. 8

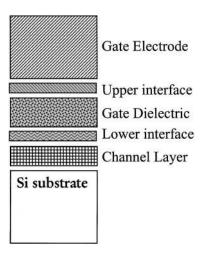

# III. METAL-INSULATOR-SEMICONDUCTOR (MIS) GATE STACK STRUCTURES

Figure 3 provides the reader a schematic overview of the various regions associated with the gate stack of a CMOS FET (regions are separated simply to clarify the following discussion). The gate dielectric insulates the gate electrode (gate) from the Si substrate. Gate electrodes in modern CMOS technology are composed of polycrystalline Si (poly-Si) which can be highly doped (e.g. by ion implantation) and subsequently annealed in order to substantially increase conductivity. The selection of the dopant species and concentra-

FIG. 3. Schematic of important regions of a field effect transistor gate stack.

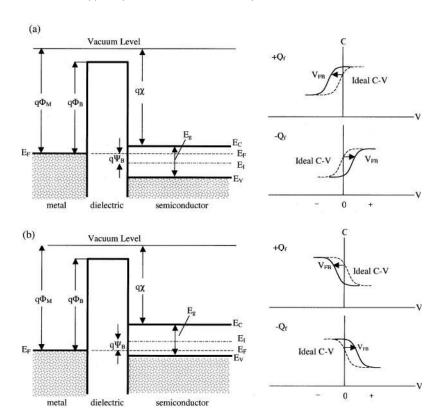

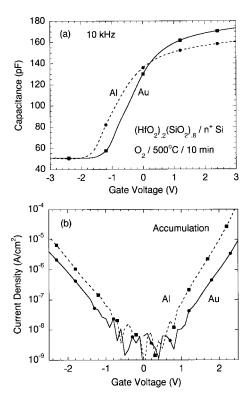

FIG. 4. Energy-band diagrams and associated high-frequency C-V curves for ideal MIS diodes for (a) n-type and (b) p-type semiconductor substrates. For these ideal diodes,  $V\!=\!0$  corresponds to a flatband condition. For dielectrics with positive  $(+Q_f)$  or negative  $(-Q_f)$  fixed charge, an applied voltage  $(V_{\rm FB})$  is required to obtain a flatband condition and the corresponding  $C\!-\!V$  curve shifts in proportion to the fixed charge. (after Refs. 9 and 10).

tion permits the adjustment of the poly-Si Fermi level for either nMOS or pMOS FETs. Metals can also be used as the gate electrode, and, in fact, are commonly used for evaluation of capacitor structures. Work is underway to find suitable metal gates for CMOS (see Sec. VIE).

The interfaces with either the gate or the Si channel region are particularly important in regard to device performance. These regions,  $\sim$ 5 Å thick, serve as a transition between the atoms associated with the materials in the gate electrode, gate dielectric and Si channel. As will be discussed, these interface regions can alter the overall capacitance of the gate stack, particularly if they have a thickness which is substantial relative to the gate dielectric. Additionally, these interfacial regions can be exploited to obtain desirable properties. The upper interface, for example, can be engineered in order to block boron outdiffusion from the  $p^+$ poly-Si gate. The lower interface, which is in direct contact with the CMOS channel region, must be engineered to permit low interface trap densities (e.g. dangling bonds) and minimize carrier scattering (maximize mobility) in order to obtain reliable, high performance.

It is instructive to consider the band diagrams for the MIS structures discussed in this review. Figure 4 shows the energy-band diagrams for ideal MIS diode structures using (a) n-type and (b) p-type semiconductor substrates. <sup>9,10</sup> For these ideal structures, at  $V\!=\!0$  applied voltage on the metal gate, the work function difference between the metal and semiconductor,  $\Phi_{\rm MS}$ , is zero

$$\Phi_{\rm MS} = \Phi_{\rm M} - \left(\chi + \frac{E_g}{2q} - \Psi_B\right) = 0; \quad n\text{-type}$$

$$\Phi_{\rm MS} = \Phi_{\rm M} - \left(\chi + \frac{E_g}{2q} + \Psi_B\right) = 0; \quad p\text{-type}, \tag{8}$$

where  $\Phi_{\rm M}$  is the metal work function,  $\chi$  is the semiconductor electron affinity,  $E_g$  is the semiconductor band gap,  $\Phi_B$  is the potential barrier between the metal and dielectric, and  $\psi_B$  is the potential difference between the Fermi level  $E_F$  and the intrinsic Fermi level,  $E_I$ . Under these conditions, the energy bands are flat across the structure as shown in Fig. 4 and  $V=V_{\rm FB}=0$ , where  $V_{\rm FB}$  is the flat band voltage (i.e., the voltage required to bring the Fermi levels into alignment). A more typical case is that the Fermi levels of the electrode and substrate are misaligned by an energy difference, and a voltage ( $V_{\rm FB}\neq 0$ ) must be applied to bring the Fermi levels into alignment.

Many dielectrics exhibit a fixed charge  $(Q_f)$ , however, resulting in a required applied voltage  $V = V_{FB} \neq 0$  to achieve a flat band condition. The amount of fixed charge can be related to the measured  $V_{FB}$  value by the expression<sup>9</sup>

$$V_{\rm FR} = \Phi_{\rm MS} \pm Q_f / C_{\rm acc}, \tag{9}$$

where  $C_{\rm acc}$  is the measured capacitance in accumulation. Thus, a value for fixed charge density  $Q_f$  can be determined from measured values of  $V_{\rm FB}$ ,  $\Phi_{\rm MS}$  and  $C_{\rm acc}$ . The sign of the fixed charge is also important, as negative fixed charge correlates with the plus sign in Eq. (9), and positive fixed charge correlates with the minus sign. These expressions will be discussed further in Sec. V C 2.

The source of such fixed charge, often though *not always* positive, is thought to originate from the detailed bonding of the atoms associated with the dielectric near the dielectric/

semiconductor interface. Several proposed explanations for the cause of the observed fixed charge will be discussed in Sec. V C 2. Figure 4 shows that for positive  $Q_f$ , a negative shift in the  $V_{\rm FB}$  from ideal conditions (where V=0) is required for both n-type and p-type MIS structures. Similarly, a positive  $V_{\rm FB}$  is required for negative  $Q_f$ .

Most of the alternate dielectric candidates examined to date appear to have a substantial amount of fixed charge, which could present significant issues for CMOS applications. Given the scaling limitations on applied voltages due to power consumption, shifts in the  $V_{\rm FB}$  value are undesirable and must be minimized. In some applications, biasing the substrate to compensate for the fixed charge has been proposed. Moreover, a reproducible  $V_{\rm FB}$  (correspondingly  $V_{\rm T}$  for transistors) value is also required for stable, reliable transistor operation. Thus, hysteretic changes in the  $V_{\rm FB}$  from voltage cycling of less than 20 mV are often required.

Some dielectrics which incorporate aluminum, however, thus far suggest that a negative fixed charge is present. It has been recently proposed to combine Al ions with some alternate dielectric candidates in order to compensate positive and negative fixed charges to achieve a neutral state or, at least, minimize such fixed charge effects. If fixed charge is determined to be large and difficult to minimize and control in high- $\kappa$  dielectrics, it will be a significant issue for obtaining the desired device performance on both nMOS and pMOS transistors. The magnitude of measured  $V_{\rm FB}$  shifts for many alternate dielectrics will be discussed later.

# IV. SCALING LIMITS FOR CURRENT GATE DIELECTRICS

The previous sections outlined the need to scale oxide thicknesses to improve performance. The next two sections describe the present understanding in the field regarding the limits of scaling current gate dielectric materials, SiO<sub>2</sub> and Si-oxide-nitride variations, for CMOS. Issues include band offset, interfacial structure, boron penetration and reliability. Beyond this scaling limit, another material will be required as the gate dielectric to allow further CMOS scaling.

# A. Ultrathin SiO<sub>2</sub> properties

Experiments and modeling have been done on ultrathin  $SiO_2$  films on Si, as a way to determine how the  $SiO_2$  band gap or band offsets to Si change with decreasing film thickness. <sup>12–15</sup> In the study by Muller *et al.*, <sup>12</sup> electron energy loss spectroscopy (EELS) was carried out on 7–15 Å  $SiO_2$  layers on Si. It was found that the density of states (as measured by the oxygen K-edge in EELS, with a probe resolution <2 Å) transition from the substrate into the  $SiO_2$  layer indicated that the full band gap of  $SiO_2$  is obtained after only about two monolayers of  $SiO_2$ . This indicates that within two monolayers of the  $SiO_2$  in the full arrangement of oxygen neighbors and therefore cannot form the full band gap that exists within the "bulk" of the  $SiO_2$  film.

An earlier ab inito model by Tang et al. 13 of extremely thin SiO2, which was modeled as a modified betacristoballite phase, showed an important result, in that the band gap of SiO<sub>2</sub> did not begin to decrease until there were fewer than three monolayers of oxide. Moreover, estimates of the changes in the associated conduction and valance band offsets for these systems indicated that a minimum of 7 Å of SiO<sub>2</sub> is required to obtain bulk properties. The recent first principles study by Neaton et al. 14 determined that the local energy gap in SiO2 is directly related to the number of O second nearest neighbors, for a given O atom. The last row of O atoms (next to the Si substrate) by definition cannot have the full six nearest neighbor O atoms. The second row of O atoms from the Si interface is thus the first layer of O atoms that have the required six second-nearest neighbor O atoms. The distance required to obtain the full band gap of SiO<sub>2</sub> at each interface is therefore given by 1.6 Å (the spacing of one Si-O bond length) +2.4 Å (the distance between neighboring O atoms is 2.7 Å, but this is variable because of Si-O bond bending. The distance is typically in the range  $\sim$ 2 to 2.4 Å). The thickness at each interface required for the full SiO<sub>2</sub> band gap is therefore  $\sim 3.5-4.0$  Å. Counting both interfaces, the total thickness of 7-8 Å is required, in agreement with Tang et al. 13 and with the experiment. 12 These results set an absolute physical thickness limit of SiO2 of 7 Å. Below this thickness, the Si-rich interfacial regions from the channel and polycrystalline Si gate interfaces used in MOSFETs overlap, causing an effective "short" through the dielectric, rendering it useless as an insulator.

The agreement between the experiment and simulation in these cases indicates that the inherent band gap of  $SiO_2$  remains intact, even down to only a few monolayers of material. Other important properties of  $SiO_2$  have been reported in the ultrathin, sub-20 Å regime, such as the conduction band offset  $\Delta E_C$  to Si [using x-ray photoelectron spectroscopy (XPS)], <sup>16</sup> the tunneling electron effective mass  $m^*$  (from tunneling I-V measurements), <sup>17</sup> and the photoelectron attenuation length. <sup>18</sup> These measurements have further demonstrated very little change in fundamental  $SiO_2$  properties between bulk and ultrathin sub-20 Å films.

The apparent robust nature of SiO<sub>2</sub>, coupled with industry's acquired knowledge of oxide process control, has helped the continued use of SiO<sub>2</sub> for the past several decades in CMOS technology. As experimental evidence of the excellent electrical properties of such ultrathin SiO2 films, it has been demonstrated that transistors with gate oxides as thin as 13–15 Å continue to operate satisfactorily. 19–24 Although high leakage current densities of 1-10 A/cm<sup>2</sup> (at  $V_{\rm DD}$ ) are measured for such devices, 25 transistors intended for high-performance microprocessor applications can sustain these currents. As first reported by Timp et al. 20-22 scaling of CMOS structures with SiO2 gate oxides thinner than about 10-12 Å results in no further gains in transistor drive current. This result has been subsequently and independently reported by other groups, thus 10-12 Å could serve as a practical limit for reducing the SiO<sub>2</sub> thickness. <sup>23,24,26</sup>

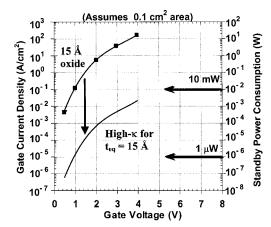

FIG. 5. Power consumption and gate leakage current density for a chip which has a 15 Å thick  $SiO_2$  gate dielectric compared to the potential reduction in leakage current by an alternate dielectric exhibiting the same equivalent oxide thickness. Assumes at total gate area of 0.1 cm<sup>2</sup>.

In contrast to the high performance microprocessor market, the rapidly growing market of low-power applications requires transistors with much lower ( $\sim 10^{-3}$  A/cm²) leakage currents. This is illustrated in Fig. 5, where the current density and standby power consumption are plotted as a function of gate voltage. The curve for 15 Å oxide is based on measured values, the curve for a high- $\kappa$  film is meant to show the potential reduction in leakage current for a high- $\kappa$  dielectric with the same  $t_{\rm eq}$  value. Depending on the specific materials and conditions, leakage current reduction may be less than shown. It is clear that a gate dielectric with a permittivity higher than that of SiO<sub>2</sub> is required to meet low-power application requirements.

# B. Ultrathin SiO<sub>2</sub> reliability

An equally important issue regarding ultrathin SiO<sub>2</sub> gate oxides has been understanding and predicting oxide reliability. Considerable debate existed over whether SiO2 gate oxides <22-27 Å thick would exhibit the stringent ten year reliability criteria,<sup>27</sup> which is required for CMOS devices. The first report of a sub-20 Å SiO<sub>2</sub> gate oxide to meet reliability requirements was given by Weir et al.,25 where a 16 Å oxide was shown to have reliability projections at 1.6 V operation for greater than ten years. This is much thinner than projected even three to five years ago. 28,29 The high reliability of ultrathin oxides suggests that there is no intrinsic (i.e., not limited by intrinsic defects or thickness variations) reliability limitation to SiO<sub>2</sub> layers at least down to thicknesses of about 16 Å. In fact, more recent projections indicate that oxides down to 14 Å (as measured by ellipsometry) at 1.4 V operating voltage will meet ten year reliability requirements.<sup>30</sup> Several independent groups have also recently reached similarly encouraging reliability projections for such thin SiO<sub>2</sub> gate oxides.<sup>26,31</sup> Other *extrinsic* reliability factors, however, such as particles or contaminants, could still yield an ultimately poorer oxide reliability.

Part of the difficulty in making reliability projections arises from the difference between test conditions and operating conditions. It is clearly not feasible to test individual devices for ten years prior to product incorporation, thus test-

ing must be "accelerated" at higher voltages and temperatures than are actually experienced by typical devices. Making reliability projections from accelerated to actual conditions requires proper scaling for area (from one device area to an entire chip area), voltage, temperature, and the failed fraction of devices. 27,32 Recent results by Stathis et al.,31 Weir et al.,25 and Nicollian et al.33 show that extrapolations of reliability factors, such as the critical defect (trap) density, with voltage scaling changes dramatically at lower voltages, such as those used for testing oxides <20 Å thick. This realization of the change in voltage scaling behavior at low voltages is the largest factor contributing to the improved reliability projections described earlier. In addition, improved macroscopic oxide uniformity across the wafer and wafer-to-wafer has also been shown to give more accurate reliability projections.<sup>25,34</sup> This analysis should not be misinterpreted as meaning that the oxide reliability itself is improved. Rather, the reliability projection becomes more accurate (regardless of whether the projection is for good or poor oxide reliability) with higher macroscopic oxide uniformity.<sup>35</sup> Improving microscopic oxide uniformity should further produce more accurate reliability projections, according to simulation.<sup>36</sup> It has also been demonstrated that making reliability measurements on a large number of samples is important for obtaining better breakdown statistics and accurate projections.<sup>34</sup>

A fundamental mechanism for oxide breakdown in this ultrathin SiO<sub>2</sub> regime was first reported by DeGraeve *et al.*<sup>37,38</sup> as a percolation model. This model describes ultrathin oxide breakdown as the buildup of many "defects" within the SiO<sub>2</sub> layer, where after a certain amount of stress (either constant voltage or constant current through the oxide at a given temperature), a complete path of defects form across the oxide thickness.<sup>37</sup> This point defines breakdown or failure of the oxide. While there is general agreement on the percolation model for oxide breakdown, the defects which act as precursors to breakdown are not defined or specified. The mechanism which leads to the creation of these defects is under debate, and has been proposed as an anode hole injection model<sup>36,39</sup> and a hydrogen release model.<sup>40,41</sup>

It is also important to distinguish between previously reported leakage current projections by simulation for oxide thicknesses measured in accumulation, and the presently accepted methods. Extrapolated leakage current versus gate oxide thickness data from three to five years ago was valuable at the time, when sufficient data for oxides <16 Å was not available. Caution should be used, however, when referring to such extrapolations now, as data from more recent measurement methodology must be adopted for useful comparisons. Much of the understanding for ultrathin oxides have come about only in the past five years, despite decades of research on SiO<sub>2</sub>. This suggests that understanding the reliability and failure mechanisms in high- $\kappa$  dielectrics will require significant effort, especially if any material is to replace SiO<sub>2</sub> within five years, as most roadmaps suggest.

# C. Boron penetration and surface preparation

In addition to leakage current increasing with scaled oxide thickness, the issue of boron penetration through the ox-

ide is a significant concern. The large boron concentration gradient between the heavily doped poly-Si gate electrode, the undoped oxide and lightly doped Si channel causes boron to diffuse rapidly through a sub-20 Å oxide upon thermal annealing, which results in a higher concentration of boron in the channel region. A change in channel doping then causes a shift in threshold voltage, which clearly alters the intended device properties in an unacceptable way. <sup>43</sup> As will be discussed in the next section, incorporating nitrogen into the oxide can greatly reduce boron diffusion.

Some approaches to enhance performance have also focused on surface preparation as a way to provide a flatter, more uniform Si interface in attempts to minimize electron channel mobility degradation (due to scattering at the interface) and gate leakage. 44,45 Growing or depositing sub-15 Å oxides has also been investigated as a potential means for producing high-quality, reproducible and uniform gate oxides, either for use as the gate dielectric or as the bottom layer of a dielectric stack. 46,47 Obtaining high-quality oxides in this thickness regime is challenging, because intrinsic pinhole formation has been reported in ultrathin SiO<sub>2</sub> films. 48-50

Perhaps the most significant benefit resulting from the incorporation of an alternative gate dielectric with a relative permittivity higher than  $\mathrm{SiO}_2$  is the dramatic reduction in the off-state tunneling (leakage) current which is observed in devices using ultrathin  $\mathrm{SiO}_2$  gate dielectric films. Thus, the area of alternative gate dielectrics has gained considerable attention recently because technology roadmaps predict the need for a sub-20 Å Si-oxide gate dielectric for sub-0.1  $\mu$ m CMOS. <sup>4,5</sup>

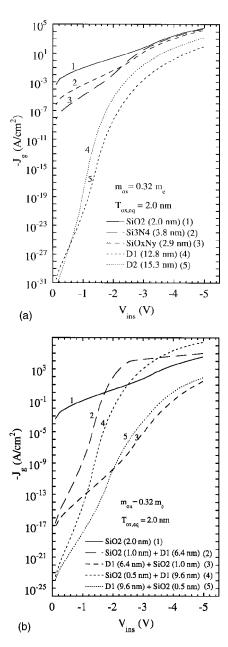

#### D. $SiO_xN_v$ and $Si-N/SiO_2$ dielectrics

The concerns regarding high leakage currents, boron penetration and reliability of ultrathin  $SiO_2$  have led to materials structures such as oxynitrides and oxide/nitride stacks for near-term gate dielectric alternatives. These structures provide a slightly higher  $\kappa$  value than  $SiO_2$  (pure  $Si_3N_4$  has  $\kappa\sim7$ ) for reduced leakage (since the film is physically slightly thicker), reduced boron penetration and better reliability characteristics.  $^{51-53}$  The addition of N to  $SiO_2$  greatly reduces boron diffusion through the dielectric, and has been shown to result from the particular Si-O-N network bonding formed in silicon nitride and oxynitride.  $^{54,55}$  Furthermore, small amounts of N ( $\sim0.1$  at.%) at or near the Si channel interface have been shown to improve device performance.  $^{56}$  Larger amounts of N near this interface degrade device performance, as discussed later.

The simplest approach is to use a pure nitride layer at or near the channel interface, but device performance is typically degraded in these structures. Recent work using remote plasma enhanced chemical vapor deposition (PECVD) to deposit Si-nitride directly on the Si channel<sup>57</sup> resulted in poor *p*MOS performance, with significant degradation of channel mobility and drive current. This degradation is attributed to several factors, including excess charge of pentavalent nitrogen atoms, a high defect density arising from bonding constraints imposed at the interface<sup>58</sup> (which causes increased channel carrier scattering), and from the defect levels in the Si-nitride layer which reside near the valence band of Si. In

contrast, improved electrical properties have been obtained by using various oxynitrides. Yang and Lucovsky demonstrated that an oxynitride alloy with a 1:1 ratio of SiO<sub>2</sub>:Si<sub>x</sub>N<sub>y</sub> can achieve  $t_{\rm eq} < 17 \,\text{Å}$  with a leakage current of  $\sim 10^{-3} \text{ A/cm}^2$  at 1.0 V bias.<sup>56</sup> This leakage current is  $\sim 100 \times$  lower than that for a pure SiO<sub>2</sub> layer of the same thickness, and the leakage reduction arises from both a physically thicker film and from a small amount of N at the channel interface. Song et al. 59 have also shown that a proper choice of thermal processing steps using a NO passivation layer, Si<sub>r</sub>N<sub>v</sub> deposition with SiH<sub>4</sub> and NH<sub>3</sub> and further anneals in NH3 and N2O can achieve oxynitride layers with  $t_{eq} = 18 \text{ Å}$  and a leakage current density of  $10^{-4} \text{ A/cm}^2$  at 1.0 V bias. Guo and Ma<sup>60</sup> have reported results with jet vapor deposited nitrides demonstrating  $t_{eq} = 15 \,\text{Å}$  with a leakage current density of  $J \sim 10^{-4} \text{ A/cm}^2$  at 1.0 V.

Despite these encouraging results from a variety of deposition and growth techniques, scaling with oxynitrides/nitrides appears to be limited to  $t_{\rm eq} \sim 13~{\rm \AA}.^{61}$  Below this, the effects of gate leakage, reliability or electron channel mobility degradation will most likely prevent further improvements in device performance. According to the most recent industry roadmaps,  ${\rm SiO}_x{\rm N}_y$  and  ${\rm Si}_x{\rm N}_y/{\rm SiO}_2$  dielectrics represent current three year near-term solutions for scaling the CMOS transistor.<sup>5</sup>

#### E. Fundamental limitations

Despite the current efforts with SiO<sub>2</sub>, oxynitrides and even high- $\kappa$  gate dielectrics, several potential fundamental limitations could seriously threaten the continued scaling of all gate dielectrics, regardless of the material.<sup>26</sup> First, the electrical thickness of any dielectric is given by the distance between the centroids of charge in the gate and the substrate. This thickness, typically denoted by  $t_{eq}$ , therefore includes the effective thickness of the charge sheet in the gate and the inversion layer in the substrate (channel). These effects can add significantly to the expected  $t_{eq}$  derived from the physical thickness of the dielectric alone. Depletion in the poly-Si gate electrode arises from the depletion of mobile charge carriers in the poly-Si near the gate dielectric interface, particularly in the gate bias polarity required to invert the channel. The result is often that  $\sim 3-4$  Å in the poly-Si electrode nearest to the gate dielectric interface essentially behaves like intrinsic Si, which adds  $\sim 3-4$  Å to the effective dielectric thickness (rather than acting as a metal with a Fermi sea of electrons right up to the dielectric interface). In the best case, the electrode depletion region can be reduced to  $\sim 1-2$ Å for degenerately doped poly-Si electrode right up to the interface, but this is difficult to obtain.

The nature of the inversion charge layer in the Si substrate (or channel, for transistors) contributes about 3–6 Å to the effective  $t_{\rm eq}$  value, thus even for ideal, degenerately doped poly-Si gates, it is difficult to realize an overall  $t_{\rm eq}$  <10 Å in MOSFETs using current process technology. Metal gates offer a possible solution to the gate depletion problem, but the addition of 3–6 Å to the  $t_{\rm eq}$  value from the Si channel will remain. We note that most of the high- $\kappa$  dielectrics discussed later in this review are measured on capacitors and transistors with metal gates. Although metal

gates are convenient for obtaining properties of the dielectric, current CMOS technology does not use metal gates. Therefore, for a given high- $\kappa$  dielectric, any realistic device using current CMOS processing techniques should exhibit a  $t_{\rm eq}$  value 4–8 Å larger than that reported in this review (except where poly-Si gates are noted as being used, and where no quantum mechanical correction has been performed).

Second, the ideal scaling scenario is one in which the operating voltage and transistor dimensions are reduced by the same factor, thus maintaining a constant electric field across the gate dielectric for a given technology node. In practice, however, the feature dimensions have been reduced more rapidly than the operating voltage, thereby causing a rapidly increasing electric field across the gate dielectric. The continually decreasing  $t_{\rm eq}$  value for scaling CMOS also increases the effective electric field in the channel region. This increased electric field pulls the carriers in the channel closer against the dielectric interface, which causes increased phonon scattering of more confined carriers and thereby decreases the channel carrier mobility. At very high electric fields in the channel, such as would exist for  $t_{\rm eq} < 10 \,\rm \mathring{A}$ , interface roughness scattering further reduces carrier mobility. Thus, for  $t_{\rm eq} < 10\,\rm \mathring{A}$ , the combination of these deleterious effects may result in not only reducing the expected performance increase for a given increase in gate capacitance, but may indeed even decrease device performance at fixed supply voltage. If this effect on channel mobility is in fact realized, then it may be the case that no dielectric will be acceptable in the required  $t_{\rm eq}$  range (since this effect depends only on  $t_{eq}$ , not on the material).

#### F. Device structures

In addition to ongoing work in scaling gate dielectrics, there is also a substantial amount of research being conducted toward obtaining a device structure for CMOS, such that the demand for scaling SiO<sub>2</sub> or oxynitrides (and lithography) will be somewhat alleviated. In particular, efforts have been focused on structures such as vertical transistors, 62-65 and double gate planar transistors. 66-68 The premise of double gate transistors arises from the potential of achieving nearly twice the drive current over a planar, bulk CMOS device for a given channel length. Alternatively, a nearly equal drive current could be produced while using a SiO<sub>2</sub> layer that is twice the thickness as that required in the planar geometry (and thereby meet roadmap performance requirements with a much thicker gate oxide). This potential gain from a double gate device is explained simply by the fact that there are two parallel, aligned channels operating simultaneously, compared to one channel in a standard, planar bulk device.

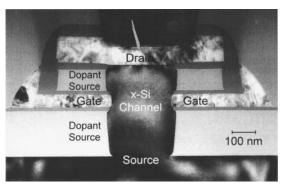

One particularly promising vertical transistor uses a vertical replacement gate (VRG) structure, 62 where standard CMOS processes are used in an innovative way to remove the lithography constraint for defining the gate length. Instead, a deposited oxide layer thickness defines the gate length, which can thus be easily controlled below 50 nm. This dummy oxide layer can then be etched away, followed by growth and deposition of the gate oxide and poly-Si gate electrode, respectively. Figure 6 shows a cross-sectional

FIG. 6. Cross-sectional TEM image of a vertical replacement gate transistor, with a 50 nm gate length and 25 ÅSiO<sub>2</sub> gate oxide (as measured by ellipsometry) (see Ref. 63). © 2000 IEEE, reprinted with permission from IEEE.

transmission electron microscopy (TEM) image of a VRG device with parallel 50 nm gate lengths and 25 Å gate oxides (as measured by ellipsometry) and a single crystal, epitaxially grown Si body. 62 As an example of the potential for increased performance with thicker gate oxides, VRG transistors with 100 nm gate lengths, 25 Å gate oxides, and operating voltage 1.5 V have shown an 80% increase in drive current<sup>63</sup> compared to that required by the SIA Roadmap (at the same off current) using much thinner, sub-20 A oxides. High-performance planar devices reported to date have shown only about 20% increase in drive current compared to that of the roadmap, under comparable operating conditions.<sup>23,24</sup> For 50 nm gate length devices and 1.0 V operation, VRG transistors have been demonstrated to meet the requirements of the roadmap, while still using 25 Å gate oxides. 63 In contrast, no reported planar CMOS devices to date have been able to even approach the drive current and off-current roadmap requirements for 50 nm gate length, 1.0 V operation.

These device approaches to stave off CMOS scaling will continue in parallel with investigations into high- $\kappa$  gate dielectrics. One of these structures may ultimately prove to be a viable replacement for the planar, bulk CMOS transistor and retard the need to scale SiO2 gate oxides. Most device structures under consideration therefore will not immediately suffer from the limitations discussed in the previous section, because a thicker gate oxide reduces the effects of dopant depletion in the poly-Si gate electrode, as well as reduces the electric field present in the channel region. Since these deleterious effects become amplified as the gate oxide thickness decreases, even device structures would eventually suffer from these degradation mechanisms, but in the meantime would afford more time to find other solutions to these problems. In this case, high- $\kappa$  dielectrics can be combined with these device structures to further improve performance and power consumption.

# V. ALTERNATIVE HIGH-K GATE DIELECTRICS

As an alternative to oxide/nitride systems, much work has been done on high- $\kappa$  metal oxides as a means to provide a substantially thicker (physical thickness) dielectric for reduced leakage and improved gate capacitance. In the search to find suitable high- $\kappa$  gate dielectrics for use beyond oxynitride systems, several approaches have been used in fabricat-

ing potential materials candidates. The following sections review the current status of work in this field. We also describe the materials properties considerations that are necessary for determining the best high- $\kappa$  candidate to replace SiO<sub>2</sub> as the gate dielectric for CMOS. It is important to note that we do not compile all of the relevant, measured electrical and physical characteristics on high- $\kappa$  materials into one table. Although a table format can be helpful for organizational purposes, at the present time for high- $\kappa$  gate dielectrics, it is too cumbersome (and potentially misleading) to attempt to provide all of the proper caveats (e.g., leakage current values for the same material system can vary widely depending on surface preparation, deposition method and conditions, gate electrode type, bias voltage ramp rate, stated bias for a given current ( $J@V_{\text{bias}} = 1 \text{ V}$ , or  $V_{\text{FB}} + 1 \text{ V}$ , etc.).

# A. High- $\kappa$ candidates from memory applications

Many of the materials initially chosen as potential alternative gate dielectric candidates were inspired by memory capacitor applications<sup>42</sup> and the resultant semiconductor manufacturing tool development infrastructure.

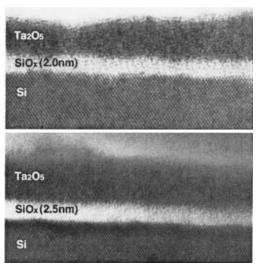

The most commonly studied high- $\kappa$  gate dielectric candidates have been materials systems such as Ta<sub>2</sub>O<sub>5</sub>, <sup>68-78</sup> SrTiO<sub>3</sub>, <sup>79–84</sup> and Al<sub>2</sub>O<sub>3</sub>, <sup>85–95</sup> which have dielectric constants ranging from 10 to 80, and have been employed mainly due to their maturity in memory capacitor applications. With the exception of Al<sub>2</sub>O<sub>3</sub>, however, these materials are not thermodynamically stable in direct contact with Si (this thermodynamic stability is not a requirement for memory capacitors, since the dielectric is in contact with the electrodes, which are typically nitrided poly-Si or metal). An excellent and thorough review on the Ta<sub>2</sub>O<sub>5</sub> system, for both memory capacitor and transistor applications, has been given by Chaneliere et al. 77 The Ta<sub>2</sub>O<sub>5</sub> system is known to exhibit Frenkel— Poole and Schottky transport mechanisms, depending on bias polarity, under typical voltage bias conditions. The mechanisms for relaxation or transient current of Ta<sub>2</sub>O<sub>5</sub> have recently been attributed to a defect band near the conduction band in thin Ta<sub>2</sub>O<sub>5</sub> films, which allows ac transient conduction leakage that follows a widely observed power law decay.78

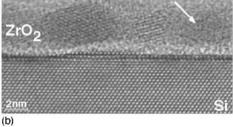

Interfacial reaction, seen in Fig. 7, has been observed for the case of Ta<sub>2</sub>O<sub>5</sub> on Si,<sup>75</sup> as is expected based on thermodynamic arguments discussed later and in agreement with previous work in dynamic random-access memory capacitor applications.<sup>76</sup> As evidenced by these studies, the earliermentioned metal oxides *require* that both the gate electrode and the channel interfaces be modified to limit the amount of reaction.

Interface engineering schemes have been developed to form oxynitrides and oxide/nitride reaction barriers between these high- $\kappa$  metal oxide materials and Si in an attempt to prevent or at least minimize reaction with the underlying Si.<sup>69–74</sup> The passivating properties of such reaction barriers is widely reported.<sup>94</sup> In most cases, this amounts to further scaling the approaches used to form oxynitrides, discussed in the previous section. These barrier layers have been shown to reduce the extent of reaction between the high- $\kappa$  dielectric

FIG. 7. Reaction at the  $Ta_2O_5/Si$  interface is observed resulting in the formation of a thin  $SiO_2$  layer (see Ref. 75).

and Si, as well as to help maintain a high channel carrier mobility.

It is important to note, however, that using an interfacial layer of  $SiO_2$  or another low permittivity material, will limit the highest possible gate stack capacitance, or equivalently, the lowest achievable  $t_{\rm eq}$  value [see Eq. (4)]. In addition, the increased process complexity for the deposition and control of additional ultrathin dielectric layers, as well as scalability to later technology nodes, remains a concern.

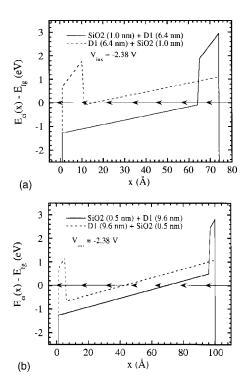

This effect of reduced capacitance can be seen by noting that when the structure contains several dielectrics in series, the lowest capacitance layer will dominate the overall capacitance and also set a limit on the minimum achievable  $t_{\rm eq}$  value. For example, the total capacitance of two dielectrics in series is given by

$$1/C_{\text{tot}} = 1/C_1 + 1/C_2, \tag{10}$$

where  $C_1$  and  $C_2$  are the capacitances of the two layers, respectively. If one considers a dielectric stack structure such that the bottom layer (layer 1) of the stack is  $SiO_2$ , and the top layer (layer 2) is the high- $\kappa$  alternative gate dielectric, Eq. (4) is simplified (assuming equal areas) to

$$t_{\rm eq} = t_{\rm SiO_2} + (\kappa_{\rm ox}/\kappa_{\rm high-\kappa})t_{\rm high-\kappa}. \tag{11}$$

It is clear from Eq. (11) that the minimum achievable equivalent oxide thickness [defined as  $t_{\rm eq}$  in Eq. (11)] will never be less than that of the lower- $\kappa$  (in this case pure SiO<sub>2</sub>) layer. Therefore, much of the expected increase in the gate capacitance associated with the high- $\kappa$  dielectric is compromised. The implications of current transport through such stacked structures will be considered further later.

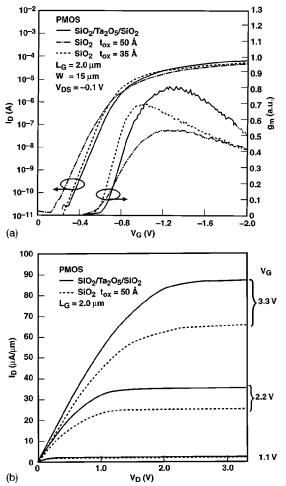

The largest benefit of using  $SiO_2$  as the underlayer of a stack (at the Si channel interface) is that the unparalleled quality of the  $SiO_2$ –Si interface will help maintain a high channel carrier mobility. The prospect of using such  $SiO_2$  interface layers was examined by Kizilyalli and Roy.  $^{70,71}$  In that work, a  $Ta_2O_5$  film was sandwiched between  $SiO_2$  layers located at the substrate and gate (poly-Si) interfaces. The  $SiO_2/Si$  substrate interface layer was formed by a low pres-

FIG. 8. (a) Drain current and transconductance for long channel PMOS transistors incorporating a  $SiO_2/Ta_2O_5/SiO_2$  dielectric stack (see Ref. 70). (b) Comparison of drain current drive and saturation characteristics.

sure (850 mTorr) thermal anneal at 850 °C in  $O_2$ , resulting in a  $\sim 10$ -Å-thick oxide layer. A  $Ta_2O_5$  layer was then deposited by (CVD), followed by a 10 Å capping layer of CVD  $SiO_2$ . The entire structure was then reoxidized in  $O_2$  or  $N_2O$  at 650 °C and 850 mTorr. Given the stacked structure of the dielectric, the total capacitance of the stack will be diminished by the presence of the two lower-permittivity layers.

For the Ta<sub>2</sub>O<sub>5</sub> sandwich, <sup>70,71</sup> using Eq. (11) for the Ta<sub>2</sub>O<sub>5</sub> layer ( $t \approx 50-60$  Å,  $\kappa \approx 20-30$ ), an equivalent oxide thickness  $t_{\rm eq} = 10+10+(3.9/\kappa)t=25-30$  Å is expected. The experimentally determined value from capacitance-voltage (C-V) measurements was in good agreement with this estimate: 23 Å. No charge trapping was observed in the C-V experiments, as evidenced by a lack of hysteresis. This study is an important attempt to demonstrate the feasibility of integrating Ta<sub>2</sub>O<sub>5</sub> into a standard CMOS process, but it is clear that the presence of a SiO<sub>2</sub> layer (or any low- $\kappa$  layer) at either interface limits the ultimate device performance.

Long channel transistor measurements utilizing this stack were also made using poly-Si gates and  $WSi_x$  contacts, as shown in Fig. 8. Figure 8(a) shows drain current and transconductance for long-channel PMOS transistors as a function of gate voltage, and Fig. 8(b) shows a comparison of drain current drive and saturation characteristics. Dopant

activation anneals were accomplished with a relatively low temperature (600–800 °C) rapid thermal anneal process, presumably to avoid crystallization of the Ta<sub>2</sub>O<sub>5</sub> layer and to prevent further SiO2 formation at the interfaces within the constraints of a conventional CMOS process flow. 70,71 An interface state density (Dit) comparable to transistors incorporating only SiO<sub>2</sub> as the gate dielectric was observed based on subthreshold slope measurements. The effective dielectric thickness estimate from the transistor transconductance and drain current measurements results in a larger value,  $\sim 30$  Å. The 20% discrepancy with the MIS capacitor C-V measurements was attributed to partial dopant activation (from the relatively low temperature anneal process). Some degradation in mobility, relative to SiO<sub>2</sub>, was also measured. As expected, leakage currents were well below 1 A/cm<sup>2</sup> as a result of the physically thicker dielectric.

It is essential at this point to distinguish between the requirements for memory  $^{42}$  and transistor applications. Memory capacitors require extremely low leakage currents (typically  $J < 10^{-8}$  A/cm<sup>2</sup>) and very high capacitance density for charge storage, but the interface quality is not as critical. Memory capacitor applications require control of the interface primarily to limit interfacial reactions to keep the total capacitance high. Since the main requirement is that the capacitors store charge, however, current transport along the dielectric interface is not important. Furthermore, no electric field penetration is required below the bottom electrode, so the bottom electrode is often metal, or nitrided poly-Si (heavily doped). All of the requirements amount to the important distinction that the bottom dielectric interface quality is not as critical to capacitor performance.

In contrast, a key requirement of a FET is that the electric field penetrate into the Si channel to modulate carrier transport, and that the dielectric-channel interface be of very high quality. The channel must of course be Si, so any potential high- $\kappa$  dielectric must be compatible with Si. Transistors have more lenient leakage requirements ( $<10^2$  A/cm² for high-performance processors, and  $\sim10^{-3}$  A/cm² for low-power applications), although high capacitance densities are still needed. The most critical distinction between high- $\kappa$  materials requirements for capacitors versus gate dielectrics is the interface and materials compatibility: gate dielectrics *must* form an extremely high-quality interface with Si, and also be able to withstand CMOS processing conditions while in contact (or near contact) with Si.

# B. Issues for interface engineering

It is well known that the industry roadmap presents a major problem for the core transistor gate dielectric, because it calls for a much thinner effective thickness for future alternative gate dielectrics:  $t_{\rm eq} \le 10~{\rm \AA}$ . This would then require the SiO<sub>2</sub> layer to be ~5 Å thick. Such an extremely thin SiO<sub>2</sub> layer is very difficult to obtain with high quality. The resulting voltage drop across the oxide could also lead to significant charge trapping in the film, especially since the interface between such stacked dielectrics may almost certainly contain a large density of traps. Furthermore, such a thin interface layer most likely will *not* prevent reaction between the substrate and any high- $\kappa$  material which is not

FIG. 9. Comparison of stacked and single layer gate dielectrics in a hypothetical transistor gate stack. Either structure results in the same overall gate stack capacitance or equivalent oxide thickness,  $t_{eq} = 10 \text{ Å}$ .

thermodynamically stable to  $SiO_2$  formation on Si, under standard thermal processing required for CMOS (previously discussed pinhole formation in ultrathin  $SiO_2$  is also a concern).

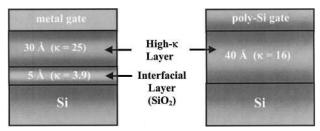

To illustrate this point, an example for obtaining a dielectric stack with  $t_{\rm eq} = 10\,\rm \mathring{A}$  is considered in Fig. 9. One way to achieve this would be to use 5 Å of  $\rm SiO_2(t_{\rm eq} = 5\,\mathring{A})$  as the lower (first) layer, at the Si interface, and 30 Å of a dielectric with  $\kappa = 25$  ( $t_{\rm eq,high-\kappa} \sim 5\,\mathring{A}$ ) as the upper (second) layer. Even for low applied voltages, such a thin layer will have a large enough electric field to create a significant amount of charge trapping. In addition, an oxide layer this thin will allow a large amount of direct electron tunneling into the high- $\kappa$  dielectric, likely causing further deleterious effects to the electrical performance of the stack.

It is important to note, however, that if a *single* layer dielectric can be used, then  $t_{\rm eq} = 10\,\rm \mathring{A}$  can be achieved with 40  $\rm \mathring{A}$  (physical thickness) of a material which only has a moderate permittivity of  $\kappa = 16$  (see Fig. 9). This physical thickness is greater than the total physical thickness of the stack in the earlier example (=35  $\rm \mathring{A}$ ), even though the permittivity of the single layer gate dielectric ( $\kappa = 16$ ) is *much lower* than that of the alternate dielectric in the stack ( $\kappa = 25$ ). In addition, any potential charge trapping at a dielectric-dielectric interface would be avoided. These considerations for the choice of the best high- $\kappa$  materials will be covered in more detail later.

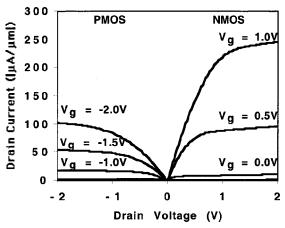

The approach of using an epitaxial high- $\kappa$  gate dielectric, such as SrTiO<sub>3</sub>, requires submonolayer control of the channel interface for dielectric deposition. <sup>79–84</sup> As with the use of all perovskites for dynamic random access memory (DRAM) applications (e.g.,  $Ba_xSr_{1-x}TiO_3$ ,  $Pb_xZr_{1-x}TiO_3$ , etc.), the dielectric must be crystalline (usually polycrystalline) to obtain the enormous permittivities typically observed ( $\kappa > 300$ ). The work done thus far on gate dielectrics therefore has required molecular beam epitaxy (MBE), to obtain interface control and layer-by-layer deposition. Since it is difficult to attain a crystalline oxide on Si, interface engineering has been employed to provide submonolayer deposition of several initial "template" Sr-Si-O layers. 79,82,84 This interface helps reduce reaction due to the thermodynamic instability of SrTiO<sub>3</sub> on Si, and also helps accommodate the difference in lattice constants between Si and SrTiO<sub>3</sub>. Transistors showing encouraging results have been fabricated using SrTiO<sub>3</sub> gate dielectrics, with metal gates (to prevent reaction between SrTiO3 and poly-Si gates) and modified device processing.80,82

FIG. 10. Transistor results for effective gate length  $L_{\rm eff}$ =1.3  $\mu m$  which incorporate a high- $\kappa$  SrTiO<sub>3</sub> gate dielectric (see Refs. 82–84).

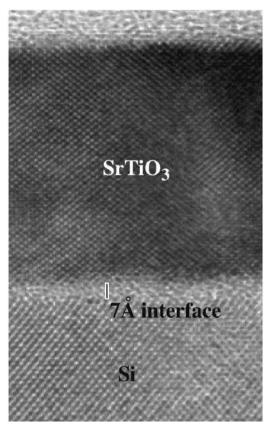

In the study by Eisenbeiser et al., TaN gate electrodes were used, and devices exhibited  $t_{eq} \approx 8 \text{ Å}$  (with quantum mechanical correction to the C-V data) with a leakage current density  $J \sim 10^{-2} \text{ A/cm}^2$  at 1 V bias, for a 110 Å physically thick SrTiO<sub>3</sub> film. 82 Transistors with a 1.2  $\mu$ m effective channel length showed electron and hole mobilities of 221 and 62 cm<sup>2</sup>/V s, respectively. Device characteristics are shown in Fig. 10, with a subthreshold slope of 103 mV/ decade for n-channel devices, 95 mV/decade for p-channel devices. The extracted interface state density showed a low  $D_{\rm ir} \sim 6 \times 10^{10} / {\rm cm}^2$ , but the fixed, low work function ( $\Phi_R$ =4.2 eV) of the TaN gates produced undesirable threshold voltages for p-channel devices.<sup>82</sup> Figure 11 shows that the dielectric deposition process can cause interfacial reaction to occur with Si, resulting in an amorphous SiOx-containing layer.<sup>84</sup> This layer most likely provides a better interface to the Si channel than the SrTiO<sub>3</sub> would, thereby exhibiting encouraging device properties. This MBE approach and the implications of the UHV conditions required for MBE will be discussed further in Sec. VIF.

# C. Recent high- $\kappa$ results

Considering the potential problems and limitations in using a ~5 Å SiO<sub>2</sub> layer in a dielectric stack, it is highly desirable to employ an advanced gate dielectric which is stable on Si, and exhibits an interface quality to Si which is comparable to that of SiO2. This would avoid the need for an interfacial layer and at the same time, the high permittivity of the material could be fully realized. Table I is a compilation of several potential high- $\kappa$  dielectric candidates, with the columns indicating the most relevant properties, which will be discussed in detail throughout the remainder of this review. Although a substantial amount of work has been reported on Ta<sub>2</sub>O<sub>5</sub> as a gate dielectric, <sup>77</sup> and it clearly has many attributes for memory capacitor applications, the inherent thermal instability when in direct contact with Si is a severe limitation as a gate dielectric. We now examine the available results from the literature on such metal oxide and pseudobinary systems, and have categorized them for chemical similarities by group in the periodic table.

FIG. 11. Reaction at the interface of the  $SrTiO_3$  gate dielectric and the Si interface (see Ref. 82).

#### 1. Group IIIA and IIIB metal oxides

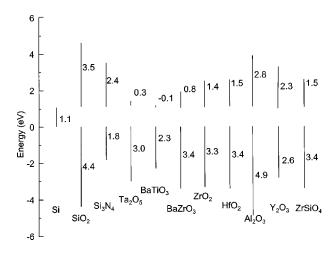

Among the group III candidate dielectrics, alumina  $(Al_2O_3)$  is a very stable and robust material, and has been extensively studied for many applications. Regarding its usefulness as an alternate gate dielectric,  $Al_2O_3$  has many favorable properties, as shown in Table I, including a high band gap, thermodynamic stability on Si up to high temperatures, and is amorphous under the conditions of interest. The drawback is that  $Al_2O_3$  only has  $\kappa \sim 8-10$ , and would therefore make it a relatively short-term solution for industry's needs (1-2 generations). If no longer-term solution is available by the time that a replacement is required, however, such a short-term solution may indeed be suitable. The otherwise

TABLE I. Comparison of relevant properties for high- $\kappa$  candidates.

| Material         | Dielectric constant $(\kappa)$ | Band gap $E_G$ (eV) | $\Delta E_C$ (eV) to Si | Crystal structure(s)                              |

|------------------|--------------------------------|---------------------|-------------------------|---------------------------------------------------|

| SiO <sub>2</sub> | 3.9                            | 8.9                 | 3.2                     | Amorphous                                         |

| $Si_3N_4$        | 7                              | 5.1                 | 2                       | Amorphous                                         |

| $Al_2O_3$        | 9                              | 8.7                 | $2.8^{a}$               | Amorphous                                         |

| $Y_2O_3$         | 15                             | 5.6                 | $2.3^{a}$               | Cubic                                             |

| $La_2O_3$        | 30                             | 4.3                 | 2.3 <sup>a</sup>        | Hexagonal, cubic                                  |

| $Ta_2O_5$        | 26                             | 4.5                 | 1-1.5                   | Orthorhombic                                      |

| $TiO_2$          | 80                             | 3.5                 | 1.2                     | Tetrag.c (rutile, anatase)                        |

| $HfO_2$          | 25                             | 5.7                 | 1.5 <sup>a</sup>        | Mono.b, tetrag.c, cubic                           |

| $ZrO_2$          | 25                             | 7.8                 | 1.4 <sup>a</sup>        | Mono. <sup>b</sup> , tetrag. <sup>c</sup> , cubic |

<sup>&</sup>lt;sup>a</sup>Calculated by Robertson (See Ref. 153).

FIG. 12. HRTEM image of CVD  $Al_2O_3$  on Si with an interfacial Al-silicate reaction layer evident (see Ref. 85).

desirable attributes of Al<sub>2</sub>O<sub>3</sub> have resulted in several recent studies of both its physical and electrical properties as a gate dielectric.

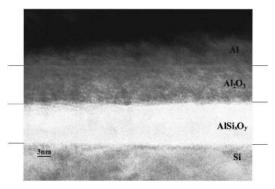

As mentioned before, Al<sub>2</sub>O<sub>3</sub> is thermodynamically stable on Si against SiO<sub>2</sub> formation, but any deposition technique of interest typically operates under nonequilibrium conditions. This means that reactions can occur, and phases can form which are not predicted by equilibrium phase diagrams, although further thermal processing (depending on the temperatures and times involved) will tend to drive the system toward the equilibrium state. Klein et al. 85 studied thin Al<sub>2</sub>O<sub>3</sub> films deposited by CVD (using triethyldialuminum for the Al precursor) at temperatures below 400 °C, and found evidence of an aluminum silicate phase formed at the interface with Si, as seen in Fig. 12. Nuclear resonance profiling (NRP) (which measures the Al concentration) of the films showed a two-layered structure, with the expected Al concentration for Al<sub>2</sub>O<sub>3</sub> in the top layer, and a marked decrease in Al content in the interface layer. XPS indicated the presence of Al-O-Si bonds in an interface layer for a 35 Å deposited Al<sub>2</sub>O<sub>3</sub> film. A significant amount of carbon was also observed in the films ( $\sim$ 20 at. %), but it is nevertheless apparent that kinetics can play an important role in determining the interface structure, which is the most critical region for thin gate dielectrics.

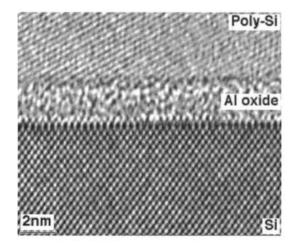

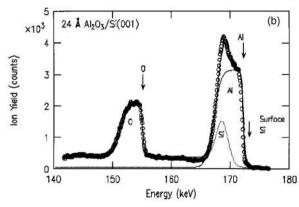

Atomic layer CVD (ALCVD) Al<sub>2</sub>O<sub>3</sub> has been studied by Gusev et al. 87 both physically and electrically, in particular to better understand the interface formed between Si and Al<sub>2</sub>O<sub>3</sub> deposited by this technique. Using NRP, medium energy ion scattering (MEIS) and high-resolution TEM, it was determined that ALCVD-deposited Al2O3 (using trimethylaluminum and water as the Al and O precursors, respectively) could be deposited on H-terminated Si without forming an interfacial SiO<sub>2</sub> layer, as shown in Fig. 13.87 This is an important result, because even though Al<sub>2</sub>O<sub>3</sub> is thermodynamically stable on Si (as mentioned previously), all of the deposition and growth techniques discussed here occur under nonequilibrium conditions. It is therefore usually found that an interfacial SiO<sub>2</sub>-containing layer forms during deposition, between the high- $\kappa$  material (in this case Al<sub>2</sub>O<sub>3</sub>) and the Si substrate. The combination of the three physical analyses used in the study by Gusev et al. 87 show that it is possible to control the interface reactions, at least for this case of precursors and deposition conditions.

bMono.=monoclinic.

<sup>&</sup>lt;sup>c</sup>Tetrag.=tetragonal.

FIG. 13. (a) TEM image of  $Al_2O_3$  film deposited by ALCVD methods on a hydrogen passivated surface from a HF-last process. (b) Corresponding MEIS profile of the film. No interfacial layer is detected (see Ref. 87). © 2000 IEEE, Fig. 13(a) reprinted with permission from IEEE.

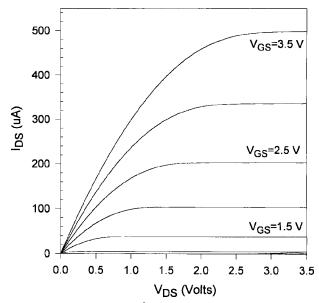

Transistor results for 48 Å of Al<sub>2</sub>O<sub>3</sub> (thermally evaporated Al followed by thermal oxidation) were reported by Chin *et al.*, <sup>88</sup> which exhibited  $t_{\rm eq}$  = 21 Å with a leakage current of ~10<sup>-8</sup> A/cm² at 1 V gate bias, compared to ~10<sup>-1</sup> A/cm² for 21 Å of pure SiO<sub>2</sub>. The Al<sub>2</sub>O<sub>3</sub> films exhibited low stress-induced leakage current (SILC) effects, but did show a high interface state density,  $D_{\rm it}$  >10<sup>11</sup> eV<sup>-1</sup> cm<sup>-2</sup>. A follow-up study by Chin *et al.*<sup>89</sup> achieved a thinner physical thickness of 21 Å Al<sub>2</sub>O<sub>3</sub> to produce  $T_{\rm eq}$  = 9.6 Å, with 22 mV of hysteresis and  $D_{\rm it}$   $\geq$  3  $\times$  10<sup>10</sup> cm<sup>-2</sup>, and a flatband shift  $\Delta V_{\rm FB}$   $\sim$  +600 mV, suggesting negative fixed charge in the film. Very good transistor properties were reported for these films, again with low SILC effects.

Buchanan *et al.*<sup>91</sup> reported *n*MOSFET results on AL-CVD Al<sub>2</sub>O<sub>3</sub> for 0.08  $\mu$ m gate length transistors with poly-Si gates, using standard processing conditions, including a rapid-thermal dopant activation anneal at  $T>1000\,^{\circ}$ C. A leakage current of  $J\sim10^{-1}$  A/cm² (at  $V_{\rm bias}=V_{\rm FB}+1$  V) was measured for  $t_{\rm eq}=13\,\rm \mathring{A}$ , showing a reduction in leakage current of  $\sim100\times$  compared to SiO<sub>2</sub> of the same  $t_{\rm eq}$  value. A trend in fixed charge correlated with Al<sub>2</sub>O<sub>3</sub> thickness was demonstrated, showing that fixed charge increases with decreasing film thickness. Extrapolation of that data indicated that the fixed charge is concentrated near the top, poly-Si interface. Furthermore, an interfacial layer was determined to

contribute  $\sim 8$  Å to the overall the overall  $t_{\rm eq}$  value. The composition of the interface reaction layer is currently not known, but apparently has a  $\kappa$  value larger than that of pure SiO<sub>2</sub>. At an effective field of 1 MV/cm, the channel carrier mobility value for Al<sub>2</sub>O<sub>3</sub> was measured to be smaller by a factor of  $\sim 2 \times (100 \, {\rm cm^2/V} \, {\rm s}$  compared to 220 cm<sup>2</sup>/V s for the universal mobility curve) than that expected by the universal mobility curve. Encouraging drive currents and reliability characteristics were demonstrated for these devices, but the significant mobility degradation clearly indicates some deleterious effects of the ALCVD Al<sub>2</sub>O<sub>3</sub> which warrant further investigation.

The study by Park et al. 90 demonstrated that boron diffuses through ALCVD Al2O3 during dopant activation anneals, and indeed this may be a serious issue for any alternative dielectric. It was reported that dopant activation anneals of 800-900 °C performed on boron implanted poly-Si gates on top of ~60 Å Al<sub>2</sub>O<sub>3</sub> caused significant diffusion of boron through the Al<sub>2</sub>O<sub>3</sub> film and into the n-Si substrate, as evidenced by a flatband shift of  $\sim 1.5$  V. Secondary ion mass spectroscopy profiles also indicated a significant amount of boron in the substrate after anneal. Furthermore, the addition of an oxynitride layer, grown by an N<sub>2</sub>O anneal before Al<sub>2</sub>O<sub>3</sub> deposition, greatly reduced the flatband shift to 90 mV. In a different study by Lee et al., 92 phosphorous diffusion from the  $n^+$  poly-Si electrode into ALCVD Al<sub>2</sub>O<sub>3</sub> was observed under reasonable annealing conditions of 850 °C for 30 min. C-V analysis showed a flatband shift  $\Delta V_{\rm FB}$ = 670-740 mV (depending on the particular dopant incorporation process), which corresponds to  $> 10^{12} \,\mathrm{cm}^{-2}$  of negative fixed charge in the film. These results indicate that in this case, phosphorous not only diffused through the Al<sub>2</sub>O<sub>3</sub> layer, but also introduced fixed charge into dielectric. The authors propose that phosphorous modifies the Al<sub>2</sub>O<sub>3</sub> network, causing negatively charged Al-O dangling bonds. It will continue to be extremely important to identify and understand dopant diffusion in any potential alternative gate dielectric.

Most of the high- $\kappa$  films thus far exhibit a flatband voltage different from that expected for the given choice of electrode and substrate type. As can be seen in Fig. 4, the flatband voltage is ideally determined only by the electrode work function and the electron affinity of the substrate. We therefore very roughly estimate flatband shifts from the data reported in the literature. (Note that this shift is different from the hysteresis flatband shift, which is required to be at least an order of magnitude smaller, and arises from sweeping the C-V curve in opposite polarity directions.) In most studies,  $\Delta V_{\mathrm{FB}}$  values are not reported by the authors. We estimate the value of  $\Delta V_{\rm FB}$  from published C-V curves, however, using work function values reported by Michaelson<sup>95</sup> for a given electrode, along with electron affinity values of 4.18 and 5.3 eV for *n*-Si and *p*-Si substrates, respectively. The  $\Delta V_{\rm FB}$  values we estimate are not intended to be extremely accurate, but rather to show an approximate value, within a few hundred millivolts.

In the studies mentioned above for  $Al_2O_3$  on Si, the measured flatband voltage shift  $\Delta V_{FB}$  is about +300 to +800 mV, compared to that expected by the electrode and sub-

strate types used. This shift is typically interpreted as fixed charge within the film, although it can also arise from oxide damage associated with gate electrode deposition or other forms of processing treatments. As mentioned previously, a positive  $\Delta V_{\rm FB}$  value corresponds to a negative fixed charge. Considering that large  $\Delta V_{\rm FB}$  values have been measured by several independent groups, using different processing conditions and electrodes, this is currently being interpreted as fixed charge within the films.

Several groups have studied the group IIIB metal oxides  $Y_2O_3$ ,  ${}^{96-100}$  La<sub>2</sub>O<sub>3</sub>  ${}^{89,99}$  and Pr<sub>2</sub>O<sub>3</sub>  ${}^{101}$  for the purposes of high- $\kappa$  gate dielectrics. Manchanda and Gurvitch<sup>96,97</sup> thermally oxidized sputtered yttrium films to form Y2O3, for structures with and without an intentional SiO2 layer between the Y<sub>2</sub>O<sub>3</sub> and Si substrate. It was found that structures with  $\sim 260$  Å  $Y_2O_3$  showed very low leakage of  $<10^{-10}$  A/cm<sup>2</sup> at 5 V bias and breakdown fields of  $E_{BD}$ ~4 MV/cm. Capacitors accumulated well with little hysteresis and dispersion, but showed an interface charge density of  $\sim 6 \times 10^{11} \, \text{cm}^{-2}$  and showed an interface trap density of  $\sim 10^{11}\,\text{cm}^{-2}\,\text{eV}^{-1}$ . The dielectric constant of the  $Y_2O_3$ grown on SiO<sub>2</sub> was found to be  $\kappa \sim 17-20$ , but for Y<sub>2</sub>O<sub>3</sub> grown directly on Si, it was found that  $\kappa \sim 12$ . This lower measured permittivity value likely resulted from growth of interfacial SiO<sub>2</sub> during the thermal oxidation step.

Kwo *et al.* investigated  $Y_2O_3$  and  $Gd_2O_3$  films deposited by molecular beam epitaxy (see Secs. VID and VIF), in both crystalline and amorphous phases (as measured by x-ray diffraction). Amorphous films showed lower leakage current densities than crystalline layers, and capacitors showed  $t_{\rm eq} = 10 - 15 \, \text{Å}$  with leakage current densities of  $J = 10^{-6} - 10^{-3} \, \text{A/cm}^2$ , depending on morphology, deposition and postannealing conditions. Breakdown fields were measured as  $E_{\rm BD} \sim 3 \, \text{MV/cm}$ , with interface state density  $D_{\rm it} < 10^{12} \, \text{cm}^{-2} \, \text{eV}^{-1}$ . The C-V curves for these films also exhibited frequency dependence between 100 Hz and 1 MHz.

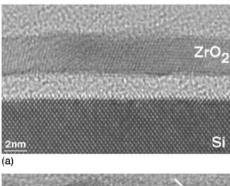

Guha et al. recently investigated relatively thick ( $t_{\rm eq} \sim 45\,{\rm Å}$ )  ${\rm Y}_2{\rm O}_3$  films using an atomic O and Y metal beam epitaxy approach. <sup>99</sup> It was found that quasistatic and high frequency (100 kHz) C-V measurements using Al electrodes overlap well upon postmetallization annealing suggesting that interface state densities less than  $10^{11}\,{\rm cm}^{-2}$  were obtained. Little or no flatband voltage shift was reported. Leakage currents at 1 V in thinner films ( $t_{\rm eq} \sim 21\,{\rm Å}$ ) were reported to be  $\sim 10^{-8}\,{\rm A/cm}^2$ . High resolution TEM and MEIS studies, however, indicate the formation of a columnar polycrystalline structure with  $\sim 10\%$  Si in the film and a 15-Å-thick interfacial SiO<sub>x</sub> layer which was attributed to oxygen diffusion (possibly along grain boundaries) and/or catalytic reaction.

Chambers and Parsons<sup>100</sup> recently investigated the interface associated with  $Y_2O_3$ , Si and oxidized/nitrides Si surfaces. They found that silicides can readily form depending on the kinetics of the deposition process, and that subsequent oxidation of the silicide yields an interfacial silicate layer. They also point out that such reaction kinetics may well be expected for other metal–oxide systems used for alternate gate dielectrics. The flatband voltages for the  $Y_2O_3$  films reported to this point are shifted by  $\Delta V_{\rm FB} = 300-600\,\mathrm{mV}$

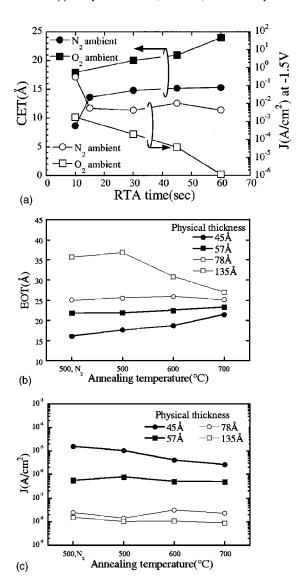

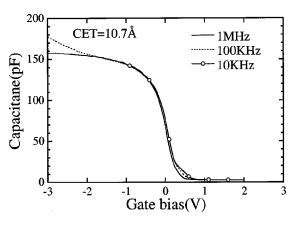

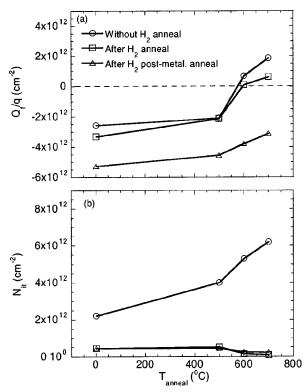

from that expected for an ideal capacitor using the respective electrodes and substrate types in these studies. As with Al<sub>2</sub>O<sub>3</sub>, these are very large voltage shifts measured in a broad array of sample conditions.