### This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

# High-level synthesis algorithm for the design of reconfigurable constant multiplier

Chen, Jiajia; Chang, Chip Hong

2009

Chen, J., & Chang, C. H. (2009). High-level synthesis algorithm for the design of reconfigurable constant multiplier. IEEE Transactions On Computer-Aided Design Of Integrated Circuits And Systems, 28(12), 1844-1856.

## https://hdl.handle.net/10356/80022

## https://doi.org/10.1109/TCAD.2009.2030446

© 2009 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE. This material is presented to ensure timely dissemination of scholarly and technical work. Copyright and all rights therein are retained by authors or by other copyright holders. All persons copying this information are expected to adhere to the terms and constraints invoked by each author's copyright. In most cases, these works may not be reposted without the explicit permission of the copyright holder.

Downloaded on 23 Aug 2022 13:13:33 SGT

## High-Level Synthesis Algorithm for the Design of Reconfigurable Constant Multiplier

Jiajia Chen and Chip-Hong Chang, Senior Member, IEEE

Abstract—Multiplying a signal by a known constant is an essential operation in digital signal processing algorithms. In many application scenarios, an input or output signal is repeatedly multiplied by several predefined constants at different instances. These temporal redundancies can be exploited for the design of an efficient reconfigurable constant multiplier (RCM). An RCM achieves greater hardware savings than the conventional multiple constant multiplication architecture, limited only by the available latency of the subsystem. Motivated by a number of lucrative examples, this paper presents a new high-level design methodology for RCM. Common subexpressions in the preset constants represented in minimum signed-digit system are first eliminated to obtain a minimum depth multiroot directed acyclic graph (DAG). The DAG is converted into a primitive data flow graph (DFG) where mobile adders are identified. By scheduling each mobile adder into a control step within its legitimate time window with the minimum opportunity cost, mutually exclusive adders can be merged with significantly reduced adder and multiplexing cost. The opportunity cost for each scheduling decision is assessed by the probability displacement and disparity measures of the scheduled node as well as its predecessors and successors in the DFG. The algorithm is runtime efficient as exhaustive search for the best fusion of independently optimized constant multipliers has been avoided. Simulation results on randomly generated 12-b constant sets show that the solutions generated by the proposed algorithm are on average 19% to  $25\overline{\%}$  more area-time efficient than the best reported solutions.

*Index Terms*—High-level synthesis, multirate digital signal processing (DSP), reconfigurable constant multiplier (RCM), scheduling.

#### I. INTRODUCTION

**M** ULTIPLICATION of a variable with constant is essential in many digital signal processing (DSP) applications. It can become a throughput bottleneck when many different constant multiplications are iteratively executed in the data path. Such computationally intensive kernels are commonly found in convolutions, correlations, inner products, fast Fourier transform, recursive discrete cosine transform (DCT), finite impulse response (FIR), and infinite impulse response filters. An analysis from over two hundred industry examples

Manuscript received January 7, 2009; revised May 4, 2009. Current version published November 18, 2009. This work was supported by the Singapore Ministry of Education's Academic Research Fund Tier 2 under Grant T208B1216. This paper was recommended by Associate Editor R. Camposano.

J. Chen is with 3M Singapore Pte. Ltd., Singapore 738205 (e-mail: herbert. chen@mmm.com).

C. H. Chang is with the School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore 639798 (e-mail: echchang@ntu.edu.sg).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCAD.2009.2030446

mainly on DSP, communication, graphics, and control applications showed that more than 60% of them have more than 20% of operations that are multiplications with constants [1]. As constant multiplication operations can be reused in many application domains, dedicated hardware resources and programmatic architecture generator capable of delivering a highpeak computational density (in bit operations per unit of silicon area per second) are desired to accelerate a well-defined set of repetitive operations. To maximize the computational density provided by a specialized resource, its use should be generalized, but the more it is generalized, the less suited it is for solving a particular problem [2], [3].

Reconfiguration provides advantages in irregular architectures, and previous work has shown that converting multifunction cores to several reconfigurable field-programmable gate array (FPGA) cores resulted in core area reduction of around 21% and a performance increase of 14% [4]. A FIR filter implementation using a single multiply accumulate (MAC) stage and employing real time reconfiguration to change tap values showed a 37% improvement in clock speed as compared to a static design [5]. However, each time an FPGA fabric is configured, there is a time penalty. Moreover, the time it takes to convert a system description to an FPGA configuration is significant. As the proportion of silicon area devoted to reconfigurable space scales up, the amount of configuration data that is required to set up large parallel structures and the interconnect congestion become a limiting factor.

An alternative approach to optimize computational density and reconfiguration time overhead is to focus on the design methodologies of parametric and lightweight problem-oriented special purpose architecture. Reconfigurable Multiplier Block (ReMB) mappings to FPGA have been proposed in [6]-[11] to specially reduce the complexity of the multiplier block of digital filter. These algorithms are developed to optimize the designs on FPGAs by efficiently utilizing the four-input lookup tables (LUTs). It is based on fixed graph topologies and relies on high-complexity exhaustive search to obtain the minimal solution. The latest known algorithms with similar objective are proposed in [12], [13], and the solution is technology mapped to the standard cell library in an application-specified integrated circuit (ASIC) design flow. Reference [12] reduces the number of partial products of the coefficient multiplier by modified Booth encoding but the sharing of common subexpressions is also limited by the encoding method. In [13], the method uses an existing algorithm [14], [15] to create the directed acyclic graph (DAG) representation for the constant coefficients and performs DAG fusion [13]. The best solution is returned after all admissible assignments have been attempted

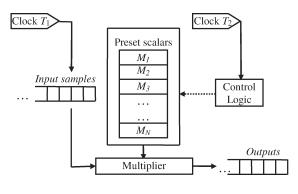

Fig. 1. RCM.

for DAG fusion. However, the use of decimal numbers in DAG fusion assumes no specific binary format. Due to the enormous number of alternatives, it is difficult to explore the totality of adder redundancies over all constant multiplications. Common subexpression sharing may be undermined as the DAG and partial sums of each coefficient multiplier are independently optimized before they are fused. In addition, the algorithm requires exhaustive or quasi-exhaustive searches among existing DAG pairs, which results in high computational complexity.

Fusing independently optimized single constant multipliers is not always expedient for the general parallel multiple constant multiplication problems. Section II of this paper exemplifies several classes of system architectures whereby a reconfigurable constant multiplier (RCM) can be most cost effectively integrated without impediment to the system's throughput. Fig. 1 shows the general structure of an RCM where a serial constant multiplier is shared in several multiplications involving N scalars specified *a priori*. The delay of the RCM is limited by the system's throughput  $T_1$ . The control logic operates at an internal rate  $T_2$  which is d time faster than  $T_1$ . The constant multiplier can be implemented multiplication free by an adder and shifter network. To amortize the processing bandwidth and resource utilization over all multiplications, the logic depth and adder width of the combinatorial adders are to be minimized while eliminating the redundancy among different scalar multiplications. The logic depth is constrained by d and  $T_2$ , which, in turn, are dependent on the cost of realizing the adders (for the same operand length, faster adder is more costly) in the critical path. This relation has led us to the new formulation of RCM design as a programmatic resource scheduling and allocation problem. A rudimentary method adopting an as soon as possible (ASAP) scheduling strategy to solve this problem was proposed in [16]. In this paper, the adder resources are prepensely generated and minimized by common subexpression elimination (CSE). The data dependences of these adder resources are modeled by a data flow graph (DFG) in Section III. A new heuristic algorithm is proposed to schedule the adders in the DFG to maximize the resource utilization over several control steps to generate a more area  $\times$  time (AT) product efficient RCM architecture than previously reported designs. The experimental results are compared with existing methods and discussed in Section IV.

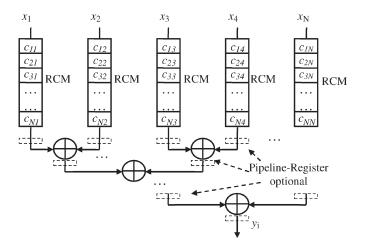

Fig. 2. RCM blocks in matrix multiplication.

#### II. HARDWARE REDUCTION BY RECONFIGURABLE CONSTANT MULTIPLICATIONS

Making a multiplier reconfigurable for different predefined scalars can provide a significant overall cost savings in many DSP applications. This section suggests several interesting application scenarios that motivate the design of efficient RCM. These scenarios show that ingenious deployment of RCMs can lower the hardware cost significantly at little or no penalty to the overall system performance.

A linear time invariant system without feedback can be described by a linear transform

$$\begin{bmatrix} y_1 \\ y_2 \\ \vdots \\ y_N \end{bmatrix} = \begin{bmatrix} c_{11} & c_{12} & \cdots & c_{1N} \\ c_{21} & c_{22} & \cdots & c_{2N} \\ \vdots & \vdots & \ddots & \vdots \\ c_{N1} & c_{N2} & \cdots & c_{NN} \end{bmatrix} \begin{bmatrix} x_1 \\ x_2 \\ \vdots \\ x_N \end{bmatrix}$$

(1)

where N input data  $\mathbf{X} = \{x_i\}$  are mapped by an  $N \times N$ matrix  $C = \{c_{ij}\}$  to generate the outputs  $Y = \{y_i\}$ . This matrix-vector multiplication is an expensive operation, which is also found in the state-space equations of systems involving feedback. In many DSP applications such as digital filtering [17]–[21], error detection and correction [22], fast Fourier and Consine transforms [23], autoregressive model [24], the matrix C consists of constants that are determined a priori from the system specifications. The parallel processing of  $Y = C \times X$  requires the replication of N independent sumof-products (SOP) processing units. Each SOP performs Ndiscrete constant multiplications with different input variables and N-1 additions. In many situations, this quadratic increase in hardware cost is prohibitive due to the limitation in design areas. However, if the N outputs are decimated in time, the  $N \times N$  array of SOP units can be collapsed into N parallel scalar multiplications such that each input data are multiplied by only one out of N constant factors at any cycle, as shown in Fig. 2. The scalar products in each cycle are summed by an adder tree to produce an output element of Y. The adder tree can be pipelined, if necessary, to improve the throughput. In this example, each column of N processing units is reduced to a single RCM.

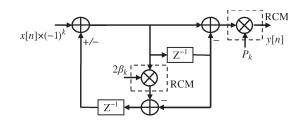

Fig. 3. Recursive Goertzel filter.

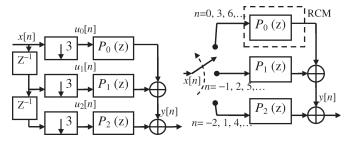

Fig. 4. Polyphase decimation filters (M = 3).

Goertzel algorithm has been used to reduce the complex multiplications to real multiplications in the recursive computation of discrete Fourier transform. Recently, it has been shown that Goertzel kernels also offer significant improvement in quantization noise performance for the DCT used in many multimedia and image compression applications [25]. The transfer function of an N-point DCT is given by

$$H(z) = \frac{P_k(1-z^{-1})}{1-2\beta_k z^{-1}+z^{-2}}$$

(2)

where  $k \in [0, N)$  is the frequency bin index.  $\beta_k = \cos(k\pi/N)$ and  $P_k = 4\beta_k/N$  for all k except k = 1. For k = 1,  $P_1 = (2\sqrt{2}/N)\beta_1$ .

This transfer function can be realized with several resonator configurations of recursive Goertzel filter [25]. All Goertzel kernel structures involve a premultiplication of the difference signal by  $2\beta_k$  in the feedback path and a postmultiplication of the output signal by  $P_k$ . The two sets of scalars can be predetermined by the discrete cosine function according to the frequency bin index k and the transform length N. The same recursive structure can be employed for all frequency bins by multiplexing it in time. One such architecture using two RCM units is shown in Fig. 3. Prestored LUTs have been avoided as the RCM can be implemented multiplication free by combinational adders. To cut down the circuit cost, the RCM can be designed to share the adder resources for different scalar multiplications of different frequency bins by exploiting the time-multiplexed system.

Multirate DSP uses decimators and interpolators to change the sampling rates of a system internally to maximize the performance of DSP system while keeping the cost down. Using the Noble relation [26], a complex DFG can be decomposed into several simpler DSP blocks, which can be processed parallelly at a faster rate. An example of a polyphase decomposition is shown in Fig. 4. The input signal x is down sampled into M subsequences by an M-fold decimator and each of the Mdecimated input sequences is fed to a subfilter. Each subfilter is reduced by a factor of M from the original filter length. The decimator generates one output for every M input samples, and each subfilter can thus be processed at M times slower rate than that of the original input sequence x[n]. In each decimation filter, each MAC implementation is realized by an ReMB. One input sample will be multiplied with N constants generated from the ReMB sequentially and the products are stored into the partial sum store. As the input sample frequency has been reduced by M times in each subfilter, the time interval between two samples are much longer. Therefore, the multiplier block in each subfilter can afford to be processed by a serial-parallel architecture by merging L different coefficient multipliers into an RCM. The adder resources of the L coefficient multipliers can then be shared by processing them serially, provided that the total time taken to produce the L scalar multiples is able to meet the slower output rate of the subfilter. If the subfilter sampling period is not sufficient for one RCM to generate all distinct coefficient multiplier outputs, the filter coefficients can be partitioned into several subsets of distinct constants for an input sample to be concurrently multiplied by a few RCM units.

#### III. PROPOSED HIGH-LEVEL ALGORITHM FOR RCM DESIGN

The scenarios depicted in the previous section show that RCM units are amenable for integration into multirate digital systems or other subsystems when not all constant multiplications are processed in parallel. A practical consequence of these scenarios is the number of different multiplication operations is bound by the ratio of the system's sampling clock period and the critical path delay of the RCM. Our proposed design methodology allows the elementary operators in an RCM to assume different input operands to fulfill a prespecified set of scalar multiplications by suitably rearranging the input bits through a multiplexer network. The latency of the RCM is thus dependent on the control step granularity and the number of control steps used to execute the most time critical operation among a group of prespecified multiplications. The former is defined by the delay of the most critical adder, and the latter is constrained by the logic depth of the RCM. The resolution of any control step can be minimized by reducing the length of the adders in that control step and the worst case delay of each adder can be independently optimized, if necessary, by different parallel structures at the cost of hardware complexity. To meet the latency constraint with the best utilization of silicon resources, our design methodology emphasizes on a global reduction of adder depth while optimizing the number of adders, and the average sizes of adders and multiplexers. If the latency constraint cannot be met by a single RCM, this process itself also identifies underutilized hardware resources and provides an insight into the partitioning of operations into multiple RCM units in a partially parallel implementation.

#### A. Design Problem Formulation

To allow for programmability of different scalar product generations, temporally independent adders are shared across different constant multiplications. This is illustrated with an example of four different constant multiplications using the values

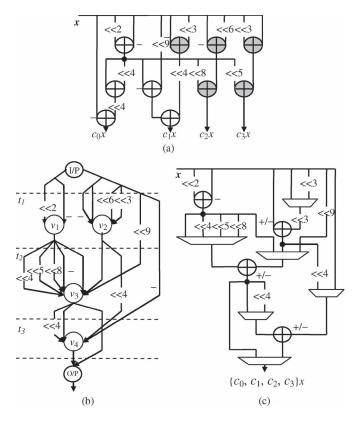

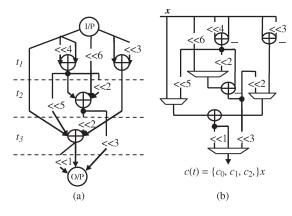

Fig. 5. Example of RCM design. (a) DAGs of constant multipliers. (b) Reduced DFG. (c) Mapping to RCM.

from, [1, Table II]. Fig. 5(a) shows the DAG representation of the four constants after eliminating the common subexpressions. Since an RCM makes only one multiplication at a time, the span of the input variable can be divided into as many number of control steps as, if not more than, the number of adders in the critical path of the DAG. The adders are then scheduled into the control steps without violating the precedence of any connected pair of adders in the DAG. The gray color adders in Fig. 5(a) are called the mobile adders. Mobile adders are critical variants to reduce the implementation complexity as they have some flexibility to be scheduled into more than one control steps without increasing the logic depth of the RCM.

To schedule the adders, the data dependence of DAG is compacted into a primitive DFG. A DFG G has a node set V and an edge set E. Each node,  $v \in V$  represents an adder, and each edge  $e \in E$  is an interconnection between two adders or between an adder and a primary input or output. Each edge is annotated with the output shift and a directed edge implies an intraprecedence constraint of two adders. If the shift amount is negative, it indicates that the node to which this edge is connected is a subtractor. For convenience, adder and subtractor are both called adder. The source and sink of the DFG are the input and output of the RCM, respectively.

In a properly scheduled DFG, each node can only fire when all its predecessor nodes have fired. Upon firing, a node computes the required value and places it on all its output edges. Fig. 5(b) shows a primitive DFG by merging some adders that are not executed concurrently. The number of adders has been reduced significantly from ten to four, but some adders have more inputs than needed to fire. This happens because every time an adder is eliminated, it is accompanied by an increase in the fan-out of some other adder. These contentions are resolved by introducing multiplexers as the point-to-point interconnecting elements between two nodes so that every node v in a properly scheduled DFG has exactly two predecessor nodes firing at time t and satisfies the following dependence relation:

$$v(t) = 2^{e_{l(v(t))}} l(v(t)) + 2^{e_{r(v(t))}} r(v(t))$$

(3)

where v(t) is the output of v at time t. l(v(t)) and r(v(t)) are the left and right predecessor operators of v(t).  $e_u$  denote the amount of shifts applied to  $u \in \{l(v(t), r(v(t))\}.$

To generate a scheduled DFG, cut lines are drawn through the primitive DFG of Fig. 5(b) so that only one adder depth is allowed between two cut lines. For every operator that has a fan-in greater than two, multiplexers are placed at the cut edge. Control steps  $t_1$ ,  $t_2$ , and  $t_3$  define the boundaries between the outputs of one adder or the source, and the inputs of another adder or the sink, by hard wirings or through multiplexers. The resolution of each control step needs not be equal. It is determined by the maximum delay of the adders in the critical paths that are allocated to the control step and their maximum input connection delay through the multiplexer, if the inputs are not directly wired to the adders. Fig. 5(c) shows the architectural mapping of the RCM from the scheduled DFG. Therefore, the design of an area-time efficient RCM can be viewed as the transformation of a given set of constants into a reduced DFG by scheduling and merging of the mobile adders that are not used simultaneously in the same control step. The quality of the solution is measured in terms of the adder and interconnection cost. The adder cost is contributed by the total number of nodes in the set V of the final DFG while the cost of the interconnects is measured by the number and the size of multiplexers used.

#### B. CSE

Without affecting the adder depth, the spatial redundancy in the original DAG is converted into temporal redundancy in the primitive DFG to increase the mobility of as many nodes as possible. The nodes in our DFG are atomic in that they encapsulate information about the elementary operations at bit level granularity. To preserve the atomic information of the nodes after removing the redundant adders, the detection and elimination of common subexpressions are better carried out in a positional representation.

Signed-digit (SD) representations are widely used for coefficient quantization and online arithmetic due to its attractive property for digit-serial and distributive operations. Minimum SD (MSD) [27] and its canonical SD (CSD) subset are two popular symmetric binary SD representations. They allow a fixed point number to be represented by a minimal number of SDs, such that its multiplication with a variable can be realized with reduced depth adder tree. Although representation with more SD terms can help to further reduce the adder cost [28], the improvement is made at the expense of higher logic depth and computational complexity. To reduce the search space, the uniqueness of CSD has been exploited by many CSE algorithms [29], [30] for common subexpressions but the canonicity also limits the number of common subexpressions. For a given magnitude response specification, a signed powersof-two coefficient set with more sharable subexpressions of 101 and  $10\ \overline{1}$  can be synthesized from CSD or MSD by [31]. On the other hand, the advantage of having more subexpression sharing with binary representation [20], [18] is often offset by the higher number of nonzero power-of-two terms over MSD and CSD. Since solutions for MSD and CSD based on weighttwo common subexpressions have the same minimum logic depth of  $\lceil \log_2 n \rceil$ , where n is the maximum number of nonzero digits in a coefficient, the logic depths (LDs) of contention resolution algorithm (CRA) [32] and non-recursive signed common subexpression elimination (NR-SCSE) [30] reported in [20] are incorrect. Experiments run on random coefficient sets for CSE using binary, CSD, and MSD representations [18] concluded that MSD is preferred when seeking minimum delay solution. As minimum delay solution is critical for the scenarios discussed in Section II, MSD representation of integers will be considered.

We minimize the latency of the RCM by minimizing the adder depth. If the latency is relaxed, more control steps than the adder depth can be allocated which makes every adder mobile. Finding an optimal CSE solution for a set of integers in the MSD space is an NP-complete problem. The search space is reduced by detecting only common subexpressions of hamming weight two instead of all possible common subexpressions in the set of integers. These common subexpressions can be categorized into two different types. An even parity subexpression takes the form IOI, where  $I \in \{1, \overline{1}\}$  and O is either void or a string of zeros. The number of zeros in O is the distance of the subexpression. This distinction allows the frequencies of different weight-two subexpressions to be tracked by a simple 2-D *PT* array defined in [30].

Definition 1: A PT array of a set of MSD numbers  $C = \{c_i\}$  is a  $2 \times (B-1)$  dimensional array. The entry in the upper (lower) row and the *j*th column represents the frequency of occurrences of even (odd) parity subexpressions of distance *j*, where  $j = 0, 1, \ldots, B-1$  and *B* is the maximum wordlength of  $c_i$ .

As an example, an MSD representation for the constants of Fig. 5 and its corresponding PT array is given by

An entry in the PT(C) array with value greater than one indicates the presence of a common subexpression in C. The number of adders saved by every common subexpression is one less than its frequency in the PT array. We adopt the MSD generation method of [33] to generate all possible sets of MSD numbers for a given set of constants. With the help of the PTarrays, the MSD set with the highest total saving of adders is selected. The common subexpression with the highest value in the PT array is first identified, and an adder node v is created in a DAG to add the two operands corresponding to the input variable shifted by the positions of the two nonzero digits. If there are more than one entry with the same highest value, the one with the least distance d is selected to minimize the wordlength of the adder. The distance d and coefficients from which the common subexpression is detected are also recorded. These information are used to determine the amount of shifts applied to the left and right operands of v and the firing time t of v. The two nonzero digits of the common subexpression are replaced by zeros in all their occurrences in the set of MSD coefficients. The PT array is updated to reflect the removal of this subexpression. This process of searching for the highest frequency subexpression and the creation of adder node in the DAG to eliminate the common subexpression from the MSD coefficient set is repeated until no entry in the PT array is greater than one. Finally, new nodes are created to add the operands corresponding to the remnant nonzero digits (which are not parts of the common subexpressions) to the outputs of the existing nodes in the DAG accordingly.

#### C. Proposed Mobile Operator Scheduling Scheme

After the aforementioned global CSE process, the total number of adders in the DAG G can be further reduced by merging the adders allocated for different constant multiplications. There are many different ways of merging the adders without violating the intraprecedence relationship of G by routing the inputs to an adder from the output of another adder or the primary inputs through multiplexers. The objective of our proposed adder scheduling scheme is to minimize the total cost of the adders and multiplexers within the given latency constraint. Let D(G) be the adder depth of G. The latency constraint can be sliced into a number of control steps  $t_1, t_2, \ldots, t_{\text{max}}$  so that  $t_{\max} \geq D(G)$  and each control step  $t_i$  has a time resolution sufficient to complete the longest latency addition scheduled to that control step. The time resolution of a control step can be reduced by minimizing the wordlengths of the merged adders allocated to the control step without resorting to faster but more complex adder structure. This is possible if there exist mobile adders.

An adder is said to be mobile if it can be assigned to more than one control step in a DFG. The mobility of a node v in Gis defined as  $\mu(v) = t_{\max} - \delta(v)$ , where  $\delta(v)$  is the number of nodes in the longest path through v from a root to a leaf. The significance of the mobility of a node is that before scheduling, the probability of a node v appearing in a control step  $t_i$ , denoted by  $p_v(t_i)$ , is equal to  $\{\mu(v) + 1\}^{-1}$  for  $t_i \in [t_e, t_l]$ and zero outside this time window, where  $t_e$  and  $t_l$  are the earliest and the latest control steps the node can fire due to the intraprecedence relation of the DFG. Scheduling a mobile adder to a particular control step fixes its probability to one in that control step and to zero in all other control steps. The probability displacement before and after scheduling a mobile node v to a specific control step  $t_j \in [t_e, t_l]$  is given by

$$\Delta p_v(t_i) = \begin{cases} \frac{\mu(v)}{\mu(v)+1}, & \text{if } t_i = t_j \\ -\frac{1}{\mu(v)+1}, & \text{if } t_i \neq t_j \end{cases}$$

(4)

where  $t_i, t_j \in [t_e, t_l]$ .

This change in adder probability is associated with the opportunity cost of merging a mobile adder with the mutually exclusive adders in any control step within the time window defined by  $[t_e, t_l]$ . Two adders in the same control steps are said to be mutually exclusive if they are not used to generate the same scalar multiplier output simultaneously. Merging two mutually exclusive adders results in a saving of one adder but the merged adder assumes the length of the longer adder. In other words, the output of the shorter length adder will be expanded by an amount equal to the difference between the two adder lengths. This will increase the bitwidths of its successive adders and multiplexers. To minimize the cost of RCM, it is important to schedule the mobile node to a control step that will minimize the disparities in the bitwidths among mutually exclusive adders.

The output of each node  $v(t) = a(v) \cdot x(t)$ , where x(t) is the input variable x to the RCM, and the constant a(v) can be expressed in a SD representation as follows:

$$a(v) = \sum_{i=1}^{h(v)} s_i 2^{w_i}$$

(5)

where h(v) is the hamming weight of a(v),  $s_i \in \{-1, 1\}$  is the *i*th SD and  $w_i \in \{0, 1, 2, \dots, w_{\max}\}$  is the weighted bit position of  $s_i$ .

From [34], if the length of the variable x is fixed, the bitwidth of an adder is largely dependent on the difference between the maximum most significant and the maximum least significant SD positions of its input operands. Since the SDs of a(v)are inherited from those of its input operands and the input operands to an adder are commutative, a meaningful metric to assess the disparity of mutually exclusive adders is through the aggregate distance of all SDs to the leading SD position  $w_l$ . Let

$$W(v) = \sum_{i=1}^{h(v)-1} (w_l - w_i).$$

(6)

The disparity of a node v in control step  $t_i$  is defined as

$$\Delta W_v(t_i) = \left| W(v) - \frac{1}{M_i} \times \left( \sum_{j=1}^{M_i} W(u_j) \right) \right|$$

(7)

where  $M_i$  is the total number of existing nodes in control step  $t_i$  that are mutually exclusive to v.

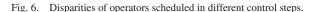

The aggregate distance W(v) measures how compact the sign digits in a(v) are distributed and the disparity of v is an indicator of the bitwidth variation by merging the existing adders in the same control step with v. Fig. 6 shows the disparities of mobile nodes  $v_4$ ,  $v_5$ , and  $v_6$  in control steps  $t_1$  to  $t_3$  after nodes  $v_1$ ,  $v_2$ , and  $v_3$  have been scheduled. Scheduling  $v_4$  to  $t_1$ ,  $v_5$  to  $t_1$  or  $t_2$ , and  $v_6$  to  $t_2$  will minimize the disparity and reduced the costs of the merged adders and multiplexers.

To minimize the bitwidth of the merged adders and multiplexers, mobile nodes should be scheduled to control steps with minimal disparity. However, scheduling a mobile node

to a particular control step will restrict the mobility of its predecessor and successor nodes and hence the probabilities and disparities of their scheduling in other control steps. The overall effect can be accounted by the probability displacement and the time window reduction of the predecessor and successor nodes when evaluating the opportunity cost of scheduling a mobile node v in control step  $t_i \in [t_e, t_l]$ . This opportunity cost is given by

$$\operatorname{Cost}(v, t_i) = \sum_{t=t_e}^{t_l} \Delta p_v(t) \cdot \Delta W_v(t) + \sum_{u \in \operatorname{parent}(v)} \sum_{t=\tilde{t}_e}^{\tilde{t}_l} \Delta p_u(t) \cdot \Delta W_u(t) + \sum_{u \in \operatorname{children}(v)} \sum_{t=\tilde{t}_e}^{\tilde{t}_l} \Delta p_u(t) \cdot \Delta W_u(t) \quad (8)$$

where  $[\tilde{t}_e, \tilde{t}_l]$  denotes the reduced time windows of the predecessor or successor nodes, in general, due to the scheduling of v to control step  $t_i$ . parent(v) and children(v) refer to the immediate predecessors and successors of v, respectively.

To minimize the computational complexity, the opportunity costs are evaluated in batches of identical mobility nodes, commencing from the least mobility nodes. When a node with the least opportunity cost is scheduled, the mobilities of all its affected predecessor and successor nodes are recalculated. After all nodes with the least mobility have been allocated into the DFG, the opportunity costs of all mobile nodes with the next higher mobility are evaluated and the least cost mobile node will be scheduled. The process repeats until all nodes in the DAG have been scheduled into the DFG.

#### D. Adder Merging and Multiplexer Splitting

After all nodes in the DAG have been scheduled into a DFG, the DFG are reduced by merging mutually exclusive nodes in

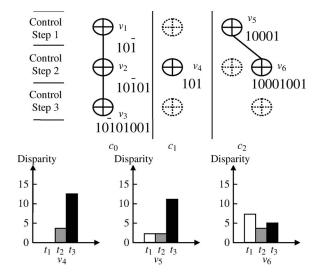

Fig. 7. RCM design (a) before and (b) after multiplexer splitting.

the same control step. For the calculation of disparity, each node v in the DAG is annotated with a set of labels  $\phi(v)$  to indicate its phases of computation in the RCM. An RCM is programmed to output only one product of an input variable x and a constant  $c_i$  in any one phase but each node in a reduced DAG may involve in more than one phase of computation due to the presence of common subexpressions. Using the index of the coefficient as phase number, the criterion for merging two scheduled nodes v and u is given by  $\phi(v) \cap \phi(u) = \emptyset$ . Merging two mutually exclusive nodes v and u introduces at least a multiplexer at either or both inputs of the merged node  $\hat{v}$ , where

$$\operatorname{child}(\hat{v}, t) = c(t) \cdot \operatorname{child}(v, t) + c(t) \cdot \operatorname{child}(u, t)$$

(9)

where the control input to the multiplexer c(t) = 0 if  $t = \phi(v)$  and 1 if  $t = \phi(u)$ . child $(v, t) \in \{l(v(t)), r(v(t))\}$  and child $(u, t) \in \{l(u(t)), r(u(t))\}$  with the constraint that  $l(\hat{v}, t) \neq r(\hat{v}, t)$ .

In general, more than one mutually exclusive node can be merged after scheduling. Every legitimate merging increases the in degree of the merged node in the DFG. Large multiplexers for high in degree nodes can be decomposed into smaller multiplexers. The data inputs to the large multiplexer can be split and rescheduled into one or more smaller multiplexers. The split inputs can be merged into existing smaller multiplexers in the earlier control steps instead of forming new multiplexers provided that these inputs are not required by the adders in two consecutive control steps. Multiplexer splitting attempts to speed up the connection time by reducing the fanins of large multiplexers at the expense of increasing the fan-ins of smaller multiplexers. Fig. 7 shows the result of multiplexer load balancing by extracting four data inputs from an eight-toone multiplexer into a new four-to-one multiplexer so that the interconnection time is reduced in the critical path.

An *m*-to-one multiplexer has *m* data inputs and the number *m* is also called the fan-in of the multiplexer. It should be noted that to reduce the adder width, appropriate amount of shifts have been applied to the inputs and output of each adder during the scheduling and merging processes so that the most significant digit of its a(v) is either 1 or -1. Thus, the data inputs to the multiplexer have nonuniform bitwidth. Unfortunately, the cost of a multiplexer is a function of its bitwidth and the bitwidth of a multiplexer must be catered to the largest data input [13]. This cost may be reduced by splitting

Fig. 8. Flow chart of the proposed algorithm.

a large multiplexer into two smaller multiplexers. Which data inputs to be split can be judicially decided by examining the disparity of each fan-in, which takes a similar form as (7). The disparity of a data input  $f_i$  to an *m*-to-one multiplexer is defined as

$$\Delta b(f_i) = \left| b(f_i) - \frac{1}{m} \times \left( \sum_{j=1}^m b(f_j) \right) \right| \tag{10}$$

where  $b(f_i)$  is the bitwidth of the *i*th data input of the multiplexer.

$\Delta b(f_i)$  measures the deviation of the bitwidth of a specific data input  $f_i$  from the average bitwidth of a multiplexer. Decoding of wide multiplexers requires large logical effort. When the stray capacitance is considered, over a broad range of assumption, the best multiplexer has 4 inputs [35]. For each multiplexer, MUX with  $m \ge 4$ , we first assume that it is cost effective to decompose it into two multiplexers MUX<sub>1</sub> and  $MUX_2$ . Let F be the set of data inputs to MUX sorted by their bitwidths, i.e.,  $F = \{f_i\}_{i=1}^m$  with  $b(f_i) \le b(f_j)$  if i < j. Initially, the data input sets of MUX<sub>1</sub> and MUX<sub>2</sub> are set to  $F_1 = \{f_i\}_{i=2}^m$  and  $F_2 = \{f_1\}$ , respectively. Then, the disparity of the smallest data input of  $F_1$ , i.e.,  $\Delta b_1(f_j)$  for  $j = \arg\{\min(F_1)\}$  is computed and compared with the average bitwidth of MUX<sub>2</sub>,  $ave(F_2)$ . If  $\Delta b_1(f_j) < ave(F_2)$ , then  $F_1 =$  $F_1 - \{f_j\}$  and  $F_2 = F_2 + \{f_j\}$ . The process is repeated with the next smallest data inputs of  $F_1$  until all data inputs of  $F_1$ have been evaluated. If the final fan-in of MUX<sub>2</sub>,  $|F_2| \ge 2$ , MUX will be decomposed into MUX<sub>1</sub> and MUX<sub>2</sub>. Otherwise, MUX will be preserved.

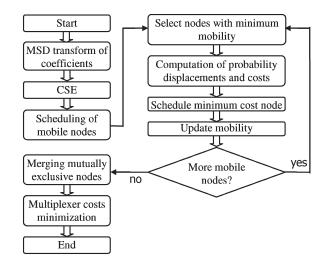

The flow chart in Fig. 8 summarizes the proposed optimization strategy for the design of RCM.

#### E. Design Example

A design example of an RCM for a eight-point Goertzel recursive DCT from [6, Fig. 7] is used to illustrate the proposed adder scheduling algorithm. The three constants of the RCM are  $C = \{362, 392, 473\}$ . The best MSD set with the highest

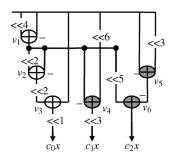

Fig. 9. DAG of constant multipliers with  $C = \{362, 392, 473\}$ .

common subexpression frequency happens to be its CSD subset and its PT array are given as follows:

$$C = \begin{cases} 362\\ 392\\ 473 \end{cases} = \begin{cases} 1 & 0 & \overline{1} & 0 & \overline{1} & 0 & 1 & 0 & 1 & 0 \\ 1 & 0 & \overline{1} & 0 & 0 & 0 & 1 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 & \overline{1} & 0 & \overline{1} & 0 & 0 & 1 \end{cases}$$

$$PT(C) = \begin{bmatrix} 0 & 3 & 0 & 0 & 0 & 2 & 0 & 1 & 1 \\ 0 & 3 & 1 & 4 & 1 & 2 & 0 & 0 & 0 \end{bmatrix}.$$

Following the CSE procedure described in Section III-B, the reduced DAG is shown in Fig. 9.

We assume the number of control steps to be the minimal adder depth of the reduced DAG for the most stringent timing requirement. Therefore,  $t_{max} = 3$ . From the DAG, the number of nodes in the longest path through each node is given by:  $\delta(v_1) = \delta(v_2) = \delta(v_3) = 3$  and  $\delta(v_4) = \delta(v_5) = \delta(v_6) = 2$ . The computation phases of each node in the DFG are  $\phi(v_1) = \{0, 1, 2\}, \ \phi(v_2) = \phi(v_3) = \{0\}, \ \phi(v_4) = \{1\}, \ \phi(v_5) = \phi(v_6) = \{2\}$ . The three fixed nodes are identified by  $\mu(v_1) = \mu(v_2) = \mu(v_3) = 0$ . These three adders will be directly scheduled into control steps  $t_1, t_2$ , and  $t_3$ , respectively. Since  $\mu(v_4) = \mu(v_5) = \mu(v_6) = 1$ , we need to compute the opportunity costs of scheduling these mobile nodes into specific control steps within their legitimate time windows.

Consider  $v_4$ . From (7), since  $a(v_4) = 10\overline{1}0001$ , the aggregate distance of  $v_4$  is  $W(v_4) = (w_3 - w_1) + (w_3 - w_2) = (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0) + (6 - 0$ (6-4) = 8.  $v_4$  can be scheduled into either control step  $t_2$ or  $t_3$ . According to (8), its disparity in  $t_2$  and  $t_3$  can be calculated as follows. If  $v_4$  is scheduled into  $t_2$ ,  $\Delta p_{v_4}(t_2) =$ 0.5 and  $\Delta p_{v_4}(t_3) = -0.5$ . Since  $v_2$  is the only scheduled (fixed) node in  $t_2$  and  $\phi(v_2) \cap \phi(v_4) = \emptyset$ ,  $v_2$  and  $v_4$  are mutually exclusive. From  $a(v_2) = 10\overline{1}0\overline{1}01, W(v_2) = (w_4 - w_1) + (w_4 - w_2) +$  $(w_4 - w_2) + (w_4 - w_3) = (6 - 0) + (6 - 2) + (6 - 4) = 12$  and  $\Delta W_{v_4}(t_2) = |W(v_4) - W(v_2)| = |8 - 12| = 4$ . Similarly,  $v_3$  is the only fixed node in  $t_3$  and  $\phi(v_3) \cap \phi(v_4) = \emptyset$ . From  $a(v_3) =$  $10\overline{1}0\overline{1}0101, W(v_3) = (w_5 - w_1) + (w_5 - w_2) + (w_5 - w_3) + (w$  $(w_5 - w_4) = (8 - 0) + (8 - 2) + (8 - 4) + (8 - 6) = 20$  and  $\Delta W_{v_4}(t_3) = |W(v_4) - W(v_3)| = |8 - 20| = 12$ . As  $v_4$  has no unscheduled predecessor or successor node, according to (9), the opportunity cost of scheduling  $v_4$  into step  $t_2$  is  $Cost(v_4, t_2) = 0.5 \times 4 + (-0.5) \times 12 = -4$ . If  $v_4$  is scheduled into  $t_3$ ,  $\Delta p_{v_4}(t_2) = -0.5$  and  $\Delta p_{v_4}(t_3) = 0.5$ . Hence,  $Cost(v_4, t_3) = (-0.5) \times 4 + 0.5 \times 12 = 4.$

Consider  $v_5$ . Since  $a(v_5) = 1001$ ,  $W(v_5) = 3$ .  $v_5$  can be scheduled into either  $t_1$  or  $t_2$ . Since the only scheduled

TABLE I

TRACES OF COMPUTATION OF THE PROPOSED SCHEDULING ALGORITHM

| Stage | v                     | W(v) | t                     | $\Delta W_v(t)$ | $\operatorname{Cost}(v, t)$ |    |

|-------|-----------------------|------|-----------------------|-----------------|-----------------------------|----|

|       | 11.                   | 8    | $t_2$                 | 4               | -4                          |    |

|       | <i>v</i> <sub>4</sub> | 0    | t <sub>3</sub>        | 12              | 4                           |    |

| 1     | 11-                   | 3    | $t_1$                 | 3               | -3                          |    |

| 1     | <i>v</i> 5            | 5    | $t_2$                 | 9               | 0                           |    |

|       | Ne                    | 19   | <i>t</i> <sub>2</sub> | 7               | 0                           |    |

|       | <i>v</i> <sub>6</sub> | 6 19 | t <sub>3</sub>        | 1               | -3                          |    |

|       | 11-                   | 3    | $t_1$                 | 3               | -2                          |    |

| 2     | <i>v</i> 5            | 5    | 5                     | $t_2$           | 7                           | -2 |

| 2     |                       | 19   | $t_2$                 | 9               | 2                           |    |

|       | v <sub>6</sub>        | 6 19 | $t_3$                 | 1               | -4                          |    |

| 3     | 11-                   | v5 3 |                       | 3               | -2                          |    |

| 5     | v5                    | 5 3  | <i>t</i> <sub>2</sub> | 7               | 2                           |    |

adder in  $t_1$ ,  $v_1$ , is involved in all phases of computation,  $\phi(v_1) \cap \phi(v_5) \neq \emptyset$ . There is no fixed node that is mutually exclusive with  $v_5$  in  $t_1$  and  $\Delta W_{v_5}(t_1) = |W(v_5) - 0| = 3$ . In addition,  $v_2$  is the only fixed node in  $t_2$  and  $\phi(v_2) \cap$  $\phi(v_5) = \emptyset$ . Thus,  $v_2$  and  $v_4$  are mutually exclusive and  $\Delta W_{v_5}(t_2) = |W(v_5) - W(v_2)| = 9$ . If  $v_5$  is scheduled into  $t_1$ ,  $\Delta p_{v_5}(t_1) = 0.5$  and  $\Delta p_{v_5}(t_2) = -0.5$  and its successor node,  $v_6$ , can still be scheduled into  $t_2$  and  $t_3$ . There is no change in the probability of  $v_6$  and  $\Delta p_{v_6}(t_2) = \Delta p_{v_6}(t_3) = 0$ . According to (9),  $Cost(v_5, t_1) = 0.5 \times 3 + (-0.5) \times 9 = -3$ . If  $v_5$  is scheduled into  $t_2$ ,  $\Delta p_{v_5}(t_1) = -0.5$  and  $\Delta p_{v_5}(t_2) =$ 0.5. Its successor node,  $v_6$ , has to be scheduled into  $t_3$ . Therefore,  $\Delta p_{v_6}(t_2) = -0.5$  and  $\Delta p_{v_6}(t_3) = 0.5$ . Since  $a(v_6) = 1000\overline{101001}, W(v_6) = 19$ . There is only one fixed node,  $v_2$ , in  $t_2$  and  $\phi(v_2) \cap \phi(v_6) = \emptyset$ . Thus,  $\Delta W_{v_6}(t_2) =$  $|W(v_6) - W(v_2)| = 7$ .  $v_3$  is the only fixed node in  $t_3$  and  $\phi(v_3) \cap \phi(v_6) = \emptyset$ . Thus,  $\Delta W_{v_6}(t_3) = |W(v_6) - W(v_3)| =$ 1. According to (9),  $Cost(v_5, t_2) = [(-0.5) \times 3 + 0.5 \times 9] +$  $[(-0.5) \times 7 + 0.5 \times 1] = 0.$

Now, consider node  $v_6$ . Since  $v_6$  can be scheduled into either  $t_2$  or  $t_3$ . If  $v_6$  is scheduled into  $t_2$ ,  $\Delta p_{v_6}(t_2) = 0.5$  and  $\Delta p_{v_6}(t_3) = -0.5$ . Its predecessor node,  $v_5$ , has to be scheduled into  $t_1$ . Thus,  $\Delta p_{v_5}(t_1) = 0.5$  and  $\Delta p_{v_5}(t_2) = -0.5$ .  $\operatorname{Cost}(v_6, t_2) = [0.5 \times 7 + (-0.5) \times 1] + [0.5 \times 3 + (-0.5) \times 9] = 0$ . If  $v_6$  is scheduled into  $t_3$ ,  $\Delta p_{v_6}(t_2) = -0.5$  and  $\Delta p_{v_6}(t_3) = 0.5$ .  $v_5$  can still be scheduled into  $t_1$  and  $t_2$ . Since there is no change in the probability of  $v_5$ ,  $\Delta p_{v_5}(t_1) = \Delta p_{v_5}(t_2) = 0$ . According to (9),  $\operatorname{Cost}(v_6, t_3) = (-0.5) \times 7 + 0.5 \times 1 = -3$ .

The traces of computation are summarized in Table I. In Stage 1, the minimum opportunity cost is -4. Consequently,  $v_4$ is scheduled into  $t_2$  and become a fixed node. The opportunity costs of scheduling  $v_5$  and  $v_6$  need to be reevaluated after updating their mobilities. The traces of computation are shown in Stage 2 of Table I, from which  $v_6$  is scheduled into  $t_3$  with the minimum opportunity cost. After fixing  $v_6$  in  $t_3$ , the only mobile node is  $v_5$ . It can be scheduled in either  $t_1$  or  $t_2$  as computed in Stage 3. The scheduling of  $v_5$  into  $t_1$  has less opportunity cost, hence  $v_5$  is scheduled into  $t_1$ .

After all mobile nodes have been fixed, the mutually exclusive nodes in the same control steps are merged. Multiplexers are inserted between the nodes with fan-in greater than two and their immediate predecessor nodes or primary inputs. Since all

Fig. 10. RCM of the design example. (a) DFG. (b) Circuit architecture.

multiplexers have fan-in less than four, no multiplexer splitting is performed. The optimized DFG and the RCM circuit are shown in Fig. 10.

#### IV. EXPERIMENTAL RESULTS AND DISCUSSION

In this section, the area and time complexities of the RCM solutions generated by our proposed method are evaluated and compared against other methods in the literature. In the first part of the experiments, four commonly cited sets of constants in the ReMBs are considered. Set A is obtained from [7, Fig. 6], Sets B and C are taken from [6, Figs. 7 and 8], respectively, and Set D is taken from [9, Fig. 6]. Unitless cost function in [13] is adopted for the area estimate. In this estimate, the cost of an operator is equal to  $a \cdot k$ , where k is the bitwidth of the operator and a is a constant of proportionality. The value of a can be characterized by the implementation technology. Technology mapping of typical operators using a commercial 0.18- $\mu$ m standard cell library [13] yields  $a_{m-1$  multiplexer =  $14 \cdot m$ ,  $a_{adder} = 67$ ,  $a_{subtractor} = 75$ , and  $a_{adder/subtractor} = 98$ measured in square micrometers. With Artisan TSMC 0.18- $\mu$ m standard cell library,  $a_{m-1 \text{multiplexer}} = 13.3 \cdot m$  and  $a_{\text{adder}} =$ 69.9, which show that the same cells from different libraries developed for the same process technology have very similar areas. With Avant! Passport 0.35-µm standard cell library,  $a_{m-1$  multiplexer} = 1.17 \cdot m,  $a_{adder} = 5.0$ ,  $a_{subtractor} = 5.66$ , and  $a_{\rm adder/subtractor} = 7.0$  measured in number of equivalent gates.

The numbers of operators and multiplexers used in our designs in RCM and their area costs, "I" and "II" estimated based on 0.18- and 0.35- $\mu$ m cell libraries, respectively, are presented in Tables II–V. The results are compared with those reported in [6], [7], and [9] by ReMB methods, [13] by DAG fusion algorithm, and [16] by our preliminary ASAP scheduling approach. The bitwidth of the input signal to the RCM is assumed to be 8 b for all designs. It should be noted that the result of DAG fusion for Set C is different from that of [13] because of an erratum in [13]. The inputs to the top 2-1 multiplexer in, Fig. 16(c)[13] should be multiplied by "16 and 4," instead of "4 and 2." We have verified this using the online tool provided by authors of [13]. The results reported in Table IV are based on the corrected design of DAG fusion.

From Tables II–V, the proposed RCM design algorithm generates lower cost solutions than the classical ReMB approaches. On average, the proposed algorithm is 19.3% more

TABLE II

Area Cost Estimation for Data Set A

| Algorithm          | Adder      | Subtractor | Adder/<br>Subtractor                                 | Multiplexers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Ι    | Π     |

|--------------------|------------|------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|

| DAG<br>Fusion [13] | 0          | 0          | 1× (12-bit)<br>1× (14-bit)                           | 1×Mux <sub>3-to-1</sub> (14-bit)<br>1×Mux <sub>7-to-1</sub> (16-bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4704 | 361.7 |

| ReMB [7]           | 1×(10-bit) |            | 1×(10-bit)<br>2×(11-bit)<br>1×(12-bit)<br>1×(16-bit) | $eq:linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_line$ | 9578 | 715.3 |

| ASAP [16]          | 0          | 0          | 1× (12-bit)<br>1× (14-bit)                           | 1×Mux <sub>3-to-1</sub> (14-bit)<br>1×Mux <sub>4-to-1</sub> (11-bit)<br>1×Mux <sub>4-to-1</sub> (16-bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4648 | 357.0 |

| Proposed           | 0          | 0          | 1× (12-bit)<br>1× (14-bit)                           | 1×Mux <sub>3-to-1</sub> (14-bit)<br>1×Mux <sub>4-to-1</sub> (11-bit)<br>1×Mux <sub>4-to-1</sub> (16-bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4648 | 357.0 |

TABLE III Area Cost Estimation for Data Set B

| Algorithm          | Adder                                  | Subtractor                                | Adder/<br>Subtractor     | Multiplexers                                                                                                                                 | Ι    | Π     |

|--------------------|----------------------------------------|-------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|-------|

| DAG<br>Fusion [13] | 1×(19-bit)                             | 1× (16-bit)                               |                          | 2×Mux <sub>2-to-1</sub> (12-bit)<br>1×Mux <sub>2-to-1</sub> (19-bit)<br>1×Mux <sub>3-to-1</sub> (16-bit)<br>1×Mux <sub>3-to-1</sub> (20-bit) | 6365 | 496.0 |

| ReMB [6]           | 1×(11-bit)<br>1×(12-bit)<br>1×(17-bit) | 0                                         |                          | 3×Mux <sub>2-to-1</sub> (11-bit)<br>1×Mux <sub>2-to-1</sub> (14-bit)                                                                         |      | 386.7 |

| ASAP [16]          | 2×(17-bit)                             | 0                                         | 1×(10-bit)<br>1×(17-bit) | 1×Mux <sub>2-to-1</sub> (13-bit)<br>2×Mux <sub>2-to-1</sub> (17-bit)                                                                         | 6240 | 486.5 |

| Proposed           | 1×(17-bit)                             | 1× (11-bit)<br>1× (12-bit)<br>1× (14-bit) | 0                        | 1×Mux <sub>2-to-1</sub> (14-bit)<br>1×Mux <sub>2-to-1</sub> (16-bit)<br>1×Mux <sub>2-to-1</sub> (17-bit)<br>1×Mux <sub>3-to-1</sub> (18-bit) | 5986 | 467.3 |

TABLE IV Area Cost Estimation for Data Set C

| Algorithm          | Adder | Subtractor  | Adder/<br>Subtractor       | Multiplexers                                                                                             | Ι    | П     |

|--------------------|-------|-------------|----------------------------|----------------------------------------------------------------------------------------------------------|------|-------|

| DAG<br>Fusion [13] | 0     | 1× (16-bit) | 1× (12-bit)                | $2 \times Mux_{2-to-1}(12-bit)$<br>$1 \times Mux_{3-to-1}(16-bit)$<br>$1 \times Mux_{3-to-1}(18-bit)$    |      | 349.7 |

| ReMB [6]           | 0     | 1×(15-bit)  | 1×(12-bit)<br>1×(15-bit)   | $2 \times Mux_{2-to-1}(10-bit)$<br>$1 \times Mux_{2-to-1}(15-bit)$                                       | 4751 | 355.7 |

| ASAP [16]          | 0     | 0           | 1× (10-bit)<br>1× (14-bit) | 1×Mux <sub>2-to-1</sub> (10-bit)<br>1×Mux <sub>2-to-1</sub> (11-bit)<br>1×Mux <sub>3-to-1</sub> (16-bit) | 3612 | 273.0 |

| Proposed           | 0     | 0           | 1× (10-bit)<br>1× (14-bit) | 1×Mux <sub>2-to-1</sub> (10-bit)<br>1×Mux <sub>2-to-1</sub> (11-bit)<br>1×Mux <sub>3-to-1</sub> (16-bit) | 3612 | 273.0 |

area efficient than ReMB algorithms, [6], [7] and [9], which are originally designed to target on FPGAs. This indicates that the ReMB approaches may not be as efficient on ASIC implementation as they are on FPGA. For ASIC implementation, a more insightful conclusion can be drawn from the comparison with the solutions generated by DAG fusion [13], which is not tailored to dedicated configurable logic cell structure. On average, the proposed algorithm is still 7% more area efficient than this latest and most competitive method [13]. This saving is mainly contributed by the holistic consideration of opportunity costs in scheduling mobile adders. Merging adders with minimal disparity has successfully reduced the overall bitwidth of the adders and multiplexers. As shown in Tables III–V,

| Algorithm          | Adder       | Subtractor | Adder/<br>Subtractor       | Multiplexers                                                         | Ι    | П     |

|--------------------|-------------|------------|----------------------------|----------------------------------------------------------------------|------|-------|

| DAG<br>Fusion [13] | 1× (10-bit) | 0          | 1× (14-bit)                | 2×Mux <sub>2-to-1</sub> (10-bit)<br>1×Mux <sub>2-to-1</sub> (14-bit) | 2994 | 227.3 |

| ReMB [9]           | 1×(13-bit)  |            |                            | $1 \times Mux_{2-to-1}(8-bit)$ $1 \times Mux_{2-to-1}(12-bit)$       |      | 265.0 |

| ASAP [16]          | 0           |            |                            | 1×Mux <sub>2-to-1</sub> (10-bit)<br>1×Mux <sub>2-to-1</sub> (14-bit) |      | 224.0 |

| Proposed           | 0           | 0          | 1× (10-bit)<br>1× (14-bit) | $1 \times Mux_{2-to-1}(10-bit)$ $1 \times Mux_{2-to-1}(11-bit)$      | 2940 | 217.0 |

TABLE V Area Cost Estimation for Data Set D

TABLE

VI

Synthesized Areas of Data Sets A–D (in Square Micrometers)

| Data sets | Algorithms | RCA      | Improvement | CLA      | Improvement |

|-----------|------------|----------|-------------|----------|-------------|

|           | ReMB       | 17360.48 | 62.67%      | 18108.92 | 61.00%      |

| A         | DAGfusion  | 7477.75  | 13.35%      | 8212.88  | 14.01%      |

|           | Proposed   | 6479.83  |             | 7061.95  |             |

|           | ReMB       | 11991.68 | -0.72%      | 12520.57 | -2.47%      |

| В         | DAGfusion  | 11901.86 | -1.48%      | 12294.37 | -4.36%      |

|           | Proposed   | 12078.16 |             | 12829.92 |             |

|           | ReMB       | 9749.68  | 38.76%      | 9972.55  | 34.82%      |

| C         | DAGfusion  | 7221.61  | 17.32%      | 7693.96  | 15.52%      |

|           | Proposed   | 5970.89  |             | 6499.78  |             |

|           | ReMB       | 8086.48  | 28.14%      | 8226.19  | 26.04%      |

| D         | DAGfusion  | 6127.23  | 5.16%       | 6300.2   | 3.43%       |

|           | Proposed   | 5811.22  |             | 6083.99  |             |

TABLE VII

Synthesized Delays of Data Sets A–D (in Nanoseconds)

| Data sets | Algorithms | RCA  | CLA  |

|-----------|------------|------|------|

|           | ReMB       | 9.25 | 6.06 |

| А         | DAGfusion  | 6.65 | 4.45 |

|           | Proposed   | 6.72 | 4.6  |

|           | ReMB       | 9.81 | 6.06 |

| В         | DAGfusion  | 9.15 | 6.49 |

|           | Proposed   | 8.36 | 5.89 |

|           | ReMB       | 9.17 | 6.1  |

| С         | DAGfusion  | 8.15 | 5.2  |

|           | Proposed   | 7.27 | 4.99 |

|           | ReMB       | 7.61 | 4.69 |

| D         | DAGfusion  | 7.95 | 4.79 |

|           | Proposed   | 7.85 | 4.78 |

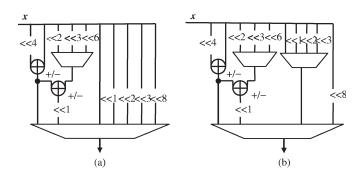

the bitwidths of the arithmetic operators and multiplexers of the proposed designs are always smaller than those of [13]. In addition, the proposed multiplexer splitting also helps. For example, in Table II, instead of having a 16-b seven-to-one multiplexer [13], our proposed algorithm divides the large fanin multiplexer into multiplexers of lower fan-in and bitwidth. The improved scheduling method also outperforms ASAP in data sets B and D.

To corroborate the merits of our proposed algorithm, the designs are technology mapped to TSMC 0.18-µm standard cell library using Synopsys Design Compiler. The synthesized areas and delays are tabulated in Tables VI and VII, respectively. Ripple carry adders (RCAs) and carry look-ahead adders (CLAs) are used to demonstrate the two different scenarios of using the faster but more costly adders versus using the slower but simpler adders for the RCM design under the same timing constraint. Due to the multiplexer overheads for reconfigurability

TABLE VIII AT PRODUCTS OF DATA SETS A–D (IN SQUARE MICROMETERS × NANOSECONDS)

| Data sets | Algorithms | RCA      | Improvement | CLA      | Improvement |

|-----------|------------|----------|-------------|----------|-------------|

|           | ReMB       | 160584.4 | 72.88%      | 109740   | 70.40%      |

| A         | DAGfusion  | 49727.04 | 12.43%      | 36547.32 | 11.12%      |

|           | Proposed   | 43544.46 |             | 32484.97 |             |

|           | ReMB       | 117638.4 | 14.17%      | 75874.65 | 0.40%       |

| В         | DAGfusion  | 108902   | 7.28%       | 79790.46 | 5.29%       |

|           | Proposed   | 100973.4 |             | 75568.23 |             |

|           | ReMB       | 89404.57 | 51.45%      | 60832.56 | 46.68%      |

| С         | DAGfusion  | 58856.12 | 26.25%      | 40008.59 | 18.93%      |

|           | Proposed   | 43408.37 |             | 32433.9  |             |

|           | ReMB       | 61538.11 | 25.87%      | 38580.83 | 24.62%      |

| D         | DAGfusion  | 47811.48 | 4.59%       | 30177.96 | 3.63%       |

|           | Proposed   | 45618.08 |             | 29081.47 |             |

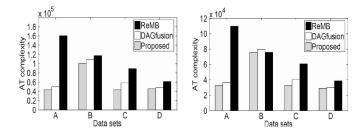

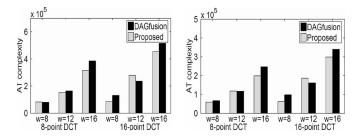

Fig. 11. AT complexity comparison of proposed RCM, ReMB methods, and [13] with (left) RCA and (right) CLA adders for data sets A–D.

and the reduced number of adders, the overall area increment caused by the use of CLA over RCA is not as significant.

The area and delay values are combined into an overall AT complexity evaluation. The AT product of each design is shown in Table VIII. The results demonstrate the effectiveness of our proposed algorithm in reducing both the critical path delay and the logic area for different RCM designs. On average, our proposed algorithm generates RCM designs of 41.09% and 35.53% lower AT complexities than ReMB with RCA and CLA implementations, respectively. Comparing with DAGfusion, our AT products are 12.63% and 9.74% lower with RCA and with CLA implementations, respectively. The AT complexity comparisons are shown in Fig. 11. The reduction of AT product is attributed in part to the CSE using MSD representation and in part to the minimization of average adder disparity in each control step. The balanced adder graph after CSE and the reduction in adder/subtractor and multiplexer bitwidths play a crucial role in shortening the critical path delay.

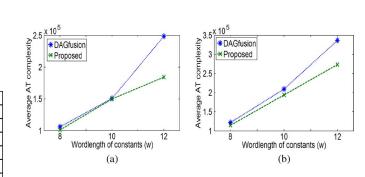

The RCM of the  $2 \times \alpha$  multipliers of type A Goertzel recursive DCT structure in [25] are implemented for two different DCT transform lengths N = 8 and N = 16. The coefficients are generated in three levels of precision w = 8, 12, and 16 b. Every design is implemented with two types of adders, RCA and CLA. The synthesis results are presented in Table IX. Since [13] is the latest and most relevant method for ASIC implementation, the AT product is compared with that in [13] in Fig. 12. On average, the proposed algorithm reduces the AT product by 8.51% and 10.60% over DAG fusion method [13] based on RCA and CLA, respectively. The AT products are also evaluated with the constant sets from seven FIR filters in Table X. The results show that the proposed method is able to generate more area-time efficient solutions in general.

TABLEIXSynthesized Area (A) (in Square Micrometers), Delay (T) (in<br/>Nanoseconds), and AT Product (in Square Micrometers  $\times$ <br/>Nanoseconds) of  $2 \times \alpha$  Multipliers in 8-Point/16-Point<br/>Type A Goertzel Recursive DCT Structures

| DCT        | Algorithms | Algorithms RCA |      | CLA      |         |     |          |

|------------|------------|----------------|------|----------|---------|-----|----------|

| attributes | Aigonums   | A              | Т    | AT       | А       | Т   | AT       |

| 8-point,   | DAGfusion  | 10854.0        | 7.3  | 79668.7  | 11446.1 | 5.8 | 66731.0  |

| w=8        | Proposed   | 10824.1        | 7.6  | 82696.2  | 11592.5 | 5.1 | 58542.1  |

| 8-point,   | DAGfusion  | 15863.6        | 10.3 | 163395.1 | 16914.7 | 6.9 | 116880.9 |

| w=12       | Proposed   | 16349.3        | 9.3  | 151394.1 | 17433.7 | 6.8 | 117677.2 |

| 8-point,   | DAGfusion  | 25985.5        | 14.8 | 385369.9 | 28044.9 | 8.8 | 246794.9 |

| w=16       | Proposed   | 24811.1        | 12.6 | 313370.7 | 27163.4 | 7.3 | 198835.9 |

| 16-point,  | DAGfusion  | 13771.3        | 9.5  | 130827.3 | 14463.2 | 6.8 | 98349.7  |

| w=8        | Proposed   | 10787.5        | 7.9  | 85221.4  | 11422.9 | 5.5 | 62825.7  |

| 16-point,  | DAGfusion  | 21298.9        | 11.1 | 235353.3 | 22463.2 | 7.2 | 161285.6 |

| w=12       | Proposed   | 23830.3        | 11.6 | 276908.4 | 25340.5 | 7.4 | 186252.8 |

| 16-point,  | DAGfusion  | 35239.9        | 14.6 | 514502.3 | 37405.4 | 9.1 | 339640.7 |

| w=16       | Proposed   | 34554.6        | 13.2 | 454739.1 | 37804.5 | 7.9 | 299033.9 |

Fig. 12. AT complexity comparison of proposed RCM and [13] for type A Goertzel recursive DCT with (left) RCA and (right) CLA adders.

TABLE X AT PRODUCTS OF FIR FILTER COEFFICIENT SETS (IN SQUARE MICROMETERS  $\times$  NANOSECONDS)

| FIR filter  | Algorithms | AT product (RCA) | AT product (CLA) |

|-------------|------------|------------------|------------------|

| FIR1 [36]   | DAGfusion  | 26490.7          | 19084.7          |

| FIKT [50]   | Proposed   | 18087.1          | 12793.4          |

| FIR2 [37]   | DAGfusion  | 17195.4          | 13336.5          |

| FIK2 [57]   | Proposed   | 15497.5          | 11809.4          |

| FIR3 [38]   | DAGfusion  | 19208.2          | 14389.7          |

| FIK5 [56]   | Proposed   | 14900.6          | 11357.7          |

| FIR4 [39]   | DAGfusion  | 103410.2         | 80104.6          |

| FIK4 [39]   | Proposed   | 111724.1         | 74093.8          |

| FIR5 [40]   | DAGfusion  | 106368.3         | 76512.9          |

| FIK5 [40]   | Proposed   | 95732.5          | 64922.0          |

| FIR6 [38]   | DAGfusion  | 97721.1          | 65528.4          |

| 1.110 [29]  | Proposed   | 103662.9         | 67406.6          |

| FIR7 [41]   | DAGfusion  | 31688.2          | 21375.8          |

| 1°11X7 [41] | Proposed   | 29929.8          | 21205.8          |