### MASTER

**High level synthesis** performance analysis and code optimization

Hendriks, J.

Award date: 2012

Link to publication

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

EINDHOVEN UNIVERSITY OF TECHNOLOGY

MASTER THESIS EMBEDDED SYSTEMS

# High Level Synthesis: Performance Analysis and Code Optimization

August 14, 2012

Author: Johan Hendriks

Supervisor: Prof. Dr. H. CORPORAAL

Tutors: Ir. Z. YE Ir. S. Fernando

### Abstract

With increasing FPGA chip density, it is possible to implement more sophisticated algorithms on FPGA. However, programming an FPGA using a register transfer level (RTL) language is timeconsuming and error-prone. To make use of the re-programmability of FPGAs for fast design space exploration and fast time-to-market it becomes more and more necessary to raise the abstraction level from structural design to behavioral design. High level synthesis (HLS) seems a promising solution for this issue.

The sequential nature of C as input specification is an issue in HLS and code transformations are often necessary to produce better quality of results. The question is if HLS can compete with handwritten RTL designs, with regard to several performance metrics such as resource utilization, execution time and design time. If HLS can compete with handwritten RTL design, the question is which code transformations are required to achieve good quality of results.

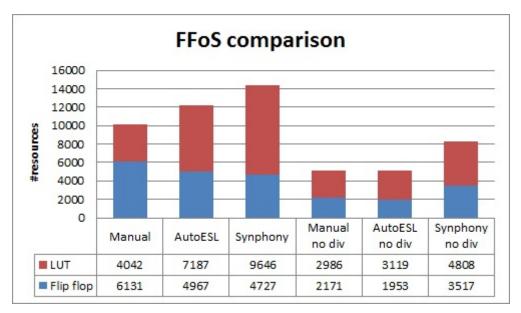

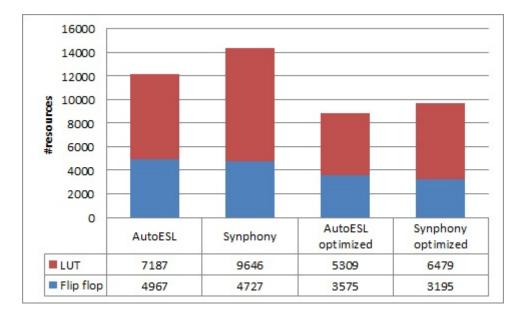

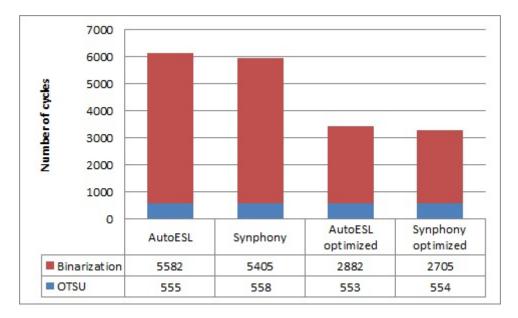

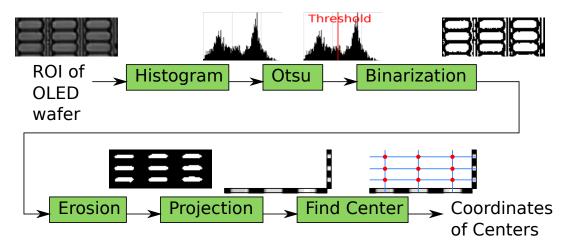

Using the HLS tools AutoESL and Synphony, two image processing kernels are benchmarked for an in-depth analysis of HLS performance. To avoid performance pitfalls by using only small toy examples, a real application called Fast Focus on Structures (FFoS) is ported to FPGA to investigate performance with regard to a comparable handwritten RTL design.

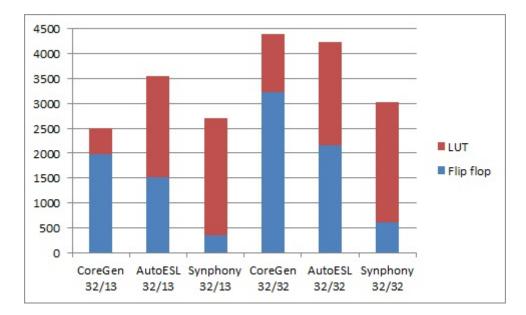

The benchmarks using two image processing kernels have shown that it is possible to efficiently mimic a datapath from a reference manual RTL design. However, the analysis also shows that in HLS it is impossible to describe fine-grained interface and memory control. Both AutoESL and Synphony are capable of producing a design similar to the reference design. AutoESL requires 5% less flip flops and 4% more LUTs whereas Synphony requires 62% more flip flops and 61% more LUTs. Design time, for both tools, is reduced by a factor 6 and the latency stays within 2% of the reference. The explored code transformations, in combination with an existing algorithm classification and source-to-source compiler, are used to create a skeleton library for HLS to decrease design time by a factor 15 compared to handwritten RTL design.

From the two HLS tools, AutoESL seems the most promising although Synphony might produce better results in a different application domain. Furthermore, it is shown that small modifications at behavioral level can have a large positive impact on the performance results without requiring time-consuming and error-prone RTL modifications. The code transformations show that in many cases tool specific code optimizations need to be done to achieve good results, making it debatable if it can be automated.

# Contents

| 1        | Introduction                                                       | 1         |

|----------|--------------------------------------------------------------------|-----------|

|          | 1.1 Reconfigurable Computing Platforms                             | 1         |

|          | 1.2 Compiling for Reconfigurable Computing Platforms               | 2         |

|          | 1.3 High Level Synthesis                                           | 3         |

|          | 1.4 Domain Specific Approach                                       | 12        |

|          | 1.5 Problem Description, Contributions and Overview                | 13        |

| <b>2</b> | Related Work                                                       | 16        |

| -        | 2.1 Pattern Based Approach                                         | 16        |

|          | 2.2 FPGA Implementation Approaches for the Image Processing Domain | 17        |

|          | 2.3 Related Work in High Level Synthesis                           | 20        |

| _        |                                                                    |           |

| 3        |                                                                    | 22        |

|          | 3.1 Platform                                                       | 22        |

|          | 3.2 Logic Synthesis and Implementation                             | 22        |

|          | 3.3 High Level Synthesis                                           | 22        |

|          | 3.4 Kernels and application                                        | 27        |

| 4        | HLS: A Kernel Comparison                                           | <b>28</b> |

|          | 4.1 Histogram                                                      | 28        |

|          | 4.2 Erosion                                                        | 35        |

|          | 4.3 Conclusion                                                     | 43        |

| 5        | HLS: Application Mapping                                           | 44        |

| 0        | 5.1 The Application                                                | 44        |

|          | 5.2 Manual Implementation                                          | 45        |

|          | 5.3 AutoESL Implementation                                         | 47        |

|          | 5.4 Synphony Implementation                                        | 51        |

|          | 5.5 Discussion                                                     | 54        |

|          | 5.6 Alternative Implementations                                    | 57        |

|          | 5.7 Conclusion                                                     | 62        |

|          |                                                                    | 02        |

| 6        | Design Space Exploration                                           | 65        |

|          | 6.1 Histogram Design Space Exploration                             | 65        |

|          | 6.2 Erosion Design Space Exploration                               | 71        |

|          | 6.3 Discussion                                                     | 72        |

| 7        | Algorithmic Skeletons for High Level Synthesis                     | 74        |

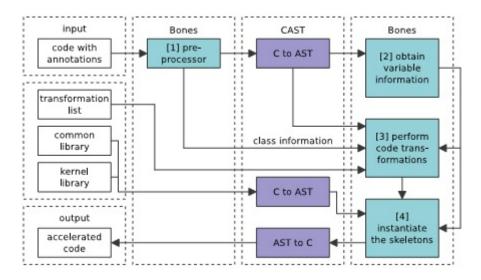

|          | 7.1 Source-to-Source Compiler                                      | 74        |

|          | 7.2 Algorithm Classification                                       | 76        |

|          | 7.3 Code Structures in FFoS                                        | 79        |

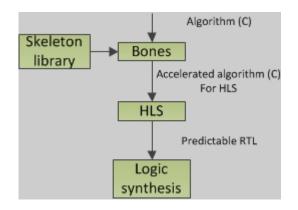

|          | 7.4 Algorithmic Skeletons for HLS in Bones                         | 81        |

|          | 7.5 Discussion                                                     |           |

| 8  | Conclusion and Future Work         8.1       Conclusion         8.2       Future Work |    |  |

|----|---------------------------------------------------------------------------------------|----|--|

| Α  | Parameterized Histogram Descriptions for DSE                                          | 88 |  |

| в  | Erosion Descriptions for DSE                                                          | 90 |  |

| Bi | Bibliography                                                                          |    |  |

# List of Figures

| $1.1 \\ 1.2 \\ 1.3 \\ 1.4$                                                                | Design flow using HLS                                                                                                                                                                                                                                                                | $     \begin{array}{r}       3 \\       6 \\       10 \\       14     \end{array} $ |

|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

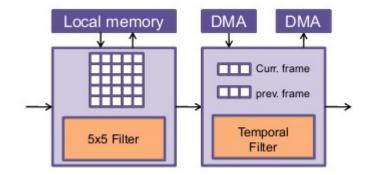

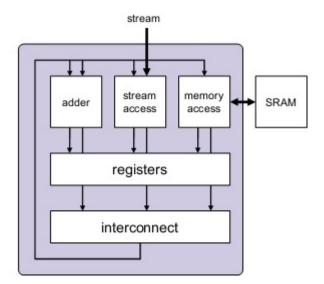

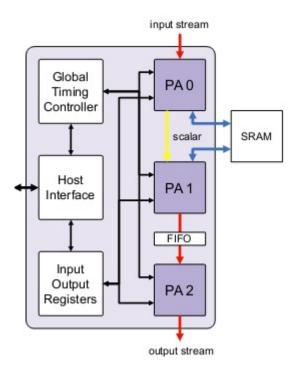

| <ol> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> </ol>                            | AutoESL use model [80]          Example of library driven image processing          Low level template for a processing array          High level template for a pipeline of processing arrays                                                                                       | 24<br>25<br>26<br>27                                                                |

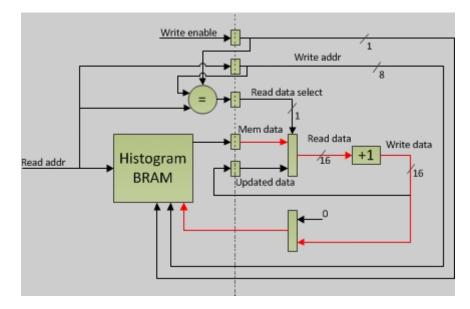

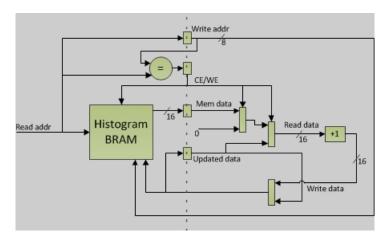

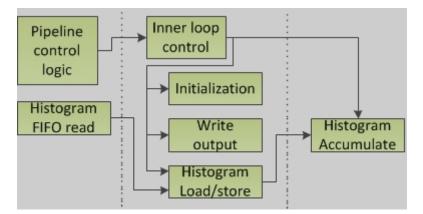

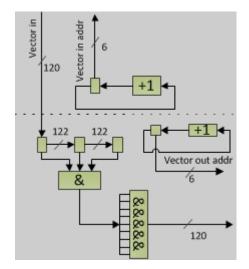

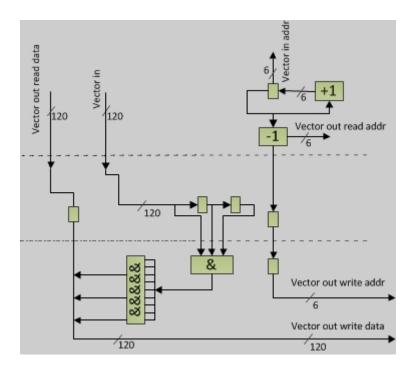

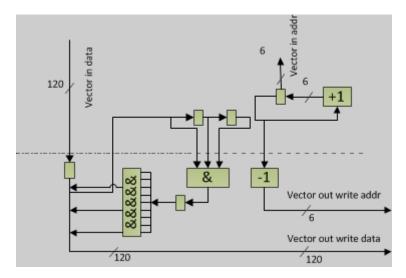

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \end{array}$                     | Main histogram datapath in manual implementationMain histogram datapath in AutoESL implementationHistogram top-level design overviewMain erosion data-path in manual implementationMain erosion data-path in AutoESL implementationMain erosion data-path in Synphony implementation | 29<br>31<br>33<br>36<br>39<br>42                                                    |

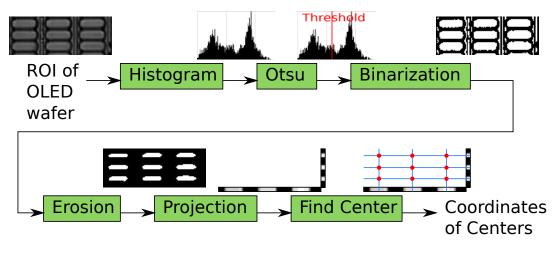

| $5.1 \\ 5.2 \\ 5.3 \\ 5.4 \\ 5.5 \\ 5.6 \\ 5.7 \\ 5.8 \\ 5.9 $                            | The vision pipeline for the fast focus on structures application                                                                                                                                                                                                                     | $ \begin{array}{r} 45\\ 46\\ 47\\ 48\\ 49\\ 49\\ 51\\ 52\\ 53\\ \end{array} $       |

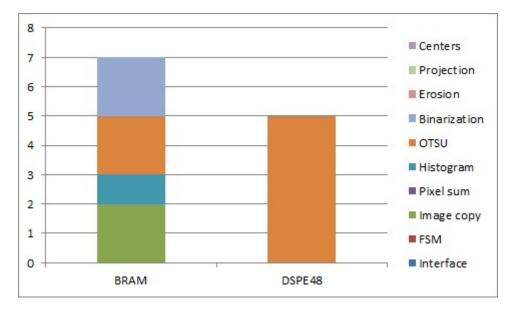

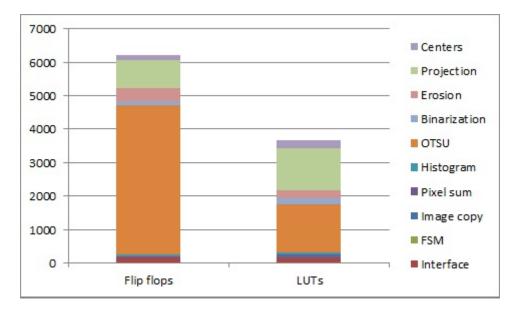

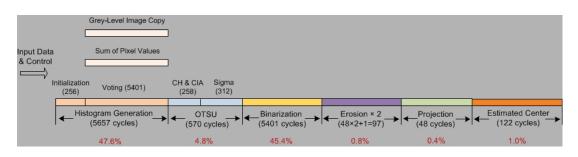

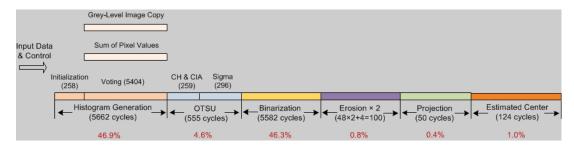

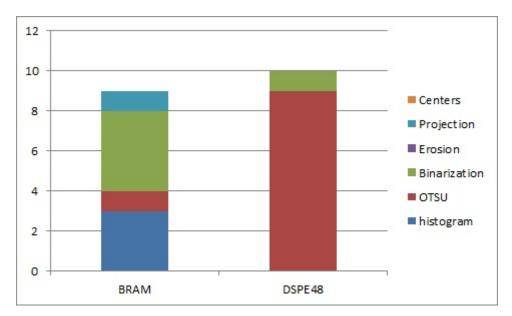

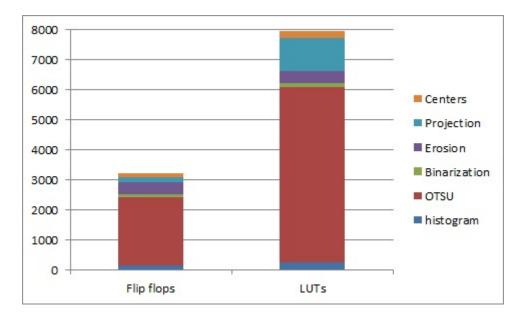

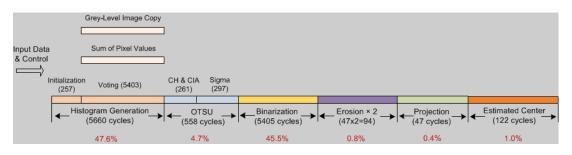

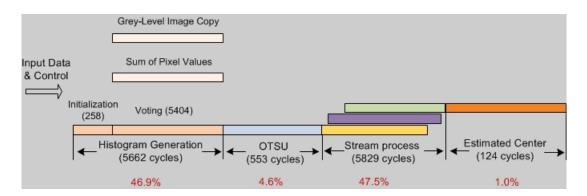

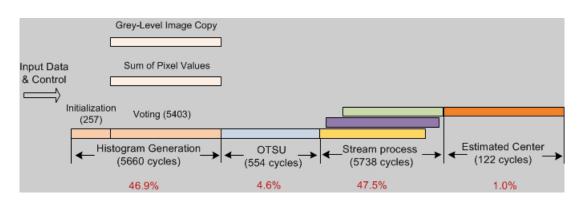

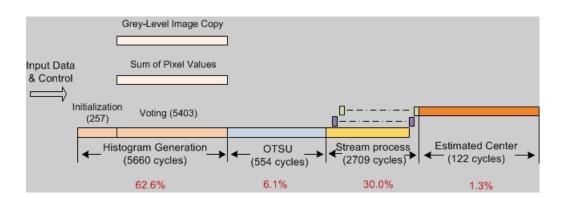

| 5.10<br>5.11<br>5.12<br>5.13<br>5.14                                                      | Latency distribution for the AutoESL FFoS implementation                                                                                                                                                                                                                             | 54<br>55<br>55<br>58<br>59                                                          |

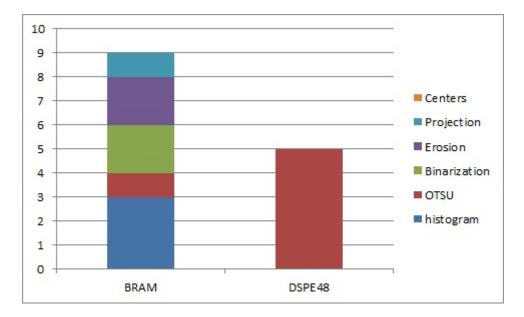

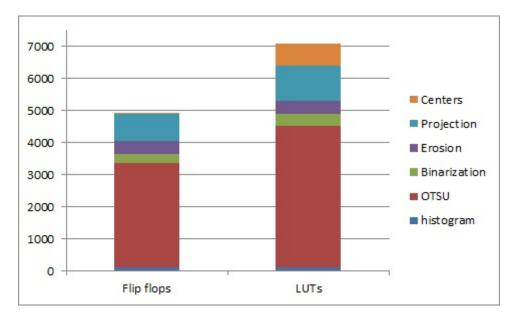

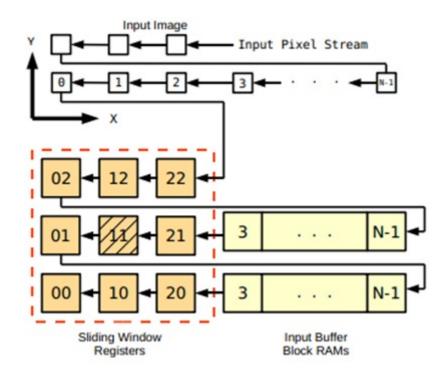

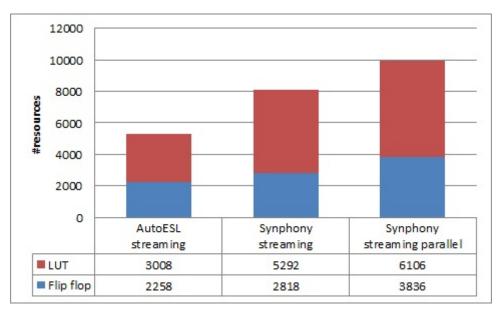

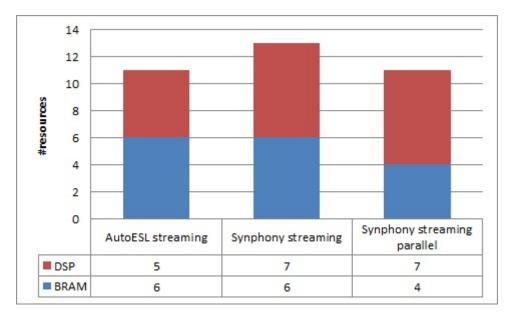

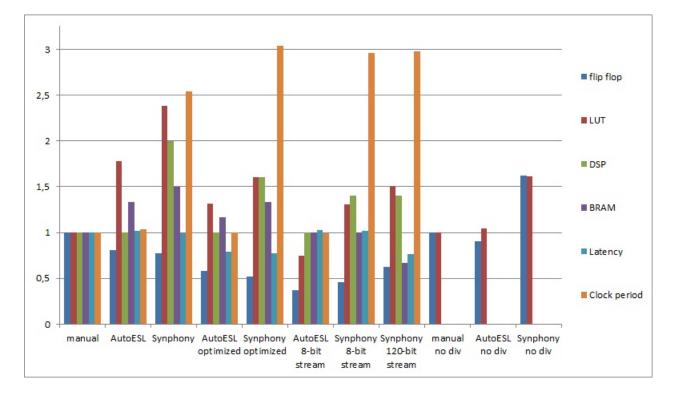

| 5.16<br>5.17<br>5.18<br>5.19<br>5.20                                                      | Architecture to support streaming in window based operations Comparison of different streaming implementations: flip flops and LUTs Comparison of different streaming implementations: DSP and BRAM Latency distribution streaming 8-bit in AutoESL                                  | 60<br>60<br>61<br>62<br>62<br>62<br>63                                              |

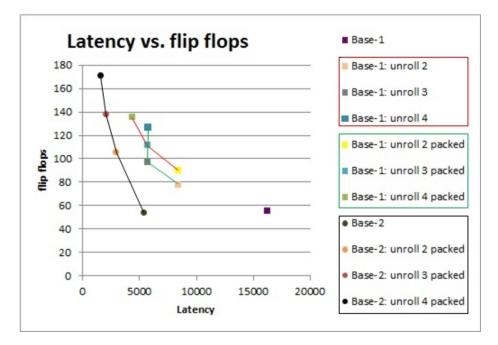

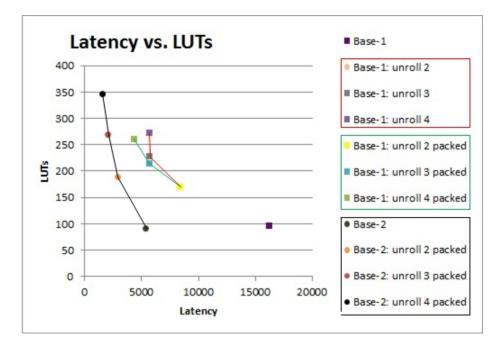

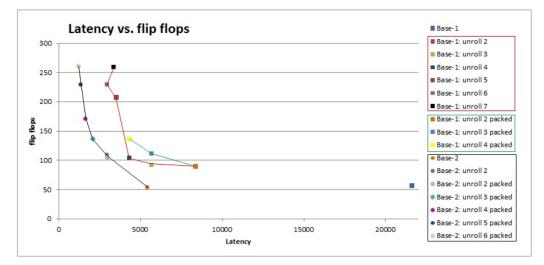

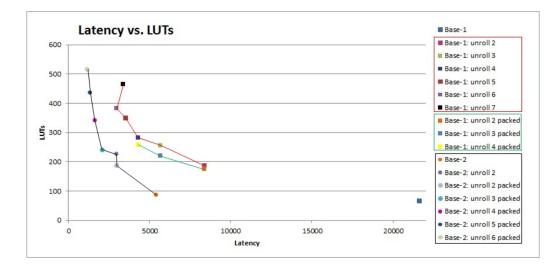

| $     \begin{array}{r}       6.1 \\       6.2 \\       6.3 \\       6.4     \end{array} $ | Latency versus flip flop utilization for the histogram kernel                                                                                                                                                                                                                        | 66<br>67<br>68<br>69                                                                |

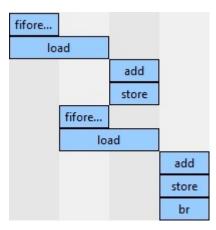

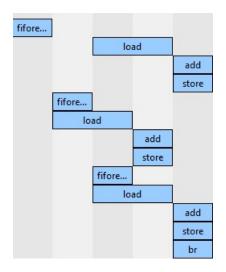

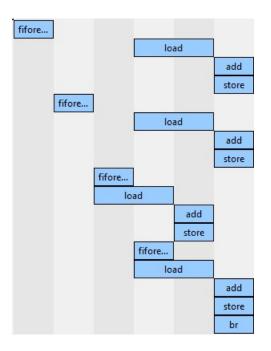

| 6.5 | Pipeline initiation interval dominated by FIFO access            | 69 |

|-----|------------------------------------------------------------------|----|

| 6.6 | Latency vs. flip flop utilization for the histogram kernel       | 70 |

| 6.7 | Latency vs. LUT utilization for the histogram kernel             | 71 |

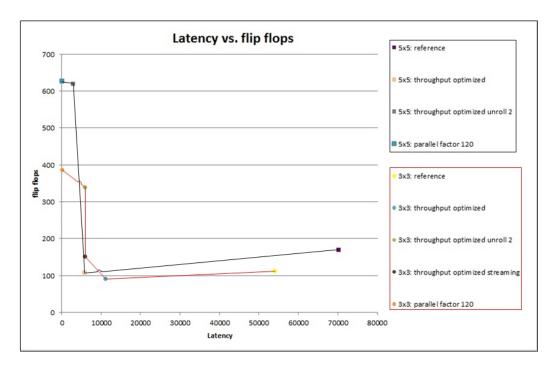

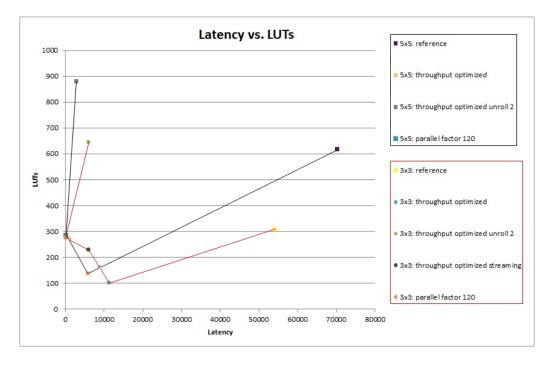

| 6.8 | Latency vs. flip flop utilization for the erosion kernel         | 73 |

| 6.9 | Latency vs. LUT utilization for the erosion kernel               | 73 |

| 7.1 | High-level overview of the Bones source-to-source compiler       | 75 |

| 7.2 | Complete design flow using algorithmic skeletons and HLS         | 76 |

| 7.3 | The vision pipeline for the fast focus on structures application | 76 |

# List of Tables

| 4.1  | Logic distribution of the manual histogram implementation             | 30 |

|------|-----------------------------------------------------------------------|----|

| 4.2  | Summary performance results histogram implementation                  | 30 |

| 4.3  | Logic distribution of the AutoESL histogram implementation            | 31 |

| 4.4  | Summary performance results histogram implementation                  | 32 |

| 4.5  | Macro statistics of the Synphony histogram implementation             | 34 |

| 4.6  | Summary performance results histogram implementation                  | 34 |

| 4.7  | Logic distribution of the manual erosion implementation               | 37 |

| 4.8  | Summary performance results erosion implementation                    | 37 |

| 4.9  | Logic distribution of the AutoESL erosion implementation              | 39 |

| 4.10 | Summary performance results erosion implementation                    | 39 |

| 4.11 | Macro statistics of the Synphony erosion implementation               | 41 |

| 4.12 | Summary performance results erosion implementation                    | 42 |

| 5.1  | Summary performance results FFoS implementation                       | 47 |

| 5.2  | Summary performance results FFoS implementation                       | 50 |

| 5.3  | Summary performance results FFoS implementation                       | 53 |

| 6.1  | Summary performance results FFoS implementation                       | 68 |

| 7.1  | Algorithm classification for the Fast Focus on Structures application | 76 |

| 7.2  | Total lines of code                                                   | 84 |

# Chapter 1 Introduction

Embedded systems come in many shapes and sizes, offering solutions for a wide variety of problems in many different application domains. Their presence ranges from mobile phones and washing machines to avionics and medical equipment. The complexity of an embedded system varies from single core processors to multi-core and even many-core architectures, including a wide variety of possible peripherals. With the diminishing returns on more instruction level parallelism and a stall in uniprocessor performance increase, the community has moved to multi-core designs [1]. Although multi-core solutions offer more parallelism and look promising for general purpose processing, they might not be efficient in performance and flexible enough for certain specific tasks (for example real-time systems) within an embedded system. Reconfigurable computing platforms can overcome this problem by offering efficiency, performance and flexibility, often wanted in for example the image processing domain. One of the major problems with reconfigurable computing platforms is the design time necessary to get the required efficiency and performance. This chapter introduces a possible solution for the time-consuming design time and presents the problem description and contributions. The design time can be reduced by the acceptance of high level synthesis (HLS), a compiler for reconfigurable computing platforms, in the design flow. A requirement for its acceptance is that state-of-the-art HLS tools should be capable of producing high performance designs. Section 1.1 introduces reconfigurable computing platforms and section 1.2 discusses some history in compiling for reconfigurable platforms. Section 1.3 introduces high level synthesis as a new form of compiling for reconfigurable architectures, including a brief discussion about its history and covering several aspects of the high level synthesis design flow. In section 1.4, the image processing domain and algorithmic skeletons are introduced. Readers already known with previously mentioned concepts can skip to section 1.5 and section ?? for the problem description and contributions of the thesis.

# 1.1 Reconfigurable Computing Platforms

The idea of reconfigurable computing has been there since the 60's. While general purpose processors or microprocessors have a fixed architecture, reconfigurable computing architectures contain reconfigurable processing units (RPUs). In a normal processor, the data path and handling of control flow is fixed, but with a reconfigurable architecture the designer has the possibility to design a data path and control flow. There is many interest in reconfigurable platforms as they can be used to accelerate computations or even complete algorithms by use of parallel hardware structures which can be completely customized. General purpose processors have a fixed data path which may not be optimal for a certain computation. On the other side there's application specific integrated circuits (ASIC) and application specific instruction set processors (ASIP). ASIPs have a specially designed instruction set targeting a specific application, such a processor is a trade-off between the (application) flexibility of a general purpose processor and the performance of an ASIC which is a specially designed integrated circuit executing a specific functionality or appli-

cation. The gap between flexibility and performance can be filled with reconfigurable computing platforms. The goal of reconfigurable computing is to fill the gap between hardware and software, aiming for more performance than a software implementation of an algorithm on a general purpose CPU while maintaining flexibility in hardware.

Reconfigurable computing platforms come in many different granularities. A platform might consist of a completely customizable reconfigurable architecture or it might be a hybrid form consisting of a (reduced) general purpose processor coupled with a reconfigurable array of reconfigurable processing units. The task of the general purpose processor in such an architecture is to control the hardware accelerator custom build in the reconfigurable part and to supply the accelerator with data to operate on. The reconfigurable part of the architecture consists of reconfigurable processing units which also come in many different granularities, ranging from coarse grained to fine grained RPUs. An example of a coarse grained RPU architecture is the KressArray [2], consisting of a reconfigurable data path array laid out as a rectangular grid of 32-bit ALUs with three levels of interconnect (nearest neighbor, row/column back-buses and a global bus). Field programmable gate arrays (FPGAs) are an example of reconfigurable platforms with fine-grained RPUs. Usually the RPUs in an FPGA, also called configurable logic blocks (CLB), contain one or two flip flops to temporarily store data and a lookup table used to implement a boolean function. By organizing these CLBs in a certain fashion, the designer is able to implement any digital circuit (as long as the design can be routed and there are enough resources). FPGA architectures can also contain, for example, distributed multiplier and memory blocks, creating a mix of coarse-grained and fine-grained configurable blocks. These kind of reconfigurable architectures are not only interesting because of their flexibility and their possibilities to exploit parallelism for specific tasks, they also provide a platform for design space exploration to test different architectures without major production costs.

## 1.2 Compiling for Reconfigurable Computing Platforms

The evolution of silicon technology and the ever increasing complexity of applications has given rise to a need for higher abstraction levels in programming architectures. Since the 1950's raising the abstraction level has been an evolving process as with each improved technology, enabling more complex applications, it became more and more difficult to generate and validate designs. This raise has been seen in both the software and the hardware community. In the software community, complex and diverse architectures resulted in the need for a raise in abstraction level from machine code (different for each architecture) to assembly language (instruction-set dependent) and later followed by even higher level languages such as C (architecture and instruction set independent) because of the ever increasing code complexity. The hardware community faced a similar evolution in the design process. As chips were growing in size it became harder to hand-craft complete designs with the increasing transistor count on chips. To exploit the increasing chip density, designers needed to raise the abstraction level from transistor level design to gate-level design, effectively reducing the amount of hardware components to deal with during the design process. The increase in transistor count did not stop however, resulting in the introduction of hardware description languages (HDL) such as Verilog and VHDL and the logic synthesis tools to synthesize (transform to gates) the design written in a HDL which is comparable to the compiler which translates the high level programming language to a specific target device.

The latest trend in hardware design is electronic system level design (ESL), which moves from behavioral or structural hardware description using an HDL to behavioral system modeling using languages such as C, SystemVerilog and SystemC. Reason for this is the large gap between hardware designers programming in VHDL for FPGAs and software designers programming in, for example, C. Programming an FPGA using a register transfer language such as VHDL can be a time-consuming and error-prone process for someone lacking the skills of experienced hardware designers (and often even for an experienced HDL programmer) [3] [4]. RTL descriptions are usually

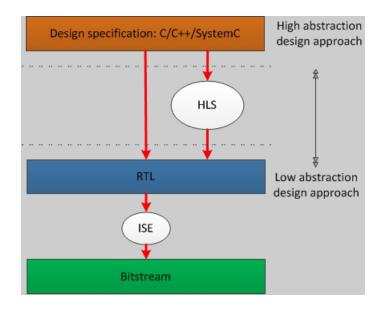

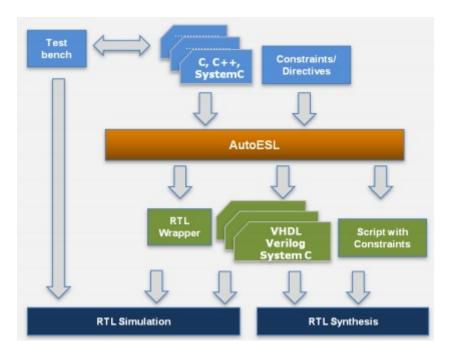

Figure 1.1: Design flow using HLS

heavily tweaked for a particular device (analogous to assembly language software programming), the cycle by cycle behavior needs to be specified for every register inside the design and because of FPGA hardware flexibility every aspect of the hardware needs to be designed. Moreover, designers need to meet specific timing requirements, often requiring several design iterations to achieve timing closure. All of this makes it hard for an experienced designer to use an FPGA as massive multi-core device to speed up applications, as for software engineers who think in a higher level language and not in hardware it will often be impossible to achieve an efficient design without a significant HDL learning curve. ESL design decreases the gap between software and hardware design and enables co-design and easier reuse of IP cores as cores written in RTL suffer from less flexibility and timing and performance constraints. Figure 1.1 presents the design flow including HLS, giving the designer the possibility to either implement the functional description on FPGA directly using HLS or manually coding using an RTL. The driving force for these developments are the increasing transistor count on chips and the fast-time-to-market driven companies who want to maintain or improve productivity [5].

### **1.3 High Level Synthesis**

Raising the abstraction level from assembly to programming languages like C have enabled software engineers to develop more complex applications with improved productivity. This raise in the abstraction level resulted in languages which are platform independent and follow rules of the human language easing the design process. Hardware design is undergoing a similar process. High level synthesis tools, electronic design automation (EDA) tools supporting ESL design, try to bridge the hardware/software gap by supporting automatic transformations from high level programming models to RTL hardware descriptions, redirecting the time consuming HDL work to the compiler instead of the programmer.

High level synthesis is the process of transforming a behavioral untimed description of an application written in a high level language such as C, C++ or SystemC to a hardware description in a HDL. High level synthesis thus transforms untimed specifications to timed specifications which can then, automatically, be synthesized into gates. The power of high level synthesis is that it enables system-level design space exploration and reduces design and verification efforts. Architectural decisions on the hardware/software design (the partitioning), power consumption, area usage and speed can be made at system level. The same system level specification can be

used to explore, and verify, a wide range of architectures on a wide range of different technologies such as a wide variety of FPGAs and ASICs [6]. Another powerful property of high level synthesis is the possibility to introduce behavioral IP cores, which are completely architecture independent, by applying source code transformations and tool specific constraints different architectures can be quickly generated and explored.

This section introduces the evolution of high level synthesis for a historical view, the general compilation flow used in current high level synthesis tools, the common way of specifying a design followed by the concept of interface synthesis and design verification.

### 1.3.1 Evolution

Compiler technology for high-level languages has been in practice since the 1950s, enabling researchers to use this technology in relation with high level synthesis. The high level synthesis concept started with CMU-DA [7] in the 1970s, before FPGAs started to emerge. The tool used an instruction set processor specification (ISPS) language to specify a design, targeting ASIC design. Many common code-transformations from compiler technology were already used at this time, such as dead-code elimination, constant propagation, sub-expression elimination and code motion. After this first step towards high level synthesis, many HLS tools emerged mainly for research and prototype purposes. Next to academic efforts in HLS tools such as ADAM [8], HAL [9] and MIMOLA [10], the industry started to show interest as well in the 1980s and ealy 1990. An examples of industry efforts is Cathedral-II [11], one of the first domain specific silicon compilers based on the idea that there is no generalized silicon compiler which can perform well for all types of applications. Cathedral focuses on the digital signal processing domain and they use a language, called Silage, optimized for high-level description of signal processing algorithms.

At this point, most HLS tools already decomposed synthesis tasks. Code transformation, module selection, scheduling, datapath and control path generation were typical steps in the synthesis process. Fundamental algorithms for scheduling in high level synthesis were developed during this time, such as list scheduling to solve resource constraint scheduling, force-directed scheduling to optimize resource utilization with a performance constraint and path-based scheduling to optimize conditional branch performance. Although both academic as industrial research was being done to high level synthesis, several generations of tools have failed to be accepted by the industry [12] for several reasons. As RTL synthesis was just emerging, it was not widely accepted yet and schematic design was still the optimal solution. RTL synthesis still had to improve before high level synthesis would become interesting to place in the front-end of RTL synthesis. Although HLS tools were developed prior to good RTL synthesis tools, the HLS tools themselves also lacked performance. Results from the tools were often variable and unpredictable, requiring an intensive learning process to get good results. The lack of formal verification to verify generated designs and the use of new languages increasing the learning curve also resulted in rejection of high level synthesis in the design flow.

When RTL synthesis tools were improved and widely adopted in RTL design flow during the 1990s, high level synthesis would become more practical and semiconductor design companies and EDA vendors would jump in on the high level synthesis effort. Companies such as IBM [13], Philips with the PHIDEO tools [14], Synopsys with the Behavioral Compiler [15], and Cadence Visual Architect based on SYNT [16], started developing and providing HLS tools. Although tools from now on started receiving wide attention, they did not yet replace manual RTL design. Still, designers were relying on manual RTL work for better performance and the use of behavioral HDLs as HLS input languages was not considered popular as it required a steep learning curve and designers were more comfortable with the VHDL/Verilog language.

The progress made in the 1990s influenced the new generation of HLS tools developed by academia and industry since 2000. As a major change, input languages for HLS tools would now include C/C++ or C-like languages such as SystemC to describe the design making the tools more accessible for algorithm and system designers and enabled software/hardware co-design and verification. The use of C-like languages also enabled HLS tools to incorporate the newest compiler technology which had undergone vast improvements in parallelization and optimization techniques.

Besides these advantages of the use of C-like languages, there is still no common language which serves as input for high level synthesis tools and there is even discussion if C-like languages are even suitable for HLS [17] [18]. To address short comings in C/C++, HLS tools introduce language restrictions and extensions to tailor the specification language towards hardware synthesis. Besides language restrictions and extensions to solve input language problems for synthesis, many tools use directives or pragmas to address concurrency (aiding the compiler) in the sequential input specification.

With the improved capacity and speed of state-of-the-art FPGAs, many HLS tools specifically target FPGAs and following the Cathedral approach many tools focus on a specific application domain to improve quality of results. Since 2000, many HLS tools have been designed to target FPGAs, such as C2H [19] from Altera, GAUT [20], ROCCC [21], AutoESL from Xilinx [22], Cadence C-to-Silicon Compiler [23], Forte [24], Catapult-C from Mentor [25] and Synopsys C-Compiler [26]. Current HLS tools solve many of the problems which caused previous generations to fail. The use of high level programming languages such as C/C++ overcomes the learning curve of behavioral HDL and enables reusable portable designs as a large subset of C/C++ is completely portable across HLS tools and the C/C++ language is independent of the target architecture. Many tools have extended their accepted input languages in expressing concurrency. Furthermore, tools put effort in interface synthesis solving system integration problems and can make use of DSP blocks and on-chip memories which have vastly increased FPGA performance over the last decade.

### **1.3.2** General Compilation Flow

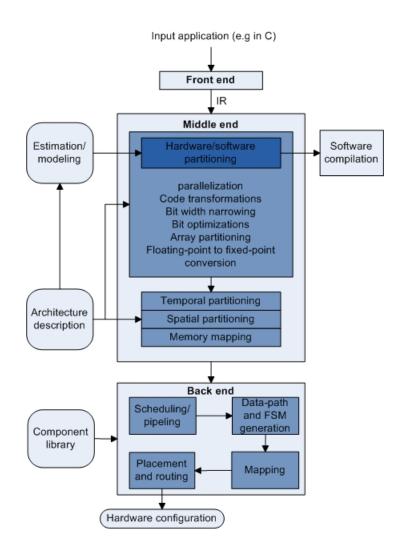

The general compilation flow for high level synthesis is shown in figure 1.2. The input to the front-end is a high level language such as C/C++ or SystemC, such languages usually adhere to the imperative programming model and do not explicitly address concurrency. To overcome this programming model problem, the front-end typically transforms the input description into a formal model. This formal model, the intermediate representation (IR), should explicitly address the notion of concurrency which is natural for reconfigurable architectures. Typically, the IR is represented using a control and data flow graph (CDFG), which is an extension to the DFG model which is only capable in addressing data flow. The nodes inside a CDFG are basic blocks of computations without any control statements and thus can be transformed to a DFG. The edges between the nodes represent the control flow. For each basic block, parallelism can be easily extracted by analyzing data dependencies. This is not the case for extracting parallelism across multiple basic blocks by uncovering the data-dependencies. To extract concurrency across basic blocks, compilers need to have the ability to transform a CDFG to other representations such as the hyperblock representation or the hierarchical task graph representation. Although a CDFG seems a good solution to represent concurrency not every high level synthesis tool uses a CDFG as the intermediate representation, extracting concurrency is still a hot research topic and there is no widely adopted standard input language [17] or intermediate representation. However, the front-end of high level synthesis will always involve some behavioral high level language as input and a formal model expressing the concurrency as output.

If the high level synthesis tool permits software/hardware co-design, it is likely that in the middle-end of the compiler decisions should be made upon the partitioning of the hardware/software. That is, by estimation and modeling the user receives feedback from the compiler about how to partition the original application into a software part running on a traditional processor and a part to be accelerated by hardware. Metrics involving the choice of the partitioning might include power consumption, resource utilization and latency of the application. For traditional accelerator generation, from an algorithm description, with a separate design path for the controlling processor this partitioning is ignored and the entire application is transformed into a hardware accelerator. Often the user has control over the applied optimizations, next to some automatic optimizations such as constant folding and subexpression elimination[27], applied in the middle-

Figure 1.2: Generic compilation flow for high level synthesis [4]

end of the compilation. There are numerous tools which for example enable the user to apply directives to let the compiler apply loop transformations, pipelining and resolving memory collisions by increasing bandwidth (splitting BRAMs or mapping to flip flops). Such optimizations, and others, can also be achieved by manually applying source code transformations, on which will be elaborated in the next section. The basic functionality of the middle-end is to apply spatial and temporal partitioning on the computations in the application. Temporal partitioning refers to isolating computations which should be executed by the same RPU, for example sequentially executing a loop with a multiplication in the body to save area while sacrificing latency (there is only one multiplier). Spatial partitioning refers to isolating computations which should be executed in parallel using multiple RPUs, for example by unrolling a loop with a multiplication in the body to decrease latency while increasing area (since more multipliers are needed). Mapping data structures to memories involves a bandwidth versus area trade-off. Memories have only one or two read/write ports and accesses to memory form a bandwidth bottleneck when many memory operations need to be executed in parallel, in such cases it might be better to bind the data to flip flops as storage units which can be accessed in parallel. The architecture description informs the partition process about the available resources in order to increase the chances for design closure.

The back-end performs the scheduling of operations, effectively distributing the clock cycles

among the operations to be executed. The operations are mapped to functional units, the RPUs, and the control FSM and data path are generated. In many cases the high level synthesis tools provide the option to use commercial tools to performs mapping, placement and routing. Most of the tasks involved in high level synthesis are interdependent and the order in which they are executed is not fixed. Each compiler uses their own algorithm to produce a design and this can range from an iterative approach applying small steps at a time or a complex interplay of many tasks all communicating with each other to generate the final design.

### 1.3.3 Design Specification

The C/C++ and SystemC specifications give the user an extensive set of constructs to write a design specification. High level synthesis poses several restrictions on this input language and adds several extensions which are a direct result of the target architecture. Next to the restrictions and extensions, an untimed specification in C/C++ potentially gives bad performance results when directly used for HLS. Often, several optimization steps need to be made (sometimes as a result of the limitations and extensions of the specification language) in order for HLS to produce an efficient design. The following sections discuss common restrictions/extensions and the common 'tools' provided by the HLS tool to optimize the input specification.

### Limitations and Extensions

The most commonly supported input specifications for HLS are C/C++ and SystemC. High level synthesis imposes several restrictions on the supported constructs from the modeling language. Dynamic memory allocations is not supported as a synthesizable hardware implementation must be fully self-contained specifying all required resources. For that same reason, recursion often poses a problem if the recursion can be endless, in such cases tools might be unable to determine the required resources and the latency of the design. Although pointers are often supported, as long as the size of the structure pointed to is known, many tools discuss limitations or pitfalls during synthesis when using pointers such as multi-access pointer use in which a pointer in accessed multiple times in the same function or pointer casting to ensure correct bit-widths in the hardware design.

Next to the restrictions on the design specification language, high level synthesis tools often extend the set of native data types from an input language by supplying a library or directives to use arbitrary precision data types to take advantage of the possibility of arbitrary bit-width operations and signals in RTL which can vastly improve performance. The availability and extend of arbitrary precision integer and fixed point is highly HLS tool dependent as it is not part of the C/C++ specification. The support for floating point is also dependent on the HLS tool and the target technology which needs floating point cores to assign the floating point operations to. In general, HLS tools make their own choice of the provided support with regard to bit accuracy and support for native data types (integer/floating). Next to the scheduling and allocation performance of a high level synthesis, in other words the performance of the generated designs, the availability of functional libraries to support bit-level operations and support multiple data types is a part of high level synthesis tool performance as arbitrary precision and integer/floating implementations can have a big impact on design performance.

Besides the input specification limitations and supported extensions some tools use a specific architecture template, possibly posing limitations to the input specification and performance of the design, to which they map the input specification. The use of multiple clock domains, often only available with a SystemC input specification, streaming support and parallelization techniques are usually dependent on the target architecture template. Although is seems to be a drastic limitation when using architecture templates, it is often a choice by HLS tool designers to be able to generate predictable designs and target specific application domains. These are all design choices which influence tool performance but have a positive effect on predictability and make source-to-source transformations easy as the designer will be able to know in advantage what kind of transformations to apply to improve the design.

### **Design Optimization**

The optimization process of a design using HLS involves source-to-source transformations and the use of directives and tool-libraries to direct the compiler to a specific design. In many cases, directives or architecture settings inform the compiler to pipeline or unroll particular loops in the input specification. Pipelining and unrolling often improves the throughput/latency of a design but in loops with multiple array accesses the pipelining or unrolling will bring bandwidth problems to light which prevent or limit the performance gain of pipelining and unrolling. In such cases, manual source-to-source transformations or directives can be used to enable performance gain of loop unrolling and pipelining. Some tools support automatic array, which are implemented in BRAM, partitioning or reshaping to increase bandwidth while in other cases the tool supports a certain coding style (possibly using tool libraries) to ensure an increase in bandwidth. Architecture settings, coding styles or pragma's/directives can be available to map operations to specific functional units, limit the number of used functional units at the cost of latency and map variables to BRAM with a certain amount of read/write ports or simply to registers.

The optimization process usually focuses on the available bandwidth. The compiler will take care of pipelining and unrolling, informing the designer about limiting factors in the design such as multiple BRAM accesses which need to be spread out across multiple clock cycles due to limited resources. It is up to the user to either increase bandwidth, by use of directives or a different coding style, or decrease the number of BRAM accesses by recoding the input specification (particularly useful when aiming for a streaming implementation). Each tool has its own approach to design optimization, from requiring many source transformations by the user to source transformations in combination with directives to take advantage of the transformations and to fully automated input specification optimization requiring the user to inform the compiler to partition, pipeline or unroll parts of the input specification.

As with manual RTL design, there's an area/latency trade-off for the designer to take into account. With an increasing unroll factor, more resources and bandwidth is needed to execute operations in parallel. Many factors influence the design performance and the difficulty of design optimization, such as the pipeline initiation interval parameter, the unroll factor, the difficulty of creating more bandwidth by packing data elements into wider vectors or distributing them across multiple storage elements, parameters to limit the use of certain functional units, streaming/interface support and the use of arbitrary precision types. All the discussed optimizations are summarized and combined in an optimization process in [28].

### **1.3.4** Basic Source Code Transformations

As mentioned in the previous section, it is up to the compiler to extract concurrency from the input program. Since the input is written according to the imperative programming model the compiler might not be able to extract all the possible parallelism from the input, since writing sequential programs is quiet different from explicitly specifying concurrency. Depending on the high level synthesis tool of choice, although it might even hold for every tool currently available, the coding style of the input program can drastically influence the end result of the generated design [29] [30]. Raising the abstraction level from HDLs like VHDL or Verilog to HLLs like C and SystemC does not mean the designer can ignore hardware completely. The designer still needs to be aware of the underlying hardware to understand the proper coding style to achieve a particular architecture. Some examples follow to illustrate this important fact of high level synthesis, these examples are taken from the High-Level Synthesis Blue Book written by Michael Fingeroff[31]. The book illustrates coding styles to obtain certain architectures, including the area/latency trade-offs which come with the design choices. Only two small examples are presented, as it is outside the scope of this report to elaborate on the vast amount of possible trade-offs in the coding style.

### Example 1: Bit accuracy

When targeting coarse grained reconfigurable architectures containing programming arrays of 32bit ALUs or general purpose processors with standard 8, 16 or 32-bit architectures, the bit-width of variables may not affect performance. When targeting fine-grained architectures such as FPGAs, the use of native types in C/C++ will drastically affect performance. The size and delay of functional units (adders, barrel shifters, floating point cores) can be substantially reduced by using bit accurate data types, in contrast to general purpose processors who's functional units cannot be customized. The control logic, the generated FSM, can also be substantially reduced by correct use of bit accurate types. While many compilers are able to extract bit-width information from the input code, there are situations where the user has to inform the compiler about properties of data types.

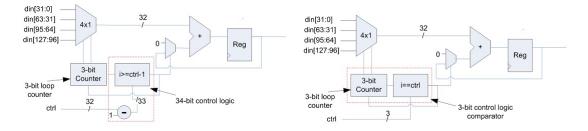

Listing 1.1 shows a code example for an accumulator, including a control variable in the interface to control the number of accumulations. As there exists a static upper loop bound, the loop counter in the control hardware is fixed to three bits. The control variable 'ctrl' on the interface however consists of 32 bits and the compiler will not be able to reduce the number of bits as the variable is on the control interface and theoretically can take up any value up to 32 bits. High level synthesis only reduces bit-width if it can prove that it is possible without changing the functionality. The left side of figure 1.3 shows an approximation of the resulting hardware after synthesis, it can be seen that the generated control logic (FSM) includes a 33-bit subtracter to test the conditional statement in the loop resulting in a larger area than required.

```

void accumulate( int din[4], int &dout, int ctrl ){

int acc = 0;

ACCUM: for(int i = 0; i < 4; i++){

acc += din[i];

if(i >= ctrl-1)

break;

}

dout = acc;

}

```

Listing 1.1: simple accumulate loop with control

Not only is it possible to reduce the bit-width of the subtracter, a minor code change can also eliminate the subtracter completely. Listing 1.2 presents this solution. Because the user puts a constraint on the interface variable 'ctrl', only a 4-bit subtracter would be needed if the conditional check would be done as in listing 1.1. By using a comparison between the current loop iteration and the previous loop iteration, only a 3-bit comparator would be needed. The right side of figure 1.3 shows an approximation of the resulting hardware after synthesis. For a small example such as this, area will not be reduced drastically, but such minor changes will result in a noticeable decrease in area when synthesizing larger applications.

```

void accumulate( int din[4], int &dout, ac_int <3, false> ctrl ){

int acc = 0;

int i_old = 0;

ACCUM: for(int i = 0; i < 4; i++){

if(i_old == ctrl)

break;

acc += din[i];

i_old = i;

}

dout = acc;</pre>

```

}

Listing 1.2: optimized accumulate for simplified control hardware

Figure 1.3: Generated architecture of listing 1.1 (left) and listing 1.2 (right)

### Example 2: Pipelining and unrolling of loops in combination with memory accesses

Pipelining is a well known approach to exploit instruction level parallelism (ILP). By dividing an operation in several steps and creating a pipeline, different parts of the operation can be executed simultaneously and thus increasing throughput at the cost of area. There are various forms of pipelining such as resource pipelining, memory access pipelining and loop pipelining. Memory access pipelining is less interesting for FPGA as accessing a BRAM takes just one clock cycle. Resource pipelining involves the creation of functional units which usually have a large latency such a multipliers and dividers, some tools offer the possibility to create constraints on the created multipliers such as the number of stages within the unit. This is however not something which can be controlled with the source code. Loop pipelining, and function pipelining, allows multiple loop iterations to be overlapped, increasing throughput.

Loop unrolling is a common practice to increase parallelism within a design [32]. By decreasing loop overhead and increasing ILP opportunities, the scheduler is able to schedule more operations in parallel at the cost of area. Loop unrolling differs from pipelining in the sense that a fully unrolled loop can, theoretically, be executed in a single clock cycle whereas pipelining a loop, again theoretically, results in a start of a new loop iteration each clock cycle and pushing instructions through the pipeline just like water flows through a pipe.

The performance increase of both these optimization methods depends heavily on the loop body, in particular the memory accesses within a loop. There are many possible ways to code an application in a way that memory accesses prevent a gain in performance when using loop pipelining or unrolling. The fundamental problem however is always the same, if one tries to access the same memory multiple times in the same clock cycle the scheduler needs to insert an extra clock cycle to separate these memory accesses. Listing 1.3 gives a simple example to illustrate the problem.

```

void accumulate (int din [4], int & dout, bool flag [4]) {

int acc = 0;

if( flag [0] )

acc += \dim [0];

if (

flag [1]

)

acc +

-=din [1];

if(

flag [2]

)

acc += \dim [2];

if (

flag [3]

)

acc += \dim [3];

dout = acc;

```

Listing 1.3: accumulate with memory access bottleneck

The body of this function is basically a fully unrolled loop. If 'din' is mapped to a BRAM without any further optimizations, each element of 'din' will be placed in a single entry in the BRAM. Accessing 4 entries in a BRAM in the same clock cycle is not possible, so the expected parallelism will not be achieved. To overcome this problem, one might try to pipeline the function (the top level function can be seen as a main loop) to speed up the design and start a new iteration of the accumulator each cycle. Again, the memory access to 'din' prevents pipelining because it is impossible to schedule multiple reads in a single cycle. Listing 1.4 presents a possible code transformation to overcome the above mentioned problems. An internal copy of the input data is created. By completely unrolling the DIN loop and mapping the input data to a single entry in a BRAM or separate registers it is possible to read the input data in a single cycle, assuming the delay of the adders does not exceed the clock cycle time. The latency of the design has been reduced from 6 cycles to 4 cycles in this solution, moreover it is now also possible to pipeline the accumulate function. Note that it is assumed all other variables are stored in internal registers instead of BRAMs.

```

void accumulate(int din[4], int &dout, bool flag[4]){

int acc=0;

int din_int[4];

DIN: for(int i=0;i<4;i++)

din_int[i] = din[i];

ACCUM: for(int i=0;i<4;i++){

if(flag[i])

acc += din_int[i];

}

dout = acc;

}</pre>

```

Listing 1.4: accumulate with faster memory access pattern

This example only highlights a small portion of the memory access problem, and only presents one of many solutions to this particular problem. Other solutions involve the removal of conditional statements, reshaping of memories (changing bit-widths of the entries) or partitioning a single memory into multiple memories to increase access possibilities. Although the memory access problem is a general problem because of the hardware implementation of memories in an FPGA, the solutions necessary to increase performance might differ among high level synthesis tools depending on the influence the user has on the mapping and resource choices.

### 1.3.5 Interface Synthesis

High level coding languages such as C make it easy to connect multiple blocks together to create a complete algorithm or application. The interface between these modules is automatically generated during synthesis by extracting the information from the function parameters, depending on the HLS tool capability the user can have an influence on synthesized interface between modules and the between the design and its environment. It is up to the designer to set constraints on the interface between modules by adding synchronization variables, such as start/stop/reset wires, or mapping the data to FIFOs or BRAMs. The interface to the environment is also an important design aspect, if the high level synthesis tool or environment only supports a single slow interface it is not useful to optimize the latency beyond the interface bandwidth bottleneck. The positive aspect of having untimed C as input for the high level synthesis is that it leaves the tool completely free to create a top level interface for the design. The amount of possible interfaces is dependent on the tool of choice, and it is up to the compiler to generate the proper streaming buffers, memories and handshaking. It is important that the designer recognizes the fact that designing an accelerator makes no sense if the designer puts no thought in the interface, as eventually the

accelerator will have to be controlled by an external processor and have its data fed by some external source. Although not every HLS tool supports general interface protocols, it is possible to write a top level interface wrappers using a HDL which wraps around the generated design.

### 1.3.6 Verification

One of the time consuming tasks when designing an accelerator using a HDL such as VHDL is the verification. Tools such as ModelSim (Mentor) and Vsim (Xilinx) exist to help the designer validate the design. It is up to the designer to validate the cycle-by-cycle behavior of the design by either verifying the generated waveform showing internal and external values of the design or by implementing a test-bench supplying the design with data and verifying the output data. Care has to be taken that all possible inputs to the design are tested to ensure correct behavior. For high level synthesis to be successful, it is important that it overcomes the cumbersome task of verifying the design 'by hand'. There exist many different approaches to solve the verification problem, from supporting down-flow verification tools such as ModelSim and Vsim to simulate the design using automatically generated test-benches based on the C/C++ testbench used to verify the functional description, to intermediate SystemC models to simulate cycle-accurate behavior and formal verification using model checking methods.

## 1.4 Domain Specific Approach

Based on the lessons learned from decades of research, the research community is taking the domain-specific approach towards parallel computing [33] [34]. This approach explores patterns within, and across, application domains. The goal is to provide an easy way to write applications which can execute on highly parallel architectures. To avoid the programmer to have vast knowledge of the underlying hardware, programming models should be high-level and separate the programmer from the hardware itself while still supporting parallelism. The main goal is to make parallel computing productive, energy efficient, scalable, portable, performant and verifiable. Applications often contain naturally parallel parts and hardware is naturally parallel. Now we have access to multi-core, many-core and reconfigurable highly parallel platforms there is a need to simplify the programming model to efficiently program these parallel platforms. The high level synthesis section already indicated that raising the abstraction level to a high level language such as C does not mean the designer can ignore the underlying hardware. High level synthesis does speed up the design trajectory, but still requires that the designer is able to reason about what is going on in the underlying synthesis steps. Having an even higher abstraction level, by introducing a framework on top of high level synthesis might be a good solution to enable the software engineer to develop applications without understanding details of the underlying platform. Many applications contain specific patterns which can be mapped to parallel architectures in many different ways, depending on the underlying platform and the aimed performance. An application is a combination of many different computational patterns. Letting the software engineer develop applications in a functional manner, without having to apply code transformations to efficiently implement the application on hardware, might even further increase productivity and re-usability. The domain of interest, the image processing domain, is explained next as it will be the application domain used in this research.

### 1.4.1 Image Processing Domain and Skeletons

Modern day image processing applications become more and more computationally intensive, requiring special purpose hardware solutions to be created. The image processing domain is a hot research topic, especially within the parallel computing community as enormous speedup can be achieved by parallelizing such applications and implementing them on reconfigurable architectures maintaining the advantages of custom hardware solutions while enabling fast design space exploration (using HLS) and re-programmability. According to [35] most image processing applications can be divided and categorized into three different IP task categories:

- Pixel to pixel operations: an operation is performed on a single pixel in the input image to produce a single pixel in the output image.

- Neighborhood to pixel operations: the operation is performed on multiple input pixels to produce a single output pixel.

- Global operations: operations done on the complete image to produce either a single scalar value such as the maximum, or a vector such as a histogram.

Although this is a very global class definition, many image processing tasks can be easily recognized to fit in one of the three. The ease of distinguishing image processing tasks into IP classes makes the image processing domain an interesting research domain with regard to high level synthesis and identifying common code structures for certain IP classes. Skeletons can be introduced to capture certain memory access patterns such as neighborhood access or single-pixel access and the re-use of accessed data across several iterations of the operator performed on the data. Such a skeleton classification can be used to instantiate a particular parametrized code structure (theoretically in any imaginable programming language) while maintaining the functionality of the IP core which has been classified. Essentially, a high level coding language as C/C++, which is sequential, can be classified and transformed into a parallel description for a specific platform while maintaining functionality. Care has to be taken however that the used skeleton classification does not contain as much skeletons as there are enough skeletons to capture all possible patterns of memory accesses such that each processing kernel can be classified.

Related to high level synthesis, a skeleton classification might include a class for window-based operations such as an erosion kernel removing noise from an image. High level synthesis requires a certain coding style, or a certain memory access pattern in the C-code, to generate a specific architecture. Using parameters as the image size, window size and a certain parallelization factor, the skeleton could automatically be instantiated by replacing the parameters in the skeleton code (the certain coding style for particular architectures) with the parameters available with the kernel classification.

### 1.5 Problem Description, Contributions and Overview

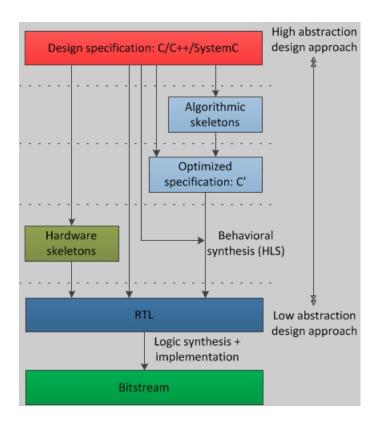

In figure 1.4, several design flows for the implementation of an algorithm on FPGA are shown. The current standard in design for FPGA is manually coding the application using RTL such as Verilog or VHDL, which is becoming more and more difficult and time consuming with technology scaling and increasing application complexity. This approach requires a designer to manually implement the algorithm using an RTL language, often based on a reference functional description (possibly in C/C++/SystemC) which is used to verify the correctness of the algorithm.

Using high level, behavioral, synthesis the RTL can be generated directly from the functional description, drastically reducing the design effort. However, the sequential nature of functional descriptions in C/C++ potentially results in bad performance of the generated design by HLS and the designer has to put effort into optimizing the functional description. These optimizations involve structural changes to separate the functional description in smaller computational kernels, optimizing and re-ordering memory accesses for parallelization, selecting internal memory/vector widths and sizes and tune interfaces between each computational kernel. The figure represents this optimized description as the optimized C' specification. The main question is if state-of-the-art high level synthesis is capable of competing with manual RTL designs and if source transformations at C/C++ level are sufficient enough to produce good quality of results. If high level synthesis produces good quality of results, the next step in the design process is to alleviate the designer from manually optimizing the design specification. If the source transformations result in good HLS quality of results, algorithmic skeletons, based on common patterns in the embedded vision application domain, can be introduced to enable automatic code optimizations/transformations to generate

Figure 1.4: Design trajectories for FPGA implementation

C' level descriptions. The algorithmic skeleton, based on a certain algorithmic classification, describes a structural body representing the datapath to be generated by HLS. By classifying parts of the design specification, algorithmic skeletons can be instantiated automatically to produce C/C++ resulting in good quality of results using HLS.

If the HLS quality of results is poor compared to manual design, another design flow remains a possibility. The hardware skeletons design path is at a lower abstraction level, closer to the hardware, and might produce better results. Although not part of this thesis, this path is mentioned for completeness. Just as with algorithmic (software) skeletons, hardware skeletons describe the structural body for a specific architecture and a front-end needs to take care of instantiating the skeleton with the proper parameters and operations to generate a computational kernel. The difference with algorithmic software skeletons is that hardware skeletons describe the structural body in an HDL such as VHDL or Verilog, being a lower abstraction level closer to the logic synthesis back-end. It is well-known that the lower the abstraction level, the better the performance can be but the more time consuming the design trajectory usually is.

The contributions of this work include the following:

- Benchmark of two small image processing kernels using two HLS tools, with as goal to mimic two RTL designs, which are common in handwritten RTL design, and observe performance metrics between different HLS tools and handwritten RTL.

- Benchmark of an application closely matching a handwritten RTL implementation observing HLS performance and highlighting issues.

- Implementation of a scope of designs for an application using two HLS tools to observe HLS performance.

- A design space exploration on two image processing kernels, showing parameterization of HLS input specifications and achievable scope and scalability of designs.

- An introduction towards algorithmic skeletons for HLS to shorten design time by enabling automatic source-to-source transformations for high quality of results.

- Coding styles for high level synthesis.

To analyze HLS performance, two small image processing kernels are ported to FPGA using two promising state-of-the-art HLS tools. This analysis serves as means to observe hardware generation in relation to the input specification, i.e. how to optimize the source code for good QoR. A complete application is ported to FPGA using the same HLS tools to analyze the performance (area, latency, design time). This complete application is required to use HLS for what it is intended for, the automatic generation of RTL for complex or large applications without the need for manual RTL coding. This HLS analysis, in combination with a design space exploration performed on two small kernels, will show several coding styles for good and predictable QoR. These coding styles, in combination with an algorithm classification, are then used to reason about the possibility for the introduction of algorithmic skeletons for HLS to decrease design time.

Acceptable performance metrics for the acceptance of HLS in the design flow are hard to express and are dependent on the designer's requirements. This work will show however that significant code transformations are required for good QoR, requiring hardware knowledge by the designer. For this reason, algorithmic skeletons are proposed and it is vital that coding styles can be related to a specific algorithm classification. This will be shown in the final part of this thesis.

This thesis will first focus on the HLS quality of results compared to manual RTL design, based on an in-depth datapath analysis of two small image processing kernels followed by a case study in which an algorithm is mapped to FPGA and compared to a reference manual implementation. Chapter 2 introduces related work on all design trajectories visualized in figure 1.4 and chapter 3 introduces the tools and platform used throughout this work. Chapters 4 and 5 discuss high level synthesis performance based on an in-depth comparison of two small computational kernels and a complete algorithm. In chapter 6, the process and power of design space exploration using high level synthesis is described. Chapter 7 introduces algorithmic skeletons for HLS based on conclusions from the high level synthesis performance investigation. Finally, chapter 8 presents an overall conclusion and future work of this thesis.

# Chapter 2 Related Work

This work covers a large scope, ranging from algorithmic skeletons and it's classification to backend RTL implementation. Although this research does not focus on creating a new algorithmic classification or improving high level synthesis tools itself, this chapter will present related work done in the entire scope of the design flows as shown in figure 1.4. Section 2.1 introduces related research done in the pattern based approach field for reasoning about and implementing for parallel computing platforms, section 2.2 discusses related work to each of the design flows in figure 1.4 and finally section 2.3 presents multiple branches of HLS related research.

# 2.1 Pattern Based Approach

The pattern based approach involves pattern matching and recognition during synthesis, referred to as pattern mining in [36]. Pattern mining does not focus on a specific domain, but tries to extract patterns across application domains. The following sections present related work done related to algorithmic classes, pattern and idioms. In general, these definitions are coarse-grained, used to reason about parallel computing rather then moving towards a higher implementation abstraction level. Most of these classifications do talk about memory access patterns, but refer to multiple applications domains and do not refer to specific parallel architectures but reason about the concept of parallel architectures in general.

### 2.1.1 Dwarfs

Berkeley has introduced 'Dwarfs' in a try to raising the abstraction level from standard applications to patterns of computation [33]. They reason that one of the biggest obstacles in parallel computing is the unclarity in how to express parallel computation in the best way. They claim it is unwise to let current benchmark applications, based on an imperative programming model, drive an investigation to parallel computing. The introduction of dwarfs, which capture certain patterns of computation and communication common to important applications, lets them reason about hardware requirements instead of focusing on individual applications and how to map them to certain hardware platforms. The claim is that the design community should focus on higher level abstractions instead of focusing on parallelizing legacy applications based on the imperative program model. The work of Berkeley is inspired by the definition of 7 particular computational methods by Phil Colella [37]. Next to these 7 dwarfs, Berkeley extends this list with 6 more dwarfs they feel are not included yet. The dwarfs do not identify parallelism but they identify computational and communication classes which are regarded as important for current and future applications such as database software, computer graphics, graph traversal and linear algebra. As applications in most cases will consist of a combination of several dwarfs, focus is not on the performance of individual dwarfs but on the composition of them.

### 2.1.2 Idioms

An idiom is a pattern of computation that a user may expect to occur frequently in certain applications. They have been used to classify which portions of C-code can benefit from being ported to hardware accelerators such as GPUs [38]. In [39] several common idioms are discussed such as a stream idiom describing the sequentially reading and writing of arrays in C-code. Other examples are so called gather and scatter idioms which describe the gathering of data in a random access order in memory and writing data to memory in a random order respectively. These idioms are very coarse-grained and besides indicating regions of C-code which could potentially benefit from parallelization, they do not describe or include properties which can be used for automatic code parallelization.

### 2.1.3 Algorithm Classifications

There are many variations of algorithm classifications used for code generation, reasoning, analysis and performance prediction, examples of which can be found in [40], [41], [42], [43] and [44]. This work will not focus on developing a new classification but will make use of an internally developed modular and parameterizable algorithmic classification [45]. This work includes a comparison with existing work as well as a new classification including well-defined grammer and vocabulary. The main advantages of this classification are the fine granularity and modularity to support construction of classes by use of the existing grammar and vocabulary.

The used classification is not final and the completeness and correctness of the classification is researched with the use of an internally developed source-to-source compiler called Bones [46]. The compiler currently generates high-performance CUDA and OpenCL code using the algorithmic skeleton technique. The goal is to generate code based on skeletons of parallel structures, or simply a library of parameterizable implementations for a particular target and algorithm class. It is already shown that the tool delivers better performance compared to other C-to-CUDA tools for a small set of image processing kernels. The tool is build in a way that makes it easy to add a target architecture such as an FPGA. The tool generates readable code allowing finetuning after code generation and requires minor modifications to the original C-code. Future work includes the implementation of more skeletons (and more target architectures), fine-tuning existing skeletons, applying kernel fusion of two algorithm classes if its gains performance and automatically identifying algorithm classes from the source code relieving the programmer of classifying the input code.

# 2.2 FPGA Implementation Approaches for the Image Processing Domain

There are several possible approaches to get to an FPGA implementation of an image processing algorithm. The, up till now, usual approach is the manual approach. Perhaps high level synthesis will be able to match the performance of the manual work. For high level synthesis there are still several possible design trajectories, such as manual C optimization to aim for a particular performance/architecture, parameterizable skeletons as input for the high level synthesis removing the need for manual code optimizations or hardware skeletons to directly go to an RTL implementation. The following sections explain these design trajectories, elaborating on existing work being done with regard to the design trajectories introduced in figure 1.4.

### 2.2.1 Manual RTL Implementation

Manually implementing algorithms on reconfigurable platforms has for long been the usual design approach. Although manually implementing RTL is a time-consuming and error-prone approach, it is possible to design high performance accelerators by completely specifying the architecture of choice. Experienced digital hardware designers create their design at gate-level using hard description languages (HDLs), while less experienced designers can make use of a module library with common interfaces to compose their design [47]. A lot of research has been to done in optimizing very specific algorithms and doing design space exploration for manual RTL implementations, such as can be found in [48] [49]. In the image processing domain, Donald Bailey is one of the leading researchers as group leader of the image and signal processing research group at Massey university. His work involves algorithm transformation for FPGA implementation [50] [51], efficient vision algorithms on FPGA [52] [53] [54] and the introduction of design patterns to overcome mapping problems due to processing mode dependent parallelization [55]. This last work is already a step towards pattern matching, limiting the number of design patterns applicable to the porting of an algorithm to FPGA based on a processing mode such as streaming, offline (data to operate on is available in memory) or a hybrid form.

### 2.2.2 Straightforward High Level Synthesis

Doing efficient high level synthesis, using either a commercial or open source HLS tool, is not as easy as just pushing a button to generate code. As is explained in section 1.3, the coding style of the application can significantly influence the performance of the generated design. The straightforward high level synthesis approach does not imply an efficient design and requires recoding to be done depending on the performance goal and the HLS tool of choice. Such code modifications might not be a problem for someone who is experienced with FPGA RTL design or has general knowledge of processor architectures, as they are assumed be able to find performance bottlenecks of C/C++ input code such as memory access collisions. For someone working in the software domain it might be harder to come up with an efficient design by re-coding the application for efficient hardware generation. In essence, sequentially written programs for a CPU will generate bad results in high level synthesis. This is not a problem of high level synthesis however, as it simply schedules operations based on the input specification which essentially describes the resulting architecture to be generated. This design approach is normally not acceptable, unless an algorithm's portability needs to be verified or there are no design constraints at all (proof of concept designs).

### 2.2.3 Algorithmic Software Skeletons for High Level Synthesis

The research of Wouter Caarls addresses the domain specific approach, in particular the embedded image processing domain [40]. The aim of the research is to bring the programming language closer to the algorithm instead of the architecture. Porting applications to new architectures is a time-consuming task if the application is programmed in a general-purpose language or an architecture specific language. Architecture independence is claimed to be resolved by the use of algorithm-specific languages (ASLs). The execution models of general-purpose languages such as C is sequential. Although it is possible to compile the application to different architectures, it still involves a restricted set of architectures adhering to the sequential execution model. Porting such applications to parallel architectures requires significant changes to the application/algorithm. Languages enabling writing parallel applications such as OpenMP, MPI and Handel-C are available but still pose restrictions on certain hardware features which have to be available and their performance differs among architectures. Algorithmic skeletons are introduced, which are higher-order functions written in an algorithm-specific language. These skeletons are then source-to-source translated (compiled) to an operation written in a target-specific language.