Passlack, M. and Zurcher, P. and Rajagopalan, K. and Droopad, R. and Abrokwah, J. and Tutt, M. and Park, Y-B and Johnson, E. and Hartin, O. and Zlotnicka, A. and Fejes, P. and Hill, R.J.W. and Moran, D.A.J. and Li, X. and Zhou, H. and Macintyre, D. and Thoms, S. and Asenov, A. and Kalna, K. and Thayne, I.G. (2007) High mobility Ill-V MOSFETs for RF and digital applications. In, *IEEE International Electron Devices Meeting (IEDM 2007), 10-12 December 2007*, pages pp. 621-624, Washington DC, USA.

http://eprints.gla.ac.uk/4040/

Deposited on: 19 March 2008

# **High Mobility III-V MOSFETs For RF and Digital Applications**

M. Passlack, P. Zurcher, K. Rajagopalan, R. Droopad, J. Abrokwah, M. Tutt, Y.-B. Park, E. Johnson, O. Hartin, A. Zlotnicka, and P. Fejes

Freescale Semiconductor, Inc., 2100 East Elliot Road, Tempe, AZ 85284 USA

R.J.W. Hill, D.A.J. Moran, X. Li, H. Zhou, D. Macintyre, S. Thoms, A. Asenov, K. Kalna, and I.G. Thayne Nanoelectronics Research Centre, University of Glasgow, Rankine Building, Oakfield Avenue, Glasgow, G12 8LT UK

#### Abstract

Developments over the last 15 years in the areas of materials and devices have finally delivered competitive III-V MOS-FETs with high mobility channels. This paper briefly reviews the above developments, discusses properties of the GdGaO/Ga<sub>2</sub>O<sub>3</sub> MOS systems, presents GaAs MOSFET DC and RF data, and concludes with an outlook for high indium content channel MOSFETs. GaAs based MOSFETs are potentially suitable for RF power amplification, switching, and front-end integration in mobile and wireless applications while MOSFETs with high indium content channels are of interest for future CMOS applications.

#### Introduction

Novel device architectures, high-κ gate dielectrics, metal gates, and high mobility channel materials will be required to continue CMOS device scaling according to Moore's Law and the International Technology Roadmap for Semiconductors (1). In the shorter term, high mobility GaAs MOSFET development will likely be more driven by RF applications. Developments over the last 15 years including the discovery of the device quality, MBE (molecular beam epitaxy) grown Ga<sub>2</sub>O<sub>3</sub>/ GaAs interface in 1996 (2), the concept of bilayer dielectric stacks in 1995 (3), the proposal of heterostructure use to mitigate high band-edge interface-state density in 1997 (4), the realization of bilayer GdGaO/Ga2O3 dielectric stacks on GaAs in 1999 (5), the concept/fabrication of implant-free enhancement-mode high-mobility MOSFETs in 2000/2005 (6), (7), and the realization of low R<sub>c</sub> Ohmic contacts in 2006 (8) have finally delivered competitive GaAs MOSFETs with effective channel mobilities exceeding 5,500 cm<sup>2</sup>/Vs. Electron Hall mobilities of 12,000 cm<sup>2</sup>/Vs have been measured in InP based MOSFET structures with In<sub>0.75</sub>Ga<sub>0.25</sub>As channel layers (9). This paper discusses oxide/GaAs interface properties, presents GaAs MOSFET DC and RF data, and concludes with an outlook for high indium content channels for future CMOS applications.

### Wafer Manufacturing

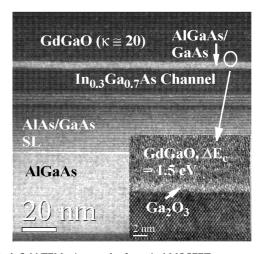

MOSFET wafers have been fabricated by MBE using an ultrahigh vacuum (UHV) dual chamber configuration manufactured by DCA Instruments. Fig. 1 shows a dark field TEM micrograph of a typical GaAs MOSFET layer structure with an In<sub>0.3</sub>Ga<sub>0.7</sub>As channel. Further fabrication details can be found in (10).

#### **Results and Discussion**

## A. Oxide-GaAs Interface Properties

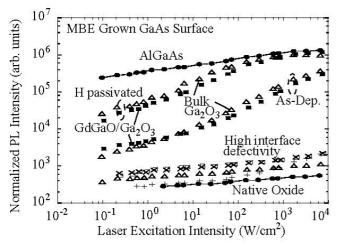

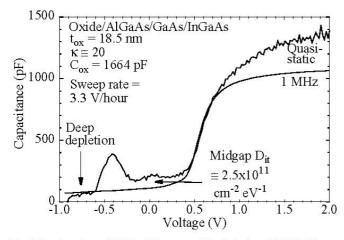

Electrical interface properties of  $Ga_2O_3$  films and  $GdGaO/Ga_2O_3$  dielectric stacks have been determined by a photoluminescence-intensity (PL-I) technique and by capacitance-voltage measurements. All investigated materials (Si, AlN,  $In_2O_3$ ,  $SiO_x$ , MgO,  $Al_xO_y$ ,  $Ti_xO_y$ ,  $Ta_xO_y$ ,  $Mo_xO_y$ ,  $Zr_xO_y$ ,  $Gd_2O_3$ ,  $LaAlO_3$ , O,  $O_2$ ) show essentially native oxide behavior on GaAs (group of high-interface defectivity films) except for  $Ga_2O_3$  which provides a device quality interface (Fig. 2). Typical quasi-static and high-frequency (1 MHz) C-V curves of the dielectric stack deposited on a MOSFET-like epitaxial structure of Fig. 1 are shown in Fig. 3.

Fig. 1 Dark field TEM micrograph of a typical MOSFET structure with an InGaAs channel. The inset shows a high resolution TEM micrograph of the oxide/semiconductor interface.

Fig. 2 Normalized GaAs photoluminescence (PL) intensity as a function of excitation intensity for AlGaAs (solid circles), bulk Ga<sub>2</sub>O<sub>3</sub> (open triangles), GdGaO/Ga<sub>2</sub>O<sub>3</sub> (solid squares), high interface defectivity films, and native oxide (solid circles) on GaAs. All materials are deposited on MBE grown surfaces under UHV conditions (except for native oxide).

Fig. 3 Quasi-static and 1 MHz C-V curves of the GaAs based MOSFET structure shown in Fig. 1. The midgap interface state density for the dielectric stack with  $\kappa = 20$  is determined to be  $\cong 2.5 \times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup>.

#### B. GaAs MOSFET DC and RF Data

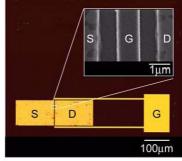

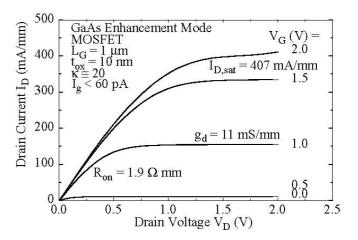

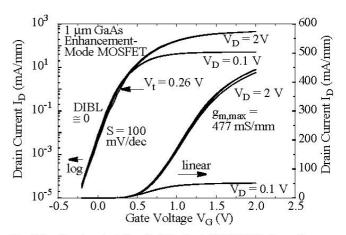

Enhancement-mode 1 μm n-channel GaAs MOSFETs with metal gate (Pt) and a 10 nm high-κ dielectric GdGaO/Ga<sub>2</sub>O<sub>3</sub> (κ  $\cong$  20) have been manufactured based on the implant-free device architecture proposed in (6). A two-level wrap-around gate design (where the gate encircles the drain) was used to simplify the device process flow, removing the need for isolation (see Fig. 4). With typical figures of merit including threshold voltage,  $V_t = +0.26~V$ , peak transconductance,  $g_{m,max} = 477~mS/mm$ , on-resistance,  $R_{on} = 1.9~\Omega$  mm, saturation drive current,  $I_{D,sat} = 407~mA/mm$ , gate leakage current,  $I_g < 60~pA$ , output conductance,  $g_d = 11~mS/mm$ , and subthreshold swing, S = 100~mV/dec (Fig. 5, Fig. 6), our GaAs

Fig. 4 Optical micrograph and SEM image of a 1  $\,\mu m$  gate length GaAs MOSFET with wrap-around gate design. The source-drain distance is 2.7  $\mu m$ .

Fig. 5 Output characteristics of a 1  $\mu$ m GaAs MOSFET.

Fig. 6 Transfer characteristics of a 1  $\mu$ m GaAs MOSFET.  $I_{on}/I_{off}$  ratio =  $6.3x10^4$  ( $I_{off}$ ,  $V_G$  = 0 V,  $V_D$ = 2 V) ( $I_{on}$ ,  $V_G$  = 2 V,  $V_D$  = 2 V) and drain-induced barrier lowering, DIBL  $\cong 0$ .

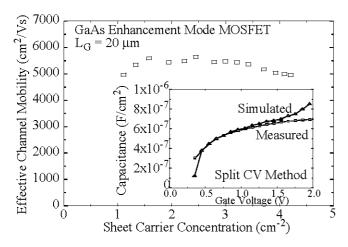

enhancement-mode MOSFETs perform as predicted by 2-dimensional device simulation. In contrast, GaAs enhancement-mode devices published by other groups over the last 40 years had typical  $g_m$  of less than 1 mS/mm with some recent marginal improvement into the 10-20 mS/mm range (11), (12). The peak effective channel electron mobility

Fig. 7 Effective channel electron mobility as a function of sheet carrier density. The inset shows measured and simulated capacitance as a function of gate voltage.

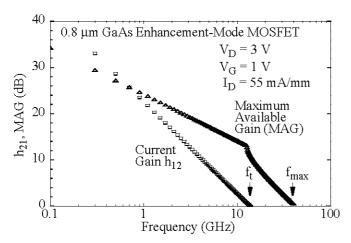

Fig. 8 Current gain  $h_{21}$  and maximum available gain MAG for a 0.8  $\mu m$  GaAs enhancement-mode MOSFET (W =  $2x100~\mu m$ ).  $f_t$  and  $f_{max}$  are 13 and 42 GHz, respectively.

is  $\cong 5,500 \text{ cm}^2/\text{Vs}$  (Fig. 7) as measured by an advanced split-CV method (13).

The gate and ohmic modules employed in the wrap-around gate design have been integrated into a flow for coplanar devices using oxygen implantation for device isolation. A first run has resulted in enhancement-mode devices ( $V_t \cong +0.4 \text{ V}$ ) with reduced DC performance of  $g_m = 135\text{-}160 \text{ mS/mm}$ ,  $R_{on} = 7\text{-}10 \Omega$  mm, and  $I_{D,sat} = 175 \text{ mA/mm}$ . Small-signal parameters have been measured (Fig. 8) and average  $f_t$  and  $f_{max}$  of 13 GHz and 37 GHz ( $L_G = 1 \mu m$ ), and of 14 GHz and 40 GHz ( $L_G = 0.8 \mu m$ ), respectively, have been obtained (2x100, 2x200, 2x300  $\mu m$  width). Preliminary on-wafer load-pull measurements at f = 900 MHz tuned for maximum power in class AB operation, provided  $P_{out} = 12.4 \text{ dBm}$  with a corresponding gain of 11.3 dB and a power added efficiency of

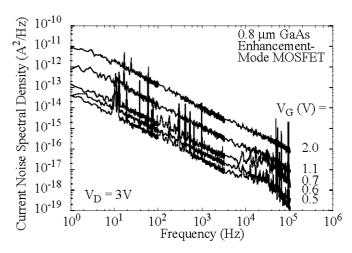

Fig. 9 Current noise spectral density vs. frequency with log-log scale with gate voltage bias point as a parameter for a  $0.8~\mu m$  GaAs enhancement-mode MOSFET (W =  $2x200~\mu m$ ).

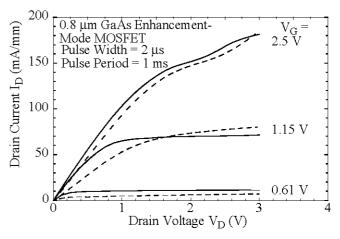

Fig. 10 DC (solid lines) and pulsed (dashed lines) I-V data of a 0.8  $\mu m$  GaAs enhancement-mode MOSFET (W = 2x100  $\mu m$ ). The quiescent point for pulsed I-V is  $V_D$  = 3V and 10%  $I_{D,sat}(V_G\!\cong\!0.6~V)$ .

45.6% (2x300  $\mu$ m). Low frequency noise results are indicative of 1/f noise behavior with flicker noise typical of Si based MOSFETs (Fig. 9). Preliminary pulsed I-V measurements show small dispersion, with maximum dispersion occurring in the linear region at small  $V_D$  and in the threshold region (Fig. 10).

## C. Towards CMOS

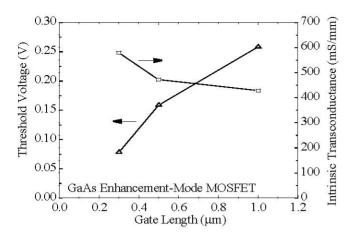

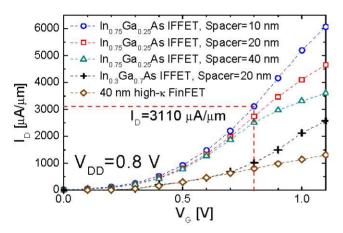

Preliminary lateral scaling data for  $0.3 \le L_G \le 1~\mu m$  GaAs enhancement-mode MOSFETs with  $In_{0.3}Ga_{0.7}As$  channels are shown in Fig. 11. To predict the performance of aggressively scaled III-V MOSFETs, we have used a finite element Monte-Carlo device simulator (14) verified against experimental data (sheet carrier density and mobility). As shown in Fig. 12, sub-20 nm gate length MOSFETs with  $In_{0.3}Ga_{0.7}As$  channels could reach peak drive currents of around  $1000~\mu A/\mu m$  at 0.8

Fig. 11 Threshold voltage and intrinsic transconductance vs. gate length of 1, 0.5, and 0.3  $\mu m$  GaAs MOSFET with an oxide thickness of 10 nm. The vertical layer structure was not scaled. Source-drain distance is 1.7  $\mu m$  for  $L_G=0.3$  and 0.5  $\mu m$ , and 2.7  $\mu m$  for  $L_G=1$   $\mu m$ .

Fig. 12 Comparison of Monte-Carlo simulation of 15 nm III-V MOSFETs with different sidewall spacer sizes with a fabricated Si FINFET at  $\rm V_D$ =0.8 V (supply voltage at the ITRS 22 nm node).

V supply voltages, outperforming the leading Si FINFET technologies (15). Moving to an  $In_{0.75}Ga_{0.25}As$  channel potentially improves the drive current in excess of 2700  $\mu A/\mu m$  (the current ITRS 22 nm technology generation target).

## Summary

All investigated materials on GaAs were found to show essentially native oxide behavior except for  $\rm Ga_2O_3$  which provides a device quality interface. 1  $\mu m$  GaAs enhancement-mode MOSFETs employing GdGaO/Ga\_2O\_3 dielectric stacks have been manufactured with  $V_t$ ,  $\rm I_{D,sat}$ ,  $g_{m,max}$ ,  $R_{on}$ ,  $g_d$ , S, and  $\rm I_g$  of 0.26 V, 407 mA/mm, 477 mS/mm, 1.9  $\Omega$  mm, 11 mS/mm, 100 mV/dec, and < 60 pA, respectively. An off-state breakdown voltage of 18 V was obtained for an oxide thickness of 18 nm. An effective channel mobility of  $\cong$  5,500 cm $^2/\rm Vs$  was measured using the split C-V method. A first coplanar process

flow produced an average  $f_t$  and  $f_{max}$  of 13 GHz and 37 GHz ( $L_G$  = 1  $\mu m$ ), and of 14 GHz and 40 GHz ( $L_G$  = 0.8  $\mu m$ ).

#### References

- International Technology Roadmap for Semiconductors. (2006).

[Online]. Available: http://www.itrs.net/Links/2006Update/ 2006UpdateFinal.htm

- (2) M. Passlack, R.N. Legge, D. Convey, Z. Yu, and J.K. Abrokwah, "Optical measurement system for characterizing compound semiconductor interface and surface states," *IEEE Trans. Instrum. Meas.*, vol. 47, no. 5, pp. 1362 1366, 1998.

- M. Passlack, "Method of forming a dielectric layer structure," US Patent 5,665,658, issued 09/09/97.

- (4) M. Passlack, J. Wang, J. Abrokwah, and Z. Yu, "Insulator-compound semiconductor interface structure" US Patent 6.359.294, issued 03/19/02.

- (5) M. Passlack, "Methodology for Development of High-κ Stacked Gate Dielectrics on III-V Semiconductors," in *Materials Fundamentals of Gate Dielectrics*," edited by A.A. Demkov and A. Navrotsky, Springer Verlag, 2005, pp. 403-467.

- (6) M. Passlack, O. Hartin, M. Ray, N. Medendorp, "Enhancement mode metal-oxide-semiconductor field effect transistor," US Patent 6,963,090, issued 11/08/05.

- (7) M. Passlack, K. Rajagopalan, J. Abrokwah, and R. Droopad, "Implant-Free, High Mobility Flatband MOSFET: Principles of Operation," *IEEE Trans. Electron. Dev.*, vol. ED-53, no. 10, pp. 2454-2459, 2006.

- (8) R.J.W. Hill et al., "Enhancement-mode GaAs MOSFETs with In<sub>0.3</sub>Ga<sub>0.7</sub>As channel, mobility over 5000 cm<sup>2</sup>/Vs and transconductance over 475 μS/μm," IEEE Electron. Dev. Lett., 2007.

- (9) R. Droopad, K. Rajagopalan, J. Abrokwah, M. Canonico, and M. Passlack, "In<sub>0.75</sub>Ga<sub>0.25</sub>As Channel Layers with Record Mobility Exceeding 12,000 cm<sup>2</sup>/Vs for Use in High-κ Dielectric NMOSFETs," *Solid State Electronics*, vol. 50, no 7-8, pp. 1175-1177, 2006.

- (10) R. Droopad, J. Abrokwah, K. Rajagopalan, L. Adams, N. England, D. Uebelhoer, and M. Passlack, "Development of GaAs-based MOSFET using Molecular Beam Epitaxy," J. of Crystal Growth, vol. 301-302, pp. 139-144, 2007.

- (11) M. Tametou, M. Takebe, K. Nakamura, N.C. Paul, K. Iiyama, and S. Takamiya, "Improved Transconductance N-Channel Enhancement/Inversion Mode GaAs-MISFETs with Gate Insulating Layers Formed by Dry Oxi-Nitridation," Proc. 2004 International Conference on Indium Phosphide and Related Materials, pp. 187-190.

- (12) P. Fay, X. Li, Y. Cao, J. Zhang, T.H. Kosel, and D.C. Hall, "III-V MOS-FETs with Native Oxide Gate Dielectrics," Proc. 2007 MANTECH, pp. 227-230.

- (13) W. Zhu W, J.-P. Han, and T.P. Ma, "Mobility measurement and degradation mechanism of MOSFETs made with ultrathin high-κ dielectrics," IEEE Trans. Electron Devices, vol. 51, no. 1, pp. 98-105, 2004.

- (14) K. Kalna et al., "Monte Carlo simulations of high performance implant free In<sub>0.3</sub>Ga<sub>0.7</sub>As nano-MOSFETs for low-power CMOS applications," IEEE Trans. Nanotechnol. vol. 6, no. 1, pp. 106-112, 2007.

- (15) J. Kavalieros et al., "Tri-Gate Transistor Architecture with High-k Gate Dielectrics, Metal Gates and Strain Engineering," 2006 Symp VLSI. Technol. Tech Dig., pp. 62-63, 2006.

### Acknowledgment

The authors would like to thank N. England and D. Uebelhoer for MBE wafer growth, L. Adams for wafer processing, L. Kaufmann and H. Stewart for electrical device measurements, and the Physical Analysis Laboratories for analysis support. Finally, the authors would like to thank K. Johnson and M. Miller for their support.