**ABSTRACT**

Title of Document: HIGH-PERFORMANCE 3D IMAGE

PROCESSING ARCHITECTURES FOR IMAGE-GUIDED INTERVENTIONS

Omkar Dandekar, Ph.D., 2008

Directed By: Professor Raj Shekhar (Chair/Advisor),

Professor Shuvra S. Bhattacharyya (Co-advisor), Department of Electrical and Computer Engineering

Minimally invasive image-guided interventions (IGIs) are time and cost efficient, minimize unintended damage to healthy tissues, and lead to faster patient recovery. Advanced three-dimensional (3D) image processing is a critical need for navigation during IGIs. However, achieving on-demand performance, as required by IGIs, for these image processing operations using software-only implementations is challenging because of the sheer size of the 3D images, and memory and compute intensive nature of the operations. This dissertation, therefore, is geared toward developing high-performance 3D image processing architectures, which will enable improved intraprocedural visualization and navigation capabilities during IGIs.

In this dissertation we present an architecture for real-time implementation of 3D filtering operations that are commonly employed for preprocessing of medical images. This architecture is approximately two orders of magnitude faster than

| maintaining the data needed, and c<br>including suggestions for reducing          | lection of information is estimated to<br>ompleting and reviewing the collect<br>this burden, to Washington Headqu<br>uld be aware that notwithstanding an<br>DMB control number. | ion of information. Send comments<br>arters Services, Directorate for Info | regarding this burden estimate or regarding this burden estimate or regarding the rega | or any other aspect of the 1215 Jefferson Davis | nis collection of information,<br>Highway, Suite 1204, Arlington |  |  |

|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------------------------------------------------|--|--|

| 1. REPORT DATE 2008 2. REPORT TYPE                                                |                                                                                                                                                                                   |                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                 | 3. DATES COVERED <b>00-00-2008 to 00-00-2008</b>                 |  |  |

| 4. TITLE AND SUBTITLE                                                             |                                                                                                                                                                                   |                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5a. CONTRACT NUMBER                             |                                                                  |  |  |

| High-Performance 3D Image Processing Architectures for Image-Guided Interventions |                                                                                                                                                                                   |                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5b. GRANT NUMBER                                |                                                                  |  |  |

|                                                                                   |                                                                                                                                                                                   |                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5c. PROGRAM ELEMENT NUMBER                      |                                                                  |  |  |

| 6. AUTHOR(S)                                                                      |                                                                                                                                                                                   |                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5d. PROJECT NUMBER                              |                                                                  |  |  |

|                                                                                   |                                                                                                                                                                                   |                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5e. TASK NUMBER                                 |                                                                  |  |  |

|                                                                                   |                                                                                                                                                                                   |                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5f. WORK UNIT NUMBER                            |                                                                  |  |  |

| <b>University of Mary</b>                                                         | ZATION NAME(S) AND AE<br>land, College Park,<br>ring,College Park,N                                                                                                               | Department of Elec                                                         | etrical and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8. PERFORMING<br>REPORT NUMB                    | G ORGANIZATION<br>ER                                             |  |  |

| 9. SPONSORING/MONITO                                                              | RING AGENCY NAME(S) A                                                                                                                                                             | ND ADDRESS(ES)                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10. SPONSOR/M                                   | ONITOR'S ACRONYM(S)                                              |  |  |

|                                                                                   |                                                                                                                                                                                   |                                                                            | 11. SPONSOR/MONITOR'S REPORT<br>NUMBER(S)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                 |                                                                  |  |  |

| 12. DISTRIBUTION/AVAII Approved for publ                                          | LABILITY STATEMENT ic release; distributi                                                                                                                                         | on unlimited                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                 |                                                                  |  |  |

| 13. SUPPLEMENTARY NO                                                              | OTES                                                                                                                                                                              |                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                 |                                                                  |  |  |

| 14. ABSTRACT see report                                                           |                                                                                                                                                                                   |                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                 |                                                                  |  |  |

| 15. SUBJECT TERMS                                                                 |                                                                                                                                                                                   |                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                 |                                                                  |  |  |

| 16. SECURITY CLASSIFICATION OF:                                                   |                                                                                                                                                                                   | 17. LIMITATION OF ABSTRACT                                                 | 18. NUMBER<br>OF PAGES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 19a. NAME OF<br>RESPONSIBLE PERSON              |                                                                  |  |  |

| a. REPORT<br>unclassified                                                         | b. ABSTRACT<br><b>unclassified</b>                                                                                                                                                | c. THIS PAGE<br><b>unclassified</b>                                        | Same as<br>Report (SAR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 220                                             |                                                                  |  |  |

**Report Documentation Page**

Form Approved OMB No. 0704-0188 corresponding software implementations and is capable of processing 3D medical images at their acquisition speeds.

Combining complementary information through registration between pre- and intraprocedural images is a fundamental need in the IGI workflow. Intensity-based deformable registration, which is completely automatic and locally accurate, is a promising approach to achieve this alignment. These algorithms, however, are extremely compute intensive, which has prevented their clinical use. We present an FPGA-based architecture for accelerated implementation of intensity-based deformable image registration. This high-performance architecture achieves over an order of magnitude speedup when compared with a corresponding software implementation and reduces the execution time of deformable registration from hours to minutes while offering comparable image registration accuracy.

Furthermore, we present a framework for multiobjective optimization of finite-precision implementations of signal processing algorithms that takes into account multiple conflicting objectives such as implementation accuracy and hardware resource consumption. The evaluation that we have performed in the context of FPGA-based image registration demonstrates that such an analysis can be used to enhance automated hardware design processes, and efficiently identify a system configuration that meets given design constraints. In addition, we also outline two novel clinical applications that can directly benefit from these developments and demonstrate the feasibility of our approach in the context of these applications. These advances will ultimately enable integration of 3D image processing into clinical workflow.

# HIGH-PERFORMANCE 3D IMAGE PROCESSING ARCHITECTURES FOR IMAGE-GUIDED INTERVENTIONS

By

#### Omkar Dandekar

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2008

Advisory Committee: Professor Raj Shekhar, Chair/Advisor Professor Shuvra S. Bhattacharyya, Co-advisor Professor Rama Chellappa Professor Manoj Franklin Professor Yang Tao © Copyright by Omkar Dandekar 2008

# **Dedication**

To my Mother, Mangal, Himani, and the memories of my late Father, for their love and support

#### **Publications**

- W. Plishker, O. Dandekar, S. Bhattacharyya, and R. Shekhar, "Towards a heterogeneous medical image registration acceleration platform," *IEEE Transactions on Biomedical Circuits and Systems*, (in preparation), 2008.

- R. Shekhar, O. Dandekar, V. Bhat, R. Mezrich, and A. Park, "Development of CT-guided minimally invasive surgery," *Surgical Innovation*, (in preparation), 2008.

- O. Dandekar, W. Plishker, S. S. Bhattacharyya, and R. Shekhar, "Multiobjective optimization for reconfigurable implementation of medical image registration," *International Journal of Reconfigurable Computing*, (under review), 2008.

- P. Lei, O. Dandekar, D. Widlus, P. Malloy, and R. Shekhar, "Incorporation of PET into CT-guided liver radiofrequency ablation," *Radiology, (under revision)*, 2008.

- O. Dandekar, W. Plishker, S. S. Bhattacharyya, and R. Shekhar, "Multiobjective optimization of FPGA-based medical image registration," presented at *IEEE Symposium on Field-Programmable Custom Computing Machines*, 2008.

- O. Dandekar and R. Shekhar, "FPGA-accelerated deformable image registration for improved target-delineation during CT-guided interventions," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 1 (2), 2007, pp. 116-127.

- O. Dandekar, C. Castro-Pareja, and R. Shekhar, "FPGA-based real-time 3D image preprocessing for image-guided medical interventions," *Journal of Real-Time Image Processing*, vol. 1 (4), pp. 285-301, 2007.

- W. Plishker, O. Dandekar, S. Bhattacharyya, and R. Shekhar, "Towards a heterogeneous medical image registration acceleration platform," presented at IEEE Biomedical Circuits and Systems Conference, 2007, pp. 231-234.

- O. Dandekar, K. Siddiqui, V. Walimbe, and R. Shekhar, "Image registration accuracy with low-dose CT: How low can we go?," presented at *IEEE International Symposium on Biomedical Imaging*, 2006, pp. 502-505.

- C. R. Castro-Pareja, O. Dandekar, and R. Shekhar, "FPGA-based real-time anisotropic diffusion filtering of 3D ultrasound images," in *SPIE Real-Time Imaging*, 2005, pp. 123-131.

- S. Venugopal, C. R. Castro-Pareja, and O. Dandekar, "An FPGA-based 3D image processor with median and convolution filters for real-time applications," in *SPIE Real-Time Imaging*, 2005, pp. 174-182.

## Acknowledgements

I would like to express my sincere gratitude to Dr. Raj Shekhar for his guidance and financial support throughout my graduate education at The Ohio State University, the Cleveland Clinic, and University of Maryland. He has been the perfect mentor for my doctoral research, and a person from whom I have learnt a lot during the past five years. He ensured that I master not only the intricacies of medical image processing, but also put a strong emphasis on developing the qualities necessary for effective dissemination of scientific research and results. Beyond doubt, he has played the most important role in shaping my technical writing and presentation skills. All throughout my graduate career he has made himself available at any moment when I needed his inputs and feedback for my work or anything else. The time spent working with Dr. Shekhar has truly been the most rewarding career experience of my life.

I would also like to thank my dissertation committee members, Prof. Shuvra Bhattacharyya, Prof. Rama Chellappa, Prof. Manoj Franklin, and Prof Yang Tao for their cooperation and support. I would especially like to thank Prof. Bhattacharyya for his help and collaboration in my work that resulted in an important chapter of this dissertation. The research work reported in this dissertation was partly supported by U.S. Department of Defense (TATRC) under grant DAMD17-03-2-0001.

My research at the University of Maryland would not have been possible without the support and encouragement of Drs. Rueben Mezrich, Adrian Park, Eliot Siegel, Khan Siddiqui, Nancy Knight, Faaiza Mahmoud, Steve Kavic, and all clinical staff at the University of Maryland and Baltimore VA. Whenever I

requested, they have spared valuable time from their busy schedules for discussions with me, and have been immensely helpful especially during the clinical validation studies. Dr. Siddiqui, in particular, was instrumental in providing clinical perspective on some of the research problems I have explored.

I would like to thank Prof. Jogikal Jagadeesh for allowing me to work in his lab during my first two years at the Ohio State University, and for his crucial guidance during early stages of my graduate education. I am also thankful to Dr. Carlos R. Castro-Pareja, Dr Vivek Walimbe, Dr William Plishker, Dr. Jianzhou Wu, Peng Lei, and Venkatesh Bhat from Dr. Shekhar's research group for providing valuable help and inputs at various times during my research.

My parents have always been the biggest source of inspiration in my life. They have always stressed the importance of education and instilled in me the virtues of honest and dedicated effort, for which I will forever be indebted to them. Their love and constant encouragement has been an important driving force throughout my life. I would like to thank my sister, Mangal, for her kind words of encouragement from time to time during the last few years. I would like to especially mention my long time friends Mukta, Prashant, Sandip, Siddharth, Rahul, Rakhi, and Vinayak, for always being there with me.

Last, and most importantly, I would like to thank Himani – my wife and my best friend. She has shown incredible patience and understanding throughout the course of my graduate studies. I would not have been able to successfully complete my doctoral program without the constant encouragement and motivation she provided. My achievements are my tribute to her unconditional love and support.

# **Table of Contents**

| Dedication                                                            | ii    |

|-----------------------------------------------------------------------|-------|

| Publications                                                          | iii   |

| Acknowledgements                                                      | v     |

| Table of Contents                                                     | . vii |

| List of Tables                                                        | X     |

| List of Figures                                                       | xiii  |

| Chapter 1: Introduction                                               | 1     |

| 1.1. Overview                                                         | 1     |

| 1.2. Contributions of this Dissertation                               | 3     |

| 1.2.1. Real-time 3D Image Preprocessing                               | 4     |

| 1.2.2. Hardware-Accelerated Deformable Image Registration             |       |

| 1.2.3. Framework for Optimization of Finite Precision Implementations |       |

| 1.3. Outline of this Dissertation                                     | 7     |

| Chapter 2: Background and Related Work                                |       |

| 2.1. Image-Guided Interventions                                       | 9     |

| 2.1.1. Role of Preprocedural Imaging                                  |       |

| 2.1.2. Need for Image Registration                                    | . 12  |

| 2.2. Classification of Image Registration                             | . 13  |

| 2.2.1. Image Registration using Extrinsic Information                 | . 14  |

| 2.2.2. Image Registration using Intrinsic Information                 | . 15  |

| 2.3. Intensity-Based Image Registration                               | . 17  |

| 2.3.1. Transformation Models                                          |       |

| 2.3.2. Image Similarity Measures                                      | . 22  |

| 2.3.3. Optimization Algorithms                                        | . 26  |

| 2.4. Image Preprocessing                                              | . 28  |

| 2.4.1. Anisotropic Diffusion Filtering                                |       |

| 2.4.2. Median Filtering                                               | . 31  |

| 2.5. Optimization of Finite Precision Implementations                 | . 32  |

| 2.5.1. Optimal Wordlength Formulation                                 | . 33  |

| 2.5.2. Simulation-Based Optimal Wordlength Search                     | . 34  |

| 2.5.3. Multiobjective Optimization                                    | . 35  |

| 2.6. Related Work                                                     | . 37  |

| 2.6.1. Real-Time Image Preprocessing                                  | . 37  |

| 2.6.2. Acceleration of Image Registration                             |       |

| 2.6.3. Optimization of Finite Precision Implementations               |       |

| Chapter 3: Real-time 3D Image Processing                              |       |

| 3.1. Motivation                                                       | . 47  |

| 3.2. Filtering Algorithms                                             | . 50  |

| 3.2.1. Anisotropic Diffusion Filtering                                |       |

| 3.2.2. Median Filtering                                               |       |

| 3.3. Architecture                                                     | . 52  |

| 3.3.1. Memory Controller and Brick-caching Scheme                         | 54  |

|---------------------------------------------------------------------------|-----|

| 3.3.2. 3D Anisotropic Diffusion Filtering                                 | 58  |

| 3.3.3. Median Filtering                                                   | 64  |

| 3.4. Implementation and Results                                           | 68  |

| 3.4.1. Effects of Finite Precision Representation                         | 69  |

| 3.4.2. Hardware Requirements                                              |     |

| 3.4.3. Filtering Performance                                              | 75  |

| 3.5. Summary                                                              | 78  |

| Chapter 4: Hardware-Accelerated Deformable Image Registration             | 80  |

| 4.1. Motivation                                                           | 80  |

| 4.2. Algorithm for Deformable Image Registration                          | 83  |

| 4.2.1. Calculating MI for a Subvolume                                     | 85  |

| 4.3. Acceleration Approach                                                | 86  |

| 4.4. Architecture                                                         | 88  |

| 4.4.1. Voxel Counter                                                      | 89  |

| 4.4.2. Coordinate Transformation                                          | 90  |

| 4.4.3. Partial Volume Interpolation                                       | 92  |

| 4.4.4. Image Memory Access                                                | 94  |

| 4.4.5. Updating Mutual Histogram                                          | 99  |

| 4.4.6. Entropy Calculation                                                |     |

| 4.4.7. Operational Workflow                                               |     |

| 4.5. Implementation and Results                                           | 111 |

| 4.5.1. Execution Speed                                                    | 114 |

| 4.5.2. Performance Comparison                                             | 117 |

| 4.5.3. Qualitative Evaluation of Deformable Image Registration            |     |

| 4.6. Summary                                                              | 124 |

| Chapter 5: Framework for Optimization of Finite Precision Implementations | 126 |

| 5.1. Motivation                                                           | 126 |

| 5.2. Multiobjective Optimization                                          | 129 |

| 5.2.1. Problem Statement                                                  | 129 |

| 5.2.2. Parameterized Architectural Design                                 | 131 |

| 5.2.3. Multiobjective Optimization Framework                              | 134 |

| 5.3. Experiments and Results                                              | 142 |

| 5.3.1. Metrics for Comparison of Pareto-optimized Solution Sets           | 146 |

| 5.3.2. Accuracy of Image Registration                                     | 148 |

| 5.3.3. Post-synthesis Validation                                          | 150 |

| 5.4. Summary                                                              | 154 |

| Chapter 6: Clinical Applications                                          |     |

| 6.1. Radiation Dose Reduction                                             | 157 |

| 6.1.1. Motivation                                                         | 157 |

| 6.1.2. Dose Reduction Strategy                                            |     |

| 6.1.3. Evaluation of Registration Accuracy with Low-Dose CT               | 159 |

| 6.1.4. Experiments                                                        | 163 |

| 6.1.5. Results                                                            | 164 |

| 6.1.6. Summary                                                            |     |

| 6.2. Incorporation of PET into CT-Guided Liver Radio-Frequency Ablation   | 168 |

| 6.2.1. Motivation                      | 168 |

|----------------------------------------|-----|

| 6.2.2. Registration of PET and CT      | 170 |

| 6.2.3. Experiments                     | 171 |

| 6.2.4. Results                         | 174 |

| 6.2.5. Summary                         | 178 |

| Chapter 7: Conclusions and Future Work |     |

| 7.1. Conclusion                        | 180 |

| 7.2. Future Work                       | 185 |

| Bibliography                           | 189 |

# **List of Tables**

| Table 2.1: | Broad classification of image registration in the context of IGI        | . 13 |

|------------|-------------------------------------------------------------------------|------|

| Table 3.1: | Software execution time of 3D anisotropic diffusion filtering and 3I    | )    |

|            | median filtering of 8-bit images for common kernel sizes (N)            | . 48 |

| Table 3.2: | Average error in intensity per voxel for a Gaussian filtered image      |      |

|            | resulting from fixed-point representation of Gaussian coefficients      | . 69 |

| Table 3.3: | Average error per sample of diffusion function resulting from fixed-    | -    |

|            | point representation of diffusion coefficients employed in the          |      |

|            | presented architecture.                                                 | . 70 |

| Table 3.4: | Average error in intensity per voxel for anisotropic diffusion filtered | d    |

|            | resulting from fixed-point representation of Gaussian coefficients ar   | nd   |

|            | the diffusion function                                                  | . 72 |

| Table 3.5: | Hardware requirements of the architecture for real-time 3D image        |      |

|            | preprocessing.                                                          | . 73 |

| Table 3.6: | Hardware requirements for the components of the linear systolic         |      |

|            | implementation of the 3D median filtering                               | . 74 |

| Table 3.7: | Execution time of 3D anisotropic diffusion filtering and 3D median      |      |

|            | filtering                                                               | . 75 |

| Table 3.8: | Performance comparison of the 3D anisotropic diffusion filtering        |      |

|            | kernel                                                                  | . 76 |

| Table 3.9: | Performance comparison of the 3D median filtering kernel                | . 78 |

| Table 4.1: | Configurations of LUT-based entropy calculation module that were        |      |

|            | considered in the presented architecture.                               | 106  |

| Table 4.2: | Operational workflow for performing volume subdivision–based          |

|------------|-----------------------------------------------------------------------|

|            | deformable image registration using the presented architecture 109    |

| Table 4.3: | Comparison of mutual information calculation time for subvolumes at   |

|            | various levels in volume subdivision-based deformable registration    |

|            | algorithm. 115                                                        |

| Table 4.4: | Execution time of deformable image registration                       |

| Table 4.5: | Performance comparison of the presented FPGA-based                    |

|            | implementation of intensity-based deformable image registration with  |

|            | an equivalent software implementation and prior approaches for        |

|            | acceleration of intensity-based registration                          |

| Table 5.1: | Design variables for FPGA-based architecture. Integer wordlengths are |

|            | determined based on application-specific range information, and       |

|            | fractional wordlengths are used as parameters in the multiobjective   |

|            | optimization framework                                                |

| Table 5.2: | Number of solutions explored by search methods                        |

| Table 5.3: | Parameters used for the EA-based search                               |

| Table 5.4: | Validation of the objective function models using post-synthesis      |

|            | results. The wordlengths in a design configuration correspond to the  |

|            | FWLs of the design variables identified earlier                       |

| Table 6.1: | Execution time for deformable image registration using low-dose CT.   |

|            |                                                                       |

| Table 6.2: | Execution time for deformable image registration using                |

|            | intraprocedural CT and preprocedural PET images                       |

| Table 6.3: | Interexpert variability in landmark identification across 20 image           |              |

|------------|------------------------------------------------------------------------------|--------------|

|            | pairs. PET <sub>ALGO</sub> corresponds to the software implementation of the | <del>)</del> |

|            | algorithm.                                                                   | 177          |

| Table 6.4: | Interexpert variability in landmark identification across 20 image           |              |

|            | pairs. PET <sub>ALGO</sub> corresponds to the FPGA-based implementation o    | f the        |

|            | algorithm                                                                    | 178          |

# **List of Figures**

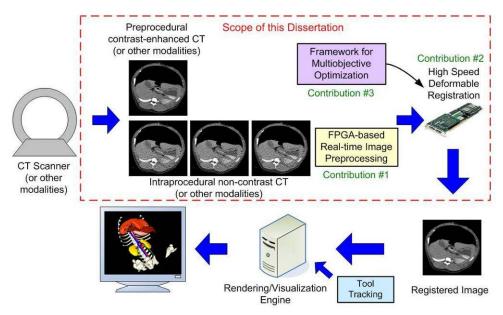

| Figure 1.1: | A typical IGI workflow and the scope of this dissertation work 3      |

|-------------|-----------------------------------------------------------------------|

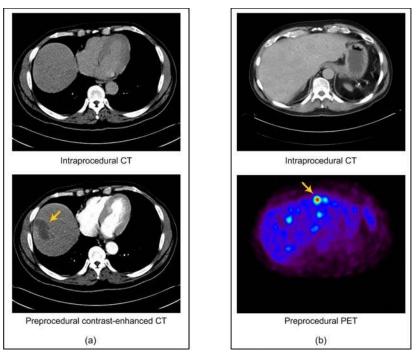

| Figure 2.1: | Two examples of pre- and intraprocedural image pairs. The arrows      |

|             | indicate the targets that are visible in preprocedural images but not |

|             | visible in intraprocedural images                                     |

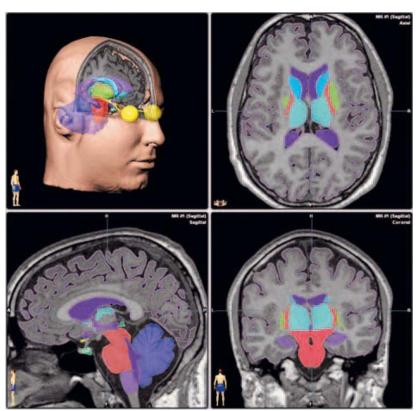

| Figure 2.2: | An example of volumetric image guidance using intraprocedural         |

|             | multislice CT and preprocedural MR                                    |

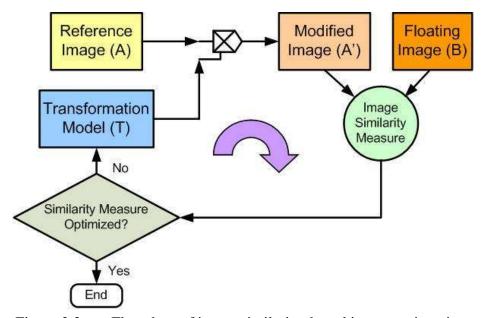

| Figure 2.3: | Flowchart of image similarity–based image registration                |

| Figure 2.4: | Example of preprocessing techniques employed prior to intensity-      |

|             | based image registration                                              |

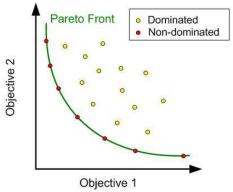

| Figure 2.5: | Pareto front in the context of multiobjective optimization            |

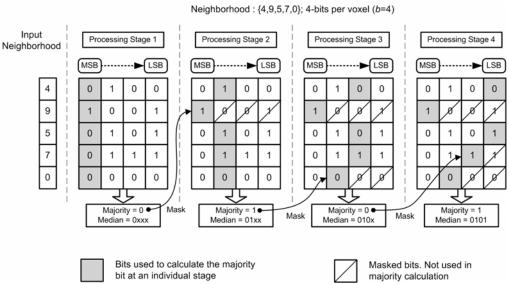

| Figure 3.1: | A median filtering example using majority voting technique 52         |

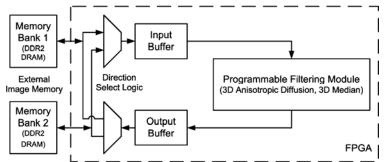

| Figure 3.2: | Block diagram of the FPGA-based real-time 3D image preprocessing      |

|             | system                                                                |

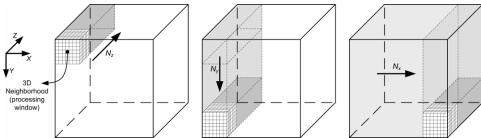

| Figure 3.3: | Typical voxel access pattern for neighborhood operations-based image  |

|             | processing. 54                                                        |

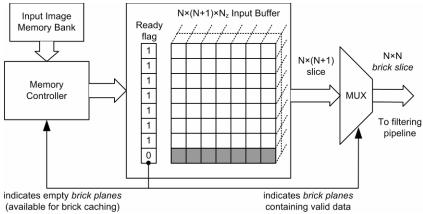

| Figure 3.4: | Block diagram showing the input image memory and the input buffer     |

|             | configuration                                                         |

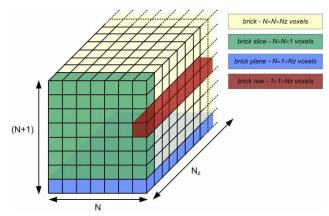

| Figure 3.5: | Pictorial representation of the notation used in the brick-caching    |

|             | scheme                                                                |

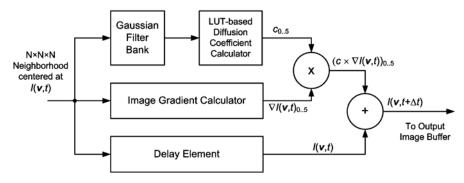

| Figure 3.6: | Top-level block diagram of 3D anisotropic diffusion filtering. This   |

|             | diagram indicates paths that are executed in parallel                 |

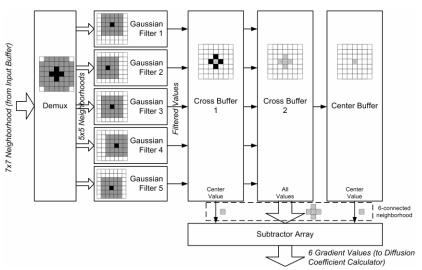

| Figure 3.7:  | Block diagram of the embedded Gaussian filter bank (for $N = 7$ ,    |      |

|--------------|----------------------------------------------------------------------|------|

|              | corresponding Gaussian kernel size is 5)                             | . 61 |

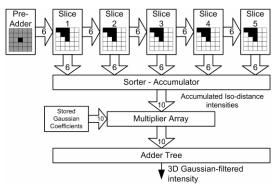

| Figure 3.8:  | Pipelined implementation of an individual Gaussian filter element    |      |

|              | (Gaussian kernel size = 5)                                           | . 62 |

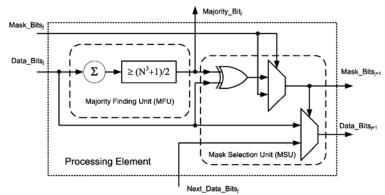

| Figure 3.9:  | A single stage (processing element) of the linear systolic median    |      |

|              | filtering kernel                                                     | . 65 |

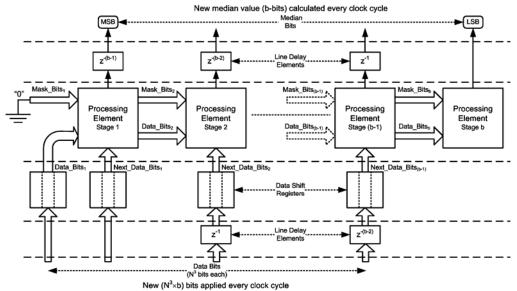

| Figure 3.10: | Linear systolic array architecture for median filter kernel using    |      |

|              | majority voting technique.                                           | . 68 |

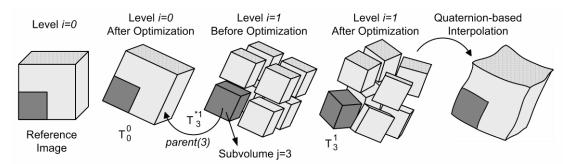

| Figure 4.1:  | Pictorial representation of hierarchical volume subdivision-based    |      |

|              | deformable image registration and associated notation.               | . 83 |

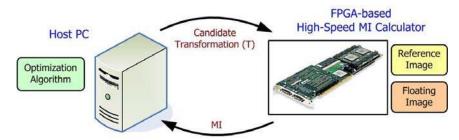

| Figure 4.2:  | Pictorial representation of the acceleration approach.               | . 86 |

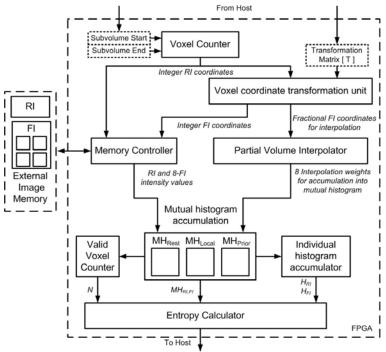

| Figure 4.3:  | Top-level block diagram of the architecture for accelerated          |      |

|              | implementation of deformable image registration.                     | . 88 |

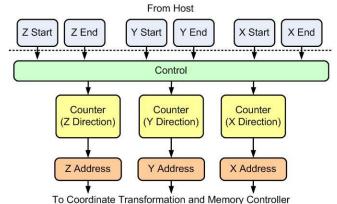

| Figure 4.4:  | Functional block diagram of voxel counter.                           | . 89 |

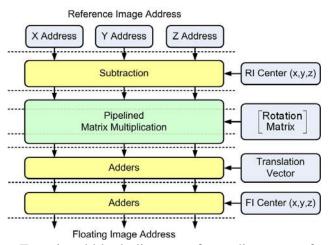

| Figure 4.5:  | Functional block diagram of coordinate transformation unit           | . 91 |

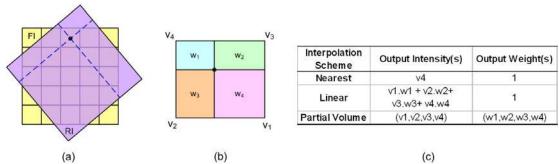

| Figure 4.6:  | Fundamentals of interpolation schemes                                | . 92 |

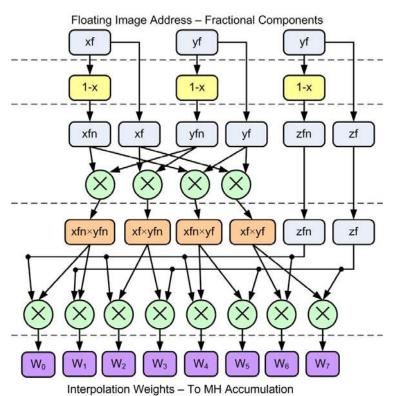

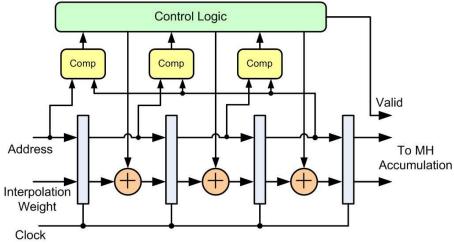

| Figure 4.7:  | Functional block diagram of partial volume interpolation unit        | . 94 |

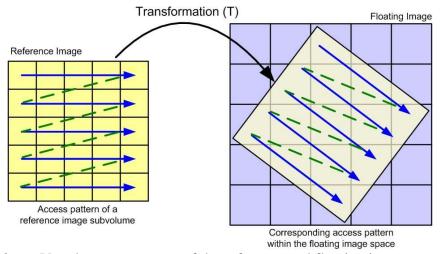

| Figure 4.8:  | Voxel access patterns of the reference and floating images encounter | ered |

|              | during image registration.                                           | . 95 |

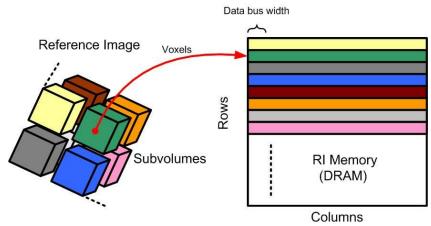

| Figure 4.9:  | Organization of the reference image memory.                          | . 97 |

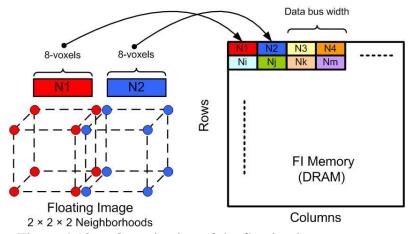

| Figure 4.10: | Organization of the floating image memory                            | . 98 |

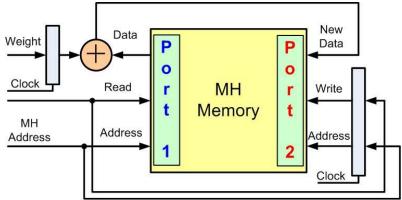

| Figure 4.11: | Pipelined implementation of MH accumulation using dual port          |      |

|              | memory                                                               | 100  |

| Figure 4.12: | Preaccumulate buffers to eliminate RAW hazards in MH accumulation       |

|--------------|-------------------------------------------------------------------------|

|              | pipeline                                                                |

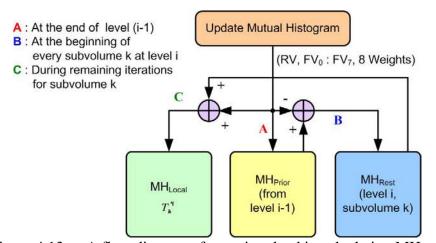

| Figure 4.13: | A flow diagram of steps involved in calculating MH <sub>Rest</sub>      |

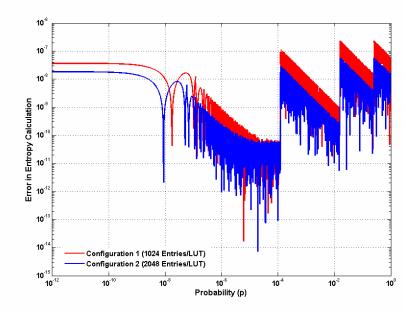

| Figure 4.14: | Error in entropy calculation corresponding to the two configurations of |

|              | the multiple LUT-based implementation                                   |

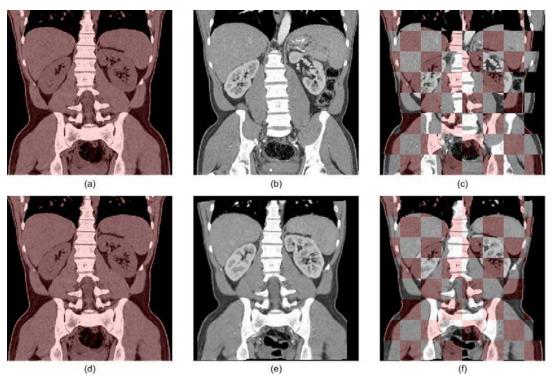

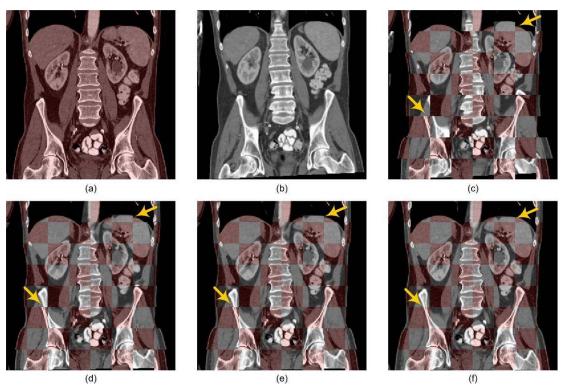

| Figure 4.15: | Qualitative validation of deformable registration between iCT and       |

|              | preCT images performed using the presented FPGA-based solution.         |

|              |                                                                         |

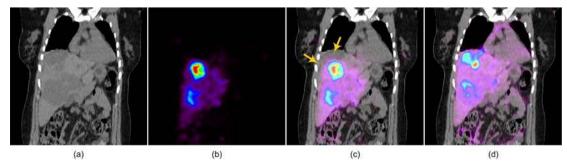

| Figure 4.16: | Qualitative validation of deformable registration between iCT and PET   |

|              | images performed using the presented FPGA-based solution 123            |

| Figure 5.1:  | Examples of parameterized architectural design style                    |

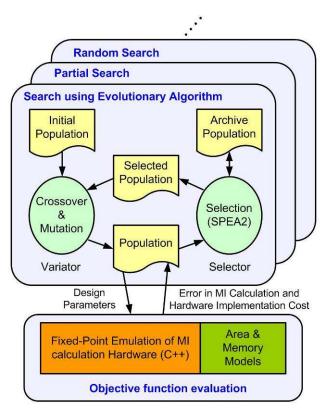

| Figure 5.2:  | Framework for multiobjective optimization of FPGA-based image           |

|              | registration                                                            |

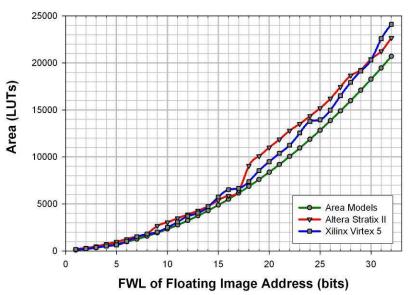

| Figure 5.3:  | Comparison of the area values predicted by the adopted area models      |

|              | with those obtained after physical synthesis                            |

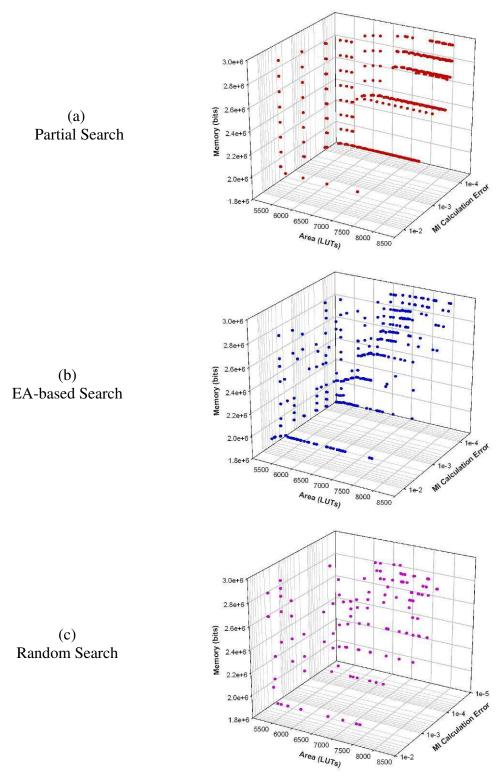

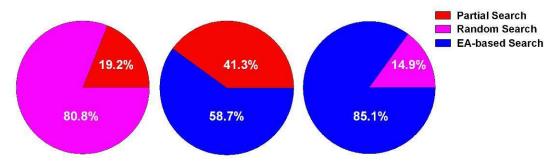

| Figure 5.4:  | Pareto-optimized solutions identified by various search methods 144     |

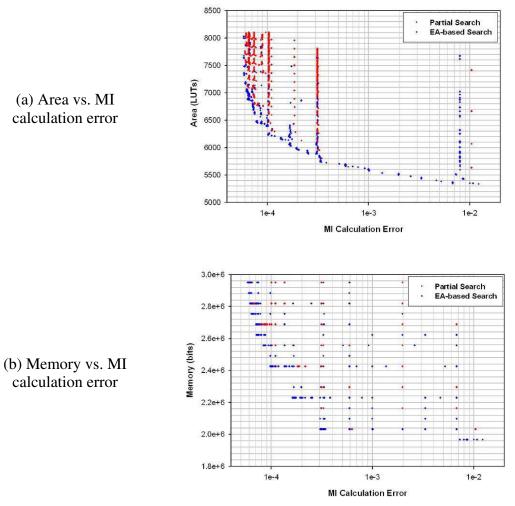

| Figure 5.5:  | Qualitative comparison of solutions found by partial search and EA-     |

|              | based search. 145                                                       |

| Figure 5.6:  | Quantitative comparison of search methods using the ratio of non-       |

|              | dominated individuals (RNI)                                             |

| Figure 5.7:  | Quantitative comparison of search methods using cover rate 148          |

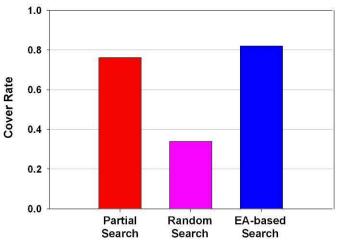

| Figure 5.8:  | Relationship between MI calculation error and resulting image           |

|              | registration error                                                      |

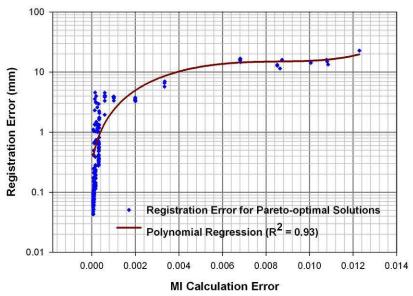

| Figure 5.9: | Results of image registration performed using the high-speed, FPGA-      |

|-------------|--------------------------------------------------------------------------|

|             | based implementation for design configurations offering various          |

|             | registration errors. 153                                                 |

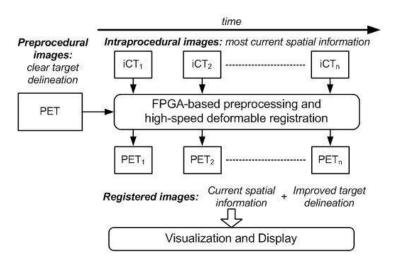

| Figure 6.1: | Integration of deformable registration into IGI workflow                 |

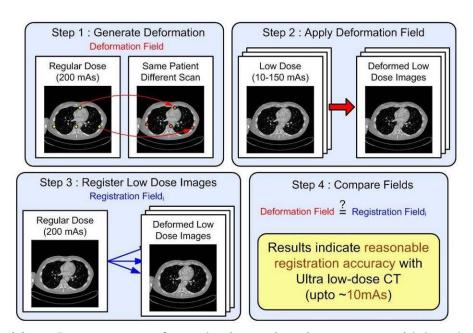

| Figure 6.2: | Important steps for evaluating registration accuracy with low-dose CT.   |

|             |                                                                          |

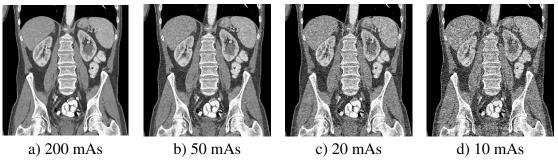

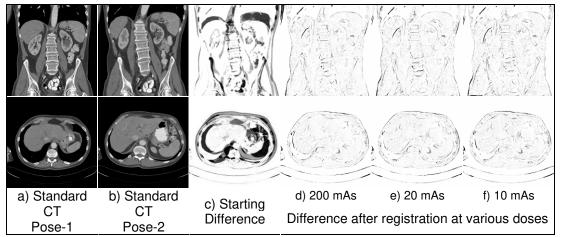

| Figure 6.3: | Low-dose CT images generated by the dose-simulator 160                   |

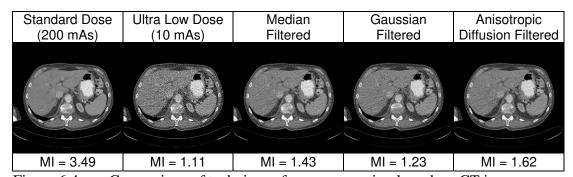

| Figure 6.4: | Comparison of techniques for preprocessing low-dose CT images 162        |

| Figure 6.5: | Qualitative comparison of registration accuracy with low-dose CT. 165    |

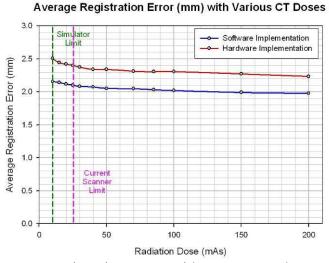

| Figure 6.6: | Average registration error with respect to dose using software and       |

|             | FPGA-based implementations. 166                                          |

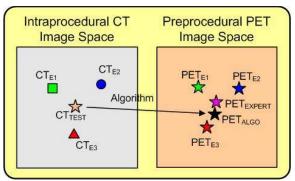

| Figure 6.7: | Graphic illustration of the quantitative validation approach used in the |

|             | context of deformable registration between intraprocedural and           |

|             | preprocedural PET                                                        |

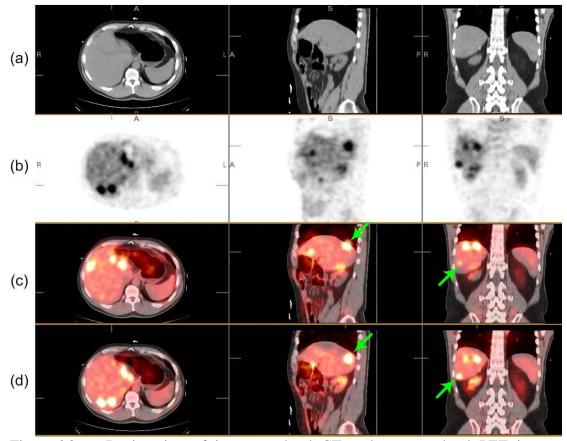

| Figure 6.8: | Registration of intraprocedural CT and preprocedural PET images          |

|             | using the FPGA-based implementation of deformable image                  |

|             | registration                                                             |

## **Chapter 1: Introduction**

#### 1.1. Overview

Image-guided interventions (IGIs), including surgeries, biopsies, and therapies, have the potential to improve patient care by enabling new and faster procedures, minimizing unintended damage to healthy tissue, improving the effectiveness of the procedures, producing fewer complications, and allowing for clinical intervention at a distance. As a result, IGIs has been identified by clinical experts to have a significant impact on the future of clinical care [1]. With further invention and development of imaging and image processing techniques, innovative minimally invasive image-guided inventions will replace conventional open and invasive techniques. Continuous three dimensional (3D) imaging and visualization for intraprocedural navigation, critically important to the success of IGI, has been technologically difficult until recently. However, the advances in medical imaging technology and visualization capabilities, leading to improved imaging speed and coverage, have prompted developments in imaging protocols and enabled volumetric image-guided procedures.

The efficiency and efficacy of IGIs is critically dependant on accurate and precise target identification and localization. Lack of clear target delineation could lead to lengthy procedures, larger than necessary safety margins and unintended damage to healthy tissue—factors that undermine the very motivation behind IGIs. Intraprocedural imaging techniques provide a rich source of accurate spatial information that is crucial for navigation but often suffer from poor signal-to-noise

ratio (SNR) and poor target definition from background healthy and/or benign tissue. As in most clinical protocols, IGIs are preceded by one or more preprocedural images, containing additional information, such as contrast-enhanced structures or functional details such as metabolic activity, which are used for diagnosis, treatment/navigation planning, etc. Combining this functional and/or contrast information with intraprocedural morphological and spatial information, through coregistration between pre- and intraprocedural images, has been shown to improve the intraprocedural target delineation [2-6].

Achieving this registration between intraprocedural and preprocedural images is a fundamental need during the IGI workflow. Moreover, given the on-demand nature of IGIs, this alignment should be achieved sufficiently fast so as not to affect the clinical workflow. Earlier approaches to meet this need primarily employed rigid body approximation, which can be less accurate because of non-rigid tissue misalignment between these images. Intensity-based deformable registration is a promising option to correct for this misalignment. These algorithms are automatic, which is an important aspect that enables their easy integration into many applications; However, the long execution times of these algorithms have prevented their use in clinical workflow. In addition, since this technique is based on intensitybased alignment between images, it is sensitive to the SNR of the images to be registered. Consequently, the images (in particular, intraprocedural images that are characterized with poor SNR) need to be preprocessed and de-noised before they can be registered. This workflow for providing improved visualization during IGIs is illustrated in Figure 1.1.

**Figure 1.1:** A typical IGI workflow and the scope of this dissertation work

The overall goal of this dissertation work is to improve the identification and localization of targets during image-guided interventions through automatic, fast, and accurate deformable image registration between preprocedural and intraprocedural images. With this accurate registration and fusion of complementary information an interventionist will be able to visualize accurately aligned anatomical structures (such as vasculature) and/or functional (metabolic) activity not natively present in the routine intraprocedural scans and thereby improving the targeting capability.

#### 1.2. Contributions of this Dissertation

The specific goal of this dissertation work is to develop and validate the core components of this advanced image processing system, which will enable improved visualization and target-delineation during image-guided procedures. These core components are identified in Figure 1.1. First, we employ reconfigurable hardware platform to develop an architecture for real-time implementation of image