## High-Performance Carbon Nanotube Field Effect Transistors with a Thin Gate Dielectric Based on a Self-Assembled Monolayer

Ralf Thomas Weitz,\*,† Ute Zschieschang,† Franz Effenberger,‡ Hagen Klauk,† Marko Burghard,† and Klaus Kern†

Max Planck Institute for Solid State Research, Heisenbergstrasse 1, 70569 Stuttgart, Germany, and Department of Chemistry, University of Stuttgart, Pfaffenwaldring 55, 70569 Stuttgart, Germany

Received July 4, 2006; Revised Manuscript Received December 7, 2006

## ABSTRACT

Individual single-walled carbon nanotube (SWCNT) field effect transistors (FETs) with a 2 nm thick silane-based organic self-assembled monolayer (SAM) gate dielectric have been manufactured. The FETs exhibit a unique combination of excellent device performance parameters. In particular, they operate with a gate-source voltage of only -1 V and exhibit good saturation, large transconductance, and small hysteresis ( $\leq 100$  mV), as well as a very low subthreshold swing (60 mV/dec) under ambient conditions. The SAM-based gate dielectric opens the possibility of fabricating transistors operating at low voltages and constitutes a major step toward nanotube-based flexible electronics.

During the past few years, single-walled carbon nanotubes (SWCNTs) have emerged as highly promising components of nanoscale electrical devices. Among these, SWCNT-based field effect transistors (FETs) have attracted especially strong interest due to their excellent device characteristics. Three crucial factors that govern the performance of SWCNT-FETs are the chemical nature, the structural quality, and the thickness of the gate dielectric. In the most widely used configuration, a highly doped silicon substrate covered with thermally grown SiO<sub>2</sub> (typical thickness 100-200 nm; growth temperature >700 °C) serves as a macroscopic backgate.<sup>1</sup> In order to achieve increased capacitive coupling, alternative gate dielectrics of ultrathin thickness (e.g.,  $Al_2O_3$ )<sup>2</sup> or high dielectric permittivity (e.g., ZrO<sub>2</sub>)<sup>3,4</sup> have been investigated, in some cases employing a top-gate geometry. While the corresponding FETs exhibit very high transconductance and carrier mobility, they often suffer from pronounced hysteresis in the transfer characteristic.<sup>5</sup> Backgated FETs based on random SWCNT networks have recently been reported using a thin (16 nm) organic selfassembled multilayer gate dielectric.<sup>6,7</sup> Devices reported in that work show a greatly reduced hysteresis, but-since they are based on SWCNT networks-show inferior on/off drain current ratio and mobility. In addition, such devices display relatively large gate leakage currents.

<sup>‡</sup> University of Stuttgart.

Here we investigate individual semiconducting SWCNT-FETs that employ a simpler gate dielectric comprised of a 2 nm thick organic self-assembled monolayer (SAM) prepared in a single process step on a 4 nm thick SiO<sub>2</sub> layer on a silicon substrate used as a back-gate. The SiO<sub>2</sub> layer results from a brief oxygen plasma step required to create a sufficient density of hydroxyl groups for organic selfassembly. The SAM is based on (18-phenoxyoctadecyl)trichlorosilane, which has been shown to be a suitable gate dielectric for the fabrication of low-voltage, high-mobility pentacene organic thin-film transistors.8 Owing to their low formation temperature of less than 200 °C, SAM gate dielectrics are compatible with unconventional substrates such as metalized plastic foils, thereby enabling electronics on flexible substrates.9 One important question is whether the SAM is stable under the conditions of electron-beam (ebeam) lithography, which is required for fabricating transistors with a channel length of 200 nm. To date there has only been a single report of FETs obtained through e-beam lithography on top of a SAM-based dielectric. In this pioneering work on molecular gate dielectrics, oligothiophene-based organic thin-film transistors with carboxyl group-terminated silane-based SAM dielectrics were fabricated on silicon substrates.<sup>10</sup> However, no systematic study of the effect of different electron doses on the structural integrity of the SAM has been performed.

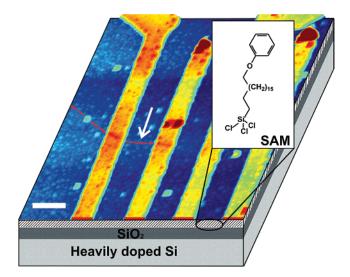

The structure of our SWCNT-FET devices is apparent from Figure 1. The SAM self-assembles subsequent to a brief

<sup>&</sup>lt;sup>†</sup> Max Planck Institute for Solid State Research.

**Figure 1.** AFM image of the SWCNT-FET device structure. The 4 nm thin  $SiO_2$  layer on top of the highly doped silicon wafer (light gray) is shown in dark gray. Four AuPd electrode lines are deposited onto the SAM (hatched layer) that has formed on the  $SiO_2$  surface. A 0.3 nm layer of titanium is evaporated on top of the monolayer to enable spin coating of PMMA. The individual SWCNT in the AFM image has been colored to enhance its visibility. The scale bar is 200 nm. Inset: Chemical structure of the silane molecule used for SAM formation.

oxygen plasma treatment (0.1 mbar, 100 W, 10 s, substrate at room temperature) of a p<sup>+</sup>-doped silicon wafer serving as the substrate and gate electrode from the vapor phase (lowpressure nitrogen atmosphere) at a temperature of 200 °C. Ellipsometry revealed that the plasma activation resulted in a  $\sim$ 4 nm thick SiO<sub>2</sub> coating of the silicon substrate. We note that plasma activation is required for high-quality molecular self-assembly in order to generate a sufficient density of functional groups at the surface. During the plasma treatment the substrate remains at room temperature which in principle opens up the possibility of implementing the devices on flexible substrates (in which case a natively oxidizing metal would be used instead of silicon). Compared with silicon dioxide formed by thermal oxidation above 700 °C (ref 11), our room-temperature plasma-grown SiO<sub>2</sub> is of lower quality, but as far as gate leakage and interface state density are concerned, this deficiency is compensated by the SAM which is also created at low temperature (200 °C). Although the SAM adds only  $\sim$ 2 nm to the total dielectric thickness (as determined by ellipsometry), it reduces the leakage current by more than 3 orders of magnitude, from  $10^{-4}$  to  $10^{-7}$  A/cm<sup>2</sup> (measured at a gate field of 2 MV/cm). For a thin (6 nm), low-temperature (200 °C), large-area dielectric this is an exceptionally small current density. The SAM-covered substrate is smooth over large areas as shown by atomic force microscopy (Figure S1, Supporting Information). Scanning tunneling microscopy studies have shown that the SAM is essentially free of pinholes.8

The capacitance of the dielectric stack, in which the SAM accounts for the majority of the insulating properties, has been determined by impedance spectroscopy to be 0.5  $\mu$ F/cm<sup>2</sup>. The relative permittivity of the dielectric is estimated to be about 3.3 and is determined mostly by the permittivities

of the SAM and the SiO<sub>2</sub>. Due to the strongly hydrophobic character of the SAM-modified surface, a 0.3 nm thick layer of titanium had to be evaporated onto the samples to allow spin-coating of the electron-beam resist (PMMA). The titanium does not form a closed layer as confirmed by atomic force microscopy (AFM) measurements. Due to the small thickness and fast oxidation of the titanium layer upon air exposure, it does not contribute to the electrical conduction between source and drain, as has been confirmed by electrical measurement. The contribution of the capacitance of the oxidized titanium to the total capacitance of the dielectric stack can be ignored, since titanium oxide has a very large permittivity (>50) in comparison to the SiO<sub>2</sub>/SAM stack (adding the titanium oxide reduces the total capacitance by about 1%).

Carbon nanotubes (CNI, Houston, TX) were dispersed in an aqueous surfactant solution (1 wt % sodium dodecyl sulfate) and then purified by centrifugation and deposited on the substrate after the deposition of the 0.3 nm Ti. Source and drain contacts were then fabricated on top of the SWCNTs by e-beam lithography using a standard doublelayer poly(methyl methacrylate) (PMMA) resist with a thickness of 200 nm, an electron energy of 25 keV, and an electron beam dose of 300  $\mu$ C/cm<sup>2</sup>. Electrodes with a separation of 200 nm were formed through thermal evaporation of 0.3 nm Ti/15 nm AuPd (60/40) and subsequent liftoff in acetone. Thin metal wires were carefully glue-bonded to the contact pads to establish reliable electrical connections between the device terminals and the chip carrier. The electrical measurements were carried out at room temperature in air.

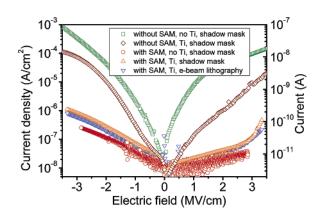

In order to determine the extent to which the e-beam exposure during lithography causes structural damage of the SAM as well as to evaluate the contribution of the SAM to the insulating properties of the SiO<sub>2</sub>/SAM-dielectric, five different types of test structures were investigated. These samples consist of a heavily doped silicon substrate covered by a thin dielectric (bare or SAM-modified 4 nm plasmagrown SiO<sub>2</sub>, with or without 0.3 nm oxidized Ti) and a top metal contact (patterned either through an evaporation mask or by e-beam lithography). In Figure 2, the results of current-voltage (I-V) measurements performed on the respective samples under ambient conditions are shown. The SiO<sub>2</sub> dielectric without SAM has very poor insulating properties, as apparent from the substantial current density of about 10<sup>-4</sup> A/cm<sup>2</sup> at an electric field of 2 MV/cm applied between the silicon gate and the metal contact. The leakage current does not decrease significantly upon evaporating 0.3 nm of Ti onto the 4 nm thick plasma-grown SiO<sub>2</sub> and allowing the Ti to oxidize prior to depositing the contact pads. The large leakage currents in the devices without SAM originate from the poor quality of plasma-grown SiO2 as compared to high-quality SiO<sub>2</sub> grown by thermal oxidation.<sup>11</sup>

In comparison, the test structures including a SAM exhibit a significantly reduced leakage current density of less than  $10^{-7}$  A/cm<sup>2</sup> at the same electric field. This confirms the crucial role of the SAM in determining the insulating properties of the dielectric stack, despite its small thickness.

**Figure 2.** Current density through the gate dielectric vs bias field measured at room temperature on sandwich structures with and without the organic SAM. In the devices incorporating the SAM, the top gold contacts were patterned either by e-beam lithography or by evaporation through a shadow mask. The absolute current is displayed on the right axis.

A similar conclusion has previously been drawn for organic SAM-containing sandwich devices.<sup>8,12,13</sup> Comparing the SAM devices with and without a 0.3 nm thick Ti layer evaporated on top of the SAM shows an increase in leakage current by a factor of about 2 as a result of the titanium deposition. If the SAM was significantly damaged or destroyed by the Ti, as has been reported in the literature,<sup>14</sup> we would expect a more significant increase in leakage current. In our case however we believe that the 0.3 nm Ti oxidizes sufficiently fast (due to its very small thickness and the residual gas in our evaporator) to not inflict substantial damage on the SAM.

More intriguingly, the leakage current through the SAM dielectric is found to be virtually the same ( $\sim 10^{-7}$  A/cm<sup>2</sup> at 2 MV/cm) regardless of whether the top metal contact is patterned by a shadow-mask technique or by electron-beam lithography, which demonstrates that the electron dose of  $300 \ \mu\text{C/cm}^2$  does not significantly damage the SAM. Due to its small thickness the electron absorption in the oxidized Ti can be ignored, especially since our AFM measurements suggest that the oxidized Ti does not form a closed layer. At first glance, the good stability of the SAM under e-beam exposure appears to be in contrast to literature reports of considerable damage involving bond rapture and partial desorption of molecular fragments after e-beam irradiation of thiol-based SAMs on Au substrates.<sup>15</sup> However, it has to be taken into account that the electron energy of 25 keV in the present study is much higher than the 10-100 eV used in case of the thiol-based monolayers. It is well-documented that higher-energy electron irradiation causes less damage in thin organic films than lower-energy irradiation.<sup>16</sup> This difference can be attributed to the lower stopping power of higher-energy electrons, whereby only little energy is deposited in thin films. First signs of electron-induced damage of our PMMA resist-covered SAMs, manifested by increased leakage currents ( $\geq 10^{-6}$  A/cm<sup>2</sup>), were detected for doses larger than 1800  $\mu$ C/cm<sup>2</sup>.

Building upon the excellent process stability and insulating properties of the SAM-based dielectric, we were able to obtain excellent FETs from individual semiconducting

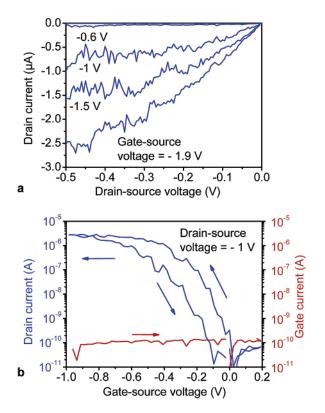

**Figure 3.** (a) Output characteristics of a FET device with a SAMbased gate dielectric comprising an individual semiconducting SWCNT as channel. (b) Transfer characteristics of the same device. The gate voltage sweep rate was 150 mV/s. All measurements were performed under ambient conditions. The measured gate leakage current resolution is limited by the measurement setup in this experiment. Data for the leakage current density should be taken from Figure 1 which shows measurements of the gate leakage current with a higher accuracy.

SWCNTs. The output characteristics of an exemplary device (tube diameter 1.2 nm) shown in Figure 3a display p-type behavior, a common feature of SWCNT-FETs that were not subjected to further treatment.<sup>2,17</sup> The drain current vs drainsource voltage characteristic resembles that of conventional p-type metal-oxide-semiconductor FETs (MOSFETs). One of these features is the saturation of the drain current at higher  $V_{\rm ds}$ . For the present device, saturation occurs for example at a drain-source voltage of approximately -0.3 V and a gatesource voltage of -1.5 V (also see Figure 4a for a different device showing good saturation). From the transfer characteristics, shown in Figure 3b, one finds a transconductance<sup>18</sup>  $g_{\rm m} = dI_{\rm d}/dV_{\rm gs}$  of about 20  $\mu$ S at  $V_{\rm ds} = -1$  V. This value is similar to the highest reported so far for SWCNT-FETs<sup>19</sup> and testifies to the superior gate coupling and to a large carrier field-effect mobility. The device exhibits a threshold voltage between -0.05 and -0.5 V, depending on whether the threshold voltage is estimated from the plot of the square root of the drain current versus gate-source voltage or from the plot of the drain current versus drain-source voltage. Moreover, the large on/off drain current ratio of about 10<sup>5</sup> (at  $V_{\rm ds} = -1$  V) is particularly remarkable in view of the small thickness of the gate dielectric and theoretical predictions on drain voltage scaling in SWCNT-FETs.4,20-22 Finally, evaluation of the subthreshold swing  $S = [dV_{gs}/d(\log$

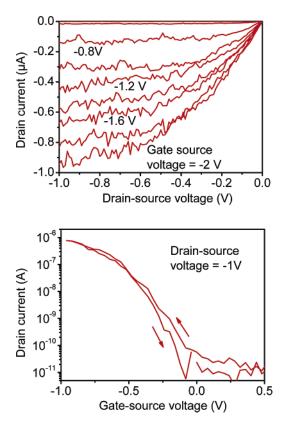

**Figure 4.** Output (a) and transfer (b) curve of a device at a drainsource voltage of -1 V. Negligible hysteresis is measured under ambient conditions. The gate voltage sweep rate was 210 mV/s.

$I_{ds}$ )] within the model for MOSFETs<sup>18</sup> yields the value of 60 mV/decade in the subthreshold region (between about  $10^{-10}$  and  $10^{-8}$  A), close to the theoretical limit of the subthreshold swing at room temperature.<sup>18</sup> Such a low value has not been previously reported for undoped Schottkybarrier SWCNT FETs with low operating voltages, 3,23-26 and its realization within the present devices is notable considering that no attempts were made to reduce the contact resistance<sup>27</sup> and we work with a global back-gate structure. Previous publications have reported subthreshold swings of 60-70 mV/decade for SWCNT FETs in which the channel conductance was controlled with a local gate field while the contact regions were either chemically doped<sup>23</sup> or electrostatically "doped" by applying a large static field from a global back-gate.<sup>3,26</sup> It is known, that in such devices the subthreshold swing is not limited by the gate dielectric.<sup>26,28</sup> In our devices the low-voltage back-gate controls the entire nanotube and the low subthreshold swing is an indication for the high quality of the gate dielectric used in this work. From the subthreshold swing the interface state density N=  $(\log(e) q S/k_{\rm B}T - 1)*C/q$  of the SAM/SWCNT interface can be calculated where q is the electron charge,  $k_{\rm B}$ Boltzmann's constant, T the temperature, and C the gate capacitance per area.<sup>29</sup> The obtained value of  $N = 6 \times 10^{10}$  $cm^{-2} V^{-1}$  is more than 1 order of magnitude lower compared to other SWCNT transistors<sup>4,17,19,21</sup> and underlines the high structural quality of the SAM (see Figure S2 within Supporting Information). It should be stressed, that in order to achieve a minimal subthreshold swing, both the capacitance of the gate dielectric and the interface state density have to be optimized. While in most works using high-permittivity dielectrics a large capacitive coupling is realized, the interface trap density is often high in comparison to dielectrics with lower permittivity like the one used in this work (see Figure S2 within Supporting Information). It is furthermore relevant that the device exhibits a very low gate leakage current (~100 pA at  $V_{gs} = -1$  V) that is smaller than the drain current by more than 4 orders of magnitude. This leakage current is an upper limit of the actual leakage since the minimum resolution of our measurement device in this measurement is about 100 pA. Figure 2 gives a better idea of the real leakage current through the gate dielectric.

While the electrical characteristics presented above belong to one of the best devices, we note that only a relatively small variation in performance was observed from sample to sample. In particular, all of the devices displayed saturation of the drain current in the output characteristic. The lowest transconductance and on/off ratio found among the investigated devices were 0.5  $\mu$ S and 10<sup>4</sup>, respectively, while subthreshold swings as large as 300 mV per decade were measured.

The transfer characteristics of the investigated devices (Figure 3b) disclose a hysteresis. This phenomenon is common to SWCNT-FETs. It has been ascribed to traps located within the bulk SiO<sub>2</sub> gate insulator or near the nanotube/SiO2 interface, which get filled with electrons from the nanotube channel upon sweeping to more positive gate voltages.<sup>22,30</sup> Similar to other SWCNT-FETs, the present devices show forward-type hysteresis.<sup>5</sup> Its magnitude (defined as the separation between the forward and backward curves at 50% of the maximum source-drain current) depends on temperature as well as the  $V_{gs}$  sweep rate and range, whereas it is only weakly affected by  $V_{ds}$ . We find a room-temperature hysteresis of 900 mV when sweeping the gate voltage between 1.5 and -1.5 V at a rate of 7.5 mV/s. Its value decreases down to 100 mV upon increasing the sweep rate to 350 mV/s. Such a decrease in hysteresis with rising sweep rate of the gate voltage indicates the presence of trap charging on a time scale on the order of several hundreds of milliseconds. Moreover, the hysteresis experiences a significant reduction when the devices are cooled, similar to the behavior of SWCNT-FETs with a pure SiO<sub>2</sub> gate insulator.30,31

Hysteresis in SWCNT-FETs has previously been considered mostly from the viewpoint of potential memory applications.<sup>30–32</sup> This task still requires a better control over the hysteretic effect, although the first promising steps have already been taken in this direction, for instance via removal of the water layer from the SiO<sub>2</sub> gate insulator surface.<sup>5</sup> A prerequisite for efficient operation as a FET, by contrast, is the absence of hysteresis. In this regard, it is pertinent to note that some of our devices exhibit essentially no hysteresis even when measured under ambient conditions, i.e., with the CNT channel exposed to air (Figure 4). This result is outstanding since a vanishing hysteresis has only been achieved so far with the nanotube protected from air either by inorganic ALD dielectrics<sup>21</sup> or when working with a liquid

gate.<sup>25</sup> We attribute the small or absent hysteresis in our SWCNT-FETs to two major factors. A first contribution may arise from the low operation voltage enabled by the strong gate coupling, as has been put forward previously.<sup>6</sup> Second, the SAM-modified dielectric surface should adsorb only small amounts of water, despite the thin oxidized titanium layer covering the SAM.<sup>8</sup> This is further supported by the finding that the hysteresis of our devices is not significantly reduced upon transfer of the device into vacuum. Since water is known to enhance hysteretic behavior,<sup>5</sup> the predominantly hydrophobic character of the surface should help to reduce the hysteresis. To prove that really the monolayer is responsible for the reduction of a hysteresis, we fabricated devices with a 100 nm thick thermal SiO<sub>2</sub> gate dielectric covered by the SAM and 0.3 nm of Ti. We found the hysteresis to be between 0 and about 20% of the maximum gate voltage window. In Figure S3 (Supporting Information) such a transfer curve is compared with a device that does not have a SAM covering the thermal SiO<sub>2</sub>. In the device with the SAM the hysteresis is significantly reduced. To evaluate the extent to which the SAM reduces the hysteresis, we compare our data taken from the work by Kim et al.5 Since the hysteresis is known to depend on gate voltage sweep rate and the maximum applied gate field, not the absolute value of the hysteresis can be compared but it has to be set in relation to the maximum gate field and the sweep rate. When in the FET comprising the SAM-covered SiO<sub>2</sub> the gate field is swept at a speed of  $3.8 \times 10^4$  V/(cm·s) across a gate field of  $\pm 1 \times 10^6$  V/cm ( $\pm 10$  V) a hysteresis of 12% of the maximum gate field window (i.e., the difference between the maximum and minimum gate field) can be observed. In Kim et al. 's work a thermally grown SiO<sub>2</sub> is used without any surface functionalization.<sup>5</sup> The gate field is for example swept at a speed of  $1.1 \times 10^5$  V/(cm·s) between a maximum field of  $\pm 2 \times 10^5$  V/cm ( $\pm 10$  V). A hysteresis of 38% of the maximum gate field window was observed. In comparison with our results it can be seen that even when a device with SAM is swept across a larger gate electric field at a low sweep speed the hysteresis in the drain current is still lower than in devices that do not include the SAM. It has to be noted that the hysteresis is known to increase when the gate voltage sweep rate is increased and the maximum of the applied gate voltage is increased.

In summary, we have demonstrated that the integration of a high-quality gate dielectric based on an organic selfassembled monolayer into nanotube-based electronic devices permits strong gate coupling. The high stability of the SAM against electron exposure during electron-beam lithography has enabled the fabrication of field-effect transistors with a channel length of 200 nm from individual semiconducting SWCNTs. Back-gated SWCNT-FETs obtained in this manner not only exhibit an unprecedented combination of excellent performance parameters but also approach the room-temperature limit of 60 mV/dec for the subthreshold swing which is a key performance parameter of FETs. It is equally important to stress that the low temperature used for incorporating the organic SAM makes the fabrication process compatible with flexible polymeric substrates. Acknowledgment. The authors thank Frank Schartner and Benjamin Stuhlhofer for expert technical assistance.

**Supporting Information Available:** An AFM image of a SAM-covered silicon substrate; a comparison between literature data of the interface state density of SWCNT FETs with different gate insulator materials and the data obtained in this work; transfer curves of SWCNT FETs with a 100 nm thick thermally grown  $SiO_2$  gate dielectric with and without a silane SAM covering the oxide layer.

## References

- Avouris, P.; Appenzeller, J.; Martel, R.; Wind, S. J. Proc. IEEE 2003, 91 (11), 1772–1784.

- (2) Bachtold, A.; Hadley, P.; Nakanishi, T.; Dekker, C. Science 2001, 294 (5545), 1317–1320.

- (3) Lu, Y.; Bangsaruntip, S.; Wang, X.; Zhang, L.; Nishi, Y.; Dai, H. J. Am. Chem. Soc. 2006, 128 (11), 3518–3519.

- (4) Javey, A.; Kim, H.; Brink, M.; Wang, Q.; Ural, A.; Guo, J.; McIntyre,

P.; McEuen, P.; Lundstrom, M.; Dai, H. J. *Nat. Mater.* 2002, *1* (4), 241–246.

- (5) Kim, W.; Javey, A.; Vermesh, O.; Wang, Q.; Li, Y.; Dai, H. Nano Lett. 2003, 3 (2), 193–198.

- (6) Hur, S. H.; Yoon, M. H.; Gaur, A.; Shim, M.; Facchetti, A.; Marks, T. J.; Rogers, J. A. J. Am. Chem. Soc. 2005, 127 (40), 13808–13809.

- (7) Lo, S. H.; Buchanan, D. A.; Taur, Y.; Wang, W. *IEEE Electron Device Lett.* **1997**, 18 (5), 209–211.

- (8) Halik, M.; Klauk, H.; Zschieschang, U.; Schmid, G.; Dehm, C.; Schutz, M.; Maisch, S.; Effenberger, F.; Brunnbauer, M.; Stellacci, F. *Nature* **2004**, *431* (7011), 963–966.

- (9) Klauk, H.; Halik, M.; Eder, F.; Schmid, G.; Dehm, C.; Zschieschang, U.; Rohde, D.; Brederlow, R.; Briole, S.; Maisch, S.; Effenberger, F. 2004 International Electron Devices Meet., Tech. Dig. 2004, 369– 372.

- (10) Collet, J.; Tharaud, O.; Chapoton, A.; Vuillaume, D. Appl. Phys. Lett. 2000, 76 (14), 1941–1943.

- (11) Mardou, M. Fundamentals of Microfabrication; CRC Press: New York, 1997.

- (12) Boulas, C.; Davidovits, J. V.; Rondelez, F.; Vuillaume, D. Phys. Rev. Lett. 1996, 76 (25), 4797–4800.

- (13) Rittner, M.; Martin-Gonzalez, M. S.; Flores, A.; Schweizer, H.; Effenberger, F.; Pilkuhn, M. H. J. Appl. Phys. **2005**, 98 (5), 054312.

- (14) de Boer, B.; Frank, M. M.; Chabal, Y. J.; Jiang, W. R.; Garfunkel, E.; Bao, Z. Langmuir 2004, 20 (5), 1539–1542.

- (15) Zharnikov, M.; Grunze, M. J. Vac. Sci. Technol., B: Microelectron. Nanometer Struct. 2002, 20 (5), 1793–1807.

- (16) Tan, Z. Y.; Xia, Y. Y.; Liu, X. D.; Zhao, M. W. *Microelectron. Eng.* 2005, 77 (3–4), 285–291.

- (17) Appenzeller, J.; Knoch, J.; Derycke, V.; Martel, R.; Wind, S.; Avouris, P. Phys. Rev. Lett. 2002, 89 (12), 126801.

- (18) Sze, S. M. Semiconductor Devices—Physics and Technology; Wiley: New York, 2002.

- (19) Javey, A.; Guo, J.; Farmer, D. B.; Wang, Q.; Yenilmez, E.; Gordon, R. G.; Lundstrom, M.; Dai, H. *Nano Lett.* **2004**, *4* (7), 1319–1322.

- (20) Javey, A.; Guo, J.; Wang, Q.; Lundstrom, M.; Dai, H. J. Nature 2003, 424 (6949), 654–657.

- (21) Yang, M. H.; Teo, K. B. K.; Gangloff, L.; Milne, W. I.; Hasko, D. G.; Robert, Y.; Legagneux, P. Appl. Phys. Lett. 2006, 88 (11).

- (22) Radosavljevic, M.; Heinze, S.; Tersoff, J.; Avouris, P. Appl. Phys. Lett. 2003, 83 (12), 2435–2437.

- (23) Javey, A.; Tu, R.; Farmer, D. B.; Guo, J.; Gordon, R. G.; Dai, H. Nano Lett. 2005, 5 (2), 345–348.

- (24) Lu, C.; Fu, Q.; Huang, S.; Liu, J. *Nano Lett.* 2004, *4* (4), 623–627.

(25) Siddons, G. P.; Merchin, D.; Back, J. H.; Jeong, J. K.; Shim, M.

- Nano Lett. 2004, 4 (5), 927–931.

- (26) Lin, Y. M.; Appenzeller, J.; Knoch, J.; Avouris, P. IEEE Trans. Nanotechnol. 2005, 4 (5), 481–489.

- (27) Chen, J.; Klinke, C.; Afzali, A.; Avouris, P. Appl. Phys. Lett. 2005, 86 (12), 123108.

- (28) Wind, S. J.; Appenzeller, J.; Avouris, P. Phys. Rev. Lett. 2003, 91 (5).

- (29) Rolland, A.; Richard, J.; Kleiderer, J. P.; Mencaraglia, D. J. *Electrochem. Soc.* **1993**, *140* (12), 3679–3683.

(30) Fuhrer, M. S.; Kim, B. M.; Durkop, T.; Brintlinger, T. *Nano Lett.*

- 2002, 2 (7), 755-759.

- (31) Cui, J. B.; Sordan, R.; Burghard, M.; Kern, K. Appl. Phys. Lett. 2002, 81 (17), 3260-3262.

- (32) Radosavljevic, M.; Freitag, M.; Thadani, K. V.; Johnson, A. T. Nano Lett. 2002, 2 (7), 761-764.

NL061534M