# High-performance electronics using dense, perfectly aligned arrays of single-walled carbon nanotubes

# SEONG JUN KANG<sup>1</sup>\*, COSKUN KOCABAS<sup>2</sup>\*, TANER OZEL<sup>2</sup>, MOONSUB SHIM<sup>1,7</sup>, NINAD PIMPARKAR<sup>8</sup>, MUHAMMAD A. ALAM<sup>8</sup>, SLAVA V. ROTKIN<sup>9</sup> AND JOHN A. ROGERS<sup>1,3-7†</sup>

<sup>1</sup>Department of Materials Science and Engineering, <sup>2</sup>Department of Physics, <sup>3</sup>Department of Mechanical Science and Engineering, <sup>4</sup>Department of Electrical and Computer Engineering, <sup>5</sup>Department of Chemistry, <sup>6</sup>Beckman Institute for Advanced Science and Technology, <sup>7</sup>Frederick Seitz Materials Research Laboratory, University of Illinois at Urbana Champaign, Urbana, Illinois 61801, USA

\*School of Electrical and Computer Engineering, Purdue University, West Lafayette, Indiana 47907-1285, USA

<sup>9</sup>Department of Physics and Center for Advanced Materials and Nanotechnology, Lehigh University, Bethlehem, Pennsylvania 18015, USA \*These authors contributed equally to this work.

<sup>+</sup>e-mail: jrogers@uiuc.edu

Published online: 25 March 2007; doi:10.1038/nnano.2007.77

Single-walled carbon nanotubes (SWNTs) have many exceptional electronic properties. Realizing the full potential of SWNTs in realistic electronic systems requires a scalable approach to device and circuit integration. We report the use of dense, perfectly aligned arrays of long, perfectly linear SWNTs as an effective thin-film semiconductor suitable for integration into transistors and other classes of electronic devices. The large number of SWNTs enable excellent device-level performance characteristics and good device-to-device uniformity, even with SWNTs that are electronically heterogeneous. Measurements on p- and n-channel transistors that involve as many as  $\sim 2,100$  SWNTs reveal device-level mobilities and scaled transconductances approaching  $\sim 1,000$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and  $\sim 3,000$  S m<sup>-1</sup>, respectively, and with current outputs of up to  $\sim 1$  A in devices that use interdigitated electrodes. PMOS and CMOS logic gates and mechanically flexible transistors on plastic provide examples of devices that can be formed with this approach. Collectively, these results may represent a route to large-scale integrated nanotube electronics.

Fundamental studies of charge transport through individual SWNTs reveal remarkable room-temperature properties, including mobilities more than ten times larger than silicon, current-carrying capacities as high as 109 A cm<sup>-2</sup> and ideal subthreshold characteristics in single-tube transistors<sup>1-4</sup>. The implications of these behaviours could be significant for many applications in electronics, optoelectronics, sensing and other areas<sup>5-9</sup>. Devices that use single SWNTs as functional elements might not, however, form a realistic basis for these technologies, due in part to their low current outputs and small active areas. More importantly, integration of single tube devices into scalable integrated circuits requires a solution to the very difficult problem of synthesizing and accurately positioning large numbers of individual, electrically homogeneous tubes with linear geometries. The use of densely packed, perfectly aligned horizontal arrays of non-overlapping linear SWNTs as an effective thin-film electronic material has the potential to avoid these problems while retaining the attractive properties of the individual tubes. The multiple, parallel transport pathways in these arrays provide large current outputs and active areas, together with statistical averaging effects that lead to small device-to-device variations in properties, even with tubes that individually have widely different transport characteristics. Although theoretical work has examined some of the

anticipated electrical properties of such arrays<sup>10,11</sup>, experimental results are lacking<sup>12-14</sup>, owing to difficulties associated with generating dense, large-scale, aligned SWNTs at the extremely high degrees of alignment and linearity needed to avoid percolating transport pathways, tube/tube overlap junctions, electrostatic screening effects and non-ideal electrical properties<sup>15–17</sup>. This paper presents high-performance p- and n-channel transistors and unipolar and complementary logic gates that use perfectly aligned arrays of long, pristine, individual SWNTs with perfectly linear geometries. The excellent properties of the devices derive directly from a complete absence, to within experimental uncertainties, of any defects in the arrays, as defined by tubes or segments of tubes that are misaligned or have nonlinear shapes. This level of perfection represents several orders of magnitude improvement over previous results<sup>12,18-20</sup>. Analysis of measurements on these devices using rigorous models of the capacitance coupling of the arrays to the gate electrodes reveals device-level properties that approach those of pristine individual tubes. These features, together with the ability of these devices to provide both p- and n-type operation and CMOS circuit designs, and their compatibility with a range of substrates, suggest that these approaches have some promise for realistic SWNT-based electronic and optoelectronic technologies.

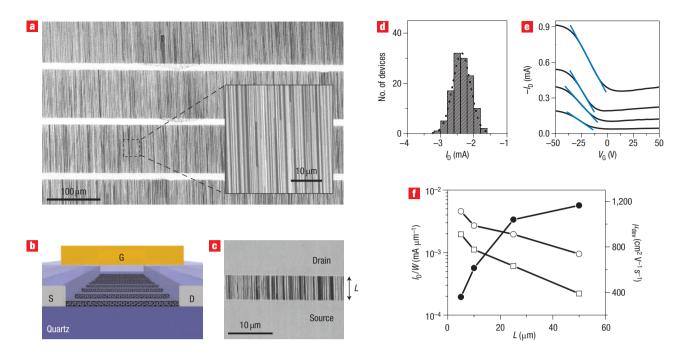

**Figure 1** Perfectly aligned arrays of long, linear SWNTs and their implementation in thin-film-type transistors. a, SEM image of a pattern of perfectly aligned, perfectly linear SWNTs formed by CVD growth on a quartz substrate. The bright horizontal stripes correspond to the regions of iron catalyst. The inset provides a magnified view. These arrays contain  $\sim$ 5 SWNTs  $\mu$ m<sup>-1</sup>. **b**, Schematic illustration of the layout of a type of transistor that incorporates these aligned SWNTs as the semiconductor. The device uses source (S), drain (D) and gate (G) electrodes, and a dielectric layer formed sequentially on top of the SWNTs on quartz. **c**, SEM image of the channel region of such a device. The distance between the source and drain electrodes defines the channel length (*L*). **d**, Output currents (*I*<sub>D</sub>) measured on more than 100 two-terminal test structures using electrodes with widths, *W*, of 200  $\mu$ m and separated by distances (that is, channel lengths, *L*) of 7  $\mu$ m, evaluated with an applied potential, *V*<sub>D</sub>, of 10 V. **e**, Transfer curves (*I*<sub>D</sub> as a function of gate voltage, *V*<sub>G</sub>) measured from transistors with *L* = 5, 10, 25 and 50  $\mu$ m, from top to bottom, and *W* = 200  $\mu$ m at *V*<sub>D</sub> = -0.5 V. The blue lines indicate the linear regions of the transfer curves. These devices used polymer gate dielectrics, with thickness of ~1.5  $\mu$ m. **f**, Width-normalized on and off currents (open circles and squares, respectively, left axis) and linear-regime device mobilities (solid circles,  $\mu_{dev}$ , right axis) as a function of *L*.

#### FABRICATION OF NANOTUBE ARRAYS AND DEVICES

Figure 1 shows scanning electron microscope (SEM) images of representative arrays of SWNTs, SEM images and schematics of their integration into transistors, and some electrical properties. Chemical vapour deposition (CVD) on ST (stable temperature) cut quartz wafers using patterned stripes of iron catalyst and methane feed gas forms arrays of individual SWNTs with average diameters of  $\sim 1$  nm, lengths of up to 300  $\mu$ m, and densities (D) approaching  $\sim 10$  SWNTs  $\mu m^{-1}$ . More than 99.9% of the SWNTs lie along the  $[2\overline{1}\overline{1}0]$  direction of the quartz, to within <0.01°, with perfectly linear configurations, within the measurement resolution of an atomic force microscope12. (Fig. 1a; see also Supplementary Information, Fig. S1). This nearly ideal layout, in particular as obtained at high D, is critically important to the device results presented here, and represents a significant improvement over previously reported results<sup>18-20</sup>. The simplest method to integrate these arrays into transistors begins with photolithography to define source and drain electrodes (Ti, 1 nm/Pd, 20 nm) on the SWNT/quartz substrates in regions between the catalyst stripes. Etching SWNTs outside the channel region, spin casting a uniform epoxy gate dielectric (1.5 µm) and photolithographically defining top gate electrodes (Ti, 1 nm/Au, 20 nm) aligned to the channel regions yields arrays of electrically isolated transistors. Figure 1b,c shows a schematic illustration and image. We formed devices in this manner with channel lengths (L) between 5 and 50  $\mu$ m, all with widths (W) of 200  $\mu$ m. For these geometries, each device incorporates ~1,000 perfectly linear parallel SWNTs in the channel, most of which (for example, >80%, even for  $L = 50 \,\mu\text{m}$ ) span the source/drain electrodes. This large number of active tubes per device provides high current outputs and good statistics for uniform reproducible properties. Figure 1d presents measurements that show a ~10% standard deviation in source/drain currents,  $I_D$ , measured in more than 100 two-terminal test structures (source/drain voltage,  $V_D = 10$ V;  $L = 5 \,\mu\text{m}$ ;  $W = 200 \,\mu\text{m}$ ). We observe high yields both for growing the arrays and for building devices that incorporate them (see Supplementary Information, Figs. S1 and S2).

Figure 1e shows typical transfer characteristics measured from a set of devices. The responses indicate p-channel behaviour, consistent with observations in single-tube devices that use similar materials and designs (see Supplementary Information, Fig. S3). The large current outputs are consistent with the high channel conductance provided by the multiple tubes. These currents vary approximately linearly with the channel length, indicating diffusive transport, with ratios of the on and off currents in a range (between  $\sim$ 2.3 and  $\sim$ 5) consistent with the relative populations of metallic and semiconducting SWNTs (see Supplementary Information, Figs. S1 and S4). Resistances of the semiconducting tubes in their 'on' state (that is, biased to gate voltages,  $V_{\rm G}$ , of  $-50 \,\rm V$ ), are  $36 \pm 10 \,\rm k\Omega \,\mu m^{-1}$  for  $L = 50 \,\mu m$ , where the effects of contacts are least significant. Single-tube device results, computed using reported diameter-dependent resistances<sup>1</sup> and diameter distributions measured from these arrays (see Supplementary Information, Fig. S1), yield a resistance of  $\sim 21 \text{ k}\Omega \text{ }\mu\text{m}^{-1}$ . Similar calculations for the metallic tubes in these

### ARTICLES

devices yield higher and lower resistances in the low- and high-bias regimes, respectively, than the best single-tube device measurements<sup>14,21–23</sup> (see Supplementary Information, Figs. S4–S6).

#### CAPACITANCE COUPLING AND MOBILITY CALCULATIONS

The low on-state resistances of the semiconducting tubes vield excellent device-level transistor properties. Figure 1f presents linear-regime device mobilities as a function of channel length, computed from the transfer curves, the physical widths of the source/drain electrodes ( $W = 200 \,\mu\text{m}$ ), and a parallel plate model for the capacitance, *C*, according to  $\mu_{dev} = (L/WC)(1/V_D)\partial I_D/\partial V_G$ . These mobilities are as high as ~1,100 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for  $L > 25 \mu m$ , decreasing with L, likely owing to effects of contacts<sup>1,24,25</sup> that are not considered explicitly in these calculations. The validity of this simple parallel plate model for the capacitance can be explored through measurements and calculations for devices having different values of D. Figure 2a,b presents SEM images of SWNT arrays with D between  $\sim 0.2$  SWNTs  $\mu m^{-1}$  and  $\sim 5$  SWNTs  $\mu m^{-1}$ , obtained by controlling the growth conditions. The responses of devices built with these arrays and with single tubes are similar to those in Fig. 1 (see Supplementary Information, Figs. S3 and S7). The influence of fringing fields and partial electrostatic screening by the tubes on the capacitance,  $\hat{C}$ , are important in this range of tube spacing and gate dielectric thickness<sup>10,11</sup>. Figure 2c,d presents results of calculations that include these effects, the quantum nature of the tubes and their intrinsic capacitance for D = 5 SWNTs  $\mu m^{-1}$ , where screening is dominant, and for D = 0.2 SWNTs  $\mu m^{-1}$ , where it is small. In the former regime, the calculated C differs, only by  $\sim 10\%$ , from that determined by a simple parallel plate model. In the latter case, the capacitance coupling to each individual tube is nearly the same as that for isolated tubes (see Supplementary Information, Figs. S8 and S9).

Such models enable calculations of the average per tube mobilities, which we denote as  $\langle \mu_t \rangle$ , according to  $\langle \mu_t \rangle = (L/WC_t)$  $D_{\rm s})(1/V_{\rm D})\partial I_{\rm D}/\partial V_{\rm G}$  where  $C_{\rm t}$  is the capacitance per unit length for a semiconducting tube in the array (computed using D), and  $D_{\rm s}$  is the density of semiconducting tubes that span the channel. For  $L = 50 \,\mu\text{m}$  and  $D = 5 \,\text{SWNTs} \,\mu\text{m}^{-1}$ ,  $\langle \mu_t \rangle \approx 2,200 \,\pm$  $130 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , if we assume that approximately two out of three of the SWNTs in the channel are semiconducting and that  $\sim 80\%$ of them span the source and drain electrodes. As with the device mobility, the per tube mobility (as computed in a manner that does not account for the contacts) decreases with channel length (for example,  $\sim 570 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ,  $L = 5 \,\mu\text{m}$ ), which is qualitatively consistent with expectations based on reports on single-tube devices<sup>1,24-26</sup>. Averaging the diameter-dependent mobilities inferred from single-tube devices<sup>1</sup>, weighted by the measured distribution of tube diameters in the arrays (see Supplementary Information, Fig. S1d), yields  $\sim$  3,000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> if we assume that most of the 3-4 nm tubes are small bundles  $(\sim 4,300 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  without this assumption). This value is only somewhat higher than the results determined from measurements on the array devices. An analysis of per tube mobilities in devices with various tube densities at  $L = 10 \,\mu\text{m}$ , where the effects of contacts are significant, yields  $\langle \mu_t \rangle \approx 800 \pm$  $100 \,\mathrm{cm}^2 \,\mathrm{V}^{-1} \,\mathrm{s}^{-1}$ , with a negligible systematic dependence on D. Similar mobility values are observed in single-tube devices (see Supplementary Information, Fig. S3).

#### HIGH-PERFORMANCE NANOTUBE ARRAY DEVICES

Although the devices of Figs. 1 and 2 have high mobilities, their on/off ratios are modest, owing to the presence of metallic tubes,

**Figure 2** Capacitance effects and density scaling studies of transistors that use aligned arrays of SWNTs. a,b, SEM images of an array of aligned SWNTs with ~0.2 SWNTs  $\mu$ m<sup>-1</sup> (a) and ~5 SWNTs  $\mu$ m<sup>-1</sup> (b). c,d, Colour contour plots and electric field lines for the computed electrostatic coupling of a gate electrode (top yellow plate) through a dielectric layer to an array of SWNTs with low density (that is, average spacing between the SWNTs is larger than the gate dielectric) (c), and with high density (average spacing between the SWNTs is smaller than the gate dielectric) (d). The results in c and d show field distributions that are similar to those associated with an isolated tube and a parallel plate, respectively. e, Width-normalized on and off currents (open circles and squares, respectively, left axis) measured in transistors built with arrays of SWNTs with different densities, *D*. The thickness of the gate dielectric was ~1.5  $\mu$ m. The plot also shows the average per tube mobilities (filled circles,  $\langle \mu_y \rangle$ , right axis) computed from transfer curves measured from these devices.

and their transconductances are low, owing to the use of lowcapacitance gate dielectrics. The on/off ratios can be improved by destroying the metallic tubes in a breakdown procedure that involves slowly increasing  $V_{\rm D}$ , while holding  $V_{\rm G}$  at a large positive value (Fig. 3a; see also Supplementary Information, Fig. S10) in a manner similar to previous demonstrations on random-network and multiwalled nanotube devices<sup>15,27</sup>. To implement this procedure, the SWNT arrays were first transferred, with high yields (see Supplementary Information, Figs. S10–S12), onto a substrate of epoxy (150 nm)/SiO<sub>2</sub> (100 nm)/Si, using an adaptation of previously reported techniques<sup>28–30</sup>. The epoxy/SiO<sub>2</sub> bilayer and Si provided the gate dielectric and gate, respectively, in a back-gate geometry that leaves the SWNTs exposed to air to facilitate the breakdown

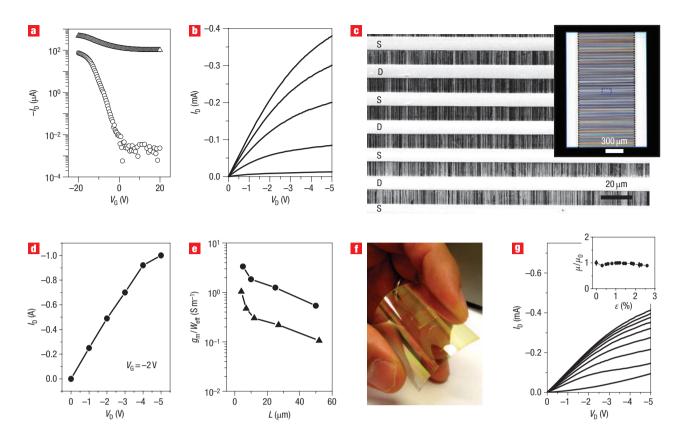

**Figure 3** High on/off ratios, current outputs and transconductances in transistors that use aligned arrays of SWNTs as the semiconductor, on rigid and flexible substrates. a, Transfer curves from a transistor ( $L = 12 \,\mu$ m,  $W = 200 \,\mu$ m) that uses aligned arrays of SWNTs ( $D = 4 \,\text{SWNTs} \,\mu\text{m}^{-1}$ ) transferred from the quartz growth substrate to a doped silicon substrate with a bilayer dielectric of epoxy (150 nm)/SiO<sub>2</sub> (100 nm). The data correspond to measurements on the device before (open triangles) and after (open circles) an electrical breakdown process that eliminates metallic transport pathways from source to drain. This process improves the on/off ratio by a factor of more than 10,000. **b**, Full current/voltage characteristics of the same device, measured after breakdown, illustrating a well-behaved response. The gate voltage varies from  $-5 \,\text{V}$  to  $5 \,\text{V}$  (top to bottom). **c**, Optical (inset) and SEM images of a transistor that uses interdigitated source and drain electrodes, in a bottom gate configuration with a gate dielectric of HfO<sub>2</sub> (10 nm) on a substrate and gate of Si. The width and length of the channel are 93 mm and 10  $\mu$ m, respectively. The box indicated by the dashed blue lines in the optical image inset delineates the region shown in the SEM image. **d**, Output current ( $I_0$ ) as a function of  $V_D$  at  $V_G = -2 \,\text{V}$ , for the device shown in **c**. High on currents (up to  $\sim 1 \,\text{A}$ ) can be obtained. **e**, Transconductance per unit effective width ( $g_m/W_{eff}$ ) as a function of channel length (L), for devices ( $D = 2 \,\text{SWNTs} \,\mu\text{m}^{-1}$ ) that use a polymer electrolyte gate (solid circles,  $V_D = -0.5 \,\text{V}$ ) and a 10-nm HfO<sub>2</sub> (solid triangles,  $V_D = -0.5 \,\text{V}$ ) gate dielectric, respectively. **f**, Optical image of an array of SWNT transistors with  $D = 3 \,\text{SWNTs} \,\mu\text{m}^{-1}$  on a flexible plastic substrate (PET), and  $L = 27 \,\mu\text{m}$  and  $W = 200 \,\mu\text{m}$ . **g**, Current/voltage characteristics of a typical device. The gate voltage varies from  $-20 \,\text{V}$  to  $20 \,\text{V}$

process. Transfer curves in Fig. 3a, collected before and after this process for a typical case of D = 4 SWNTs  $\mu m^{-1}$  ( $L = 12 \,\mu m$ ,  $W = 200 \,\mu m$ ,  $V_D = -0.5$  V), demonstrate that the on/off ratios can be increased by four orders of magnitude, or more, in this manner. Figure 3b shows full current/voltage characteristics recorded after breakdown. The response is consistent with a well-behaved device (that is, saturated and linear current outputs for  $V_D \gg V_G$  and  $V_D \ll V_G$ , respectively), offering large current output even with low operating voltages (selected to avoid hysteresis) and the low-capacitance dielectrics used here. The differences in threshold voltages observed in Fig. 3a,b result from hysteresis that occurs at the high voltages associated with measurements in Fig. 3a.

Increasing the capacitance of the gate dielectric improves the transconductance and eliminates the hysteresis. These aspects, as implemented in devices described in the following, also increase the voltage gain by more than one order of magnitude. In addition, extremely high current outputs can be obtained in this manner, especially in devices that use interdigitated source and drain electrodes to increase W. Figure 3c,d shows images and electrical responses of such a device that uses an array of SWNTs  $(D = 7 \text{ SWNTs } \mu \text{m}^{-1})$  transferred onto a substrate of HfO<sub>2</sub> (10 nm)/Si, where the HfO2 serves as the gate dielectric and the Si provides the gate. In such a device, each SWNT in the array is active at multiple separate segments along its length, similar to related demonstrations in single-tube systems<sup>31</sup>. For this device, the output current reaches  $\sim 1$  A at  $V_{\rm G} = -2$  V and  $V_{\rm D} = -5$  V, as illustrated in Fig. 3d. The transconductance  $(g_m)$ , computed using an effective width  $(W_{\text{eff}})$  defined by the summed widths of the SWNTs that are active in the device, in a manner analogous to similar analyses of single-tube devices<sup>31</sup>, can also be high in such devices. Figure 3e shows results from devices that use slightly lower tube densities  $(D = 2 \text{ SWNTs } \mu \text{m}^{-1})$ , non-interdigitated electrodes and various channel lengths. The peak values of transconductances scaled in this manner are ~800 S m<sup>-1</sup> (at  $V_{\rm D}$  = -0.5 V,  $L = 7 \,\mu$ m) with HfO<sub>2</sub> (10 nm) dielectrics, and up to ~ 3,000 S m<sup>-1</sup> (at  $V_{\rm D}$  = -0.5 V,  $L = 5 \,\mu$ m) with polymer electrolyte gating<sup>32</sup>.

The transfer process used for these devices also enables integration onto unusual substrates, including flexible plastics. As an example, Fig. 3f,g shows an image and electrical characteristics of devices  $(D = 3 \text{ SWNTs } \mu \text{m}^{-1})$  on a sheet of poly(ethylene terephthalate) (180  $\mu$ m), where polyimide (1.6  $\mu$ m) and indium tin oxide (150 nm) provide the gate dielectric and gate, respectively, with  $L = 27 \,\mu\text{m}$  and  $W = 200 \,\mu\text{m}$ . The linear-regime mobility, computed using a parallel plate approximation for the capacitance, is ~ 480 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. The inset of Fig. 3g shows the normalized mobility as a function of bending induced strain ( $\varepsilon$ ) for bending down to radii of curvature of 0.4 cm. At higher values of strain, the devices fail owing to fracture of the gate electrode.

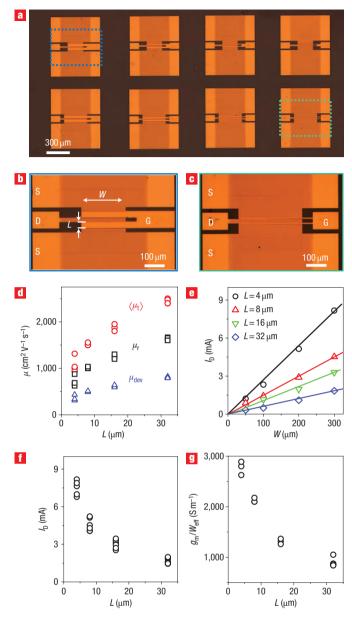

Many of the exceptional electrical properties can be obtained, at once, in suitably designed devices. Figure 4 provides optical micrographs and electrical measurements of such devices, formed on quartz growth substrates in top gate geometries similar to the devices of Figs. 1 and 2, but with high-capacitance dielectrics and with split gate electrodes aligned to the transistor channel to avoid parasitic overlap capacitances for high-speed operation. The dielectric consists of a bilayer of HfO<sub>2</sub> ( $\sim 10$  nm) deposited by atomic layer deposition, on top of a layer of benzocyclobutene (BCB,  $\sim 20$  nm) spin-cast on the SWNTs. Figure 4a-c shows several devices that use arrays with D = 7 SWNTs  $\mu$ m<sup>-1</sup>. The design enables high-speed (radio frequency, RF) operation, and provides electrode pad layouts in the ground-signal-ground configuration to facilitate RF probing. The mobilities can be computed using the parallel plate model for the capacitance or using rigorous calculations similar to those for  $\langle \mu_t \rangle$ , but which also include capacitance contributions from the metallic tubes. Figure 4d shows the results, along with the average per tube mobility, from measurements on 15 devices. The high mobilities and scaling behaviours are quantitatively similar to those of the devices in Fig. 1. The on resistances of the semiconducting tubes are also similar, at  $\sim 40 \,\mathrm{k}\Omega \,\mathrm{\mu m^{-1}}$ . The current outputs are high; they scale linearly with W, and in an expected manner with L. Figure 4e,f presents these results. The high-capacitance gate dielectrics lead to transconductances scaled by W<sub>eff</sub> as high as  $\sim$ 2,900 S m<sup>-1</sup>, as shown in Fig. 4g. Behaviours in the upper end of the range for all of these properties are achieved in devices with  $L = 4 \,\mu\text{m}$  and  $W = 600 \,\mu\text{m}$ , where, for example, the mobility, scaled transconductance and current output are  $400 \pm 50 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  (using the parallel plate capacitance,  $\sim 160 \text{ nF cm}^{-2}$ ),  $\sim 3,000 \text{ Sm}^{-1}$  and 8 mA, respectively. The mobility is  $800 \pm 100 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  when evaluated using the rigorous models for the capacitance (  $\sim 70 \text{ nF cm}^{-2}$ ). These devices also have a strong potential for high-speed operation. Measurements using a network analyser indicate small signal gain up to frequencies  $(f_T)$  approaching 0.5 GHz, evaluated without any de-embedding (see Supplementary Information, Fig. S14).

#### COMPLEMENTARY DEVICES AND LOGIC GATES

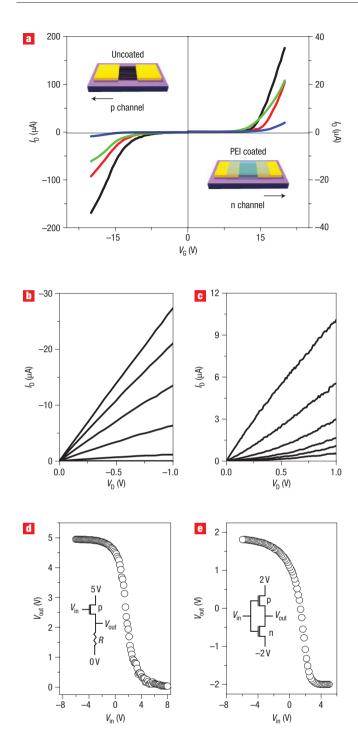

As illustrated in Fig. 5a-c, coating the devices with polyethyleneimine (PEI)<sup>15,33</sup> enables n-channel operation, similar to observations in single-tube devices<sup>33</sup>. These results provide straightforward means to form complementary and unipolar logic gates (inverters), and other circuit elements. Figure 5d shows a PMOS inverter that uses an SWNT-array-based p-channel transistor (response shown in Fig. 5b) as the drive and an array of SWNTs, partially processed by electrical breakdown, as the load. Combining n- and p-channel devices yields CMOS

Figure 4 High-performance top gate transistors that use aligned arrays of SWNTs for the semiconductor. a, Optical micrograph showing an array of eight transistors that use SWNT arrays for the semiconductor, the quartz growth wafer as the substrate, high-capacitance bilayer gate dielectrics of BCB (20 nm)/HfO<sub>2</sub> (10 nm) and split gate electrodes aligned to the channels of the devices. b, Optical micrograph of a device with  $L = 32 \,\mu\text{m}$  and  $W = 200 \,\mu\text{m}$ , corresponding to the box indicated by the dashed blue line in the left portion of part a. c, Optical micrograph of a device with  $L = 4 \,\mu\text{m}$  and  $W = 300 \,\mu\text{m}$ , corresponding to the box indicated by the dashed green line in the right portion of part a. d, Mobilities computed using parallel plate ( $\mu_{dev}$ , blue triangles) and rigorous ( $\mu_{r}$ , black squares) models for the capacitance coupling between the gate electrode and the SWNT arrays. The plot also shows the average per tube mobilities ( $\langle \mu_t \rangle$ , red circles). **e**, Output currents,  $I_{\rm D}$  ( $V_{\rm D}$  = -1 and  $V_{\rm G}$  = -1 V), for devices with L = 4, 8, 16 and 32  $\mu$ m at W = 50, 100, 200 and 300  $\mu$ m. **f**, Output currents,  $I_{\rm D}$  ( $V_{\rm D} = -1$  and  $V_{\rm c} = -1$  V), for 18 devices with L between 4 and 32  $\mu$ m. g, Scaled transconductances  $(g_m/W_{eff})$  for 15 devices with L between 4 and 32  $\mu$ m.

inverters, as illustrated in Fig. 5e. The gains observed in the PMOS and CMOS inverters were 2.75 and 1.8, respectively, as

**Figure 5** n- and p-type SWNT array transistors, with implementation in CMOS and PMOS logic gates. a, Transfer curves of p- and n-channel transistors that use aligned arrays of as-fabricated and PEI-coated arrays of SWNTs, respectively. All devices were processed using electrical breakdown to achieve high on/off ratios. In the case of the n-channel devices, this process was performed before PEI coating.  $L = 4 \,\mu$ m, black;  $L = 7 \,\mu$ m, red;  $L = 12 \,\mu$ m, green;  $L = 27 \,\mu$ m, blue;  $V_D = -0.5 \,$  V. b. Current/voltage response of a typical p-channel device in a regime of small  $V_D (V_G = -5 \,$  V to  $-5 \,$  V). c, Similar results from an n-channel device. ( $V_G = -0.0 \,$  V to 5 V). d, Transfer curve from a PMOS inverter that uses an SWNT-array transistor for the drive, and a two-terminal device with SWNT arrays for the resistive load. The gain of the PMOS inverter is 2.75. The inset provides a circuit schematic. e, Similar information for a CMOS inverter that combines p- and n-channel SWNT-array transistors. The gain of the CMOS inverter is 1.8. involved photolithography to open lines ( $W = 10 \ \mu m$  and  $L = 1 \ cm$ ) in a layer of photoresist (AZ 5214) on the quartz, followed by electron beam evaporation  $(3 \times 10^{-6} \text{ torr}; \text{ Temescal CV-8})$  of Fe (Kurt J. Lesker; 99.95%) to a nominal thickness of <0.5 nm. Lifting off the photoresist with acetone left a pattern of Fe lines. Annealing the Fe at 550 °C in air formed isolated iron oxide nanoparticles with diameters near  $\sim$ 1 nm. The particles served as the catalytic seeds for CVD growth of the SWNTs. Purging with hydrogen at 900 °C for 5 min and then introducing a flow of methane (1,900 s.c.c.m.) and hydrogen (300 s.c.c.m.) at 900 °C for 1 h led to the growth of SWNTs (see Supplementary Information, Fig. S2, for the reproducibility of this growth technique). FABRICATION OF TOP AND BOTTOM GATE TRANSISTORS To make top gate transistors on the quartz growth substrates, Ti (1 nm)/Pd (20 nm) (electron beam evaporated at  $3 \times 10^{-6}$  torr; Temescal CV-8) source/drain electrodes were formed by photolithography and lift-off. For device isolation, these electrodes and the channel region were covered with photoresist, the exposed tubes were removed by reactive ion etching (50 mtorr, 20 s.c.c.m. O2, 30 W, 30 s), and then the resist was washed away with acetone. A spin-cast layer of a photodefinable epoxy (SU8-2, Microchem) formed the gate dielectric. On top of this layer, we defined the gate (Ti (1 nm)/Au (20 nm)) using photolithography and lift-off. Reactive ion etching through the epoxy, using a

GROWTH OF PERFECTLY ALIGNED ARRAYS OF LONG, LINEAR SWNTs

measured at  $V_{DD} = 5$  V for the PMOS device and  $V_{DD} = \pm 2$  V for

the CMOS device. Taken together, these and the other results

presented in this paper indicate a scalable path to SWNT-based thin-film electronics, with high-performance capabilities. Initial

applications might be envisioned in areas that require unusual substrates (for example plastics), such as flexible displays or

conformal structural health monitors, or optical transparency,

such as in heads-up displays and certain security devices. The high-performance attributes, combined with the possibility of

direct integration with silicon, also create interest in the possible use of nanotube array devices with Si CMOS for enhanced

operation (for example, power-handling capabilities, linearresponse or high-speed operation). The array geometry should

also be useful for a range of other applications, which currently

exist only in the form of single-tube demonstrations. Examples

include light-emitting diodes, photodetectors, chemical sensors,

nanoelectromechanical oscillators, and electrically or thermally conductive elements. These and other related systems appear

CVD procedures were used to grow SWNTs on ST cut quartz wafers (Hoffman),

which were annealed at 900 °C in air for 8 h. The first step of the growth process

promising for future study.

METHODS

layer of photoresist as a mask, created openings to enable probing of the source and drain electrodes (see Supplementary Information, Figs S3–S6, for various measured properties of devices with different tube densities and layouts). For the high-performance devices of Fig. 4, spin-casting and atomic layer deposition techniques defined the high-capacitance bilayer dielectrics of BCB and HfO<sub>2</sub>. In addition, gate electrodes with widths comparable to the channel length provided low overlap capacitances for high-speed operation. The electrodes' layouts match probing configurations for high-speed measurements with a network analyser.

For bottom gate devices, the SWNT arrays were transferred from quartz onto other substrates. To pick up the aligned tubes, a 100-nm layer of Au was first deposited on the nanotubes/quartz by electron beam evaporation  $(3 \times 10^{-6} \text{ torr}, 0.1 \text{ nm s}^{-1}; \text{Temescal CV-8})$ . On top of this Au layer, a film of polyimide (polyamic acid, Aldrich) was spin-coated at 3,000 r.p.m. for 30 s and cured at 110 °C for 2 mins. Physically peeling away the polyimide/Au/SWNT film lifted the tubes off the quartz with nearly 100% transfer efficiency. Placing this film on the receiving substrate (SiO<sub>2</sub>/Si) coated with an adhesive layer of SU8-2 (150 nm) and then etching away the polyimide by reactive ion etching (150 mtor, 20 s.c.c.m. O<sub>2</sub>, 150 W, 35 min) left the Au/SWNTs film on the substrate. Photolithography and etching of the Au (Au-TEA, Transene) defined the Au source and drain electrodes. In the final step of the fabrication, SWNTs outside the channel regions were removed by reactive ion etching to isolate the devices (see Supplementary Information, Figs. S11 and S12, for SEM images that indicate the nearly 100% efficiency of this process).

## ARTICLES

#### FABRICATION OF TRANSISTORS WITH POLYMER ELECTROLYTE AND Hf02 GATE DIELECTRICS

To achieve high transconductances, we used high-capacitance gate dielectrics consisting of either 10-nm HfO<sub>2</sub> or a polymer electrolyte. The electrolytes were made by directly dissolving LiClO<sub>4</sub> \* 3H<sub>2</sub>O in poly(ethylene oxide) (PEO,  $M_n = 550$ ) or in polyethylenimine (PEI,  $M_n = 800$ ) in air at room temperature with 2.4:1 and 1:1 polymer to salt weight ratios, respectively. The electrolytes were injected into a polydimethylsiloxane (PDMS) fluidic channel laminated over aligned arrays of SWNTs on quartz substrates with source/drain electrodes defined according to the previously described procedures. In these devices, gate voltages were applied through a silver wire dipped in the electrolyte. The HfO<sub>2</sub> was prepared on a doped silicon substrate by atomic layer deposition (Savannah 100, Cambridge NanoTech) using H<sub>2</sub>O and Hf(NMe<sub>2</sub>)<sub>4</sub> (99.99+%, Aldrich) and a substrate temperature of 150 °C. SWNT arrays were transferred onto the HfO<sub>2</sub> using the procedures described above, but without the adhesive layer.

#### FABRICATION OF *n*-TYPE TRANSISTORS, CMOS AND PMOS LOGIC GATES

Spin-coating layers of PEI ( $M_n = 800$ , Aldrich) on the top of the nanotubes switches the operation of the transistors from unipolar p-channel to unipolar n-channel. To form these coatings, PEI was first dissolved in methanol with a volume concentration of 1:5. Spin-casting the PEI directly onto the SWNTs at 2,000 r.p.m. for 30 s created the coatings. Heating at 50 °C for 10 h gave n-channel transistors. Suitable interconnection of such devices can yield logic gates of various types. For PMOS inverters, one transistor served as a resistor load, and the other served as the drive. CMOS inverters were formed with uncoated p-channel devices and PEI-coated n-channel devices.

# Received 3 November 2006; accepted 23 February 2007; published 25 March 2007.

#### References

- Zhou, X., Park, J.-Y., Huang, S., Liu, J. & Mceuen, P. L. Band structure, phonon scattering and the performance limit of single-walled carbon nanotube transistors. *Phys. Rev. Lett.* 95, 146805 (2005).

- Durkop, T., Getty, S. A., Cobas, E. & Fuhrer, M. S. Extraordinary mobility in semiconducting carbon nanotubes. *Nano Lett.* 4, 35–39 (2004).

Yao, Z., Kane, C. L. & Dekker, C. High-field electrical transport in single-wall carbon nanotubes.

- Yao, Z., Kane, C. L. & Dekker, C. High-field electrical transport in single-wall carbon nanotubes. Phys. Rev. Lett. 84, 2941–2944 (2000).

- Lin, Y.-M., Appenzeller, J., Knoch, J. & Avouris P. High-performance carbon nanotube field-effect transistor with tunable polarities. *IEEE Trans. Nanotechnol.* 4, 481–489 (2005).

- Chen, Z. et al. An integrated logic circuit assembled on a single carbon nanotube. Science 311, 1735 (2006).

- Bachtold, A., Hadley, P., Nakanishi, T. & Dekker, C. Logic circuits with carbon nanotube transistors. Science 294, 1317–1320 (2001).

- Misewich, J. A. et al. Electrically induced optical emission from a carbon nanotube FET. Science 300, 783-786 (2003).

- Chen, J. et al. Bright infrared emission from electrically induced excitons in carbon nanotubes. Science 310, 1171–1174 (2005).

- 9. Kong, J. et al. Nanotube molecular wires as chemical sensors. Science 287, 622-625 (2000).

- Guo, J., Hasan, S., Javey, A., Bosman, G. & Lundstrom, M. Assessment of high-frequency performance potential of carbon nanotube transistors. *IEEE Trans. Nanotechnol.* 4, 715–721 (2005).

Guo, J., Goasguen, S., Lundstrom, M. & Datta, S. Metal–insulator–semiconductor electrostatics of

- Costa and Cos

- Liu, X., Han, S. & Zhou, C. Novel nanotube-on-insulator (NOI) approach toward single-walled carbon nanotube devices. *Nano Lett.* 6, 34–39 (2006).

- Li, S., Yu, Z., Rutherglen, C. & Burke, P. J. Electrical properties of 0.4 cm long single-walled carbon nanotubes. *Nano Lett.* 4, 2003–2007 (2004).

Zhou, Y. et al. P-channel, n-channel thin film transistors and p-n diodes based on single wall carbon

- 15. Zhou, I. et al. P-chainer, in-chainer thin him transitions and p-n diodes based on single wan carbon nanotube networks. Nano Lett. 4, 2031–2035 (2004).

- Hu, L., Hecht, D. S. & Gruner, G. Percolation in transparent and conducting carbon nanotube networks. *Nano Lett.* 4, 2513–2517 (2004).

- Snow, E. S., Campbell, P. M., Ancona, M. G. & Novak, J. P. High-mobility carbon-nanotube thin-film transistors on a polymeric substrate. *Appl. Phys. Lett.* 86, 033105 (2005).

- Ismach, A., Segev, L., Wachtel, E. & Joselevich, E. Atomic-step-templated formation of single wall carbon nanotube patterns. *Angew. Chem. Int. Edn* 43, 6140–6143 (2004).

- Han, S., Liu, X. & Zhou, C. Template-free directional growth of single-walled carbon nanotubes on aand r-plane sapphire. J. Am. Chem. Soc. 127, 5294–5295 (2005).

- Kocabas, C., Shim, M. & Rogers, J. A. Spatially selective guided growth of high-coverage arrays and random networks of single-walled carbon nanotubes and their integration into electronic devices. *J. Am. Chem. Soc.* **128**, 4540–4541 (2006).

- Park, J.-Y. et al. Electron-phonon scattering in metallic single walled carbon nanotubes. Nano Lett. 4, 517–520 (2004).

- 22. Javey, A. et al. High-field quasiballistic transport in short carbon nanotubes. Phys. Rev. Lett. 92, 106804 (2004).

- McEuen, P. L., Fuhrer, M. & Park, H. Single-walled carbon nanotube electronics. *IEEE Trans.* Nanotechnol. 1, 78–86 (2002).

- Chen, Z., Appenzeller, J., Knoch, J., Lin, Y.-M. & Avouris, P. The role of metal-nanotube contact in the performance of carbon nanotube field-effect transistors. *Nano Lett.* 5, 1497–1502 (2005).

- Kim, W. et al. Electrical contacts to carbon nanotubes down to 1 nm in diameter. Appl. Phys. Lett. 87, 173101 (2005).

- Heinze, S. et al. Carbon nanotubes as Schottky barrier transistors. *Phys. Rev. Lett.* 89, 106801 (2002).

Collins, P. G., Arnold, M. S. & Avouris, P. Engineering carbon nanotubes and nanotube circuits using electrical breakdown. *Science* 292, 706–709 (2001).

- Hur, S.-H., Park, O. O. & Rogers, J. A. Extreme bendability of single-walled carbon nanotube networks transferred from high-temperature growth substrates to plastic and their use in thin-film transistors. *Appl. Phys. Lett.* 86, 243502 (2005).

- Huang, X. M. H. et al. Controlled placement of individual carbon nanotubes. Nano Lett. 5, 1515–1518 (2005).

- Bradley, K., Gabriel, J.-C. P. & Gruner G. Flexible nanotube electronics. Nano Lett. 3, 1353–1355 (2003).

- Javey, A. et al. High-κ dielectrics for advanced carbon-nanotube transistors and logic gates. Nature Mater. 1, 241–246 (2002).

- Ozel, T., Gaur, A., Rogers, J. A. & Shim, M. Polymer electrolyte gating of carbon nanotube network transistors. *Nano Lett.* 5, 905–911 (2005).

- Shim, M., Javey, A., Kam, N. W. S. & Dai, H. Polymer functionalization for air-stable n-type carbon nanotube field-effect transistors. J. Am. Chem. Soc. 123, 11512–11513 (2001).

#### Acknowledgements

We thank T. Banks and K. Colravy for help with processing, using facilities at the Frederick Seitz Materials Research Laboratory. This material is based upon work supported by the National Science Foundation under grant NIRT-0403489 and the US Department of Energy, Division of Materials Sciences under Award No. DEFG02-91ER45439, through the Frederick Seitz MRL and Center for Microanalysis of Materials at the University of Illinois at Urbana-Champaign. S.J.K. acknowledges fellowship support from the Institute of Information Technology Assessment of Korea. N.P. and M.A.A. acknowledge the support from the Network for Computational Nanotechnology. Correspondence and requests for materials should be addressed to I.A.R.

Supplementary information accompanies this paper on www.nature.com/naturenanotechnology.

#### Author contributions

S.J.K, C.K. and J.A.R. designed the experiments, S.J.K., C.K. and T.O. performed the experiments, S.J.K., C.K., T.O., M.S., N.P., M.A.A., S.V.R. and J.A.R. analysed the data, S.J.K, C.K. and J.A.R. wrote the paper.

#### Competing financial interests

The authors declare that they have no competing financial interests.

Reprints and permission information is available online at http://npg.nature.com/reprintsandpermissions/