# NANO EXPRESS

**Open Access**

# High-performance III-V MOSFET with nanostacked high-k gate dielectric and 3D fin-shaped structure

Szu-Hung Chen<sup>3</sup>, Wen-Shiang Liao<sup>1\*</sup>, Hsin-Chia Yang<sup>1</sup>, Shea-Jue Wang<sup>4</sup>, Yue-Gie Liaw<sup>5</sup>, Hao Wang<sup>1\*</sup>, Haoshuang Gu<sup>2</sup> and Mu-Chun Wang<sup>1\*</sup>

# Abstract

A three-dimensional (3D) fin-shaped field-effect transistor structure based on III-V metal-oxide-semiconductor fieldeffect transistor (MOSFET) fabrication has been demonstrated using a submicron GaAs fin as the high-mobility channel. The fin-shaped channel has a thickness-to-width ratio ( $T_{Fin}/W_{Fin}$ ) equal to 1. The nano-stacked high-k Al<sub>2</sub>O<sub>3</sub> dielectric was adopted as a gate insulator in forming a metal-oxide-semiconductor structure to suppress gate leakage. The 3D III-V MOSFET exhibits outstanding gate controllability and shows a high  $I_{on}/I_{off}$  ratio > 10<sup>5</sup> and a low subthreshold swing of 80 mV/decade. Compared to a conventional Schottky gate metal-semiconductor field-effect transistor or planar III-V MOSFETs, the III-V MOSFET in this work exhibits a significant performance improvement and is promising for future development of high-performance n-channel devices based on III-V materials.

Keywords: GaAs, High-k, MOSFET, Three-dimensional device, FinFET

# Background

Since the transistor speed in circuit consideration is very impressive, III-V compound semiconductors [1] can be treated as potential channel replacement materials for Si in deep nanoprocess integration. III-V materials such as GaAs and InAs possessing higher electron mobility are expected to conduct higher drive current. Conventionally, operation of III-V field-effect transistors (FETs) mainly relies on a Schottky gate structure to modulate channel potential. However, the Schottky gate suffers from high leakage current issue which restrains III-V devices from very-large-scale integration. Metal-oxidesemiconductor (MOS) gate structure used in Si MOS-FET is thermodynamically stable and effective for leakage current reduction. In contrary, the lack of a high-quality oxide/semiconductor scheme has limited the applications of III-V devices for decades. Recently, several groups have demonstrated encouraging results in aspects of III-V surface cleaning or pretreatment

Full list of author information is available at the end of the article

methods [2,3], growth of insulator on various III-V materials [4,5], as well as realization of III-V MOSFETs [6-11]. Up-to-date III-V MOSFET technologies have demonstrated significant performance enhancement and have achieved low gate leakage [8,10], high channel mobility [7,11], and high drive current [6]. Consequently, it is feasible to produce high-performance MOSFETs using III-V materials. On the other hand, when the scaling of planar complementary-symmetry metal-oxide-Si semiconductor (CMOS) gradually approaches its physical limit, three-dimensional fin-shaped FET (FinFET) device architecture [12-15] is a promising alternate enabling transistor scaling beyond the 22-nm technology node. FinFET [16] structure provides superior control of short channel effects [13]; however, there are only few reports on III-V-based FinFETs [15,17,18]. In this letter, for the first time, a novel III-V MOSFET device technology based on a three-dimensional FinFET structure is reported. Al<sub>2</sub>O<sub>3</sub> film [19] is used as the gate insulator [4], and submicron GaAs fin is the channel. Both III-V MOSFET and metal-semiconductor FET (MESFET) with a FinFET structure were fabricated, characterized, and evaluated.

© 2012 Chen et al.; licensee Springer. This is an Open Access article distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/2.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

<sup>\*</sup> Correspondence: wsliaoumc@yahoo.com.tw; nanoguy@126.com;

mucwang@must.edu.tw

<sup>&</sup>lt;sup>1</sup>Department of Electronic Engineering, Minghsin University of Science and Technology, Hsinchu 30401, Taiwan

## **Methods**

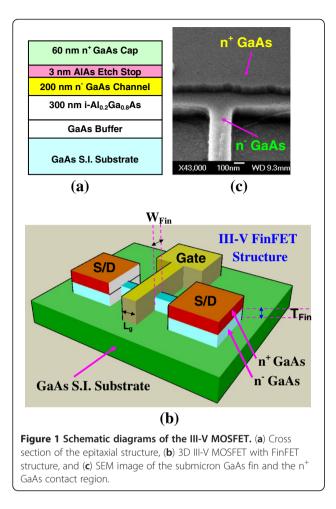

GaAs epitaxial wafer grown by molecular beam epitaxy was used as a vehicle for studying III-V-based MOSFETs. The device structure, as shown in Figure 1a, consists of a 300-nm Al<sub>0.2</sub>Ga<sub>0.8</sub>As buffer layer on a semi-insulating (S.I.) GaAs substrate, a 200-nm GaAs channel layer with a doping concentration of  $3 \times 10^{17}$  cm<sup>-3</sup>, a 3-nm AlAs etch stop layer, and a 60-nm heavily doped GaAs cap layer at the top. Figure 1b shows a schematic diagram of the III-V MOSFET with a FinFET structure fabricated on the S.I. GaAs substrate. The source/drain regions contain heavily doped GaAs layer for low contact resistance. The gate strip crosses the narrow GaAs fin forming the resultant three-dimensional (3D) FinFET structure. The key fabrication processes for III-V MOS-FET and MESFET include removing the GaAs cap layer by wet etching method using citric acid/hydrogen peroxide solution, selectively removing the AlAs etch stop layer to reveal the underneath GaAs channel, and patterning the active GaAs fin region by electron beam lithography. Subsequently, dry etching was performed using inductively coupled plasma to etch down to the buffer layer to form the GaAs fin and simultaneously offer better device isolation. Note that the wet etch process is widely used in mesa isolation step for conventional III-V FETs. However, in this study, a dry etch process was adopted instead to form GaAs fin mainly due to the better integrity of submicron pattern transfer using the dry etch process. As shown in Figure 1c, the edge profile of the submicron GaAs fin is well defined by the dry etch process and good selectivity between n<sup>+</sup> GaAs/n<sup>-</sup> GaAs is also achieved by the wet etch process using the AlAs layer as etch stop. AuGeNiAu ohmic contacts were deposited by electron beam evaporation, followed by liftoff process and rapid thermal annealing treatment at 400°C for 30 s. The gate metal is Ti/Au, and the gate length is 0.5 µm. For III-V MOSFET fabrication, there is an additional step of gate insulator growth before the deposition of the gate metal to generate the final MOS structure. The insulator used is an Al<sub>2</sub>O<sub>3</sub> high-k dielectric. Surface pretreatment prior to dielectric deposition is important to ensure an unpinned interface between the dielectric and GaAs [2-4]. After surface treatment using an ammonia-based solution [3], the wafer was subsequently transferred to an atomic layer deposition system for Al<sub>2</sub>O<sub>3</sub> deposition. The growth temperature is 300°C, and the thickness of the  $Al_2O_3$  is 10 nm. For MESFET, hydrochloric acid solution was used for surface treatment before gate metal deposition. Both fabricated MOSFETs and MESFETs have the same 3D FinFET structure. The thickness  $(T_{\rm fin})$  and width  $(W_{\rm fin})$  of the GaAs fins are both 200 nm.

## **Results and discussion**

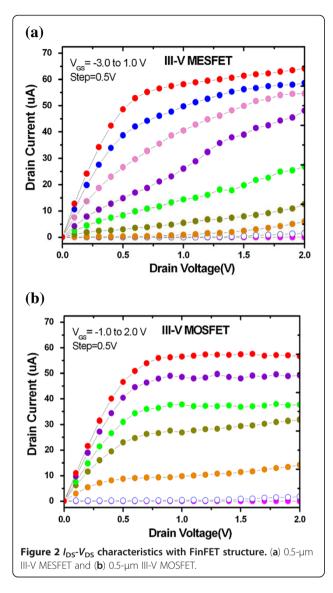

Drain current  $(I_{\rm DS})$  versus drain voltage  $(V_{\rm DS})$  curves under different gate voltages  $(V_{GS})$  of the devices are shown in Figure 2. The threshold voltage  $(V_{\rm th})$  is -1.5 and -0.25 V for III-V MESFET and MOSFET, respectively. In Figure 2a, a kink behavior was observed. The knee voltage which defines the transition between linear and saturation regions in the normal  $I_{DS}$ - $V_{DS}$  curve was smeared as the channel is near pinch-off. This phenomenon is related to Fermi level pinning and electron trapping by surface states [20]. A depletion region was created between gate and source/drain electrodes which results in reduced drain output current. When the gate bias is increased, the device behaves more like a typical FET. For the  $I_{DS}$ - $V_{DS}$  curves of the MOSFET as shown in Figure 2b, the performance was improved. This is mainly due to the deposited Al<sub>2</sub>O<sub>3</sub> dielectric layer on the surface of the GaAs channel. The Al<sub>2</sub>O<sub>3</sub> high-k dielectric layer not only acts as a gate insulator, but also plays an important role of surface passivation [21]. The significant performance difference between MOSFET and MESFET implies that devices with a three-dimensional FinFET structure inherently suffer from surface trap issue more seriously than conventional

planar devices. This is primarily due to the additional exposed side walls of the fin-shaped channel (i.e., the channel has larger surface-to-volume ratio). Consequently, a good device passivation procedure preventing surface trap-induced effects is indispensable for III-V FETs with a FinFET structure to ensure high device performance.

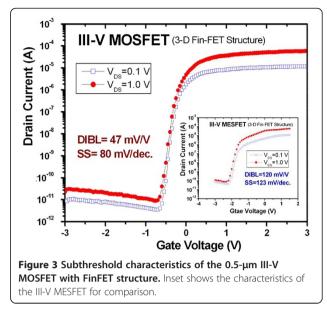

The subthreshold characteristics of the devices were also evaluated to further verify the benefit of applying a FinFET structure to III-V MOSFETs. Figure 3 shows the transfer curves of the devices measured at  $V_{\rm DS} = 0.1$  and 1 V. Device parameters such as drain-induced barrier lowering (DIBL), on current/off current ( $I_{\rm on}/I_{\rm off}$ ) ratio, and subthreshold swing (SS) were extracted. The calculated DIBL of MESFET is 120 mV/V (shown in the inset of Figure 3), while the value is decreased to 47 mV/V for MOSFET. By introducing a dielectric film, the

gate leakage current of the device can be reduced as shown in Figure 3. This is beneficial for improving the  $I_{\rm on}/I_{\rm off}$  ratio of the device. The definition of  $I_{\rm on}$  and  $I_{\rm off}$ can be found in the literature [22]. The supply voltage  $V_{\rm CC}$  is 1 V for parameter extraction. The MESFET has an  $I_{\rm on}/I_{\rm off}$  ratio of  $1.17 \times 10^2$ , and the ratio is improved significantly to  $2.54 \times 10^5$  for MOSFET. The SS at  $V_{\rm DS}$  = 1 V is 123 mV/decade for MESFET and 80 mV/decade for MOSFET. The low SS value of the MOSFET is an indication that the devices have low interface trap density and good gate controllability over the channel [8,23]. These results further demonstrate that MOSFET outperforms MESFET in terms of subthreshold characteristics. As a result, the use of a MOS gate scheme is essential in the performance improvement of the III-V MESFETs. The extracted effective channel mobility in the linear region of the III-V nMOSFET was about 100 cm<sup>2</sup>/V-s using the following expression:  $I_{\text{DS}} = \frac{W}{L} \cdot \mu \cdot C_{\text{gate}} \cdot \left(V_{\text{GS}} - V_{\text{th}} - \frac{V_{\text{DS}}}{2}\right) \cdot V_{\text{DS}}$ [14], where  $\mu$  is the carrier mobility and  $C_{\text{gate}}$  is the gate capacitance per unit area. The 3D III-V nMOSFET has a total gate width W/gate length  $L = 0.6:0.5 \mu m$ . The low value of the extracted channel mobility of the 3D III-V nMOSFET was possibly due to the high parasitic access resistance caused by the narrow fin in the source/drain (S/D) regions. Further improvement can be achieved by using a self-aligned S/D process or forming a heavily doped fin region in the S/D extension. In short, the comparison of electrical performance between 3D III-V nMOSFET and 3D III-V nMESFET is presented in Table 1. As shown in Table 1, when compared to conventional planar III-V MOSFETs, the fabricated MOSFET in this work with a FinFET structure exhibits very promising results under low-voltage operation. Although the  $T_{\rm Fin}$  of the GaAs fin is

Table 1 Electrical performance of 3D III-V nMOSFET and nMESFET with 0.6-µm gate width and 0.5-µm length

|                                                      | MOSFET               | MESFET               |

|------------------------------------------------------|----------------------|----------------------|

| I <sub>on</sub> /I <sub>off</sub> ratio              | $2.54 \times 10^{5}$ | $1.17 \times 10^{2}$ |

| $I_{\rm on}$ (µA) at $V_{\rm GS} = V_{\rm DS} = 1$ V | 37                   | 58                   |

| $V_{\rm th}$ (V) at $V_{\rm DS}\!=\!0.1$ V           | -0.25                | -1.5                 |

| SS (mV/decade) at $V_{\rm DS} = 1$ V                 | 80                   | 123                  |

| SS (mV/decade) at $V_{\rm DS}$ = 0.1 V               | 68                   | 109                  |

| DIBL (mV/V)                                          | 47                   | 120                  |

|                                                      |                      |                      |

200 nm, the SS value of the device with a 0.5- $\mu$ m gate length is better than the published results of 1  $\mu$ m × 100  $\mu$ m planar In<sub>0.2</sub>Ga<sub>0.8</sub>As MOS-high electron mobility transistor [8] which essentially has longer gate length and buried quantum well channel design with higher carrier mobility. The above results further confirm that the III-V MOSFET developed in this work exhibits excellent gate controllability over the channel due to the use of a 3D Fin-FET structure.

$I_{\rm on}/I_{\rm off}$ , on current/off current;  $V_{\rm GS}$ , gate voltage;  $V_{\rm DS}$ , drain voltage;  $V_{\rm th}$ , threshold voltage; SS, subthreshold swing; DIBL, drain-induced barrier lowering; MOSFET, metal-oxide-semiconductor field-effect transistor; MES-FET, metal-semiconductor field-effect transistor.

## Conclusions

Measurement and analysis of high-performance III-V nMOSFET are achieved by applying a FinFET structure to device fabrication. The device exhibits excellent sub-threshold characteristics and demonstrates significant performance improvement over conventional Schottky gate nMESFET or planar III-V nMOSFETs because of the enlarging channel width, the existing higher channel electron mobility compared with silicon channel and lower channel interface states, as well as the good gate controllability representing the smaller swing value. The three-dimensional III-V nMOSFET device technology developed illustrates great potential and is promising when the CMOS technology is pushed toward more stringent scaling in the foreseeable future.

#### **Competing interests**

The authors declare that they have no competing interests.

#### Authors' contributions

The achievement presented here was completed in collaboration among all authors. MCW, WSL, and HW defined the research topic. SHC provided the tested samples. HCY, YGL, HSG, and SJW collected the measurement data or gave this topic some precious advices. All authors contributed to the data interpretation and analysis. MCW and SHC wrote the paper. All authors have contributed to, checked, and approved the final manuscript.

#### Authors' information

SHC is an associate researcher at National Nano Device Laboratories, Hsinchu, 30078, Taiwan. WSL is a full professor in the Faculty of Physics and Electronic Technology, Hubei University, Wuhan, 430062, People's Republic of China. HCY is an assistant professor in the Electronic Engineering, Minghsin University of Science and Technology, Hsinchu, 30401, Taiwan. SJW is an assistant professor in the Department of Materials and Resources Engineering, National Taipei University of Technology, Taipei, 10608, Taiwan. YGL is the vice president of ADATA Technology Company, New Taipei, 23553, Taiwan. HW is a distinguished professor from the Faculty of Physics and Electronic Technology, Hubei University, Wuhan, 430062, People's Republic of China. HSG is a full professor in the Faculty of Physics and Electronic Technology, Hubei University, Wuhan, 430062, People's Republic of China. MCW is a full professor in the Electronic Engineering, Minghsin University of Science and Technology, Hsinchu, 30401, Taiwan.

#### Acknowledgments

The authors would like to thank the National Nano Device Laboratories in Hsinchu, Taiwan for the experimental sample preparation.

#### Author details

<sup>1</sup>Department of Electronic Engineering, Minghsin University of Science and Technology, Hsinchu 30401, Taiwan. <sup>2</sup>Faculty of Physics and Electronic Technology, Hubei University, Wuhan 430062, People's Republic of China. <sup>3</sup>National Nano Device Laboratories, Hsinchu 30078, Taiwan. <sup>4</sup>Department of Materials and Resources Engineering, National Taipei University of Technology, Taipei 10608, Taiwan. <sup>5</sup>ADATA Technology Company, New Taipei 23553, Taiwan.

#### Received: 8 December 2011 Accepted: 26 April 2012 Published: 1 August 2012

#### References

- International technology Roadmap for Semiconductors, [Online]. Available: http://www.itrs.net/Links/2007TRS/Home2007.htm.

- Shahrjerdi D, Garcia-Gutierrez DI, Akyol T, Bank SR, Tutuc E, Lee JC, Banerjee SK: GaAs metal-oxide-semiconductor capacitors using atomic layer deposition of HfO<sub>2</sub> gate dielectric: fabrication and characterization. *Applied Physics Letters* 2007, 91:193503.

- Xuan Y, Lin HC, Ye PD: Simplified surface preparation for GaAs passivation using atomic layer deposited high-k dielectrics. *IEEE Trans. Electron Devices* 2007, 54(8):1811.

- Ye PD, Wilk GD, Kwo J, Yang B, Gossmann H-JL, Frei M, Chu SNG, Mannaerts JP, Sergent M, Hong M, Ng KK, Bude J: GaAs MOSFET with oxide gate dielectric grown by atomic layer deposition. *IEEE Electron Device Letters* 2003, 24(4):209.

- Kim HS, Ok I, Zhang M, Lee T, Zhu F, Yu L, Lee JC: Depletion-mode GaAs metal-oxide-semiconductor field-effect transistor with HfO<sub>2</sub> dielectric and germanium interfacial passivation layer. *Applied Physics Letters* 2006, 89:222904.

- Xuan Y, Wu YQ, Ye PD: High-performance inversion-type enhancementmode InGaAs MOSFET with maximum drain current exceeding 1 A/mm. IEEE Electron Device Letters 2008, 29(4):294.

- Hill RJW, Moran DAJ, Li X, Zhou H, Macintyre D, Thoms S, Asenov A, Zurcher P, Rajagopalan K, Abrokwah J, Droopad R, Passlack M, Thayne IG: Enhancement-mode GaAs MOSFETs with an In<sub>0.3</sub> Ga<sub>0.7</sub>As channel, a mobility of over 5000 cm<sup>2</sup>/V·s, and transconductance of over 475 µS/ µm. IEEE Electron Device Letters 2007, 28(12):1080.

- Lin HC, Yang T, Sharifi H, Kim SK, Xuan Y, Shen T, Mohammadi S, Ye PD: Enhancement-mode GaAs metal-oxide-semiconductor high-electronmobility transistors with atomic layer deposited Al<sub>2</sub>O<sub>3</sub> as gate dielectric. *Applied Physics Letters* 2007, 91:212101.

- Zhang J, Kosel TH, Hall DC, Fay P: Fabrication and performance of 0.25-µm gate length depletion-mode GaAs-channel MOSFETs with self-aligned InAIP native oxide gate dielectric. *IEEE Electron Device Letters* 2008, 29(2):143.

- Cao Y, Zhang J, Kosel TH, Hall DC, Fay P: Microwave-frequency InAIP-oxide /GaAs MOSFETs. In Proceedings of the IEEE CSIC Symposium: November 12–15: San Antonio. *IEEE*; 2006, 2006:43–46.

- Xuan Y, Wu YQ, Lin HC, Shen T, Ye PD: Submicrometer inversion-type enhancement-mode InGaAs MOSFET with atomic-layer deposited Al<sub>2</sub>O<sub>3</sub> as gate dielectric. *IEEE Electron Devices Letters* 2007, 28(11):935.

- Doyle B, Boyanov B, Datta S, Doczy M, Hareland S, Jin B, Kavalieros J, Linton T, Rios R, Chau R: Tri-Gate fully-depleted CMOS transistors: fabrication, design and layout. In Proceedings of the Symposium on VLSI Technology. Digest of Technical Papers: June 10–12: Hillsboro. *IEEE*; 2003, 2003:133–134.

- Lee RTP: Eu-Jin Lim A, Tan KM, Liow TY, Lo GQ, Samudra GS, Chi DZ, Yeo YC: N-channel FinFETs with 25-nm gate length and Schottky-barrier source and drain featuring ytterbium silicide. *IEEE Electron Device Letters* 2007, 28(2):164.

- Singh N, Agarwal A, Bera LK, Liow TY, Yang R, Rustagi SC, Tung CH, Kumar R, Lo GQ, Balasubramanian N, Kwong D-L: High-performance fully depleted silicon nanowire (diameter ≤ 5 nm) gate-all-around CMOS devices. *IEEE Electron Device Letters* 2006, 27(5):383.

- Benedicto M, Galiana B, Molina-Aldareguia JM, Monaghan S, Hurley PK, Cherkaoui K, Vazquez L, Tejedor P: Fabrication of HfO<sub>2</sub> patterns by laser interference nanolithography and selective dry etching for III-V CMOS application. *Nanoscale Research Letters* 2011, 6:400.

- Liao WS, Wang MC, Hu YM, Chen SH, Chen KM, Liaw YG, Ye C, Wang WF, Zhou D, Wang H, Gu HS: Drive current and hot carrier reliability improvements of high-aspect-ratio n-channel fin-shaped field effect transistor with high-tensile contact etching stop layer. *Applied Physics Letters* 2011, 99:173505.

- Liu Y, Neophytou N, Klimeck G, Lundstrom MS: Band-structure effects on the performance of III–V ultrathin-body SOI MOSFETs. *IEEE Trans Electron Devices* 2008, 55(5):1116.

- Kim D, Krishnamohan T, Nishi Y, Saraswat KC: Band to band tunneling limited off state current in ultra-thin body double gate FETs with high mobility materials: III-V, Ge and strained Si/Ge. In Proceedings of the International Conference on SISPAD: September 6–8: Monterey. *IEEE*; 2006, 2006:389–392.

- Suh DC, Cho YD, Kim SW, Ko DH, Lee YS, Cho MH, Oh JW: Improved thermal stability of Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> high-k gate dielectric stack on GaAs. Applied Physics Letters 2010, 96:142112.

- Liang CL, Wong H, Cheung NW, Sato RN: Parasitic effects of surface states on GaAs MESFET characteristics at liquid-nitrogen temperature. *IEEE Trans Electron Devices* 1989, 36(9):1858.

- Xuan Y, Ye PD, Lin HC: Minority-carrier characteristics of InGaAs metaloxide-semiconductor structures using atomic-layer-deposited Al<sub>2</sub>O<sub>3</sub> gate dielectric. Applied Physics Letters 2006, 89:132103.

- Chau R, Datta S, Doczy M, Doyle B, Jin B, Kavalieros J, Majumdar A, Metz M, Radosavljevic M: Benchmarking nanotechnology for high-performance and low-power logic transistor applications. *IEEE Trans on Nanotechnology* 2005, 4(2):153.

- Sze SM: NG KK: Physics of Semiconductor Devices. 3rd edition. Hoboken: Wiley; 2007.

#### doi:10.1186/1556-276X-7-431

**Cite this article as:** Chen *et al.*: **High-performance III-V MOSFET with nano-stacked high-k gate dielectric and 3D fin-shaped structure**. *Nanoscale Research Letters* 2012 **7**:431.

# Submit your manuscript to a SpringerOpen<sup>®</sup> journal and benefit from:

- Convenient online submission

- ► Rigorous peer review

- Immediate publication on acceptance

- Open access: articles freely available online

- High visibility within the field

- Retaining the copyright to your article

Submit your next manuscript at > springeropen.com