#### High-Performance Scalable Base-4 Fast Fourier Transform Mapping

Dr. J. Greg Nash, Centar

(jgregnash@centar.net, www.centar.net)

A novel, scalable parallel FFT architecture mapping is described here that supports transform lengths which aren't powers of two or four, that provides low latency as well as high throughput, that can do both 1-D and 2-D discreet Fourier transforms (DFTs), that is ideally suited to today's complex FPGA architectures, that possesses all the regularity and design simplicity of systolic arrays and that is naturally suited to a parameterized HDL form. Its algorithmic underpinnings are based on an observation that with suitable permutations, the DFT coefficient matrix can be partitioned into regular blocks of smaller "base-4" matrices (equivalent to a decimation in time *and* frequency) [1]. From this new base-4 matrix DFT description we have derived a new latency and throughput optimal base-4 FFT architecture. It combines the performance of traditional radix-4 "pipelined FFTs" with the design and implementation simplicity of systolic arrays, and yet is versatile.

An *N* point DFT is defined by

$$Z[k] = \sum_{n=1}^{N} X[n] e^{-j(2\pi/N)(k-1)(n-1)} k = 1, 2...N \quad \text{or} \quad Z = CX$$

(1)

where X[n] are the time domain input values, Z[k] are the frequency domain outputs and *C* is a coefficient matrix containing elements  $W_N^{kn} = e^{-2j\pi(n-1)(k-1)/N}$ . In order to transform *C* into the desired base-*b* (*b*=4) format it is necessary to find a permutation matrix *P* that reorders *X* and *Z* according to

$$X_{b} = P \left[X_{1} X_{2} X_{3} X_{4} X_{5} ... X_{N-3} X_{N-2} X_{N-1} X_{N}\right]^{t}$$

=  $\left[X_{1} X_{1+N/4} X_{1+N/2} X_{1+3N/4} X_{2} ... X_{N/4} X_{N/2} X_{3N/4} X_{N}\right]^{t}$  (2)

and  $Z_b = P Z$ . With this value of P, C can be transformed into  $C_b = PCP^t$ , so that  $Z_b = C_b X_b$ . This transformation allows  $C_b$  to be written as an  $(N/b) \times (N/b)$  array of bxb blocks, each block  $C_b[i, j]$  specified by

$C_{b}[i, j] = W_{M}[i, j] * c_{D((j-1) \mod(b))+1} C_{((i-1) \mod(b))+1}$ where  $c_{Di} = c_{i}^{t} I$  with  $c_{i}$  a *b*-element vector,  $C_{i}$  is a *bxb* matrix, each row being  $c_{i}^{t}$ , and  $W_{M}[i, j]$  is an element in the  $(N/b) \times (N/b)$  matrix,

$$W_{M} = \begin{bmatrix} 1 & 1 & 1 & 1 & \cdots \\ 1 & W^{1} & W^{2} & W^{3} & \cdots \\ 1 & W^{2} & W^{4} & W^{6} & \cdots \\ 1 & W^{3} & W^{6} & W^{9} & \cdots \\ \vdots & \vdots & \vdots & \vdots & \ddots \end{bmatrix}.$$

(3)

With this block reformulation it is possible to factor (1) into

$$Y = W_M \bullet C_{M1} X$$

$$Z = C_{M2} Y^t$$

(4)

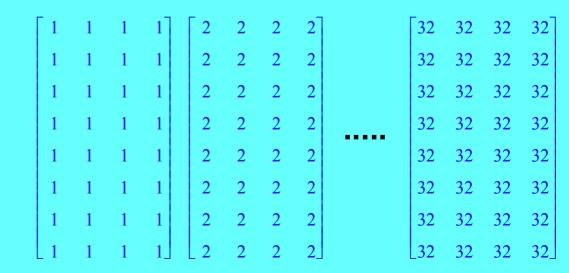

where "•" in (4) corresponds to an element by element multiply [2]. In (4)  $C_{M1}$  and  $C_{M2}$  contain  $N/b^2$  submatrices

$C_B = [c_1 | c_2 | ... | c_b]^t$  with the form  $C_{M1} = [C_B^t | C_B^t | ...]^t$  and  $C_{M2} = [C_B | C_B | ...]$ , and Z, X have been redefined as follows:

$$Z = \begin{bmatrix} Z_1 & Z_{N/4} \\ Z_{1+N/4} & \cdots & Z_{N/2} \\ Z_{1+N/2} & Z_{3N/4} \\ Z_{1+3N/4} & Z_N \end{bmatrix}, X = \begin{bmatrix} X_1 & X_{N/4} \\ X_{1+N/4} & \cdots & X_{N/2} \\ X_{1+N/2} & X_{3N/4} \\ X_{1+3N/4} & X_N \end{bmatrix}.$$

(5)

For base-4 designs (b=4),  $c_1 = \begin{bmatrix} 1 \\ 1 \\ 1 \\ 1 \end{bmatrix}, c_2 = \begin{bmatrix} 1 \\ -1 \\ -1 \\ j \end{bmatrix}, c_3 = \begin{bmatrix} 1 \\ -1 \\ 1 \\ -1 \end{bmatrix}, c_4 = \begin{bmatrix} 1 \\ j \\ -1 \\ -j \end{bmatrix}$

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Form Approved<br>OMB No. 0704-0188                  |                              |                   |                                             |                    |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------|-------------------|---------------------------------------------|--------------------|--|--|--|--|

| Public reporting burden for the collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington Headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington VA 22202-4302. Respondents should be aware that notwithstanding any other provision of law, no person shall be subject to a penalty for failing to comply with a collection of information if it does not display a currently valid OMB control number. |                                                     |                              |                   |                                             |                    |  |  |  |  |

| 1. REPORT DATE<br>20 AUG 2004                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                     | 2. REPORT TYPE<br>N/A        |                   | 3. DATES COVERED                            |                    |  |  |  |  |

| 4. TITLE AND SUBTITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                     |                              |                   | 5a. CONTRACT                                | NUMBER             |  |  |  |  |

| High-Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Scalable Base-4 Fas                                 | st Fourier Transfor          | m Mapping         | 5b. GRANT NUM                               | 1BER               |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |                              |                   | 5c. PROGRAM E                               | LEMENT NUMBER      |  |  |  |  |

| 6. AUTHOR(S)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                     |                              |                   | 5d. PROJECT NU                              | JMBER              |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |                              |                   | 5e. TASK NUMBER                             |                    |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |                              |                   | 5f. WORK UNIT NUMBER                        |                    |  |  |  |  |

| 7. PERFORMING ORGANI<br><b>Centar</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ZATION NAME(S) AND AE                               | DDRESS(ES)                   |                   | 8. PERFORMING ORGANIZATION<br>REPORT NUMBER |                    |  |  |  |  |

| 9. SPONSORING/MONITO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RING AGENCY NAME(S) A                               | ND ADDRESS(ES)               |                   | 10. SPONSOR/MONITOR'S ACRONYM(S)            |                    |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |                              |                   | 11. SPONSOR/MONITOR'S REPORT<br>NUMBER(S)   |                    |  |  |  |  |

| 12. DISTRIBUTION/AVAII<br>Approved for publ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | LABILITY STATEMENT<br><b>ic release, distributi</b> | on unlimited                 |                   |                                             |                    |  |  |  |  |

| 13. SUPPLEMENTARY NOTES<br>See also ADM001694, HPEC-6-Vol 1 ESC-TR-2003-081; High Performance Embedded Computing<br>(HPEC) Workshop (7th)., The original document contains color images.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                     |                              |                   |                                             |                    |  |  |  |  |

| 14. ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                     |                              |                   |                                             |                    |  |  |  |  |

| 15. SUBJECT TERMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                     |                              |                   |                                             |                    |  |  |  |  |

| 16. SECURITY CLASSIFIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ATION OF:                                           |                              | 17. LIMITATION OF | 18. NUMBER                                  | 19a. NAME OF       |  |  |  |  |

| a. REPORT<br>unclassified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | b. ABSTRACT<br>unclassified                         | c. THIS PAGE<br>unclassified | ABSTRACT<br>UU    | OF PAGES <b>28</b>                          | RESPONSIBLE PERSON |  |  |  |  |

| Standard Form | 298  | (Rev.    | 8-98)  |

|---------------|------|----------|--------|

| Prescribed b  | y AN | SI Std 2 | Z39-18 |

and  $C_B$  describes a radix-4 decimation in time butterfly.

By comparing (4) with (1), the computational advantages of the manipulation leading to the FFT algorithm form (4) for base-4 designs are readily evident. In (4) the matrix products  $C_{M1}X$  and  $C_{M2}Y^{t}$  involve only exchanges of real and imaginary parts plus additions because the elements of  $C_{M1}$  and  $C_{M2}$  contain only  $\pm 1$  or  $\pm j$ , whereas the product CX in (1) requires complex multiplications. Also, the size of the coefficient matrix  $W_{M}$  in (4) is  $(N/b) \times (N/b)$  vs. the  $N \times N$  size of C in (1); consequently the number of overall direct multiplications in (4) is reduced by a factor of x16 compared to the direct form (1) on which past systolic FFT implementations are based. Note that distribution of the elements in  $C_{M1}$  and  $C_{M2}$  does not impose significant bandwidth requirements because full complex numbers are not used.

The overall processing for an *M* point FFT is done using the factorization  $M=N_1N_2$ , followed by a series of "row/column" 1-D FFTs on  $N_1$  and  $N_2$ . Each of these 1-D FFTs is performed by a secondary factorization into 2-D FFTs according to (4) and again using a "row/column" approach. The first equation in (4) is equivalent to performing a "column" FFT and the second equation is equivalent to performing a "row" FFT. In between there is a "twiddle factor" multiplication by the  $W^p$  in  $W_M$  (3). Because both the row and column FFTs in the secondary factorization (4) are broken down entirely into sets of 4-point DFTs, they can be done without complex multiplications. Also, the usual matrix transpose in between column and row DFTs is not necessary.

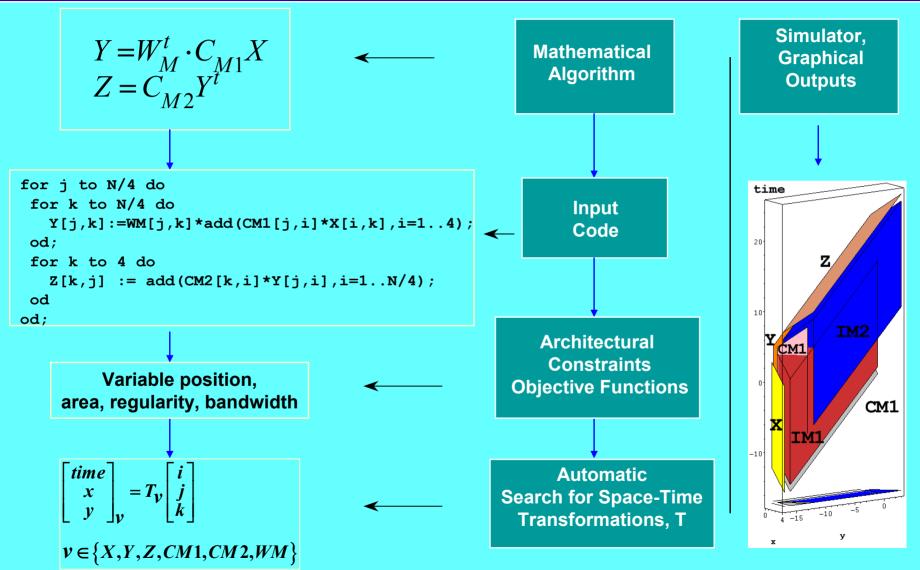

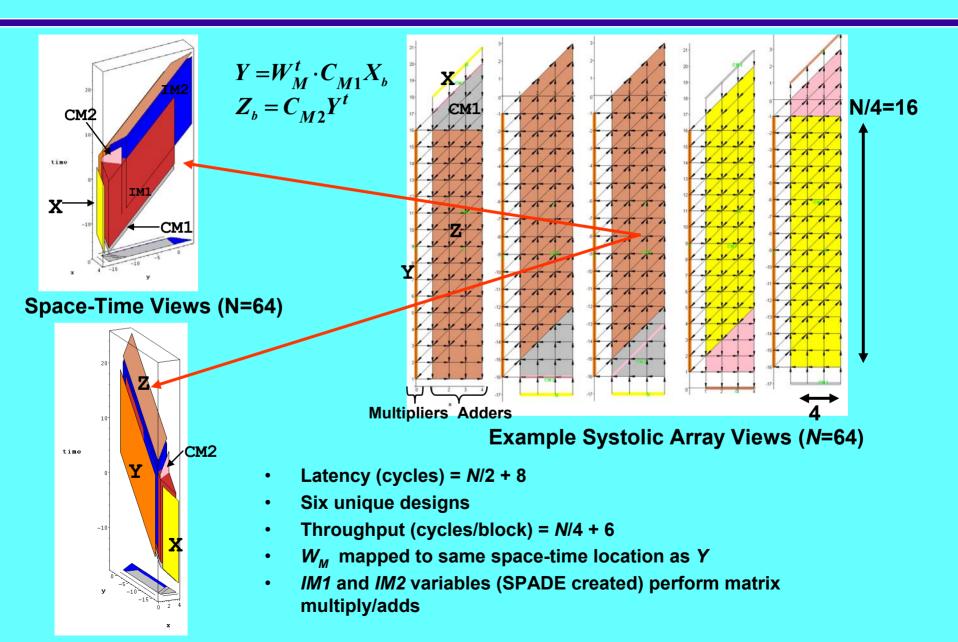

A systolic array architecture mapping was performed using the mathematical formulation (4) as input to the mapping tool SPADE [2]. Behavioral simulations of this architecture using a register transfer level simulator verify its operation. Performance estimates of the FFT computation times are shown in Table 1 for a variety of transform sizes.

| Size (points) | T (cycles/DFT) | T (µsec/DFT) | Multipliers | Adders |

|---------------|----------------|--------------|-------------|--------|

| 256           | 210            | 1.0          | 4           | 32     |

| 512           | 274            | 1.3          | 8           | 64     |

| 1024          | 658            | 3.1          | 8           | 64     |

| 2048          | 914            | 4.3          | 16          | 128    |

| 4096          | 2322           | 10.8         | 16          | 128    |

| 8192          | 3346           | 15.6         | 32          | 256    |

Table 1. Performance estimates and arithmetic requirements for various transform sizes (16-bits fixed point) based on a partially populated Altera Stratix EP1S60 "medium speed grade" FPGA chip. In this table "T" is the throughput. (Computational latency for each transform size above is approximately equal to the inverse of the throughput time/DFT).

Although Table 1 only shows transforms that are powers of two, the base-4 FFT lengths are not limited to powers of two or four. For example, the base-4 FFT is capable of 29 transform lengths from 256 to 65,536 *vs.* only 5 possible lengths for a radix-4 pipelined FFT.

The single biggest drawback to past use of systolic arrays has been the substantial arithmetic hardware that is normally required because systolic approaches use a number of complex multipliers equal to the size of the transform. Thus, a 1024-point DFT would require 1024 complex multipliers, compared to the 8 multipliers shown in Table 1 for the base-4 FFT.

Traditional "pipelined" FFTs, although computationally efficient, are difficult to map into VLSI because in general each butterfly, delay/commutator, and twiddle factor ROM has a different circuit design and/or its operation varies from stage to stage. Also, the butterflies do not usually work with 100% resource efficiency, the designs are limited to transform lengths that are powers of two or four, they are architecturally suited only for a 1-D DFT or 2-D DFT but not both, and it is difficult to build scalable designs because of their irregularity and large granularity. Finally, the latency (time to do the first DFT in a series) is low because the pipeline has to be "filled" first. Alternatively, the base-4 FFT architecture is comprised of simple, identical, small processing elements (PEs), arranged in regular arrays with each PE operating at near 100% efficiency. Performance figures in Table 1 compare very well to larger custom ASIC designs and recent FPGA implementations.

- C. C. W. Hui, T. J. Ding, J. V. McCanny, and R. F. Woods, "A New FFT Architecture and Chip Design for Motion Compensation based on Phase Correlation," Proc. Int. Conf. on Application Specific Systems, Architectures and Processors (ASAP 96), pp. 83-92.

- [2] J. Greg Nash, "Hardware Efficient Base-4 Systolic Architecture for Computing the Discrete Fourier Transform," Proc. 2002 IEEE Workshop on Signal Processing Systems (SIPS'02), pp. 87-92.

### High Performance Scalable Base-4 Fast Fourier Transform Mapping

Greg Nash Centar

2003 High Performance Embedded Computing Workshop

www.centar.net

### Outline

- Base-4 transformation for calculating DFT

- Mapping methodology

- Direct form DFT architecture

- FFT architecture

- Performance

#### **Discreet Fourier Transform**

| • | Mathematical form:                        |   |   |         | Ζ               | [k]                                |                     | $\sum_{n=1}^{N}$    | X[                    | n]                  |                     | (2π                   | τ / N)                | )( <i>k</i> -1       | 1)( <i>n</i> -       |                      | <i>k</i> =                       | = 1,            | 2                                        | N |

|---|-------------------------------------------|---|---|---------|-----------------|------------------------------------|---------------------|---------------------|-----------------------|---------------------|---------------------|-----------------------|-----------------------|----------------------|----------------------|----------------------|----------------------------------|-----------------|------------------------------------------|---|

|   |                                           |   |   | [1<br>] | 1<br>W          | 1<br>w <sup>2</sup>                | 1<br>W <sup>3</sup> | 1<br>W <sup>4</sup> | 1<br>w <sup>5</sup>   | 1<br>W <sup>6</sup> | 1<br>w <sup>7</sup> | 1<br>W <sup>8</sup>   | 1<br>W <sup>9</sup>   | 1<br>w <sup>10</sup> | 1<br>w <sup>11</sup> | 1<br>w <sup>12</sup> | 1<br>w <sup>13</sup>             |                 | 1<br>w <sup>15</sup>                     |   |

|   |                                           |   |   |         |                 | w <sup>4</sup><br>w <sup>6</sup>   |                     |                     |                       |                     |                     |                       |                       |                      |                      |                      |                                  |                 |                                          |   |

|   |                                           |   |   |         |                 | w <sup>8</sup><br>w <sup>10</sup>  |                     |                     |                       |                     |                     |                       |                       |                      |                      |                      |                                  |                 |                                          |   |

| • | Matrix form <i>Z=CX</i> : ( <i>N</i> =16) | Ζ | = |         |                 | w <sup>12</sup><br>w <sup>14</sup> | w <sup>5</sup>      | w <sup>12</sup>     | <i>w</i> <sup>3</sup> | w <sup>10</sup>     | W                   | w <sup>8</sup>        | w <sup>15</sup>       | w <sup>6</sup>       | w <sup>13</sup>      | $W^4$                | w <sup>11</sup>                  | $W^2$           | w <sup>9</sup>                           | X |

|   |                                           |   |   | 1       |                 | $w^2$                              | w <sup>11</sup>     | $W^4$               | w <sup>13</sup>       | w <sup>6</sup>      |                     | <i>w</i> <sup>8</sup> | W                     | w <sup>10</sup>      | w <sup>3</sup>       | w <sup>12</sup>      | w <sup>5</sup>                   | w <sup>14</sup> |                                          |   |

|   |                                           |   |   | 1       |                 | w <sup>6</sup>                     | W                   | w <sup>12</sup>     | $w^7$                 | $w^2$               |                     | w <sup>8</sup>        | <i>w</i> <sup>3</sup> | w <sup>14</sup>      | w <sup>9</sup>       | $W^4$                | w <sup>15</sup>                  | w <sup>10</sup> | w <sup>5</sup>                           |   |

|   |                                           |   |   | 1       | w <sup>13</sup> | w <sup>8</sup><br>w <sup>10</sup>  | $w^7$               | $W^4$               | W                     | w <sup>14</sup>     | w <sup>11</sup>     | w <sup>8</sup>        | w <sup>5</sup>        | $w^2$                | w <sup>15</sup>      | w <sup>12</sup>      |                                  | w <sup>6</sup>  | $W^4$<br>$W^3$                           |   |

|   |                                           |   |   |         |                 | w <sup>12</sup><br>w <sup>14</sup> |                     |                     |                       |                     |                     |                       |                       |                      |                      |                      | w <sup>6</sup><br>w <sup>3</sup> | $w^4$<br>$w^2$  | $\begin{bmatrix} W^2 \\ W \end{bmatrix}$ |   |

• Multiplications =  $N^2$

$W = e^{-2\pi I (n-1)(k-1)/N}$

Find reordering permutation P

$$X_{b=4} = P \begin{bmatrix} X_1 \\ X_2 \\ X_3 \\ X_4 \\ X_5 \\ \vdots \\ X_{N-3} \\ X_{N-2} \\ X_{N-1} \\ X_N \end{bmatrix} = \begin{bmatrix} X_1 \\ X_{1+N/4} \\ X_{1+N/2} \\ X_{1+3N/4} \\ X_2 \\ \vdots \\ \vdots \\ X_{N/4} \\ X_{N/2} \\ X_{3N/4} \\ X_N \end{bmatrix}, and \quad Z_{b=4} = P \ Z$$

DFT matrix equation becomes

$$X_b = C_b Z_b$$

where

$$C_b = PCP^t$$

#### **Base-4 Coefficient Matrix**

$$d1 = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix}; \quad d2 = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & -I & 0 & 0 \\ 0 & 0 & -1 & 0 \\ 0 & 0 & 0 & I \end{bmatrix}; \\ d3 = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & -I & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & -1 \end{bmatrix}; \\ d4 = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & -I & 0 & 0 \\ 0 & 0 & -I & 0 \\ 0 & 0 & 0 & -I \end{bmatrix};$$

### Base-4 DFT Matrix Equation (Compact Form)

• Form for *N*=16

$$Y = \begin{bmatrix} 1 & 1 & 1 & 1 & 1 \\ 1 & W & W^2 & W^3 \\ 1 & W^2 & W^4 & W^6 \\ 1 & W^3 & W^6 & W^9 \end{bmatrix} \bullet \begin{pmatrix} \begin{bmatrix} 1 & 1 & 1 & 1 \\ 1 & -I & 1 & I \\ 1 & -I & 1 & -1 \\ 1 & I & 1 & -I \end{bmatrix} \begin{bmatrix} x_1 & x_2 & x_3 & x_4 \\ x_5 & x_6 & x_7 & x_8 \\ x_9 & x_{10} & x_{11} & x_{12} \\ x_{13} & x_{14} & x_{15} & x_{16} \end{bmatrix} \\ \begin{bmatrix} z_1 & z_2 & z_3 & z_4 \\ z_5 & z_6 & z_7 & z_8 \\ z_9 & z_{10} & z_{11} & z_{12} \\ z_{13} & z_{14} & z_{15} & z_{16} \end{bmatrix} = \begin{bmatrix} 1 & 1 & 1 & 1 \\ 1 & -I & 1 & -I \\ 1 & I & 1 & -I \end{bmatrix} Y^t$$

$$\begin{array}{c} \text{``erement by element} \\ \text{multiply} \end{array}$$

General Form

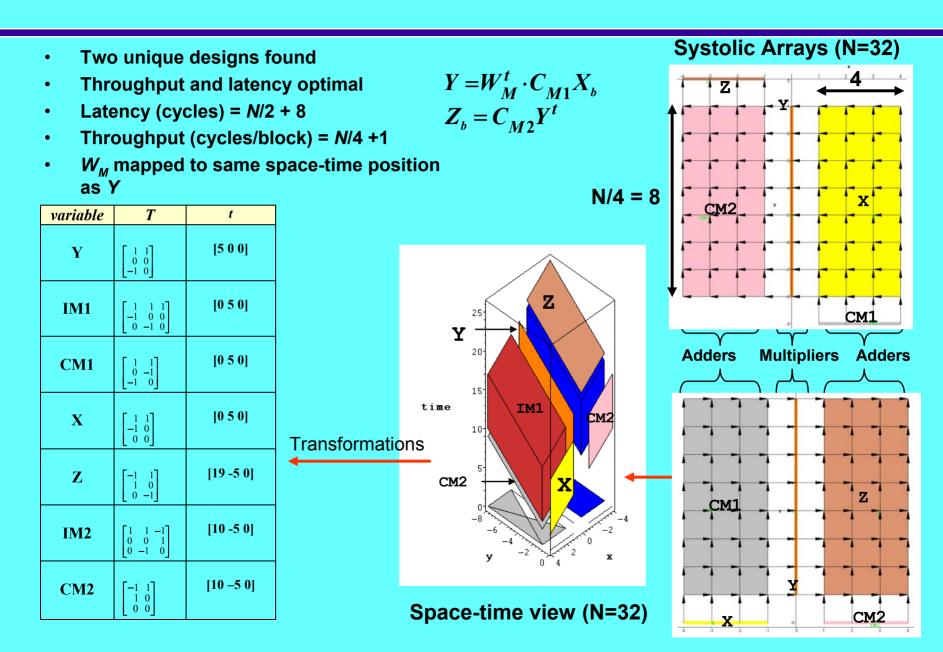

$$Y = W_{M}^{t} \cdot C_{M1} X_{b}$$

$$Z_{b} = C_{M2} Y^{t}$$

$$Z_{b} = \begin{bmatrix} Z_{1} & Z_{N/4} \\ Z_{1+N/4} & \cdots & Z_{N/2} \\ Z_{1+N/2} & Z_{3N/4} \\ Z_{1+3N/4} & Z_{N} \end{bmatrix}, \quad X_{b} = \begin{bmatrix} X_{1} & X_{N/4} \\ X_{1+N/4} & \cdots & X_{N/2} \\ X_{1+N/2} & X_{3N/4} \\ X_{1+3N/4} & X_{N} \end{bmatrix}$$

#### **Base-4 DFT Equation Characteristics**

Coefficient matrices represent series of 4-point transforms:

$$C_{M1} = \begin{bmatrix} C_B^t \mid C_B^t \mid ... \end{bmatrix}^t$$

$$C_{M2} = \begin{bmatrix} C_B \mid C_B \mid ... \end{bmatrix} \text{ where } C_B = \begin{bmatrix} 1 & -1 & -1 & 1 \\ 1 & -1 & -1 & I \\ 1 & I & -1 & I \end{bmatrix}$$

- ⇒ Takes advantage of reduced arithmetic with radix r = 4 butterfly, but transform length not limited to  $N = r^m$

- $\Rightarrow$  Transform length must be divisible by 16

- $C_{M1}$  and  $C_{M2}$  contain only elements from the set  $\{1,-1,-I,I\}$  $\Rightarrow C_{M1} X$  and  $C_{M2} Y^t$  only involve complex additions

- Twiddle factor matrix  $W_M$  is of size  $N/4 \ge N/4$  rather than  $N \ge N$

$\Rightarrow$  x16 fewer multiplies than original DFT equation (Z=CX)

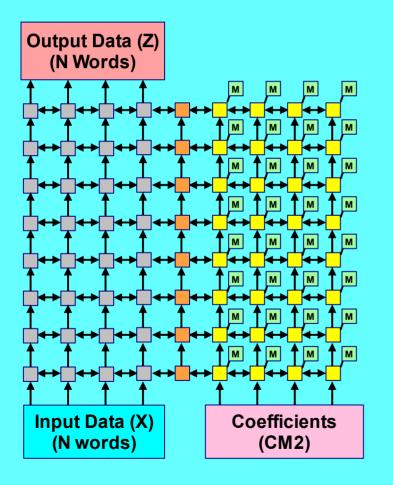

### Systolic Array Example: Matrix Multiply

• Algorithm:

$$c[i,j] = \sum_{k=1}^{N} d[i,k] * e[k,j] \quad for \quad 1 \le i, j,k \le N$$

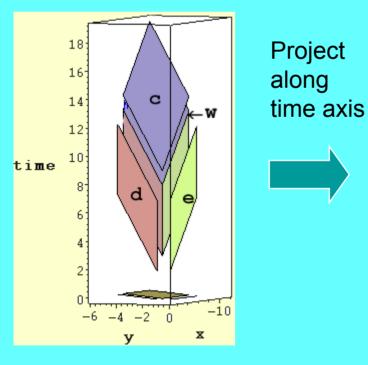

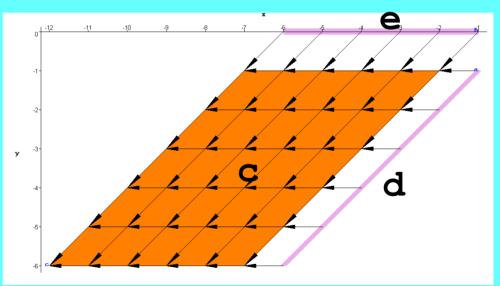

Space-time mapping: computations at {i,j,k} "mapped" to indices {time,x,y}

"Space-Time" View

<u>Systolic Array</u>: Each intersection point corresponds to a "processing element" (PE) that receives data from its neighbors, does a multiply-add, and passes the result to adjacent PEs, once per time cycle.

# Find Systolic Architecture Using SPADE

<sup>†</sup>Symbolic Parallel Algorithm Development Environment

#### **SPADE** Functionality

• SPADE accepts input statements of the affine form

$$\begin{aligned} x(A_x I + a_x) & depends & on \quad y(B_y I + b_y) & for all \ I \in V(I) \\ e.g., x(2i, j+1) &\equiv x(\begin{bmatrix} 2 & 0 \\ 0 & 1 \end{bmatrix} \begin{bmatrix} i \\ j \end{bmatrix} + \begin{bmatrix} 0 \\ 1 \end{bmatrix}) \end{aligned}$$

- Where  $A_x, B_y/a_x, b_y$  are integer matrices/vectors, S is the dimension of the algorithm space and the "depends on" includes commutative and associative operators: *min, max,*  $\Sigma$ *,*  $\Pi$

- SPADE finds latency optimal systolic designs subject to constraints imposed by scheduling, localization, reindexing, and allocation

- Secondary objective functions used to select architectures are minimum area, maximum regularity and minimum network bandwidth

#### **Systolic Array Designs: Minimum Area**

### **Systolic Array Designs: Maximum Regularity**

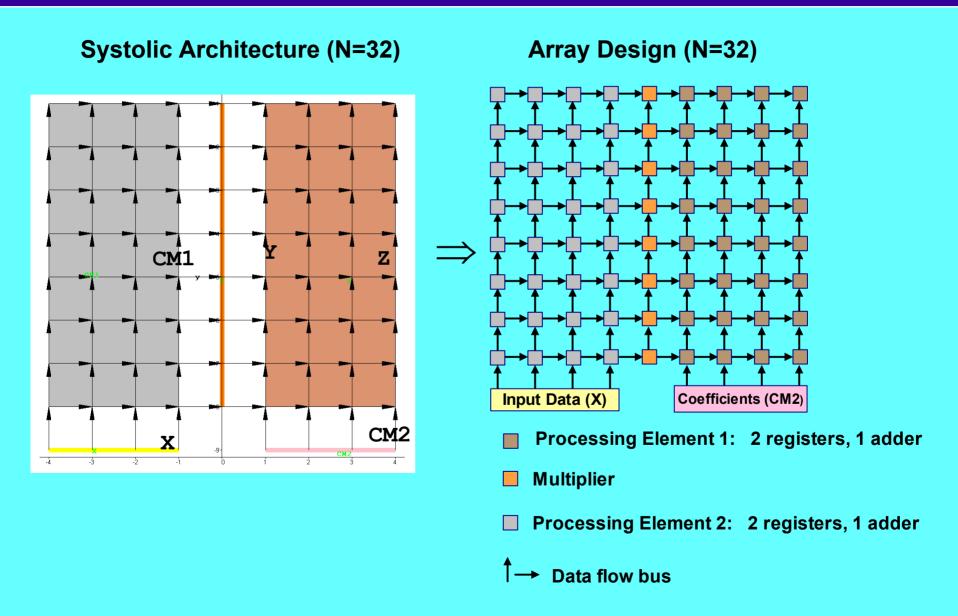

#### **Systolic Architecture to Array Design**

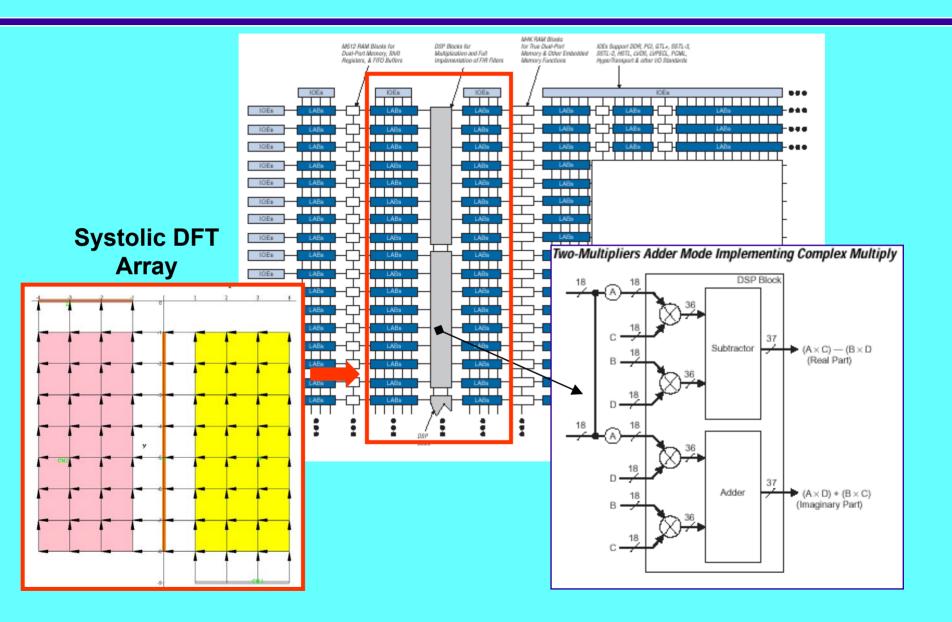

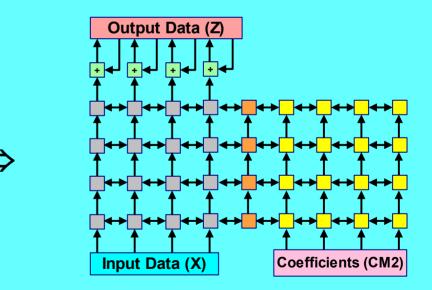

### **Altera Stratix FPGA: DFT Mapping**

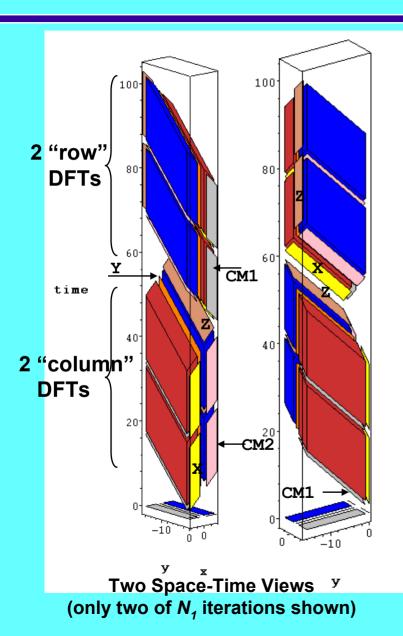

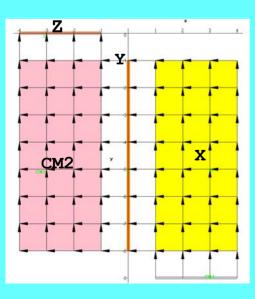

#### **1D FFT via Factorization**

- Factor  $N = N_1 * N_2$

- Creat a 2-D matrix with  $N_1$  rows by  $N_2$  columns, (assume  $N_1 > N_2$ ),

- Do  $N_2$  1-D "column" DFTs followed by  $N_1$  "row" DFTs:

$$Y = W_{N1} * X$$

$$Y' = W_{N} \bullet Y$$

$$Z = Y' * W_{N2}$$

- If  $N_1 \approx N_2$  then (linear) array size can be reduced from O( $N_1 N_2$ ) to O( $N_1$ ) with minimal effect on throughput:

- Cycles for *N*/4 array (no factorization) = *N*/4 + 1

- Cycles for  $N_1/4$  array =  $N_1(N_1/4 + 1) + N_1(N_1/4 + 1) + twiddle mult <math>\approx N/2$

- Can do 2-D DFT by not performing twiddle multiplication W<sub>N</sub>

- Use base-4 DFT mapping to do all row/column DFTs

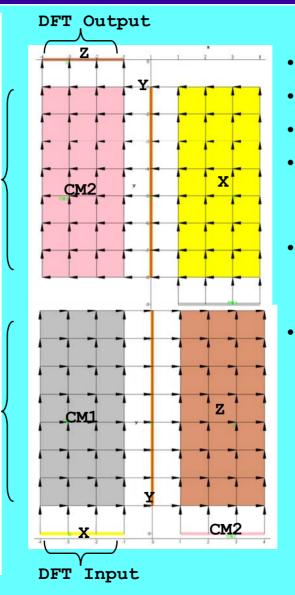

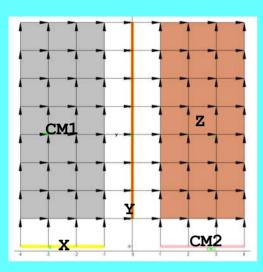

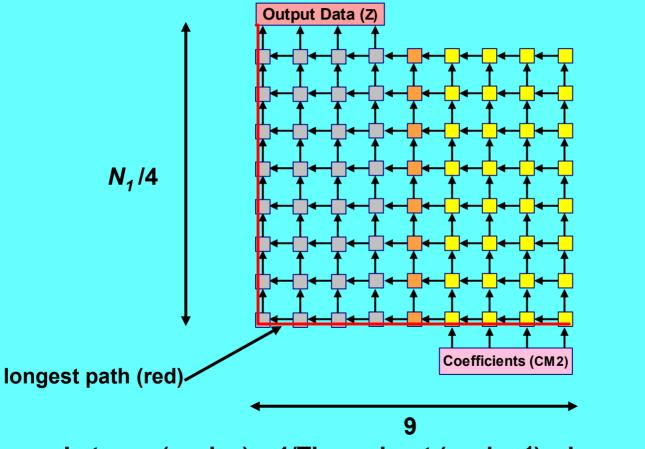

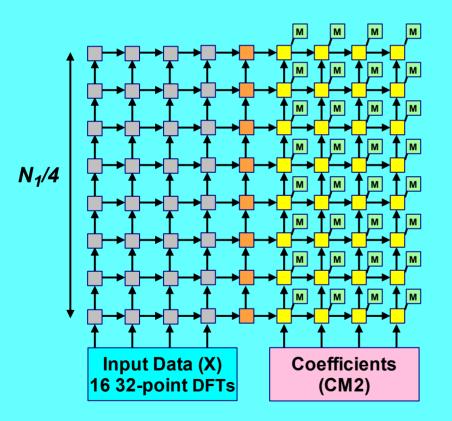

#### **Base-4 Factorization Architecture**

- *N* = 1024 points

- $N = N_1 * N_2$

- $N_1 = N_2 = 32$

- Uses both of the two optimal systolic designs

- Twiddle multiplications not shown

- Throughput/latency optimal except for interstage delay

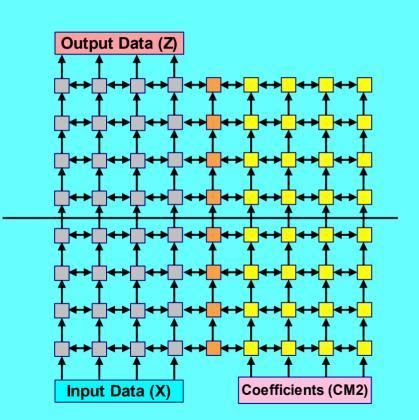

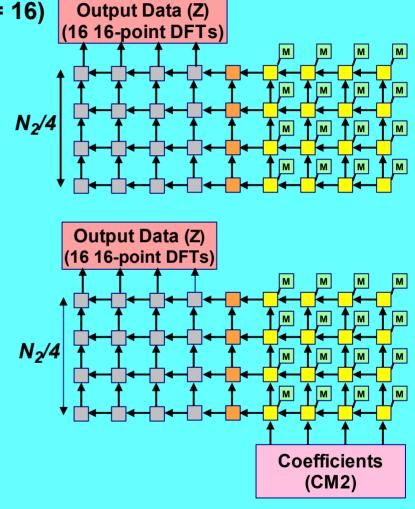

#### **Two DFT Architectures Combined**

- Shown for *N* = 1024 points

- $N = N_1 * N_2$

- $N_1 = N_2 = 32$

- M = 512 bits (16 bit word)

- Processing Element 1: 2 registers, 1 adder

- Memory

- Multiplier

- Processing Element 2: 2 registers, 1 adder

#### $4 \leftrightarrow$ Local data flow bus

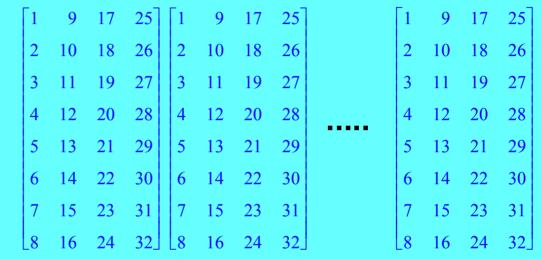

## 1<sup>st</sup> to 2<sup>nd</sup> Stage Data Formatting Problem (32 Point DFT)

• DFT data positions of 1<sup>st</sup> stage output sequences

• Desired data positions for input sequences to 2<sup>nd</sup> stage

### Interstage Data Formatting via "On-the-Fly" Permutations

#### New code with matrix rotation steps

#### New DFT first stage output sequences

| [1 | 9  | 17 | 25  | 2 | 10 | 18 | 26  | 3 | 11 | 19 | 27  | 25     | 1 | 9  | 17 |

|----|----|----|-----|---|----|----|-----|---|----|----|-----|--------|---|----|----|

| 2  | 10 | 18 | 26  | 3 | 11 | 19 | 27  | 4 | 12 | 20 | 28  | 26     | 2 | 10 | 18 |

| 3  | 11 | 19 | 27  | 4 | 12 | 20 | 28  | 5 | 13 | 21 | 29  | <br>27 | 3 | 11 | 19 |

| 4  | 12 | 20 | 28  | 5 | 13 | 21 | 29  | 6 | 14 | 22 | 30  | 28     | 4 | 12 | 20 |

| 5  | 13 | 21 | 29  | 6 | 14 | 22 | 30  | 7 | 15 | 23 | 31  | 29     | 5 | 13 | 21 |

| 6  | 14 | 22 | 30  | 7 | 15 | 23 | 31  | 8 | 16 | 24 | 32  | 30     | 6 | 14 | 22 |

| 7  | 15 | 23 | 31  | 8 | 16 | 24 | 32  | 1 | 9  | 17 | 25  | 31     | 7 | 15 | 23 |

| _8 | 16 | 24 | 32_ | 1 | 9  | 17 | 25_ | 2 | 10 | 18 | 26_ | 32     | 8 | 16 | 24 |

| FFT  | Throughput   | Throughput |                    |        |

|------|--------------|------------|--------------------|--------|

| Size | (cycles/DFT) | (µsec/DFT) | <b>Multipliers</b> | Adders |

| 256  | 210          | 1.0        | 4                  | 32     |

| 512  | 274          | 1.3        | 8                  | 64     |

| 1024 | 671          | 3.1        | 8                  | 64     |

| 2048 | 914          | 4.3        | 16                 | 128    |

| 4096 | 2322         | 10.8       | 16                 | 128    |

| 8192 | 3346         | 15.6       | 32                 | 256    |

#### Based on:

- Register transfer level behavioral simulation of 1024 point DFT

- Partially populated layout

- Timing analysis using Altera Stratix EP1S60 FPGA chip

- 16 bit fixed-point word length

#### Latency

Base-4 FFT pipeline depth is nominally N<sub>1</sub>/4+ 9 << N</li>

Latency (cycles) ≅ 1/Throughput (cycles<sup>-1</sup>) when complete X available

### **Partitioning to Scale Computations to Application**

#### Use an array "section" to perform partially processed result

- Partial results accumulated at output

- Memory needed scales with partition size

#### **Fully Parallel Array**

**Partitioned Array**

- Example: 512-point FFT ( $N_1 = 32, N_2 = 16$ )

- On-the-fly permutations for correct data placement

Columns: Compute 16 32-point DFTs

**Rows: Compute 2 sets of 16 16-point DFTs**

| Resource             | Logic<br>Cells | Flip<br>flops | M512 | M4K | DSP<br>Blocks | Global<br>Clocks |

|----------------------|----------------|---------------|------|-----|---------------|------------------|

| Usage                | 14717          | 9200          | 64   | 32  | 8             | 1                |

| Percent<br>Resources | 26             | 15            | 11   | 11  | 44            | 17               |

<sup>†</sup>Altera Stratix EP1S60F1508C6 FPGA chip (16 bit fixed point)

- High performance 1-D and 2-D DFTs

- Based on latency and throughput optimal parallel circuits

- Transform size not restricted to  $N = r^m$

- Latency  $\approx$  1/throughput when entire input block available

- Architecture is scaleable and easily parameterized

- Design is simple, regular, local and synchronous

- Fast convolutions naturally supported

- Natural partitioning strategies exist

- Pseudo-linear architecture good fit to latest generation of FPGA chips

- "Automatic Generation of Systolic Array Designs For Reconfigurable Computing", Proc. Engineering of Reconfigurable Systems and Algorithms (ERSA '02), International Multiconference in Computer Science, Las Vegas, Nevada, June 24, 2002.

- General description of SPADE

- Faddeev algorithm (Find CX+D, given AX=B, X is unknown)

- Constraint Directed CAD Tool For Automatic Latency-Optimal Implementations, SPIE ITCom 2002, Boston, Massachussetts, July 29-August 2, 2002.

- Use of constraints as a filter of systolic designs

- 2-D Discreet Fourier transforms using base-4 architecture