### **UC Riverside**

## **UC Riverside Electronic Theses and Dissertations**

#### **Title**

High Performance Vertex-Centric Graph Analytics on GPUs

#### **Permalink**

https://escholarship.org/uc/item/26g8702n

#### **Author**

Khorasani, Farzad

#### **Publication Date**

2016

## **Copyright Information**

This work is made available under the terms of a Creative Commons Attribution License, available at <a href="https://creativecommons.org/licenses/by/4.0/">https://creativecommons.org/licenses/by/4.0/</a>

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA RIVERSIDE

High Performance Vertex-Centric Graph Analytics on GPUs

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Computer Science

by

Farzad Khorasani

December 2016

#### Dissertation Committee:

Dr. Rajiv Gupta, Chairperson

Dr. Laxmi N. Bhuyan

Dr. Zizhong Chen

Dr. Nael Abu-Ghazaleh

University of California, Riverside

#### Acknowledgments

This dissertation would not have been possible if it wasn't for the help of my advisor, my professors, friends and collaborators, and my family.

First, I would like to express my gratitude to my academic prophet, my advisor, Prof. Rajiv Gupta, for leading me through the hardships of this path. I have no doubt it was Dr. Gupta's trust in my abilities and his experience and guidance that made this dissertation possible. I consider myself a lucky person for the opportunity of working with Dr. Gupta. Thanks Dr. Gupta!

I would like to thank Dr. Bhuyan, for the collaboration and guidance during my research. I would like to thank my dissertation committee members Dr. Chen and Dr. Abu-Ghazaleh for their valuable feedback and support.

I would like to thank the members of our research group who were always willing to help me during these years: Kishore, Min, Changhui, Yan, Sai, Mehmet, Vineet, Amlan, Keval, Zack, Bo, and Bryan. I also extend my gratitude to all the teachers I have had throughout my life.

I would like to thank my family, my mother Soheila Bahadori, my father Parviz Khorasani, and my brother Roozbeh Khorasani for their help and support throughout my life. I would like to thank my wife Dänae G. Khorasani for her constant love and support.

Finally, I would like to acknowledge the support of National Science Foundation by providing grants CCF-0905509, CCF-0963996, CNS-1157377, CCF-1318103, CCF-1423108, and CCF-1524852 to UC Riverside.

To my parents and my brother for all the love and support, and to my wife  $D\ddot{a}nae$ .

#### ABSTRACT OF THE DISSERTATION

High Performance Vertex-Centric Graph Analytics on GPUs

by

#### Farzad Khorasani

Doctor of Philosophy, Graduate Program in Computer Science University of California, Riverside, December 2016 Dr. Rajiv Gupta, Chairperson

Massive parallel processing power of GPU's presents an attractive opportunity for accelerating large scale vertex-centric graph computations. However, the inherent irregularity and large sizes of real-world power law graphs creates many challenges. Lock-step execution by threads within a SIMD group restricts exploitable parallelism, the limited GPU's DRAM size restricts the sizes of graphs that can be offloaded to the GPU, and the limited inter-GPU communication bandwidth necessitates judicious use available bandwidth. This dissertation addresses all of these challenges.

We present Warp Segmentation that greatly enhances GPU device utilization by dynamically assigning appropriate number of SIMD threads to process a vertex while employing the compact CSR representation to maximize the graph size that can be held in GPU global memory. Prior works can either maximize graph sizes (e.g., VWC [34]) or device utilization (e.g., CuSha [42]). We scale graph processing over multiple GPUs via Vertex Refinement that dynamically collects and transfers only the updated boundary vertices leading to dramatically reduced amount of inter-GPU data transfer. Existing multi-GPU techniques (Medusa [94], TOTEM [24]) perform high degree of wasteful vertex transfers.

Since processing all vertices at every iteration wastes much of GPU's computation power, we present a work-efficient solution that processes only those vertices during an iteration that were activated in the previous iteration. We employ an effective task expansion strategy that avoids intra-warp thread underutilization. For multi-GPU graph computation, we present *permissive partitioning* to dynamically balance load across GPUs. Also, as recording vertex activeness requires additional data structures, to manage the graph storage overhead, we introduce *vertex grouping* that enables trade-off between memory consumption and work efficiency.

Finally, to apply the proposed solutions to other irregular applications, we generalize our techniques and present *Collaborative Context Collection* (CCC) and *Collaborative Task Engagement* (CTE). CCC is a software/compiler technique to enhance the SIMD-efficiency in loops containing thread divergence. CTE abstracts away the complexities of a rather complicated technique using a CUDA C++ device side template library and balances load across threads within a SIMD group.

# Contents

| List of Figures |                 |                                                                 | X    |

|-----------------|-----------------|-----------------------------------------------------------------|------|

| Li              | st of           | Γables                                                          | xiii |

| 1               | $\mathbf{Intr}$ | oduction                                                        | 1    |

|                 | 1.1             | Dissertation Overview                                           | 3    |

|                 |                 | 1.1.1 Addressing the Warp Efficiency and Scalability Challenges | 4    |

|                 |                 | 1.1.2 Enabling Work Efficiency for the Vertex-Centric Model     | 5    |

|                 |                 | 1.1.3 Extending Techniques to Other GPU Applications            | 7    |

|                 | 1.2             | Dissertation Organization                                       | 9    |

| 2               | War             | o Efficiency and Scalability                                    | 10   |

|                 | 2.1             | Warp Efficiency via Warp Segmentation                           | 13   |

|                 |                 | 2.1.1 Motivating Study                                          | 14   |

|                 |                 | 2.1.2 Warp Segmentation                                         | 16   |

|                 | 2.2             | Graph Processing Framework for WS                               | 19   |

|                 |                 | 2.2.1 Core Processing Procedure                                 | 19   |

|                 |                 | 2.2.2 Framework Interface                                       | 22   |

|                 | 2.3             | Scaling via Vertex Refinement                                   | 23   |

|                 |                 | 2.3.1 Inefficiency of Existing Inter-GPU Communication          | 24   |

|                 |                 | 2.3.2 Data Structure Organization                               | 24   |

|                 |                 | 2.3.3 Vertex Refinement                                         | 27   |

|                 | 2.4             | Performance Evaluation                                          | 29   |

|                 |                 | 2.4.1 Warp Segmentation Performance Analysis                    | 29   |

|                 |                 | 2.4.2 Vertex Refinement Performance Analysis                    | 33   |

|                 | 2.5             | Summary                                                         | 38   |

| 3               | Ena             | oling Work-Efficiency                                           | 40   |

|                 | 3.1             | Data Structures for Work-Efficiency                             | 43   |

|                 |                 | 3.1.1 Recording Vertex Activeness using Bitmasks                | 45   |

|                 |                 | 3.1.2 Vertex Grouping                                           | 47   |

|                 | 3.2             | Warp Efficiency with Dynamic Thread Assignment                  | 49   |

|                 | 3.3             | Permissive Partitioning for Inter-GPU Load Balance              | 52   |

|    | 3.4   | KiTES and its Interface                                       | 55 |

|----|-------|---------------------------------------------------------------|----|

|    | 3.5   | Evaluation of Techniques                                      | 57 |

|    |       | 3.5.1 Single-GPU Performance Analysis                         | 57 |

|    |       | 3.5.2 Multi-GPU Performance Analysis                          | 32 |

|    | 3.6   |                                                               | 66 |

| 4  | Ger   | eralizing Techniques 6                                        | 67 |

|    | 4.1   | Collaborative Context Collection                              | 38 |

|    |       | 4.1.1 CCC Core Procedure                                      | 70 |

|    |       |                                                               | 76 |

|    |       | 4.1.3 CCC Optimizations                                       | 33 |

|    |       | 4.1.4 CCC Implementation                                      | 36 |

|    |       | 4.1.5 Experimental Evaluation                                 | 39 |

|    | 4.2   | Collaborative Task Engagement                                 | 97 |

|    |       |                                                               | 99 |

|    |       | 4.2.2 Collaborative Task Engagement                           | )4 |

|    |       | 4.2.3 Experimental Evaluation                                 | 13 |

|    |       | 4.2.4 Sensitivity Analysis: varying coarse-grained task sizes | 17 |

|    | 4.3   | Summary                                                       | [9 |

| 5  | Rel   | ted Work 12                                                   | 20 |

|    | 5.1   | Graph Processing on GPUs                                      | 20 |

|    | 5.2   | SIMD Thread Divergence                                        | 23 |

| 6  | Cor   | clusions and Future Work 12                                   | 28 |

|    | 6.1   | Contributions                                                 | 28 |

|    | 6.2   | Future Directions                                             | 30 |

| Bi | bliog | raphy 13                                                      | 2  |

# List of Figures

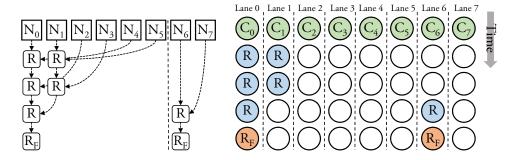

| 2.1          | An example graph with 5 vertices and 8 edges and its CSR representation             | 13 |

|--------------|-------------------------------------------------------------------------------------|----|

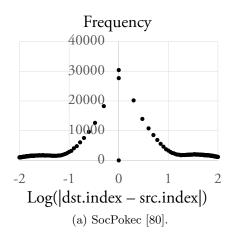

| 2.2          | Degree distribution for graph vertices                                              | 14 |

| 2.3          | An example: reduction in VWC with assumed warp size of 8 and first 6                |    |

|              | neighbors belonging to one vertex and last 2 belonging to another                   | 16 |

| 2.4          | Reduction using Warp Segmentation with the same scenario in Figure 2.3              | 17 |

| 2.5          | Discovering segment size and the index within segment by warp lanes for the         |    |

|              | graph in Figure 2.1. Warp size is assumed 8                                         | 17 |

| 2.6          | Framework's graph processing procedure pseudo-algorithm. Assumed warp               |    |

|              | size is 32. Shared memory pointers in the program code are declared with            |    |

|              | volatile qualifier                                                                  | 20 |

| 2.7          | User-specified structures and functions for SSWP                                    | 22 |

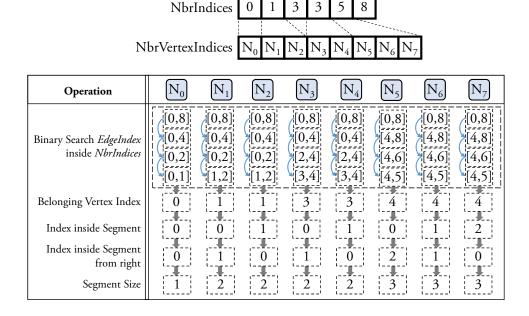

| 2.8          | Organization of data structures in multi-GPU processing                             | 25 |

| 2.9          | An example of online vertex refinement stages                                       | 28 |

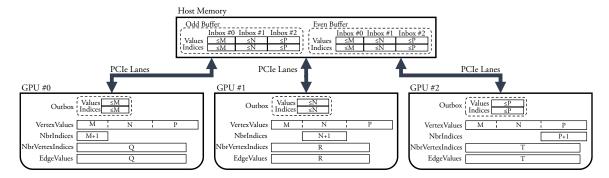

| 2.10         | Profiled average warp execution efficiency of Warp Segmentation compared            |    |

|              | to VWC's. SSSP is the benchmark                                                     | 32 |

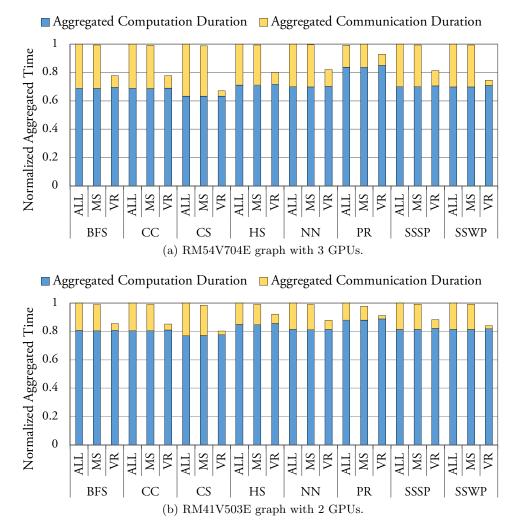

| 2.11         | Processing-time break down into computation time and communication time             |    |

|              | for the Vertex Refinement (VR) compared to ALL and MS. Computation                  |    |

|              | time is the total duration of kernel execution, and communication time is           |    |

|              | the total duration of inbox/outbox management plus inter-device memory              |    |

|              | copies. For each benchmark, the times are normalized with respect to the            |    |

|              | longest time. Note that this times cannot be used to infer the overall speedup      |    |

|              | due to asynchronicity of devices                                                    | 36 |

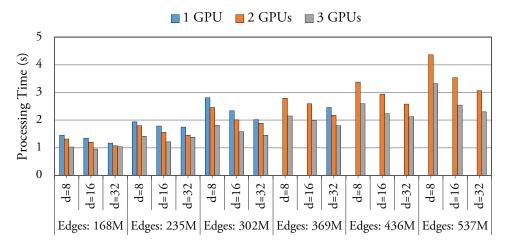

| 2.12         | The scalability of our framework over graphs with different number of edges         |    |

|              | and densities for SSSP benchmark. All the graphs are Rmat created with              |    |

|              | parameters $a = 0.45$ , $b = 0.25$ , and $c = 0.15$ . y axis is the processing time |    |

|              | (lower is better)                                                                   | 39 |

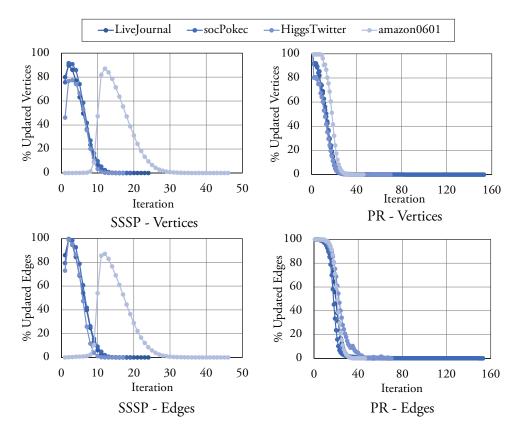

| 3.1          | The percentage of updated vertices and their connected edges across iterations.     | 41 |

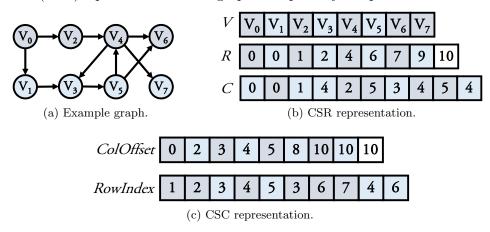

| $3.1 \\ 3.2$ | An example directed graph, its CSR representation, and the main compo-              | 41 |

| 0.2          | nents of its CSC representation                                                     | 44 |

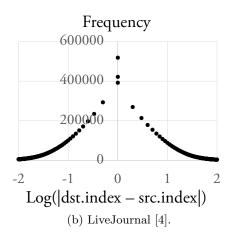

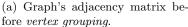

| 3.3          | The frequency distribution of differences between source and destination in-        | 44 |

| ა.ა          | dices of edges of 2 real-world graphs                                               | 47 |

|              | dices of edges of 2 rear-world graphs                                               | 41 |

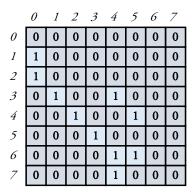

| 3.4  | The effect of vertex grouping with ratio 2 on the size of the CSC representa-   |     |

|------|---------------------------------------------------------------------------------|-----|

|      | tion of the example graph in Figure 3.2                                         | 48  |

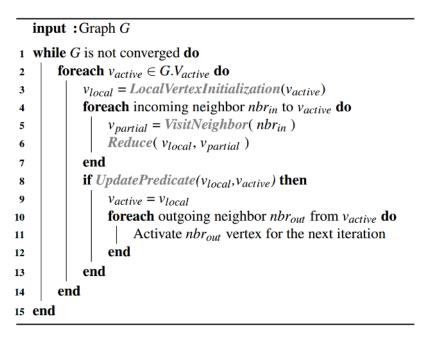

| 3.5  | Iterative Vertex-Centric Graph Processing                                       | 50  |

| 3.6  | A simplified example demonstrating our dynamic thread assignment strategy.      | 51  |

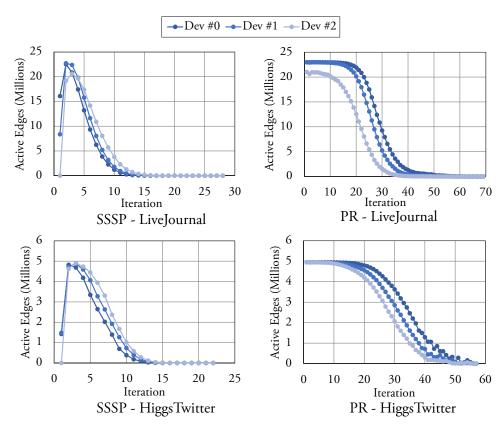

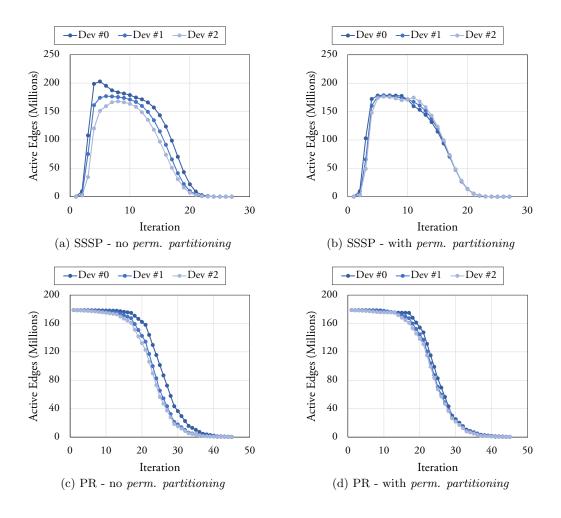

| 3.7  | The distribution of active edges on 3 GPUs across iterations in WS-VR [41].     | 53  |

| 3.8  | An example of <i>permissive partitioning</i> using the graph in Figure 3.2a and |     |

|      | the resulting data structures for each device                                   | 54  |

| 3.9  | A sample use of KiTES to execute user-defined SSSP with 3 GPUs                  | 56  |

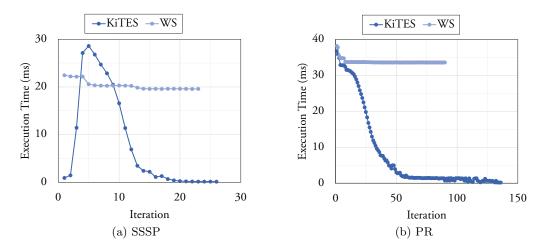

|      | Per-iteration kernel execution time for KiTES and Warp Segmentation (WS)        |     |

|      | for PR and SSSP on LiveJournal                                                  | 59  |

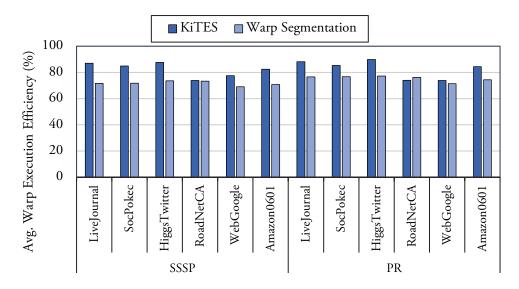

| 3.11 | Average warp execution efficiency profiled for KiTES and Warp Segmentation      |     |

|      | for SSSP and PR                                                                 | 60  |

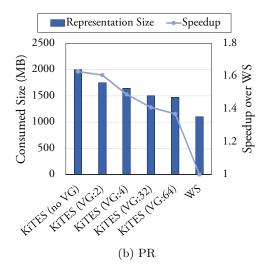

| 3.12 | The effect of vertex grouping on the GPU's DRAM consumption and the             |     |

|      |                                                                                 | 63  |

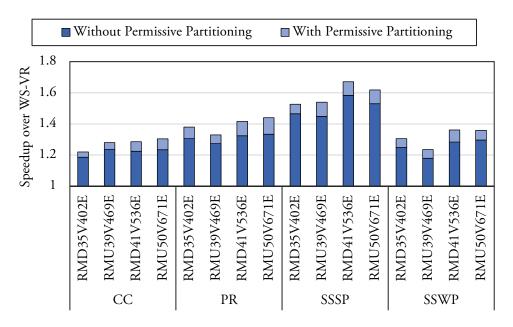

| 3.13 | The speedup of KiTES over WS-VR in multi-GPU graph processing with              |     |

| 0.10 | and without permissive partitioning.                                            | 64  |

| 3 14 | The effect of permissive partitioning on the distribution of active edges be-   | 0 1 |

| 0.11 | tween 3 GPUs across iterations. $RMD41V536E$ is the input graph                 | 65  |

|      | ween of the decrease recreations. Ith D41 / 000D is the input graph.            | 00  |

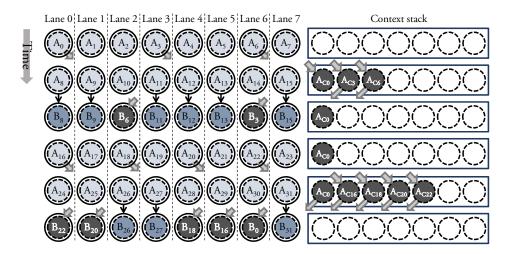

| 4.1  | An example: BFS graph processing visualization in CUDA [30]                     | 71  |

| 4.2  | Applying Collaborative Context Collection to the program in Figure 4.1 elim-    |     |

|      | inates warp execution inefficiency                                              | 73  |

| 4.3  | Applying CCC on the BFS CUDA kernel in Figure 4.1a                              | 74  |

| 4.4  | A grid-stride loop applied to the BFS CUDA kernel in order to make it           |     |

|      | accessible by CCC. The maximum theoretical occupancy is assumed 100%.           | 77  |

| 4.5  | An example demonstrating the transformation of a CUDA device function           |     |

|      | (BFS processing of a vertex's neighbors) with variable trip-count to a form     |     |

|      | accessible by CCC                                                               | 79  |

| 4.6  | An example demonstrating the transformation of a recursive CUDA device          |     |

|      |                                                                                 | 80  |

| 4.7  | Transformation of a loop with unknown trip-count (Cuckoo Hashing on GPU [3])    |     |

|      | by CCC                                                                          | 81  |

| 4.8  | Variation generation CUDA device function in Fractal Flame [77] from Iter-      |     |

|      | ated Function System (IFS) class                                                | 83  |

| 4.9  | SSSP graph processing CUDA kernel from [30] containing a coalesced global       |     |

|      | memory access to the costs buffer in the divergent path. We preserve the        |     |

|      | coalescence in CCC by excluding the memory access from the divergent path.      | 84  |

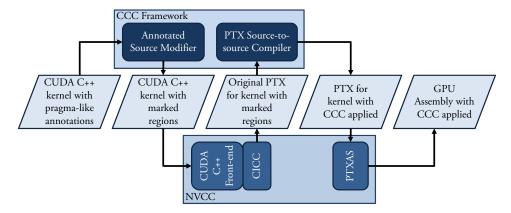

| 4.10 | 12 <sub>CCC</sub> Framework operates alongside NVCC                             | 86  |

|      | A PTX sample code inside the repetitive section and the resulted graph from     |     |

|      | connecting definition and usage of virtual registers                            | 88  |

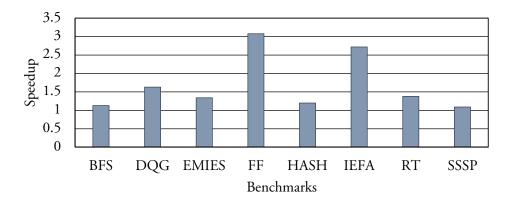

| 4.12 | The kernel execution speedup provided by CCC. For benchmarks with iter-         |     |

|      | ative GPU kernel launches (BFS and SSSP) the speedup is measured based          |     |

|      | on the aggregation of kernels                                                   | 92  |

|      |                                                                                 |     |

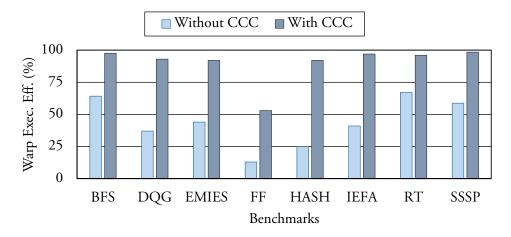

| 4.13 | Warp execution efficiency comparison for kernels with and without CCC. For                 |     |

|------|--------------------------------------------------------------------------------------------|-----|

|      | BFS and SSSP the warp execution efficiency is averaged across all the kernel               |     |

|      | launches.                                                                                  | 92  |

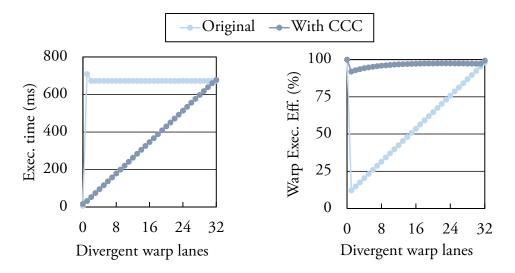

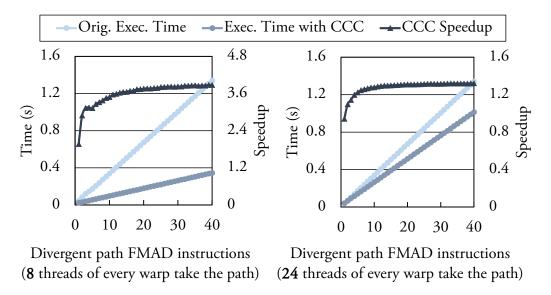

| 4.14 | CCC performance enhancement compared to the original divergent kernel                      |     |

|      | over different amount of intra-warp divergence (and hence workload imbal-                  |     |

|      | ance). The divergent path contains 20 FMAD operations                                      | 96  |

| 4.15 | Sensitivity of CCC against different execution paths lengths plotted for two               |     |

|      | different amounts of intra-warp divergence                                                 | 97  |

| 4.16 | An example — Sparse Matrix-Vector Multiplication (SpMV) CUDA kernel                        |     |

|      | with a CSR matrix using 1D decomposition. Intra-warp load imbalance in-                    |     |

|      | duces warp inefficiency and performance loss                                               | 100 |

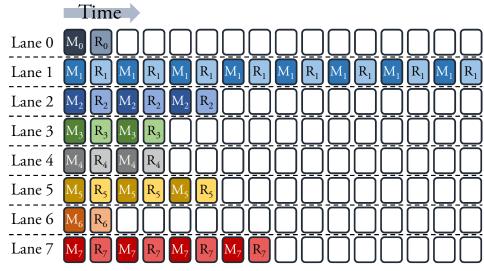

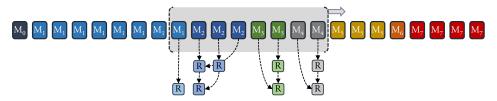

| 4.17 | Warp execution visualization in sub-warp decomposition (with width 4) for                  |     |

|      | the example in Figure 4.16. Sub-warp decomposition attempts to exploit                     |     |

|      | parallelism inside coarse-grained tasks                                                    | 102 |

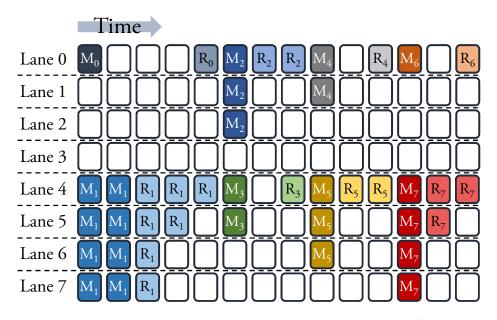

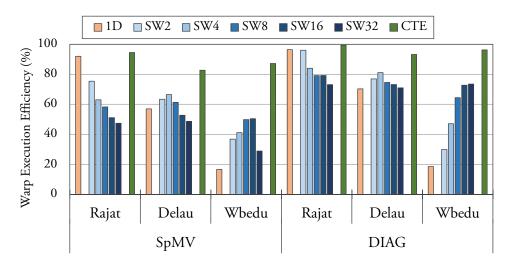

| 4.18 | Visualization of the SpMV CUDA kernel in Figure 4.16a after applying CTE.                  | 105 |

|      | GPU pseudo-code for CCC                                                                    | 107 |

| 4.20 | Expressing the nested pattern in Fig. 4.16a CUDA C++ kernel in CTE form                    |     |

|      | using our template library interface                                                       | 110 |

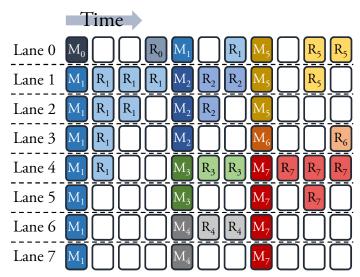

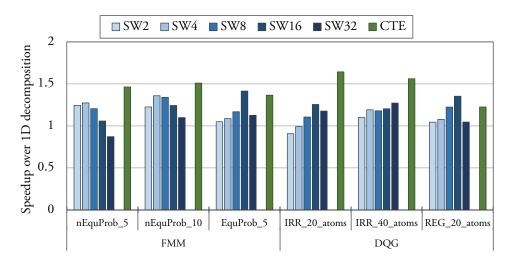

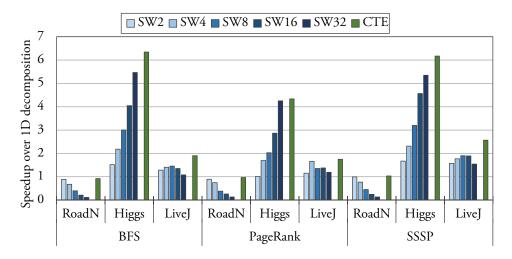

| 4.21 | The kernel execution speedup of CTE and sub-warp decomposition over 1D                     |     |

|      | decomposition for matrix operations on real-world matrices                                 | 114 |

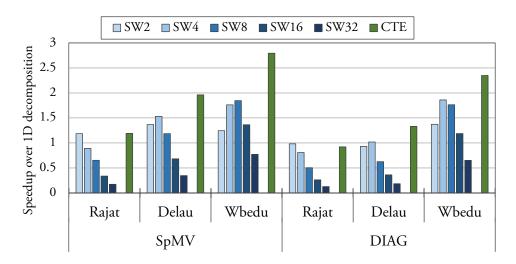

| 4.22 | Profiled warp execution efficiency of CTE, sub-warp decomposition, and 1D                  |     |

|      | decomposition kernels for experiments in Figure 4.21                                       | 115 |

| 4.23 | The kernel execution speedup of CTE and sub-warp decomposition over 1D                     |     |

|      | decomposition for Fast Multiple Method [43] and Dynamical Quadrature                       |     |

|      | Grids [54] with different inputs                                                           | 116 |

| 4.24 | The kernel execution speedup of CTE and sub-warp decomposition over 1D                     |     |

|      | decomposition for different graph applications and inputs                                  | 117 |

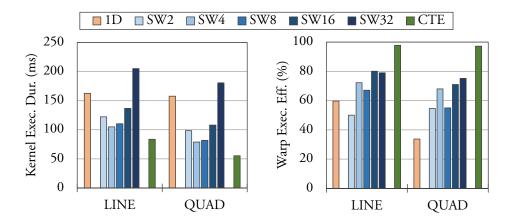

| 4.25 | Kernel execution duration (left plot) and Warp execution efficiency (right                 |     |

|      | plot) for decomposition methods when the task sizes vary linearly and quadrat-             |     |

|      | ically proportional to the lane index. Map and reduce portion of the fine-                 |     |

|      | grained tasks each contain 20 FMAD instructions. For the LINE scenario,                    |     |

|      | the coarse-grained task size is calculated with $4 \times laneID$ while for the QUAD       |     |

|      | scenario it is calculated with $\frac{laneID^2}{8}$ . Task sizes for the sub-warp decompo- |     |

|      | sition are calculated using their sub-warp index                                           | 118 |

# List of Tables

| 2.1 | The percentage of useful vertex data among all the transferred data when all the vertices (ALL) or the maximal subset of them (MS) are copied from one GPU to another. In this two-GPU configuration, the graph under the examination is an Rmat graph with approximately 40 million vertices and |     |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | 470 million edges                                                                                                                                                                                                                                                                                 | 25  |

| 2.2 | Graphs used in single-GPU experiments – across benchmarks the size ranges in MBytes for CSR and CW representations. Sizes exceeding GPU's global                                                                                                                                                  | 9.6 |

| 2.3 | memory capacity are bolded                                                                                                                                                                                                                                                                        | 30  |

|     | different graphs.                                                                                                                                                                                                                                                                                 | 31  |

| 2.4 | Speedup ranges of Warp Segmentation over VWC excluding data transfer times. Since both methods use CSR representation, their data transfer times                                                                                                                                                  | 2.5 |

| 0.5 | are equal                                                                                                                                                                                                                                                                                         | 32  |

| 2.5 | The speedup of Warp Segmentation over CuSha's [42] CW for <i>large</i> graphs. The shards reside inside the host pinned buffers (x means graph is small -                                                                                                                                         |     |

| 2.6 | fits in GPU memory)                                                                                                                                                                                                                                                                               | 33  |

| 2.0 | The shards reside inside the GPU's global memory (x means graph is large - requires host memory)                                                                                                                                                                                                  | 33  |

| 2.7 | Graphs for multi-GPU experiments: Top 6 graphs used in experiments with 3 GPUs; rest used with 2 GPUs.                                                                                                                                                                                            | 34  |

| 2.8 | The speed-up of VR over ALL and MS for three-GPU and two-GPU configurations.                                                                                                                                                                                                                      | 35  |

| 2.9 | The speedup of our framework when scaling to more GPUs: From 2 to 3                                                                                                                                                                                                                               |     |

|     | GPUs for the top 6 graphs; and From 2 to 3 and from 1 to 2 GPUs for the                                                                                                                                                                                                                           |     |

|     | rest of the graphs                                                                                                                                                                                                                                                                                | 38  |

| 3.1 | The memory required for CSR representation of four directed graphs [50] and                                                                                                                                                                                                                       |     |

| 2.2 | their additional CSC representation                                                                                                                                                                                                                                                               | 47  |

| 3.2 | Graphs for single-GPU evaluations and their representation sizes (in MB).                                                                                                                                                                                                                         | E 7 |

|     | For undirected graphs, CSC size is zero                                                                                                                                                                                                                                                           | 57  |

| 3.3 | Raw execution time (ms) of KiTES (KT) in comparison with Warp Segmen-          |     |

|-----|--------------------------------------------------------------------------------|-----|

|     | tation's (WS) [41] and Concatenated Windows's (CW) from CuSha [42] when        |     |

|     | all the graphs reside inside the GPU's global memory                           | 58  |

| 3.4 | Execution times (ms) of KiTES (KT), Warp Segmentation (WS) [41] and            |     |

|     | Concatenated Windows (CW) [42] including host to device copy time. While       |     |

|     | WS and KiTES can fit the graph inside the GPU, CuSha must hold graphs          |     |

|     | in host pinned memory                                                          | 61  |

| 3.5 | Execution time (ms) of KiTES (KT), Warp Segmentation (WS) [41] and             |     |

|     | Concatenated Windows (CW)[42] including host to device copy time. KiTES        |     |

|     | has to apply vertex grouping to fit the representation inside the GPU's DRAM.  | 62  |

| 3.6 | Graphs used for multi-GPU experiments: Top 4 graphs employed for exper-        |     |

|     | iments with 3 GPUs and bottom 4 graphs for experiments with 2 GPUs             | 63  |

| 3.7 | Speedup provided by KiTES over WS-VR [41]. Top 4 entries use 3 GPUs            |     |

|     | and bottom 4 entries use 2 GPUs                                                | 64  |

| 4.1 | The CCC overhead in terms of resource usage (per thread). Underlined entry     |     |

| 4.1 | results from spilling two excessive registers into local memory (L1 cache) via |     |

|     | -maxrregcount compiler option. The maximum theoretical occupancy is            |     |

|     | 100% in all cases                                                              | 94  |

| 4.2 | Kernel warp execution efficiency of CUDA applications exposed to different     | 01  |

|     | inputs with 1D and sub-warp decomposition methods. The efficiency of ker-      |     |

|     | nels not only varies from one sub-warp width to another (the best in each      |     |

|     |                                                                                | 103 |

|     | ,,                                                                             |     |

# Chapter 1

# Introduction

Graph analytics have become one of the critical members in the suite of infrastructures dealing with big data processing. The need for efficient large scale graph processing has grown due to the importance of applications involving graph mining and graph analytics. Iterative vertex-centric processing model is one of the most popular and a methodical yet straightforward approach to representing graph algorithms. It has been incorporated in software systems such as PowerGraph [27], GraphLab [53], GraphChi [47] and others. The designer only needs to focus on the interaction of a vertex with its neighbors during an iteration. The underlying system orchestrates the execution of the vertex-centric methods on graph vertices over multiple iterations until convergence.

The deployment of GPUs as general purpose accelerators that started a decade ago has now become mainstream. Today GPUs serve as an essential processing platform for speeding-up data parallel computations. GPUs contain thousands of execution units and sufficient memory bandwidth that makes them well-suited for graph applications requiring massive parallelism. However, using GPUs for efficient graph processing has remained a challenging open problem. Even though GPUs provide a massive amount of parallelism with the potential to outperform general purpose CPUs, the underlying architecture imposes restrictions and introduces challenges in processing irregular real-world power law graphs. Thus, the challenges this thesis seeks to address are as follows.

- Lock-step traversal of SIMD threads restricts exploitable parallelism on GPUs. The SIMD architecture demands repetitive processing patterns on regular data which is contrary to the irregular nature of real-world graphs. All the threads inside a SIMD group (i.e., all the warp lanes) execute the same instruction at any given time. The presence of conditionals – such as if-else code blocks – causes thread divergence because a conditional may evaluate to true for some warp lanes and false for other lanes. In this situation, the warp takes all the divergent paths, while disabling non-relevant lanes inside every path. That is, the warp scheduler fetches instructions for all the divergent paths while the execution stage is performed only for a number of threads that are active in the path. As a result, a portion of the available processing power goes unutilized for the duration of divergence, diminishing the SIMD execution benefits. On the other hand, real-world graphs usually exhibit an irregular degree distribution known as power-law in which a great portion of the vertices have a few neighbors and a small portion of the vertices have a very high number of neighbors. Previously introduced task decomposition schemes assign one [30] or a fixed number [34] of threads to process vertices; thus, the mismatch between static decomposition and unpredictable irregularity of the computation in graph processing leads to the problem of underutilization of GPUs and thus limits performance.

- Limited amount of available DRAM presents another challenge in processing of large graphs. High performance GPUs come in the form of discrete GPUs and are equipped with high bandwidth GDDR5 or HBM off-chip memories. However, available memories are fixed, limiting the maximum size of the graph that can be kept at the device side and efficiently processed by the GPU. Therefore, the applicability of solutions with high storage overhead such as CuSha [42] is limited. In addition, although there has been research on utilizing host memory as auxiliary storage [78] to hold a larger graph, the resulting unavoidable performance drop is large due to the comparatively low communication bandwidth between the host and the GPU device.

- Comparatively low inter-GPU bandwidth makes processing very large graphs over multiple GPUs a challenge. A natural approach for processing very large graphs that do not fit inside one GPU is to partition them and process the partitions using multiple GPUs. However, during this out-scaled processing of the graph computation over multiple GPUs, the devices have to communicate via PCIe links which have low transfer rates compared to the rate at which GPUs access their own DRAM. Addressing this challenge requires a carefully-designed inter-device communication scheme. However, multi-GPU graph processing frameworks such as TOTEM [24] and Medusa [94] suffer from redundant inter-GPU communication data which makes the PCIe links a major bottleneck that limits achievable performance.

In this thesis, we address above challenges in high performance vertex-centric graph analytics on GPUs. This dissertation develops a dynamic task decomposition scheme to overcome the SIMD efficiency problem in irregular graph processing, while maximizing the allowable graph size by employing space-efficient CSR representations. It further extends the techniques to eliminate computation redundancy, and generalizes them via template libraries and compiler techniques to be deployed easily in other GPU applications that exhibit similar issues.

#### 1.1 Dissertation Overview

The vast computing power of GPUs makes them an attractive platform for accelerating large scale data parallel computations such as popular graph processing applications. However, the inherent irregularity and large sizes of real-world power law graphs makes effective use of GPUs a major challenge. In this dissertation, we develop techniques based on CUDA platform that greatly enhance the performance and scalability of iterative vertexcentric graph processing on GPUs. In the vertex-centric model of graph computation, vertices update their value at every iteration using the vertex values seen at the other end of an edge. The computed values must be reduced to get the new vertex content. When

there is no change to the content of vertices at an iteration, the computation has converged, and the procedure terminates.

#### 1.1.1 Addressing the Warp Efficiency and Scalability Challenges

We introduce techniques for efficient scaling of iterative graph algorithms to larger graphs using multiple GPUs. The graphs are stored in the space-saving CSR form that allows processing large graphs. To overcome the SIMD execution inefficiency in existing CSR-based graph processing methods, we present Warp Segmentation, a novel technique that assigns appropriate number of warp threads to process vertices with irregular number of neighbors on-the-fly. To scale the graph processing over multiple GPUs, we introduce Vertex Refinement that collects and transfers only those vertices that are boundary and recently updated. Vertex Refinement maximizes the inter-device bandwidth utilization efficiency.

#### Warp Segmentation for Efficient Warp Execution

Real-world graphs often exhibit power-law degree distribution, i.e. the number of neighbors a vertex owns vary greatly from one vertex to another. This makes existing methods such as Virtual Warp Centric (VWC) [34] that statically assign a fixed number of threads to vertices vulnerable to the intra-SIMD underutilization. We present Warp Segmentation, a novel method that greatly improves intra-warp utilization by dynamically assigning appropriate number of SIMD threads to process vertices with irregular-sized neighbors while employing compact CSR representation to maximize the graph size that can be kept inside the GPU global memory. This is in contrast to prior vertex-centric methods such as CuSha [42] that use G-Shards and CW representations requiring up to 2.5x more memory than CSR in order to boost the SIMD efficiency. Warp Segmentation assigns a warp to process a group of vertices and let threads iterate over the expanded list of neighbors. When the set of neighbors for the vertices is viewed as expanded, each thread can visit a neighbor, and then reduce the computed value with other threads inside the SIMD group that have processed a neighbor belonging to the same vertex. Therefore, at every iteration

all the threads execute the compute function without underutilization, and participate in a parallel reduction with appropriate threads. As a result, warp utilization is increased and the processing time is reduced. Warp Segmentation delivers average speedups of 1.29x to 2.80x over VWC.

#### Vertex Refinement for Efficient Inter-GPU Communication

We further scale graph processing to make use of multiple GPUs while proposing Vertex Refinement to address the challenge of judiciously using the limited bandwidth available for transferring data between GPUs over the PCIe bus. Whereas existing multi-GPU techniques (Medusa [94] and TOTEM [24]) perform high degree of wasteful vertex transfers, Vertex Refinement picks out, packs, and transfers only the updated boundary vertices thus dramatically reducing inter-GPU data transfer volume. Vertex Refinement essentially works as a fused stream compaction. To perform it inside the same GPU kernel by warp threads efficiently, at the end of the computation, threads get assigned to vertices. Threads check vertices for updates, each producing a predicate. Using techniques such as intra-warp binary reduction and prefix sum, intra-warp data propagation using shuffle, and warp-aggregated atomics, threads with true predicate effectively write the updated vertex index and content into the outbox buffer. Our design achieves up to 2.71x performance improvement compared to inter-GPU vertex communication schemes used by other multi-GPU techniques (i.e., Medusa and TOTEM).

#### 1.1.2 Enabling Work Efficiency for the Vertex-Centric Model

The above vertex-centric solution lacks work-efficiency because, at the expense of being generic, it processes all vertices at every iteration. As a result GPU's SIMD power is wasted on processing inactive vertices that do not result in any change in vertex values. We remedy this issue by enabling work-efficiency when processing the graph on one or more GPUs. Our solution processes only those vertices that are activated in the previous iteration and hence their values are subject to change. Our experiments show that enabling work

efficiency enhances the performance of the procedure by up to 5.46x and 1.67x for single and multi-GPU configurations respectively over multiple algorithms and inputs. Below are the techniques used to overcome the challenges induced as the side effects of enabling work efficiency.

#### **Vertex Grouping**

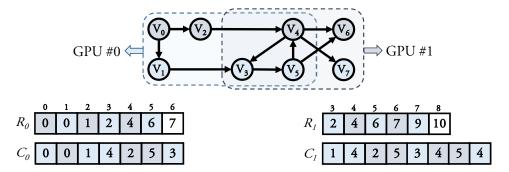

Enabling work efficiency for the vertex-centric model needs a mechanism to keep track of the propagation of updates which necessitates storing outgoing neighbors for the vertices of the graph alongside its incoming neighbors. In directed graphs, we utilize the CSC representation of the graph and store it alongside the CSR representation. However, this increases space required by 1.5x to 1.98x and thus limits the maximum allowable size of the graph that can be kept inside the GPU. To attenuate the impact of graph storage overhead on limited GPU DRAM, we introduce vertex grouping as a technique that enables trade-off between memory consumption and work efficiency in our solution. Vertex grouping groups consecutive vertices in the CSC representation and represents them as a single entity, therefore, if there are multiple edges between vertices in two groups, they are represented by only one edge between entities. This results in reduced space consumption but also lower work efficiency since activation of any one vertex in the group leads to processing of all the vertices in the group during the next iteration.

#### Warp Efficiency with Dynamic Thread Assignment

In Warp Segmentation, the list of accessed neighbors for the set of vertices assigned to the warp are placed consecutively in the memory. However, by enabling work efficiency, only the neighbors assigned to active vertices need to be visited requiring the warp to access disjoint locations inside the memory. For a SIMD-efficient kernel operation we require gathering of active neighbors and performing reduction on them. This is achieved by an effective task expansion strategy that avoids intra-warp thread underutilization. Threads iterate over a concatenated view of the neighbors for active vertices and utilize high per-

formance SIMD primitives such as intra-warp binary reduction and binary prefix sum to realize the actual neighbor locations and indices. Our experiments show that this method sustains a high warp execution efficiency and is 82.4% on average.

#### Permissive Partitioning for Inter-GPU Load Balancing

Without work efficiency, since all the vertices are processed at every iteration, static partitioning of the graph is enough to balance the load across devices. However, when work efficiency is enabled, the amount of load for each GPU dynamically changes with each iteration. In a given iteration, one GPU may end up with a great number of active vertices and edges while another GPU may have much lower number of active graph components. This creates inter-device load imbalance in graph processing. To deal with this problem, for multi-GPU graph computations, we present permissive partitioning to achieve a maximally balanced load across GPUs. Permissive partitioning allows partitions stored on GPUs to overlap as much as the GPUs' available DRAM allows. During the iterative graph computation, while GPUs are busy processing the graph, the host asynchronously calculates the approximate borders for the set of vertices that will lead to the best load balance across devices. Accordingly, the sets of vertices assigned to the GPUs change in the next iteration. This scheme enhances the overall multi-GPU graph processing performance by up to 20%.

#### 1.1.3 Extending Techniques to Other GPU Applications

GPU's SIMD architecture is a double-edged sword confronting parallel tasks with control flow divergence. On the one hand, it provides a high performance yet power-efficient platform to accelerate applications via massive parallelism; however, on the other hand, irregularities induce inefficiencies due to the warp's lockstep traversal of all diverging execution paths. This is true not only for graph applications, as we described earlier, but also for other programs that exhibit characteristics such as thread divergence or irregular load distribution. Sparse matrix vector multiplication (SpMV), parallel hashing, and ray

tracing are a few examples of such programs. We extend two SIMD efficiency enhancement techniques and make them applicable to GPU kernels beyond graph computation.

#### Collaborative Context Collection

We present a software (compiler) technique named Collaborative Context Collection (CCC) that increases the warp execution efficiency when faced with thread divergence incurred either by different intra-warp task assignment or by intra-warp load imbalance. CCC collects the relevant registers of divergent threads in a warp-specific stack allocated in fast shared memory, and restores them only when the perfect utilization of warp lanes becomes feasible. We propose code transformations to enable applicability of CCC to program segments such as recursive functions and loops with variable trip-count. We also introduce optimizations to reduce the cost of CCC and to avoid device occupancy limitation or memory divergence. We experiment with CCC on real-world applications, and analyze it under multiple scenarios using synthetic programs. CCC improves the warp execution efficiency of real-world benchmarks by up to 56% and achieves up to 3.08x speedup compared to the original programs.

#### Collaborative Task Engagement

Nested patterns are one of the most frequently occurring algorithmic themes in GPU applications where coarse-grained tasks are constituted from a number of fine-grained ones. However, efficient execution of irregular nested patterns, with coarse-grained tasks that substantially vary in size, has remained an open problem for the GPUs SIMT architecture. Existing methods, similar to what we observe in graph computation domain, rely on static task decomposition where one or a fixed number of threads inside the SIMD grouping (warp) carry out the fine-grained tasks. These approaches fail to provide portable performance across diversity of irregular inputs. Moreover, due to intra-warp load imbalance, they incur warp underutilization. We generalize our dynamic decomposition scheme for graph processing and introduce it as a software technique called *Collaborative Task En-*

gagement (CTE) that, unlike previous methods, achieves sustained high warp execution efficiencies across irregular inputs and provides portable performance. CTE assigns a group of coarse-grained tasks to the warp and allows threads inside the warp to carry out the expanded list of fine-grained tasks collaboratively. In multiple rounds, all the warp threads perform mapping portion of fine-grained tasks and participate in a reduction phase with appropriate lanes to reduce calculated values. This strategy avoids over-subscription or under-subscription of threads while preserving the benefits of parallel reduction. We prepared a CUDA C++ device-side template library for developers to easily express nested patterns in GPU kernels using our technique. Our experiments show that CTE delivers up to 37% warp execution efficiency improvement and gives up to 1.51x speedup over sub-warp decomposition with the best sub-warp width.

### 1.2 Dissertation Organization

The rest of this dissertation is organized as follows. Chapter 2 presents Warp Segmentation for SIMD-efficiency and Vertex Refinement for effective multi-GPU scalability of vertex-centric graph processing. Chapter 3 gives our solution to enable work-efficiency and offers a dynamic task assignment scheme. Chapter 3 also presents Vertex Grouping and Permissive Partitioning to overcome challenges introduced as side-effects of supporting work-efficiency. Chapter 4 generalizes two of our techniques and extends them as Collaborative Context Collection and Collaborative Task Engagement in forms of compiler optimization and template library respectively. Chapter 5 discusses the related work and Chapter 6 concludes the thesis by giving a summary of our work as well as directions for future work.

# Chapter 2

# Warp Efficiency and Scalability

Due to their ability to represent relationships between entities, graphs have become the building blocks of many high performance data analysis algorithms. A wide variety of graph algorithms are iterative in nature – during each iteration vertices update their state based upon states of neighbors connected by edges using a computation procedure until the graph state becomes stable. The inherent data parallelism in an iterative graph algorithm makes many-core processors, with underlying SIMD hardware such as GPUs, an attractive platform for accelerating the algorithms. However, efficient mapping of real-world power law graphs with irregularities to symmetric GPU architecture is a challenging task [55].

This chapter presents techniques that enhance the scalability and performance of vertex-centric graph processing on multi-GPU systems. This is achieved by fully exploiting the resources available on a multi-GPU system as follows:

• The irregular nature of power law graphs makes it difficult to balance load across threads leading to underutilization of SIMD resources. We address the device underutilization problem by developing Warp Segmentation that dynamically assigns appropriate number of SIMD threads to process a vertex with irregular-sized neighbors. Our experiments show that the warp execution efficiency of warp segmentation exceeds 70% while for the well known VWC [34] technique it is around 40%.

- For scaling performance to large graphs, they must be held in the global memories of GPUs in the system. To maximize the graph sizes that can be held in global memories, a compact graph representation must be used. Therefore Warp Segmentation makes use of the compact CSR representation. To tolerate the long latency of non-coalesced memory accesses that arise while accessing the neighbors of a vertex in CSR, warp segmentation keeps the GPU cores busy by scheduling other useful operations that compute the segment size and lane's intra-segment index.

- Since large graphs must be distributed across the global memories of multiple GPUs, processing at each GPU requires values of neighboring vertices that reside on other GPUs. Here we must make judicious use of the limited bandwidth available for transferring data between GPUs via the PCIe bus. We introduce an approach based upon parallel binary prefix sum that dynamically limits the inter-GPU transfers to only include updated vertices. In contrast, existing multi-GPU techniques perform high degree of wasteful vertex value transfers.

Our solution maximizes the graph sizes for which high performance can be achieved by fully utilizing GPU resources of SIMD hardware, memory, and bandwidth.

Let us briefly consider the related works and see how our approach overcomes their drawbacks. First, we consider the prominent single GPU techniques for vertex-centric graph processing, namely VWC [34] and CuSha [42]. Virtual-Warp Centric (VWC) [34] is the state-of-the-art method that uses the compact CSR representation and is inevitably prone to load imbalance when processing real-world graphs due to high variation in degrees of vertices. When the size of the virtual warp is less than the number of neighbors for a vertex, the virtual warp needs to iterate over the neighbors forcing other virtual warps within the warp that are assigned to vertices with fewer neighbors to stay inactive. When the size of the virtual warp is greater than the the size of the neighbors for a vertex, a great portion of the virtual warp is disabled. Both cases lead to underutilization of SIMD resources and poor warp execution efficiency. In addition, discovering the best virtual warp size for every

graph and every expressed graph algorithm requires multiple tries. CuSha [42] addresses the drawbacks of VWC, namely warp execution inefficiencies and non-coalesced accesses, but at the cost of using G-Shards and CW graph representations which are 2x-2.5x larger than the CSR representation due to vertex replication. In contrast, Warp Segmentation uses the compact CSR representation while delivering high SIMD hardware utilization. In warp segmentation the neighbors of warp-assigned vertices are grouped into segments. Warp lanes then get assigned to these neighbors and recognize their position inside the segment and the segment size by first performing a quick binary search on the fast shared memory content and then comparing their edge index with corresponding neighbor indices. When the segment size and the position in the segment are known for the lanes, user-defined reduction can be efficiently performed between neighbors of a vertex without introducing any intra-warp load imbalance. It will be shown in experiments that WS outperforms VWC by 1.29x-2.80x on average.

Next let us consider the related works on multi-GPU graph processing [94, 24]. Given a partitioning of a graph across multiple GPUs, these techniques underestimate the importance of efficient inter-device communication and do not effectively utilize the PCIe bandwidth. This is a significant problem because, the PCIe bus, as the path to communicate data from one GPU to another GPU, is tens of times slower than GPU global memory. Previous multi-GPU techniques either copy the whole vertex set belonging to one GPU to other GPUs at every iteration [94], or they identify boundary vertices in a pre-processing stage and make GPUs exchange these subsets of vertices in every iteration [24, 25]. In both approaches, a great number of vertices that are exchanged between devices is redundant. In contrast, we propose Vertex Refinement, a new strategy that enables our framework to efficiently scale to multiple GPUs. Vertex Refinement refines and transfers only those vertices that are updated in the previous round and are needed by other devices. It consists of two stages: online and offline. In the offline stage, boundary vertices are recognized and marked during pre-processing. In the online stage, we exploit parallel binary prefix sum to refine updated vertices from not-updated ones on-the-fly. A vertex is transferred to another

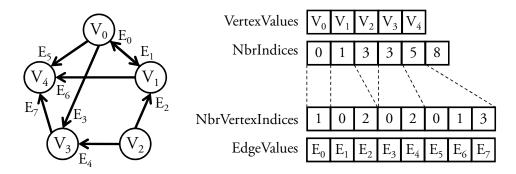

Figure 2.1: An example graph with 5 vertices and 8 edges and its CSR representation.

device only if it is marked and refined by the online stage. Thus, Vertex Refinement eliminates wasteful communication and provides higher multi-GPU performance and provides exclusive speedup of up to 2.71x over other multi-GPU vertex communication schemes.

The remainder of this chapter is organized as follows. We first present *Warp Segmentation* and the interface of the framework we created to express and execute the graph vertex-centric algorithms. Then we describe efficient scaling of our framework to multiple GPUs via Vertex Refinement. Finally, we evaluate the performance of our methods.

## 2.1 Warp Efficiency via Warp Segmentation

In this section we present Warp Segmentation (WS) that eliminates intra-warp load imbalance and enhances execution efficiency for processing a graph in CSR form. CSR is a compact form suitable for representing large and sparse graphs in a minimum space. Due to its space-efficiency, CSR is a good choice to hold large graphs inside the limited GPU memory.

As Figure 2.1 shows, CSR consists of 4 arrays:

- Vertex Values holds the content of the  $i^{th}$  vertex in its  $i^{th}$  element.

- NbrVertexIndices holds the indices for a vertex's neighbors in a contiguous fashion.

- NbrIndices holds a prefix sum of the number of neighbors for vertices. The  $i^{th}$

vertex's neighbors inside NbrVertexIndices start at NbrIndices[i] and end before NbrIndices[i+1].

• Edge Values holds the edge values corresponding to the neighbors inside NbrVertexIndices.

### 2.1.1 Motivating Study

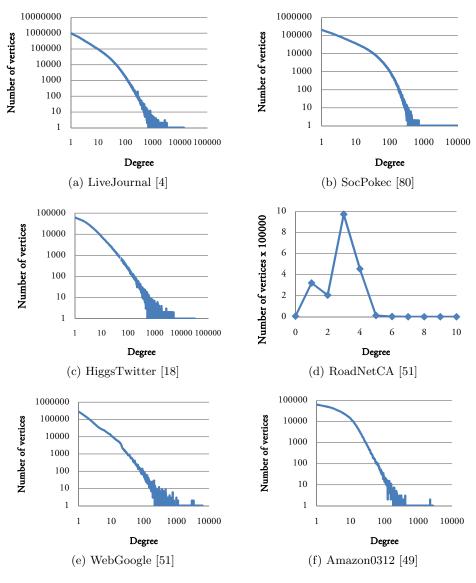

Figure 2.2: Degree distribution for graph vertices.

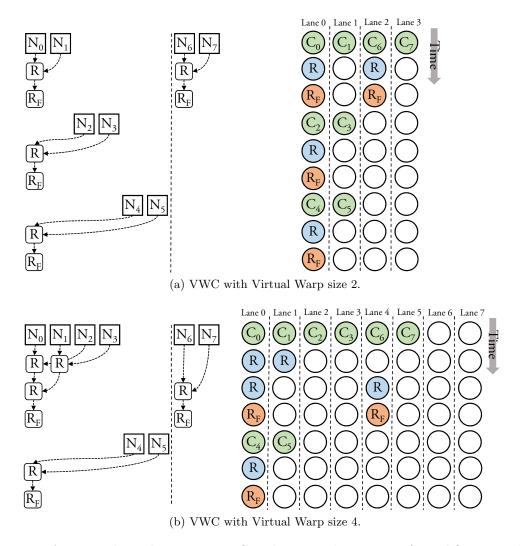

To motivate the need for WS, we first describe the drawbacks of the Virtual-Warp Centric (VWC) [34] method that also uses the CSR representation. VWC divides the SIMD group (warp, in CUDA terms) with the physical length of 32 into smaller virtual warps with fixed lengths (2, 4, 8, 16, or 32). Virtual warp size is kept the same throughout the graph processing. Each virtual warp is assigned to process one vertex and its incoming edges. As an enhancement of the original work [34], Khorasani et al. proposed a generalized form of VWC in [42] in which threads of the virtual warp are involved in reduction over the computed values. However, real-world graphs often exhibit power-law degree distribution, as it is evident in Figure 2.2, i.e. the number of neighbors a vertex owns vary greatly from one vertex to another. Thus, due to fixed number of virtual lanes involved in a reduction, VWC unavoidably suffers from underutilization:

- If the virtual warp is *smaller* than the vertex's number of neighbors, it will have to iterate over the vertex's connected edges hence dragging with it other virtual warps that have already finished their jobs (see the example in Figure 2.3a).

- If the virtual warp has a size that is *larger* than the number of neighbors for a vertex, a portion of virtual warp's lanes stays *idle* during the reduction leading to underutilization (see the example in Figure 2.3b).

This motivates the need for a technique that, independent of inner graph structure, takes minimum number of reduction steps in a SIMD environment, i.e. Warp Segmentation. Note that VWC suffer from the SIMD load imbalance in the same way PRAM-style thread assignment [30] does. In both PRAM-style and VWC, assigning fixed number of SIMD threads to process one vertex and its edges leads to thread-idling due to highly irregular vertex degree distribution. This fixed number in the former is exactly one while in the latter it can be a power of 2.

Figure 2.3: An example: reduction in VWC with assumed warp size of 8 and first 6 neighbors belonging to one vertex and last 2 belonging to another.

#### 2.1.2 Warp Segmentation

To remedy the drawbacks of fixed-sized virtual warps, we propose Warp Segmentation (WS) technique. In WS, a warp is assigned to a group of 32 consecutive vertices and their connected edges. When warp lanes process edges iteratively, those that process edges belonging to one vertex—i.e. having the same destination index—form a segment. By knowing the segment size and the index inside the segment, lanes can participate in the appropriate reduction of segment, minimizing the total number of reduction steps.

Figure 2.4: Reduction using Warp Segmentation with the same scenario in Figure 2.3.

Figure 2.4 shows the reduction in WS in an example scenario. In this example, first six lanes belong to one segment and two last lanes belong to another. The minimum number of reduction steps in this case is  $\lceil \log_2 6 \rceil = 3$  which is also the case in WS. As Figure 2.3 shows, on-the-fly efficient reduction procedure in WS leads to better utilization of SIMD resources compared to VWC. In addition, WS does not need any pre-processing or trial-and-error for the best configuration determination.

VertexValues

Figure 2.5: Discovering segment size and the index within segment by warp lanes for the graph in Figure 2.1. Warp size is assumed 8.

The key feature of WS is its fast determination of the segment a lane belongs to and the index of the lane within the segment. The step-by-step approach shown in Figure 2.5 illustrates this. Warp lanes perform a binary search over NbrIndices elements for their assigned edge index. Since NbrIndices elements are already fetched to the fast shared memory of the GPU, the binary search is performed quickly. After  $\log_2(warpSize)$  steps, the starting position of the resulting search boundary shows the vertex index to which the edge belongs. Knowing the vertex index, the lane's index inside the segment and the segment size is retrieved using NbrIndices array. The distance of the holding edge index from the vertex's corresponding NbrIndices element reveals the position of the vertex in the segment. The difference between the holding edge index and the next vertex's corresponding NbrIndices element, minus one, yields the distance of the lane from the end of the segment. Addition of these two distances plus one represents the segment size.

WS is based upon the vertex-centric paradigm where in every iteration the shared memory serves as a scratchpad for vertices. The shared memory regions corresponding to vertices are: initialized by the vertex content within the global memory, modified depending upon the edges connected to the vertex using appropriate reductions, and at the end of the iteration, the updated values are pushed back to the global memory. Two alternatives for the intra-warp reduction in WS are possible. The first one is to use atomics to survive the concurrent modifications of the vertices as in [42]. However, this alternative imposes heavy use of atomics on shared memory locations on top of CSR's inherent non-coalesced neighbor accesses. The second alternative is processing a groups of vertices by one thread block. However, this approach necessitates multiple synchronization primitive across the thread block that degrade the performance. WS assigns a set of vertices to GPU's architectural SIMD grouping (warp) and performs efficient reductions hence it avoids shared memory atomic operations alongside any explicit synchronizations throughout the kernel.

The reduction in WS can be viewed as a form of intra-warp segmented reduction but without a *head flags* array, consisting of two main steps. First, warp lanes identify the vertex index via a fast binary search. Second, they discover the intra-segment index and the segment size. Also, note that these two sets of operations are independent from the neighbor vertex value hence can be used to cover the latency of the inevitable non-coalesced access. The thread exploits instruction level parallelism by simultaneously executing non-dependent instructions. Thus, GPU cores are kept busy performing operations while neighbor's vertex value is on its way.

### 2.2 Graph Processing Framework for WS

Next we describe the framework that uses the graph processing procedure based on WS. Then, we present the interface functions that allow easy expression of graph algorithms by non-expert users.

#### 2.2.1 Core Processing Procedure

Figure 2.6 shows the graph processing procedure. The convergence of iterative graph processing is controlled via a variable passed between the host and the device. If no thread updates this variable, it means the algorithm has converged and no more iterations are needed. In the outer-most for loop, according to the WS paradigm, each warp is assigned to process a contiguous set of vertices with the size equivalent to the warp size (32 for current CUDA devices). A warp task during one iteration is to process its assigned vertices. This task can be broken down into three major steps.

First step. In this step (lines 11 to 15 in Figure 2.6) threads of a warp fetch 32 elements of *VertexValues* and initialize the designated shared memory region for vertex values using user-provided initialization function. The threads also put 32+1 corresponding elements of *NbrIndices* into another shared memory buffer. Using the *NbrIndices* starting and ending element, warp lanes can recognize the region within *EdgeValues* and *NbrVertexIndices* arrays that belongs to the assigned group of vertices.

```

0. converged = false;

while(!converged) {

2.

converged = true;

parallel-for warp w {

3.

__shared__ Vertex V[blockDim];

5.

__shared__ Vertex tLocal_V[blockDim];

7.

__shared__ uint NIdx[blockDim];

w_V = V + warpOffsetWithinCTA;

w_tLocal_V = tLocal_V + warpOffsetWithinCTA;

9.

10.

w_NIdx = NIdx + warpOffsetWithinCTA;

/* 1st major step */

initVertex(w_V+laneID, VertexValues+globalTID);

11.

w_NIdx[laneID] = NbrIndices[globalTID];

12.

13.

startEIdx = w_NIdx[0];

14.

endEIdx = NbrIndices[warpGlobalOffset+32];

/* 2nd major step */

15.

for( currEIdx = startEIdx + laneID;

currEIdx < endEIdx;</pre>

currEIdx += 32 ) {

16.

nbrIdx = NbrVertexIndices[currEIdx];

17.

srcV = VertexValue[nbrIdx];

belongingVIdx = binarySearch(currEIdx, w_NIdx);

18.

19.

inSegID = min( laneID,

currEIdx - w_NIdx[belongingVIdx] );

20.

SegSize= inSegID + 1 + min( 31 - laneID,

( (belongingVIdx==31)?endEIdx:

w_NIdx[belongingVIdx+1] ) - currEIdx - 1 );

21.

ComputeNbr( srcV, EdgeValues+currEIdx,

w_tLocal_V+laneID );

reduceInsideSegment( w_tLocal_V+laneID,

22.

inSegID, SegSize );

23.

if( inSegID==0 )

24.

ReduceVertices( w_V+belongingVIdx,

w_tLocal_V+laneID );

25.

/* 3rd major step */

26.

if( IsUpdated( w_tLocal_V+laneID,

VertexValues+globalTID ) ) {

27.

atomicExch( VertexValues+globalTID,

w_tLocal_V[laneID] );

28.

converged = false;

29.

30.

31.

sync_device_with_host();

32. }

```

Figure 2.6: Framework's graph processing procedure pseudo-algorithm. Assumed warp size is 32. Shared memory pointers in the program code are declared with volatile qualifier.

Second step. This step involves iteration of warp lanes over the elements of the Edge Values and Nbr VertexIndices arrays region (lines 15 to 25 in Figure 2.6). Warp lanes perform a user-provided compute function with the fetched neighbor vertex value and the connected edge value and save the outcome in a local shared memory buffer (line 21). Besides, every warp lane must discover which of 32 vertices that are assigned to the warp owns the processed edge and neighbor. This involves a log 32 = 5 stepped binary search on fetched edge Indices in the shared memory (line 18). Using the resulting vertex index, warp lanes can be grouped into segments, each segment corresponding to one vertex. Each lane identifies its position within the segment and the size of the segment it belongs to (lines 19 and 20). Therefore warp lanes can execute user-provided reduction function in parallel (line 22). Finally, the first lane in each segment performs the reduction function over the outcome and associated element in the shared memory region for vertex values (lines 23 and 24). Warp lanes perform these steps iteratively until all the edges for the set of vertices are processed.

**Third step.** In this step, the warp lanes compare the content of designated shared memory region for vertex values with the corresponding *VertexValues* elements using the user-provided function (line 26). If the function returns true, the vertex content inside the global memory will be updated.

Once all the vertices are processed, the framework executes another iteration of the algorithm on all the graph vertices if any vertex in the current iteration is updated. Graph processing with WS method dynamically determines the proper size for reduction based on the segment size and it is guaranteed that the number of steps for parallel reduction will never exceed five ( $\log warpSize$ ).

Note that the memory transactions in all the steps are *coalesced* except for accessing the neighbor vertex value (line 17), which is inherent in the compact graph representation like CSR. However by moving "binary search" and "segment realization" functions (lines 18 to 20) before the neighbor computation function, we exploit instruction level parallelism to hide the latency associated with the non-coalesced memory access.

### 2.2.2 Framework Interface

```

0. struct Edge{ uint BW; };

1. typedef unsigned int Vertex;

inline __device__ void initVertex(

volatile Vertex* initV, Veretx* V ){

3.

*initV = *V;

4.

inline __device__ void ComputeNbr(

Vertex SrcV, Edge* E, volatile Vertex* localV ) {

6.

*localV = min( SrcV, E->BW );

7.

inline __device__ void ReduceVertices(

volatile Vertex* firstV, Veretx* secondV ){

9.

*firstV = max( *firstV, *secondV );

10. }

11. inline __device__ bool IsUpdated(

volatile Vertex* computedV, Veretx* V ){

return ( *computedV > *V );

12.

13. }

```

Figure 2.7: User-specified structures and functions for SSWP.

In addition to trivial input/output handling functions, type definition for the vertex, and the structure definition for the edge, our framework accepts the following user specified functions:

- *InitVertex* initializes the vertex at the beginning of an iteration.

- ComputeNbr is performed for every neighbor vertex.

- Reduce Vertices acts as the reduction function between the results of ComputeNbr for two neighbors of a vertex.

- Is Updated verifies if a vertex has updated during the current iteration.

Figure 2.7 illustrates the usage of the framework by showing the functions for Single Source Widest Path (SSWP) algorithm as an example. SSWP requires a variable for expressing the edge bandwidth and another variable for specifying maximum visible bandwidth by the

vertex from the source. In SSWP, during multiple rounds, the content of a vertex is updated by the maximum bandwidth it observes picked from the minimums between incoming edges and corresponding neighbors. As Figure 2.7 shows, this algorithm can be easily expressed in our framework via the above processing functions. First, the vertex content inside the shared memory is initialized by the most updated content of the vertex. Second, for each neighbor a local value is computed, which in this case is the minimum between every connecting edge bandwidth and its corresponding source vertex visible bandwidth. Third, these values are reduced two-by-two using the reduction function and the result is saved to the first argument content. For SSWP, reduction function selects the maximum of visible values through neighbors. Also, at the end of the third step of the processing procedure, the reduction function is executed for the initialized vertex and the final reduction result. Finally, in the fourth step, the framework verifies if the vertex should be updated. If the Is Updated function returns true—which in case of SSWP is observing a greater bandwidth to the source—the content of the vertex inside global memory is replaced with the reduced vertex content at the current iteration. If any vertex is updated, the host must executes another iteration.

## 2.3 Scaling via Vertex Refinement

To handle larger graphs we must scale our method to use multiple GPUs that provide more memory and processing resources. Although graph partitioning strategies for GPUs have been explored, inter-GPU data transfer efficiency has not received adequate attention. Given a partitioning, for scaling of graph processing to be effective, we must make good use of limited PCIe bandwidth. We show the inefficiency of existing techniques and then present Vertex Refinement that avoids redundant data exchange between GPUs.

### 2.3.1 Inefficiency of Existing Inter-GPU Communication

Existing multi-GPU generic graph processing schemes divide the graph in two or more partitions and assign each partition to one GPU. Graph vertices completely fall into partitions while there can be edges that pass the partition boundaries. Due to these boundary edges, a GPU needs to be informed of the vertex updates happening in other GPUs. To keep the content of its assigned vertices held inside other GPUs updated, the GPU needs to transfer vertices belonging to its own partition over the PCIe bus. PCIe data transfer rate is tens of times slower than that of GPU global memory; thus extra care must be taken to transfer only necessary data so as not to waste PCIe precious bandwidth.

Nonetheless, since implementing a mechanism to efficiently manage queues in GPU's massively multithreaded environment is challenging, previous works choose simple but inefficient approaches. Medusa [94] copies all the vertices belonging to one device to other devices at every iteration. We refer to this solution as the ALL method. TOTEM [24, 25] pre-selects the boundary vertices in a pre-processing stage but similar to Medusa copies the boundary vertices after every iteration. We refer to this solution as Maximal Subset (MS) method. Both of these methods suffer from wastage of PCIe bandwidth because usually only a small portion of the vertices are updated during each iteration. Table 2.1 shows the ratio of useful transferred vertices—vertices that are updated in the last iteration—to all the vertices that are transferred in such schemes. Such low percentages motivate the need for a new solution that utilizes limited PCIe bandwidth economically.

To eliminate the overhead of transferring unnecessary vertices between devices, our framework performs Vertex Refinement in two steps: *offline* and *online*. We first describe the required data structures and then present the two-staged refinement procedure.

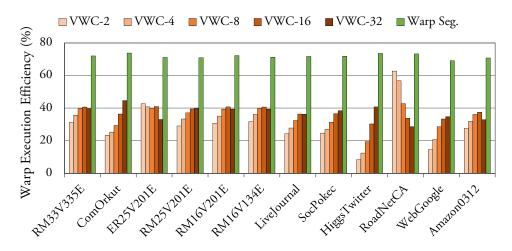

### 2.3.2 Data Structure Organization

To process a graph with multiple GPUs, our framework divides the vertices and their associated edges into partitions and assigns each partition to one GPU, so that each

| Graph Algorithm                    | ALL % | MS %  |

|------------------------------------|-------|-------|

| Breadth-First Search (BFS)         | 10.43 | 12.21 |

| Connected Components (CC)          | 9.55  | 11.19 |

| Circuit Simulation (CS)            | 2.34  | 2.39  |

| Heat Simulation (HS)               | 31.29 | 36.66 |

| Neural Network (NN) [5]            | 15.66 | 18.34 |

| PageRank (PR) [65]                 | 10.38 | 13.65 |

| Single Source Shortest Path (SSSP) | 13.65 | 15.99 |

| Single Source Widest Path (SSWP)   | 3.14  | 3.68  |

Table 2.1: The percentage of useful vertex data among all the transferred data when all the vertices (ALL) or the maximal subset of them (MS) are copied from one GPU to another. In this two-GPU configuration, the graph under the examination is an Rmat graph with approximately 40 million vertices and 470 million edges.

GPU processes a continuous set of vertices. Since the processing time is mostly affected by the memory accesses associated with gathering the values of neighbor vertices, determining the boundaries of vertex partitions depends upon the total number of edges that vertices of each subset hold. In our scheme, vertices of each partition will have roughly the same number of edges in order to provide a balanced load between GPUs. Each GPU will hold relevant subset of NbrIndices, NbrVeretxIndices, and Edge Values but will contain a full version of VertexValues array. This organization allows each device to process vertices belonging to its own partition as long as vertices inside VertexValues that belong to other GPUs are updated during an iteration.

Figure 2.8: Organization of data structures in multi-GPU processing.

In addition to CSR representation buffers, each GPU will hold one *Outbox* buffer that is filled with updated vertex indices and vertex values of the GPU-specific division. As shown in Figure 2.8, we keep the inboxes inside host pinned buffers. In other words, the set of host buffers is similar to a hub that are filled by devices. At the start of an iteration, a device accesses inboxes corresponding to other devices and updates its own *VertexValues* array. Also at the end of an iteration, the device transfers its own outbox content to device's corresponding inbox. Moreover, we apply double buffering technique by alternating read buffers and write buffers. In an odd (even) iteration, devices read from the odd (even) inbox buffers and copy their outbox to their designated even (odd) inbox buffer. In summary:

- Inbox and outbox buffers are vital for a fast data transfer between GPUs. Direct peer-device memory access as an alternative will introduce significant performance penalty due to non-coalesced transactions over PCIe bus [86]. In contrast, inbox and outbox buffers allow the collection of necessary data together and hence accelerate the inter-device communication.