Publishing

### High pulsed current density $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs verified by an analytical model corrected for interface charge

Cite as: Appl. Phys. Lett. **110**, 143505 (2017); https://doi.org/10.1063/1.4979789 Submitted: 15 December 2016 • Accepted: 23 March 2017 • Published Online: 04 April 2017

Neil A. Moser, 🔟 Jonathan P. McCandless, Antonio Crespo, et al.

#### COLLECTIONS

Paper published as part of the special topic on The Dawn of Gallium Oxide Microelectronics

#### ARTICLES YOU MAY BE INTERESTED IN

1-kV vertical Ga<sub>2</sub>O<sub>3</sub> field-plated Schottky barrier diodes Applied Physics Letters **110**, 103506 (2017); https://doi.org/10.1063/1.4977857

Gallium oxide (Ga<sub>2</sub>O<sub>3</sub>) metal-semiconductor field-effect transistors on single-crystal  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (010) substrates Applied Physics Letters **100**, 013504 (2012); https://doi.org/10.1063/1.3674287

A review of Ga<sub>2</sub>O<sub>3</sub> materials, processing, and devices Applied Physics Reviews **5**, 011301 (2018); https://doi.org/10.1063/1.5006941

# Lock-in Amplifiers up to 600 MHz

## High pulsed current density $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs verified by an analytical model corrected for interface charge

Neil A. Moser,<sup>1,a)</sup> Jonathan P. McCandless,<sup>2</sup> Antonio Crespo,<sup>3</sup> Kevin D. Leedy,<sup>3</sup> Andrew J. Green,<sup>2</sup> Eric R. Heller,<sup>4</sup> Kelson D. Chabak,<sup>3</sup> Nathalia Peixoto,<sup>1</sup> and Gregg H. Jessen<sup>3</sup>

<sup>1</sup>Department of Electrical and Computer Engineering, George Mason University, Fairfax, Virginia 22030, USA <sup>2</sup>KBRWyle, 4200 Colonel Glenn Hwy, Beavercreek, Ohio 45431, USA <sup>3</sup>Air Force Research Laboratory, Sensors Directorate, Wright-Patterson AFB, Ohio 45433, USA <sup>4</sup>Air Force Research Laboratory, Materials and Manufacturing Directorate, Wright-Patterson AFB,

(Received 15 December 2016; accepted 23 March 2017; published online 4 April 2017)

We report on Sn-doped  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs grown by molecular beam epitaxy with as-grown carrier concentrations from  $0.7 \times 10^{18}$  to  $1.6 \times 10^{18}$  cm<sup>-3</sup> and a fixed channel thickness of 200 nm. A pulsed current density of >450 mA/mm was achieved on the sample with the lowest sheet resistance and a gate length of 2  $\mu$ m. Our results are explained using a simple analytical model with a measured gate voltage correction factor based on interface charges that accurately predict the electrical performance for all doping variations. © 2017 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution (CC BY) license (http:// creativecommons.org/licenses/by/4.0/). [http://dx.doi.org/10.1063/1.4979789]

$\beta$ -Ga<sub>2</sub>O<sub>3</sub> has recently emerged as a promising semiconductor for high-power, high-voltage device applications because of its ultra-wide bandgap of ~4.8 eV and the corresponding expected critical breakdown field of ~8 MV/cm.<sup>1,2</sup>  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> also has the advantage of a native substrate that can be synthesized in bulk by melt growth techniques with Sn and compensating Fe and Mg impurity doping.<sup>3–5</sup> Further, homoepitaxial channel conductivity for field effect transistor (FET) device applications has been demonstrated by Sn and Si doping using both molecular beam epitaxy (MBE) and metalorganic vapour phase epitaxy (MOVPE).<sup>6,7</sup> Disadvantages include low thermal conductivity<sup>8</sup> and high hole effective mass.<sup>9</sup> Depletion-mode metal-semiconductor FETs and Si-implanted metal-oxide-semiconductor FETs (MOSFETs) have been demonstrated with current densities exceeding 25 and 40 mA/mm, respectively.<sup>2,10</sup> Further, a depletion-mode MOSFET exceeding 750 V with a field plate and an enhancement-mode fin-array MOSFET up to 600 V were recently reported.<sup>11,12</sup> Finally, Green et al measured a lateral gate-drain critical field strength >3.8 MV/cm on a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET surpassing bulk GaN and SiC theoretical limits.13

Ohio 45433, USA

While high blocking voltages have been achieved, insight into the high-current density potential of  $Ga_2O_3$  MOSFETs has been largely unexplored. In this letter, we compare n-type  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs with various Sn channel concentrations and accurately predict the I-V performance using a simple electrostatic model that includes the gate oxide-gallium oxide interface charge voltage. The model which does not include self-heating effects or gate and drain dispersion is validated by isothermal pulsed I-V measurements with quiescent voltages and sweep parameters chosen to minimize dispersion effects. Agreement between measured and theoretical values for knee voltage (V<sub>knee</sub>) and saturated drain current (IDSS) over a wide range of Sn doping concentrations is verified. A MOSFET with the highest channel charge-mobility  $(N_d - \mu)$ product achieved a pulsed current density of 478 mA/mm at a gate voltage of +4 V, much higher than previously reported DC values of 60 mA/mm for MOSFETs on homoepitaxial materials<sup>13</sup> and 90 mA/mm for ion-implanted MOSFETs,<sup>11</sup> and second only to nanomembrane devices which achieved 610 mA/mm at a high forward gate bias of  $+120 \text{ V}.^{14}$  This indicates the performance of the material system if self-heating due to the low thermal conductivity can be mitigated by cooling techniques or less thermally stressful applications. MOSFETs were fabricated on single crystal  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> grown by MBE on commercially available Fe-doped (010) semi-insulating substrates.<sup>6</sup> Sn-doping was performed during the epitaxial growth, and carrier concentrations from  $0.7 \times 10^{18}$  to  $1.6 \times 10^{18}$  cm<sup>-3</sup> were measured after growth using electrochemical capacitance-voltage (C-V) measurements. Table I includes these values as  $N_d$  As Grown and also summarizes the measured data for all the samples as described further below.

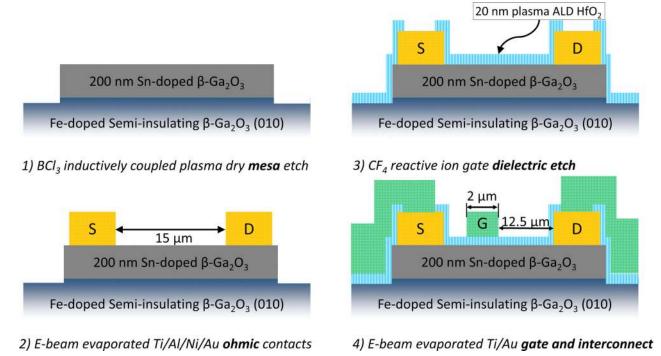

A schematic process flow for the MOSFET is shown in Figure 1. Mesa isolation of the active channel was conducted using a BCl<sub>3</sub> inductively coupled plasma (ICP) dry etch and verified by profilometer measurements. Source and drain ohmic contacts were formed using an evaporated Ti/Al/Ni/ Au metal stack and annealed for 60 sec in a nitrogen ambient at 470 °C.<sup>10</sup> All the contacts were ohmic and the contact resistance (R<sub>C</sub>) ranged from 10.7 to 80.0 ohm-mm as measured by the circular transfer length method (TLM)<sup>15</sup> and shown in Table I. A 20 nm thick gate dielectric layer of HfO<sub>2</sub> was deposited by plasma-enhanced atomic layer deposition (ALD) at 250 °C without any surface pre-treatment. The gate dielectric was selectively removed in the ohmic pad regions by CF<sub>4</sub> reactive ion etching (RIE). Interconnects and 2-µm long gates were patterned and deposited simultaneously using a 20/480 nm Ti/Au metal stack.

0

a)nmoser@gmu.edu

TABLE I.  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET sample summary.

| N <sub>d</sub> As Grown <sup>a</sup> | $V_{knee}^{c}$ | IDSS <sup>d</sup> | $V_{off}{}^{c}$ | N <sub>d</sub> post process <sup>a</sup> | $\mu_{eff}{}^{\mathbf{b}}$ | $IDSS_{mod}{}^{\mathbf{d}}$ | $\mathrm{IDSS}_{\mathrm{mod}} \Delta V_{G}^{\mathbf{d}}$ | $V_{knee \mod} \Delta V_G^{\ c}$ | R <sub>C</sub> <sup>e</sup> |

|--------------------------------------|----------------|-------------------|-----------------|------------------------------------------|----------------------------|-----------------------------|----------------------------------------------------------|----------------------------------|-----------------------------|

| $0.70 \times 10^{18}$                | 13.0           | 19                | -9.6            | $2.50 \times 10^{17}$                    | 74.5                       | 36.5                        | 20.5                                                     | 12.9                             | 80.0                        |

| $1.00 \times 10^{18}$                | 33.9           | 111               | -18.8           | $4.84 	imes 10^{17}$                     | 58.3                       | 136.1                       | 111.2                                                    | 35.8                             | 32.0                        |

| $1.30 \times 10^{18}$                | 53.7           | 235               | -24.5           | $6.29 \times 10^{17}$                    | 52.4                       | 258.8                       | 235.4                                                    | 54.7                             | 14.0                        |

| $1.60 	imes 10^{18}$                 | 69.6           | 381               | -30.8           | $7.88 \times 10^{17}$                    | 51.0                       | 404.6                       | 381.4                                                    | 71.0                             | 10.7                        |

<sup>a</sup>cm<sup>-3</sup>. <sup>b</sup>cm<sup>2</sup>/V · s. <sup>c</sup>V. <sup>d</sup>mA/mm.

<sup>e</sup>Ohm-mm.

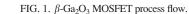

All device electrical testing was conducted on selfisolating ring-type FETs with a gate-source spacing of 0.5  $\mu$ m and a total source-drain spacing of 15  $\mu$ m (12.5  $\mu$ m G-D spacing). The total gate width was 422  $\mu$ m. All the structures were fabricated on a single 10 × 15 mm sample for each doping level. Figure 2 shows a static log transfer curve (I<sub>D</sub> -V<sub>GS</sub>) for the highest current density MOSFET with good transistor operation including a high on/off ratio of >10<sup>8</sup> which was typical of all the devices measured regardless of the carrier concentration. Sister devices routinely achieved breakdown voltages >400 V for a 10.5  $\mu$ m gate-drain spacing and were limited by the failure of the gate dielectric.

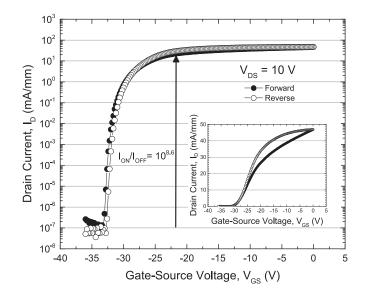

Pulsed-IV measurements were conducted on MOSFET devices using an AMCAD system to provide a pulsed drain voltage and a Keysight E5270a to provide static gate bias. The pulse width was 200 ns with a quiescent drain bias of 0 V and a low duty-cycle of 0.001 percent to minimize thermal effects. The pulsed measurement used represents an ideal environment where gate and drain dispersion and self-heating effects can be ignored to evaluate the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET under ideal conditions and assess the material system. Figure 3 shows a pulsed-

FIG. 2. DC log transfer curve for a high current density  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET showing good transistor operation. The inset shows a linear plot of the transfer curve showing significant gate dispersion between forward and reverse curves.

FIG. 3. Pulsed family of drain current curves (symbols) for a high current density  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET. The maximum current density measured was 478 mA/mm. The device operates very close to theoretical values shown using an analytical electrostatic model (blue lines). Gate dispersion was avoided by measuring from the on to off states. A static measurement limited to V<sub>DS</sub> = 20 V and V<sub>GS</sub> = 0 V is also shown with a maximum current of 118 mA/mm @ V<sub>DS</sub> = 20 V and V<sub>GS</sub> = 0 V, which agrees with the pulsed measurement (120 mA/mm @ V<sub>DS</sub> = 20 V and V<sub>GS</sub> = 0 V) and the model.

IV and static family of curves ( $I_D - V_{DS}$ ) for the highest current density device. We extracted the knee voltage,  $V_{knee}$ , and the saturated drain current at  $V_G = 0 V$ , IDSS, from the inflection point in the pulsed-IV family of curves as shown in Figure 3.  $V_{knee}$  and *IDSS* are recorded for all the samples in Table I.

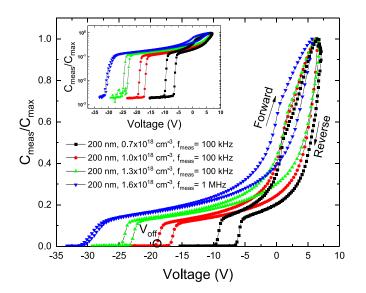

Capacitance-voltage (C-V) measurements were performed on lateral C-V structures with diameters of 75, 100, and 125  $\mu$ m using a B1505a equipped with a multi-frequency capacitance measurement unit and needle probes. A representative C-V curve for each sample is presented in Figure 4. Measurements were performed at frequencies that provided smooth C-V characteristics (100 kHz or 1 MHz), and

FIG. 4. Normalized capacitance vs. voltage, C-V, for MOS structures on MBE grown  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layers with varying target doping and an active layer thickness of 200 nm. The inset shows log scale plots of the same. The inflection point used to determine V<sub>off</sub> is shown for one device. All the samples had HfO<sub>2</sub> gate dielectric.

measurement differences at frequencies between 1 kHz and 1 MHz were confirmed to have a negligible effect on the experimental results. We used the C-V measurement data to determine the off-state gate voltage,  $V_{off}$ , from the inflection point where the C-V curve (and therefore the available drift carriers) is minimized. This inflection point is shown for one device in Figure 4, and  $V_{off}$  is recorded for all the samples in Table I. The measured  $V_{off}$  is the gate voltage required to deplete the entire active layer:

$$V_{off} = V_{FB} - dq N_d \left(\frac{d}{2\epsilon_s \epsilon_0} + \frac{1}{C_{ox}}\right),\tag{1}$$

where  $V_{FB}$  is the flat-band voltage, *d* is the active layer thickness, *q* is the electron charge,  $N_d$  is the average active ionized dopant concentration in the active layer,  $\epsilon_s \epsilon_0$  is the static dielectric constant of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, and  $C_{ox} = \frac{\epsilon_{ax}\epsilon_0}{t_{ox}}$  is the oxide capacitance per unit area.

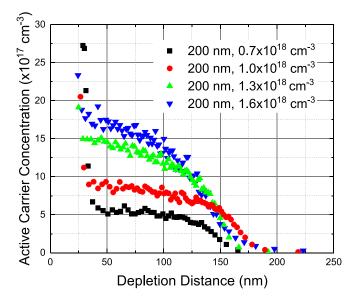

Obtaining exact values for  $V_{FB}$  and  $N_d$  from measurements is difficult because of interface trap charges at the  $Ga_2O_3$ -HfO<sub>2</sub> interface and non-uniform carrier concentration in the active layer after fabrication as shown in Fig. 5. To simplify our calculations, we use the measured value of  $V_{off}$  from C-V data, substitute the ideal value of the flatband voltage:

$$V_{FB} = \Phi_M - \Phi_S = \Phi_M - \left(\chi_S + \phi_t \ln\left(\frac{N_C}{N_d}\right)\right), \quad (2)$$

where  $\Phi_x$  is the work function of the metal or semiconductor,  $\phi_t$  is the thermal voltage,  $\chi_S$  is the electron affinity of Ga<sub>2</sub>O<sub>3</sub>, and N<sub>C</sub> is the effective density of states in the conduction band, and then solve for N<sub>d</sub> iteratively starting from the maximum value of  $V_{FB} = \Phi_M - \chi_S$  in (1). The result obtained is an average of N<sub>d</sub> through the active layer thickness of each sample, and it is recorded in Table I as N<sub>d</sub> Post Process. The difference between the carrier concentration before and after the fabrication results from the depletion of carriers at the epitaxy-substrate interface during processing and surface effects at the gate oxide-gallium oxide interface. The average value extracted from V<sub>off</sub> agrees reasonably with average values extracted from post-process C-V profiling (Figure 5); however, C-V profiling is unreliable near the gate oxidegallium oxide interface.

To verify the MOSFET current density, we used simple electrostatic model equations for the depletion region. We first acknowledge that the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET never creates a conducting inversion layer. Then, we started with the basic equation for the drain current<sup>16</sup>

$$I_D = -QWv = -QW\mu E(y) = -QW\mu \frac{dV}{dy},$$

(3)

where v is the carrier velocity, W is the gate width, E(y) is the lateral electric field at a point under the gate (y is the direction along the gate length), V is the potential at a point along the channel, and  $\mu$  is the average carrier mobility. Then, assuming that the total channel charge per unit area, Q, is equal to the charge in the un-depleted portion of the channel and using the depletion approximation where

FIG. 5. Depletion distance dependent carrier concentration through the channel thickness for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> homoepitaxial layers after MOSFET fabrication extracted from capacitance vs. voltage measurements using the slope of  $1/C^2$ -V to extract carrier concentration and a depletion and gate oxide capacitor in series to extract the distance from the gate oxide-gallium oxide interface. The result shows the difficulty in characterizing the gate oxide-gallium oxide interface (near 0 nm) and the epi-substrate interface (near 200 nm) using C-V profiling after fabrication.

$$x_{dep}(y) = \sqrt{\frac{2\epsilon_s \epsilon_0 \Psi_s(y)}{qN_d}} \tag{4}$$

is the depletion distance and

$$\Psi_s(y) = V_{FB} - V_G + V(y) - V_{ox}$$

(5)

is the surface potential, we can integrate (3) from source to drain to obtain

$$I_D = I_o \left\{ V_{DS} \left( d + \frac{\epsilon_s \epsilon_0}{C_{ox}} \right) + \sqrt{\frac{8\epsilon_s \epsilon_0}{9qN_d}} [V_o] \right\},\tag{6}$$

where

$$I_o = \frac{qN_d\mu W}{L}$$

(7)

$$V_o = (A^2 - V_{GS} + V_{FB})^{3/2} - (A^2 - V_{GS} + V_{FB} + V_{DS})^{3/2},$$

(8)

$A = \frac{\sqrt{2\epsilon_x\epsilon_0qN_d}}{2C_{ax}}$ , and  $V_{ox}$  is the voltage drop across the gate oxide. Equation (6) is valid in the depletion region only  $(V_{off} < V_{GS} < V_{FB})$ . We also modeled the effect of access resistance in the un-gated regions at the source and drain by implementing (6) in VerilogA in series with source and drain access resistors in the TINA circuit simulator.<sup>17,18</sup> Each access resistor was the sum of the measured R<sub>C</sub> and the resistance for the ungated region based on R<sub>SH</sub> and lateral device geometry (Figure 1).

The measured value of  $R_{SH}$  was also used with  $N_d$  calculated above to determine the effective mobility from the  $N_d$ - $\mu$  product. This mobility is included in Table I as  $\mu_{eff}$  and agrees with the expected value from sister epitaxial growth. Finally,  $N_d$ ,  $V_{FB}$ , and  $\mu_{eff}$  are used in (6) to estimate the drain current under isothermal, ideal-interface-state

| Parameter       | Value                                                  |  |  |  |

|-----------------|--------------------------------------------------------|--|--|--|

| $\epsilon_s$    | 10.0 Ref. 19                                           |  |  |  |

| $\epsilon_{ox}$ | 22.3 meas <sup>a</sup>                                 |  |  |  |

| N <sub>C</sub>  | $3.72 \times 10^{18} \text{ cm}^{-3} \text{ Ref. } 20$ |  |  |  |

| $\Phi_M$        | 4.33 eV Ref. 21                                        |  |  |  |

| $\chi_S$        | 4.0 eV Ref. 20                                         |  |  |  |

<sup>a</sup>Measured on MIM caps.

conditions. Additional parameters used in the model are shown in Table II. The modeled value of IDSS using (6) is included in Table I as  $IDSS_{mod}$ .

While our devices operate close to theoretical values under pulsed conditions, the drain current is still reduced by surface potential dependent negative charges at the gate oxide-gallium oxide interface<sup>22</sup> that effectively reduce the gate voltage applied by:<sup>16</sup>

$$\Delta V_G = \frac{-\Delta Q_{it}(V_G)}{C_G(V_G)},\tag{9}$$

where  $\Delta Q_{it}(V_G)$  is the interface charge difference between a device with filled and empty gate oxide-gallium oxide interface traps and C<sub>G</sub> (V<sub>G</sub>) is the total capacitance seen by the gate at a given gate voltage. In (9), we used the fact that the surface potential in (5) depends only on the gate voltage to replace  $\Psi_S$  with V<sub>G</sub>. Based on the assumption that the time constant of traps is slower than the AC signal, and that interface traps are filled and empty for reverse and forward C-V sweeps, respectively, we calculate  $\Delta V_G$  from the charge difference between the two curves in Figure 4 and the measured C<sub>G</sub> at every point. We then replace V<sub>GS</sub> with V<sub>GS</sub>- $\Delta V_G$  in (6) to obtain the values for *IDSS<sub>mod</sub>*  $\Delta V_G$  and  $V_{knee mod}$   $\Delta V_G$  in Table I. We also include the accumulation mode by solving (6) with V<sub>GS</sub> = V<sub>FB</sub> and adding an accumulation current:

$$I_{Dacc} = \mu C_{ox} V_{DS} \frac{W}{L} (V_{GS} - \Delta V_G - V_{FB}).$$

(10)

In doing so, we note that effects of the normal field on  $\mu_{eff}$  have not been evaluated, and further investigation is required. In our case, where the normal field is very small, however, this addition to our model accurately predicts the I-V curve for  $V_G = +4$  V. The result is shown in Figure 3 for our highest current density device. Similar agreement was observed for all but the lowest doped samples. As the doping level was decreased, the assumption that Vooff is not significantly affected by interface trapped charges breaks down, and (1) using the ideal value of  $V_{FB}$  miscalculates  $N_d$ . In other words, as the doping concentration (or active layer thickness) is reduced, the magnitude of  $V_{off}(\Psi_S)$  is not sufficient to drive out negative interface trapped charges, and  $\Delta V_G$  affects not only (6) but also (1). N<sub>d</sub> calculated from (1) becomes dependent on V<sub>G</sub> and transfer characteristics of the analytical model become inaccurate without additional advanced measurement techniques. With thin or lightly doped devices, the interface charge effect on  $\Delta V_G$  and  $V_{FB}$  is significant. In fact, thin enhancement-mode devices have been reported<sup>14</sup> with  $V_{off} > +75$  V exceeding the band-gapelectron-affinity sum for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and indicating significant thickness of the gate oxide-gallium oxide interface trap layer. In these difficult cases, Hall measurements can be used to determine  $\mu_{eff}$ , but techniques must be developed to overcome anomalies at the gate oxide-gallium oxide interface to accurately determine N<sub>d</sub> and V<sub>FB</sub>.

In conclusion, we have shown the measured and analytically modeled effects on device performance as a function of Sn doping concentration. A  $\mu_{eff}$  of > 50  $\frac{\text{cm}^2}{\text{V}\cdot\text{S}}$  was maintained for a device with N<sub>d</sub> = 7.8 × 10<sup>17</sup> cm<sup>-3</sup>, resulting in recordhigh pulsed current density for homoepitaxially grown  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs. The agreement between our simple MOSFET model with a gate-charge correction and the measured data highlights the importance of doping levels and interface optimization for future  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET designs.

The authors would like to acknowledge Novel-Crystal Technology, Inc. for MBE growth.

<sup>1</sup>N. Ueda, H. Hosono, R. Waseda, and H. Kawazoe, Appl. Phys. Lett. **71**, 933 (1997).

- <sup>2</sup>M. Higashiwaki, K. Sasaki, A. Kuramata, T. Masui, and S. Yamakoshi, Appl. Phys. Lett. **100**, 013504 (2012).

- <sup>3</sup>H. Aida, K. Nishiguchi, H. Takeda, N. Aota, K. Sunakawa, and Y. Yaguchi, Jpn. J. Appl. Phys., Part 1 47, 8506 (2008).

<sup>4</sup>M. H. Wong, K. Sasaki, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, Appl. Phys. Lett. **106**, 032105 (2015).

- <sup>5</sup>Z. Galazka, K. Irmscher, R. Uecker, R. Bertram, M. Pietsch, A. Kwasniewski, M. Naumann, T. Schulz, R. Schewski, D. Klimm, and M. Bickermann, J. Cryst. Growth **404**, 184 (2014).

- <sup>6</sup>K. Sasaki, A. Kuramata, T. Masui, E. G. Víllora, K. Shimamura, S. Yamakoshi, and E. G. Villora, Appl. Phys. Express **5**, 035502 (2012).

- <sup>7</sup>M. Baldini, M. Albrecht, A. Fiedler, K. Irmscher, D. Klimm, R. Schewski, and G. Wagner, J. Mater. Sci. 51, 3650 (2016).

- <sup>8</sup>E. G. Víllora, K. Shimamura, T. Ujiie, and K. Aoki, Appl. Phys. Lett. 92, 202118 (2008).

- <sup>9</sup>H. He, R. Orlando, M. A. Blanco, R. Pandey, E. Amzallag, I. Baraille, and M. Rérat, Phys. Rev. B **74**, 195123 (2006).

- <sup>10</sup>M. Higashiwaki, K. Sasaki, T. Kamimura, M. Hoi Wong, D. Krishnamurthy, A. Kuramata, T. Masui, and S. Yamakoshi, Appl. Phys. Lett. **103**, 123511 (2013).

- <sup>11</sup>M. H. Wong, K. Sasaki, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, IEEE Electron. Device Lett. **37**, 212 (2016).

- <sup>12</sup>K. D. Chabak, N. Moser, A. J. Green, D. E. Walker Jr., S. E. Tetlak, E. Heller, R. Fitch, J. P. Mccandless, K. Leedy, M. Baldini, G. Wagner, X. Li, and G. Jessen, Appl. Phys. Lett. **109**, 213501 (2016).

- <sup>13</sup>A. J. Green, K. D. Chabak, E. R. Heller, R. C. Fitch, M. Baldini, A. Fiedler, K. Irmscher, G. Wagner, Z. Galazka, S. E. Tetlak, A. Crespo, K. Leedy, and G. H. Jessen, IEEE Electron Device Lett. **37**, 902 (2016).

- <sup>14</sup>H. Zhou, M. Si, S. Alghamdi, G. Qiu, L. Yang, and P. D. Ye, IEEE Electron Device Lett. 38, 103 (2017).

- <sup>15</sup>J. H. Klootwijk and C. E. Timmering, in *Proceedings of IEEE 2004 International Conference on Microelectronic Test Structures* (2004), p. 247.

- <sup>16</sup>Y. Taur and T. H. Ning, *Fundamentals of Modern VLSI Devices* (Cambridge University Press, 2009).

- <sup>17</sup>R. Aisola, K. Cameron, D. Fitzpatrick, V. Gerousis, I. Getreu, K. Hailey, K. Kundert, O. Leuthold, S. P. Liebmann, I. Miller, T. Reeder, S. Rochel, J. Spoto, R. Trihy, Y. Trivedi, and A. Zamfirescu, *Verilog-A Language Reference Manual: Analog Extensions to Verilog HDL*, 1st ed. (Open Verilog International, 1996).

- <sup>18</sup>DesignSoft, TINA v10 The Complete Electronics Lab for Windows: Users Manual (DesignSoft, Inc., 2014).

- <sup>19</sup>M. Passlack, N. E. J. Hunt, E. F. Schubert, G. J. Zydzik, M. Hong, J. P. Mannaerts, R. L. Opila, and R. J. Fischer, Appl. Phys. Lett. **64**, 2715 (1994).

- <sup>20</sup>Silvaco, The Simulation Standard (Silvaco Inc., 2013).

- <sup>21</sup>H. B. Michaelson, J. Appl. Phys. 48, 4729 (1977).

- <sup>22</sup>T. Kamimura, D. Krishnamurthy, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, Jpn. J. Appl. Phys. 55, 1202B5 (2016).