## High-Resolution Stamp Fabrication by Edge Lithography

Yiping Zhao

The research described in this thesis was carried out at the Transducers Science and Technology and Molecular Nanofabrication groups of the MESA+ Institute for Nanotechnology at the University of Twente, Enschede, The Netherlands. The project was financially supported by the MESA+ Institute for Nanotechnology in the Strategic Research Orientation "Nanofabrication".

Graduation committee:

| Chairman                       |                                   |

|--------------------------------|-----------------------------------|

| Prof. dr. ir. A. J. Mouthaan   | University of Twente              |

| Secretary                      |                                   |

| Prof. dr. ir. A. J. Mouthaan   | University of Twente              |

| Promotor                       |                                   |

| Prof. dr. M. C. Elwenspoek     | University of Twente              |

| Prof. dr. ir. J. Huskens       | University of Twente              |

| Assistant Promotor             |                                   |

| Dr. ir. H. V. Jansen           | University of Twente              |

| Members                        |                                   |

| Prof. dr. ir. A. H. Dietzel    | Technical University of Eindhoven |

| Prof. dr. J. G. E. Gardeniers  | University of Twente              |

| Prof. dr. G. J. Vancso         | University of Twente              |

| Prof. dr. A. J. H. M. Rijnders | University of Twente              |

| Prof. H. Fujita                | University of Tokyo               |

Yiping Zhao

High-Resolution Stamp Fabrication by Edge Lithography

Ph.D. Thesis, University of Twente, Enschede, The Netherlands

ISBN: 978-90-365-3036-1

Printed by Wöhrmann Print Services, Zutphen, The Netherlands

Copyright © 2010 by Yiping Zhao

All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without the prior permission of the author.

## HIGH-RESOLUTION STAMP FABRICATION BY EDGE LITHOGRAPHY

PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Universiteit Twente, op gezag van de Rector Magnificus Prof. dr. H. Brinksma, volgens besluit van het College voor Promoties, in het openbaar te verdedigen op donderdag 27 mei 2010 om 16:45 uur door

Yiping Zhao

geboren op 1 februari 1982 te Beijing, China.

| Dit proefschrift is goedgekeurd door: |                            |  |  |

|---------------------------------------|----------------------------|--|--|

| Promotoren:                           | Prof. dr. M. C. Elwenspoek |  |  |

|                                       | Prof. dr. ir. J. Huskens   |  |  |

| Assistent-promotor:                   | Dr. ir. H. V. Jansen       |  |  |

## Contents

| 1                | Intr | Introduction                                                                |    |  |  |

|------------------|------|-----------------------------------------------------------------------------|----|--|--|

|                  | 1.1  | Nanoimprint lithography                                                     | 1  |  |  |

|                  | 1.2  | Stamp fabrication for thermal nanoimprint lithography applications          | 4  |  |  |

|                  |      | 1.2.1 Stamp fabrication by high resolution lithography techniques           | 5  |  |  |

|                  |      | 1.2.2 Unconventional methods for stamp fabrication                          | 6  |  |  |

|                  | 1.3  | Micromachining technology as a tool for stamp fabrication                   | 15 |  |  |

|                  |      | 1.3.1 Deposition methods                                                    | 15 |  |  |

|                  |      | 1.3.2 Wet etching                                                           | 17 |  |  |

|                  |      | 1.3.3 Plasma etching                                                        | 19 |  |  |

|                  | 1.4  | Aim of the research and thesis outline                                      | 25 |  |  |

|                  | Refe | erences                                                                     | 26 |  |  |

| <b>2</b>         | Fab  | rication of a silicon oxide stamp by edge lithography reinforced with       |    |  |  |

|                  |      |                                                                             | 37 |  |  |

|                  | 2.1  | Introduction                                                                | 38 |  |  |

|                  | 2.2  | Experimental details                                                        | 39 |  |  |

|                  |      | 2.2.1 NIL stamp fabrication                                                 | 39 |  |  |

|                  |      | 2.2.2 Nanoimprint lithography                                               | 40 |  |  |

|                  | 2.3  | Results and discussion                                                      | 41 |  |  |

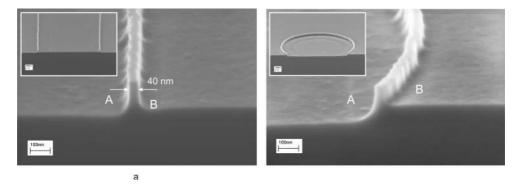

|                  |      | 2.3.1 TEOS patterning                                                       | 41 |  |  |

|                  |      | 2.3.2 $\operatorname{SiN}_x$ patterning                                     | 41 |  |  |

|                  |      | 2.3.3 Silicon dioxide nanoridges                                            | 42 |  |  |

|                  |      | 2.3.4 Nanoridges with a $SiN_x$ shield $\ldots$                             | 46 |  |  |

|                  |      | 2.3.5 Nanoimprint lithography by using a $SiN_x$ reinforced nanoridge stamp | 47 |  |  |

|                  | 2.4  | Conclusions                                                                 | 48 |  |  |

|                  | Refe | erences                                                                     | 49 |  |  |

| 3                | Sub  | -10 nm silicon ridge nanofabrication by advanced edge lithography           |    |  |  |

|                  | for  | NIL applications                                                            | 55 |  |  |

| 3.1 Introduction |      |                                                                             |    |  |  |

|                  | 3.2  | Fabrication                                                                 | 57 |  |  |

|                  | 3.3  | Discussion                                                                  | 59 |  |  |

|                  | 3.4  | Imprint and pattern transfer                                                | 60 |  |  |

|          | 3.5                                                              |          | sions                                                            |       |  |

|----------|------------------------------------------------------------------|----------|------------------------------------------------------------------|-------|--|

|          | Refe                                                             | rences   |                                                                  | . 62  |  |

| <b>4</b> | Multi-silicon ridge nanofabrication by repeated edge lithography |          |                                                                  |       |  |

|          | 4.1                                                              |          | uction                                                           | . 67  |  |

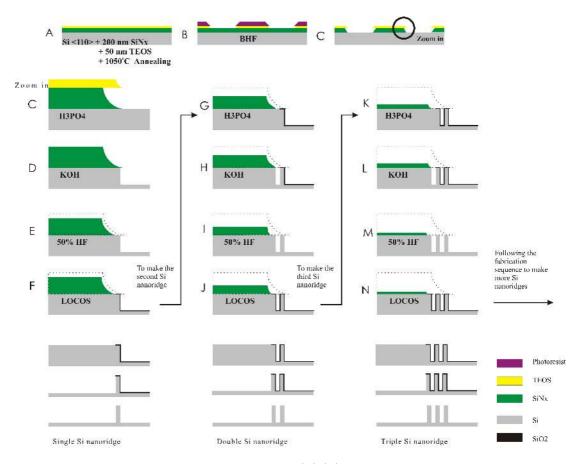

|          | 4.2                                                              | Fabric   | ation                                                            | . 69  |  |

|          | 4.3                                                              | Discus   | sion                                                             | . 73  |  |

|          |                                                                  | 4.3.1    | Substrate preparation and layer patterning                       | . 73  |  |

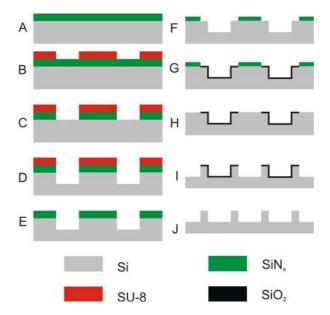

|          |                                                                  | 4.3.2    | Si etching in 20% KOH at room temperature (step D, H, L)         |       |  |

|          |                                                                  | 4.3.3    | $SiN_x$ retraction etching using a 50% HF (step E, I, M)         |       |  |

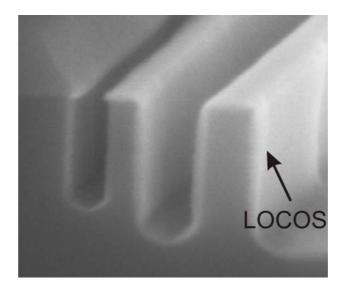

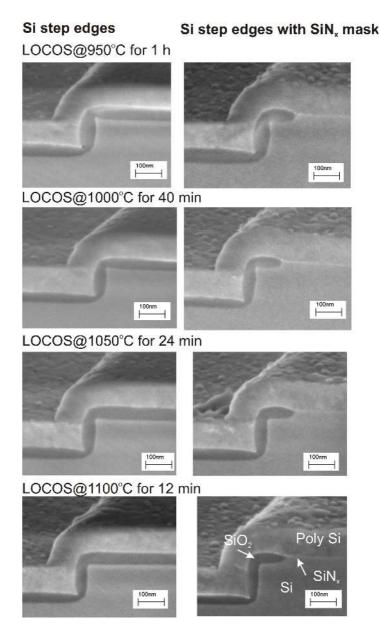

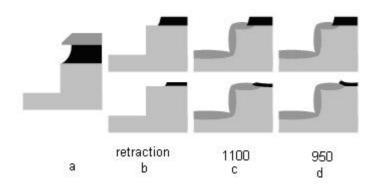

|          |                                                                  | 4.3.4    | LOCOS (step F, J, N)                                             |       |  |

|          |                                                                  | 4.3.5    | $SiN_x$ retraction etching using hot $H_3PO_4$ acid (steps G, K) |       |  |

|          |                                                                  | 4.3.6    | The determination of multi-Si nanoridge dimensions               |       |  |

|          | 4.4                                                              | Applic   | ation in nanoimprint lithography                                 |       |  |

|          | 4.5                                                              |          | isions                                                           |       |  |

|          | Refe                                                             |          |                                                                  |       |  |

|          |                                                                  |          |                                                                  |       |  |

| 5        |                                                                  | -        | g retraction edge lithography and plasma etching for arbitra     | -     |  |

|          |                                                                  |          | anoridge fabrication                                             | 85    |  |

|          | 5.1<br>5.2                                                       |          | uction                                                           |       |  |

|          | 5.2                                                              |          | cryogenic deep reactive ion etching (DRIE)                       |       |  |

|          |                                                                  | 5.2.1    | Experimental                                                     |       |  |

|          | ۳.9                                                              | 5.2.2    | Results and discussion                                           |       |  |

|          | 5.3                                                              |          | oridge fabrication using Cr as the mask                          |       |  |

|          |                                                                  | 5.3.1    | Experimental                                                     |       |  |

|          | ۳.4                                                              | 5.3.2    | Results and discussion                                           |       |  |

|          | 5.4                                                              |          | oridge with arbitrary contour fabrication using SU-8 as the mask |       |  |

|          |                                                                  | 5.4.1    | Experimental                                                     |       |  |

|          |                                                                  | 5.4.2    | Results and discussion                                           |       |  |

|          | 5.5                                                              |          | nination step dimension                                          |       |  |

|          | 5.6                                                              |          | usions                                                           |       |  |

|          | Refe                                                             | rences   |                                                                  | . 106 |  |

| 6        | Арг                                                              | olicatio | on of stamps fabricated by edge lithography in alternative r     | ia-   |  |

|          |                                                                  | abricat  |                                                                  | 111   |  |

|          | 6.1                                                              | Introd   | uction                                                           | . 112 |  |

|          | 6.2                                                              | Experi   | mental                                                           | . 113 |  |

|          |                                                                  | 6.2.1    | Fabrication of bionanoassemblies by NIL and self-assembly        |       |  |

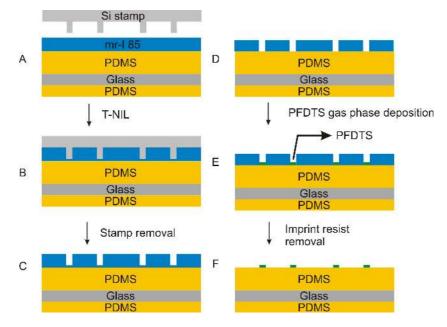

|          |                                                                  | 6.2.2    | High resolution $\mu$ CP stamp fabrication by T-NIL and CFL      |       |  |

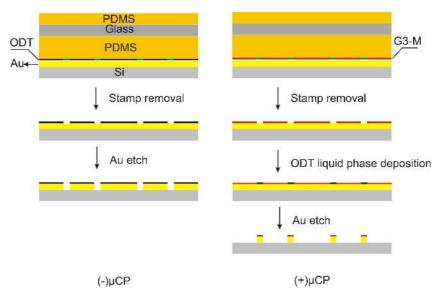

|          |                                                                  | 6.2.3    | Nanofabrication by high resolution $\mu CP$                      |       |  |

|          | 6.3                                                              |          | s and discussion                                                 |       |  |

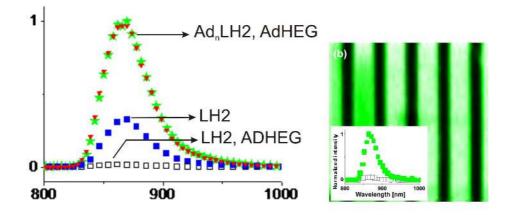

|          |                                                                  | 6.3.1    | Light harvesting complexes construction and energy transfer      |       |  |

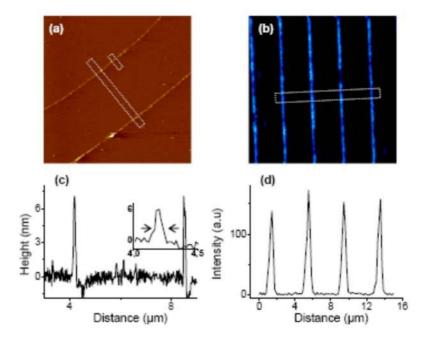

|          |                                                                  | 6.3.2    | High resolution PDMS-glass soft stamp fabrication by T-NIL and   |       |  |

|          |                                                                  |          | its application in $\mu$ CP                                      |       |  |

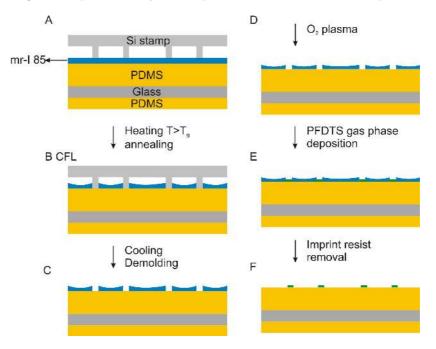

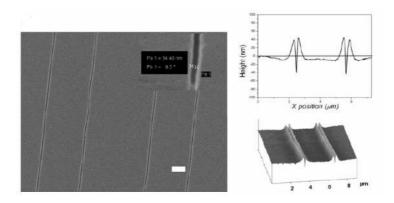

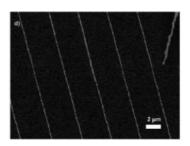

|              |        | 6.3.3     | High resolution PDMS-glass $\mu$ CP stamp fabrication by CFL and nanofabrication by $\mu$ CP | 121 |

|--------------|--------|-----------|----------------------------------------------------------------------------------------------|-----|

|              | 6.4    | Conclu    | sions                                                                                        | 122 |

|              | 0      |           |                                                                                              | 123 |

| 7            | Con    |           | ns and outlook                                                                               | 127 |

|              | 7.1    |           | usions                                                                                       | 127 |

|              | 7.2    | Outloo    | k                                                                                            | 128 |

| $\mathbf{A}$ | -      |           | ntal data                                                                                    | 131 |

|              |        |           | tion methods and conditions                                                                  | 131 |

|              | A.2    |           | ates                                                                                         | 133 |

|              |        | • -       | asma etching equipments and settings                                                         | 133 |

|              | Refe   | rences .  |                                                                                              | 133 |

| в            | Pro    | cess do   | ocuments                                                                                     | 139 |

|              | B.1    | $SiO_2$ n | anoridges and nanoridges reinforced with $SiN_x$ deposition                                  | 139 |

|              | B.2    | Si nan    | oridge fabrication                                                                           | 143 |

|              | B.3    | Multi-    | Si nanoridge fabrication                                                                     | 147 |

|              | B.4    | Plasma    | a etching scheme: Si nanoridge fabrication by positive photoresist                           |     |

|              |        | and C     | as the mask                                                                                  | 151 |

|              | B.5    | Plasma    | a etching scheme: Si nanoridge fabrication using SU-8                                        | 155 |

| Su           | ımma   | ary       |                                                                                              | 159 |

| Sa           | men    | vatting   |                                                                                              | 161 |

| A            | cknov  | wledgn    | nent                                                                                         | 163 |

| A            | oout   | the au    | thor                                                                                         | 167 |

| Pι           | ıblica | ations    |                                                                                              | 169 |

### Chapter 1

## Introduction

Nanoimprint lithography is a lithographic technology that promises high throughput patterning of nanostructures. Replicas of the pattern with high resolution is achieved by mechanical deformation of imprint polymers independent of light diffractions or beam scattering of other lithographic tools. The research described in this thesis focuses on the fabrication of high resolution stamp for thermal nanoimprint lithography (T-NIL) applications.

Nanoridges are fabricated by edge lithography and micromachining techniques. Conventional UV lithography is employed for pattern definition instead of high resolution lithography methods. The creation of nano-sized patterns is accomplished by edge lithography, which by definition means converting the edges of the original pattern into the feature of the final pattern. In this chapter, an introduction will be given concerning the development of nanoimprint lithography with the emphasis of stamp fabrication. The origination and development of edge lithography for creating nanostructures in Si are demonstrated. We will give an overview of the widely used micromachining technologies that have been applied in fabricating NIL stamps. The chapter ends with the objectives and outline of the thesis.

#### 1.1 Nanoimprint lithography

Nanofabrication is the process aiming at fabricating arbitrary shaped patterns with a dimension  $\leq 100$  nm. The primary drive for the development of nanofabrication is the requirement of ever-shrinking IC devices dimensions, which relies primarily on the improvement of lithographic techniques. In addition to conventional UV photolithography,

which has a highest resolution of 2  $\mu$ m, high resolution lithographic techniques have been developed to meet the requirement. These techniques include, for example, deep ultraviolet lithography (DUV), X-ray lithography, electron beam lithography (EBL), focused ion beam (FIB), etc. At present, the high resolution lithography techniques are generally suffering from problems such as high cost, low throughput and limited access. To circumvent the dependence on high resolution lithographic technologies, researches have been investigating alternative routes for fabricating nanostructures. These techniques, to name a few, include nanoimprint lithography, soft lithography, scanning-probe-based techniques, and dip-pen lithography.

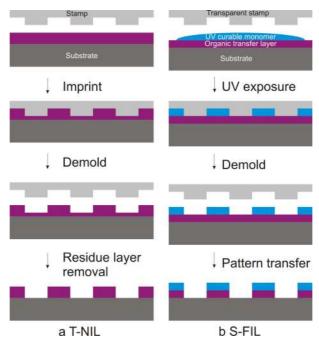

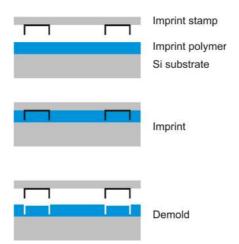

Nanoimprint lithography (NIL) is a lithographic technology that promises high throughput. Thermal NIL (T-NIL) was first developed by Chou's group in the 1990s [1]. As a variant, step-and-flash imprint lithography (S-FIL), which was developed by Wilson's group, uses a transparent stamp and UV curable monomer to complete the imprint [2]. The schematics of T-NIL and S-FIL are shown in Figure 1.1. In T-NIL, a substrate made of hard material with nanostructures is used as the stamp. Before imprint, the stamp is treated with an anti-adhesion layer to assist demolding. A substrate is cleaned and coated with imprint polymer. Then the stamp is brought into contact with the substrate. The imprint process is performed at a elevated temperature and pressure for a certain amount of time. Then the stamp is separated from the substrate after lowering the temperature and releasing the pressure. A reversed pattern from that in the stamp is replicated in the imprint polymer. In the last step, the residual layer in the imprint polymer can be directionally removed by reactive ion etching (RIE). From here on, the imprinted substrate is ready for further process. In S-FIL, the substrate is first coated with an organic pattern transfer layer, then a surface treated, transparent stamp is brought close and aligned to the coated substrate. Once in proximity, a drop of UV curable monomer is introduced into the gap between the stamp and substrate. The gap is closed when the stamp contacts the coated organic transfer layer. Then the assembly is irradiated by UV light to cure the monomer, which leaves the substrate with a solidified reverse replica of the stamp on the substrate. The pattern can be successively transferred from the monomer to the organic transfer layer with the help of RIE. The difference between T-NIL and S-FIL is that T-NIL normally asks for high temperature and pressure while S-FIL is performed at room temperature and low pressure up to 1 bar.

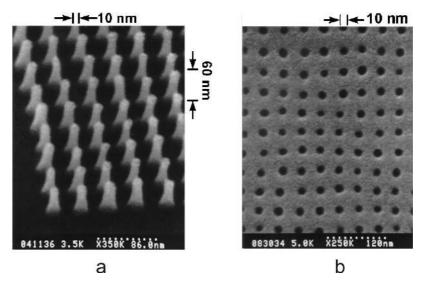

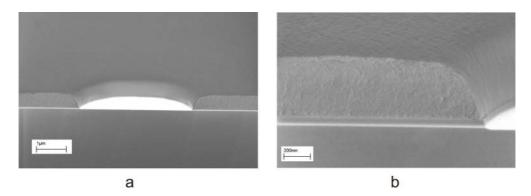

Figure 1.2 is the earliest example made by Chou *et al.* showing NIL being able to faithfully transfer features from the stamp into imprint polymer [1]. It shows that T-NIL is a high throughput and low cost process, easy to handle and requires simple process equipment. Although there is still challenges existing for the perfection of the technology

Figure 1.1: Schematics: (a) T-NIL; (b) S-FIL

itself, it is potentially interesting and found to be useful in various applications, such as electronics, optical, photonic, and biological fields.

The best performance of NIL is normally co-determined by many factors such as stamp quality, physical and chemical properties of imprint polymers, imprint conditions (pressure, temperature, and duration), etc [3, 4, 5]. Amongst them, stamp fabrication and polymer issues are the main factors influencing the performance of T-NIL. The stamp used for T-NIL is normally made of hard materials, such as Si, SiO<sub>2</sub>, metals (e.g. nickel). The hard materials promise retaining the nanostructure properties, such as shape and aspect ratio, during T-NIL under high temperature and pressure conditions. The imprint polymers used in T-NIL should be able to deform easily during the imprint process; and they should be able to retain the imprinted replica during the demolding process. Therefore, thermoplastic materials are explored as suitable imprint polymers for T-NIL applications. These thermoplastic materials have a glass transition temperature ( $T_g$ ), above which the Young's modulus and the viscosity drop several orders of magnitude compared to those at room temperature. During T-NIL, the imprint temperature is chosen ca. 70-90°C above  $T_g$  such that the polymer reaches a viscous flow state. A pressure is applied when the

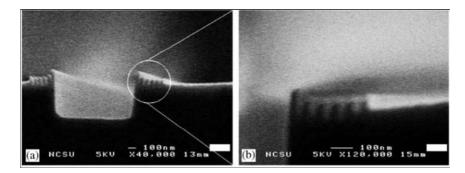

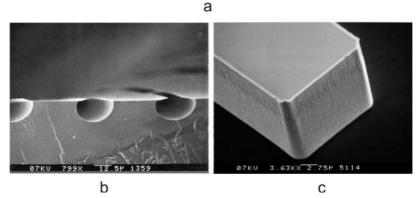

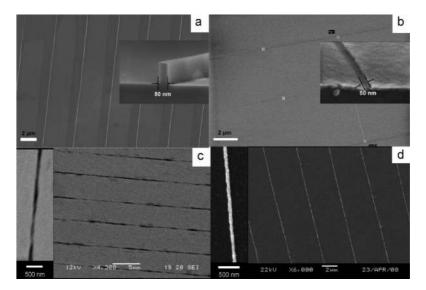

Figure 1.2: SEM images:(a) SiO<sub>2</sub> mold of pillars of minimum 10 nm diameter, 60 nm height and 40 nm period; (b) Imprint results in PMMA. Images are taken from [1].

required temperature is reached to assist polymer deformation. The demolding process is performed when the temperature is decreased lower than  $T_g$  to preserve the imprinted pattern.

As the focus of this thesis, in the following sections, a general review regarding the approaches and technologies for stamp fabrication for T-NIL applications is introduced followed by an overview of micromachining technologies employed for stamp fabrication in our research.

### **1.2** Stamp fabrication for thermal nanoimprint lithography applications

The fabrication of hard stamp with nanostructures for T-NIL applications requires the compatibility with conventional micromachining technologies. Lithographic techniques, therefore, constitutes the primary determination of feature resolution. Conventional UV photolithography has been widely and successfully applied in micromachining for pattern definition with minimum feature sizes of 2  $\mu$ m. High resolution lithographic tools have been implemented and have been demonstrated being able to fabricate nanostructures with sub-200 nm dimensions successfully. For example, electron beam lithography is able

to fabricate nanostructures with sub-10 nm resolutions and laser interference lithography can create large-area periodic structures with feature size ca. 100-200 nm. Industry implemented the current state-of-art deep UV lithography tools which can achieve minimum feature size down to 50 nm. Extreme UV lithography is considered as the next generation lithography tools for mass production. The fabrication of nanostructures by means of high resolution lithographic tools is also referred to as conventional nanofabrication approaches. In addition to conventional nanofabrication approaches, researchers have been investigating stamp fabrication by means of unconventional nanofabrication approaches, in which nanofabrication proceeds via conventional UV photolithography with the integration of micromachining techniques. Many review papers have discussed examples of nanofabrication [6, 7]. In this section, an introduction to conventional nanofabrication approaches and unconventional nanofabrication approaches by edge lithography will be given.

#### 1.2.1 Stamp fabrication by high resolution lithography techniques

#### Beam writing technologies

Beam writing technologies have the general operational principle in employing a focused beam scanning over a susceptible material surface. Electrons and ions are the energetic particles used in electron beam lithography (EBL) and focused ion beam (FIB) respectively. EBL has become a standard tool in generating nano-sized patterns with arbitrary shapes. In this technology, a focused electron beam is used to write directly onto a photoresist. PMMA is the most commonly used resist material in EBL, which is exposed by energetic electrons. The electrons include incident electrons, forward and backscattered electrons, and secondary electrons. The resolution obtained by EBL is primarily determined by the size of the beam. Other factors, such as scattering of electrons in the resist layer and generation of secondary electrons from the underlying substrate, also influence the resolution of this technology [8]. EBL writing has the advantage of creating arbitrary fine patterns but has the disadvantage of low throughput, which limits its application in the IC industry. To improve the throughput by EBL, it has also been implemented as projection printing systems, such as projection electron beam lithography (SCALPEL) and PREVAIL approaches [9]. Since the projection approaches generally suffer from difficulties such as mask fabrication and scan range enlargement, EBL writing systems have become the commonly used approach for pattern definition in the research field of nanofabrication. The highest resolution of EBL can be achieved by tuning the thickness of PMMA, electron beam energy and substrate materials. The results show that the satisfactory line width resolution made in PMMA is 10 nm [8, 10, 11]. Microfabrication techniques, such as plasma etching and lift-off techniques, have been implemented with EBL to produce nanostructures [11, 12]. Furthermore, EBL has been used for create masks for electronics applications.

Focused ion beam takes advantage of an ion beam which has a higher energy than other particle beams. It is explored in a projection process known as focused ion beam lithography (FIBL) and a direct write process known as FIB milling (FIBM) [13].

#### Deep UV and extreme UV lithography

Although beam writing technologies have the advantage of generating arbitrarily shaped patterns with sub-10 nm resolutions, the slow processing speed limits its application in large volume production. Photolithography fulfills the purpose of mass production, however, optical diffraction prevents it from being useful in nano-sized pattern definition. Therefore, deep UV (DUV) lithography was developed by employing wavelength of 248 nm KrF and 193 nm ArF excimer lasers. Currently, feature size down to 50 nm is achieved by DUV lithography.

Extreme UV lithography (EUVL) was first proposed in 1988 [14] as one of the routes of next-generation lithography (NGL). A detailed review regarding origination and latest technological development of EUVL is given by the Wu *et al.* [15]. EUVL is regarded as a natural extension to optical lithography in the sense that EUVL uses masks with 4-5 fold reduction which is achievable by current micromachining technologies. Although a broad wavelength ranging from 5 nm to 50 nm is applicable to EUVL, 13.5 nm EUV is the current candidate corresponding to a Mo/Si multilayer reflective mirror. Although the wavelength in EUV is significantly shorter than that in conventional UV and DUV lithography, the resolution is co-determined by EUV source, resist matters and mask defects. As discussed in the review by Wu *et al.*, many challenges need to be overcome before EUVL cab be implemented for mass production [15].

#### **1.2.2** Unconventional methods for stamp fabrication

The high resolution lithography techniques are commercially available and have been implemented in industry. However, their application in the research field is limited due to the high expenses and limited access. Therefore, researchers have been investigating alternatives, i.e. unconventional nanofabrication approaches. Gates *et al.* published a comprehensive review concerning the unconventional approaches to nanofabrication [6]. In general, unconventional nanofabrication can be achieved by either top-down or bottomup approaches. Bottom-up approaches use interactions between molecules or colloidal particles to assemble nanostructure in two or three dimensions. Top-down approaches employ conventional photolithography in combination with micromachining technologies to fabricate nanostructures. Edge lithography is one of the unconventional nanofabrication methods successfully utilized to create nanostructures in the top-down route. A general review regarding the development and application of edge lithography will be introduced in the following sections.

#### Edge lithography

Edge lithography can be defined as that the edge of the original pattern becomes the feature of the final pattern. In the 1970s, researchers had explored the use of edges for shadow deposition. Dean *et al.* fabricated a sub-micrometer self-aligned dual-gate GaAs FET using conventional photolithography and shadow deposition technique [16]. Later Jelk *et al.* fabricated 0.15  $\mu$ m lines on glass substrates using shadow deposition and lift-off technology [17]. Flanders *et.al.* fabricated ca. 10 nm linewidth mask using isotropic Si etching in combination with shadow deposition technique [18].

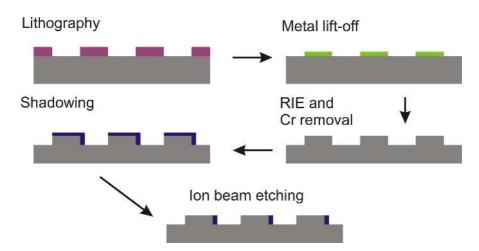

The shadow deposition technique was further developed taking advantage of the edges of steps to fabricate 10 nm metal lines [19]. In this method, as shown in Figure 1.3, a metal layer was evaporated (or sputtered) under an angle over a topography with vertical sidewalls fabricated by X-ray lithography and RIE. Metal lines of 10 nm were created after removing the material on the top and the bottom of the topography by ion beam etching. Following a similar approach, Prober *et.al.* opted for fabricating 30 nm metal lines using shadow deposition and ion beam etching [20].

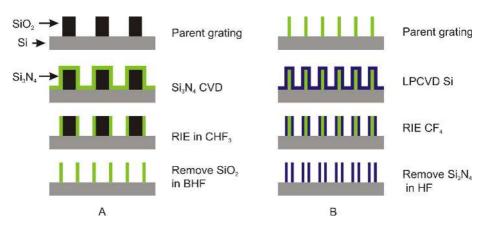

Flanders *et al.* further advanced the edge defined technique to double grating patterns [21]. The fabrication scheme is illustrated in Figure 1.4. The fabrication started from creating a SiO<sub>2</sub> parent grating pattern with vertical sidewalls by X-ray lithography, metal lift-off and RIE technologies. A layer of Si<sub>3</sub>N<sub>4</sub> was deposited over the grating pattern. Then the Si<sub>3</sub>N<sub>4</sub> at the top and the bottom of the grating pattern was removed by CHF<sub>3</sub> plasma while leaving the material at the edge taking advantage of the directionality of RIE. A grating pattern made of Si<sub>3</sub>N<sub>4</sub> with doubled number of the parent pattern was formed after removing the parent SiO<sub>2</sub> grating by buffered HF (BHF) solution. The fabrication scheme was continued, as illustrated in Figure 1.4 (B), by LPCVD Si over the created Si<sub>3</sub>N<sub>4</sub> grating pattern, directional selective removal of LPCVD Si at the top and the bottom of the grating pattern and final removal of Si<sub>3</sub>N<sub>4</sub> taking advantage of the selectivity between Si<sub>3</sub>N<sub>4</sub> and Si in concentrated HF solution.

Generally speaking, good selectivity between materials is crucial for the successful

Figure 1.3: 10 nm linewidth metal structure fabrication by Flanders et al. [19].

**Figure 1.4:** Edge defined techniques to double grating pattern by Flanders *et al.* [21]: (A) Pattern doubled after first X-ray lithography; (B) Continued fabrication of (A).

implementation of edge lithography. In Flander's case, for example, the selectivities between Si, SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> in both plasma etching and wet etching technologies should be well considered [21]. The advantage of using edge lithography is that the resolution is no longer determined by lithographic tools but by the material thickness deposited at parent structure edges. Therefore, it provides the possibility of fabricating nanostructures without relying on wavelength depending lithographic tools. By using the same concept, Choi *et al.* fabricated sub-10 nm Si nanowire arrays using conventional UV lithography, which was named size reduction lithography [22]. Size reduction lithography was integra-

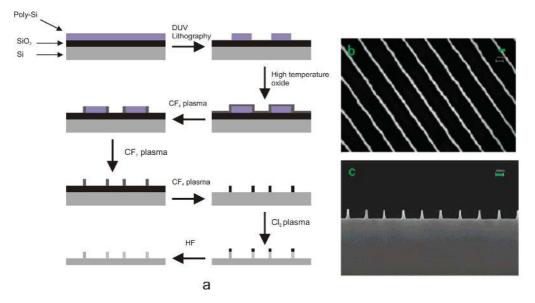

ted with DUV lithography to create Si wires of sub-20 nm wide and 110 nm high with ca. 250 nm pitch [23]. The fabrication process flow and results are shown in Figure 1.5. Moreover, it was demonstrated that the Si mold was successfully utilized as stamp in T-NIL together with metal lift-off to fabricate Pt nanowires [23].

Figure 1.5: Si mold fabrication by Yan et al. [23]: (a) Schematic drawing of the size reduction lithography process flow; (b),(c) SEM images of the final fabricated Si nanostructures of 16 nm wide and 110 nm high with 250 nm pitch.

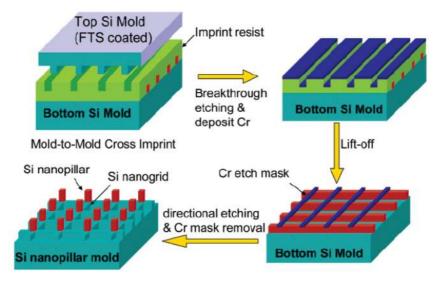

In addition to making grating patterns, Kwon *et al.* utilized the mold with Si nanowires fabricated by the size reduction lithography to create Si nanopillars by mold-tomold cross imprint (MTMCI) techniques [24]. Figure 1.6 shows the schematic of MTMCI. Different from conventional NIL procedures, the fabricated Si mold was used both as the imprint substrate and stamp. The grating pattern was imprinted into the polymer in a perpendicular direction to the gratings on the substrate. After residual layer removal to expose the grating pattern on the substrate, Cr was evaporated followed by a lift-off step to create Cr gratings standing on top of Si gratings on the substrate. Si nanopillars were created through directional plasma etching using Cr as the mask. Since both the Si and Cr gratings function as the etching mask, the Si nanopillars were formed standing on the intersection of the square fields on the substrate wafer. The fabrication results of Si nanopillars are shown in Figure 1.7.

The examples shown above share the basic idea of using the thin film deposited at

Figure 1.6: Schematic of MTMCI taken from Kwon et al. [24].

Figure 1.7: SEM images of nanopillars made by MTMCI taken from Kwon *et al.* [24]:(a) Top view; (b) angled view.

the vertical step edges as the etching mask for the followed pattern transfer steps. The fabrication of smooth vertical step edges then becomes the primary requisite for the success of these fabrication schemes. Since the thin film deposited at step edges is within few hundreds of nanometers, plasma etching is chosen over wet etching considering its directionality and selectivity. As in the SEM images shown above, the fabricated nano-structures do not have perfect vertical sidewall profiles, which can be a result of plasma etching chemistry, mask layer quality, etc. Processed in a different approach, Gabriec *et*

al. fabricated SiO<sub>2</sub> nano-lines created by oxidizing poly-Si step edges using  $Si_3N_4$  as the mask [25]. The fabrication scheme is shown in Figure 1.8.

Figure 1.8: SiO<sub>2</sub> nano-lines fabrication by Gabriec *et al.* [25].

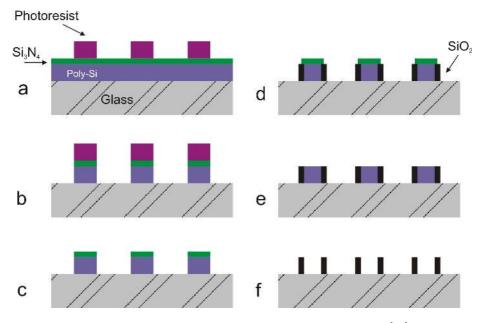

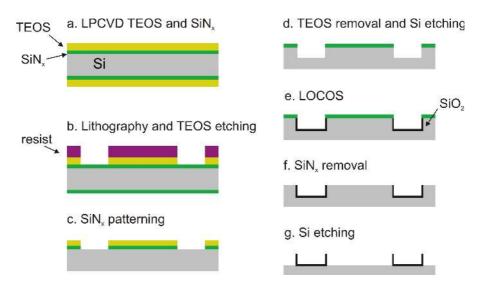

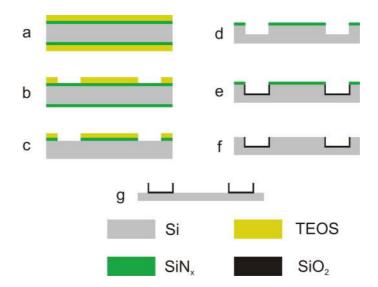

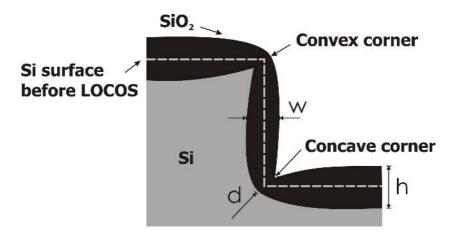

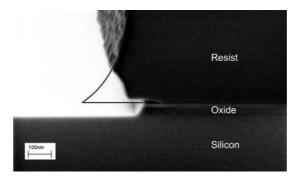

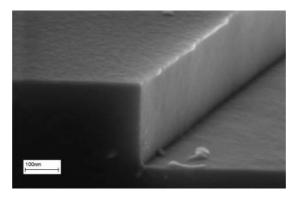

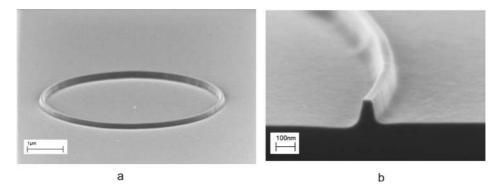

In nanofabrication, a smooth surface is always preferred and has always been addressed, especially for fluidic and nanoimprint applications. Therefore, researchers have explored the use of wet chemical etching taking advantage of Si crystalline orientations to create smooth vertical sidewalls to function as edges. Gabriec and co-workers elicited the idea of using mono-crystalline Si to fabricate step edges with vertical sidewalls using wet etching methods [25, 26]. In an attempt to improve accuracy and to show its use in T-NIL, Haneveld *et al.* created  $SiO_2$  nanoridges by local oxidation of sharp edges in <110> Si wafers using a full-wet procedure and silicon rich nitride (SiN<sub>x</sub>) as the mask [27]. Figure 1.9 is the schematic of the SiO<sub>2</sub> nanoridge fabrication process. The smooth vertical sidewalls were created by using  $\langle 110 \rangle$  Si wafer and normal photoresist developer OPD 4262, which contains 2.5% of TMAH and other organic solvents. OPD 4262 has a low etch rate of 3.7 nm/min on <110> Si planes and provides smooth surface finish to both <110> and <111> planes. SiO<sub>2</sub> nanoridges were created by oxidizing the smooth vertical Si sidewalls using  $SiN_x$  as the mask. Liang *et al.* also demonstrated the fabrication of Si nano-lines utilizing Si <110> SOI substrates and wet anisotropic Si etching for S-FIL [28].

Figure 1.9: SiO<sub>2</sub> Nanoridge fabrication by Haneveld *et al.* [27].

#### Repeated edge lithography

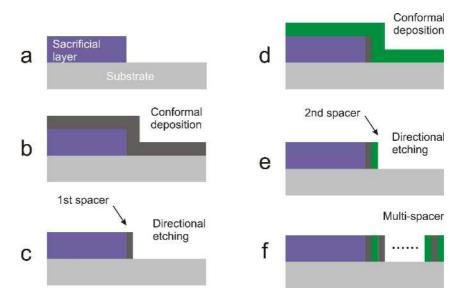

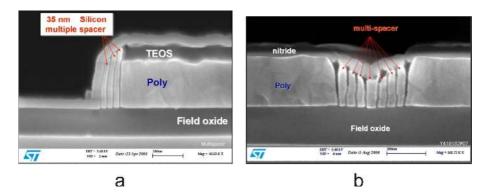

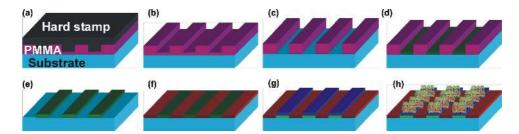

Multi-nanostructures can be generated by sequential conformal material deposition and selective etching steps. Cerofolini *et al.* demonstrated the multi-spacer patterning technique (M-SPT) which was shown to have potential in nanoelectronics applications [29, 30]. The M-SPT fabrication scheme generally comprises the following steps, as shown in Figure 1.10: (a) sacrificial structures with vertical sidewalls patterned by photolithography and directional etching; (b) conformal deposition of one layer; (c) maskless directional etching of this layer to fabricated the first spacer; (d)-(e) the formation of the second spacer by conformal deposition of another layer and maskless directional etching; (f) multi-spacer formation by repeating step (b) to (e). Poly-Si deposition and thermal oxidation of the poly-Si layer were alternated to create multi-spacer made of poly-Si and SiO<sub>2</sub>. The fabrication results are shown in Figure 1.11.

Other researchers have also demonstrated the fabrication of spacer-like structures employing similar working principles to SPT. Choi *et al.* demonstrated the fabrication of nanoscale phosphosilicate glass (PSG) complementary metal oxide semiconductor (CMOS) by conformal deposition of PSG over a SiGe block pattern [31]. Degroote *et al.* used SPT in combination with resist-based patterning to define a Si-Fin with a critical dimension below 20 nm [32].

As an alternative to M-SPT, Sonkusale et al. developed the so-called planar edge

Figure 1.10: Multi-spacer patterning technique by Cerofolini et al. [29].

Figure 1.11: SEM images of cross-section of multi-spacer structures fabricated by Cerofolini *et al.*: (a) Three spacers; (b) seven spacers. Images are taken from [29].

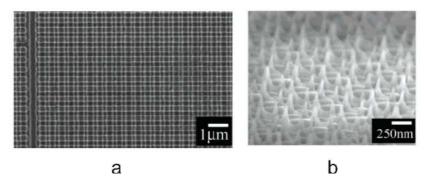

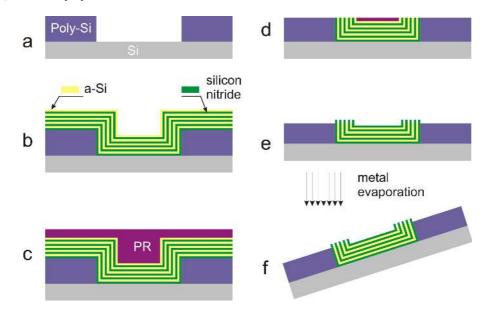

defined alternate layer (PEDAL) process to fabricate nanowires for NIL application [33, 34]. Figure 1.12 shows the schematic drawing of PEDAL process flow. The fabrication started with the creation of poly-Si sacrificial structure with vertical sidewalls on top of Si substrates by RIE. Then silicon nitride of 25 nm and amorphous-Si (a-Si) of 50 nm were alternately deposited over the created trench structures. After deposition, the trench was planarized by spinning organic polymer followed by etching the polymer,

silicon nitride and a-Si by RIE. The planaization was finished until the poly-Si sacrificial layer was reached. Either silicon nitride or a-Si nanowires can be fabricated by selective etching either of these materials. SEM images shown in Figure 1.13 confirm the successful fabrication of a-Si nanowires of 25 nm wide with 50 nm spacings. Moreover, Hussain *et al.* also employed a similar process flow to fabricate Si nanowires as template for NIL applications [35].

Figure 1.12: Process scheme of nanowire fabrication by PEDAL process by Sonkusale *et al.* [33, 34]

Figure 1.13: SEM images of nanowires fabricated by PEDAL process by Sonkusale et al. [33]

# 1.3 Micromachining technology as a tool for stamp fabrication

Micromachining is the term used to describe fabricating micron-sized features. Generally, this technology is referred as micro-electro-mechanical system (MEMS), micromachines (in Japan) or micro systems technology (MST in Europe). Micromachining process is initially borrowed from IC industry with additional adaptations specifically to silicon micromachining. The micromachining process generally consists of material deposition, lithographic patterning and etching techniques. Many studies provide general introduction to micromachining techniques [36, 37].

#### 1.3.1 Deposition methods

Epitaxy, sputtering, evaporation, chemical-vapor deposition (CVD), and spin-on methods are common deposition methods to obtain uniform layers of semiconductor materials, metals, insulators, and polymers.

Epitaxy is a deposition method to grow crystalline silicon with different dopant and concentration over crystalline substrates such as silicon and sapphire (Al<sub>2</sub>O<sub>3</sub>). It is a widely used step in CMOS fabrication and is efficient in forming wafer-scale p-n junctions for controlled electrochemical etching.

Amorphous silicon dioxide is obtained by oxidizing silicon in either dry oxygen or water vapor environment, which are generally referred as dry and wet oxidation. The oxidation process is performed at a elevated temperature between 800°C and 1200 °C. Oxidation mechanisms have been extensively studied [38, 39, 40]. Oxide quality and thickness with respect to temperature, oxidation environment and time are also well documented [41].

Sputtering and evaporation are the common methods for metal as well as insulating materials deposition. In sputtering deposition, a target made of a material to be deposited is physically bombarded by a flux of inert gas (usually argon) in a vacuum chamber at a pressure of 0.1-10 Pa. Target atoms or molecules are ejected and deposited onto the wafer. When the target size is larger than the wafer size, the directional randomness of the sputtering process results in good step coverage. In an evaporation process, a source material is heated up to a high temperature to generate a vapor which condenses on a substrate to form a film. It is performed in a vacuum chamber with a background pressure typically below  $10^{-4}$  Pa to avoid film contamination. The source material can be heated either by electrical current running through a resistor or by scanning a high voltage (e.g. 10 kV) electron beam over. The evaporation process is a directional deposition process

from a relatively small source, which results in material deposition under an angle to the wafers and hence causes poor step coverage.

Chemical vapor deposition (CVD) initiates chemical reactions of reactive species in a controlled atmosphere on heated substrates. In contrast to sputtering, CVD is a high temperature process which is usually performed above 300°C. Common thin films deposited by CVD include amorphous/poly-silicon, silicon oxide, silicon nitride, tungsten, titanium and tantalum as well as their nitrides, and most recently, copper and low-permittivity dielectric insulators. CVD processes are further categorized into atmospheric-pressure (APCVD), low-pressure (LPCVD) and plasma-enhanced (PECVD). APCVD and LPCVD work at high temperatures, e.g. 400°C to 800°C. In PECVD, the substrate is normally heated up to ca. 300°C. Substrate temperature, gas flow, presence of dopants, and pressure are important process variables for all types of CVD.

Poly/amorphous silicon, LPCVD silicon oxide and silicon nitride are the most common materials that can be obtained by CVD methods. Polysilicon is deposited by pyrolysis of silane (SiH<sub>4</sub>) to silicon and hydrogen at a temperature typically between 550°C and 700°C. It is also possible to do the deposition in a low pressure PECVD reactor which will result in amorphous silicon.

Silicon oxide deposited at a temperature below 500°C by silane and oxygen reaction in an APCVD, LPCVD or PECVD reactor is called low-temperature oxide (LTO) due to the low temperature deposition process. LTO is often used for passivation coating on aluminum, in which case the deposition temperature should be kept below 400°C to avoid Al layer degradation. The silicon dioxide deposited in a LPCVD reactor at a temperature between 650°C and 750°C by pyrolysis of tetraethoxysilane (Si(OC<sub>2</sub>H<sub>4</sub>)<sub>4</sub>) is referred as TEOS. Another method used for silicon dioxide deposition utilizes dichlorosilane (SiCl<sub>2</sub>H<sub>2</sub>) reacting with nitrous oxide (N<sub>2</sub>O) in a LPCVD reactor at a temperature near 900°C.

Stoichiometric silicon nitride  $(Si_3N_4)$  is deposited at atmospheric pressure by reacting silane  $(SiH_4)$  and ammonia  $(NH_3)$  or at low pressure by reacting dichlorosilane  $(SiCl_2H_2)$ and ammonia. The deposition temperature for either method is between 700°C and 900°C. Both CVD and LPCVD deposit silicon nitride with a high tensile stress approaching 1000 MPa. For some micromachining applications, to reduce the tensile stress, silicon rich nitride is deposited in a LPCVD reactor at a temperature between 800°C to 850°C, which results in a tensile stress around 100 MPa.

Unlike the deposition described above, the spin-on method is a simple process in which dielectric insulators and organic materials can be coated. The equipment is simple and a variable tunable spin-coater normally meets the requirement. Organic materials can be either dispensed on a wafer surface by a nozzle or manually. Spinning can be carried out at a speed between 500 to 5000 rpm for 30 to 60 s to obtain a uniform layer thickness. The spinning rate is tuned according to the specific layer thickness requirement and polymer properties.

#### 1.3.2 Wet etching

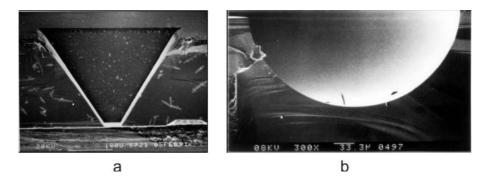

Wet chemical etching is one of the key technologies in micromachining. The methods are generally categorized into isotropic and anisotropic mechanisms. In isotropic etching, materials are removed at the same speed in all directions. Amorphous materials are generally etched isotropically by wet chemical solutions, such as hydrofluoric acid (HF) solutions used for SiO<sub>2</sub> etching, and 50% HF and phosphoric acid (H<sub>3</sub>PO<sub>4</sub>) for silicon nitride etching. In contrast, in anisotropic etching, the etching is preferable to some directions over others, which results in cavities with vertical or slanted sidewalls. Si anisotropic etching by strongly basic solutions (e.g. KOH) is the most commonly used type of anisotropic etching. Figure 1.14 shows the SEM images of anisotropically and isotropically etched Si cavities.

Figure 1.14: SEM images (a) Anisotropically etched Si cavity by EDP solutions; (b) Isotropically etched Si cavity by a solution made of HNO<sub>3</sub>:HF:CH<sub>3</sub>OOH. Images are taken from [42].

#### Anisotropic Si etching

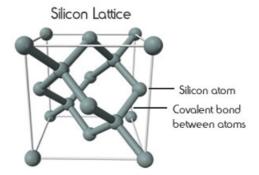

Anisotropic silicon etching stems from etch rate differeces depending on silicon crystal orientation and wet chemicals. The crystal structure of silicon is of diamond type and has a lattice constant a = 5.43Å. The lattice structure, as illustrated in Figure 1.15, is face centered cubic (FCC) with two atoms in the unit cell, which are 1/4a along the main

diagonal of the cube. Crystal planes are characterized by sets of three indices, the so

Figure 1.15: Illustration of silicon lattice

called Miller indices. Generally <111> Si planes show the slowest etch rate. Therefore, different shapes of structures can be realized by utilizing <100> and <110> oriented Si wafers to stop etching automatically at <111> Si planes. The Si anisotropic etch rate depends on etchant, temperature, concentration of the etchant, doping of the substrate and stirring [43]. Seidel *et al.* reported reviews over Si etching depending on its crystal orientation as well as the influence of doping [44, 45].

Anisotropic Si wet etching can be performed using aqueous alkali-hydroxide solutions, EDP solutions (ethylendiamine, pyrocatechol, and water),  $NH_4OH$ , and tetramethyl ammonium hydroxide ((( $CH_3$ )<sub>4</sub>NOH,TMAH). EDP solution is the earliest wet chemical explored for Si etching. It is toxic and degrades with ease when it is in contact with oxygen. Moreover, precipitation of silicates occurs after Si etching. At present, therefore, KOH and TMAH are the most commonly used less dangerous Si etchants. KOH is less dangerous, easy to handle and has fast etch rates. The etch rate is proportional to  $[H_2O]^4[KOH]^{1/2}$  and therefore shows its maximum at a KOH concentration of 20 wt% [44]. Futhermore, temperature exerts a much larger influence on the etch rate than the silicon crystal orientation [44]. Since KOH generally shows poor selectivity to oxide, silicon nitride is suggested as the appropriate masking material in Si etching using KOH. A disadvantage of Si etching by KOH is that potassium ions remain on the Si surface after etching, which makes it not compatible with IC fabrication. For MEMS purposes, for example, before oxidation, a RCA2 cleaning step  $(HCl:H_2O:H_2O_2=1:5:1, heated up$ to 80°C, the wafers are immersed in the solution for 10 to 15 min) should be performed to remove all the metal ions to avoid furnace contamination.

TMAH is also a nontoxic and easy to handle Si etchant. It is an organic solution

therefore it is compatible with IC fabrication. Researchers have investigated the etch rate of Si in TMAH solutions as a function of the temperature and concentration [46, 47, 48]. Tabata *et al.* reported that the etch rate of <100> and <110> Si planes decreases with increase of the concentration from 5 to 40 wt% [46]. The smoothness of both types of Si planes improves with the increase of the TMAH concentration and the most smooth bottom surface for <100> and <110> Si planes appears at concentrations of 22 wt% and 30 wt% respectively. The ratio of the etch rates between <111> and <100> planes varies between 0.02 to 0.05 with the maximum at a concentration of 22 wt%. The etch rate of thermal SiO<sub>2</sub> is almost 4 orders of magnitude lower than that for the <100> and <110> planes.

#### Isotropic etching thin films

Silicon dioxide and silicon nitride are the most commonly used mask materials for MEMS applications. Silicon oxide can be obtained by either wet or dry oxidation or by means of LPCVD, e.g. of LTO and TEOS. It is easily etched in HF solutions, e.g. 1%HF, BHF and 50%HF. In wet anisotropic Si etching, SiO<sub>2</sub> is a good mask when EDP and TMAH are used as the etchants. However, the fast etch rate of SiO<sub>2</sub> in KOH solutions makes it a less favorable masking material in this case. Silicon nitride can be etched in both phosphoric acid (H<sub>3</sub>PO<sub>4</sub>) at 160°C-180°C and 50%HF. The high selectvitivity between silicon oxide and silicon nitride in hot H<sub>3</sub>PO<sub>4</sub> acid and 50%HF, which is about 10:1 and 1:100, is utilized for selectively etching each other. Silicon nitride exhibits an extremely low etch rate in KOH solutions and hence is a good mask for Si anisotropic etching by KOH.

#### 1.3.3 Plasma etching

Wet chemical etching is easy to handle and allows batch processing. However, the design flexibility is compromised by wet Si etching due to the Si crystal orientation dependence. Therefore, dry plasma assisted etching is introduced and is increasingly used due to its ability of faithfully transferring patterns from the mask layers into Si without relying on Si crystal orientation and its cleanliness and compatibility with vacuum processing technologies.

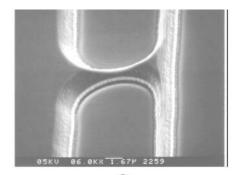

Plasma is generated when a voltage is applied in a reactor. Plasma etching can be categorized into physical plasma etching and chemical reaction etching. In physical plasma etching, as shown in Figure 1.16 (a), ion bombardment dominates the etching process while the influence of radicals is neglected. Chemical reactive etching involves the generation of chemically reactive neutrals (radicals) and ions that are accelerated under the effect of an electric field toward a target substrate. When the etching process is purely chemical, which is dominated by radicals reacting with substrate materials, as in a barrel system, it is referred to as *plasma etching*. Isotropic profiles are achieved by pure chemical radical etching, which is shown in Figure 1.16 (b). When ion bombardment is involved in the process and plays a synergistic role, the process is called *reactive ion etching* (RIE). Figure 1.16 (c) shows a structures with vertical sidewalls obtained by RIE.

Figure 1.16: SEM images showing the basic mechanisms of dry plasma etching: (a) physical plasma etching; (b) Pure chemical radical etching; (b) RIE: ion bombardment plays the synergistic role. Images are taken from [42].

#### **Reactive ion etching**

The chemically reactive species generated in plasma include neutrals (N), radicals (R), electrons (E), ions (I), photons (P), and phonons (T). The photons are responsible for the characteristic glow of the plasma. The *glow region* is full of electrons and only a small electrical field exists. The energetic particles in the glow region are transported to

a sample surface through the plasma boundary layer. The charged species recombine at the walls of plasma boundaries. In the adjacent region, electrons and ions diffuse to the sample, better known as *sheath region*. A strong electrical field exists in the *sheath region* which brings ions and reactive species to the sample surface while drives electrons and negative ions away from the surface. Radicals have only thermal energy and will leave the boundary layer for the sample surface in all directions while the ions will leave the boundary layer under an angle of 90°. Since electrons are much more mobile than ions, the sheath region can be modeled as a rectifier. The thickness of the sheath is related to the electron mean free path, and increases with decreasing gas pressure.

#### Etching mechanism

In the basic RIE system, an rf glow discharge is used to generate from a suitable feed gas (e.g.  $SF_6$ ,  $CF_4$ ,  $Cl_2$ ,  $CHF_3$ ,  $NF_3$ ) by electron-impact dissociation/ionization. The etching plasma gas consists of neutrals, electrons, photons, radicals and positive and negative ions. The substrate or wafer is placed on an rf driven capacitively coupled electrode. During etching, electrons are attracted to the substrate since they are more mobile than the ions are. Therefore, negative charge is formed on the electrode after the ignition of plasma, which is also referred to as dc self-bias voltage. The reactive species travel from the bulk of the plasma to the wafer by diffusion. Positive ions are forced to the electrode as a result of the dc-bias voltage formation, which will also assist etching. Reactive species first adsorb on the substrate, which can be assisted by ion bombardment by creating active sites for adsorption. Then the reaction between the reactive species and the wafer surface takes place. When this process is enhanced by ion bombardment, it is called ion-induced RIE. The desorption of the reaction products into the gas phase requires the reaction products to be volatile. Moreover, when blocking film is formed, it should be removed by ion bombardment via sputtering. This mechanism is also called ion-inhibitor RIE. The desorbed species into the bulk of plasma should be pumped out to avoid redeposition. Detailed discussion about plasma, such as etching mechanism, chemistry, surface finish, etc., can be found else where [49, 50, 51].

Chlorine and bromine containing plasmas have in the beginning been widely used for Si etching due to their fast etch rates and high anisotropy. However, such gases are corrosive and toxic to reactor materials and more importantly hazardous to environment [52]. Fluorine containing gases such as  $CF_4$  and  $SF_6$  are less corrosive and toxic and show higher selectivity to masking materials. Therefore, F-based plasma etching is now playing a dominant role in Si etching in MEMS applications.

The basic mixed plasma etching is reactive ion etching with two or more gas mixtures

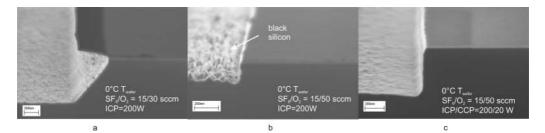

performed at room temperature, such as  $SF_6/O_2$  and  $SF_6/O_2/CHF_3$  gas mixtures [53, 54]. To achieve anisotropic etching profile, plasma etching are generally performed by mixed or pulsed processes. The two most distinguished approaches are the so-called Bosch process developed by Laermer and Schilp [55] and the cryogenic RIE developed by Tachi *et al.* [56]. The Bosch process is a room temperature process with continuously alternating etching and passivating steps. It is able to provide a fast Si etch rate with scallop sidewall finish. Typically, a Si etch rate of 2  $\mu$ m/min and selectivity to resist of 75:1 can be achieved. Cryogenic etching uses low bias F-based high density plasma with lowered Si substrate temperature. The sidewall passivation is enhanced by lowering the substrate temperature such that the reactivity of F-radicals is decreased and ion bombardment dominates the bottom passivation cleaning and etching.

#### Flurocarbon based etching

Mogab *et al.* studied the etching of Si using  $CF_4$  etching Si and indicated that the etch rate is directly related to the F atom density [57]. A  $CF_4$  plasma produces  $CF_3^+$ ,  $CF_3$ , F,  $CF_3^-$  and F<sup>-</sup>, in which negative ions ( $CF_3^-$  and F<sup>-</sup>) do not usually contribute to the etching while both  $CF_3$  radicals and  $CF_3^+$  react readily with clean Si surface [58, 59, 60].

The use of CF<sub>4</sub> plasma with the addition of hydrogen and oxygen to control the etch rate of Si and SiO<sub>2</sub> was first reported by Heinecke in 1975 [61]. The addition of hydrogen to CF<sub>4</sub> plasma has two effects: (1) H<sub>2</sub> reduces the F-atom density by forming HF and hence decreases the etch rate of Si; and (2) H<sub>2</sub> reacts with CF<sub>3</sub> radicals forming a  $C_xF_y$ film on the Si surface which stops Si etching. Therefore hydrogen addition into CF<sub>4</sub> plasma increases the etching of SiO<sub>2</sub> by suppressing the attack of Si [61, 62, 52].

The etch rate of Si is increased with the addition of  $O_2$  into  $CF_4$  glow discharge [63, 64, 65, 66]. There are several speculations concerning the reaction between  $CF_4$  and  $O_2$ , such as the oxidation of  $CF_4$  in the gas phase to form  $CF_3O_2$ , oxidation of carbon on the etched surface in the vacuum system, or oxidation of the fluorocarbon polymer deposited on surfaces [49]. The overall consequence, however, is generally the same, that is a carbon-oxygen bond is formed (e.g., CO,  $CO_2$  or  $COF_2$ ), which suppresses recombination reactions [58]. The maximum Si etch rate is obtained when the  $O_2$  content produces the maximum F atom concentration and the oxidation of Si surface limits the etching reaction [63, 66]. At low  $O_2$  percentage, the increase of Si etch rate is due to the decrease of the  $Si_xO_yF_z$  layer thickness as a result of rise of the F concentration. The  $Si_xO_yF_z$  layer grows thicker as a result of increased oxidation and decreased fluorination of the Si surface with the increase of  $O_2$  content in  $CF_4/O_2$  mixture [66]. In contrast, the etching of SiO<sub>2</sub> with  $CF_4/O_2$  plasma is different from that of Si since there is no significant retarding

effect of oxygen [57, 67]. Oehrlein*et al.* accomplished the removal of fluorocarbon residue after  $CF_4/40\%$  H<sub>2</sub> RIE by annealing samples in O<sub>2</sub> ambient at 400°C followed by BHF etching [68].

The CHF<sub>3</sub>/CF<sub>4</sub> based plasma was also implemented to tune the desired selectivity between Si and SiO<sub>2</sub>. Oehrlein *et al.* investigated the Si and SiO<sub>2</sub> using CF<sub>4</sub> and CHF<sub>3</sub> in an electron cyclotron resonance (ECR) discharge system [69]. It is suggested that oxideto-silicon etch selectivity is a result of selective fluorocarbon film deposition onto the silicon surface which prevented Si etching, which is ca. 5.5 nm and 2.5 nm in CHF<sub>3</sub> and CF<sub>4</sub> plasma respectively. Standaert *et al.* proposed the mechanism that silicon etching in a fluorocarbon plasma involves the diffusion of reactive and volatile species through a fluorocarbon steady state layer [62]. This mechanism has been proven to be applicable when ICP is used to generate CHF<sub>3</sub> plasma to etch Si and SiO<sub>2</sub> [70]. The experimental results obtained by Rolland *et al.* also suggested that the selectivity between Si/SiO<sub>2</sub> was considerably improved by adding CH<sub>4</sub> to CHF<sub>3</sub> by means of the formation of 6 nm thick fluorocarbon residue [71].

#### $SF_6$ based etching

To circumvent carbon deposition on Si surface, SF<sub>6</sub> was investigated as a proper etchant for Si etching [72]. Eisele first reported that SF<sub>6</sub> is able to achieve a high Si etch rate without the addition of O<sub>2</sub> [73]. SF<sub>6</sub> dissociates into F and SF<sub>x</sub> radicals that react readily with Si and the end product is SiF<sub>4</sub>, which is a volatile gas and can be pumped out. No sulfuric residue is found on the Si surface after etching. Flamm studied the reaction of fluorine with silicon and concluded that F radicals dominate the etching, which results in isotropic characteristics [74]. SF<sub>6</sub>/O<sub>2</sub> is an alternative to CF<sub>4</sub>/O<sub>2</sub> for plasma etching of Si and SiO<sub>2</sub>. A general review of the etching mechanism of Si in SF<sub>6</sub>/O<sub>2</sub> plasma has been given by Ryan *et al.* [75]. The addition of O<sub>2</sub> into SF<sub>6</sub> increases the etch rate of Si, which has a similar effect as the adition of O<sub>2</sub> to CF<sub>4</sub> plasma. d'Agostino investigated the etching mechanism of Si and SiO<sub>2</sub> in SF<sub>6</sub>-O<sub>2</sub> mixture [76]. Different from O atoms competing with F atoms for chemisorption on a Si surface in CF<sub>4</sub>/O<sub>4</sub> plasma, the increase of O<sub>2</sub> content in a SF<sub>6</sub>/O<sub>2</sub> mixture leads to a greater oxygen coverage and a lower etch rate. It was also suggested that the etch rates in SF<sub>6</sub>/O<sub>2</sub> plasma are 5 to 10 times faster than those in CF<sub>4</sub>/O<sub>4</sub> plasma under the same conditions.

When  $SF_6$  is used in mixed RIE at room temperature, it is common to have both  $O_2$  and  $CHF_3$  as the inhibitors for sidewall passivation. When a  $SF_6/CHF_3$  combination is used,  $CHF_3$  forms  $CF_2$  by dissociation which works as a sidewall inhibitor [77, 78, 79]. It has also been demonstrated that the etch rate and etching anisotropy are influenced

by SF<sub>6</sub>/CHF<sub>3</sub> percentage, power supply and pressure. As discussed above, the addition of O<sub>2</sub> will increase the F-atom density preventing it from recombination into SF<sub>6</sub>. A competition exists between O<sub>2</sub> and CHF<sub>3</sub>, in which the former one forms the passivating SiO<sub>x</sub>F<sub>y</sub> layer while the latter one removes it. The addition of O<sub>2</sub> helps subtly control profile [54, 80].

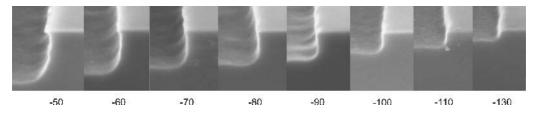

In the late 1980s, Tachi *et al.* introduced the idea of low-temperature RIE [56]. The results showed that Si trenches with vertical sidewalls were achieved and high selectivity between Si, SiO<sub>2</sub> and photoresist are obtained at a temperature from -110°C to -130°C. The cryogenic Si etching is made possible since sidewall etching by radicals is suppressed by lowering the substrate temperature while the etching at the Si bottom surface is not largely influenced because ion bombardment dominates reactive ion etching [81, 82, 83, 84]. It was observed that the cooling temperature should go below -140°C to avoid SF<sub>6</sub> freezing on the Si surface, which is in correspondence with the results obtained earlier by Oostra and co-workers, who first investigated the reaction of Si with SF<sub>6</sub> with Ar<sup>+</sup> ions bombardment at low temperatures and concluded that new molecular products can be formed at a temperature down to 100 K [85]. Moreover, Tsujimoto *et al.* demonstrated that cryogenic Si etching shows a Si crystal orientation dependence down to -150°C [86]. The performance of SF<sub>6</sub>/O<sub>2</sub> mixture etching Si at cryogenic temperature depends on many factors, e.g. gas flow, oxygen concentration, ion impact, temperature, etc [87].

#### Parameters influencing etching

The performance of plasma is influenced by factors such as system configuration, pressure, temperature, gas flow, loading, etc. Jansen *et al.* analyzed the RIE process in the aspects of system settings, equipment parameters, plasma characteristics and trench forming mechanisms [88]. Chapman *et al.* first investigated the dependence of plasma etching rates on the flow rate of the etching gas [89]. It was observed that the decrease of etch rate with the decrease of gas flow is due to insufficient gas supply and the etch rate can also be reduced because of the pumping of active species with very high flow rates [89]. The flow rate dependence of etching has further implications to other etching parameters such as preferred flow rate, pressure and flow changes, etching selectivity, etch uniformity, etc. [90]. Pressure has a major influence on plasma etching by the sheath potentials and ion bombardment energy, the electron energy, the ratio of ions to neutrals, the rate of chemical kinetics, etc. Temperature has a profound influence on discharge chemistry in plasma etching, as discussed in cryogenic etching, which is differed from gas temperature and substrate temperature.

The etch directionality is mainly determined by the directed energy into an etching

reaction, which can be accomplished by neutral, ion, electron, or photon bombardment of a surface exposed to a chemical etchant. Gerlach-Meyer *et al.* performed the famous experiment of Si etching using XeF<sub>2</sub> molecules with and without 1 keV Ne<sup>+</sup> bombardment to prove the dependence of directional etching on ion bombardment [91]. Jansen *et al.* have done an extensive study regarding various aspects influencing the performance of deep reactive ion etching (DRIE) with respect to Si etch rate, etch profile and selectivity to mask materials [92].

#### 1.4 Aim of the research and thesis outline

The thesis describes the research results obtained for high resolution stamp fabrication for thermal nanoimprint lithography applications. As described in the preceding sections, many researchers have explored the possibilities of fabricating nanostructures by edge lithography in combination with Si micromachining technologies utilizing either conventional UV lithography or high resolution lithography for pattern definition. In this project, we have investigated the fabrication of nanoridges originating from  $SiO_2$  nanoridge fabrication by oxidizing vertical Si sidewalls using  $SiN_x$  as the mask [27]. The fabricated  $SiO_2$  shows sub-20 nm resolution, however, the fragile nanoridge properties prevent the stamp from re-use in T-NIL. Consequently, we have developed the concept of advanced edge lithography to produce Si nanoridges made of crystalline Si and repeated advanced edge lithography to create multi-Si nanoridges taking advantage of Si anisotropic etching. The mechanical strength has been greatly improved and the stamps have been successfully applied in T-NIL. Furthermore, Si plasma etching is integrated into the advanced edge lithography scheme to produce Si nanoridges with arbitrary contours independent of Si crystal orientation. Finally, we show the application of Si nanoridges in alternative nanofabrication approaches. The thesis is organized as the follows:

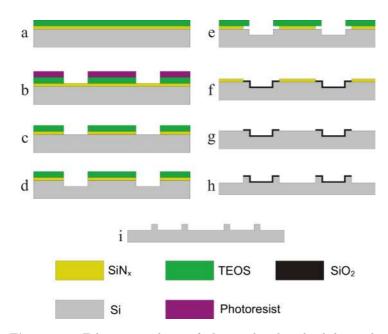

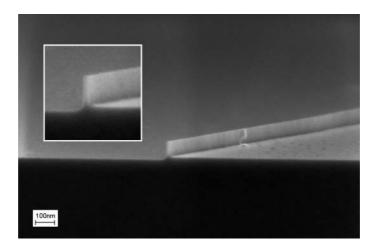

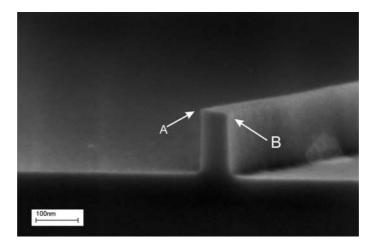

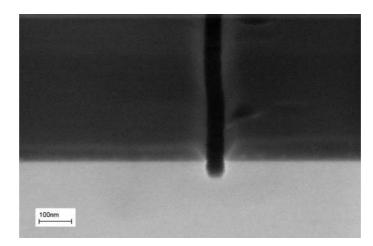

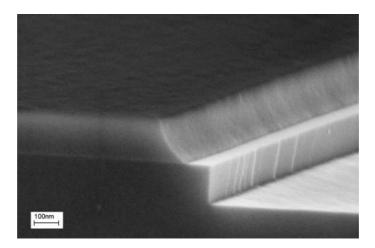

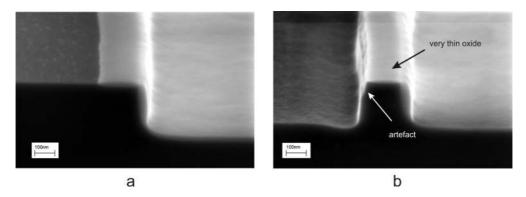

Chapter 2 describes the fabrication of a SiO<sub>2</sub> nanoridge stamp reinforced with silicon nitride for its use in nanoimprint lithography. The fabrication process is based on edge lithography using conventional optical lithography and wet anisotropic etching of <110>silicon wafers. SiO<sub>2</sub> nano-ridges of 20 nm in width were fabricated. A silicon-rich nitride layer is deposited over the original SiO<sub>2</sub> nano-ridges to improve the ridge strength and to achieve a positively tapered shape which is beneficial for T-NIL. A replica of the nanoridges with silicon-rich nitride shield is obtained by imprinting the stamp into thermoplastic nanoimprint polymer mr-I 7010E.

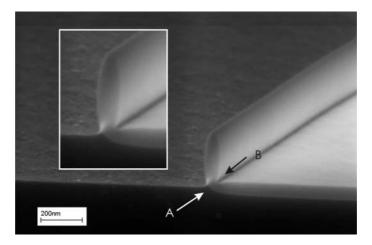

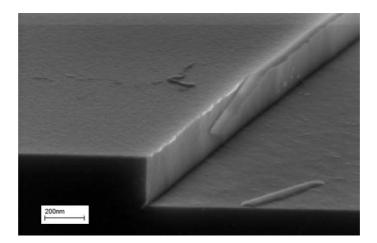

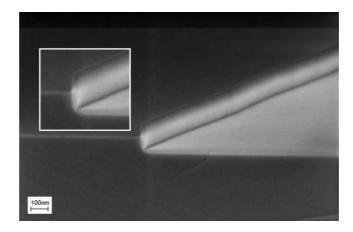

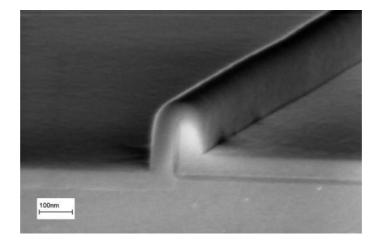

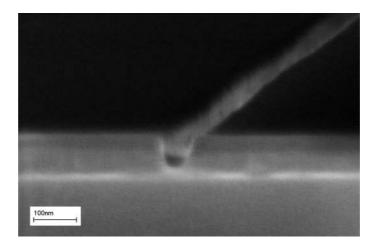

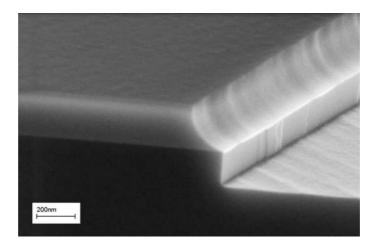

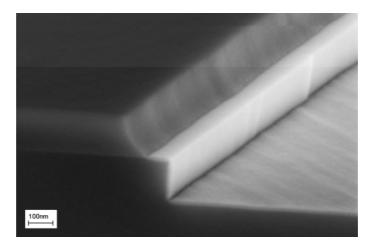

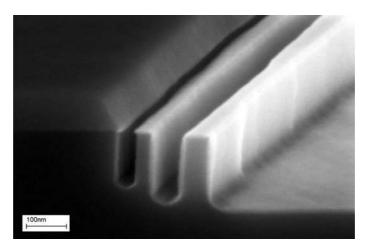

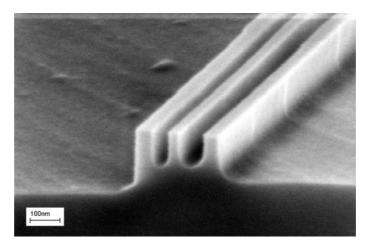

In Chapter 3, nanoridges are created in  $\langle 110 \rangle$  single crystal silicon using a full-wet etching procedure including local oxidation of silicon (LOCOS) and employing an adapted

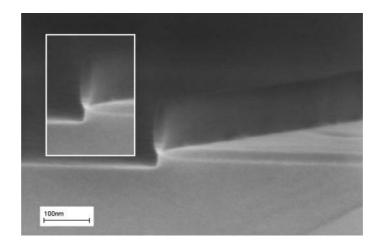

edge lithography technique on top of conventional photolithography. Ridges down to 10 nm in width have been produced. The silicon ridges have no inbuilt stress and are therefore less fragile than previously fabricated oxide ridges. The ridge sample is used as a template in T-NIL and a full 100 mm wafer size imprint has been successfully carried out in both polymethylmethacrylate (PMMA) and mr-I 7020E polymer. Moreover, the imprinted pattern in PMMA is subsequently transferred into a device wafer.

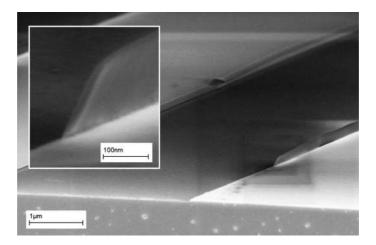

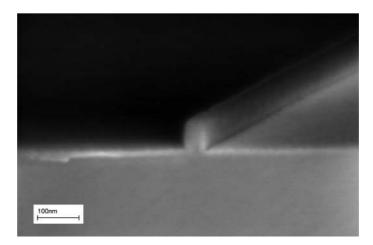

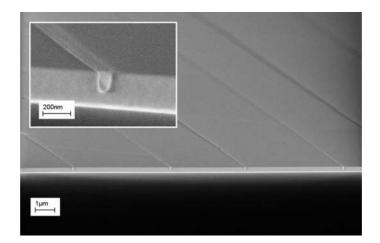

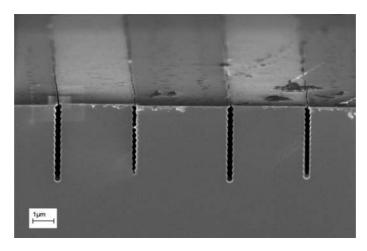

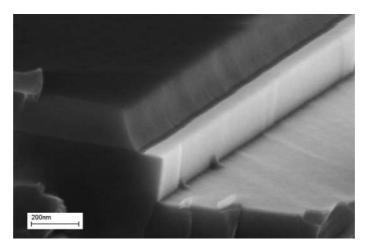

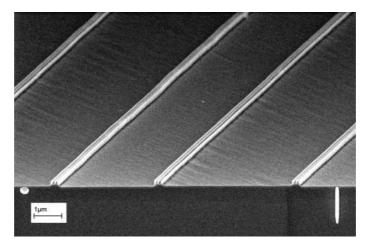

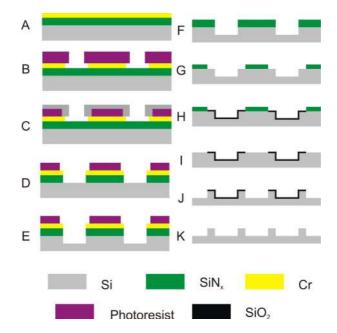

A multi-Si nanoridge fabrication scheme and its application in nanoimprint lithography (NIL) are presented in Chapter 4. Triple Si nanoridges approximately 120 nm high and 40 nm wide separated by 40 nm spacing are fabricated and successfully applied as a stamp in nanoimprint lithography. The fabrication scheme, using a full-wet etching procedure in combination with repeated edge lithography, consists of hot  $H_3PO_4$  acid  $SiN_x$ retraction etching, 20% KOH Si etching, 50% HF  $SiN_x$  retraction etching and LOCal Oxidation of Silicon (LOCOS). Si nanoridges with smooth vertical sidewalls are fabricated by using Si <110> substrates and KOH etching. The presented technology utilizes a conventional photolithography technique, and the fabrication of multi-Si nanoridges on a full wafer scale has been demonstrated.

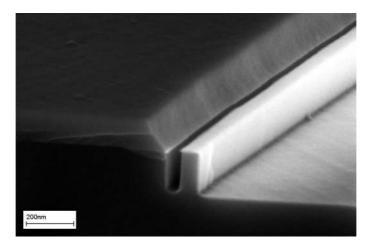

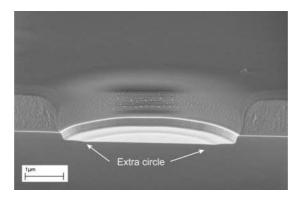

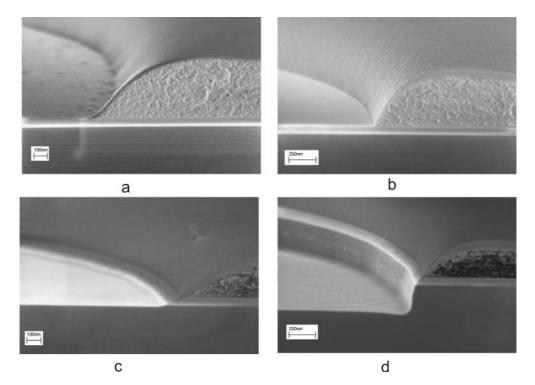

In Chapter 5, Si dry plasma etching technique is employed to integrate with advanced edge lithography method for nanoridge fabrication to avoid the dependence on Si crystalline orientation as to create Si nanoridges with arbitrary contours. We demonstrate the possibility of creating arbitrary contours by using a mask containing circular contour structures. Si etching using  $SF_6/O_2$  gas mixtures performed at cryogenic temperature using Alcatel/Adixen AMS 100 SE deep reactive ion etching (DRIE) system is explored and proven capable of providing a Si etch rate of ca. 70 nm/min with a smooth surface finish. The explored etching recipe is first used in combination with Cr functioning as the masking material. Although nanoridges with perfectly vertical sidewalls can be achieved, the introduction of Cr causes severe sidewall roughness due to Cr layer line edge roughness. Therefore, SU-8 2000.5 is later introduced as a proper material for pattern definition as well as a mask during Si cryogenic etching. Although the initial SU-8 pattern definition needs further improvement, we successfully demonstrate the fabrication of Si nanoridges having arbitrary contours with a smooth surface finish.

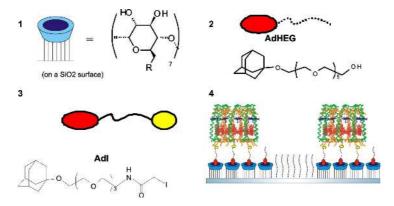

Chapter 6 presents the creation of nanostructures by means of self-assembly, microcontact printing ( $\mu$ CP) and capillary force lithography (CFL). The fabricated Si nanoridges with sub-100 nm width described in Chapter 3 are employed for high resolution pattern definition in thermal nanoimprint lithography (T-NIL) and CFL. T-NIL is successfully implemented with self-assembly and  $\mu$ CP respectively to function as alternative nanofabrication approaches. The thesis ends up with conclusions and outlook to the project.

## References

- S. Y. Chou, P. R. Krauss, W. Zhang, L. Guo, and L. Zhuang. Sub-10 nm imprint lithography and applications. *Journal of Vacuum Science and Technology B*, 15:2897– 2904, 1997.

- [2] M. Colburn, S. Johnson, M. Stewart, S. Damle, T. Bailey, B. Choi, M. Medlake, T. Michaelson, S. V. Sreenivasan, and J. Ekerdt. Step and flash imprint lithography: A new approach to high-resolution patterning. *Proceedings of SPIE - The International Society for Optical Engineering*, 3676(I):379–389, 1999.

- [3] H. C. Scheer, H. Schulz, T. Hoffmann, and C. M. Sotomayor Torres. Problems of the nanoimprinting technique for nanometer scale pattern definition. *Journal of Vacuum Science and Technology B: Microelectronics and Nanometer Structures*, 16(6), 1998.

- [4] L. J. Guo. Recent progress in nanoimprint technology and its applications. Journal of Physics D: Applied Physics, 37(11):R123–R141, 2004.

- [5] L. J. Guo. Nanoimprint lithography: Methods and material requirements. Advanced Materials, 19(4):495–513, 2007.

- [6] B. D. Gates, Q. Xu, M. Stewart, D. Ryan, C. G. Willson, and G. M. Whitesides. New approaches to nanofabrication: Molding, printing, and other techniques. *Chemical Reviews*, 105(4):1171–1196, 2005.

- [7] M. Geissler and Y. Xia. Patterning: Principles and some new developments. Advanced Materials, 16(15):1249–1269, 2004.

- [8] A. N. Broers. Resolution limits of PMMA resist for exposure with 50 kV electrons. Journal of The Electrochemical Society, 128(1):166–170, 1981.

- [9] V. A. Zlobin. Development of electron beam lithography for nanoscale devices. Proceedings of SPIE The International Society for Optical Engineering, 5824:23–32, 2005.

- [10] H. G. Craighead, R. E. Howard, L. D. Jackel, and P. M. Mankiewich. 10-nm linewidth electron beam lithography on GaAs. *Applied Physics Letters*, 42(1):38–40, 1983.

- [11] W. Chen and H. Ahmed. Fabrication of 5–7 nm wide etched lines in silicon using 100 keV electron-beam lithography and polymethylmethacrylate resist. *Applied Physics Letters*, 62(13):1499–1501, 1993.

- [12] A. A. Tseng, K. Chen, C. D. Chen, and K. J. Ma. Electron beam lithography in nanoscale fabrication: recent development. *Electronics Packaging Manufacturing*, *IEEE Transactions on*, 26(2):141–149, April 2003.

- [13] A. A. Tseng. Recent developments in micromilling using focused ion beam technology. Journal of Micromechanics and Microengineering, 14(4):R15–R34, 2004.

- [14] A. M. Hawryluk and L. G. Seppala. Soft X-ray projection lithography using an X-ray reduction camera. *Journal of Vacuum Science & Technology* B: Microelectronics and Nanometer Structures, 6(6):2162–2166, 1988.

- [15] B. Wu and A. Kumar. Extreme ultraviolet lithography: A review. Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures, 25(6):1743– 1761, 2007.

- [16] R. H. Dean and R. J. Matarese. Submicrometer self-aligned dual-gate GaAs FET. Electron Devices, IEEE Transactions on, 22(6):358–360, Jun 1975.

- [17] E. C. Jelks, G. L. Kerber, and H. A. Wilcox. A simple method for fabricating lines of 0.15-μm width using optical lithography. *Applied Physics Letters*, 34(1):28–30, 1979.

- [18] D. C. Flanders. X-ray lithography at ≈ 100 Å linewidths using X-ray masks fabricated by shadowing techniques. Journal of Vacuum Science and Technology, 16(6):1615– 1619, 1979.

- [19] D. C. Flanders and A. E. White. Application of ≈ 100 Å linewidth structures fabricated by shadowing techniques. Journal of Vacuum Science and Technology, 19(4):892– 896, 1981.

- [20] D. E. Prober, M. D. Feuer, and N. Giordano. Fabrication of 300-Å metal lines with substrate-step techniques. *Applied Physics Letters*, 37(1):94–96, 1980.

- [21] D. C. Flanders and N. N. Efremow. Generation of ≤ 50 nm period gratings using edge defined techniques. Journal of Vacuum Science and Technology B: Microelectronics and Nanometer Structures, 1(4):1105–1108, 1983.

- [22] Y. K. Choi, J. Zhu, J. Grunes, J. Bokor, and G. A. Somorjai. Fabrication of sub-10 nm silicon nanowire arrays by size reduction lithography. *Journal of Physical Chemistry B*, 107(15):3340–3343, 2003.

- [23] X. M. Yan, S. Kwon, A. M. Centreras, J. Bokor, and G. A. Somorjal. Fabrication of large number density platinum nanowire arrays by size reduction lithography and nanoimprint lithography. *Nano Letters*, 5(4):745–748, 2005.

- [24] S. Kwon, X. Yan, A. M. Contreras, J. A. Liddle, G. A. Somorjai, and J. Bokor. Fabrication of metallic nanodots in large-area arrays by mold-to-mold cross imprinting (MTMCI). *Nano Letters*, 5(12):2557–2562, 2005.

- [25] P. B. Grabiec, M. Zaborowsk, K. Domansik, T. Gotszalk, and I. W. Rangelow. Nano-width lines using lateral pattern definition technique for nanoimprint template fabrication. *Microelectronic Engineering*, 73-74:599 – 603, 2004.

- [26] M. Zaborowski, D. Szmigiel, T. Gotszalk, K. Ivanova, Y. Sarov, T. Ivanov, B. E. Volland, I. W. Rangelow, and P. Grabiec. Nano-line width control and standards using lateral pattern definition technique. *Microelectronic Engineering*, 83(4-9 SPEC. ISS.):1555–1558, 2006.

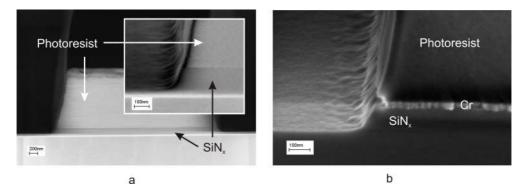

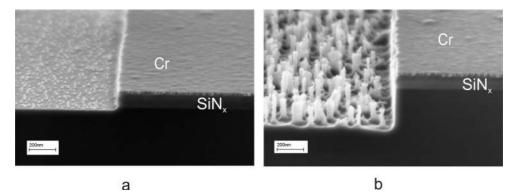

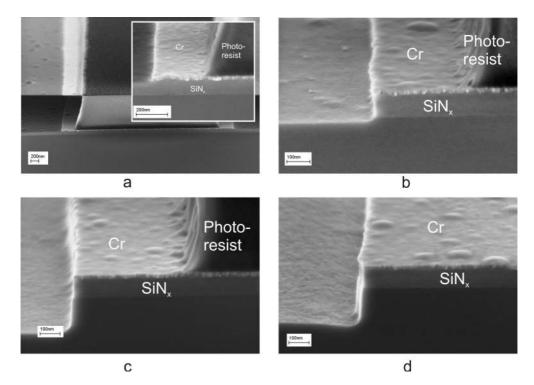

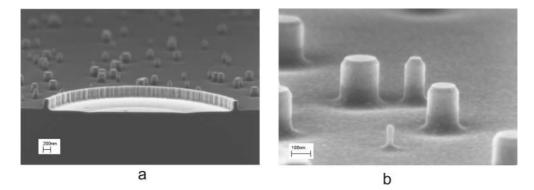

- [27] J. Haneveld, E. Berenschot, P. Maury, and H. Jansen. Nano-ridge fabrication by local oxidation of silicon edges with silicon nitride as a mask. *Journal of Micromechanics* and Microengineering, 16(6):S24, 2006.