HIGH-SPEED ARCHITECTURE FOR THE DECODING OF TRELLIS-CODED MODULATION

. . .

# Semi-Annual Status Report

Center for Space Telemetering and Telecommunications Systems Grant

Period Covered: January 1992-July 1992

NASA Grant No. NAG 5-1491

Principle Investigator: Dr. William P. Osborne

(NASA-CR-191474) HIGH-SPEED NH3-1477 ATCHITECTURE FOR THE OFFICIENCE OF TRELLIS-CREED MORNLATION Semi-innust Report, Jun. - Jul. 1992 (New Unclass Texico State Univ.) 214 p

63/60 0110351

12 214 P. 214

New Mexico State University Electrical And Computer Engineering Box 30001 - Dept. 3-0 Las Cruces, New Mexico 88003

## TABLE OF CONTENTS

.

| Chapter |                                                |  |  |  |

|---------|------------------------------------------------|--|--|--|

| 1.      | INTRODUCTION1                                  |  |  |  |

|         | 1.1 Purpose and Scope1                         |  |  |  |

|         | 1.2 Convolutional Codes and Viterbi Decoding5  |  |  |  |

|         | 1.3 Trellis-Coded Modulation21                 |  |  |  |

|         | 1.4 Coding Standards27                         |  |  |  |

|         | 1.5 Basic Implementation Considerations        |  |  |  |

|         | 1.6 High-Speed Architecture Considerations     |  |  |  |

| 2.      | QUANTIZATION                                   |  |  |  |

|         | 2.1 General Considerations                     |  |  |  |

|         | 2.2 Information Theory Considerations          |  |  |  |

|         | 2.3 Phase-Only Quantization46                  |  |  |  |

|         | 2.4 I&Q Quantization63                         |  |  |  |

|         | 2.5 The Log-Likelihood Function                |  |  |  |

|         | 2.6 Calculation of Probabilities and Related   |  |  |  |

|         | Parameters                                     |  |  |  |

|         | 2.7 I and Q Quantization for the TCM Decoder77 |  |  |  |

| 3.      | PREVIOUS TCM STUDIES                           |  |  |  |

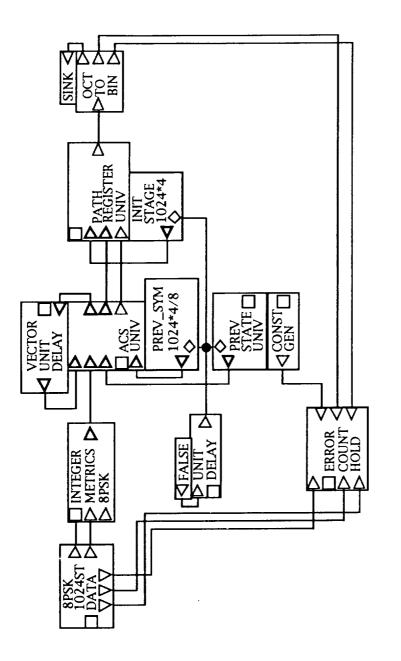

|         | 3.1 BOSS Simulations At NMSU81                 |  |  |  |

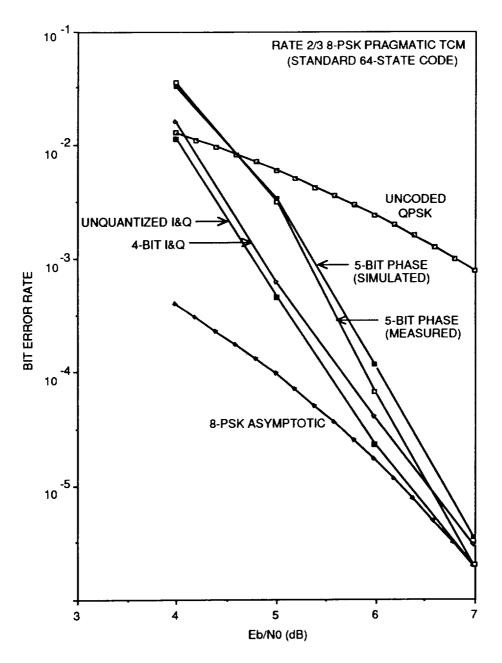

|         | 3.2 Pragmatic TCM                              |  |  |  |

|         | 3.2.1 The 24-sector Phase Quantizer91          |  |  |  |

|         | 3.2.2 Soft Decision Adaptation                 |  |  |  |

|         | 3.2.3 Outboard Decision Logic                  |  |  |  |

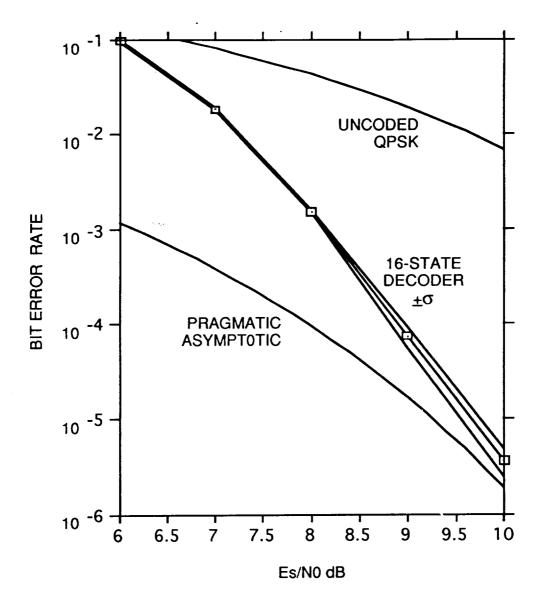

|         | 3.2.4 Performance of Pragmatic TCM107          |  |  |  |

|         |                                                |  |  |  |

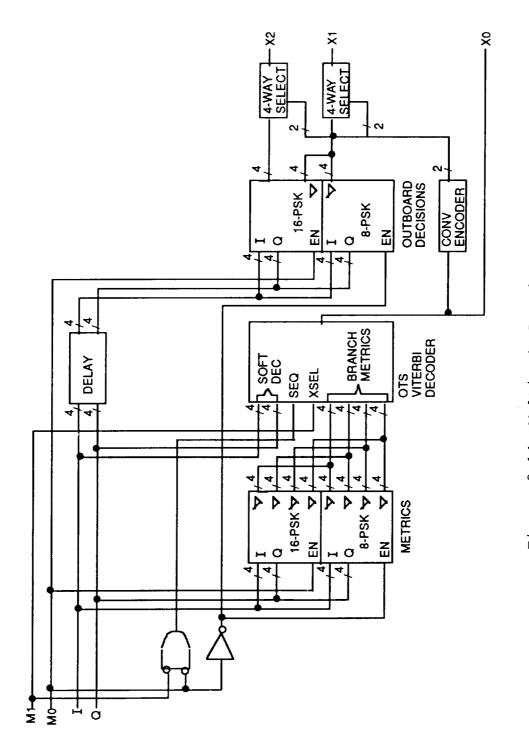

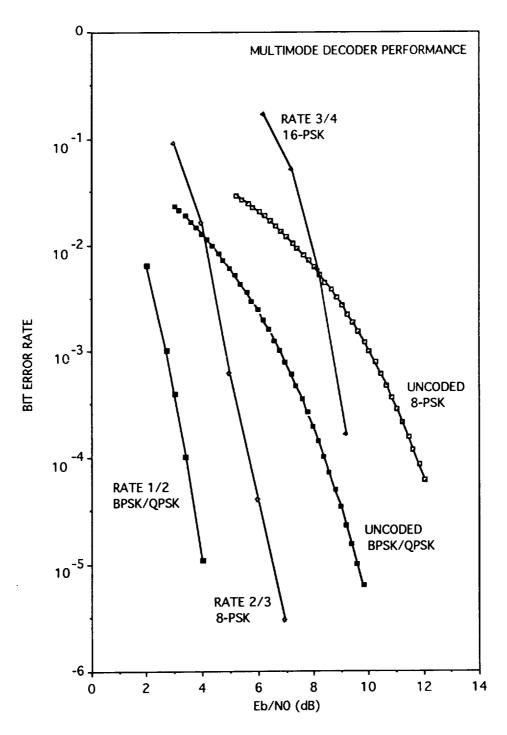

| 3.3 Multimode TCM                             |

|-----------------------------------------------|

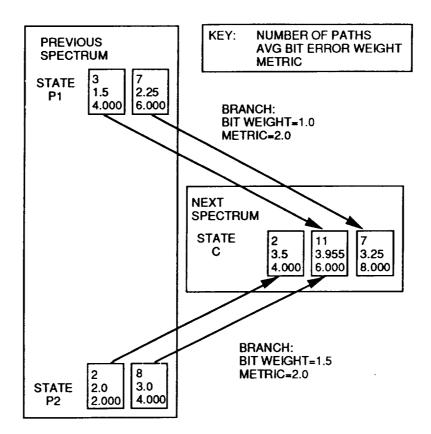

| 3.4 Bit Error Spectrum                        |

| 3.4.1 The Generating Function                 |

| 3.4.2 Bit Error Spectrum Algorithm123         |

| 3.4.3 Signal Set Mapping                      |

| 3.4.4 Applications and Results                |

| 3.5 Conclusion140                             |

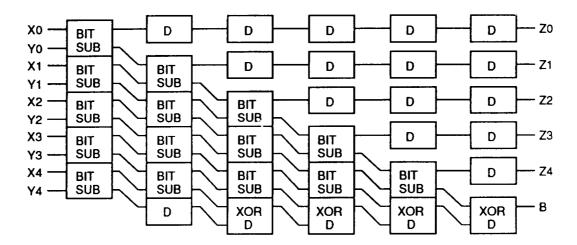

| 4. HIGH-SPEED DESIGN142                       |

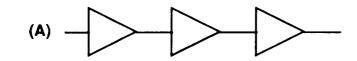

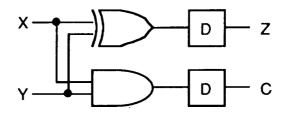

| 4.1 Pipelining147                             |

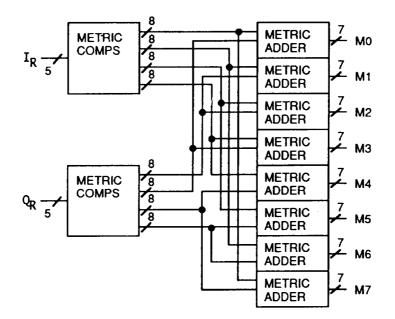

| 4.2 Metric Calculation151                     |

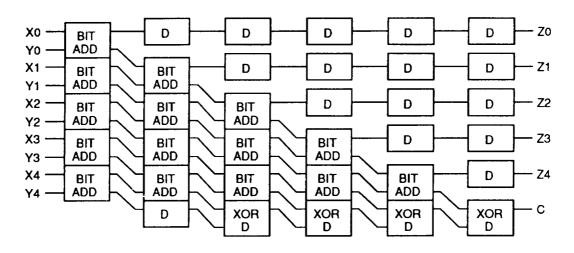

| <b>4.2.1</b> Square Law Circuit               |

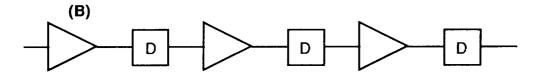

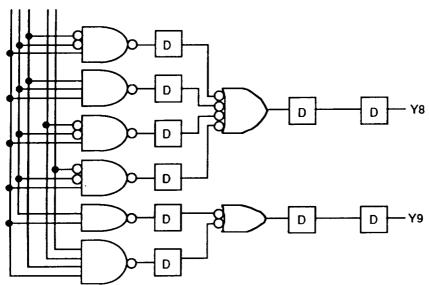

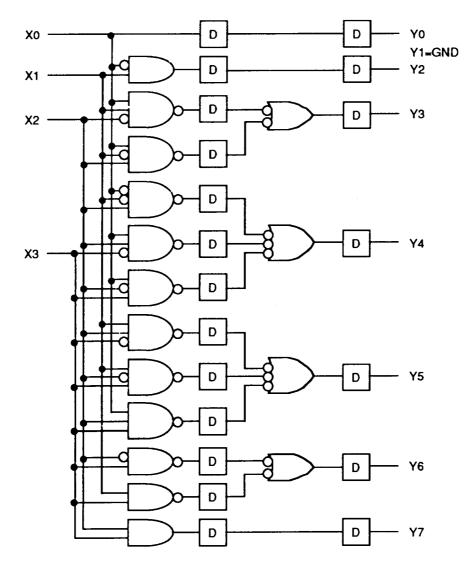

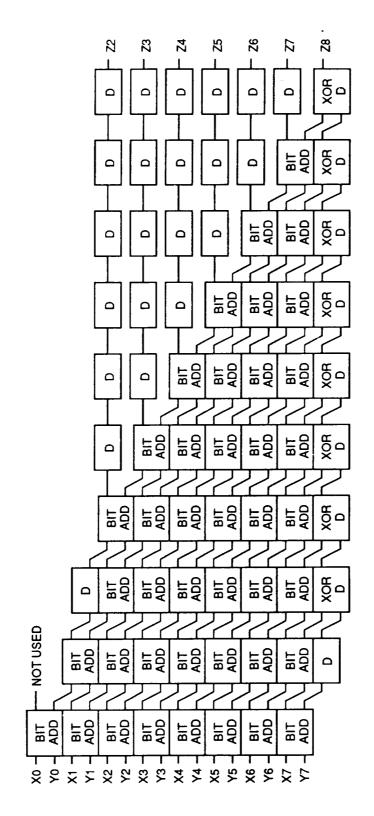

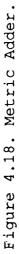

| 4.2.2 The Metric Adder                        |

| 4.3 The Add-Compare-Select Circuit            |

| 4.3.1 The Progressive Adder and the 10_bit    |

| Select171                                     |

| 4.3.2 The ACS Feedback Loop                   |

| 4.4 The Path Memory Circuit                   |

| 4.5 Testing The High-Speed Codec              |

| 4.5.1 Selection of Quantization Parameters192 |

| 4.5.2 Simulation Design                       |

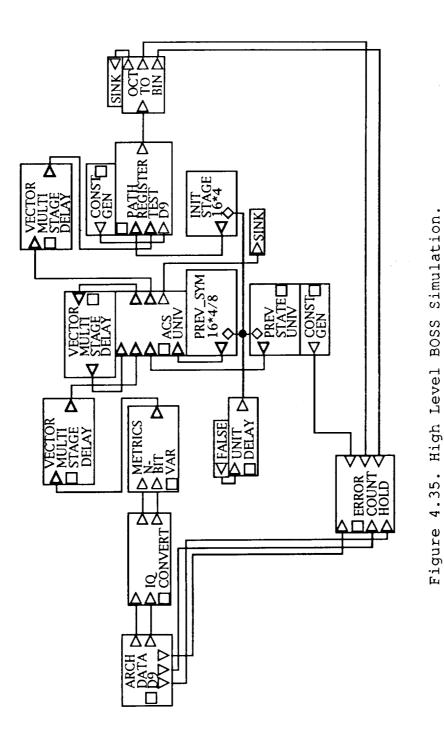

| 4.5.3 High Level Simulation                   |

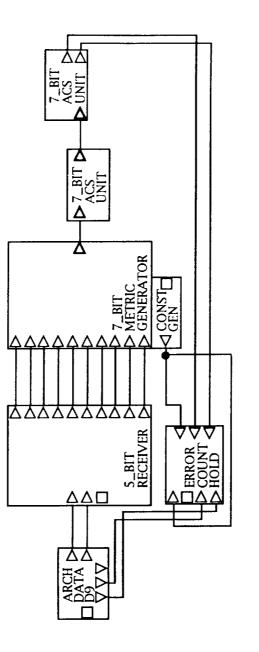

| 4.5.4 Logic Level Simulation                  |

| 4.6 Conclusion                                |

| 5.         | CONCLU | USION                                  | )4 |  |

|------------|--------|----------------------------------------|----|--|

|            | 5.1    | Summary                                | )4 |  |

|            | 5.2    | Recommendations for Further Research20 | )6 |  |

| REFERENCES |        |                                        |    |  |

#### 1. INTRODUCTION

### 1.1 Purpose and Scope

Since 1971, when the Viterbi Algorithm [1] was introduced as the optimal method of decoding convolutional codes, improvements in circuit technology, especially VLSI, have steadily increased its speed and practicality. Trellis-Coded Modulation (TCM), pioneered by Ungerboeck [2,3,4] since 1982, combines convolutional coding with higher level modulation (non-binary source alphabet) to provide forward error correction and spectral efficiency. For binary codes, the current state-of-the-art is a 64state Viterbi decoder on a single CMOS chip, operating at a data rate of 25 Mbps [5,6]. Recently, there has been an interest in increasing the speed of the Viterbi Algorithm by improving the decoder architecture, or by reducing the algorithm itself. Designs employing new architectural techniques are now in existence, however these techniques are currently applied to simpler binary codes, not to TCM. The purpose of this report is to discuss TCM architectural considerations in general, and to present the design, at the logic gate level, of a specific TCM decoder which applies these considerations to achieve high-speed decoding.

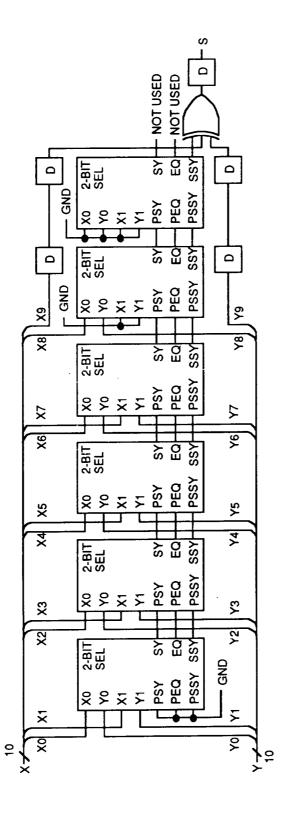

The goal of TCM architecture research is to improve the performance TCM decoders with a minimum of hardware expansion. The emphasis is on 8-PSK and 16-PSK signalling, which provide spectral efficiency and constant amplitude, desirable attributes for satellite communications. Issues of interest include speed of operation, error correction capability (coding gain) and multimode operation, that is, the ability to process multiple modulation formats using a single device with a minimum of total hardware.

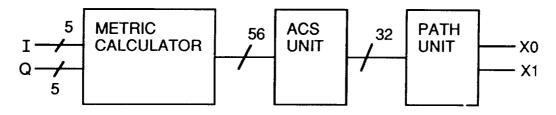

A number of approaches to the design of a high-speed TCM decoder are considered: 1) algorithmic reductions, which reduce processing time and hardware, 2) hardware expansion, or parallelism, increasing the throughput at the cost of additional hardware, 3) approximations: modifications to the algorithm which reduce hardware and processing time at the cost of compromise in performance (coding gain), 4) reductions in hardware which reduce total circuit area and allow implementation in a technology faster than CMOS. The Viterbi Algorithm consists of three distinct parts: metric calculation, the add-compare-select function, and path memory updating. Other parts of the process, which are not considered central to the Viterbi algorithm itself but are nevertheless necessary to the complete decoding system, are the quantization of the received signal vectors, and external circuitry to perform

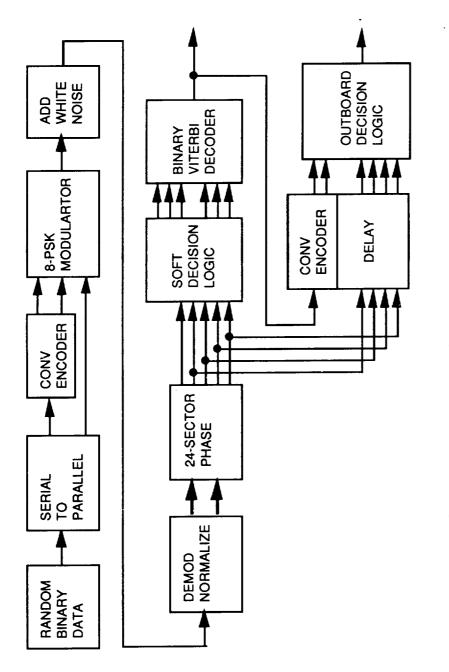

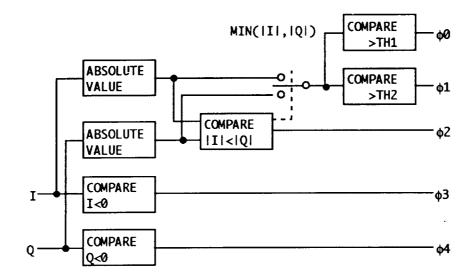

various other functions. Examples of these other functions include outboard decision making, and the generation of soft decisions used to adopt an existing binary decoder to a non-binary channel in a pragmatic [7] TCM system. As shall be shown each of the aforementioned parts of the system has the potential to impact the speed of the algorithm, and the volume of the required hardware. Also, each part of the system has the potential for reduction.

The format used to quantize the received signal vector directly determines the number of bits needed to represent the numerical quantities used in the algorithm. This ultimately affects the size of the device. Also, the choice of quantization will affect the coding gain [8,9,10]. Metric calculation must be directly matched to the quantization format. Metrics for any kind of coding system can be obtained by using the quantized decoder input as an address in a ROM, however there are advantages to be realized by designing special circuitry to calculate the metrics. The design presented in this paper obtains the metrics from combinational logic, avoiding the bulk and access time of a ROM, and allowing extensive pipelining.

The add-compare-select function includes a feedback loop that precludes pipelining. Fettweis and Meyer [11,12] consider this to be the principle bottleneck in the Viterbi Algorithm, and propose to speed up this part of the process

by combining multiple trellis stages into a super trellis stage with greater connectivity. To date, however, this technique has been applied only to simpler binary codes, and not to a TCM code.

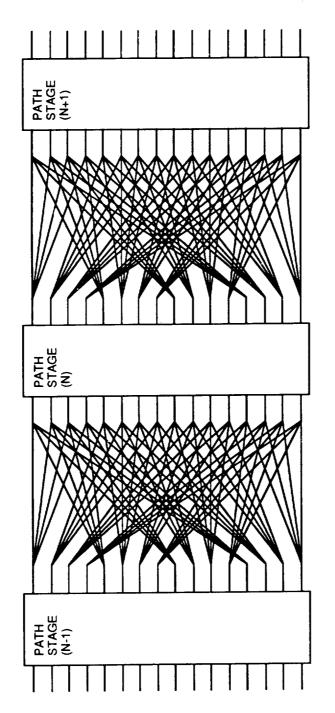

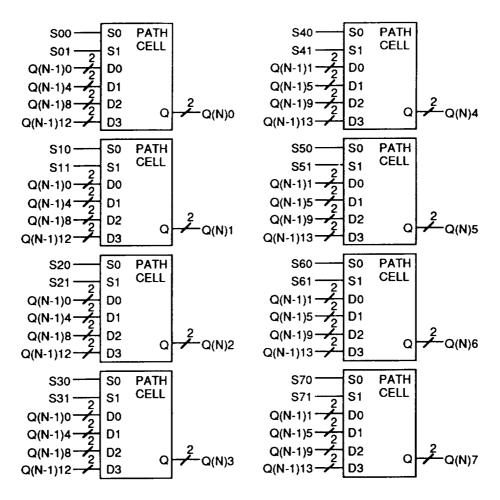

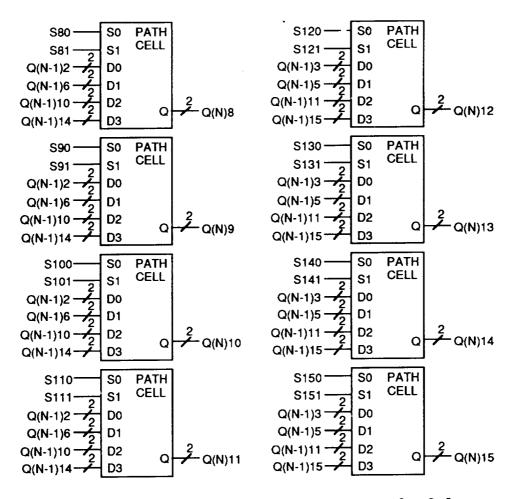

The path memory consists of memory cells and switches interconnected in a way that reflects the trellis structure of convolutional codes. The memory is not complex, but is a significant user of chip area, a factor which is affected by the choice of coding standard. The external logic has less impact on speed of operation than do the other parts of the system but is necessary to the functioning of a complete system, especially if pragmatic TCM is used.

The essential parts of a TCM system have been briefly surveyed in the preceding paragraphs and will be discussed in greater detail later. One remaining issue to be mentioned briefly at this point is the selection of the code to be used. In general, the more powerful TCM codes require larger decoding machinery. The decoding performance of TCM codes has been well researched throughout the eighties; however, less is known about the effect of the choice of code on the architecture. In 1989 Viterbi [7] published the invention of pragmatic TCM, giving a number of very strong reasons why pragmatic TCM is likely to become the TCM coding standard of the future. Based on what has been learned in the preceding years, it

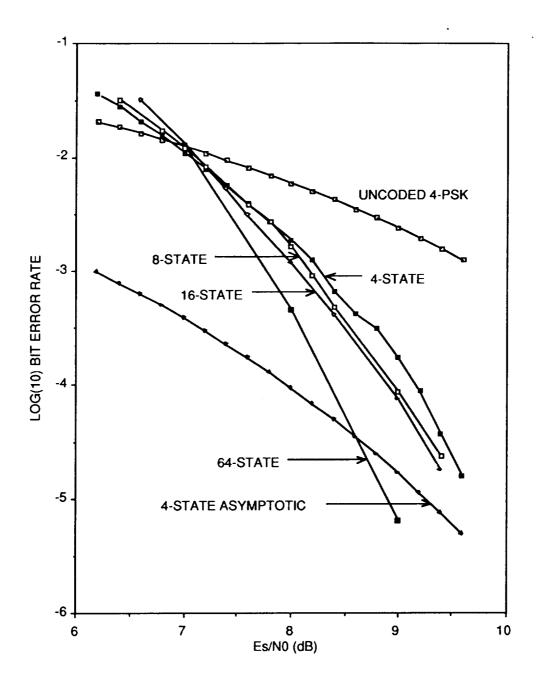

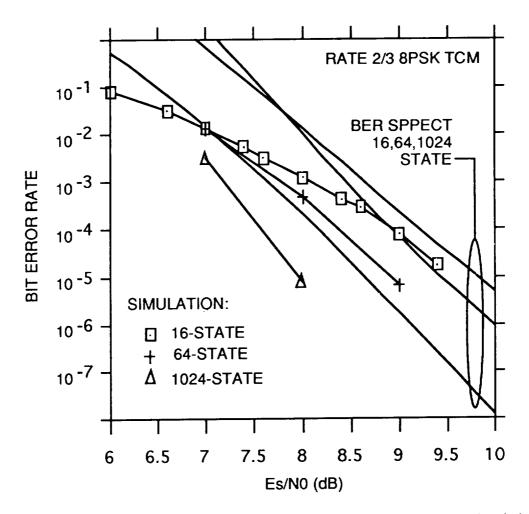

is unlikely that pragmatic TCM will be significantly improved upon, except at great expense. For example, rate 2/3 8-PSK TCM using the best known 64-state convolutional code achieves a coding gain of approximately 3.6 dB over uncoded QPSK, while pragmatic TCM using a simpler 64-state code achieves about 3db. Rate 2/3 8-PSK TCM, using a 1024state code provides an approximately 1 dB improvement over the best 64-state code [13]. So efforts to improve on pragmatic TCM are probably unwarranted at this time. However, the performance of pragmatic TCM can be matched by using the best known 16-state Ungerboeck code, which can be implemented by a smaller machine. In terms of hardware volume, the two codes are close since the pragmatic code is simpler than the 16-state code in ways that make up for the greater number of states. However, the 16-state code was decided upon, for reasons that will be discussed throughout the remainder of this work.

### 1.2 Convolutional Codes and Viterbi Decoding

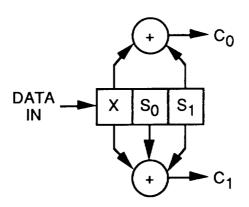

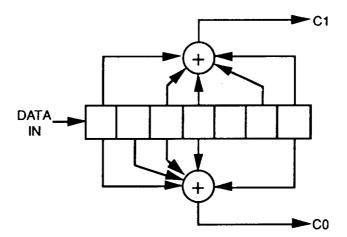

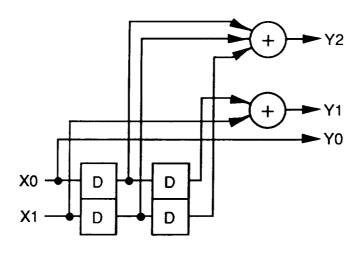

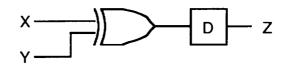

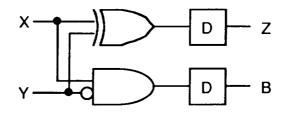

A simple convolutional encoder is shown in Figure 1.1. The device consists of a three-stage shift register with two binary (modulo-2) adders connected to the stages of the shift register as shown. Each binary adder functions as a

parity check, or an exclusive or. This encoder, although simpler than encoders used in practice, generates a reasonably powerful code. Data to be encoded is shifted into the shift register one bit at a time, then the code bits, c<sub>0</sub> and c<sub>1</sub>, form the output sequence. This encoder generates two code bits for every bit to be encoded, and thus is said to have a code rate of 1/2. The fact that the number of code bits exceeds the number of input bits makes it possible to reconstruct the correct sequence, even if some of the codebits are received in error.

Figure 1.1. 4-state convolutional encoder.

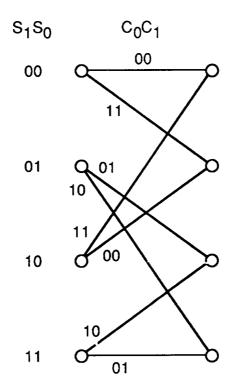

The Viterbi algorithm for decoding a convolutional code sequence is based on the finite-state behavior of the convolutional encoder. The shift register in the convolutional encoder of Figure 1.1, has two bits of memory. The first of the three stages is the current input, and so is not considered as memory. This encoder then is a 4-state machine, or 4-state convolutional encoder, and the code which it generates is referred to as a 4-state convolutional code. The contents of the memory stages defines the state, with so being the least

Figure 1.2. State diagram for 4-state convolutional encoder.

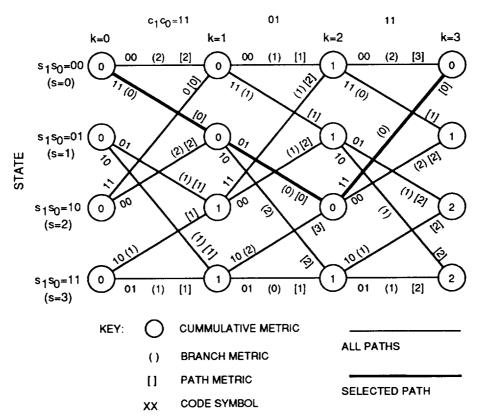

significant state bit, and s1 being the most significant state bit. The relationship between current state, current input, current output, and next state is illustrated by the state diagram of Figure 1.2. A state j which can make a transition to some state i is referred to as a predecessor to state i, and state i is referred to as a successor to state j. An output is associated with each allowed transition between two states. To represent all or any number of possible state transition histories over some period of time, the four states are arranged vertically, and then repeated horizontally to an arbitrary number of stages, resulting in the trellis diagram of Figure 1.3.

Figure 1.3. 4-state trellis diagram.

The trellis diagram shows the same state transitions as the state diagram, the difference being that the state diagram

is static, whereas the trellis diagram illustrates the behavior of the encoder over a number of periods of time.

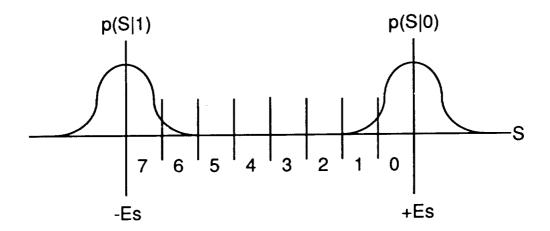

The branches of the trellis diagram, representing state transitions, are labeled with the appropriate outputs. Any output sequence which the encoder will generate is made of the outputs associated with the branches of some continuous path through the trellis. If a receiver error occurs, the received sequence will most likely not be a legitimate code sequence, in which case the receiver must find the legitimate code sequence which most closely matches the received sequence. When binary signalling is used, the sequence is selected on the basis of Hamming distance, the number of corresponding bits in which a possible code sequence differs from the received Depending on the method of signalling, a measure sequence. other than Hamming distance could be used as a basis of selection. The measure to be used is referred to as the metric, and the decoder is said to find the minimum metric path. It is impractical to accomplish this by comparing the received sequence with every possible path, since the number of possible paths doubles with each stage of the trellis.

The Viterbi algorithm avoids this massive number of comparisons by taking advantage of the finite-state property of the convolutional encoder. At any given time,

regardless of which state the encoder is actually in, there exists a minimum metric path to each state. The minimum metric path to some state  $s_j$  at some time k must include, as a subpath, the minimum metric path to a predecessor to state  $s_j$  at time k-1. The number of subpaths which must be considered at any time is therefore limited to the number of states.

Dynamic programming [14] is a well established algorithm for solving problems in which the solution at some stage of operation is a subset of the solution at the next stage. It was Viterbi's insight that Dynamic Programming can be used to decode a convolutionally encoded sequence, therefore the use of dynamic programming in this way is referred to as the Viterbi algorithm. The Viterbi algorithm works as follows: associated with each node of the trellis, which represents a state of the encoder, is a minimum metric path to that node, and a metric for that path. The metric of the minimum metric path to a node is also referred to as the state metric or cumulative metric. Initially, when no part of the code sequence has been received, all of the node metrics are zero. Each time a symbol (a pair of codebits) is received, the received symbol is compared to each branch symbol and a metric is associated with each branch of the current stage of the trellis. Each branch metric is added to the cumulative

metric at its origin node to form a new path metric. At each node of the current stage, the converging path with the least metric is selected, and the metric associated with this path is selected to be the new cumulative metric.

#### CORRECT SEQUENCE:

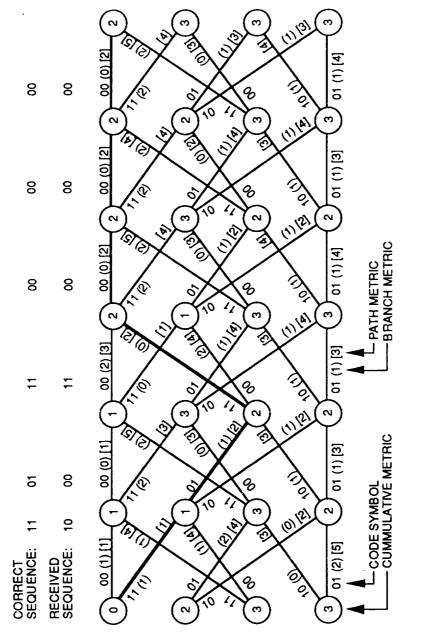

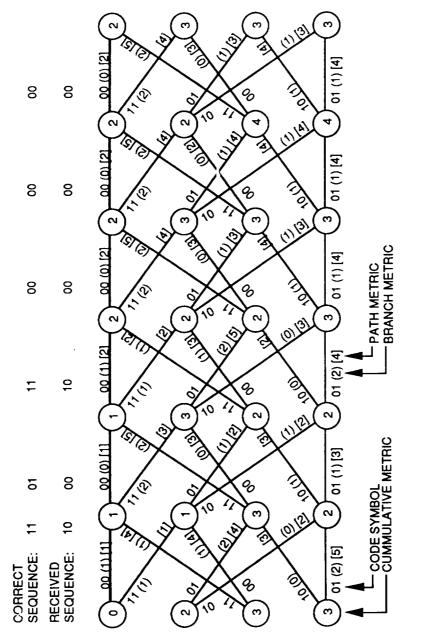

Figure 1.4. Viterbi decoding example.

As an example, suppose a single "1" is shifted through the shift register of the encoder. The resulting output sequence is 110111. The application of the Viterbi algorithm to this sequence is illustrated in Figure 1.4. At k=0, with no source code having been received, all state nodes are set initially to zero. When the first symbol, 11, is received, branch metrics are computed for all branches, i.e., 2,1,1,0 for branches having symbols 00, 01, 10, 11 respectively. Because the initial cumulative metrics are all zero, the converging path metrics are the same as the branch metrics. At node (k,s) = (1,0), the lower branch is selected, having a path metric of 0, which becomes the new cumulative metric for state 0. At state 1, the upper branch is selected. At states 2 and 3, the upper and lower branches have equal metrics of 1, so the upper branch is selected arbitrarily.

At stage k=2, the same process is repeated, except that now there are non-zero previous cumulative metrics to be added to the branch metrics. At node (k,s) = (2,0), the upper branch has a previous cumulative metric of 0 and a branch metric of 1, resulting in a path metric of 1. The lower branch has a previous cumulative metric of 1 and a branch metric of 1, resulting in a path metric of 2. The upper branch, having the least path metric, is selected, resulting in a state metric of 1. Likewise, the upper branch is selected at nodes (k,s) = (2,1), and (2,2), the lower branch is selected at node (2,3), resulting in state metrics of 1, 0, and 1, respectively. At the third stage the process is repeated again. The correct path is identified by tracing backwards through the trellis. State 0, having the least state metric at the third stage, in

this case 0, is the starting point for the trace back. The lower branch has the lesser path metric, and leads back to node (2,2). At this node, the upper branch is selected, leading back to node (1,1). Here, the upper branch is selected, leading back to node (0,0), correctly identifying the sequence.

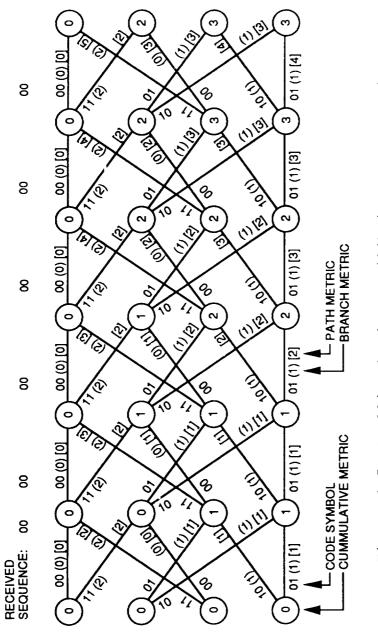

In the example of Figure 1.4, the encoder started in state 0 and finished in state 0. The decoder starts with all zero state metrics at stage 0, reflecting the fact that when no sequence has been received the decoder has no knowledge of the state of the encoder. After receiving 3 branches of correct code sequence, only the correct state has a metric of 0, the state metrics being 0, 1, 2, and 2, respectively. This reflects the fact that the decoder now has some information as to the current state of the encoder. The state metrics are updated each time a new code symbol is received, and the degree of certainty as to the state of the encoder depends on the metrics and the probability of error in transmitting a code bit, a characteristic of the channel. At all times, except during the brief start-up period, the decoder is operating with state metrics calculated from the previously received sequence, so it is the decoder's behavior in this condition which is of primary interest. Once the decoder has

received six stages of error-free symbols as is shown in Figure 1.5, the cumulative metrics reach steady state values.

With the decoder having reached this equilibrium, suppose that the encoder is made to transmit the same sequence as before, but this time two of the transmitted bits are received in error, so that the sequence 110111 is received as 100011. Figure 1.6 illustrates the operation of the decoder given this sequence, and is labeled with branch metrics, path metrics and state metrics, as is Figure 1.4. As can be seen, the Viterbi algorithm selects the correct sequence, although three further stages of operation are necessary for it to do so. If we receive the sequence with three errors, shown in Figure 1.7, the decoder selects an incorrect path. Thus we can see that the decoder has a positive but not unlimited capacity to correct errors.

The convolutional encoder is linear, i.e., the output due to the sum of two sequences is the sum of the outputs due to the individual sequences. Because of this, the encoder can be analyzed from the point of view that the all zeroes code sequence is correct, and the conclusions drawn will be applicable to all sequences in general (see Lin and Costello [15], Clarke and Cain [16], or Forney [17]). The examples of Figures 1.5, 1.6, and 1.7, show the Viterbi

Figure 1.5. Trellis showing equilibrium state metrics.

Figure 1.6. Corrected Trellis Error.

Figure 1.7. Uncorrected Trellis Error.

. •

decoder tracing backwards from the minimum metric node. In fact, the path formed by tracing backwards from any node will tend to merge back to the maximum likelihood path, given enough time. The time required depends on the properties of the code and the channel, as well as the specific interfering noise. This means that the Viterbi decoder's memory does not need to retain the likely paths for all time, but only back to the point at which there is a high probability that all paths will be merged. The decoder operates the path memory in a pipeline fashion, such that old information is shifted out as new information is shifted in. If the path memory is made long enough, there is a high probability that the information being shifted out will be correct. There is still a nonzero probability of error, because it is possible that the transmission errors will be such that an error sequence more closely matches the received sequence than does the correct sequence. If this happens, the error-correcting capacity of the code is exceeded.

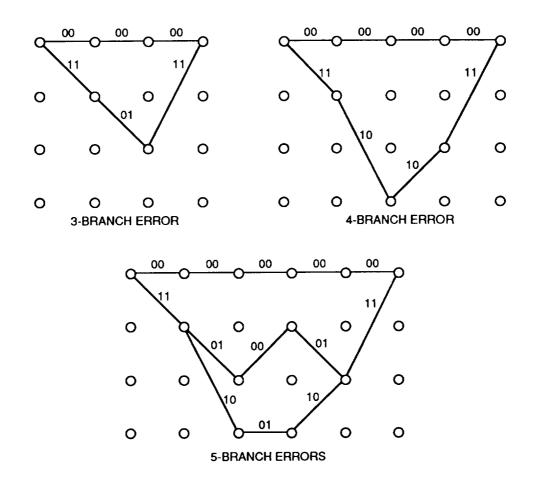

The error path illustrated in Figure 1.7 diverges from and then reconverges with the correct path. This is typical, because the metrics of non-converged error paths grow to the point that it is overwhelmingly likely that the Viterbi algorithm will eliminate them. Therefore, it is

the reconverged error paths which are of concern in predicting the performance of the code. Typical error sequences are shown in Figure 1.8. The decoder will select

Figure 1.8. Typical error paths for 4-state code.

an error sequence if at any point the received sequence more closely matches an error sequence than the correct sequence. The probability that this will happen depends on the Hamming distance between the error sequence and the correct sequence. Thus we can see that the three-branch error sequence is of the most concern as it differs from the correct sequence in only 5 bit positions. If three or more of these five bits are received in error, the threebranch error path will be selected. The longer error paths are less likely, as they differ from the correct path in a greater number of bits, yet they still make a nonnegligible contribution to the total probability of error.

More powerful codes can be generated by using a convolutional encoder with more than a three-stage shift register, which will increase the number of states and the constraint length. The constraint length, K, is the minimum number of branches in which two paths can diverge and then reconverge. The constraint length for the code used in the previous examples is 3. In general, increasing the constraint length makes it possible to achieve greater Hamming distances for the error paths, and hence reduces the probability of error. This also increases the number of states, so the Viterbi decoder must then be built correspondingly larger. It is also possible to use more than two shift registers, generating more than two codebits for every data bit shifted in, or to design encoders which shift in more than one data bit for each codebit, generating codes of various code rates, i.e., 1/3, 1/4, 2/3 etc.

Obtaining the potential power of a code of given constraint length and code rate requires finding the optimal tap settings, that is, the best connections of the shift register to the adders. There is no analytical way to do this; however, the rule that the metric of the minimum metric error path should be maximized has proven effective. The codes in use today were found by exhaustive searches, comparing the minimum distance error events of the various codes. For the rate 1/2 4-state code, the minimum metric error path is also a constraint length path, but this is not necessarily the case for the more complex codes. Therefore, finding the most powerful codes is no straightforward task.

### 1.3 Trellis-Coded Modulation

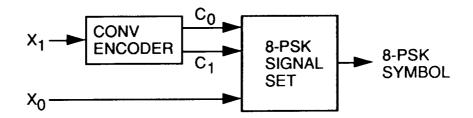

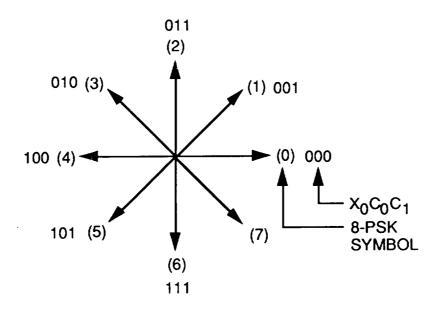

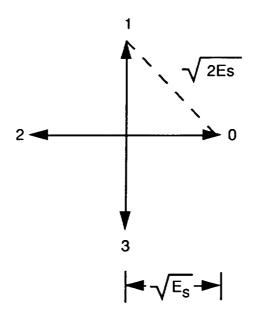

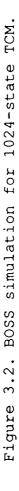

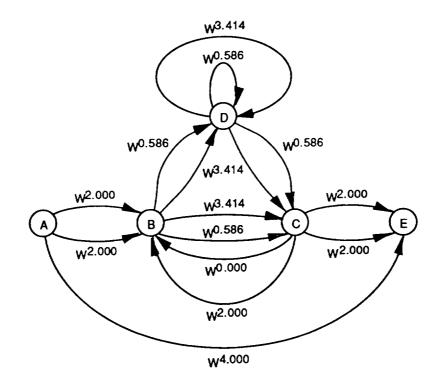

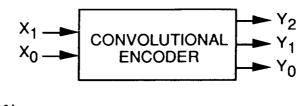

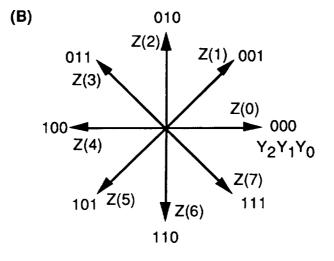

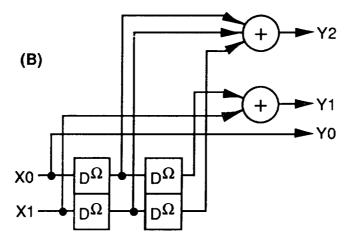

Trellis-Coded Modulation (TCM), the invention of Ungerboeck [2,3,4], is the application of convolutional encoding and Viterbi decoding to non-binary channels to obtain the advantage of bandwidth efficiency. The Viterbi algorithm for TCM is essentially the same as it is for binary codes, the important differences being that the binary code symbols have been replaced by signal vectors, and that the metric is the square of the Euclidean distance in the signal set space, rather than the Hamming distance in the binary space. As an example of a TCM system,

consider the arrangement depicted in Figure 1.9. The binary data to be encoded is divided into two streams, one of which is fed into a rate 1/2 4-state convolutional encoder as discussed in the previous section, the other of which goes directly to the signal set mapper. The two bits

Figure 1.9. Rate 2/3 8-PSK TCM encoder.

Figure 1.10. 8-PSK TCM signal set.

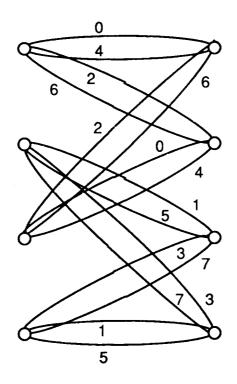

from the encoder, and the data bit which bypasses the encoder are mapped onto an 8-PSK signal set as shown in Figure 1.10. This arrangement is referred to as rate 2/3 encoding, because the 8-PSK symbol carries 3 code bits representing two encoded bits. The trellis diagram for this system is shown in Figure 1.11. Here, there are two branch symbols associated with each state transition, because only one of the two data bits determines the next state of the encoder, thus there are two ways to make any

Figure 1.11. Trellis diagram for 4-state rate 2/3 8-PSK TCM.

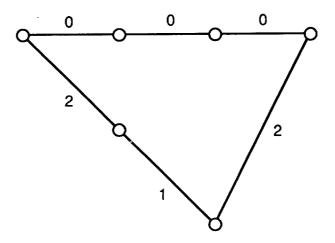

given state transition. The Viterbi algorithm operates as in the first example, except that the squares of Euclidean distances between received signal and signal set vector are used in place of the Hamming distances. As in the binary case, error events are paths which diverge from the correct path and then reconverge. The code sequence can be thought of as a vector whose dimension depends on the length of the sequence, i.e., a sequence of N two dimensional vectors can be treated as a vector of dimension 2N. The probability of error depends on the Euclidean distance between the sequence associated with the correct path, and that associated with an error event. The minimum distance error event for the system of Figure 1.9 is shown in Figure 1.12. The minimum distance error event is the most important error event, but longer error events also contribute significantly to the probability of error.

Figure 1.12. Minimum distance error event for 4-state rate 2/3 8-PSK TCM.

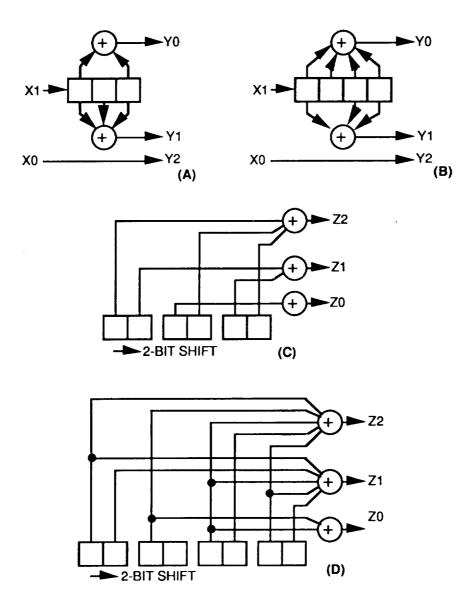

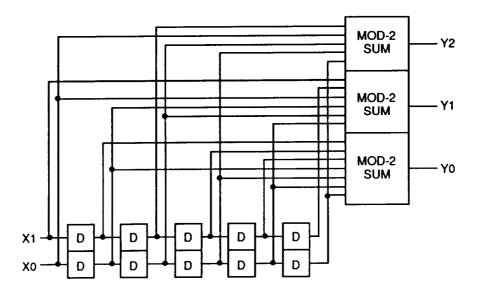

As in the binary case, it is possible to generate more powerful codes by using encoders with greater number of states. For rate 2/3 8-PSK, encoders of 4,8,16, and 64 states are illustrated in Figure 1.13. The 16-state and 64-state encoders shift two data bits into the register each time a code symbol is generated, while the 4-state

Figure 1.13. Rate 2/3 8-PSK TCM encoders: a) 4-state, b) 8-state, c) 16-state, d) 64-state.

and 8-state encoders shift in only one data bit, the other going directly to the signal set mapper. Given an encoder of a specific number of states, there is no simple analytical method to determine which of many possible tap settings will generate the best code; however, Ungerboeck has established principles for finding the better codes. First of these is the minimum metric criterion, that the code having the greatest metric for the minimum metric error event is expected to be the more powerful code (this is analogous to the minimum Hamming distance rule for binary codes). Next Ungerboeck established the set partitioning principles, which aid in maximizing the minimum distance: 1) all symbols are used with equal frequency, 2) symbols which have the greatest distance are assigned to parallel branches (branches which connect the same pair of states), and 3) symbols with the next greatest distance are assigned to branches which either diverge from the same state and reconverge to the same state. Using these principles, Ungerboeck conducted exhaustive searches to find the most powerful codes for 8-PSK, 16-PSK and a variety of QAM constellations using codes of varying number of states.

#### 1.4 Coding Standards

The coding standard is the complete specification of the method to be used to represent the original data on the communications channel. This includes the type of code (such as convolutional or block) the code rate, the block length for a block code or the constraint length for a convolutional code, the specific code to be used (tap settings or generator polynomials), and the specific signal set (binary, QAM, PSK, etc.). The rate 1/2, constraint

Figure 1.14. Industry standard rate 1/2 K=7 convolutional encoder.

length 7 convolutional encoder shown in Figure 1.14 is in common use today, and is referred to as the "defacto industry standard" [6,7]. Satellite links use this encoder in combination with a block code and convolutional code, with BPSK or QPSK signalling.

For PSK or QAM signalling, the required bandwidth is essentially proportional to the rate at which symbols are transmitted, and depends very little on the number of distinct symbols used in the system. Increasing the number of symbols increases the amount of information that can be transmitted in a given bandwidth (the spectral efficiency), but also increases the probability that one symbol will be mistaken for another (the probability of error), given the same average energy. While current terrestrial links may use signal sets of 256 symbols or more, current satellite links are almost entirely BPSK or QPSK. Future increases in demands for space communication are expected to require an increase in the spectral efficiency of satellite links, which will in turn require a shift from QPSK to a higher level of signalling (a signal set of more than 4 symbols). For a number of reasons, constant amplitude signalling is preferred for use in satellite communications. To increase spectral efficiency while preserving the property of constant amplitude signalling, the logical next step is a move from QPSK to 8-PSK, and possibly later to 16-PSK. However, due to the fact that satellite links are powerlimited as well as bandwidth-limited, the use of error correction coding is also necessary. Therefore, the emphasis of this work is on rate 2/3 8-PSK, although rate

3/4 16-PSK is also covered in the section on the multimode codec, Section 3.3.

The power or energy saved by using an error correcting code is referred to as the coding gain. This is the difference in required signal to noise ratio for coded and unccded systems maintaining the same bit error rate. In order for the comparison to be meaningful, the systems compared must have the same spectral efficiency. Thus the coding gain of a rate 2/3 8-PSK system is determined by comparison with an uncoded QPSK system, both of which carry two data bits per symbol. From the searches of Ungerboeck, it was found that for rate 2/3 8-PSK, most of the available coding gain is realized by the 4-state code, with diminishing marginal returns being obtained through 128 states. Indeed, it appears that most of the worthwhile coding gain is obtained at 64 states, although the construction of larger encoders might be worth the expense in certain specialized applications. As an example, a decoder for a 1024-state code, 16 times the size of a decoder for a 64-state code will produce a coding gain of approximately 1dB beyond that of the best 64-state code known. At a bit error rate of  $10^{-5}$ , the 64-state Ungerboeck code achieves a coding gain of approximately 3.6 dB over uncoded QPSK. This is disappointingly less than

the coding gain predicted by considering only the most likely (minimum distance) error event.

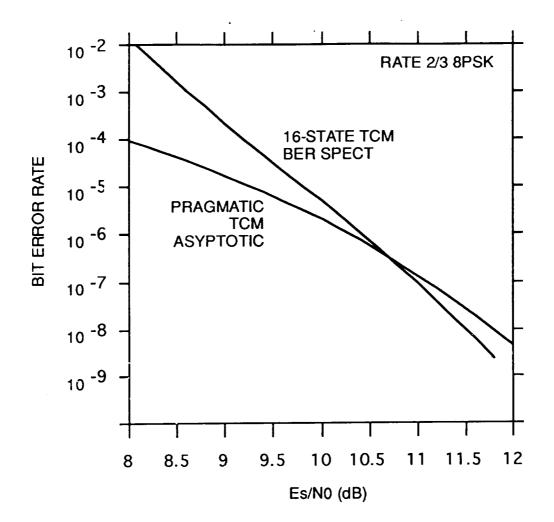

Pragmatic TCM, the invention of Viterbi [7], uses the defacto industry standard convolutional encoder of Figure 1.14, in the TCM configuration of Figure 1.9. This arrangement, applicable to a variety of signal constellations, produces a potential coding gain of 3 dB when used for rate 2/3 8-PSK. Viterbi sets forth several strong arguments for the use of pragmatic TCM: pragmatic TCM is straightforward to implement, uses a currently available industry standard decoder, and uses the same decoder for a variety of modulation schemes, while sacrificing very little in coding gain compared to the optimal code. One of the advantages of the pragmatic standard is the possibility of multimode codec design, a TCM system which handles a variety of modulation formats with a single Viterbi decoder and a minimum of additional hardware. Design considerations for such a device are discussed in [18]. For these reasons, pragmatic TCM is expected to become the primary coding standard of the next decade.

As pointed out, pragmatic TCM has many practical advantages, however, in terms of coding gain, pragmatic TCM is not the optimal code for 64-state TCM. Indeed, pragmatic TCM is asymptotically limited to a coding gain of

3.2 dB, whereas the optimal 64-state code, achieving a coding gain of 3.6 dB at a bit error rate of  $10^{-5}$  achieves continually improving coding gains at error rates less than  $10^{-5}$ . The argument in favor of pragmatic TCM is that it is worthwhile to sacrifice 0.4 dB of coding gain in exchange for certain practical advantages. However, in an application in which 3 dB of coding gain is satisfactory, one might also consider the use of the 16-state Ungerboeck code, which also achieves a coding gain of 3 dB at a bit error rate of  $10^{-5}$  and allows the use of a smaller Viterbi decoder. Also, the 16-state Ungerboeck code achieves a coding gain better than 3 dB at bit error rates less than  $10^{-5}$ .

The choice of coding standard directly effects the architecture of the decoder. The size of the decisionmaking circuits and the path memory circuits is dictated by the structure of the trellis representing the code. The use of a smaller decoder is advantageous in consideration of high-speed architecture. It should be pointed out that the trellis for the pragmatic standard has only two branches converging into each node (that is from the point of view of the Viterbi decoder, the decision between parallel branches is accomplished external to the Viterbi decoder) whereas the 16-state Ungerboeck code has a trellis with four branches converging into each node. The

consequence of this is that the 16-state code requires approximately half as much hardware as the pragmatic code, rather than one fourth, as would first be thought by looking only at the number of states. Also, the need to make four-way decisions at each node adds additional complications. Therefore, the decision between the pragmatic code and the Ungerboeck code turns out to be rather close. Also, the techniques presented here could have been applied to the pragmatic code, or almost any other useful code. However, based on the consideration of all factors involved, the design presented here uses the 16-state Ungerboeck code.

## 1.5 Basic Implementation Considerations

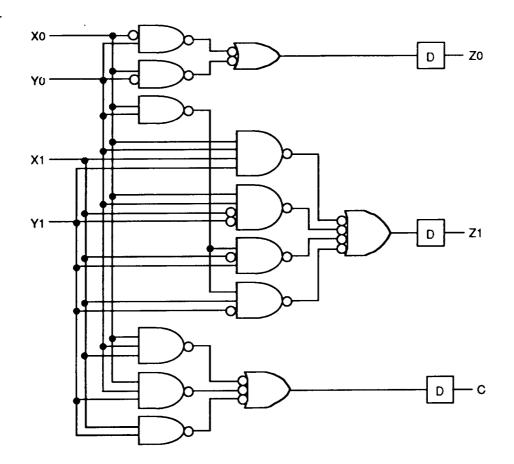

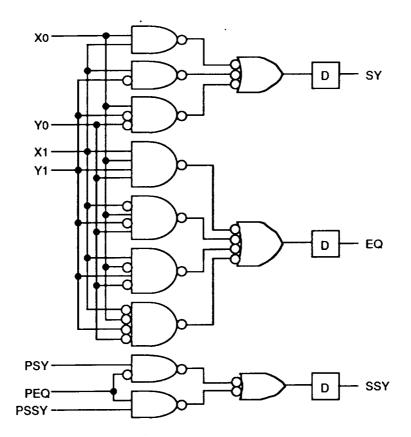

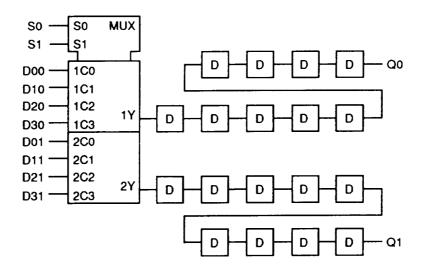

From the preceding description of the Viterbi algorithm, one can begin to form an idea of what is required to implement the Viterbi algorithm in hardware. Three distinct operations are involved: 1) calculation of the branch metrics, 2) calculation of the path metrics and selection of the minimal metric path to each node (the "add-compare-select" function), and the path memory.

Metric calculation depends directly on the type of signalling used. In the case of binary signalling with binary channel outputs, logic is needed to calculate Hamming distances, whereas slightly more sophisticated

logic would be required if the use of a soft decision metric is desired. For TCM, the metric is the square of the Euclidean distance, and depends on the geometry of the signal set. In principle, the metric for TCM is a real number. Floating point calculation of metrics may be implemented, but there is no actual advantage in doing so, since the same performance can be obtained by using sufficiently fine quantization of the receiver signal space and the metrics, and using integer arithmetic. Incidentally, the required precision for numbers used to represent the received vectors and the associated metrics is an issue that would have to be faced regardless of whether integer or floating point arithmetic is used, because even floating point arithmetic units would have to be designed to accommodate a decided number of decimal In fact, in designing a decoder for maximum speed, digits. all arithmetic circuits should be custom designed for each specific calculation, so floating point arithmetic is not even considered, and all involved quantities are quantized to an appropriate integer scale. The issue which ultimately drives the entire design is the number of bits actually needed to represent the given quantity, which can be anywhere between 3 to 12, depending on the particular calculation, the coding standard, and the performance requirement. For this design, simulations were performed

to determine how the performance of the decoder would be affected by quantization of the received signal vectors and the metrics. This had to be done *after* the coding standard was decided upon.

It is possible to obtain the metrics from read only memory (ROM) lookup tables or from in-line arithmetic. This design shows that all of the metrics required for the 8-PSK circuit can be obtained by combinational logic using an equal or lesser number of logic gates than would be required for a ROM providing exactly the same metrics. Also, the arithmetic circuits offer the advantage of improved speed through pipelining. Included in the metric calculation of this decoder is a circuit which calculates the eight-bit square of a four bit number, and adding units fit especially to the application.

The add-compare-select circuit must include a register for the cumulative metric, compare path metrics and select the minimum, and have a means for handling metric overflow. At the binary level, the comparison operation is very similar to the addition operation, and can be pipelined. In the decoder discussed here, the problem of metric overflow was avoided by using the modulo-arithmetic method of Hekstra [19]. The add compare and select function will be more complicated if four paths converge into each node, as opposed to only two, and it turns out that a four-way

decision unit requires roughly twice the hardware of a twoway decision circuit.

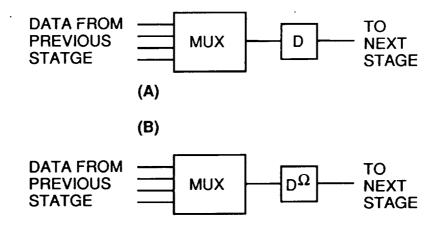

The path memory circuit retains the paths selected by the add-compare-select circuit. The information which must be retained is the path selected at each node of the trellis, for all states of the code, and for the number of stages which must be retained to insure that all selected paths will merge. The number of stages retained is referred to as the decoder depth. If two paths are merged into each node, one bit of information is required per node; However, if four paths are merged, two bits are required. Thus the total capacity of the path memory circuit is number of states times decoder depth times the base two logarithm of the number of paths converging to a This means that the 16-state Ungerboeck code node. requires about half the memory of the pragmatic code, or one fourth the memory of the 64-state Ungerboeck code. In general, a longer constraint length code requires a longer decoder depth, although a greater number of branches converging into a node requires a longer decoder depth relative to the constraint length, another factor to be considered in selecting the code to minimize the size of the hardware. It is possible to design the circuit so that the information in the memory is the sequence of data bits associated with the various paths. In this approach,

decoded data is clocked out of the path memory at the same rate that received (and quantized) signal vectors are clocked into the metric calculation unit, although with a delay imposed by the decoding circuitry.

# 1.6 High-Speed Architecture Considerations

The throughput of the Viterbi algorithm, or nearly any other operation, can almost always be increased by building identical units side by side to perform the same operation. This approach, referred to as parallelism, increases the throughput rate by the same factor as the volume of the hardware is increased. Therefore, an increase in speed which is linearly proportional to an expansion in hardware is seen as a technical baseline; a technical achievement would be an increase in speed with a less than proportional increase in hardware. The design presented here will accomplish this. If a way to reduce the hardware volume were found, several parallel units could be built in the same area previously used for only one, accomplishing the desired improvement in speed-to-hardware ratio. Therefore, the problem of increasing speed, and that of reducing hardware are in many respects the same problem.

The timing associated with on-chip operations is a small factor compared to that required for chip to chip connections. Therefore, high-speed design ideally focuses

on single chip architecture, although Fetweiss and Meyr [11.12] work around this obstacle by building parallelism in very large blocks. The choice of VLSI technology offers tradeoffs between speed and chip area. Gallium Arsenide technology offers higher speed but lesser chip area than State-of-the-art technology allows a 64-state binary CMOS. Viterbi decoder on a single CMOS chip [5,6], and Qualcomm plans to offer pragmatic TCM on a single chip in the near future [20]. One possibility for increase in speed would be reduction of the algorithm to a scale that would allow the use of the faster technology, another way in which hardware reduction is closely related to speed improvement. Much of the current research in high-speed Viterbi decoding involves hybrid technologies, i.e., using the faster technology for the speed critical parts of the operation, and slower technology for the rest [21]. To date, a variety of novel techniques for high-speed Viterbi decoding are being applied to binary codes of less than 16 states, but not to more complex codes or TCM.

As discussed in the preceding paragraphs, the objective of high-speed architecture is to achieve an improvement in the ratio of speed-to-hardware volume. In absolute terms speed and hardware volume depend on the specific family of hardware chosen for the construction of the chip, however relative comparisons of various logic

designs can be made in terms of gate counts and gate delays. Thus the logic design can be optimized before the physical design problems are undertaken. For example: a CMOS inverter consists of two MOS transistors, while a NAND gate or a NOR gate consists of four transistors. Other basic logic elements, such as exclusive ORs and latches can be rendered as combinations of inverters, NAND gates and NOR gates. In this way, the overall circuit can be looked at in terms of volume and timing.

The design to be presented here uses extensive pipelining, using a fixed number of gate delay between pipeline stages. The design is totally synchronous, so that a single clock will drive the entire decoder system from beginning to end. The code used is the rate 2/3 8-PSK 16-state Ungerboeck code. Throughout the discussion, where possible, consideration will be given to the results which might have been obtained by applying similar design strategies to the pragmatic code. Throughout the remainder of this work, the design of the decoder will be discussed in terms of gate volume and gate delays, and the reasoning behind all design decisions will be explained.

#### 2. QUANTIZATION

### 2.1 General Considerations

Ideally, Viterbi decoding of TCM would use floating point numbers for the received signal vectors, as well as the Euclidean metrics. However, due to the fact that, regardless of the technology used, it is impossible for floating point calculations to match the speed of integer calculations, some type of quantization will be employed, representing the involved quantities with a finite number of bits, and allowing metrics to be obtained from lookup tables, or by integer arithmetic. Quantization will always result in some degradation of error-correcting performance, but given an appropriate quantization scheme, performance can be made arbitrarily close to unquantized performance, by making the quantization sufficiently fine.

Quantization of the received signal vector may take a number of forms, the most prevalent being phase-only quantization, phase radius quantization, and rectangular coordinate (I and Q) quantization. This is because the problem of designing quantizers of these forms is at least approachable, whereas quantizers designed to suit generalized decision regions can be excessively complex. Regardless of the form of quantization chosen for the received signal vector, there is the additional issue of

quantization of the branch metrics. Metric quantization is closely related to, and directly affected by signal set quantization, but is an additional design consideration in its own right.

The required resolution of the received signal vectors and the metrics is also affected by the choice of coding standard. As an example of this, consider the following. Research done as part of the NMSU multimode codec study [18], which used the pragmatic standard, found that in the rate 2/3 8-PSK mode, 8-bit quantized I&Q with 4-bit metrics performed essentially as well as unquantized I,Q and metrics, whereas 4-bit I,Q and 4-bit metrics lost about 0.2 Once it was decided that the high-speed design would dB. use the 16-state Ungerboeck code rather than the pragmatic code, it was necessary to determine the necessary resolution of I,Q, and metrics. It was found that unlike the pragmatic code, the 16-state code required 5-bit metrics for satisfactory performance, using 4-bit I&Q. The 16-state code benefitted significantly from the use of 5bit I&Q but then, only if 6-bit metrics were used. This was quite contrary to the experience with the pragmatic code.

It is reasonable to ask why the 16-state code should be more sensitive to quantization, especially of the metrics, than the pragmatic codes. The performance of any practical decoder is the combined result of the inherent

error-correcting power of the code and the quality of the information given to the decoder's decision unit in the form of metrics calculated from the received signal vector. For unquantized 8-PSK, at  $\frac{E_S}{N_0}$  = 10dB (bit error rate between  $10^{-5}$  and  $10^{-6}$ ), the performance of the 16-state code is essentially equal to that of the pragmatic code. It is therefore reasonable to ask if the same degree of metric quantization represents a different quality of information to the 16-state decoder than to the pragmatic decoder. This can be seen to be the case, because the pragmatic decoder selects the four signal vectors nearest the received vector (the outboard decision) before proceeding with the Viterbi algorithm. Therefore the pragmatic decoder compares four signal vectors on the basis of the metrics, whereas the 16-state code must use the metrics to distinguish between all eight vectors. The outboard decision does in fact represent an additional bit of information. The choice of quantization scheme for the high-speed decoder was based on simulation results, not on speculation, but the foregoing argument was advanced to show that the observed results are reasonable. It would be interesting to perform further experiments to verify that the effect of the outboard decision on the signal constellation is in fact the reason for the difference in sensitivity to metric quantization.

# 2.2 Information Theory Consideration

In nearly all of the TCM research done at NMSU, the performance of various quantization schemes has been determined experimentally, through simulation. It is also of interest to look at quantization from the point of view of information theory. According to classical information theory, especially the developments of Shannon [22], the probability distribution of the outputs of any channel with respect to the inputs establishes fundamental limits on the rate at which useful information can be transmitted through the channel. Two parameters of interest in this respect are the channel capacity, C, and the random coding bound, Ro, to be discussed later. In general, practical technology does not achieve the limits indicated by these parameters; however, they are of interest because all reasonably designed codes, at whatever complexity, will show similar, relative gains and losses in response to changes in these quantities. For TCM systems, the source has a discrete signal set, but due to the presence of noise (which is usually assumed to be additive white Gaussian), the received signal is a continuously distributed vector. The quantizer converts the received vector into a discrete output, causing the source, transmission medium, and quantizer to form a discrete channel. Let the set of source symbols be denoted  $\{s_i\}$  for  $i=0,\ldots,M-1$  and the set of

output symbols be denoted  $\{z_j\}$  for j=0,...,N. The discrete channel is characterized by the matrix of transitional probabilities  $p_{ij} = P(z_j|s_i)$ , the probability that the quantizer selects output  $z_j$  given that signal vector  $s_i$  was transmitted.

The signal vectors received from the transmission medium convey a degree of information about the transmitted vector, depending on the physical characteristics of the medium, most importantly, the signal-to-noise ratio. The quantizer is included as a practical necessity but does not enhance the information from the channel, and in fact loses information. Clearly, the finer the quantization, the less loss of information. It has been well-argued, that two important parameters which affect the performance of any code using the outputs from the channel are the channel capacity, C, and the random coding bound  $R_0$  [23,24]. Both of these quantities reflect the amount of information available to the decoder. The channel capacity is a concept invented by Shannon [22] and is an absolute limit on the rate at which information can be sent through the channel. The random coding bound is an information rate, derived from the probability of error averaged over all codes which can be supported on the channel [25]. It is impossible that any communication system could ever exceed the channel capacity, and it is generally not practical to

build a system which even meets the channel capacity. The random coding bound, being a statistically expected performance rate, is a more practical parameter than channel capacity. It has been shown [23,25] that the expected attainable error probability of codes on a channel is related exponentially to the block length of the code, and  $R_0$  as follows:

$$P_{\rm P} \leq C_{\rm R} 2^{-\rm NR_0} \tag{2.1}$$

provided that  $R_0 > R$ . Here, N is the block length of the code, R is the number of data bits per symbol, and  $C_R$  is an empirically determined constant. Performance at the rate indicated by  $R_0$  has never been attained, since to do so would require large block lengths, and the use of soft decisions. To date, block codes use large block lengths but not soft decisions, whereas convolutional codes use soft decisions but have short block lengths.

For a continuous channel, the channel capacity and the random coding bound are defined in terms of the probability density functions of the channel. For the discrete channel, with a finite set of inputs  $\{s_i\}$ , and a finite set of outputs  $\{z_j\}$ ,  $R_0$  and C are calculated from the source probabilities  $P(s_i)$  and the transitional probabilities  $P(z_j|s_i)$  as follows:

$$C = -\sum_{j} P(z_{j}) \log_{2} [P(z_{j})] + \sum_{i} P(s_{i}) \sum_{j} P(z_{j}|s_{i}) \log_{2} [P(z_{j}|s_{i})]$$

(2.2)

$$R_{0} = -\log_{2} \left\{ \sum_{j} \left[ \sum_{i} P(s_{i}) \sqrt{P(z_{j}|s_{i})} \right]^{2} \right\}$$

(2.3)

where the source probabilities  $P(s_i)$  are chosen to maximize C and R<sub>0</sub>. The derivation of R<sub>0</sub> is due to Gallager [25]. Nearly all channels of practical interest possess symmetry such that C and R<sub>0</sub> are maximized when the source symbols all have equal probabilities, that is  $P(s_i) = \frac{1}{M}$ , for all i, where M is the number of source symbols. In this case:

$$C = -\sum_{j} \log_{2}[P(z_{j})] + \frac{1}{M} \sum_{i} \sum_{j} P(z_{j}|s_{i}) \log_{2}[P(z_{j}|s_{i})]$$

(2.4)

$$R_{0} = -\log_{2}\left\{\frac{1}{M^{2}}\sum_{j}\left[\sum_{i}\sqrt{P(z_{j}|s_{i})}\right]^{2}\right\}$$

(2.5)

If the channel has symmetry with respect to the relationships between inputs and outputs, that is, if the sets of transitional probabilities  $\{P(z_j|s_a)\}$  and

$\{P(z_j|s_b)\}$  are different permutations of the same set for any inputs  $s_a$  and  $s_b$ , as is the case with the phase-only and I,Q quantization schemes discussed here, then

$\sum_{j} P(z_{j}|s_{i}) \log_{2}[P(z_{j}|s_{i})] \text{ does not depend on } i, \text{ in which}$  case the calculation for the channel capacity further simplifies to:

$$C = -\sum_{j} P(z_{j}) \log_{2} [P(z_{j})] + \sum_{j} P(z_{j}|s_{0}) \log_{2} [P(z_{j}|s_{0})]$$

(2.6)

The channel capacity and the random coding bound are measures of the information available to the decoder after quantizing. This will inevitably be less than before quantizing, however, as the quantizer is a practical necessity, quantizers are included in the system and designed to optimize these parameters.

#### 2.3 Phase-Only Quantization

A TCM system can be made to work reasonably well with phase information only. While phase and magnitude both contribute to maximum likelihood decisions, phase-only quantization may be of interest in the case of non-linear

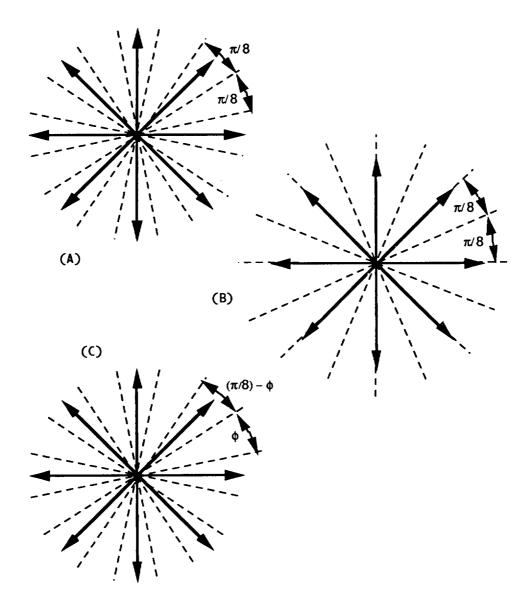

channels, or the case of relaxed requirements of automatic gain control. Also, phase-only quantization is an effective way to use a relatively small number of quantization regions, compared to I&Q quantization. Studies of phase-only quantization have been performed at NMSU since 1988 [8,9,10]. In these studies, the quantizing operation was modelled by defining a finite set of quantization points analogous to quantization levels in one-dimensional quantization. The receiver then selects the quantization point nearest the received signal vector, and the decoder calculates Euclidean metrics with respect to the quantization point, continuing the decoding process just as though the quantization point were the received vector. In this model, phase-only quantization is represented by locating the quantization points at even intervals on a circle of radius  $\sqrt{E_{\rm S}}$  , as illustrated in Figures 2.1a and 2.1b, for the 24-sector phase-only quantization. In Figure 2.1a, 8 of the 24 quantization points coincide with the 8 signal vectors, whereas in Figure 2.1b, the quantization points are offset from the signal vectors. Because the quantization points lie on a circle, the term circular quantization was used. The rule of selecting the nearest quantization point generates the decision regions shown in Figure 2.1.

Figure 2.1. 8-PSK 24-sector phase quantization.

The quantization point model is extremely practical (simulations at NMSU demonstrated the performance of TCM systems using this model) but does treat the selection of optimal decision regions, and the optimization of metrics in great detail. Before further discussion, it should be pointed out that the gains to be obtained by fine-tuning of decision regions and metrics are extremely small (which accounts for the success of the early NMSU simulations), and will most likely be eliminated when the metrics are quantized in a discrete decoder. The theoretically correct metric to use, for any set of decision regions, is the loglikelihood metric, to be discussed in Section 2.6. Once, metrics other than Euclidean distance are used, the location of the quantization points becomes less meaningful, and the quantizer is modelled merely as a set of decision regions. It then remains to discuss the optimal configuration of the decision regions. The notion of quantization points retains its utility, as it treats quantization as a question of precision of numerical quantities used in the algorithm, an issue which must be faced in hardware design anyway.

In 1990, Parsons and Wilson [26], using the term polar quantization, published a paper discussing the design of phase-only quantizers, for M-ary PSK with M=4,8, and 16, using quantizers of M, 2M and 4M zones. Their paper presents the design of phase-only quantizers which optimize  $R_0$  by satisfying Lee's optimality criterion [27], and concludes that this condition is met (for the cases discussed) by a quantizer in which the signal vectors lie on boundaries of decision regions as shown in Figure 2.2b,

as opposed to one in which the signal vectors bisect decision regions as shown in Figure 2.2a. Parsons and Wilson derive their conclusion for 16-sector 8-PSK and then suggest that the same should also be true for 32-sector 8-PSK.

Figure 2.2. 8-PSK 16-sector phase quantization.

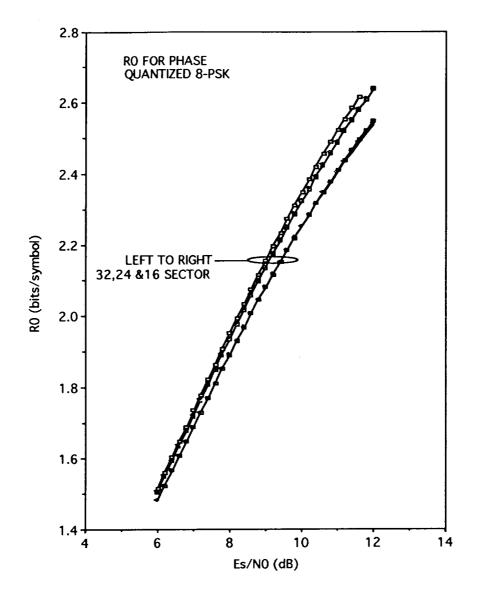

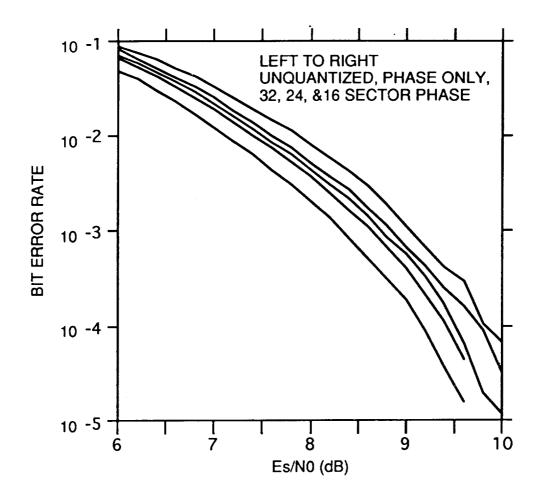

The early quantization studies at NMSU did not approach the optimization of quantization zones but rather looked at decoder bit error rate performance as a function of fineness of quantization (16-sector, 24-sector, 32sector). Because these studies used the configurations of Figures 2.1a and 2.2a, it is in our interest to numerically evaluate  $R_0$  for the various configurations, using equations (2.24), and (2.5). The results are shown in Figure 2.3. Although only three curves are apparent at first glance, there are actually six curves:  $R_0$  for 16, 24 and 32-sector quantization, for both the case where signal vectors lie on the decision boundaries and the case in which they bisect the decision regions. As can be seen, whether the signal vectors lie on the boundaries of decision regions or in the centers of decision regions makes very little difference for 16-sector guantized 8-PSK, and essentially no difference for 24-sector and 32-sector quantized 8 PSK. To gain further insight into this issue, we shall look more closely at Parsons and Wilson's work [26], and look closely at what it means to satisfy Lee's optimization criterion.

Figure 2.3. Random coding bound for phase quantized 8-PSK.

Lee's optimization criterion states that if  $\rho$  is a point on the boundary between two decision regions D<sub>a</sub> and D<sub>b</sub> of an optimal quantizer then:

$$\sum_{m=0}^{M-1} \left[ \frac{1}{\sqrt{P(b|m)}} \sum_{i=0}^{M-1} \sqrt{P(b|i)} - \frac{1}{\sqrt{P(a|m)}} \sum_{i=0}^{M-1} \sqrt{P(a|i)} \right] f(\rho|m) = 0$$

(2.7)

where f(x|m) is the probability density function of the received vector given that signal m was transmitted, P(a|m)is the probability that the quantizer will select  $D_a$ , given that m was transmitted, and P(b|m) is the probability that the quantizer will select  $D_b$ , given that m was transmitted. This meaning of Lee's criterion becomes more apparent when the equation is rewritten as

$$\sum_{m=0}^{M-1} \left[ \frac{1}{\sqrt{P(a|m)}} \sum_{i=0}^{M-1} \sqrt{P(a|i)} \right] f(\rho|m)$$

$$= \sum_{m=0}^{M-1} \left[ \frac{1}{\sqrt{P(b|m)}} \sum_{i=0}^{M-1} \sqrt{P(b|i)} \right] f(\rho|m)$$

(2.8)

The term on the left hand side represents the incremental contribution of the point  $\rho$  to R<sub>0</sub> if  $\rho$  is included in D<sub>a</sub>, the term on the right represents the incremental

contribution if  $\rho$  is included in  $\text{D}_{}_{\text{h}}.$  If the two are equal (as stated by Lee's criterion) then it is clear that  $\boldsymbol{\rho}$ belongs on the boundary between  $D_a$  and  $D_b$ . If the term on the left side were greater (not fulfilling Lee's criterion) it would mean that  $R_{0}$  could be increased by adjusting the boundary to include  $\rho$  within D<sub>a</sub>, and likewise, if the term on the right were greater, it would mean that  ${\rm R}_{_{\rm O}}$  could be increased by including  $\rho$  in  $\text{D}_{}_{b}.$  We can see then, that Lee's criterion is analogous to the condition that a single variable function is maximized at a point of zero derivative, and therefore constitutes a local, not a global maximizer of the  $R_0$  function, a fact which Parson's and Wilson acknowledge. Thus we may interpret Lee's criterion as follows: If a set of decision boundaries is drawn, and Lee's Criterion is satisfied, then incrementally adjusting the boundaries will not increase  $R_0$ , but if Lee's criterion is not satisfied, then  $R_0$  can be increased (or decreased) by incrementally adjusting the boundaries. Lee's criterion does not guarantee that  ${\rm R}_{\rm n}$  could not be higher for some completely different configuration of quantizer decision regions.

Parsons and Wilson [26] acknowledge that their work proves the configuration of Figure 2.2b to be a local maximizer of  $R_0$ , not necessarily a global maximizer. In fact they state,

"While a proof of global optimality seems difficult, we conjecture that the stated design is optimal, arguing as Lee did for the optimality of the J = M [J is the number of decision regions] design. Demonstration that no other design with J=2M satisfies [Lee's condition] would confirm this of course [p1513]."

Furthermore, Parsons and Wilson [26] do not attempt to show that Lee's condition is met for any configuration of 32sector 8-PSK, (in fact, they state that phase-only quantization for J > 2M does not meet Lee's condition) and they do not discuss 24-sector 8-PSK. For 16-sector 8-PSK, however, Parsons and Wilson [26] have stated that the configuration of Figure 2.2b satisfies Lee's criterion, whereas the configuration of 2a does not, and thus conclude that it is better that the signal vectors lie on boundaries of decision regions, rather than in centers of decision regions.

We shall now examine 16-sector 8-PSK more closely. The configuration of Figure 2.2b satisfies Lee's criterion, therefore adjusting the decision boundaries will not improve  $R_0$ . The configuration of Figure 2.2a does not satisfy Lee's criterion, and therefore its value of  $R_0$ ,

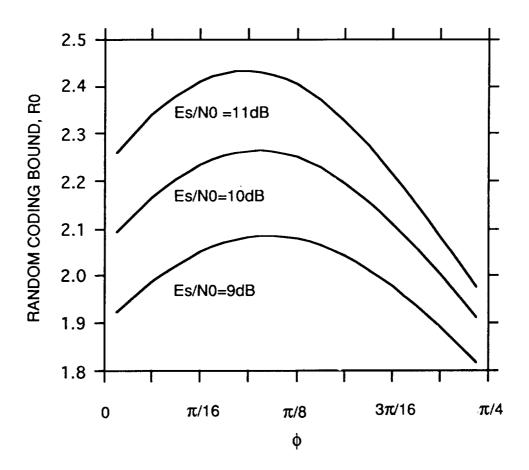

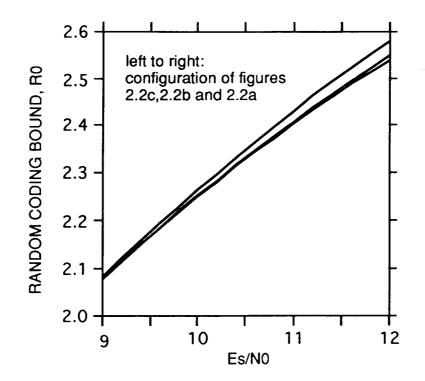

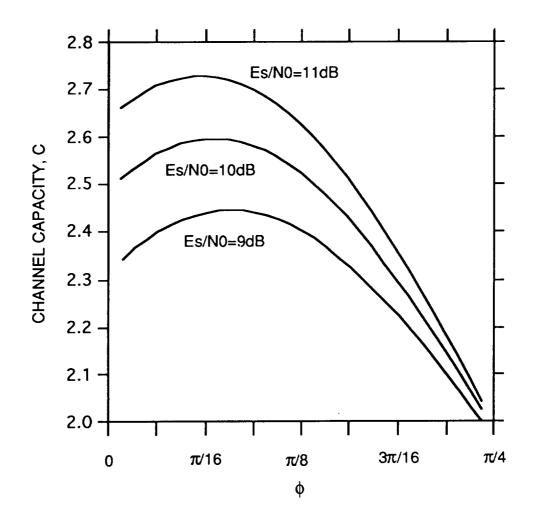

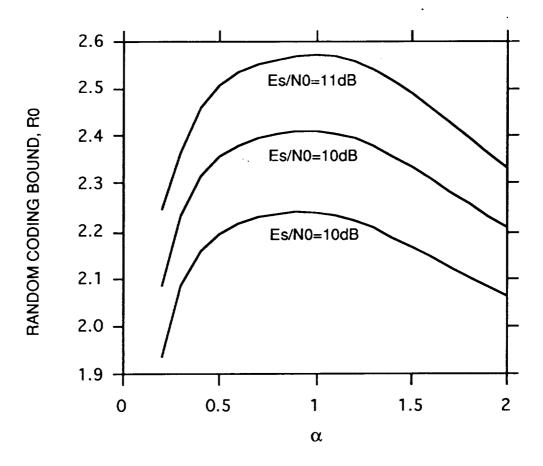

which is already close to that of Figure 2.2a, can be improved by adjusting the decision boundaries, specifically by varying the value of  $\phi$ , as shown in Figure 2.2c. In this configuration the 8 sectors which encompass a signal vector have span of  $\phi$ , the 8 which do not, have span of  $\frac{\pi}{\alpha}$  -The optimal value of  $\phi$  depends on the signal-to-noise Φ. ratio; however, by selecting an appropriate value of  $\phi$ , it is possible to make  $R_0$  for the configuration of Figure 2.2c exceed R<sub>0</sub> for the configuration of Figure 2.2b. Note that for  $\phi = 0$ , the configuration degenerates to hard decision 8-PSK, whereas for  $\phi = \frac{\pi}{8}$ , the configuration of Figure 2.2c is identical to that of Figure 2.2a. For the case of  $\phi = \frac{\pi}{4}$ the configuration degenerates to a configuration of little practical value, 8 decision regions, with the decision boundaries coincident with the 8 signal vectors. With  $\phi$  =  $\frac{\pi}{4}$ , the channel capacity (and likewise, the random coding bound) of the configuration can never be more than 2 bits per symbol, at any signal-to-noise ratio. For hard decision 8-PSK, or reasonable values of  $\phi$ , the capacity can approach 3 bits per symbol at sufficiently high SNR's. Figure 2.4 shows R0 for the configuration of Figure 2.2c as a function of  $\phi$  for  $\frac{E_S}{N_0} = 9$ , 10, and 11dB. As can be seen,  $\varphi$  can be selected to optimize  $R_0$  at the expected signal-tonoise ratio. Figure 2.5 shows  $R_0$  for the three

configurations of 16-sector 8 PSK shown in Figure 2.2. Here,  $\phi$  is chosen to optimize R<sub>0</sub> at  $\frac{E_S}{N_0} = 10$ dB. Note that if Figure 2.2c is optimized, the difference between 2c and either 2a or 2b, is greater than the difference between 2a and 2b.

Figure 2.4. Random coding bound of Figure 2.2c.

Figure 2.5. Random coding bound of 16-sector 8-PSK.

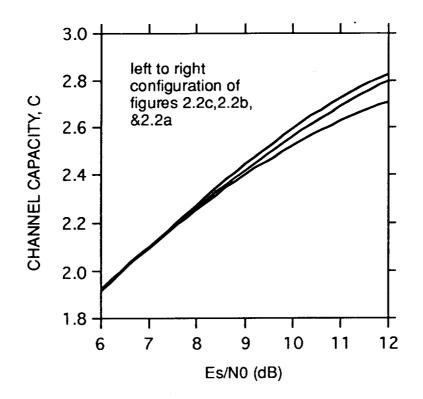

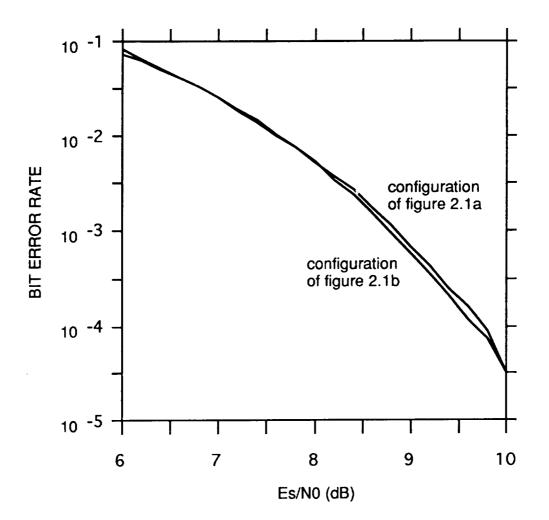

For 16-sector 8-PSK, the numerical differences in  $R_0$ involved in the previous arguments are in fact very small. For channel capacity, the results are similar, as shown in Figures 2.6 and 2.7. Note, however that the channel capacity and the random coding bound are not necessarily optimized at the same value of  $\phi$ . As the number of quantization regions is increased, the exact placement of the quantization zones becomes less critical in its effect on the performance of actual systems. For 24-sector 8-PSK, the performance of a 4-state TCM Ungerboeck code using the decision region configurations of Figures 2.1a and 2.1b, is compared in Figure 2.8. This data was obtained from early simulations using the quantization point model, and Euclidean Metrics.

Figure 2.6. Channel capacity of constellation of Figure 2.2c.

Figure 2.7. Channel capacity for 16-sector 8-PSK.

Figure 2.8. Performance of 24-sector 8-PSK, 4-state TCM.

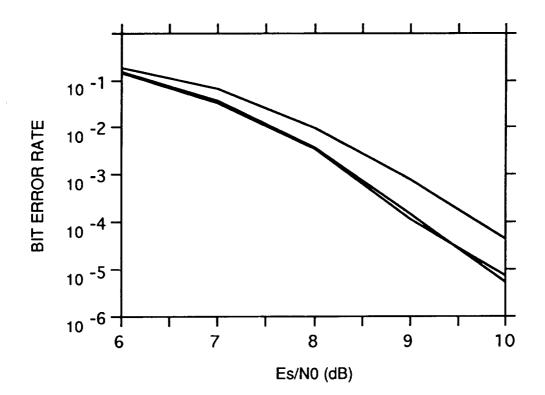

The performance of 16-, 24-, and 32-sector 8-PSK, with a 4state Ungerboeck code (previously published data [10]) is shown here in Figure 2.9. Also shown in Figure 2.9 is the performance of 8-PSK with unquantized phase and radius hardlimited to  $\sqrt{E_S}$ . These simulations also used the Euclidean metric. For comparison, the performance of unquantized 8-PSK is also shown. The unquantized phase-

Figure 2.9. Performance of phase quantized 8PSK 4-state TCM.

only curve represents the limit on the performance of phase-only quantization, although a very slight improvement could be obtained by using an optimal metric. This reflects the fact that phase-only quantization, however fine, is limited by the loss of magnitude information. This limitation led to the decision to use I&Q quantization in the high-speed architecture study, as well as the

multimode study [18]. However, phase-only quantization turned out to be extremely useful in the NMSU implementation of pragmatic TCM [28,29], using an existing (off the shelf) binary Viterbi decoder. Pragmatic TCM is discussed in Section 3.2.

### 2.4 I&Q Quantization

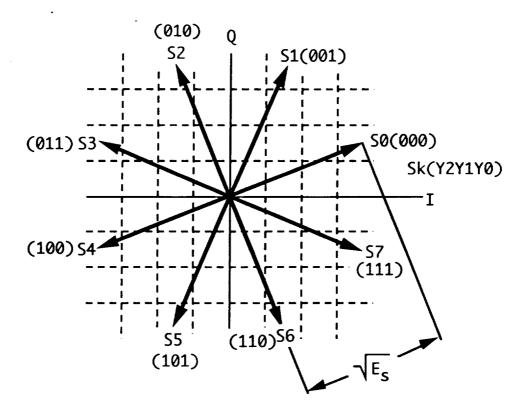

I&Q quantization, that is, individual quantization of the in-phase and quadrature components of the received vector has the important advantage of approaching unquantized performance for sufficiently fine quantization, which is not the case for phase-only quantization. However, a disadvantage is that a much larger number of quantization points must be used, which complicates metric calculation. Also, in order for the magnitude information to be meaningful, the receiver must maintain good automatic gain control. Finally, I&Q quantization limits the range of the received signal vector, so the quantizer must be designed with respect to the expected magnitude of the received vector.

Figure 2.10. I&Q quantization.

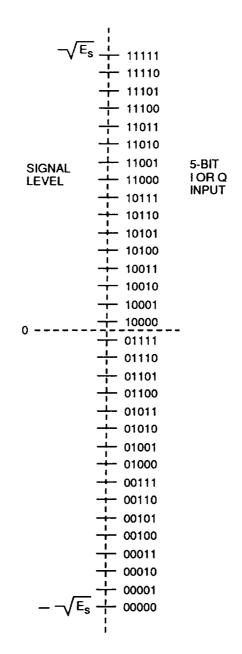

To model I&Q quantization, we first assume an 8-PSK constellation as shown in Figure 2.10. This constellation is rotated by 22.5 degrees from that of Figure 1.10. The rotation does not affect the algebraic or analytical properties of the code, but has certain advantages in hardware implementation. We let the I and Q components range from -1 to 1, and then let the signal vectors have length  $\alpha$ . We then quantize rectangularly, and symmetrically, so that an equal number of quantization points lie in each quadrant. Because the I and Q

components will be represented as binary numbers in hardware, it is desirable to let the number of quantization values (for I or Q) be a power of 2. From simulations at NMSU [28,29] it is known that 8-level (3-bit) I and Q quantization seriously degrades the performance of pragmatic TCM, whereas the performance of a system using 8bit I&Q is close to that of an unquantized system. Therefore, for the TCM decoder architecture, we expect to represent the I and Q components of the received vector using now fewer than 4 bits, but no more than eight bits.

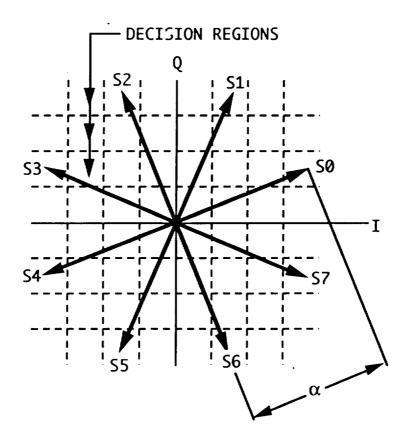

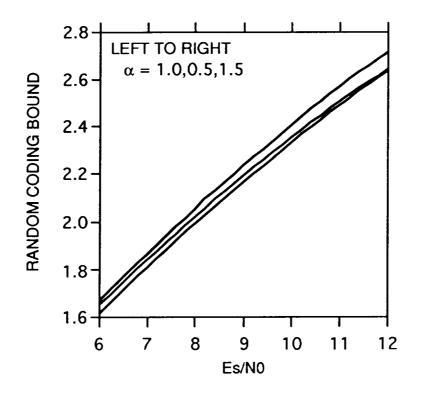

For I and Q quantization, an important parameter is the length of the received vector, relative to the boundaries of the rectangular quantization region in the receiver space, denoted as  $\alpha$  in Figure 2.10. As is the case for phase-only quantizers, I&Q quantizers should be designed to maximize the random coding bound, R<sub>o</sub>. For 4bit I and Q,  $R_0$  as a function of  $\alpha$  is shown in Figure 2.11. R<sub>0</sub> as a function of signal-to-noise ratio is shown in At  $\frac{E_s}{N_0} = 10$  dB, R<sub>0</sub> appears to be maximized at Figure 2.12. approximately  $\alpha$ =1.0 and is not very sensitive to  $\alpha$ . The insensitivity to  $\alpha$  may be due to the fact that at this operating point, most of the probability density of the received signal vector is concentrated within the small number of decision regions adjacent to the source signal vectors, while the remaining decision regions are very

Figure 2.11. Random coding bound for 4-bit I&Q quantization.

Figure 2.12. Random coding bound for 4-bit I&Q quantization.

under-utilized. This implies that some improvement in performance might be obtainable by the use of non-uniform quantization, with a greater number of decision regions concentrated near the source signal vectors. This, however, is similar to the issue of fine-tuning the decision regions for phase-only quantization, in that the gains to be obtained are probably not worth the added hardware complexity. Fine-tuning of quantization regions can do nothing more than close the gap between quantized and unquantized performance, which for 4-bit quantized I and Q is approximately 0.2dB. Furthermore, uniform

quantization has the advantage of allowing a standard analog-to-digital converter to be used in the demodulator.

### 2.5 The Log-Likelihood Function

Another issue raised by the quantization of the received signal vector is the calculation of the metrics to be used by the Viterbi decoder. The objective of a good decoder is to select the sequence of encoder output signal vectors which is most likely to be correct, given the sequence of received noisy vectors, that is, to select the encoder output sequence  $S_m$  which maximizes  $P(S_m|Z)$ . If all of the sequences have equal a priori probabilities, and the channel is continuous, then it is equivalent to select the maximum likelihood sequence, that is the sequence  $S_{\mathsf{m}}$  which maximizes  $p(Z|S_m)$ . Here,  $P(S_m|Z)$  denotes the conditioned probability of  $S_m$  given Z, while  $p(Z|S_m)$  denotes the conditioned probability density function of Z given Sm. If the channel is memoryless (that is no signalling interval is affected by any other signalling interval) then

$$p(Z|S_m) = \prod_{i=1}^{L} p(z_i|s_{mi})$$

(2.9)

where L is the length of the sequence and  $z_1$  and  $s_{m1}$  are the individual elements of the sequences Z and  $S_m$

respectively. It is equivalent, and computationally more efficient to use log-likelihood functions which may be added, rather than probability density functions, which must be multiplied. Then the decoder would select  $S_m$  to maximize

$$-\ln[p(Z|S_m)] = \sum_{i=1}^{L} -\ln[p(z_i|s_{mi})]. \quad (2.10)$$

If the noise is additive white Gaussian then

$$p(z_{i}|s_{mi}) = \frac{1}{2\pi\sigma^{2}} \exp\left(-\frac{1}{2\sigma^{2}}|z_{i}-s_{mi}|^{2}\right)$$

(2.11)

where  $|z_i - s_{mi}|$  is the Euclidean distance between  $z_i$  and  $s_{mi}$ . Taking the log-likelihood function leads to the use of Euclidean distance squared as the metric in Viterbi decoding of TCM on the memoryless additive white Gaussian channel.

If the channel is discrete, as it becomes when the quantizer is added to the system, and all  $S_m$  have equal a priori probabilities, then maximizing  $P(S_m|Z)$  is equivalent to maximizing  $P(Z|S_m)$ . Here Z denotes the sequence of discrete quantizer outputs, rather than the sequence of continuous signal vectors. The decoder would then select  $S_m$  to maximize

$$P(Z|S_m) = \prod_{i=1}^{L} P(z_i|s_{mi})$$

(2.12)

where the probabilities  $P(z_1 | s_{mi})$  are the transitional probabilities of the channel. As in the case of the continuous channel, it is preferable to use log-likelihood functions, which may be added, rather than probabilities, which must be multiplied, so the decoder is built to select the sequence  $S_m$  which maximizes

$$-\ln[P(Z|S_{m})] = \sum_{i=1}^{L} -\ln[P(z_{i}|s_{mi})]. \qquad (2.13)$$

This condition is equivalently fulfilled by using metrics of the form a + b  $\ln[P(z_i|s_{mi})]$  where a and b are arbitrary constants which may be selected to allow the range of metrics to best be represented by a particular hardware design.

# 2.6 Calculation of Probabilities and Related Parameters

For the discrete channel formed when any form of quantizer is incorporated into a TCM system, the channel capacity, the random coding bound, and the optimal set of metrics must be calculated from the transitional

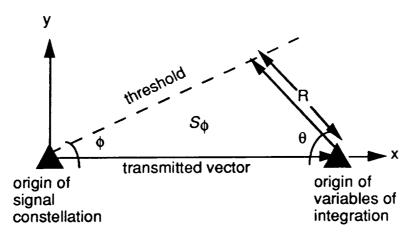

Figure 2.13. Region of integration for sector probability.

probabilities. The transitional probabilities are found by integrating the probability density function of the received vector, given the transmitted vector, over each decision region. For phase-only quantization, the decision regions are angular regions as shown in Figures 2.1a and 2.1b, and also in figures 2.2a, 2.2b, and 2.2c. To find the transitional probabilities for phase-only quantization we first consider the problem of finding the probability,  $P\phi$ , that the phase of the received signal vector will be removed from the phase of the transmitted signal vector by no more than the angle  $\phi$ , as shown in Figure 2.13. This may be found by integrating the two dimensional Gaussian distribution function over the region S $\phi$  giving:

$$P_{\phi} = \iint_{S_{\phi}} \frac{1}{2\pi\sigma^2} \exp\left\{-\frac{1}{2\sigma^2} \left[(x-1)^2 + y^2\right]\right\} dx dy \quad (2.14)$$

•

where

$$\sigma^2 = \frac{N_0}{2E_s}$$

(2.15)

The classical approach to this problem is to convert from rectangular to polar coordinates giving:

$$P_{\phi} = \int_{0}^{\phi} \int_{0}^{\infty} \frac{1}{2\pi\sigma^{2}} \exp\left\{-\frac{1}{2\sigma^{2}} \left[R^{2} - 2R\cos\theta + 1\right]\right\} R dR d\theta$$

$$= \int_{0}^{\phi} f(\theta|0) d\theta \qquad (2.16)$$

where  $f(\theta|0)$  denotes the phase density function, given that a phase of 0 was transmitted. Integrating over R gives:

$$f(\theta) = \frac{1}{2\pi} \exp\left\{-\frac{1}{2\sigma^2}\right\} + \frac{1}{\sqrt{2\pi}} \exp\left\{-\frac{\sin^2\theta}{2\sigma^2}\right\} \frac{\cos\theta}{\sigma} \left\{-\frac{\cos\theta}{\sigma}\right\}$$

(2.17)

where

$$Q(x) = \frac{1}{\sqrt{2\pi}} \int_{x}^{\infty} \exp\left\{-\frac{y^2}{2\sigma^2}\right\} dy$$

(2.18)

Finding the phase sector probability by this method requires that a double integration be performed

numerically, since no closed form solution for the Q() integral exists.

An alternative method for calculating  $P_{\phi}$ , which requires only that single integrals be performed numerically is obtained by applying the change of variables:

$$R = \left[ (x-1)^2 + y^2 \right]^{\frac{1}{2}}$$

(2.19)

$$\boldsymbol{\theta} = \arctan\left(\frac{\mathbf{y}}{1 - \mathbf{x}}\right) \tag{2.20}$$

This gives the following integral:

$$P_{\phi} = \iint_{\substack{S\phi}} \frac{1}{2\pi\sigma^2} \operatorname{R} \exp\left(-\frac{1}{2\sigma^2} \operatorname{R}^2\right) dR d\theta \qquad (2.21)$$

In this expression, the integral with respect to R can be solved in closed form. The limits on R are found as a function of  $\theta$ :

$$0 \le R \le \left[\frac{\sin \theta}{\tan \phi} + \cos \theta\right]^{-1} \qquad \text{for } 0 \le \theta \le \pi - \phi$$

$$0 \le R \le \infty$$

for  $\pi - \phi \le \theta \le \pi$

The integral is then broken into two parts and solved giving:

$$P_{\phi} = \frac{1}{2} - \frac{1}{2\pi} \int_{0}^{\pi-\phi} \exp\left\{-\frac{1}{2\sigma^{2}} \left[\frac{\sin\theta}{\tan\phi} + \cos\theta\right]^{-2}\right\} d\theta (2.22)$$

where the remaining single integral is then solved numerically. The probability that the received signal vector will have phase between  $\phi_0$  and  $\phi_1$  with respect to the transmitted vector may be found from

$$P_{\phi 0}, \phi_1 = P[\phi_0 < \phi < \phi_1] = P_{\phi 1} - P_{\phi 0}.$$

(2.23)

One problem with this form is that precision problems can arise due to the fact that the difference  $P_{\phi 1} - P_{\phi 0}$  can be quite small relative to  $P_{\phi 1}$  and  $P_{\phi 0}$ . This problem may be aleviated by rewriting equation (2.23) in the form:

$$P_{\phi 0,\phi 1} = \frac{1}{2\pi} \int_{0}^{\pi-\phi 1} \exp \left\{ -\frac{1}{2\sigma^2} \left[ \frac{\sin\theta}{\tan\phi^1} + \cos\theta \right]^{-2} \right\}$$

$$- \exp\left\{-\frac{1}{2\sigma^2}\left[\frac{\sin\theta}{\tan\phi0} + \cos\theta\right]^{-2}\right\} d\theta$$

$$+ \frac{1}{2\pi} \int_{\phi_0}^{\phi_1} \exp\left\{-\frac{1}{2\sigma^2} \left[\frac{\sin\theta}{\tan\phi_0} + \cos\theta\right]^{-2}\right\} d\theta.$$

(2.24)

This form requires more computational time, but yields greater precision when numerical integration methods are applied. A side benefit of equation (2.22) is that it leads directly to an alternative form for the Q() function as follows:

$$Q\left(\frac{1}{\sigma}\right) = 1 - 2P_{\pi/2} = \frac{1}{\pi} \int_{0}^{\pi/2} \exp\left\{-\frac{1}{2\sigma^{2}\cos^{2}\theta}\right\} d\theta \qquad (2.25)$$

Substituting x for  $\frac{1}{\sigma}$  gives:

$$Q(x) = \frac{1}{\pi} \int_0^{\pi/2} \exp\left\{-\frac{1}{2} \left(\frac{x}{\cos\theta}\right)^2\right\} d\theta \qquad (2.26)$$

This form of the integral has finite limits, unlike the standard form.

Because the system is symmetrical, that is, because the probability density function for the received phase given any transmited phase,  $f(\theta_j | \theta_i)$ , is equal to  $f(\theta_j - \theta_i | 0)$ , formula (2.24) may be used to calculate all of the transitional probabilities required in the analysis of any

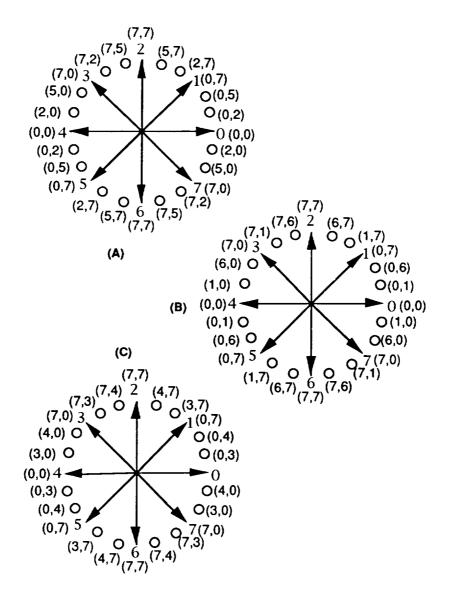

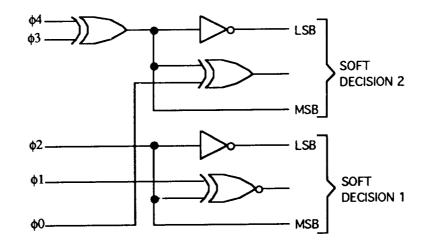

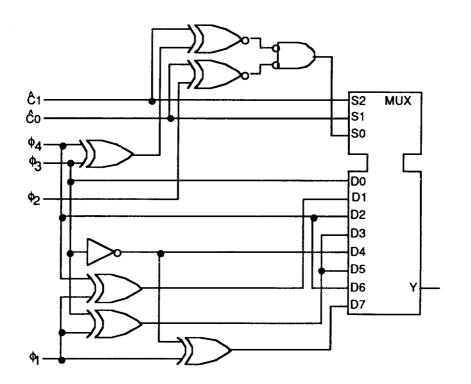

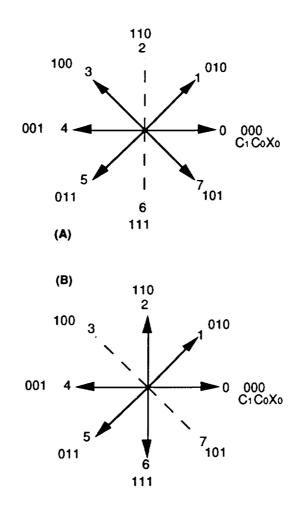

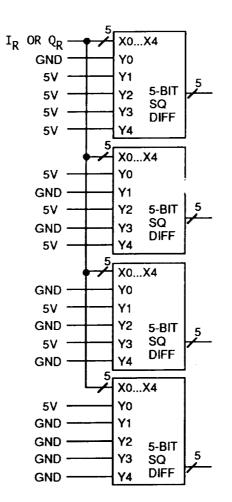

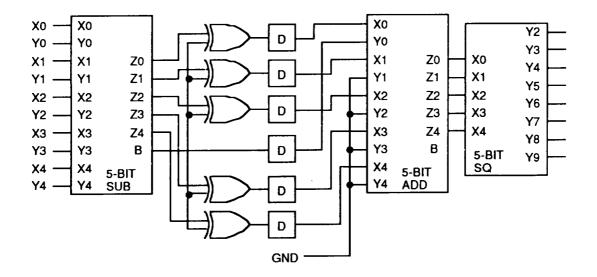

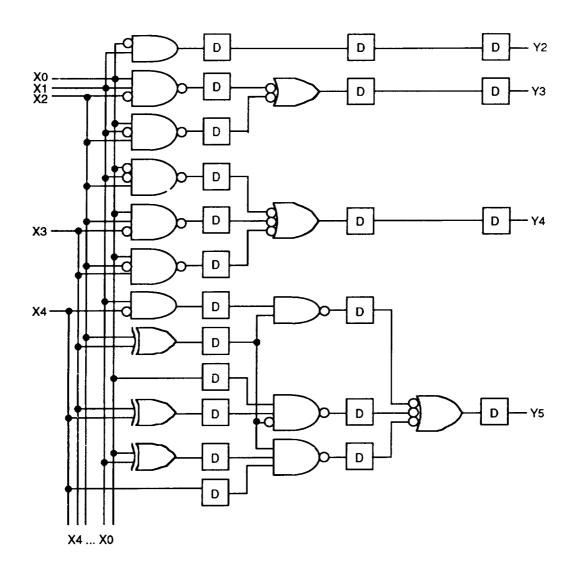

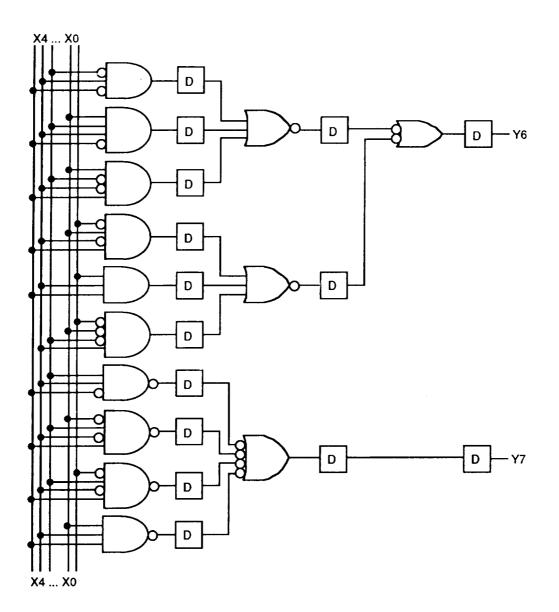

phase-only quantization scheme. These may then be used to calculate  $R_0$ , C, or log likelihood metrics. The  $R_0$  and C values used in the previous section were found by writing a "C" computer program to calculate the phase transition probabilities by numerical integration of equation (2.24). These were stored in a table and used to calculate C and  $R_0$  from equations (2.6) and (2.5) respectively.