EX

# Kohei Nagaoka<sup>1</sup>, Kentaro Chikamatsu<sup>2</sup>, Atsushi Yamaguchi<sup>2</sup>, Ken Nakahara<sup>2</sup>, and Takashi Hikihara<sup>1a)</sup>

<sup>1</sup> Department of Electrical Engineering, Kyoto University, Katsura, Nishikyo, Kyoto 615–8510, Japan

<sup>2</sup> Power Electronics R&D Division, ROHM Co., Ltd., Mizosaki-cho 21, Saiin, Ukyo, Kyoto 615–8585, Japan

a) hikihara.takashi.2n@kyoto-u.ac.jp

**Abstract:** This paper focuses on a development and an evaluation of high-speed gate drive circuit for SiC power MOSFET by GaN HEMT. The increasing requests to SiC power devices face to the difficulty of the gate drive because of the mismatching between device parameters and conventional driving circuits for Si power devices. Up to now, high frequency switching is the main target of logic and radio applications of active devices. The drive circuit of power devises has not been considered at the switching over MHz. Moreover, p-type SiC and GaN power devices are still not in our hand in spite of the development of n-type device. Therefore there are difficulties in the design of symmetric circuit structure to avoid the management of ground setting. This paper proposes a gate drive circuit applied GaN devices for high-speed switching of an SiC MOSFET. The proposed circuit is designed for the operation of SiC MOSFET at 10 MHz. The feasibility is confirmed through a simple switching circuit.

**Keywords:** GaN HEMT, SiC MOSFET, gate drive circuit, high-speed switching

Classification: Electron devices, circuits, and systems

#### References

- [1] H. Matsunami: *Technology of Semiconductor SiC and Its Application* (Nikkan Kogyo Shimbun, Tokyo, 2003) (in Japanese).

- [2] S. Pendharkar and C. Chey: ECS Trans. 50 [3] (2013) 189. DOI:10.1149/05003.

0189ecst

- [3] T. Takuno, T. Hikihara, T. Tsuno and S. Hatsukawa: 13th European Conference on Power Electronics and Applications (EPE2009), Balcelona, Spain (2009).

- [4] J. Würfl, O. Hilt, E. Bahat-Treidel, P. Kurpas, S. A. Chevchenko, O. Bengtsson, E. Ersoy, A. Liero, A. Wentzel, W. Heinrich, N. Badawi and S. Dieckerhoff: Proc. of the 8th European Microwave Integrated Circuits Conference, Nuremberg, Germany (2013) 176.

- [5] K. Nagaoka and T. Hikihara: Technical Meeting of IEE Japan, ECT 14 [46] (2014) 65 (in Japanese).

[6] J. Kashiwagi, T. Fujiwara, M. Akutsu, N. Ito, K. Chikamatsu and K. Nakahara: IEEE Electron Device Lett. 34 (2013) 1109. DOI:10.1109/LED.2013.2272491

# 1 Introduction

Power electronics technology has strongly depended on the development of power devices. SiC power device is one of possible next devices for power conversion. The extreme physical features of the SiC power devices are listed as high withstand voltage, fast switching and high frequency operation, high temperature tolerance, and low on-state-resistance [1]. However it has not clearly been discussed from the viewpoint of circuit implementation. In applying SiC power devices, the peripheral technologies including circuit design, packaging, and the method of drive are critical as much as the development of devices [2]. SiC JFET has an advantage in its high-speed operation, but normally on characteristics causes the difficulty of application [3]. SiC MOSFET is a normally off device, but the oxide layer causes the large capacitance which does not fit to high-speed switching. To drive an SiC MOSFET at high frequency, a gate drive circuit needs to change a gate voltage of the power device by rapid charge and discharge of the gate input capacitor with a high current. That is, the high-speed gate drive circuit for an SiC power MOSFET must have the abilities of high-speed response and power capability similar to low power converter circuits.

This paper proposes a gate drive circuit with GaN HEMTs. Due to the material properties and the device structure, GaN HEMTs have succeeded in the field of microwave electronics. Moreover, they are receiving a lot of attention as a power switching device with both fast response and power capacity [4]. However the defects of wafer are still the obstacles for developing high power devices. GaN HEMTs have a low gate threshold voltage, so that this leads both advantage of easy drive at low gate voltage and disadvantage of avoiding noise in power applications [5]. The advantage is well-suited for a high-speed gate drive circuit, which simultaneously operates as an interface between a drive-control circuit and a power conversion circuit. According to the concept, this paper proposes a high-speed gate drive circuit for SiC power MOSFET by GaN HEMT.

Section 2 describes the constitution of a proposed gate drive circuit and the characteristics of applied GaN HEMTs. Section 3 explains the operation of the gate drive circuit, and evaluate the proposed circuit.

## 2 Configuration of gate drive circuit with GaN HEMT

## 2.1 Configuration of gate drive circuit

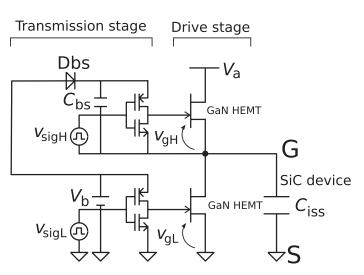

A proposed gate drive circuit is shown in Fig. 1. In the figure, the load capacitance corresponds to an input capacitance  $C_{iss}$  of an SiC power device. G and S denote the gate and the source terminal, respectively. The proposed circuit consists of two stages: Drive stage (DS) and Transmission stage (TS).

The DS is a half-bridge circuit consisting of two GaN HEMTs. The half-bridge circuit charges and discharges the input capacitor  $C_{iss}$  to drive the SiC power

Fig. 1. Constitution of proposed gate drive circuit.

device. Both GaN HEMTs are n-channel type transistors. It is because n-channel GaN devices are ahead of p-channel GaN devices in development currently.

The TS cannot drive SiC directly but can operate the SiC indirectly through DS. Each GaN HEMT in the DS needs a driver and a drive-control signal. As a gate driver of the GaN HEMTs, a push-pull structure of circuit is applied. Due to the low driving voltage of GaN HEMT, the driver requires a current amplifier without a voltage amplifier. Then, each driver of the GaN HEMTs needs a power source. For the high side power source, a bootstrap capacitor is adopted, while a dc power supply is applied to the power source of the low side driver. Owing to the low driving voltage and the small input capacitance, the GaN HEMTs exhibit low gate charge. Hence, a ceramic chip capacitor is enough to employ as the bootstrap capacitor. The structure becomes an advantage with respect to reduce the size and the parasitic wire inductance of high side circuit. A drive-control signal generator is the other structure element of TS. As shown in Fig. 1, we call the output of high side  $v_{sigH}$ , and the low side  $v_{sigL}$ , respectively. These phases must be mutually inverted, and they have different reference potentials.

## 2.2 Characteristics of GaN HEMT

The device fabrication process is basically published in [6], but some differences were introduced as described in this paragraph. 6-inch Si (111) was used as a substrate for the nitride epilayers, which comprised a buffer layer, 1- $\mu$ m GaN, 20nm Al<sub>0.19</sub>Ga<sub>0.81</sub>N, and 100-nm SiN. 2-dimensional electron gas naturally formed at this AlGaN/GaN interface had a typical sheet resistance of 561  $\Omega$ /square. The device geometry parameters were: 1- $\mu$ m gate length, 2- $\mu$ m source-gate length, 3- $\mu$ m gate-drain length, 0.5- $\mu$ m gate field plate length, and 24.6-cm total gate width. The SiN above the gate area was removed by a mixed gas of CF<sub>4</sub> and O<sub>2</sub> to expose the top AlGaN layer, and then the AlGaN was processed by use of the same conditions as described in [6], which was followed by 40-nm Al<sub>2</sub>O<sub>3</sub> deposition using atomic layer deposition method. Ni/Au/Ti/Ni was sequentially deposited as the gate metals, and the source and drain Ohmic metals were the same as already reported in [6].

Dicing process into 1.9-mm by 3.8-mm square was carried out after the wafer processes. These chips had an active area of 2.79-mm<sup>2</sup>, and were mounted on a 3-electrode-pin metal plate with their substrate side down. Wire bonding was adopted to electrically connect the metal pads of a chip to the pins. These chip-mounted metal plates were molded by resin with a mold size of 11.9-mm wide, 15.45-mm long, and 4.0-mm thick. Three electrode pins were separated by 2.54-mm each other.

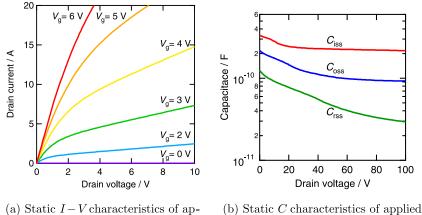

Fig. 2 shows the characteristics of the GaN HEMT applied at the high side of gate drive circuit. The figure represents the drain current and the parasitic capacitances, which means  $C_{iss}$ , output ( $C_{oss}$ ), and feedback capacitance ( $C_{rss}$ ), as a function of drain voltage, respectively. The measurements were performed by using a power device analyzer/curve tracer (Keysight, B1505A).

When the GaN device is applied to the gate drive circuit shown in Fig. 1, the capability of the drive of SiC power MOSFET can be estimated based on the *I-V* characteristics. The current at a set  $V_g$  decides the limitation of charging in a turn-on duration. The detail characteristics of the devices have already been discussed up to the switching frequency 10 MHz in [6].

(a) Static I - V characteristics of applied GaN HEMT.

GaN HEMT.

Fig. 2. GaN HEMT applied to gate drive circuit (typical).

# 3 Operation of gate drive circuit with GaN HEMT and switching characteristics of SiC MOSFET

#### 3.1 Circuit configurations

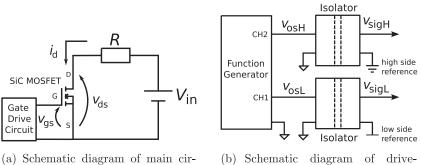

SiC MOSFET, which has a trench gate structure, is mounted in the switching power circuit for test in Fig. 3(a) with a resistive load. Hereafter, the SiC MOSFET is referred to as SiC TMOSFET. In the circuit, the power supply voltage  $V_{in}$  is set at 200 V, and the resistance *R* at 65.5  $\Omega$ . The power source of DS  $V_a$  is set at 18 V. With the setting, the range of the gate voltage  $v_{gs}$  is from 0 V to 18 V. In TS  $V_b$  is set at 4 V.  $V_b$  becomes the driving voltage of the GaN HEMTs. At the setting of  $V_a$  and  $V_b$ , the GaN HEMT can feed over 5 A in most of the switching duration as shown Fig. 2(a). For  $C_{iss}$  smaller than 2500 pF, the charging current raises the gate voltage up to 20 V within 10 ns, which is 10% of the period corresponding to 10 MHz.

(a) Schematic diagram of main circuit.

Fig. 3. Schematic diagram of circuits for driving test.

control signal generator.

The bootstrap capacitor supplies an electrical charge to make the high side GaN HEMT turn on. 2 nC is enough for the charge because the input capacitance of the GaN HEMT is smaller than 500 pF as shown in Fig. 2(b). When the bootstrap capacitor supplies 2 nC, more than 20 nF is required as the capacitance  $C_{bs}$  to suppress the voltage drop of the bootstrap capacitor under 0.1 V. In this paper, the capacitance is set at 330 nF to eliminate the influence of the voltage drop surely. Also, the push-pull circuit uses a small rated Silicon N-channel/P-channel MOSFET (ROHM, US6M1).

The bootstrap diode  $D_{bs}$  receives the voltage  $V_a$  when the low side GaN HEMT is off. In this setting,  $D_{bs}$  should withstand higher voltage than 18 V. Moreover, the reverse recovery time should be short enough in comparison with a switching period. In this paper, the gate drive circuit is designed to realize a driving operation of TMOSFET at 10 MHz. To realize the operation, the target reverse recovery time is set shorter than 4% of the switching period corresponding to 10 MHz. The selection of diode (DIODES, 1N4448HWS) depends on the rated breakdown voltage 80 V and maximum reverse recovery time at 4 ns.

Fig. 3(b) shows a schematic diagram of a drive-control signal generator, which generates  $v_{sigH}$  and  $v_{sigL}$  as shown in Fig. 1. Input signals  $v_{osL}$  and  $v_{osH}$  are given by the channel 1 and the channel 2 of a function generator, respectively. Each input signal is transmitted by a digital isolator (Silicon Laboratories, Si8660) individually. The phase between the two signals is regulated by the function generator, and the two signals can have different references by the digital isolators. Also, this configuration realizes insulation between the grounds of the input control circuit and of the power circuit.

## 3.2 Estimation of drive circuit

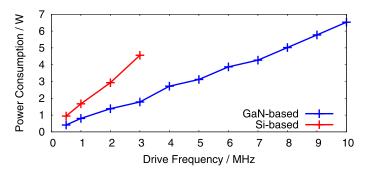

The newly proposed gate drive circuit are requested to have advantages of highspeed switching to the conventional drive method. It also must lead the high frequency switching of SiC MOSFETs. Before driving SiC MOSFET, here, the efficiency of the proposed drive circuit was estimated. The power consumption of the proposed drive circuit was compared to a drive device BM6101FV-C (ROHM Co.,Ltd.), which is a silicon based devices with on-tip transformer for isolation and thermal protection.

At a capacitive load  $C_{\rm L} = 1 \,\text{nF}$  equivalent to typical SiC power MOSFETs, the Fig. 4 shows the remarkable superiority of the proposed drive circuit. The power consumption in drive circuit is half of BM6101FV-C at 3 MHz. BM6101FV-C shows the limitation of the output frequency because of the input pulse width 130 ns (standard). If we set the duty at 50%, the output frequency becomes 3.8 MHz. This is the reason that there is no data of power consumption by BM6101FV-C exceeding 3 MHz. This is due to the thermal protection of the device. Of course it is an example of drive device, but apparently it is a typical Si-based driver which the SiC power devices can select for its operation. On the other hand, the proposed gate drive circuit shows the possibility of output until 10 MHz.

**Fig. 4.** Evaluation of power loss of proposed driver circuit (blue) with comparison to conventional Si gate driver (red) (BM6101FV-C (ROHM Co.,Ltd.)).

## 3.3 Measurement system

Switching characteristics of the SiC TMOSFET was measured by an oscilloscope (Tektronix, MDO4104-3). In this measurement, the gate voltage  $v_{gs}$  and the drain voltage  $v_{ds}$  waveforms were obtained by voltage probes (Tektronix, TPP1000). Also, the drain current  $i_d$  was obtained by a current probe (Tektronix, TCP0030).

Operation characteristics of the gate drive circuit was also measured by an oscilloscope (Tektronix, TPS2024). In this experiment, the gate voltages of GaN HEMTs  $v_{gH}$  and  $v_{gL}$  with the input signals  $v_{osH}$  and  $v_{osL}$  were measured by voltage probes (Tektronix, P2220).

As mentioned above, the switching characteristics in the power circuit and the operation characteristics in the gate drive circuit were obtained by different oscilloscopes. It implies that these two data have different time references.

## 3.4 High-speed drive of TMOSFET

Here, the drive circuit with GaN HEMT is examined to drive TMOSFET at the setting of  $V_{in} = 200$  V and  $I_d = 3$  A with a noninductive resistance *R* at 65.5  $\Omega$ . The rating of TMOSFET is higher than the setting, but they are decided considering the surge voltage and inrush current at high frequency switching in the main circuit.

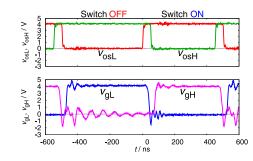

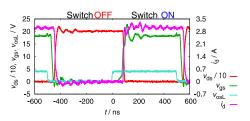

Figs. 5(a) and (b) show the operation characteristics of the gate drive circuit and the switching characteristics of SiC TMOSFET at 1 MHz. In the figures we can estimate the operation characteristics of the drive circuit. In Fig. 5(a), the high side

(a) Input signals and gate voltage waveforms of GaN HEMTs at 1 MHz.

(b) Switching characteristics of SiC TMOS-FET at 1 MHz.

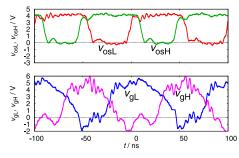

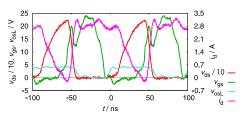

(c) Input signals and gate voltage waveforms of GaN HEMTs at 10 MHz.

(d) Switching characteristics of SiC TMOS-FET at  $10\,\mathrm{MHz}.$

Fig. 5. Switched results of SiC TMOSFET by proposed gate drive circuit at switching frequencies 1 MHz and 10 MHz.

figure shows the waveforms of  $v_{osL}$  and  $v_{osH}$ , the low side figure the waveforms of  $v_{gH}$  and  $v_{gL}$ . Fig. 5(b) shows the waveforms of  $v_{gs}$ ,  $v_{ds}$ , and  $i_d$ .

As shown in Fig. 5(a), when  $v_{osL}$  is in a high level,  $v_{gL}$  is in a low level because the push-pull circuit inverts the phase of an input signal. Also,  $v_{osH}$  is in a low level, and  $v_{gH}$  is in a high level by the similar transmission. Then, the high side GaN HEMT is on, and the low side GaN HEMT is off. The gate drive circuit generates a high level gate voltage. When the phase relationship is inverted, the drive circuit generates a low level voltage. Thus, the outputs  $v_{gs}$  of the gate drive circuit is around 18 V in Fig. 5(b) and the frequency keeps 1 MHz. As a result, the SiC TMOSFET is switched at 1 MHz, obviously.

Figs. 5(c) and (d) show the operation characteristics of the gate drive circuit at 10 MHz and the switching characteristics of SiC TMOSFET. When the switching frequency is set at 10 MHz, the period is close to the time scale of transient state at switching. It appears to the ringing of the gate drive voltage from off and on. However, the gate drive circuit achieves a driving operation at 10 MHz, due to the dull change of the switching waveform from on to off.

As shown in Fig. 5(d), the turn-off duration of SiC TMOSFET is longer than the turn-on. From the rising point to 126 V, it takes 11 ns. It almost coincides to the time constant 10 ns decided by the load  $R = 65.5 \Omega$  and  $C_{oss} = 153 \text{ pF}$  at  $V_{ds} =$ 25 V. To achieve the switching, the on-duration of low side GaN HEMT is adjusted longer than the on-duration of the high side GaN HEMT. At the on-duration of TMOSFET, the waveform of  $v_{gs}$  shows a pulsed change. In the long term measurement, the wave shape quasi-periodically changes. It does not depends on the device characteristics. As a result, the drive circuit could operate the TMOSFET correctly at 10 MHz.

As a result, the switching of the SiC TMOSFET is realized at 10 MHz as we expected at the design of circuit parameters. By the same design, the gate drive voltage was generated by 15 MHz without any improvement.

# 4 Conclusion

This paper proposes a gate drive circuit with GaN HEMTs for an SiC power MOSFET. In experiments, the gate drive circuit designed for SiC TMOSFET to operate at 10 MHz. The high frequency drive of SiC TMOSFET was successfully achieved by the n-channel GaN HEMT bridge circuit proposed here as a gate driver. The drive circuit shows higher efficiency to a Si-based driver. It was shown that, at 3 MHz, the power consumption of the drive circuit is half of the Si-based driver. The GaN HEMT circuit was proved to be an appropriate interface between a signal circuit and a power circuit. It was confirmed that the drive circuit could generate the drive voltage up to 15 MHz. More advancement of devices and circuit design is required to exceed 15 MHz switching of SiC MOSFETs as follows. The push-pull circuit operating a GaN HEMT needs higher-speed response. For the design of the gate drive circuit, a gate input capacitance of a GaN HEMT should be arranged to meet the driving capability of the push-pull circuit. Parasitic elements, which appear in both circuits and devices, cause power loss at chattering of switches and should be taken into account. The load in this paper is fixed to a resistance. From the viewpoint of power electronics, inductive and capacitive loads must be considered. At high-speed switching, the inductive load may give the transient change to the characteristics of power devices. At the same time, the high switching frequency is expected to reduce inductances in the circuit. The trade-off of the inductance at high switching frequency will be an important topics in the next phase. Moreover, high frequency switching power source is expected to the capacitive load like a RF spattering. These engineering applications will be targets of the high-speed and high frequency switching of power devices.

At any rate, the new circuit proposed in this paper is capable of achieving high frequency switching of SiC power MOSFET, maximizing its unique features. Thereby not only high frequency power electronics will develop more in laboratory but also novel practical applications will emerge.

In addition, characteristics of SiC power device become critical at high-speed switching. For example, it is clearly understood that the delay by Miller effect of power device governs the limitation of switching speed and switching frequency. Even if the gate drive circuit becomes high-speed, there appear the difficulties of the switching operation of power device. We believe that the collaborative efforts on device and circuit design should be accelerated more and more to exceed the physical limitation.

# Acknowledgements

This research is partially supported by Kyoto Super Cluster Program (JST). KN and TH also acknowledge the partial support by Council for Science, Technology and Innovation (CSTI), Cross-ministerial Strategic Innovation Promotion Program (SIP), "Next-generation power electronics" (NEDO).