### Samenstelling promotiecommissie:

Voorzitter: prof. dr. C. Hoede Universiteit Twente, EWI

Secretaris: prof. dr. ir. A. J. Mouthaan Universiteit Twente, EWI

Promotor: prof. ir. A. J. M. van Tuijl Universiteit Twente, EWI

Assistent Promotor: dr. ing. E. A. M. Klumperink Universiteit Twente, EWI

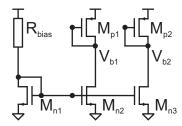

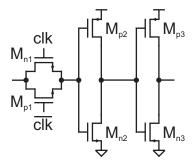

Referent: dr. ir. J. P. M. van Lammeren NXP, Nijmegen

Leden: prof. dr. ir. B. Nauta Universiteit Twente, EWI

prof. dr. ir. W. Dehaene KU Leuven prof. dr. ir. R. H. J. M. Otten TU Eindhoven

prof. dr. ir. G. J. M. Smit Universiteit Twente, EWI

Title: HIGH-SPEED GLOBAL ON-CHIP INTERCONNECTS AND

TRANSCEIVERS

Author: Eisse Mensink

ISBN: 978-90-365-2504-6

This research was supported by the Technology Foundation STW, applied science division of NWO and the technology programme of the Ministry of Economic Affairs.

### HIGH-SPEED GLOBAL ON-CHIP INTERCONNECTS AND TRANSCEIVERS

### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Universiteit Twente, op gezag van de rector magnificus, prof. dr. W.H.M. Zijm, volgens besluit van het College voor Promoties in het openbaar te verdedigen op donderdag 28 juni 2007 om 13.15 uur

door

Eisse Mensink geboren op 10 januari 1979 te Almelo Dit proefschrift is goedgekeurd door:

de promotor prof. ir. A. J. M. van Tuijl

de assistent promotor dr. ing. E. A. M. Klumperink

# **Contents**

| 1 | Introduction                                  | 1  | L |

|---|-----------------------------------------------|----|---|

|   | 1.1 Communication over long distances         | 1  |   |

|   | 1.2 Interconnects in CMOS technologies        | 2  |   |

|   | 1.3 Interconnects and technology scaling      | 3  |   |

|   | 1.4 Delay of global interconnects             | 4  |   |

|   | 1.5 Global interconnect problems              |    |   |

|   | 1.5.1 Introduction                            | 5  | , |

|   | 1.5.2 Transmitter and receiver model          | 7  | , |

|   | 1.5.3 Achievable data rate                    |    |   |

|   | 1.5.4 Data integrity                          | 11 |   |

|   | 1.5.5 Chip area                               |    |   |

|   | 1.5.6 Power consumption                       |    |   |

|   | 1.6 Solutions in literature                   | 17 | • |

|   | 1.6.1 Introduction                            | 17 | • |

|   | 1.6.2 Delay                                   | 17 | • |

|   | 1.6.3 Achievable data rate                    | 18 | , |

|   | 1.6.4 Power consumption                       |    |   |

|   | 1.6.5 Data integrity                          |    |   |

|   | 1.7 Challenges                                |    |   |

|   | 1.8 Scope of this thesis                      |    |   |

| 2 | Interconnect models                           |    |   |

|   | 2.1 Introduction.                             |    |   |

|   | 2.2 Location of interconnects in an IC        |    |   |

|   | 2.3 Response to electromagnetic waves         |    |   |

|   | 2.3.1 Introduction                            |    |   |

|   | 2.3.2 Definitions                             |    |   |

|   | 2.3.3 dV(z)/dz as a function of I(z)          |    |   |

|   | 2.3.4 dI(z)/dz as a function of V(z)          | 26 | į |

|   | 2.4 Distributed model                         |    |   |

|   | 2.4.1 Introduction                            |    |   |

|   | 2.4.2 Telegrapher's equations                 |    |   |

|   | 2.4.3 Attenuation, reflections and distortion |    |   |

|   | 2.4.4 S-parameters                            |    |   |

|   | 2.4.5 Transfer functions                      |    |   |

|   | 2.4.6 Power consumption                       | 37 | • |

| 2.4.7 Additional power consumption in receiver  | 39 |

|-------------------------------------------------|----|

| 2.5 Expanded distributed model                  | 41 |

| 2.6 Lumped versus distributed models            | 43 |

| 2.7 3D EM-field simulator                       | 45 |

| 2.8 Summary                                     | 47 |

| 3 Interconnect design and termination concepts  |    |

| 3.1 Introduction.                               |    |

| 3.2 Optimal dimensions                          | 49 |

| 3.2.1 Introduction                              |    |

| 3.2.2 LC or RC                                  |    |

| 3.2.3 Optimized dimensions                      | 53 |

| 3.3 Source impedance                            |    |

| 3.3.1 Introduction                              |    |

| 3.3.2 Ideal source impedance                    |    |

| 3.3.3 First-order model                         |    |

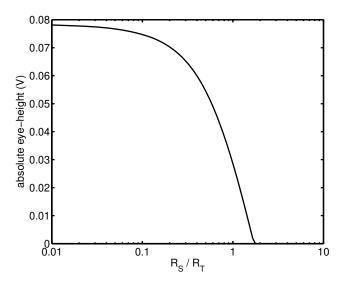

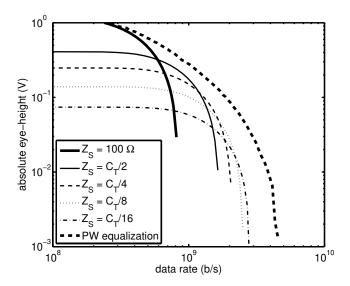

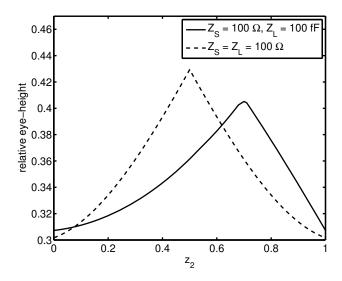

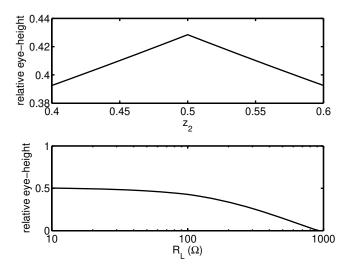

| 3.3.4 Eye-diagram properties                    |    |

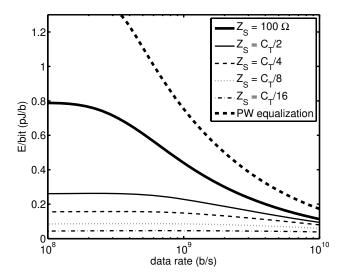

| 3.3.5 Power consumption.                        |    |

| 3.3.6 Biasing circuit                           |    |

| 3.4 Load impedance                              |    |

| 3.4.1 Introduction                              |    |

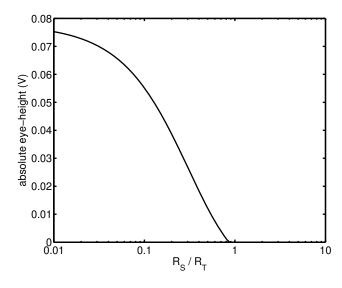

| 3.4.2 Ideal load impedance                      |    |

| 3.4.3 First-order model for delay and bandwidth |    |

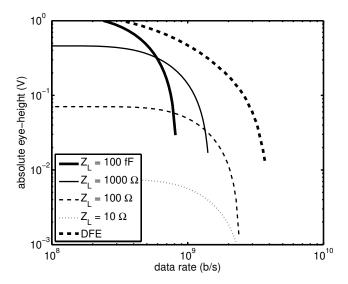

| 3.4.4 Eye-diagram properties                    |    |

| 3.4.5 Power consumption                         |    |

| 3.4.6 First-order model for power consumption   |    |

| 3.4.7 Inductive termination                     |    |

| 3.5 Comparison                                  |    |

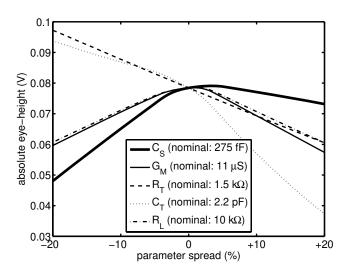

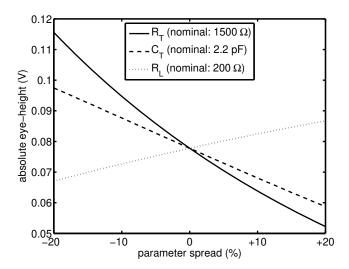

| 3.6 Parameter spread                            |    |

| 3.6.1 Introduction                              |    |

| 3.6.2 Capacitive pre-emphasis transmitter       |    |

| 3.6.3 Resistive termination                     |    |

| 3.7 Equalization techniques                     |    |

| 3.7.1 Introduction                              |    |

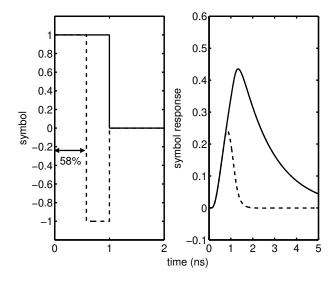

| 3.7.2 Pulse-width equalization                  |    |

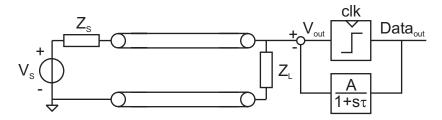

| 3.7.3 Decision feedback equalization            | 77 |

| 3.8 Summary                                     |    |

| 4 Data integrity                                |    |

| 4.1 Introduction.                               |    |

| 4.2 Offset                                      |    |

| 4.3 Neighbor-to-neighbor crosstalk              | 83 |

| 4.3.1 Introduction                              |    |

| 4.3.2 Crosstalk and twists                      |    |

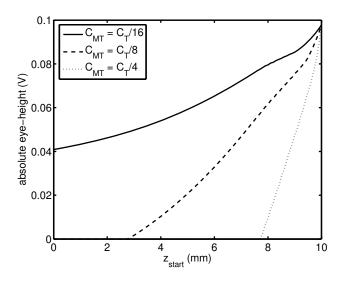

| 4.3.3 Optimal position of the single twist      |    |

| 4.3.4 First-order model                         |    |

| 4.3.5 Optimal position of the double twist      |    |

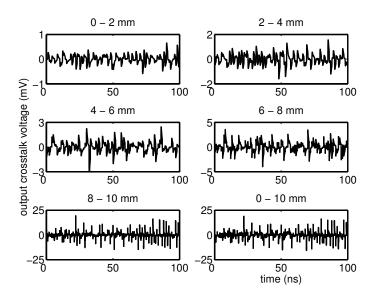

| 4.3.6 3D EM-field simulation                    |    |

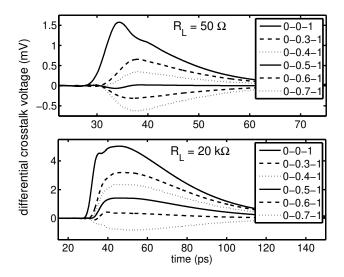

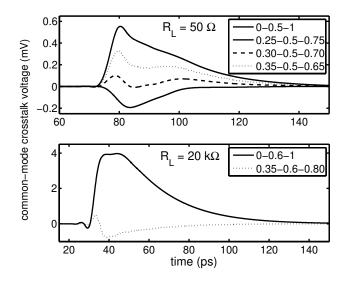

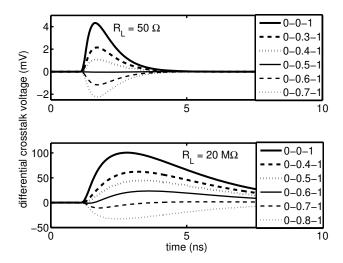

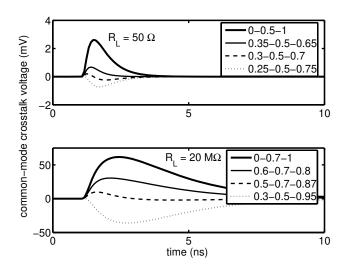

| 4.3.7 Lumped circuit simulation                 |    |

| 4.3.8 Parameter spread                          |    |

| 4.J.o fataticici Spicau                         | 93 |

| 4.4 Crosstalk from other metal layers             |  |

|---------------------------------------------------|--|

| 4.4.1 Introduction                                |  |

| 4.4.2 Perpendicular interconnects                 |  |

| 4.4.3 Full-swing interconnect running in parallel |  |

| 4.5 Summary                                       |  |

| 5 Circuit implementations                         |  |

| 5.1 Introduction                                  |  |

| 5.2 Interconnect design                           |  |

| 5.2.1 Introduction                                |  |

| 5.2.2 Technology                                  |  |

| 5.2.3 Optimal bandwidth per cross-sectional area  |  |

| 5.2.4 Interconnect parameters                     |  |

| 5.3 High speed transceiver                        |  |

| 5.3.1 Introduction                                |  |

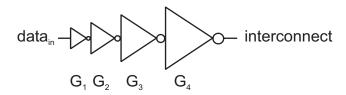

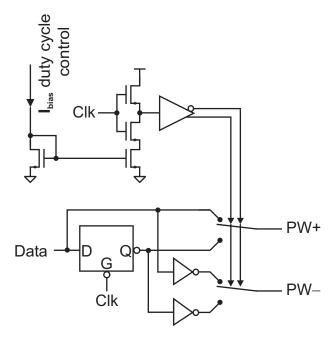

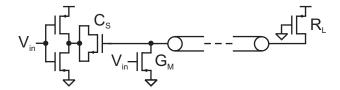

| 5.3.2 Transmitter circuits                        |  |

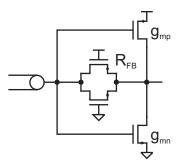

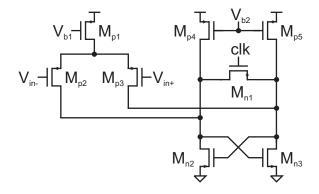

| 5.3.3 Receiver circuits                           |  |

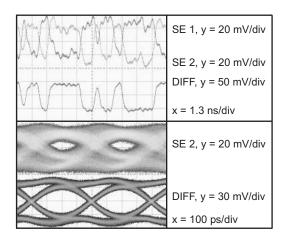

| 5.3.4 Measurement setup                           |  |

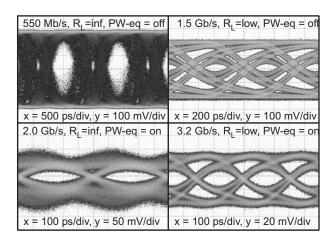

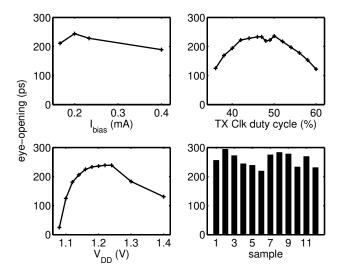

| 5.3.5 Measurement results                         |  |

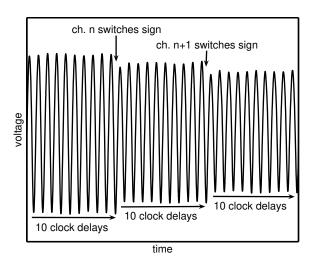

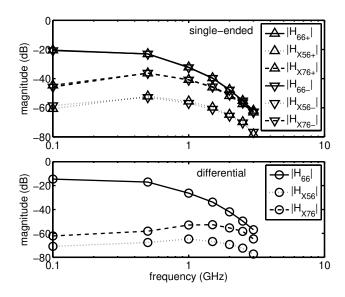

| 5.4 Crosstalk reduction with twists               |  |

| 5.4.1 Introduction                                |  |

| 5.4.2 Measurement setup                           |  |

| 5.4.3 Measurement results                         |  |

| 5.5 High speed and low power transceiver          |  |

| 5.5.1 Introduction                                |  |

| 5.5.2 Transmitter circuits                        |  |

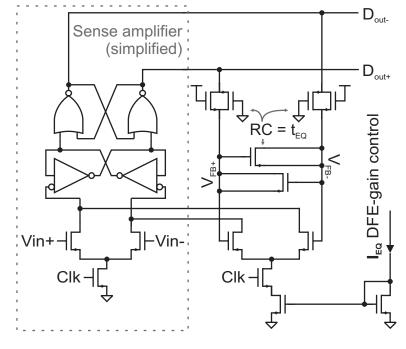

| 5.5.3 Receiver circuits                           |  |

| 5.5.4 Measurement setup.                          |  |

| 5.5.5 Measurement results                         |  |

| 5.6 Comparison                                    |  |

| 5.7 Summary                                       |  |

| 6 Conclusions                                     |  |

| 6.1 Central question                              |  |

| 6.2 Summary                                       |  |

| 6.3 Discussion                                    |  |

| 6.3.1 Presented solutions                         |  |

| 6.3.2 Future                                      |  |

| 6.3.3 Comparison                                  |  |

| References                                        |  |

| Samenvatting                                      |  |

| Publicaties                                       |  |

| Dankwoord                                         |  |

# **Chapter 1**

# Introduction

## 1.1 Communication over long distances

Communication is everywhere. People talk, write, use sms and msn, while animals warn each other for predators or try to attract a suitable partner. However, the success of communication can depend heavily on the distance between the communicators. As an illustration, imagine two people that are talking to each other. When close by, they are able to hear each other. However, if the distance between them increases, it will be harder for them to understand each other. At a certain distance they will have to shout and even further separated they cannot hear each other anymore. Then, other means are needed to talk with each other, for instance a telephone. The distance is simply too large for normal communication.

There is also communication between computers and many other electronic devices and also between different parts of an integrated circuit (IC or chip). And just as it was in the example above, also the communication on a chip becomes harder with increasing distance between the communicating parts. If two parts are close to each other, communication can take place over a short interconnect between them with voltage signals that are defined with respect to a common ground potential. However, the signals are attenuated and distorted by the interconnect and the longer the interconnect, the more attenuation and distortion is introduced. Therefore, if the two parts are placed further away from each other, they will need stronger drivers to overcome the attenuation and distortion. These stronger drivers can be compared with the shouting in the example above. For even longer interconnects, the

attenuation and distortion can be that large, that stronger drivers are not sufficient anymore for reliable communication and more elaborate techniques are necessary.

However, the attenuation and distortion do not only depend on the length of the interconnect, but also on the communication speed: the smaller the period of the transmitted symbol, the higher the attenuation and distortion will be. Thus, if an interconnect is called long, it is long relatively to the required speed.

The required speed depends of course on the application. But in general, the circuits in newer IC technologies become faster. Therefore, also the interconnects should become faster. However, we will see that there are certain interconnects that do not become faster for newer technologies. Although the actual length of these interconnects remains equal, compared to the increasing speed of the circuits their relative length becomes too large. These are the interconnects we will look at in this thesis.

# 1.2 Interconnects in CMOS technologies

There are many different technologies in which chips can be made. In this thesis, we restrict ourselves to CMOS (complementary metal oxide semiconductor) technologies. CMOS technologies are the most important technologies for very large scale integrated (VLSI) applications such as computers, digital signal processing, telecommunication, medical image processing, cryptography and digital control systems.

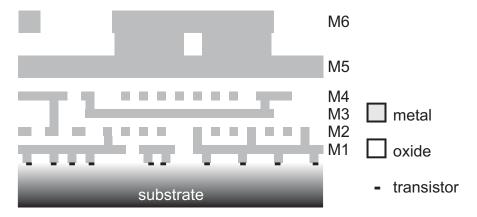

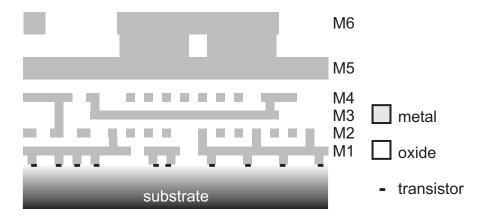

In a CMOS technology, transistors are fabricated in a doped silicon substrate, usually with a gate of polysilicon on top of a thin layer of oxide. In order to interconnect transistors, a stack of metal layers is available to the designer. An example is shown in figure 1.1.

Figure 1.1: Example of the stack of metal layers in a CMOS chip

The figure shows part of the substrate with a number of metal layers on top of it, in this case six. Transistors are located at the top of the substrate. Through vias, it is possible to make connections with the metal layers. The space in between metal is filled with silicon

oxide or some other dielectric material. The permittivity of this material can differ for different metal layers. A passivation layer is usually on top of the metal stack.

In general, the highest metal layers are thicker than the lower metal layers. Often, the thick top metal layers are reserved for the power grid and clock routing. Interconnects between transistors, gates or logic blocks can then be made with the help of the other metal layers.

## 1.3 Interconnects and technology scaling

For over 30 years, the feature size of CMOS technology has shrunk to dimensions into the nanometer region nowadays. As a result of this continuous scaling, higher circuit speeds, lower power and larger packing densities of transistors are achieved.

The scaling of technology also affects interconnects. Both the thickness of the metal layers itself and the thickness of the oxide between the metal layers decrease with scaling. Also, the minimum width of an interconnect and the minimum spacing between two interconnects decrease.

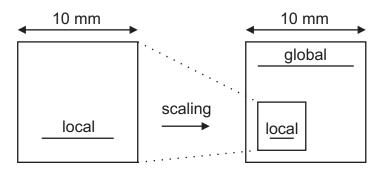

When looking at the scaling of on-chip interconnects, it is important to distinguish between local and global interconnects [1]. The concept is shown in figure 1.2.

Figure 1.2: Interconnects and scaling: local and global interconnects [1].

Under scaling, a circuit with the same functionality will be smaller in a new technology. The interconnects of this circuit will also become shorter and these scaled interconnects are called local interconnects. However, as more functionality is packed on a chip, the total size of the chip remains roughly the same under scaling. Next to local interconnects, there will also be interconnects that span the entire chip. These interconnects do not scale in length and are called global interconnects.

In this thesis, we will mainly look at these global interconnects. In the next section, we will compare the speed of these global interconnects with the speed of circuits as a function of technology scaling.

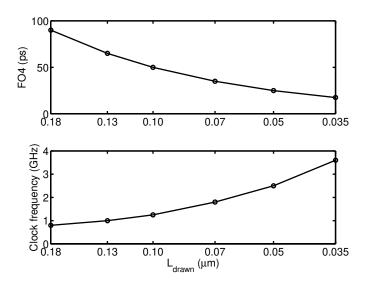

## 1.4 Delay of global interconnects

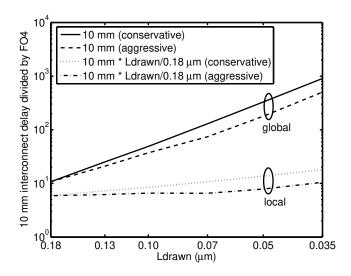

In [1], the speed of circuits is measured as the delay through an inverter driving four identical copies of itself. This delay is called a "fanout-of-four inverter delay" or simply an FO4. The FO4 scales with technology, as shown in figure 1.3. The predicted FO4 and clock frequency  $(1/(16 \cdot FO4))$  in [1] are plotted against the drawn gate length  $(L_{drawn})$ , showing the increased speed of circuits for CMOS processes with decreasing gate lengths.

Figure 1.3: FO4 delay and clock frequency as a function of technology (drawn gate length) [1].

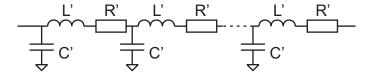

In order to also find the speed of the interconnects for these technology nodes, we model the interconnect with an infinite number of R'L'C'-sections:

Figure 1.4: Distributed RLC model of an on-chip interconnect.

R' is the distributed resistance per unit length  $(\Omega/m)$ , L' the distributed inductance per unit length (H/m) and C' the distributed capacitance (F/m) per unit length. A more detailed description on interconnect modeling is given in chapter 2.

Table 1 gives some typical values for a practical interconnect and compares it with other types of wires [2].

|          | wire cross-<br>section (m <sup>2</sup> ) | R' (Ω/m) | L' (nH/m) | C' (pF/m) |

|----------|------------------------------------------|----------|-----------|-----------|

| on-chip  | 0.5μ·0.5 μ                               | 150k     | 600       | 200       |

| PC board | 150μ·50μ                                 | 5        | 300       | 100       |

| twisted  | ~500µ                                    | 0.08     | 400       | 40        |

| pair     | diameter                                 |          |           |           |

Table 1.1: Typical values of R', L' and C' comparing a typical on-chip interconnect with board and twisted pair wires.

The table shows that although the distributed inductance and capacitance are of the same order of magnitude for all types of wires, the distributed resistance for on-chip interconnects is much larger. Because of this very large resistance, the distributed inductance can often be neglected for global on-chip interconnects. A metric for the delay of an interconnect then is [1]

$$t_D = FO4 + \frac{1}{2} \cdot R' \cdot C' \cdot l^2 \tag{1.1}$$

*l* is the length of the interconnect. The equation shows that the delay of an interconnect is proportional to the length squared. The delay is further determined by the distributed resistance and capacitance of the interconnect. (The FO4 comes from an inverter that drives the interconnect).

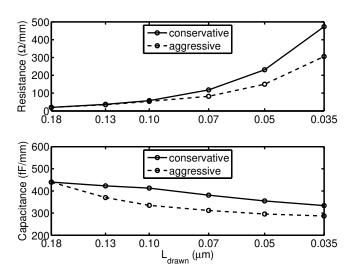

Both the distributed resistance and capacitance are plotted in figure 1.5 for a conservative and an aggressive prediction, depending on whether or not technological limitations are considered [1]. The values are for global interconnects with a pitch of  $8 \cdot L_{drawn}$  [1]. The figure shows that as technology scales, the resistance increases dramatically, while the capacitance only decreases very slowly. Based on (1.1), the delay of interconnects increases tremendously. Note that technology solutions, such as low-k dielectrics and copper interconnects are already incorporated in the predictions.

Figure 1.6 shows the delay of a 10 mm long global interconnect relative to an FO4 delay as a function of technology. The large increase over six technology nodes shows that global interconnects cannot keep up with the ever increasing speed of digital gates. Local interconnects can keep up, because their length is scaled and interconnect delay is proportional to the length squared (see (1.1)). For comparison, figure 1.6 also shows the delay of an interconnect with a length that is scaled with Ldrawn.

# 1.5 Global interconnect problems

#### 1.5.1 Introduction

The previous section showed that the distributed resistance of global interconnects increases dramatically for newer CMOS processes. As a consequence, the speed of global interconnects (measured as delay) decreases with respect to the faster digital gates. In this

Figure 1.5: Resistance and capacitance of global interconnects as a function of technology [1].

Figure 1.6: Global and local interconnect delay relative to an FO4 delay as a function of technology [1].

section, we will introduce global interconnects with respect to the achievable data rate and also to data integrity issues, area consumption and power consumption. But first, we will give a model for the transmitter and the receiver.

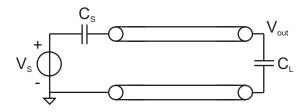

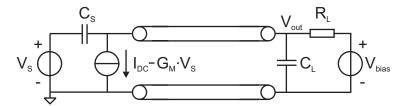

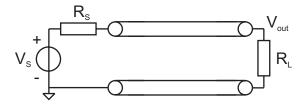

#### 1.5.2 Transmitter and receiver model

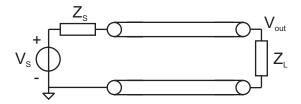

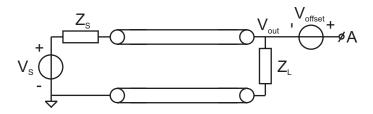

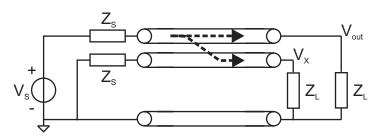

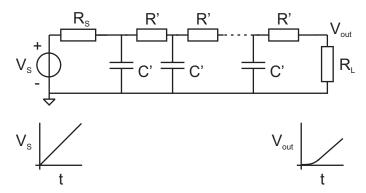

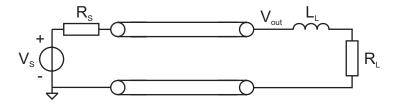

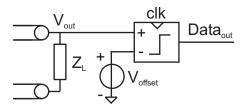

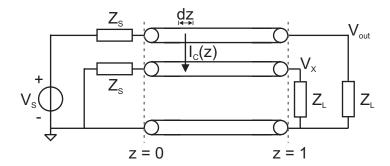

In figure 1.7, a model is given for the transmitter and receiver of an interconnect.

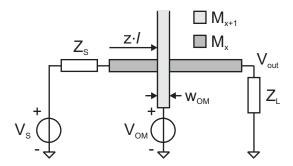

Figure 1.7: Model for global interconnects.

The voltage source, with voltage  $V_S$  and source impedance  $Z_S$ , models the transmitter. The load impedance  $Z_L$  models the receiver and  $V_{out}$  is the voltage at the receiver end of the interconnect. The symbol between  $Z_S$  and  $Z_L$  is the symbol that is used for an interconnect in this thesis.

In this thesis, we will make use of an example interconnect to illustrate the developed concepts. We will use the parameters of an 10 mm long interconnect in a 0.13  $\mu$ m CMOS process with a width and spacing of both 0.4  $\mu$ m. For this interconnect R' = 150 k $\Omega$ /m, L' = 400 nH/m and C' = 220 pF/m. If not stated otherwise, we will assume  $Z_S$  to be a resistance of 100  $\Omega$  and  $Z_L$  a capacitance of 100 fF. These impedances model inverters, which are conventionally used as both the transmitter and receiver

#### 1.5.3 Achievable data rate

The achievable data rate is defined as the maximum number of bits that can be transmitted over the interconnect in a certain time period. In this section we will see how the large resistance and capacitance of interconnects in newer CMOS processes limit the achievable data rate.

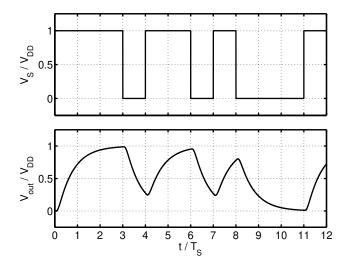

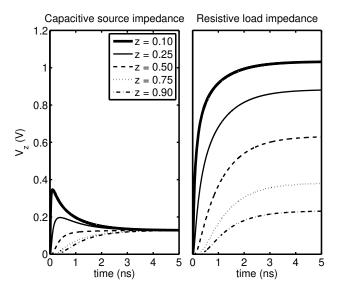

The voltage source of figure 1.7 transmits symbols on the interconnect. In figure 1.8, this is shown for plain binary signaling. The duration of one symbol is  $T_S$  seconds. The voltage at the receiver ( $V_{out}$ ) is also plotted in figure 1.8. The limited bandwidth of the interconnect is clearly seen in the slow rise and fall edges of this signal.

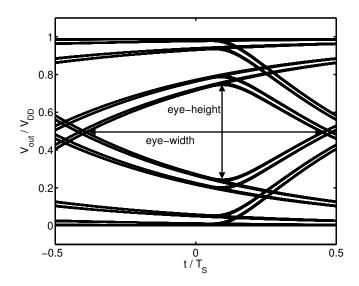

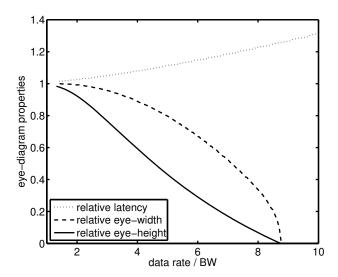

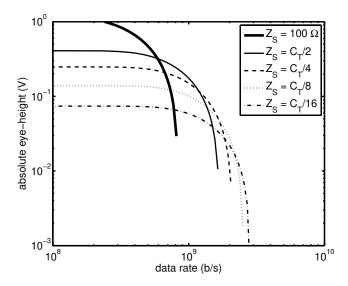

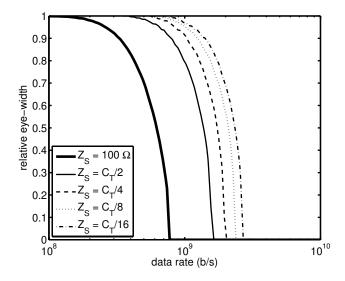

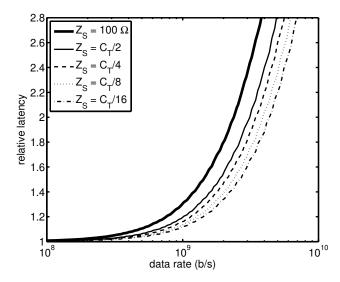

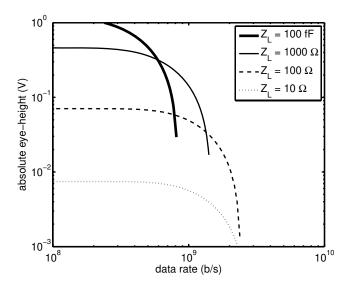

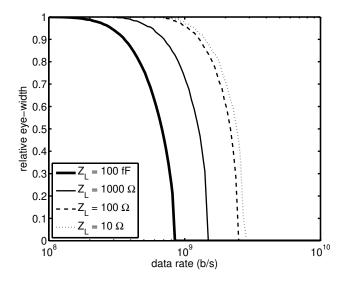

The performance of the interconnect is analyzed with the help of an eye-diagram. For this, the output signal is cut into pieces with a width of  $T_S$  and these pieces are all plotted on top of each other. Figure 1.9 shows the eye-diagram of  $V_{\text{out}}$ , using random data. The eye should be sufficiently open for reliable communication. The eye-opening is determined by an eye-height and an eye-width. Both eye-height and eye-width depend on the data rate. For determining the achievable data rate, we will calculate these eye-diagram properties as a function of data rate and see at which data rate the eye is closed. In order to do that, we will first calculate the transfer function from  $V_S$  to  $V_{\text{out}}$ . From this transfer function the impulse response is calculated. The convolution of this impulse response with the transmitted symbol shape gives the symbol response, from which it is possible to calculate the eye-diagram properties.

Figure 1.8: Input and output signals of 10 mm global interconnect.

Figure 1.9: Eye-diagram of Vout.

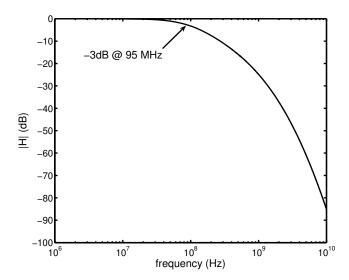

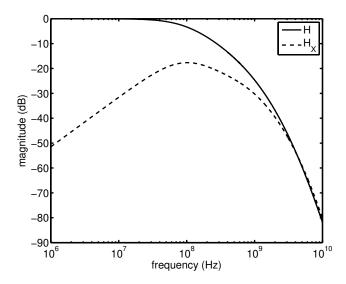

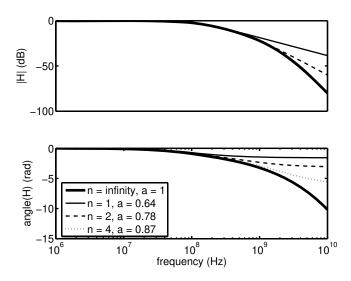

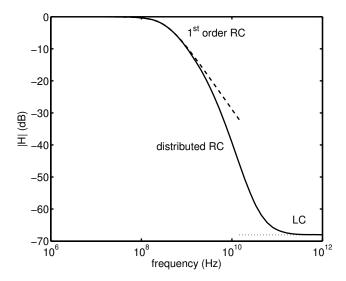

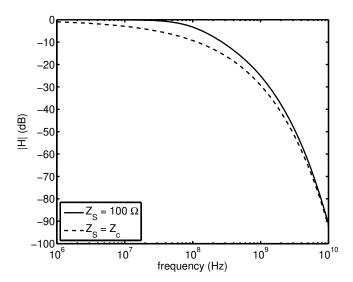

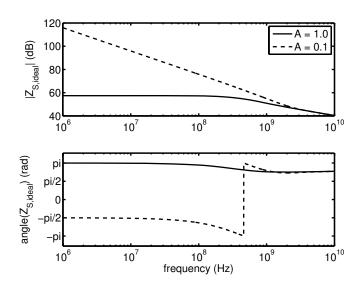

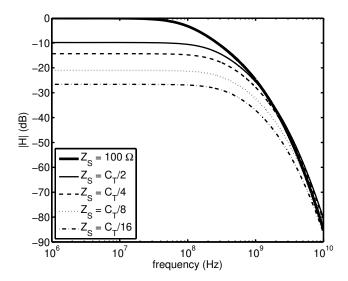

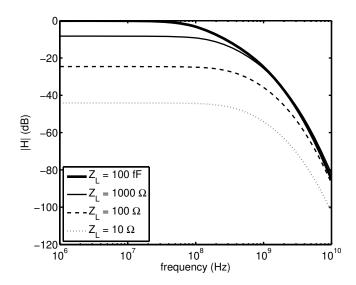

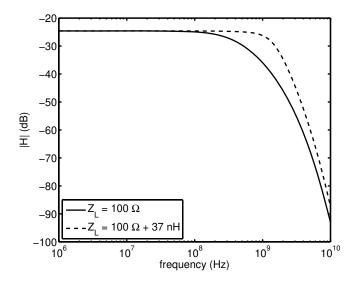

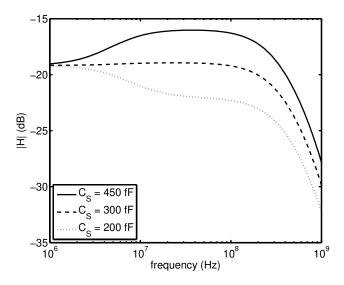

The transfer function  $H = V_{out}/V_S$  depends on both the interconnect parameters R', L' and C' (see figure 1.4) and on the termination impedances  $Z_S$  and  $Z_L$  (see figure 1.7). For the example interconnect from section 1.5.2 the transfer function is plotted in figure 1.10. Details on how to calculate this transfer function can be found in the next chapter.

Figure 1.10: Transfer function of a 10 mm global interconnect (see section 1.5.2 for parameters).

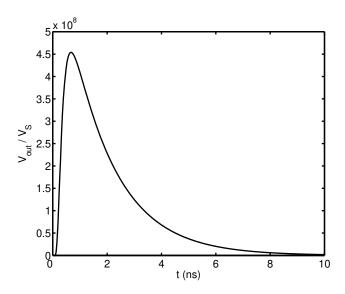

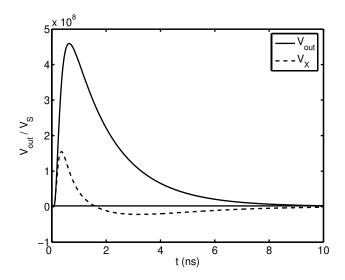

The transfer function shows that higher frequencies are more heavily attenuated. The high distributed resistance and capacitance give a -3dB bandwidth of only 95 MHz in this example. The limited bandwidth shows up as a long tail in the time domain. Figure 1.11 depicts the impulse response corresponding to the transfer function of figure 1.10.

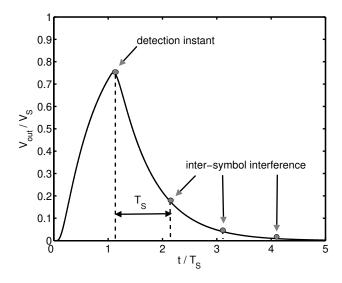

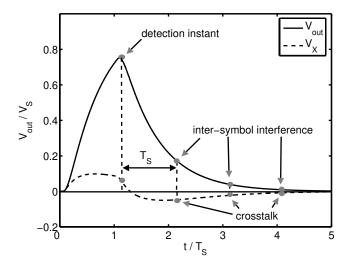

The symbol response can be found by convolving the impulse response with the transmitted symbol shape. For plain binary signaling, the symbol response is shown in figure 1.12 ( $T_S = 2.5 \text{ ns}$ ). The long tail of the impulse response is also present in the symbol response. This long tail causes inter-symbol interference (ISI) between consecutive symbols, reducing the eye-opening.

Detection of a symbol takes place at a certain detection instant. A symbol time  $(T_S)$  later, the next symbol is detected. However, at this moment there is still signal left from the previous symbol, called inter-symbol interference. The maximum ISI is the summation of the absolute value of all ISI points. By subtracting this maximum ISI from the signal value at the detection instant, the worst-case eye-height at that detection instant is found. By calculating this eye-height for different detection instants, the optimum detection instant can be found where the eye-height is maximum. Also, the eye-width can be calculated as the time between the two detection instants where the eye-height is zero. The latency is equal to the optimum detection instant, as the symbol is transmitted at time is zero.

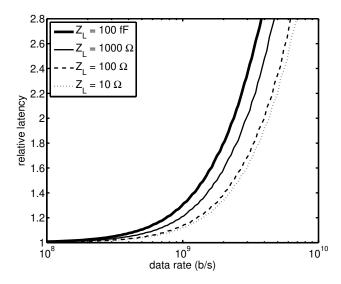

Figure 1.13 depicts the eye-diagram properties for different data rates. The data rate on the x-axis is normalized to the bandwidth (95 MHz for the example interconnect from section 1.5.2).

Figure 1.11: Impulse response of a 10 mm global interconnect (see section 1.5.2 for parameters).

Figure 1.12: Symbol response with inter-symbol interference points.

Figure 1.13: Eye-diagram properties as a function of data rate (b/s) divided by the -3 dB bandwidth (Hz) of the interconnect.

The figure shows that the eye-height, relative to  $V_s$ , decreases for higher data rates. Also the eye-width, relative to the symbol time, decreases for higher date rates. The latency, relative to the symbol time, increases. The eye-opening that is needed depends on the input swing that is required by the receiver and on error sources like offset and crosstalk. These noise sources will be treated in the next section.

In summary, the small bandwidth of global on-chip interconnects, caused by a high distributed resistance and distributed capacitance, limits the achievable data rate.

### 1.5.4 Data integrity

In the previous section, we have introduced the achievable data rate and have seen that it is limited by inter-symbol interference. In this section, we will look briefly at offset, crosstalk and noise sources like supply and substrate noise, which all degrade data integrity and further reduce the achievable data rate.

Offset results from mismatches in the circuits. We will represent all offsets by a single voltage source, as shown in figure 1.14, assuming that a circuit connected to point A has a high-ohmic input impedance. The eye-opening at the output of the interconnect should be large enough to tolerate this offset.

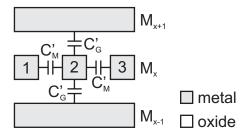

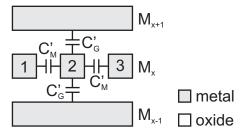

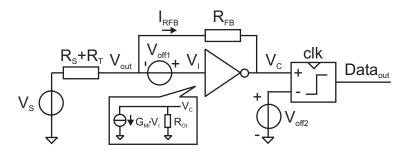

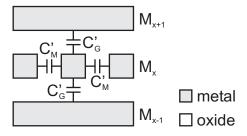

Another phenomenon that can degrade data integrity is crosstalk. A signal that is transmitted on an interconnect is not only seen at its own receiver, but also at the receiver of neighboring interconnects. The most important crosstalk mechanism is via the capacitance between two interconnects [3]. Figure 1.15 shows the capacitances of an interconnect.

Figure 1.14: Offset is represented in a single voltage source.

Figure 1.15: Capacitances to ground  $(C_G)$  and neighboring interconnects  $(C_M)$ .

Assuming all metal except the middle interconnect (2) to be grounded, the earlier defined capacitance C' in figure 1.4 is equal to  $2C_G'+2C_M'$ .

$C_M$ ' is the capacitance between two interconnects and is mainly responsible for the crosstalk between them. Assuming now that the left interconnect (1) is also terminated with  $Z_S$  and  $Z_L$ , we can define a crosstalk voltage  $V_X$  at the end of this interconnect, as shown in figure 1.16.

Figure 1.16: Definition of crosstalk voltage V<sub>X</sub>.

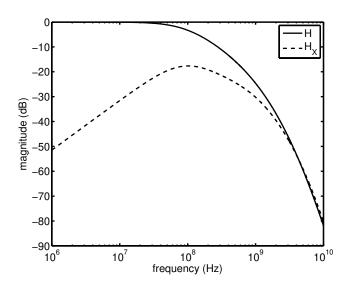

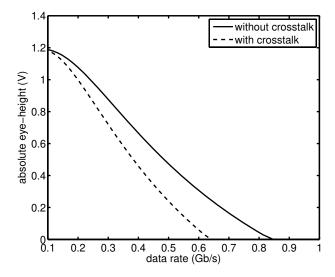

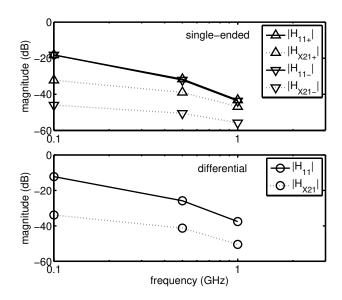

The transfer functions  $H = V_{out}/V_S$  and  $H_X = V_X/V_S$  are plotted in figure 1.17. The parameters of the example interconnect from section 1.5.2 are used again with  $C_M$ ' = 50 fF/mm.

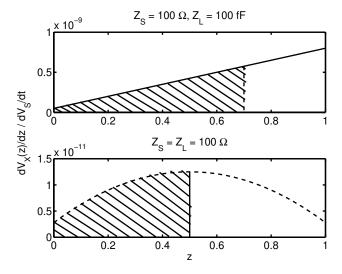

Not only the limited bandwidth of H, but also the crosstalk will limit the achievable data rate. As was done in the previous section, we will look at the impulse and symbol responses. The impulse responses are in figure 1.18. Both  $V_{out}$  and  $V_X$  have a long tail. These long tails are also present in the symbol responses, which are shown in figure 1.19 for  $T_S = 2.5$  ns.

Figure 1.17: Transfer function and crosstalk transfer function (see section 1.5.2 for parameters).

Figure 1.18: Impulse responses (see section 1.5.2 for parameters).

Figure 1.19: Symbol responses.

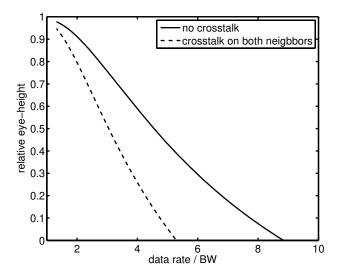

As explained in the previous section, the eye-height is calculated as the signal value at the detection instant minus all ISI points. However, the eye-height is even further reduced by the crosstalk. For calculating the worst-case eye-height, now both the absolute value of the ISI points and the absolute value of all crosstalk points (including the one at the detection instant) should be subtracted from the value at the detection instant. Therefore, the eye-diagram properties change with respect to the case when there is no crosstalk. Figure 1.20 shows the relative eye-height as a function of data rate with no crosstalk and with worst-case crosstalk on two neighboring interconnects. It is clear from the figure that the eye-height has decreased because of the crosstalk. Therefore, with crosstalk lower data rates are achievable.

There are still other noise sources besides neighbor-to-neighbor crosstalk like crosstalk from other metal layers, supply and substrate noise. Just as the eye-opening should be large enough to allow for offset, a noise margin is needed for these noise sources. However, by using differential interconnects (see chapter 4), most of these noise sources become common-mode and can be rejected by a well-designed receiver.

### 1.5.5 Chip area

We do not only want to have a high achievable data rate for our interconnects, but we also want to consume as less chip area as possible. In general, the area occupied by a global interconnect is much larger than the area occupied by its transmitter en receiver. For instance, the global interconnects that are discussed in this thesis (in 0.13  $\mu m$  CMOS and 90 nm CMOS) have a total area of about  $10^4~\mu m^2$ , while the transceivers only occupy an area in the order of  $10^2~\mu m^2$ . Therefore, for minimal area, the dimensions of the interconnect must be optimized. Small interconnects might seem optimal, but they have a limited bandwidth. Very wide interconnects offer a high bandwidth, but also occupy large area.

Figure 1.20: Eye-height with and without crosstalk.

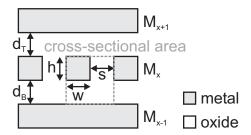

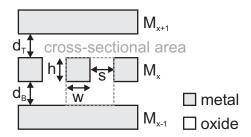

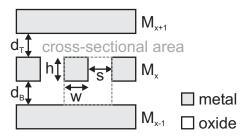

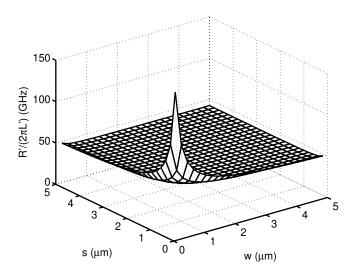

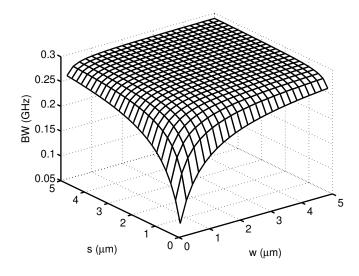

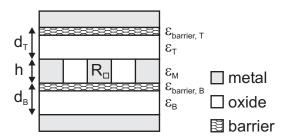

In figure 1.21, three metal layers are drawn:  $M_{x-1}$ ,  $M_x$  and  $M_{x+1}$ . The top and bottom metal layer are filled with metal and the global interconnects are placed in the middle metal layer. The height h and oxide thicknesses  $d_T$  and  $d_B$  are in general fixed by the process and often

Figure 1.21: Interconnect dimensions.

$d_T \approx d_B \approx d$ . A designer can only choose the width w of the interconnect and the spacing s between interconnects. We define the cross-sectional area as

$$area = (w+s) \cdot (h+d) \tag{1.2}$$

In this thesis, we will use optimal dimensions of the interconnect for which the bandwidth per cross-sectional area is largest. A bus with these optimized interconnects will have the highest aggregate data rate for a certain bus area.

### 1.5.6 Power consumption

Next to the desire to minimize chip area, also power consumption needs to be minimized. A simple model of power consumption is given by the following equation [4].

$$P_{dyn} = \frac{1}{2} \cdot p_{trans} \cdot C \cdot l \cdot V_{swing} \cdot V_{DD} \cdot f_{clock}$$

(1.3)

With  $P_{dyn}$  the dynamic power consumption,  $p_{trans}$  the transition probability, C' the distributed capacitance, l the length of the interconnect,  $V_{swing}$  the voltage swing on the interconnect,  $V_{DD}$  the supply voltage and  $f_{clock}$  the clock frequency. The transition probability is the probability that a transition from high to low or from low to high is made. For random data, this number is 0.5. In this thesis, we will also use the term data activity, which is equal to the transition probability.

Next to this dynamic power consumption, there will in many cases also be static power consumption (P<sub>static</sub>). For low data activities, there is not much dynamic power. In these cases, the total power is dominated by the static power. Therefore, both dynamic and static power consumption should be low.

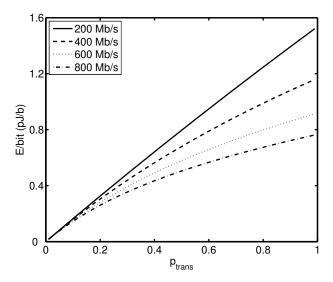

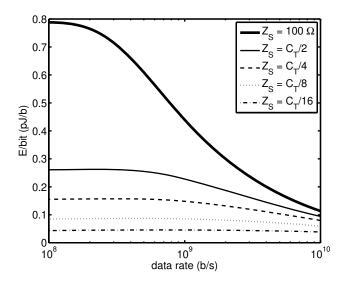

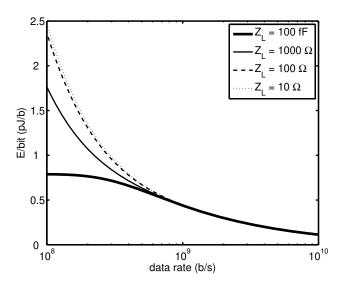

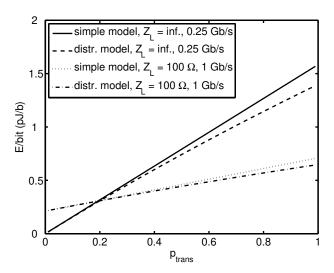

Instead of looking just at the power consumption, we will look at the power consumption divided by the data rate, as we want to minimize power consumption at maximum data rate. This energy per bit (E/bit) can be plotted against  $p_{trans}$ , as shown in figure 1.22 for the example interconnect from section 1.5.2.

The more transitions, the more E/bit is dissipated. The overall E/bit should be as low as possible. Furthermore, it is desirable to have low 'static' energy consumption at zero data activity.

Figure 1.22: Example of an energy per bit curve as a function of transition probability.

### 1.6 Solutions in literature

#### 1.6.1 Introduction

In the previous sections, we saw that global interconnects have a number of problems. First we saw that for newer technologies the delay of interconnects increases tremendously with respect to the delay of a circuit, due to an increasing distributed resistance. The high resistance and capacitance of interconnects in newer CMOS processes also limit the achievable data rate. We mentioned that offsets, supply noise and crosstalk can further limit the achievable data rate. Finally, we discussed area and power consumption, which should both be low.

In literature, a number of solutions are given to decrease the delay or increase the achievable data rate. Also solutions to lower the power consumption and decrease the influence of offset, supply noise and crosstalk can be found in literature, as summarized below

### 1.6.2 **Delay**

The delay of global interconnects can be reduced by making the delay linear, instead of quadratic (see (1.1)), with length. This can be done by breaking up the interconnect into smaller segments, with a repeater, often implemented as an inverter, driving each segment. All segments have the same delay, as they are of equal length. Thus, a two times longer interconnect, having twice as much segments, will also have a two times larger delay.

By breaking up the interconnect into N segments, the delay would in principle be N times smaller. However, the repeaters add additional delay and a delay-optimal solution exists where both the segment length and driver strength can be calculated [5]. Unfortunately, the use of repeaters has some disadvantages. With plain non-clocked buffers as repeaters, delay variations due to crosstalk and due to process variations accumulate and limit the achievable data rate [6]. Furthermore, the number of repeaters needed in microprocessors in future technologies will increase tremendously [7]. Next to the (large) occupied area and placing problems, the power that is dissipated in these repeaters can become a large portion of the total power dissipation of the chip [8].

Another approach is to use 'smart' repeaters, where fewer repeaters are needed for the same total delay. Transition aware circuits, for example, detect a transition in an early phase. This can then be used to generate an output signal earlier [9] or accelerate or boost the signals on the interconnect [10, 11]. However, this will make the transceiver more susceptible to noise. Other 'smart' repeaters use current-mode sensing [6, 12-15] to decrease the delay of the interconnect up to a factor three compared to the conventional voltage mode sensing. However, this often comes at the cost of high static power consumption.

Also, the interconnect can be designed in such a way that is has transmission line behavior [16-24]. Instead of using interconnects at minimum pitch, extreme wide interconnects are used. In this way, the resistance becomes small and the interconnect is dominated by its inductance and capacitance. Near speed of light delays are possible, but at the cost of large interconnect area.

In summary, techniques to reduce delay exist, but come at the cost of data integrity, power or area.

#### 1.6.3 Achievable data rate

The achievable data rate is limited because of the limited bandwidth of the interconnect. The bandwidth of the interconnect can be improved with an equalizer. An ideal equalizer has a transfer function such that  $H_{interconnect} \cdot H_{equalizer} = 1$ . In practice, this can be achieved only for a limited frequency band, but still, the bandwidth can be increased a lot.

In [25] switches are placed along the interconnect, that discharge the interconnect every clock period. However, this increases the already troublesome clock load and can cost considerable power consumption.

Equalization is also implemented in [13, 14, 26], referred to as dynamic overdriving or preemphasis equalization. The voltage swing on the interconnect is reduced, but at data transitions a temporarily higher voltage swing is transmitted. In this way, the data transitions are emphasized. However, a transmitter that is able to transmit both a high voltage and a low voltage in an efficient way is difficult to design. Furthermore, the low swing will make the transceiver more sensitive to noise sources.

Distributed loss compensation [27] uses negative capacitances that are placed along the interconnect, but has high static power consumption due to the bias current of the negative capacitances.

As was the case for delay, the achievable data rate can be improved, but again at the cost of data integrity, power or area.

## 1.6.4 Power consumption

For the standard repeater solution, a power reduction can be achieved by not optimizing for delay but for power. For a given delay penalty of 5%, a power reduction of 27% (180 nm technology node) up to 45% (50 nm technology node) can be achieved compared to the delay optimal solution [28].

Another way to decrease power consumption is the use of low-swing signaling [20, 25, 26, 29, 30]. Because of the low swing, the capacitance of the interconnect is not fully charged anymore. However, the lower swing makes the transceiver more susceptible to noise sources. Furthermore, methods to create low-swing signaling often use threshold voltage drops, which decrease the bandwidth and thus, the achievable data rate. Otherwise, separate low-voltage supplies are used, which is also not desirable.

Power can also be reduced by coding [31]. The coding targets to have as few data transitions as possible. However, coding schemes have often only limited power reduction for practical data activities.

### 1.6.5 Data integrity

Techniques like shielding can provide a solution for crosstalk problems. However, if low-swing signaling is used to reduce power consumption, noise margins become smaller [29].

Then, differential signaling is preferred. In differential systems, most noise sources appear as common-mode and can be rejected by the receiver. In this way, differential interconnects are for instance not sensitive to crosstalk from orthogonal crossing metal layers. However, differential interconnects do not solve the problem of neighbor-to-neighbor crosstalk.

In CMOS memory cells, twists in differential interconnect-pairs are already widely used to cancel crosstalk between bitlines [32-35]. Twists are also used on printed circuit boards [36, 37]. In general, many twists are placed at evenly-spaced intervals along the interconnects. To cancel neighbor-to-neighbor crosstalk, twists are also proposed for on-chip global interconnects [25, 38-41]. Again, many twists are placed at evenly-spaced intervals along the interconnects. However, the many vias needed to make the twists add to the already troublesome interconnect resistance. Moreover, each twist requires use of a second metal layer, which complicates global routing algorithms.

## 1.7 Challenges

From the solutions as found in literature, we can draw the conclusion that it is difficult to have a solution that does not only have a low delay or a high achievable data rate, but also low power and area consumption. Furthermore, low-swing techniques for low power consumption make data integrity issues more difficult.

In this thesis, the focus will be more on achievable data rate than on delay, because designers can get around the large delay of global interconnects by using pipelining. Moreover, solutions that increase the achievable data rate, often also decrease the delay.

While maximizing the achievable data rate, it is desirable to minimize chip area and power consumption. Also data integrity should be maintained. Crosstalk between interconnects, supply noise and substrate noise can degrade this data integrity and the interconnect should be robust against these noise sources. These issues are summarized in the central question of this thesis:

How can we design global interconnects and transmitter and receiver electronics in future IC technologies to

- maximize data capacity,

- minimize chip area consumption,

- minimize power consumption while

- maintaining data integrity?

The research that led to this thesis has been done in cooperation with Daniël Schinkel. His research includes topics like communication and equalization techniques both at the transmitter and the receiver and clocked sense amplifiers that are used to make a decision at the receiver [42]. The focus of this thesis will be on the modeling and design of the interconnect itself and the interactions of the interconnect with the transmitter and the receiver.

## 1.8 Scope of this thesis

The remainder of this thesis is organized as follows.

Chapter 2 describes the interconnect models that are used. From Maxwell's equations we find the response of interconnects to electromagnetic waves. This response results in a distributed model, described by s-parameters. With this distributed model transfer functions and power consumption can be calculated.

The design of the interconnects is discussed in chapter 3. First, the optimal dimensions of the interconnects are determined. Then, termination concepts are developed, both at the transmitter and the receiver side. These termination concepts are developed to increase the achievable data rate, while minimizing area and power. Other techniques for increasing the achievable data rate, resulting from the work of Daniël Schinkel [42], are briefly explained at the end of the chapter.

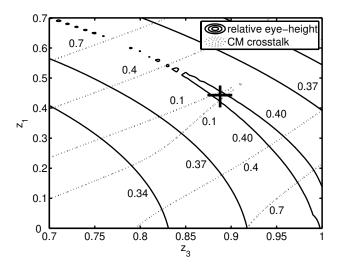

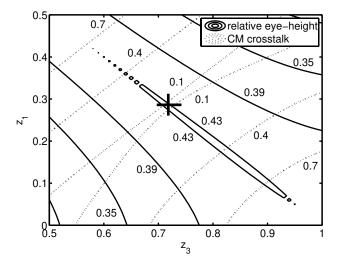

In chapter 4 the data integrity of on-chip transceivers is examined. First, offset mechanisms in the receiver are studied. After that, the interconnects are designed for minimal crosstalk. For neighbor-to-neighbor crosstalk, twists are used. The chapter describes how to calculate the optimal position of these twists, depending on the termination impedances that are used. The last section calculates the amount of crosstalk from aggressor interconnects that are not in the same, but in another metal layer than the victim interconnect.

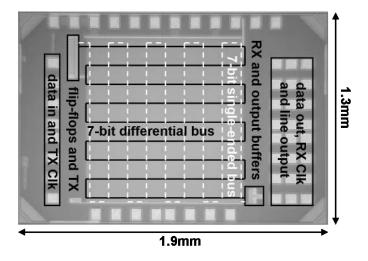

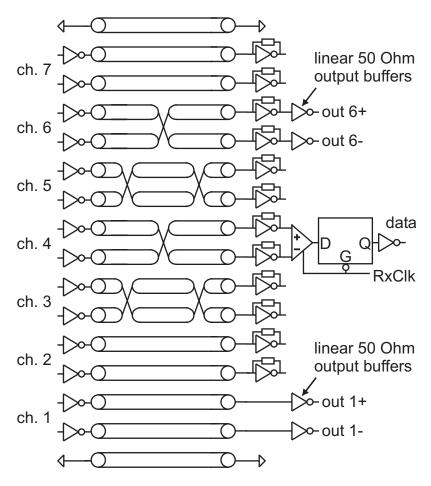

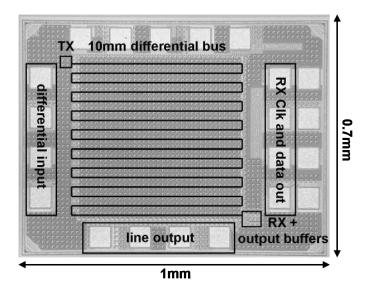

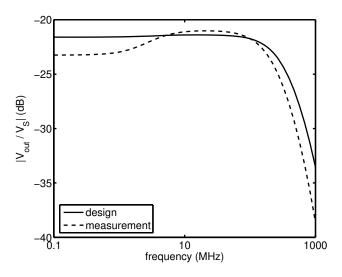

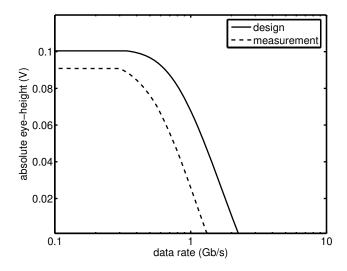

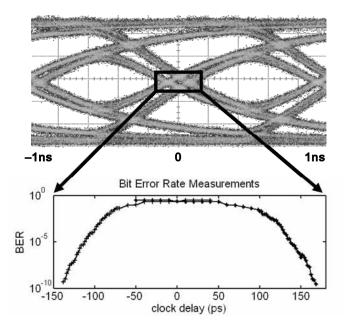

Chapter 5 describes the implementation of the concepts, as developed in chapters 3 and 4. First, optimal interconnect dimensions are calculated for two different CMOS technologies. Then, two transceiver concepts are discussed that are designed in these technologies. The first transceiver achieves a high data rate and the second transceiver achieves both a data rate and low power consumption.

The conclusions of this thesis are found in chapter 6. Key answers to the central question of this thesis are given and the proposed transceivers of chapter 5 are evaluated.

# **Chapter 2**

# Interconnect models

#### 2.1 Introduction

This chapter deals with the modeling of on-chip interconnects. The models that are treated in this chapter are used in the subsequent chapters for designing global interconnects and developing termination concepts. This chapter starts with a review of the location of interconnects in an integrated circuit in section 2.2. Section 2.3 discusses the response of interconnects to electromagnetic waves in terms of voltages and currents. This response results in a distributed model that is presented in section 2.4. In this section, it is shown how to calculate transfer functions and power consumption with the help of this distributed model. Section 2.5 expands the distributed model by introducing neighboring interconnects. In that section, the crosstalk transfer function is calculated. The relation between the distributed model and a lumped model is treated in section 2.6. Finally, in section 2.7 it is explained how we can find the parameters of the used models with the help of a 3D EM-field simulator [43].

## 2.2 Location of interconnects in an IC

In CMOS technology, transistors are fabricated in a doped silicon substrate usually with a gate of polysilicon on top of a thin layer of oxide. In order to interconnect transistors, a stack of metal layers is available to the designer. An example is shown in figure 2.1. The figure shows the cross-section of a chip with part of the substrate and six metal layers on top of it. Transistors are located at the top of the substrate and through vias, it is possible

Figure 2.1: Example of the stack of metal layers in a CMOS chip.

to make connections with the metal layers. The space that is not filled with metal is filled with silicon oxide or another dielectric (preferably with a low dielectric constant). In general, the highest metal layers are thicker than the lower metal layers.

The best place for global interconnects would be in one of these thick top metal layers, as the distributed resistance of the interconnect is inversely proportional to its cross-section (as will be shown in (2.37)). In this thesis, however, we will locate them in one of the thinner metal layers. There are two reasons for this. The first is that the top metal layers are often reserved for the power and clock grid. The second reason has to do with the goal of our research. In future CMOS technologies, the high resistance and capacitance will provide a severely limited bandwidth (see chapter 1). Therefore, we would like to look at interconnects that have a limited bandwidth and it makes therefore sense to use the thinner metal layers.

Figure 2.2 shows a schematic view and defines the dimensions of an interconnect.

Figure 2.2: Interconnect dimensions.

We assume that a bus with global interconnects is placed in metal layer x, while metal layer x-1 and x+1 are filled with metal, to emulate high-density metal use.

## 2.3 Response to electromagnetic waves

#### 2.3.1 Introduction

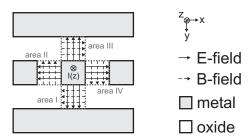

Suppose that one of the interconnects in metal layer x has a potential V(z) at a certain position z along the interconnect. If all other metal is connected to ground, the voltage difference between the interconnect and the other metal parts gives rise to an electric field density E. Suppose also a current I(z) that flows through the interconnect. This current then induces a magnetic flux density B. As both the E-field and the B-field have a direction, we will write them in bold case to denote that they are vectors. Figure 2.3 shows the direction of E and B.

Figure 2.3: Direction of **E** and **B**.

For simplicity, we neglect fringe fields and suppose all fields to be concentrated in the areas I to IV. Due to the limited conductivity of the interconnect, there will also be an E-field inside the interconnect, which has the same direction as the current. For our analysis, we assume the E-field to be much smaller in the z-direction than in the x- and y-direction. This assumption can be made, since for the interconnects we will look at, the length (z-direction) is much larger than the spacing to other interconnects (x-direction) and than the oxide thickness (y-direction).

In this section, we calculate the voltage change in the z-direction (dV(z)/dz) as a function of I(z). We also calculate the current change in the z-direction (dI(z)/dz) as a function of V(z). With the help of these relations, we are able to construct a distributed model in the next section.

#### 2.3.2 Definitions

First, some quantities are defined.

V: electric potential

The gradient of scalar V is defined as

$$\nabla V = \mathbf{a}_x \frac{\partial V}{\partial x} + \mathbf{a}_y \frac{\partial V}{\partial y} + \mathbf{a}_z \frac{\partial V}{\partial z}$$

(2.1)

with  $\mathbf{a}_x$ ,  $\mathbf{a}_y$  and  $\mathbf{a}_z$  unit vectors in the directions x, y and z respectively.

E: electric field density

B: magnetic flux density

J: current density

A: vector magnetic potential

These are all vectors and have a component in the x-, y- and z-direction.

The curl of a vector A is defined as

$$\nabla \times \mathbf{A} = \mathbf{a}_{x} \left( \frac{\partial A_{z}}{\partial y} - \frac{\partial A_{y}}{\partial z} \right) + \mathbf{a}_{y} \left( \frac{\partial A_{x}}{\partial z} - \frac{\partial A_{z}}{\partial x} \right) + \mathbf{a}_{z} \left( \frac{\partial A_{y}}{\partial x} - \frac{\partial A_{x}}{\partial y} \right)$$

(2.2)

Furthermore, the following symbols are used:

σ: conductivity

u: permeability

ε: permittivity.

Finally, we use the definition of potential [44]:

$$\nabla \mathbf{V} = -\mathbf{E} - \frac{\partial \mathbf{A}}{\partial t} \tag{2.3}$$

## 2.3.3 dV(z)/dz as a function of I(z)

First we calculate dV(z)/dz as a function of I(z). We assume that the voltage inside the interconnect is constant in both the x- and y-direction and is only changing in the z-direction.

$$\frac{\partial V(z)}{\partial z} = -E_z - \frac{\partial A_z}{\partial t} \tag{2.4}$$

In order to find dV(z)/dz as a function of I(z), we have to express both  $E_z$  and  $A_z$  as a function of I(z). E is related to the current density J [44]:

$$\mathbf{J} = \boldsymbol{\sigma} \cdot \mathbf{E} \tag{2.5}$$

and the current I(z) is given by

$$I(z) = J_z \cdot w \cdot h \tag{2.6}$$

Thus, (2.5) can be written as

$$\frac{I(z)}{w \cdot h} = \sigma_m \cdot E_z \tag{2.7}$$

with  $\sigma_m$  the conductivity of the metal. We have thus found  $E_z$  as a function of I(z). Now we come to  $A_z$ . **A** is related to **B** [44]:

$$\nabla \times \mathbf{A} = \mathbf{B} \tag{2.8}$$

A only has a component in the z-direction and (2.8) turns into

$$\mathbf{a}_{x} \cdot \frac{\partial A_{z}}{\partial y} - \mathbf{a}_{y} \cdot \frac{\partial A_{z}}{\partial x} = \mathbf{B} \tag{2.9}$$

There are four areas shown in figure 2.3 and (2.9) should be satisfied for all four areas. Thus:

$$\frac{\partial A_z}{\partial y} = B_x \to \begin{cases} A_z = -d \cdot B_{x,I} \\ A_z = d \cdot B_{x,III} \end{cases}$$

(2.10)

in areas I and III and

$$-\frac{\partial A_z}{\partial x} = B_y \to \begin{cases} A_z = -s \cdot B_{y,II} \\ A_z = s \cdot B_{y,IV} \end{cases}$$

(2.11)

in areas II and IV. Thus, the B-fields in the areas I and III are equal, but with opposite sign and the same is true for the B-fields in the areas II and IV. The relation between the B-fields in the areas I and II is

$$B_{x,I} = \frac{s}{d} \cdot B_{y,II} \tag{2.12}$$

Now we need to find either  $B_x$  or  $B_y$  as a function of I(z). This can be done with the help of one of Maxwell's equations [44]:

$$\nabla \times \frac{\mathbf{B}}{\mathbf{u}} = \mathbf{J} + \frac{\partial (\mathbf{\varepsilon} \cdot \mathbf{E})}{\partial t}$$

(2.13)

**B** has no component in the z-direction and the curl of **B** becomes

$$\nabla \times \mathbf{B} = -\mathbf{a}_x \frac{\partial B_y}{\partial z} + \mathbf{a}_y \frac{\partial B_x}{\partial z} + \mathbf{a}_z \left( \frac{\partial B_y}{\partial x} - \frac{\partial B_x}{\partial y} \right)$$

(2.14)

In areas I to IV, E has no component in the z-direction. Therefore, (2.13) can be rewritten for the z-direction as

$$\frac{\partial B_y}{\partial x} - \frac{\partial B_x}{\partial y} = \mu \cdot J_z \tag{2.15}$$

Integrating over both w and h gives

$$-w \cdot B_{x,I} - h \cdot B_{y,II} + w \cdot B_{x,III} + h \cdot B_{y,IV} = -2 \cdot w \cdot B_{x,I} - 2 \cdot h \cdot B_{y,II} = \mu \cdot I(z)$$

(2.16)

Combining (2.12) and (2.16) gives expressions for the B-field in areas I and II:

$$B_{x,I} = -\mu \cdot I(z) \cdot \frac{s}{2 \cdot (w \cdot s + h \cdot d)}$$

(2.17)

$$B_{y,II} = -\mu \cdot I(z) \cdot \frac{d}{2 \cdot (w \cdot s + h \cdot d)}$$

(2.18)

Now the B-field is known as a function of I(z), also  $A_z$  can be calculated as a function of I(z).

$$A_z = -d \cdot B_{x,I} = \mu \cdot I(z) \cdot \frac{s \cdot d}{2 \cdot (w \cdot s + h \cdot d)}$$

(2.19)

With (2.7) and (2.19) we have both  $E_z$  and  $A_z$  as a function of I(z) and can rewrite (2.4) as

$$\frac{\partial V(z)}{\partial z} = -\frac{1}{\sigma_m \cdot w \cdot h} \cdot I(z) - \mu \cdot \frac{s \cdot d}{2 \cdot (w \cdot s + h \cdot d)} \cdot \frac{\partial I(z)}{\partial t}$$

(2.20)

or

$$\frac{\partial V(z)}{\partial z} = -R' \cdot I(z) - L' \cdot \frac{\partial I(z)}{\partial t}$$

(2.21)

## 2.3.4 dl(z)/dz as a function of V(z)

Now, we calculate dI(z)/dz as a function of V(z). We use Maxwell's equation (2.13) again. In (2.15) we looked at the z-direction, now we will look at the x- and y-direction. With the help of (2.14) we find

$$-\mathbf{a}_{x}\frac{\partial B_{y}}{\partial z} + \mathbf{a}_{y}\frac{\partial B_{x}}{\partial z} = \mu \cdot \mathbf{a}_{x} \cdot (J_{x} + \frac{\partial(\varepsilon \cdot E_{x})}{\partial t}) + \mu \cdot \mathbf{a}_{y} \cdot (J_{y} + \frac{\partial(\varepsilon \cdot E_{y})}{\partial t})$$

(2.22)

which results in

$$-\frac{\partial B_y}{\partial z} = \mu \cdot J_x + \varepsilon \cdot \mu \cdot \frac{\partial E_x}{\partial t}$$

(2.23)

and

$$\frac{\partial B_x}{\partial z} = \mu \cdot J_y + \varepsilon \cdot \mu \cdot \frac{\partial E_y}{\partial t}$$

(2.24)

Expressions for  $B_x$  and  $B_y$  were already found in (2.17) and (2.18), which can be used to find

$$-\frac{\partial B_{y,II}}{\partial z} = \mu \cdot \frac{d}{2 \cdot (w \cdot s + h \cdot d)} \cdot \frac{\partial I_z}{\partial z} = \mu \cdot J_x + \varepsilon \cdot \mu \cdot \frac{\partial E_x}{\partial t}$$

(2.25)

$$\frac{\partial B_{x,I}}{\partial z} = -\mu \cdot \frac{s}{2 \cdot (w \cdot s + h \cdot d)} \cdot \frac{\partial I_z}{\partial z} = \mu \cdot J_y + \varepsilon \cdot \mu \cdot \frac{\partial E_y}{\partial t}$$

(2.26)

This can be written as

$$\frac{\partial I(z)}{\partial z} = \frac{2 \cdot (w \cdot s + h \cdot d)}{s \cdot d} \cdot (J_x \cdot s) + \frac{2 \cdot \varepsilon \cdot (w \cdot s + h \cdot d)}{s \cdot d} \cdot \frac{\partial (E_x \cdot s)}{\partial t}$$

(2.27)

$$\frac{\partial I(z)}{\partial z} = -\frac{2 \cdot (w \cdot s + h \cdot d)}{s \cdot d} \cdot (J_y \cdot d) - \varepsilon \cdot \frac{2 \cdot (w \cdot s + h \cdot d)}{s \cdot d} \cdot \frac{\partial (E_y \cdot d)}{\partial t}$$

(2.28)

To relate I(z) to a potential, we use (2.3) again. This equation can be rewritten for the x-and y-directions as

$$\frac{\partial V(z)}{\partial x} = -E_x - \frac{\partial A_x}{\partial t} \tag{2.29}$$

$$\frac{\partial V(z)}{\partial v} = -E_y - \frac{\partial A_y}{\partial t} \tag{2.30}$$

A only has a component in the z-direction, thus

$$V(z) = -E_x \cdot s \tag{2.31}$$

$$V(z) = E_{v} \cdot d \tag{2.32}$$

From (2.5), we also know

$$E_x = \frac{J_x}{\sigma_o} \to J_x \cdot s = -\frac{V(z)}{\sigma_o}$$

(2.33)

$$E_{y} = \frac{J_{y}}{\sigma_{o}} \to J_{y} \cdot d = \frac{V(z)}{\sigma_{o}}$$

(2.34)

with  $\sigma_0$  the conductivity of the oxide. Now, both (2.27) and (2.28) can be written as

$$\frac{\partial I(z)}{\partial z} = -\frac{2 \cdot \sigma_o \cdot (w \cdot s + h \cdot d)}{s \cdot d} \cdot V(z) - \frac{2 \cdot \varepsilon \cdot (w \cdot s + h \cdot d)}{s \cdot d} \cdot \frac{\partial V(z)}{\partial t}$$

(2.35)

or

$$\frac{\partial I(z)}{\partial z} = -G' \cdot V(z) - C' \cdot \frac{\partial V(z)}{\partial t}$$

(2.36)

### 2.4 Distributed model

#### 2.4.1 Introduction

In the previous section, by looking at the electric and magnetic fields of an interconnect, two relations between voltage and current were found. In this section, we show the corresponding distributed model and we show the solution of these equations. After that, we explain how to calculate transfer functions of the interconnect and how to calculate the power consumption with the help of s-parameters.

### 2.4.2 Telegrapher's equations

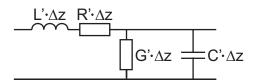

The equations (2.21) and (2.36) are known as the Telegrapher's equations [44]. R' is the distributed resistance per unit length, L' the distributed inductance per unit length, G' the distributed conductance per unit length and C' the distributed capacitance per unit length of the interconnect. The corresponding distributed model is shown in figure 2.4.

Figure 2.4: Equivalent circuit of a differential length  $\Delta z$  of an interconnect.

According to (2.20) and (2.35), the values of the distributed parameters for our interconnect are approximated by

$$R' = \frac{1}{w \cdot h \cdot \sigma_m} \quad (\Omega / m) \tag{2.37}$$

$$L' = \mu \cdot \left(\frac{s \cdot d}{2 \cdot (w \cdot s + h \cdot d)}\right) = \frac{\mu}{2} \cdot \left(\frac{d}{w} + \frac{s}{h}\right) \quad (H/m)$$

(2.38)

$$G' = \frac{2 \cdot \sigma_o \cdot (w \cdot s + h \cdot d)}{s \cdot d} = 2 \cdot \sigma_o \cdot (\frac{w}{d} + \frac{h}{s}) \quad (S/m)$$

(2.39)

$$C' = \frac{2 \cdot \varepsilon \cdot (w \cdot s + h \cdot d)}{s \cdot d} = 2 \cdot \varepsilon \cdot (\frac{w}{d} + \frac{h}{s}) \quad (F/m)$$

(2.40)

A solution for the Telegrapher's equations ((2.21) and (2.36)) is found in [44].

$$v(z,t) = \text{Re}[V(z) \cdot e^{j \cdot \omega t}]$$

(2.41)

$$i(z,t) = \text{Re}[I(z) \cdot e^{j \cdot \omega t}]$$

(2.42)

$$V(z) = V_0^{\ p} \cdot e^{-\gamma \cdot z} + V_0^{\ n} \cdot e^{\gamma \cdot z} \tag{2.43}$$

$$I(z) = I_0^p \cdot e^{-\gamma \cdot z} + I_0^n \cdot e^{\gamma \cdot z}$$

(2.44)

The p and n superscripts denote waves that travel in the positive z-direction and the negative z-direction respectively and

$$\gamma = \sqrt{(R' + j \cdot \omega \cdot L') \cdot (G' + j \cdot \omega \cdot C')}$$

(2.45)

The ratio of the voltage and current at any z for an infinitely long interconnect is independent of z and is called the characteristic impedance of the interconnect.

$$Z_c = \sqrt{\frac{R' + j \cdot \omega \cdot L'}{G' + j \cdot \omega \cdot C'}}$$

(2.46)

Of course, an interconnect is not infinitely long. If the interconnect is terminated with  $Z_c$ , then no reflections occur. Otherwise, if the interconnect is terminated with an impedance Z, reflections do occur and the ratio between reflected and incident wave is given by

$$\Gamma = \frac{Z - Z_c}{Z + Z_c} \tag{2.47}$$

### 2.4.3 Attenuation, reflections and distortion

An ideal interconnect would have R' = 1/G' = 0. Then, (2.45) and (2.46) can be written as

$$\gamma_{LC} = j \cdot \omega \cdot \sqrt{L' \cdot C'} \tag{2.48}$$

$$Z_{c,LC} = \sqrt{\frac{L'}{C'}} \tag{2.49}$$

The propagation constant has no real part. Therefore, the waves that are traveling in the interconnect are not attenuated. The characteristic impedance of the LC interconnect is real and by choosing a source and load impedance equal to this characteristic impedance, no reflections occur.

The group delay per unit length is the derivative of the imaginary part of  $\gamma$  with respect to  $\omega$ :

$$\frac{\partial \operatorname{Im}(\gamma)}{\partial \omega} = \sqrt{L' \cdot C'} \tag{2.50}$$

This group delay is independent of frequency, which means that every frequency component of a transmitted symbol arrives with the same delay, so the signal is not distorted.

However, global on-chip interconnects can have such a large R' that for the frequencies of interest, R'  $\gg$   $\omega$ L' and not R', but L' can be ignored.

$$\gamma_{RC} = \sqrt{j \cdot \omega \cdot R' \cdot C'} = (1+j) \cdot \frac{1}{2} \cdot \sqrt{2} \cdot \sqrt{\omega \cdot R' \cdot C'}$$

(2.51)

$$Z_{c,RC} = \sqrt{\frac{R'}{j \cdot \omega \cdot C'}} \tag{2.52}$$

The propagation constant does not only have an imaginary, but also a real part. This means that the transmitted signal is attenuated along the interconnect. This attenuation is frequency dependent. The characteristic impedance also depends on frequency and it will be difficult to make a source and load impedance equal to this characteristic impedance. Therefore, reflections will occur. However, we will see later on (sections 3.3 and 3.4) that these reflections are actually beneficial.

Also, the group delay depends on frequency.

$$\frac{\partial \operatorname{Im}(\gamma)}{\partial \omega} = \frac{1}{4} \cdot \sqrt{2} \cdot \frac{R' \cdot C'}{\sqrt{\omega \cdot R' \cdot C'}}$$

(2.53)

The frequency components of a transmitted symbol arrive with different delays. Therefore, the output signal is distorted.

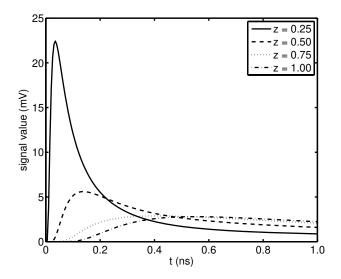

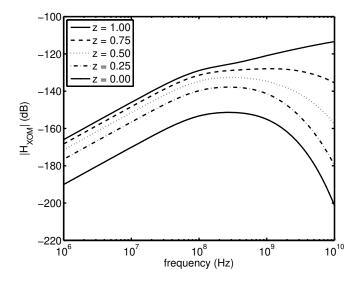

The attenuation, reflections and distortion of RC dominated interconnects can be seen in the impulse response of the interconnect. Conventionally, an interconnect is driven by a strong driver and left open at the receiver end. For simplicity, we take  $Z_S=0$  and  $Z_L=\infty$  and further use the parameters of the example interconnect from section 1.5.2. The impulse (1 V amplitude, 10 ps long) response is plotted in figure 2.5. This is done at different positions z along the interconnect, where z=1.00 is at the end of the interconnect.

Figure 2.5: Impulse response for different positions along the interconnect with  $Z_S = 0$  and  $Z_L = \infty$ .

The height of the response decreases for higher z (attenuation). Also, the pulse is widened (distorted). Note that the responses have a zero slope at starting time, which is due to LC behavior.

The shape of the impulse response at the different positions can be explained in two ways. The first way is to view the response as a diffusion process, where charge diffuses through the interconnect. A charge difference between two positions on the interconnect will give a current to counteract this difference. The larger the charge difference, the larger the current.

We can also explain the response with waves that are reflected many times by the termination impedances. The addition of all these reflected waves gives the shapes as seen in figure 2.5. These reflections can be made visible. In order to do that, we make use of two cases, an open and a shorted case.

Open case:  $Z_S = 0$  and  $Z_L = \infty$ Shorted case:  $Z_S = Z_L = 0$ .

From (2.47) we know that for Z = 0 the reflection coefficient is -1 and for  $Z = \infty$  the reflection coefficient is +1. In the open case, the waves that are on the interconnect are

$$V_0^p + V_1^n - V_2^p - V_3^n + \dots (2.54)$$

$V_i^p$  is a voltage wave traveling in the positive z-direction and  $V_i^n$  is a voltage wave traveling in the negative z-direction with i the number of reflections the wave has encountered. In the shorted case, the waves that are on the interconnect are

$$V_0^p - V_1^n + V_2^p - V_3^n + \dots (2.55)$$

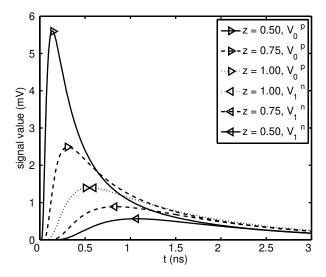

By adding (2.54) and (2.55), we are able to calculate the wave that is traveling in the positive z-direction.

$$2 \cdot V_0^p - 2 \cdot V_3^n + \dots \approx 2 \cdot V_0^p \tag{2.56}$$

Because of the large attenuation,  $V_3^n$  will be much smaller than  $V_0^p$  and can be neglected. In the same way, subtracting (2.55) from (2.54) gives the wave propagating in the negative z-direction.

$$2 \cdot V_1^n - 2 \cdot V_2^p + \dots \approx 2 \cdot V_0^n \tag{2.57}$$

So, by adding or subtracting the responses of an open and a shorted case, we are able to plot the waves that are traveling in either the positive or the negative z-direction, as shown in figure 2.6.

Figure 2.6: Impulse response for different positions along the interconnect decomposed in a wave traveling in the positive z-direction and a wave traveling in the negative z-direction.

### 2.4.4 S-parameters

The notion that the response of an RC interconnect can be thought of as a summation of waves traveling in both the positive and negative z-direction, is reflected in the s-parameter model of an interconnect.

The s-parameters of a two-port network are given by [45]:

$$b_1 = s_{11} \cdot a_1 + s_{12} \cdot a_2 b_2 = s_{21} \cdot a_1 + s_{22} \cdot a_2$$

(2.58)

The incident (a) and scattered (b) waves are defined with respect to a reference impedance  $Z_0$ .

$$a_k = \frac{V_k^p}{\sqrt{Z_0}} = \frac{1}{2} \cdot (\frac{V_k}{\sqrt{Z_0}} + \sqrt{Z_0} \cdot I_k)$$

(2.59)

$$b_k = \frac{V_k^n}{\sqrt{Z_0}} = \frac{1}{2} \cdot (\frac{V_k}{\sqrt{Z_0}} - \sqrt{Z_0} \cdot I_k)$$

(2.60)

$V_k^p$  and  $V_k^n$  are the incident and scattered voltage waves at port k, while  $V_k$  and  $I_k$  are the terminal voltage and current at port k.

If a<sub>k</sub> and b<sub>k</sub> are known, the terminal voltage and current can be calculated easily as

$$V_k = \sqrt{Z_0} \cdot (a_k + b_k) \tag{2.61}$$

$$I_k = \frac{a_k - b_k}{\sqrt{Z_0}} \tag{2.62}$$

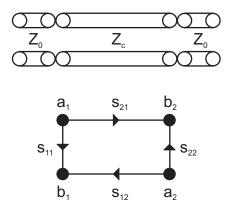

The s-parameter model of an interconnect is shown in figure 2.7. The s-parameters give the relation between the incident waves  $a_1$  and  $a_2$  and the scattered waves  $b_1$  and  $b_2$ . The values of the s-parameters are given by [45]:

$$S = \begin{bmatrix} s_{11} & s_{12} \\ s_{21} & s_{22} \end{bmatrix}$$

$$= \frac{1}{2Z_0 Z_c \cosh(\gamma t) + (Z_c^2 + Z_0^2) \sinh(\gamma t)} \times \begin{bmatrix} (Z_c^2 - Z_0^2) \sinh(\gamma t) & 2Z_0 Z_c \\ 2Z_0 Z_c & (Z_c^2 - Z_0^2) \sinh(\gamma t) \end{bmatrix}$$

(2.63)

Figure 2.7: S-parameter model of an interconnect.

The propagation constant  $\gamma$  and characteristic impedance  $Z_c$  are defined in (2.45) and (2.46) respectively. Note that by choosing  $Z_0$  equal to  $Z_c$  both  $s_{11}$  and  $s_{22}$  are zero and  $s_{12}$  and  $s_{21}$  reduce to

$$s_{21} = s_{12} = e^{-\gamma \cdot l} \tag{2.64}$$

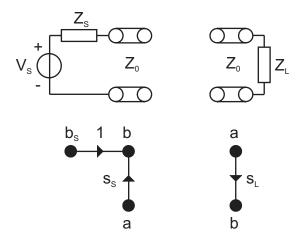

The interconnect is on one side connected to a transmitter, modeled as a voltage source with source impedance  $Z_S$ . On the other side, the interconnect is connected to a receiver, modeled as a load impedance  $Z_L$ . The s-parameter model of the transmitter and receiver are [45]:

Figure 2.8: S-parameter model of transmitter and receiver.

The values of the s-parameters of the source and load impedance are

$$s_S = \frac{Z_S - Z_0}{Z_S + Z_0} \tag{2.65}$$

$$s_L = \frac{Z_L - Z_0}{Z_L + Z_0} \tag{2.66}$$

and the source voltage appears in b<sub>s</sub>:

$$b_S = V_S \cdot \frac{\sqrt{Z_0}}{Z_0 + Z_S} \tag{2.67}$$

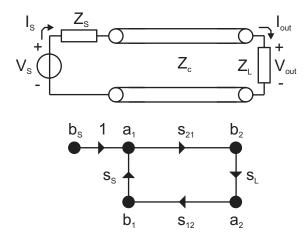

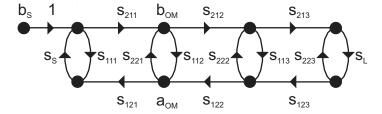

Combining figures 2.7 and 2.8 and choosing  $Z_0 = Z_c$ , the model of figure 2.9 represents the interconnect connected between a transmitter and receiver.

Figure 2.9: s-parameter model of an interconnect with transmitter and receiver.

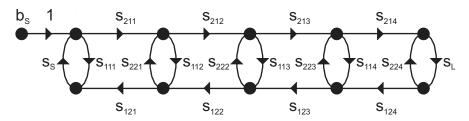

### 2.4.5 Transfer functions

We will use the s-parameter model to calculate the transfer function  $V_{out}/V_S$  of the interconnect. In the following,  $Z_0$  is always chosen equal to  $Z_c$ . Rewriting (2.67) gives the input voltage  $V_S$  of the interconnect.

$$V_S = b_S \cdot \frac{Z_c + Z_S}{\sqrt{Z_c}} \tag{2.68}$$

The output voltage  $V_{out}$  can be calculated with the help of (2.59) and (2.60) as

$$V_{out} = \sqrt{Z_c} \cdot (a_2 + b_2) \tag{2.69}$$

The transfer function from V<sub>S</sub> to V<sub>out</sub> can now be calculated as

$$H_{VV} = \frac{V_{out}}{V_S} = \frac{Z_c}{Z_c + Z_S} \cdot (\frac{a_2}{b_S} + \frac{b_2}{b_S})$$

(2.70)

Both  $a_2/b_S$  and  $b_2/b_S$  can be found with the help of Mason's rule [45].

$$\frac{a_2}{b_S} = \frac{s_{21} \cdot s_L}{1 - s_{21} \cdot s_L \cdot s_{12} \cdot s_S} \tag{2.71}$$

$$\frac{b_2}{b_S} = \frac{s_{21}}{1 - s_{21} \cdot s_L \cdot s_{12} \cdot s_S} \tag{2.72}$$

The transfer function thus is

$$H_{VV} = \frac{V_{out}}{V_S} = \frac{Z_c}{Z_c + Z_S} \cdot \frac{s_{21} \cdot (1 + s_L)}{1 - s_{21} \cdot s_L \cdot s_{12} \cdot s_S}$$

(2.73)

with  $s_{21}$ ,  $s_L$ ,  $s_{12}$  and  $s_S$  as defined in the previous section.

Of course, also other transfer functions can be calculated.

$$H_{VI} = \frac{I_{out}}{V_S} = \frac{1}{Z_c + Z_S} \cdot \frac{s_{21} \cdot (1 - s_L)}{1 - s_{21} \cdot s_L \cdot s_{12} \cdot s_S}$$

(2.74)

$$H_{IV} = \frac{V_{out}}{I_S} = Z_c \cdot \frac{s_{21} \cdot (1 + s_L)}{1 - s_{21} \cdot s_L \cdot s_{12}}$$

(2.75)

$$H_{II} = \frac{I_{out}}{I_S} = \frac{s_{21} \cdot (1 - s_L)}{1 - s_{21} \cdot s_L \cdot s_{12}}$$

(2.76)

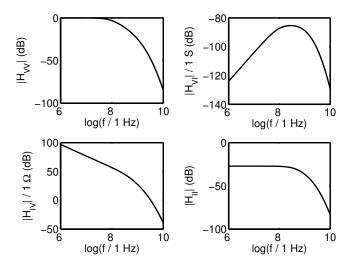

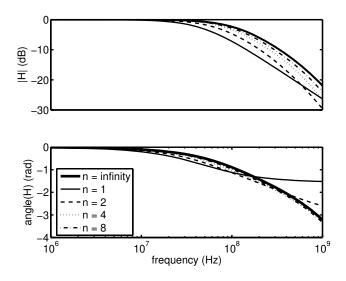

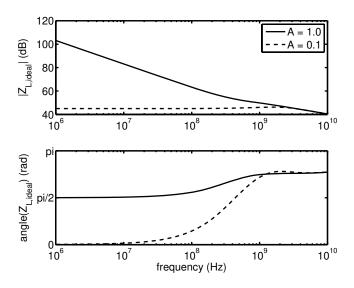

As an example, these four transfer functions are plotted in figure 2.10 for the example interconnect from section 1.5.2. The transfer function  $H_{VV}$  is the same as we saw already in figure 1.10. For high frequencies, the magnitude of  $H_{VV}$  drops and the bandwidth is limited. The transfer function  $H_{VI}$  shows that both for low and for high frequencies, no current is flowing through the load capacitance. For low frequencies, the obvious reason for this is that a capacitance has high impedance for low frequencies, while for high frequencies, the voltage across the load capacitance is small. The transfer function  $H_{IV}$  first drops with -20 dB/decade due to integration of the current in the interconnect capacitance. For higher frequencies, the drop rate becomes much more than -20 dB/decade.  $H_{II}$  has the same shape as  $H_{VV}$ . Interestingly, the bandwidth of  $H_{II}$  is larger than the bandwidth of  $H_{VV}$ .

Figure 2.10: Transfer functions of the example interconnect from section 1.5.2.

### 2.4.6 Power consumption

In order to calculate the power consumption, the current  $I_S$  that is drawn from the voltage source  $V_S$  needs to be found.  $I_S/V_S$  can be calculated with the help of the s-parameter model. With (2.59) and (2.60), we can find

$$I_S = \frac{a_1 - b_1}{\sqrt{Z_C}} \tag{2.77}$$

and with (2.67)

$$Y_{in} = \frac{I_S}{V_S} = \frac{1}{Z_c + Z_S} \cdot \frac{a_1 - b_1}{b_S}$$

(2.78)

With Mason's rule [45]

$$Y_{in} = \frac{1}{Z_c + Z_S} \cdot \frac{1 - s_{21} \cdot s_L \cdot s_{12}}{1 - s_{21} \cdot s_L \cdot s_{12} \cdot s_S}$$

(2.79)

In order to find the power, Y<sub>in</sub> has to be multiplied by the power spectral density (PSD) of the input voltage signal. The PSD of the input voltage signal can be calculated as follows.

We start with a 'binary (zero-mean) Markov source' which is characterized by:

$$\begin{cases}

\Pr(a_{n+1} \neq a_n) = p_{trans} \\

\Pr(a_{n+1} = a_n) = 1 - p_{trans}

\end{cases} \quad a = \{1, -1\} \tag{2.80}$$

Pr(x) is the probability that x is true and  $p_{trans}$  is the transition probability. The PSD of such a Markov source can be written as [46]

$$S_{MM}(f) = \frac{1}{T_S} \cdot \left| H_M(e^{j \cdot 2 \cdot \pi \cdot f \cdot T_S}) \right|^2 \cdot (1 - (1 - 2 \cdot p_{trans})^2)$$

(2.81)

with

$$H_M(e^{j \cdot 2 \cdot \pi \cdot f \cdot T_S}) = \frac{1}{e^{j \cdot 2 \cdot \pi \cdot f \cdot T_S} - (1 - 2 \cdot p_{traps})}$$

(2.82)

and  $T_S$  the symbol time. By multiplying  $S_{MM}(f)$  with  $|H_S(f)|^2$ , the PSD of the input voltage signal is found.  $H_S(f)$  is the Fourier transfer of the symbol response.

$$S_{SS}(f) = |H_s(f)|^2 \cdot \frac{1}{T_S} \cdot |H_m(e^{j \cdot 2 \cdot \pi \cdot f \cdot T_S})|^2 \cdot (1 - (1 - 2 \cdot p_{trans})^2)$$

(2.83)

The power that is consumed in the interconnect and its termination impedances can be found by multiplying the PSD of the input voltage signal by  $Y_{in}$  and integrating over frequency.

$$P = \int_{f=-\infty}^{\infty} real\left(\frac{S_{SS}(f)}{Z_{in}(f)}\right) \cdot df = 2 \cdot \int_{0}^{\infty} S_{SS}(f) \cdot \frac{Y_{in}(f) \cdot Y_{in}(f)^{*}}{real(Y_{in}(f))} df$$

$$(2.84)$$

As an illustration, the power consumption of the example interconnect from section 1.5.2 is shown in figure 2.11. As we are interested in the highest achievable data rate for minimum power consumption, the power consumption is divided by the data rate. This energy per bit is plotted for plain binary signaling against the transition probability for different data rates.

The energy that is dissipated per bit is larger for a higher transition probability. This makes sense, as with more transitions, the interconnect is charged and discharged more often. For high data rates and high transition probabilities, the receiver end of the interconnect is not fully charged and discharged anymore. Therefore, the energy per bit at high transition probabilities is lower for high data rates. Note, that for highest information density, the transition probability should be 0.5 [47].

Figure 2.11: Energy per bit as a function of transition probability and data rate.

### 2.4.7 Additional power consumption in receiver

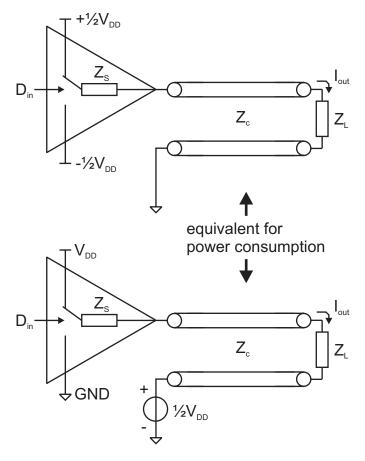

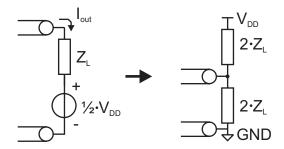

In the previous section, the power calculations have assumed signaling with normalized bipolar signals (-1 V and 1 V). However, a transceiver in CMOS will in general operate between the supply voltages  $V_{DD}$  and GND. Fortunately, from a power consumption perspective, the two schematics in figure 2.12 are equivalent. As the probability of the transmitter being connected to  $V_{DD}$  is equal to the probability of the transmitter being connected to GND, the net power delivered by the (conceptual) voltage source  $V_{DD}/2$  is zero.

However in general, the practical implementation of this voltage source gives additional power consumption. If we assume that there is no resistance in the GND line, we can place the conceptual voltage source below the load impedance and in a practical receiver, this may be implemented as shown in figure 2.13. With this implementation, additional current is flowing from  $V_{DD}$ , equal to

$$I_{DD} = \frac{V_{DD}}{4 \cdot \text{Re}(Z_L)} - \frac{I_{out}}{2}$$

(2.85)

For equal probabilities of a positive and a negative I<sub>out</sub>, the extra power delivered by V<sub>DD</sub> is

$$P_{RX} = \frac{V_{DD}^2}{4 \cdot \text{Re}(Z_L)} \tag{2.86}$$

This power has to be added to the power as calculated with (2.84), if the implementation of figure 2.13 is used.

Figure 2.12: Power consumption is equivalent for transceivers operating between  $+V_{DD}/2$  and  $-V_{DD}/2$  or between GND and  $V_{DD}$ .

Figure 2.13: A practical implementation of the receiver with impedances to both supply voltages.

## 2.5 Expanded distributed model

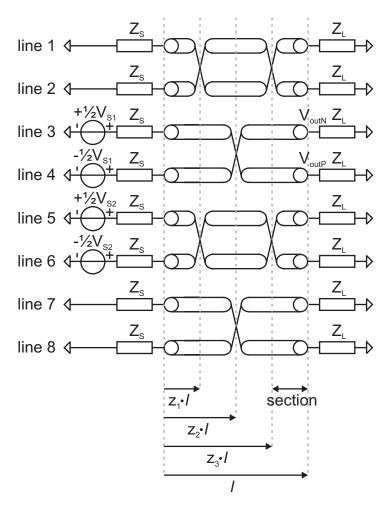

Until now, we have used a distributed model for a single interconnect, with all other metal connected to ground. However, often interconnects have neighboring interconnects running in parallel, for instance in a bus structure (see interconnect 1, 2 and 3 in figure 2.14).

Figure 2.14: Capacitances to ground  $(C_G')$  and neighboring interconnects  $(C_M')$ .

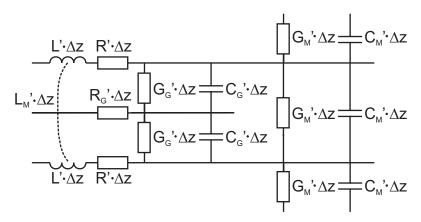

The distributed model of figure 2.4 can be expanded to the model of figure 2.15. Two interconnects are shown (for instance 1 and 2), with a ground line in between. Note however, that in the physical structure this ground line is above and below the interconnect (see figure 2.14).

Figure 2.15: Distributed model for interconnect with parallel neighboring interconnects

Both interconnects have a distributed resistance R' and a distributed inductance L' and the ground line has a distributed resistance  $R_G$ '. There is also a distributed mutual inductance  $L_M$ ' between the two interconnects. The distributed capacitance  $C_G$ ' and the distributed conductance  $G_G$ ' are connected to the ground line, while the distributed mutual capacitance  $C_M$ ' and distributed mutual conductance  $G_M$ ' are connected to neighboring interconnects.

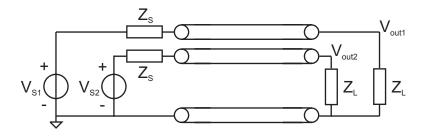

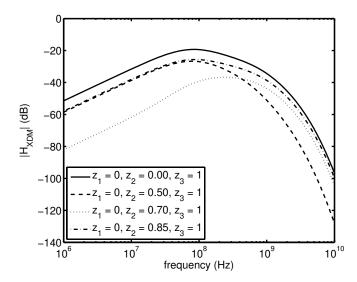

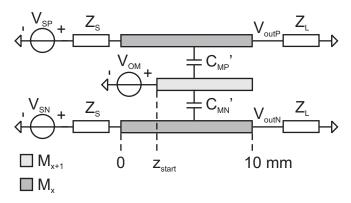

Because of the mutual capacitance, inductance and conductance and the resistance of the common ground, there will be crosstalk between two neighboring interconnects. Figure 2.16 shows two neighboring interconnects.

Figure 2.16: Two neighboring interconnects.

We assume that both interconnects are equal.  $V_{out1}$  and  $V_{out2}$  are a function of both  $V_{S1}$  and  $V_{S2}$ .

$$V_{out1} = H \cdot V_{S1} + H_X \cdot V_{S2}$$

$$V_{out2} = H \cdot V_{S2} + H_X \cdot V_{S1}$$

(2.87)

In this section, we calculate the transfer function H and the crosstalk transfer function  $H_X$ . In order to do that, we will use a modal analysis. We will look at two cases.

Even case:

$$V_{S1} = V_{S2}$$

.

Odd case:  $V_{S1} = -V_{S2}$ .

In the even case,

$$V_{out1} = (H + H_X) \cdot V_{S1} = H_{even} \cdot V_{S1}$$

$$V_{out2} = (H + H_X) \cdot V_{S2} = H_{even} \cdot V_{S2}$$

(2.88)

while in the odd case

$$V_{out1} = (H - H_X) \cdot V_{S1} = H_{odd} \cdot V_{S1}$$

$$V_{out2} = (H - H_X) \cdot V_{S2} = H_{odd} \cdot V_{S2}$$

(2.89)

If we are able to calculate H<sub>even</sub> and H<sub>odd</sub>, we can use

$$H = \frac{1}{2} \cdot (H_{even} + H_{odd})$$

$$H_X = \frac{1}{2} \cdot (H_{even} - H_{odd})$$

(2.90)

to calculate H and  $H_X$ . The transfer functions  $H_{even}$  and  $H_{odd}$  can be calculated in almost the same way as was done as in section 2.4.5. Only, the parameters R', L', C' and G' should be replaced by  $R_{even}$ ',  $L_{even}$ ',  $C_{even}$ ' and  $G_{even}$ ' in the even case and by  $R_{odd}$ ',  $L_{odd}$ ',  $C_{odd}$ ' and  $G_{odd}$ ' in the odd case.

These even and odd parameters differ from the standard RLCG parameters. In the even case, the mutual capacitance and mutual conductance to the neighboring interconnect is not seen, since the voltage across these mutual impedances is zero. In the odd case on the other hand, the voltage across these impedances is effectively doubled, thus also doubling the effective mutual capacitance and conductance (Miller multiplication). The mutual inductance should be added to the inductance of the interconnect for the even case and subtracted for the odd case. The resistance of the ground line is only seen in the even case, as for the odd case all current is returned in the neighboring interconnect.

These considerations are summarized in the equations below. For simplicity, we assume that the  $C_M$ ' and the  $G_M$ ' to other neighboring interconnects can be placed in parallel with  $C_G$ ' and  $G_G$ '. Then, in even mode

$$R_{\varrho\nu\varrho\eta}' = R' + 2 \cdot R_{G}' \tag{2.91}$$

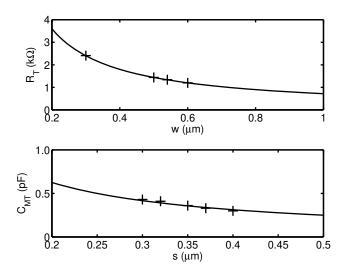

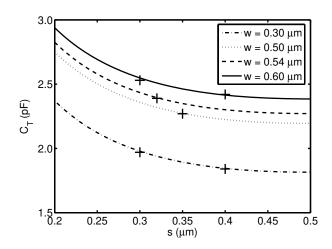

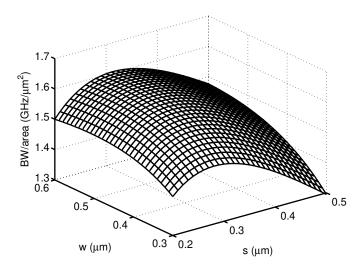

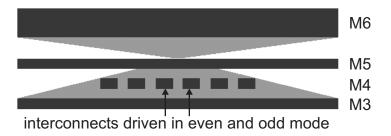

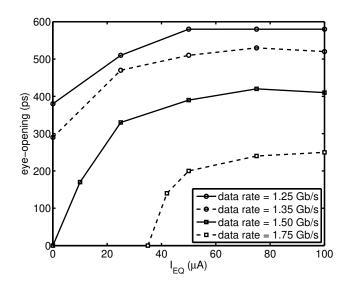

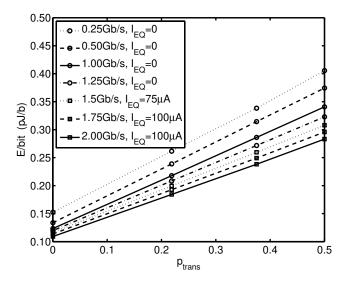

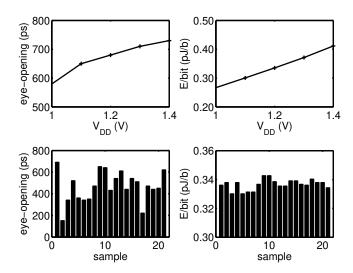

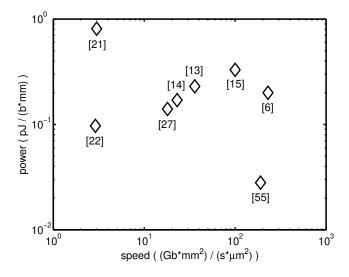

$$L_{\varrho\nu\varrho\eta}' = L' + L_M' \tag{2.92}$$