# High-Temperature Recessed Channel SiC CMOS Inverters and Ring Oscillators

Mattias Ekström<sup>®</sup>, Bengt Gunnar Malm<sup>®</sup>, *Senior Member, IEEE*, and Carl-Mikael Zetterling<sup>®</sup>, *Senior Member, IEEE*

Abstract—Digital electronics in SiC find use in hightemperature applications. The objective of this study was to fabricate SiC CMOS without using ion implantation. In this letter, we present a recessed channel CMOS process. Selective doping is achieved by etching epitaxial layers into mesas. A deposited SiO<sub>2</sub>-film, post-annealed at low temperature and re-oxidized in pyrogenic steam, is used as the gate oxide to produce a conformal gate oxide over the non-planar topography. PMOS, NMOS, inverters, and ring oscillators are characterized at 200 °C. The PMOS requires reduced threshold voltage in order to enable longterm reliability. This result demonstrates that it is possible to fabricate SiC CMOS without ion implantation and by low-temperature processing.

*Index Terms*—Inverter, recessed channel, ring oscillator (RO), silicon carbide (4H-SiC), static CMOS.

# I. INTRODUCTION

C EVERAL different transistor and circuit technologies have been demonstrated in silicon carbide (4H-SiC) technology. SiC circuit technology is suitable for extreme environments, such as high temperature [1] and high radiation [2]. The bipolar junction transistor (BJT) technology have been demonstrated for use in emitter-coupled logic (ECL) [3], [4] and transistor-transistor logic (TTL) [5], [6]. The fieldeffect transistors (FETs) include impressive results in the use of metal-semiconductor FETs (MESFETs) [7], [8], junction FETs (JFETs) [9]–[11] and metal oxide semiconductor FETs (MOSFETs) [12]-[15]. Of these transistors and circuit families, the static complementary MOSFET (CMOS) circuit family offers high input impedance, high fan-out, rail-to-rail swing output, low static power consumption, dense and simple digital circuit design and compatibility with all state-of-theart memory technologies. SiC CMOS together with integrated ferroelectric memory devices [16], [17] could give non-volatile memory operational at high temperatures.

Manuscript received January 31, 2019; revised February 27, 2019; accepted March 2, 2019. Date of publication March 5, 2019; date of current version April 25, 2019. This work was a part of the Working on Venus Project supported by the Knut and Alice Wallenberg Foundation. The Implementation of CMP was supported in part by the Swedish Foundation for Strategic Research. The review of this letter was arranged by Editor J. Vobecky. *(Corresponding author: Mattias Ekström.)*

The authors are with the School of Electrical Engineering and Computer Science, KTH Royal Institute of Technology, SE-164 40 Kista, Sweden (e-mail: mekstr@kth.se).

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2019.2903184

The state-of-the-art SiC NMOS devices uses nitridation in either N<sub>2</sub>O or NO to achieve high channel mobility ( $\mu_n$ ), typically in the range 25–35 cm<sup>2</sup>/Vs [18], [19]. Nitridation has been reported to produce high hole mobility ( $\mu_p$ ), about 7–10 cm<sup>2</sup>/Vs [20], although the highest hole mobility was reported for pyrogenic steam grown oxides, with  $\mu_p$ of 15.6 cm<sup>2</sup>/Vs [21]. However,  $\mu_n$  is reportedly low in this process (1 cm<sup>2</sup>/Vs) [12].

Previous demonstrations of SiC CMOS have used ion implantation to achieve selective doping. Ion implantation is continually improving in SiC technology [22], but the  $p^+$ -type implant requires excessively high annealing (~1700 °C) to activate the dopants. Self-aligned PMOS transistors are currently not possible. A considerable amount of point defects remain even after high temperature annealing. Based on our previous experience in SiC BJT technology [3]-[6], which did not require ion implantion, it was of interest to determine if SiC CMOS could also be done without ion implantation. A few previous works have presented recessed channel SiC NMOS transistors [23]–[25], a technology that does not require ion implantation. The recessed channel transistor can be processed by etching epitaxially grown layers to achieve selective doping. In this letter, we present the first results of our SiC CMOS process, which is the first time demonstration of a recessed channel SiC CMOS process that does not require ion implantation. We demonstrate inverters and ring oscillators (ROs) with this process. The results of this study can prove beneficial for others working with SiC CMOS, regardless of if ion implantation or epitaxy-only process is used. Both nitridation and steam process were tested, but only the steam process produced PMOS transistors that could be used for CMOS applications. Only the steam process is presented here. The presented process is intended for high temperature applications.

# **II. EXPERIMENTAL DETAILS**

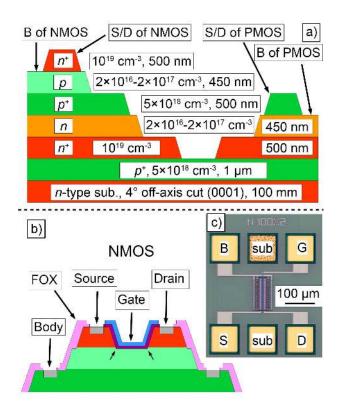

The devices were fabricated in our in-house 100 mm wafer SiC processing flow. The epitaxy was grown by Norstel [26], and was, from top to bottom,  $n^+/p/p^+/n/n^+/p^+/n$ -substrate. The lightly doped regions (*n* and *p*) served as the body of the transistors, and had a graded doping profile. The highly doped regions ( $n^+$  and  $p^+$ ) served as the source/drain or body contact region (depending on transistor polarity). The final  $p^+$ -layer isolates the PMOS transistors from the *n*-type substrate. The doping profile, with thickness

This work is licensed under a Creative Commons Attribution 3.0 License. For more information, see http://creativecommons.org/licenses/by/3.0/

Fig. 1. a) Half-pitch cell of NMOS and PMOS epitaxy after etching. The body dopings are graded, with higher doping (125 nm,  $2 \times 10^{17}$  cm<sup>-3</sup>) at the surface compared to deeper in the body (325 nm,  $2 \times 10^{16}$  cm<sup>-3</sup>). b) Cross-section of an NMOS, illustrating the four terminals (without metallization). The etch recesses the channel and exposes the *p*-type region. The poly-gate controls electron flow from the raised source to the raised drain through field-effect modulation of charge-carriers in the recessed channel. The corners at the edges of the channel are pointed out. c) Photograph of fabricated NMOS (100  $\mu$ m width, 2  $\mu$ m length). The two sub. connections are to the bottom *p*<sup>+</sup>-layer to isolate the transistors from the substrate.

and doping values, is shown in Fig. 1a). The epitaxial layers were etched into mesas by magnetically enhanced reactive ion etching (MERIE, SF<sub>6</sub>-based, 300 W, 5.3 Pa, 3 mT) in five steps, as shown in Fig. 1a). Photoresist was used, which gives sloped mesa sidewalls. The surface etch damage was removed by sacrificial oxidation. The field oxide (FOX) was formed in a sequence of depositing polysilicon films (poly), patterning the poly and oxidizing the patterned poly into polyoxide. A thin blanket polyoxide prevented SiC etch damage during the poly etch. The FOX was thinned in buffered HF to open the active regions. The oxidations were performed at 1000 °C in pyrogenic steam. The final FOX thickness was 230 nm. The merits of using polyoxide in SiC technology was recently evaluated [27]. Radio Corporation of America (RCA) clean was performed prior to depositing 33 nm SiO<sub>2</sub> by atomic layer deposition (ALD). This ALD-film sets the bulk thickness of the gate oxide. After deposition, the gate oxide interface was oxidized in O<sub>2</sub> for 10 min at 1050 °C, followed by annealing the oxide in  $N_2$  for 1 h, ended by steam for 10 min at 950 °C. The low temperature and short time was used to prevent excessive oxide growth on the exposed a-faces [28]. In-situ doped poly (n-type) was used as gate electrode. Contacts were formed as detailed in our previous work [29], [30]. The NMOS transistor without metallization is shown in Fig. 1b). A chemical-mechanical

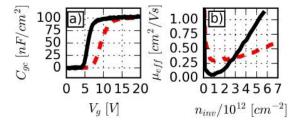

Fig. 2. NMOS (100 × 10) transistor, measured at RT (dashed) and at HT (solid). a)  $C_{gc} - V_g$ , measured at 100 kHz, 30 mV (root-mean square, RMS). b)  $\mu_{eff} - n_{inv}$ , with  $n_{inv}$  the inversion charge number density.

polishing (CMP) enabled 2-level TiW-metallization was used to connect the transistors. The metallization was covered with a plasma enhanced CVD (PECVD)  $SiO_2/SiN_x$  passivation and the measurement pads were covered with Au/Pt/Ti to prevent oxidation at high temperature [9], [31]. A processed NMOS transistor can be seen in Fig. 1c).

Electrical characterization was performed using a Keithley SCS parameter analyzer, equipped with I - V, C - V and pulse measurement units. A Cascade 12000 semi-automatic probestation with a 200 °C hotchuck enabled full wafer statistical measurements. The threshold voltage ( $V_t$ ) was mapped across the wafer by using constant current (CC) method, with the threshold current ( $I_t$ ) set to 1 nA with a drain-source voltage ( $V_{ds}$ ) of 1 V. The CC method gives somewhat higher  $V_t$  than C - V based estimation, but lower than other I - V based estimates. Effective mobility ( $\mu_{eff}$ ) is estimated by using split C - V and pulsed I - V. Density of interface traps ( $D_{IT}$ ) was estimated by frequency dependent charge pumping, as outlined in [32].

### **III. RESULTS**

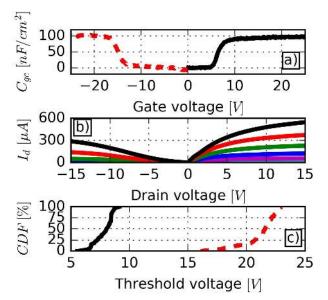

The inversion capacitance and  $\mu_{eff}$  were measured at both room temperature (RT) and at 200 °C (HT), as seen in Fig. 2. The C - V curve shifts to lower voltages, indicating  $V_t$ shift of ~3.7 V. The slope becomes steeper at HT, indicating lower amount of active traps. The estimated  $\mu_{eff}$  increases with increasing field and increasing temperature, indicating Coulomb scattered limited mobility. The transistors have clear depletion/inversion behavior at both RT and HT, as seen in Fig. 2a) and 3a). The inversion capacitance corresponds to a capacitance equivalent thickness (CET) of ~35 nm. This thickness is appropriate for 2  $\mu$ m gate length devices [14], [33]. The estimated  $\mu_{eff}$  at HT is relatively low,  $\leq 1$  cm<sup>2</sup>/Vs. It is comparable to previous results with steam oxidation [12].

The NMOS transistors have normal long channel output behavior at HT, as seen in Fig. 3b).  $V_t$  median is 8.0 V and the sample standard deviation is 0.8 V, with the cumulative distribution function (CDF) shown in Fig. 3c).

The PMOS output characteristics, shown in Fig. 3b), show some non-linearity at low drain voltages. This makes it difficult to estimate the mobility since the drain conductance cannot be determined from such data. Compared to the NMOS devices the saturation is also less clear. Physical device simulations confirm that both an overetch for the channel recess, as well as a non-conformal gate oxide thickness at the source/drain sidewalls and recess corners result in degraded subthreshold slope (not shown), higher  $V_t$  and non-linear/saturating output characteristics. A challenge with this process is to optimize both the PMOS and NMOS at the same time, since the etch

Fig. 3. PMOS and NMOS (100 × 2) transistors, measured at HT. a)  $C_{gc} - V_g$  measured at 100 kHz, 30 mV (RMS). The PMOS (dashed) enters invertison at -14.8 V, and the NMOS (solid) at 6 V. b)  $I_d - V_d$ .  $|V_{gs}|$  from 15 V to 25 V in steps of 2 V. PMOS is on left-hand side, NMOS on right-hand side. The mismatched current is due to mismatched  $V_t$ . c) CDF of  $|V_t|$ , estimated by CC method ( $|I_t| = 1$  nA). The NMOS  $|V_t|$ (solid) has a median of 8.0 V and an interquartile range (IQR, range within 25–75 %) of 1.2 V. The PMOS  $|V_t|$  (dashed) is higher than the NMOS, with an median of 21.6 V and a IQR of 1.4 V. The best PMOS (lowest  $|V_t|$ ) is shown in a) and b).

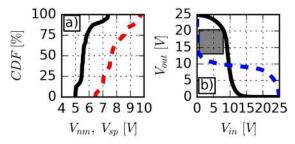

Fig. 4. Inverters measured at HT. a) CDF of  $V_{nm}$  (solid) and  $V_{sp}$  (dashed). b) Inverter transfer characteristics.  $V_{nm}$  is estimated by fitting the largest square inside the transfer curve (solid) and its transposed curve (dashed), with the length of the side of the square being the estimated  $V_{nm}$  [33, ch. 5].

variations accumulate for the last processed transistor. Even small etch variations can have significant impact for recessed channel SiC devices [25].  $|V_t|$  is very high, see 3c), with the median 21.6 V and the sample standard deviation is 1.6 V.

$D_{IT}$  was measured by charge pumping at HT. The estimated median and sample standard deviation of  $D_{IT}$  is 2.4 × 10<sup>12</sup> cm<sup>-2</sup> eV<sup>-1</sup> and 0.25 × 10<sup>12</sup> cm<sup>-2</sup> eV<sup>-1</sup>, respectively.  $D_{IT}$  is high but not unreasonable for non-optimized SiC gate oxide process. The high  $D_{IT}$  contributes to Coulomb scattering and reduce the observed mobility [34]. This low temperature and short oxidation time with steam may give higher  $D_{IT}$  than high temperature and long oxidation time [35].

The inverters (PMOS to NMOS width ratio was 60  $\mu$ m/ 40  $\mu$ m, channel length 2  $\mu$ m for both) were mapped across the wafer at HT. 25 out of the 52 (48%) inverters provided a voltage output swing  $\geq$ 90% of the power supply (25 V). The distribution of estimated noise margin voltages ( $V_{nm}$ ) and switching point voltage ( $V_{sp}$ ) is shown in Fig. 4a).

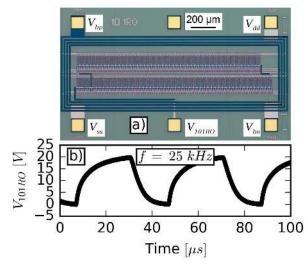

Fig. 5. Ring oscillator. a) Photograph of a 101-stage RO. It occupies an area of 0.95 mm  $\times$  1.7 mm (1.615 mm<sup>2</sup>). The circuit was designed to use four power supplies ( $V_{bp}$ ,  $V_{dd}$ ,  $V_{ss}$ ,  $V_{bn}$ ) to allow adjustable  $V_t$ . This feature was not used in this measurement ( $V_{bp} = V_{dd} = 25$  V,  $V_{ss} = V_{bn} = 0$  V). b) Oscillation at HT of a 101-stage RO. The frequency (f) is 25 kHz.

The medians are 5.5 V and 7.5 V, respectively (22% and 30% of the power supply, respectively).  $V_{nm}$  and  $V_{sp}$  can be improved (closer to 50 %) by reducing the PMOS  $V_t$  to be closer to the NMOS  $V_t$ . The transfer curve itself of the best inverter found (highest  $V_{nm}$ ) is shown in Fig. 4b).

101-stage ROs (PMOS to NMOS width ratio was 60  $\mu$ m/10  $\mu$ m, channel length 2  $\mu$ m for both) were measured at HT to determine if the within-die yield was sufficiently high for circuit applications. A 101-stage RO is shown in Fig. 5a) and the oscillating signal is shown in Fig. 5b). While the pull-up was not strong enough to achieve full swing (25 V), the RO was oscillating, indicating that all 206 transistors (2 × 101 from the RO and 2 × 2 from the two-step output buffer) were operational.

The tested ROs oscillated for a few minutes before permanently breaking. It is likely that the power supply (25 V) is too high for reliable operation, since the maximum electric field of the gate dielectric exceeds >6 MV/cm [36]. Given previous results in the literature [14], [36], 10.5–14 V would provide adequate reliability. The PMOS transistors require targeted process improvement in order to reduce  $|V_t|$  below 10.5 V.

# **IV. CONCLUSIONS**

A recessed channel CMOS process in SiC technology has been demonstrated. This process does not require ion implantation, and the highest process temperature is 1050 °C (gate oxidation). Conformal gate oxide is strongly required to get recessed channel transistors with adequate performance, which prohibits the use of long time and high temperature gate oxidation processes and requires deposited SiO<sub>2</sub>-film with post-deposition annealing. Inverters and ring oscillators have been demonstrated to be operational at 200 °C. The most important improvement required for this process is to reduce the PMOS  $V_t$  below 10 V for the intended gate oxide thickness (35 nm), as this would allow the CMOS circuits to operate at 10 V power supply in order to ensure long-term reliability.

#### REFERENCES

- P. G. Neudeck, R. S. Okojie, and L.-Y. Chen, "Hightemperature electronics—A role for wide bandgap semiconductors?" *Proc. IEEE*, vol. 90, no. 6, pp. 1065–1076, Jun. 2002. doi: 10.1109/JPROC.2002.1021571.

- [2] M. Masunaga, S. Sato, A. Shima, and R. Kuwana, "The performance of operational amplifiers consisting of 4H-SiC CMOS after gamma irradiation," *IEEE Trans. Electron Devices*, vol. 66, no. 1, pp. 343–348, Jan. 2019. doi: 10.1109/TED.2018.2877846.

- [3] L. Lanni, B. G. Malm, M. Östling, and C.-M. Zetterling, "500 °C bipolar integrated OR/NOR gate in 4H-SiC," *IEEE Electron Device Lett.*, vol. 34, no. 9, pp. 1091–1093, Sep. 2013. doi: 10.1109/LED.2013.2272649.

- [4] C.-M. Zetterling, A. Hallén, R. Hedayati, S. Kargarrazi, L. Lanni, B. G. Malm, S. Mardani, H. Norström, A. Rusu, S. S. Suvanam, Y. Tian, and M. Östling, "Bipolar integrated circuits in SiC for extreme environment operation," *Semicond. Sci. Technol.*, vol. 32, no. 3, Feb. 2017, Art. no. 034002. doi: 10.1088/1361-6641/aa59a7.

- [5] M. Shakir, H. Elahipanah, R. Hedayati, and C.-M. Zetterling, "Electrical characterization of integrated 2-input TTL NAND gate at elevated temperature, fabricated in bipolar SiCtechnology," *Mater. Sci. Forum*, vol. 924, pp. 958–961, 2018. doi: 10.4028/www.scientific.net/MSF.924.958.

- [6] M. Shakir, S. Hou, B. G. Malm, M. Östling, and C.-M. Zetterling, "A 600 °C TTL-based 11-stage ring oscillator in bipolar silicon carbide technology," *IEEE Electron Device Lett.*, vol. 39, no. 10, pp. 1540–1543, Oct. 2018. doi: 10.1109/LED.2018.2864338.

- [7] M. Alexandru, V. Banu, X. Jordà, J. Montserrat, M. Vellvehi, D. Tournier, and J. Millán, and P. Godignon, "SiC integrated circuit control electronics for high-temperature operation," *IEEE Trans. Ind. Electron.*, vol. 62, no. 5, pp. 3182–3191, May 2015. doi: 10.1109/TIE.2014.2379212.

- [8] J.-F. Mogniotte, D. Tournier, C. Raynaud, M. Lazar, D. Planson, and B. Allard, "Silicon carbide technology of MESFET-based power integrated circuits," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 6, no. 2, pp. 539–548, Jun. 2018. doi: 10.1109/JESTPE.2017.2778002.

- [9] D. J. Spry, P. G. Neudeck, L. Chen, D. Lukco, C. W. Chang, and G. M. Beheim, "Prolonged 500 °C demonstration of 4H-SiC JFET ICs with two-level interconnect," *IEEE Electron Device Lett.*, vol. 37, no. 5, pp. 625–628, May 2016. doi: 10.1109/LED.2016.2544700.

- [10] M. Kaneko and T. Kimoto, "High-temperature operation of n- and pchannel JFETs fabricated by ion implantation into a high-purity semiinsulating SiC substrate," *IEEE Electron Device Lett.*, vol. 39, no. 5, pp. 723–726, May 2018. doi: 10.1109/LED.2018.2822261.

- [11] P. G. Neudeck, L. Chen, R. D. Meredith, D. Lukco, D. J. Spry, L. M. Nakley, and G. W. Hunter, "Operational testing of 4H-SiC JFET ICs for 60 days directly exposed to Venus surface atmospheric conditions," *IEEE J. Electron. Devices Soc.*, vol. 7, pp. 100–110, Dec. 2018. doi: 10.1109/JEDS.2018.2882693.

- [12] M. Okamoto, M. Iijima, T. Yatsuo, K. Fukuda, and H. Okumura, "Effect of doping concentration in buried-channel NMOSFETs on electrical properties of 4H-SiC CMOS devices," *Mater. Sci. Forum*, vols. 645–648, pp. 995–998, Apr. 2010. doi: 10.4028/www.scientific.net/MSF.645-648.995.

- [13] M. Albrecht, T. Erlbacher, A. J. Bauer, and L. Frey, "Potential of 4H-SiC CMOS for high temperature applications using advanced lateral p-MOSFETs," *Mater. Sci. Forum*, vol. 858, pp. 821–824, May 2016. doi: 10.4028/www.scientific.net/MSF.858.821.

- [14] M. H. Weng, D. T. Clark, S. N. Wright, D. L. Gordon, M. A. Duncan, S. J. Kirkham, M. I. Idris, H. K. Chan, R. A. R. Young, E. P. Ramsay, N. G. Wright, and A. B. Horsfall, "Recent advance in high manufacturing readiness level and high temperature CMOS mixed-signal integrated circuits on silicon carbide," *Semicond. Sci. Technol.*, vol. 32, no. 5, 2017. Art. no. 054003. doi: 10.1088/1361-6641/aa61de.

- [15] V. Soler, M. Cabello, V. Banu, J. Montserrat, J. Rebollo, and P. Godignon, "Complementary p-channel and n-channel SiC MOSFETs for CMOS integration," *Mater. Sci. Forum*, vol. 924, pp. 975–979, Jun. 2018. doi: 10.4028/www.scientific.net/MSF.924.975.

- [16] K. Nomura, Y. Kondo, T. Kawae, and A. Morimoto, "Effects of SrRuO<sub>3</sub> layer on retention properties of (Bi,Pr)(Fe,Mn)O<sub>3</sub> film capacitor at high temperature," *ECS Solid State Lett.*, vol. 4, no. 5, pp. N1–N4, Jan. 2015. doi: 10.1149/2.0031505ssl.

- [17] M. Ekström, S. Khartsev, M. östling, and C.-M. Zetterling, "Integration and high-temperature characterization of ferroelectric vanadium-doped bismuth titanate thin films on silicon carbide," *J. Electron. Mater.*, vol. 46, no. 7, pp. 4478–4484, Jul. 2017. doi: 10.1007/s11664-017-5447-3.

- [18] M. Noborio, J. Suda, S. Beljakowa, M. Krieger, and T. Kimoto, "4H-SiC MISFETs with nitrogen-containing insulators," *Phys. Status Solidi A*, vol. 206, no. 10, pp. 2374–2390, Oct. 2009. doi: 10.1002/pssa.200925247.

- [19] M. Cabello, V. Soler, G. Rius, J. Montserrat, J. Rebollo, and P. Godignon, "Advanced processing for mobility improvement in 4H-SiC MOSFETs: A review," *Mater. Sci. Semicond. Process.*, vol. 78, pp. 22–31, May 2018. doi: 10.1016/j.mssp.2017.10.030.

- [20] M. Noborio, J. Suda, and T. Kimoto, "P-channel MOSFETs on 4H-SiC 0001 and nonbasal faces fabricated by oxide deposition andN<sub>2</sub>Oannealing," *IEEE Trans. Electron Devices*, vol. 56, no. 9, pp. 1953–1958, Sep. 2009. doi: 10.1109/TED.2009.2025909.

- [21] M. Okamoto, M. Tanaka, T. Yatsuo, and K. Fukuda, "Effect of the oxidation process on the electrical characteristics of 4H–SiC p-channel metal-oxide-semiconductor field-effect transistors," Appl. Phys. Lett., vol. 89, no. 2, May 2006, Art. no. 023502. doi: 10.1063/ 1.2221400.

- [22] A. Hallén and M. Linnarsson, "Ion implantation technology for silicon carbide," *Surf. Coat. Technol.*, vol. 306, pp. 190–193, Nov. 2016. doi: 10.1016/j.surfcoat.2016.05.075.

- [23] S. Scharnholz, O. Hellmund, J. Stein, B. Spangenberg, and H. Kurz, "Remote PECVD oxide utilized in U-MOS structures and different MOSFETs on SiC," *Mater. Sci. Forum*, vols. 353–356, pp. 651–654, Jan. 2001. doi: 10.4028/www.scientific.net/MSF.353-356.651.

- [24] B. G. Malm, H. Elahipanah, A. Salemi, and Östling, "Gated base structure for improved current gain in SiC bipolar technology," in *Proc.* 47th Eur. Solid-State Device Res. Conf., Sep. 2017, pp. 122–125. doi: 10.1109/ESSDERC.2017.8066607.

- [25] T. Kurose, S. Kuroki, S. Ishikawa, T. Maeda, H. Sezaki, T. Makino, T. Ohshima, M. Östling, and C.-M. Zetterling, "Low-parasiticcapacitance self-aligned 4H-SiC nMOSFETs for harsh environment electronics," *Mater. Sci. Forum*, vol. 924, pp. 971–974, Jun. 2018. doi: 10.4028/www.scientific.net/MSF.924.971.

- [26] (Jan. 31, 2019). Norstel AB, Norrköping, Sweden. Accessed: Mar. 8, 2019. [Online]. Available: http://www.norstel.com

- [27] R. Pascu, C. Romanitan, P. Varasteanu, and M. Kusko, "A reliable technology for advanced SiC-MOS devices based on fabrication of high quality silicon oxide layers by converting a-Si," *IEEE J. Electron Devices Soc.*, vol. 7, pp. 58–167, Dec. 2018. doi: 10.1109/JEDS.2018. 2886373.

- [28] Y. Song, S. Dhar, L. C. Feldman, G. Chung, and J. R. Williams, "Modified deal grove model for the thermal oxidation of silicon carbide," *J. Appl. Phys.*, vol. 95, no. 9, pp. 4953–4957, 2004. doi: 10.1063/1.1690097.

- [29] H. Elahipanah, A. Asadollahi, M. Ekström, A. Salemi, C.-M. Zetterling, and M. Östling, "A wafer-scale Ni-salicide contact technology on n-type 4H-SiC," *ECS J. Solid State Sci. Technol.*, vol. 6, no. 4, pp. 197–200, Mar. 2017. doi: 10.1149/2.0041705jss.

- [30] M. Ekström, S. Hou, H. Elahipanah, A. Salemi, M. Östling, and C.-M. Zetterling, "Low temperature Ni-Al ohmic contacts to p-type 4H-SiC using semi-salicide processing," *Mater. Sci. Forum*, vol. 924, pp. 389–392, Jun. 2018. doi: 10.4028/www.scientific.net/ MSF.924. 389.

- [31] R. S. Okojie and D. Lukco, "Pt:Ti diffusion barrier, interconnect, and simultaneous ohmic contacts to n- and p-type 4H-SiC," *Mater. Sci. Forum*, vol. 924, pp. 381–384, Jun. 2018. doi: 10.4028/www. scientific.net/MSF.924.381.

- [32] G. Groeseneken, H. E. Maes, and N. Beltran, and R. F. De Keersmaecker, "A reliable approach to charge-pumping measurements in MOS transistors," *IEEE Trans. Electron Devices*, vol. 31, no. 1, pp. 42–53, Jan. 1984. doi: 10.1109/T-ED.1984.21472.

- [33] Y. Taur and T. K. Ning, Fundamentals of Modern VLSI Devices, 2nd ed. Cambridge, U.K.: Cambridge Univ. Press, 2009.

- [34] E. Arnold and D. Alok, "Effect of interface states on electron transport in 4H-SiC inversion layers," *IEEE Trans. Electron Devices*, vol. 48, no. 9, pp. 1870–1877, Sep. 2001. doi: 10.1109/16. 944171.

- [35] D. Okamoto, H. Yano, T. Hatayama, Y. Uraoka, and T. Fuyuki, "Analysis of anomalous charge-pumping characteristics on 4H-SiC MOSFETs," *IEEE Trans. Electron Devices*, vol. 55, no. 8, pp. 2013–2020, Aug. 2008. doi: 10.1109/TED.2008.926639.

- [36] L. C. Yu, G. T. Dunne, K. S. Matocha, K. P. Cheung, J. S. Suehle, and K. Sheng, "Reliability issues of SiC MOSFETs: A technology for high-temperature environments," *IEEE Trans. Device Mater. Rel.*, vol. 10, no. 4, pp. 418–426, Dec. 2010. doi: 10.1109/TDMR.2010. 2077295.