# High voltage DC-DC converter using a series stacked topology

P.D. van Rhyn

Thesis presented in partial fulfilment of the requirements for the degree of Master of Engineering at the University of Stellenbosch

Supervisor: Prof. H. du Toit Mouton

April 2006

### **DECLARATION**

I, the undersigned, hereby declare that the work contained in the thesis is my own original work, unless otherwise stated, and has not previously, in its entirety or in part, been submitted at any university for a degree.

| Signature: _ |   |   |  |

|--------------|---|---|--|

|              |   |   |  |

| Date:        | / | / |  |

#### **SUMMARY**

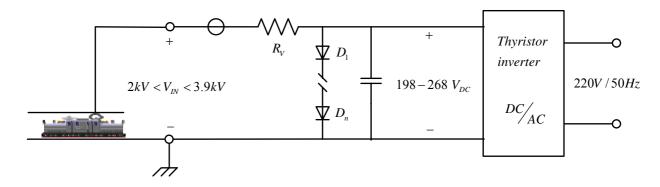

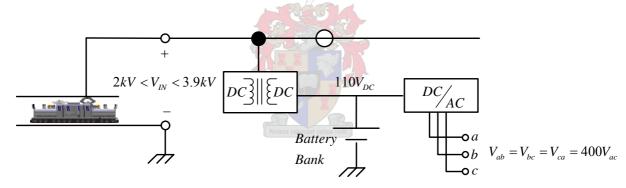

This thesis presents the design and implementation of a high voltage DC-DC converter using a series stacked topology. The converter's specifications were set by Spoornet and the converter forms part of a DC-AC inverter to be installed in Spoornet substations. Different converter topologies will be considered. A high frequency, high power coaxially wound transformer will be analysed, designed and manufactured for this specific converter application. A thermal analysis of the transformer will be carried out. The merits of different control schemes, leading to the choice of an average current mode controller, will be discussed. This controller will be designed and implemented to control the converter. The converter is then simulated to test and verify the controller functionality. A two-level series stacked converter is built and tested to verify the converter design and to test the functionality of the coaxially wound transformer. Finally, the results obtained will be discussed.

#### **OPSOMMING**

Hierdie tesis handel oor die ontwerp en implimentering van 'n hoë-spanning GS-GS omsetter deur gebruik te maak van serie-gekoppelde topologie. Die omsetter se spesifikasies is vasgestel deur Spoornet en die omsetter vorm deel van 'n GS-WS omsetter wat binne Spoornet sub-stasies geinstalleer gaan word. Verskillende omsetter-topologië sal oorweeg word. 'n Hoë-frekwensie, hoë drywing, koaksiaal gewinde transformator sal geanaliseer, ontwerp en vervaardig word. 'n Termiese analiese sal op die transformator uitgevoer word. Verskillende beheermetodes sal oorweeg word wat lei tot die keuse van 'n gemiddelde stroom beheerder. Dié beheer metode sal in die omsetter geimplimenteer word. Die omsetter sal gesimuleer word om die werking van die beheerder te toets. 'n Twee-vlak omsetter is gebou om die werking van die omsetter en die werking van die kaoksiaal gewinde transformator te toets. Laastens word die resultate verkry deur die praktiese opstelling bespreek.

# **INDEX**

| CHAPTER 1          | PROJECT BACKGROUND                                                      | 1  |

|--------------------|-------------------------------------------------------------------------|----|

| 1.1 IN             | TRODUCTION                                                              | 1  |

|                    | ACKGROUND                                                               |    |

| 1.3 SY             | STEM REQUIREMENTS                                                       | 2  |

| 1.4 TH             | IESIS OVERVIEW                                                          | 4  |

| CHAPTER 2          | HIGH POWER DC-DC CONVERTERS                                             | 5  |

| 2.1 IN             | TRODUCTION                                                              | 5  |

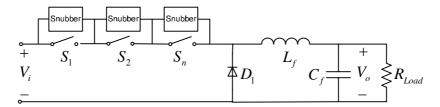

|                    | C-DC CHOPPERS.                                                          |    |

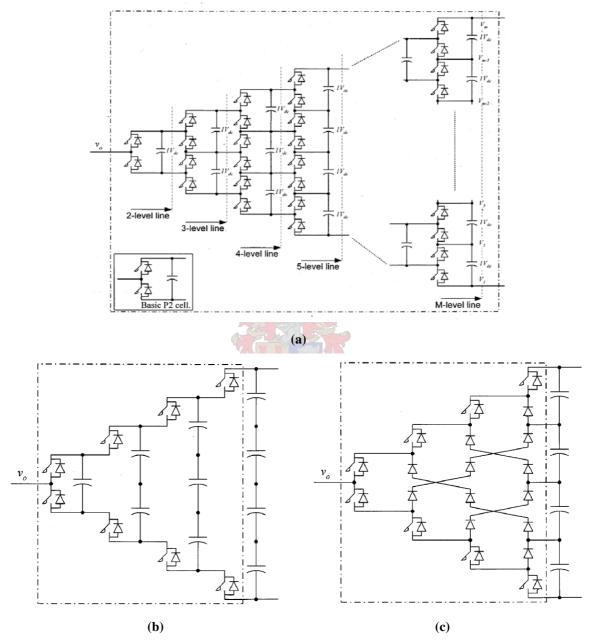

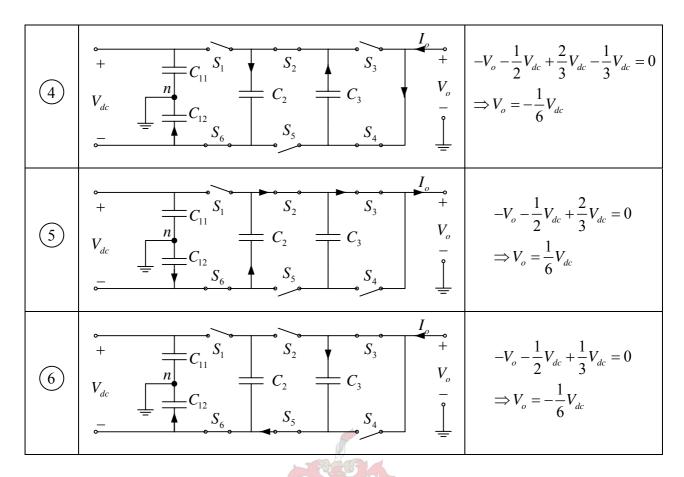

|                    | ULTILEVEL CONVERTERS                                                    |    |

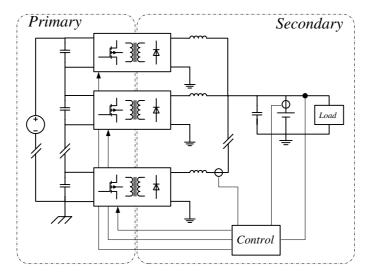

|                    | RIES OR PARALLEL CONNECTION OF CONVERTERS.                              |    |

|                    | HOOSING A TOPOLOGY                                                      |    |

| 2.5.1              | Flying capacitor topology                                               |    |

| 2.5.2              | Diode clamped topologiy                                                 |    |

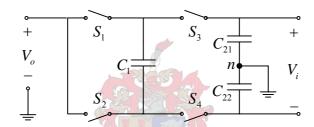

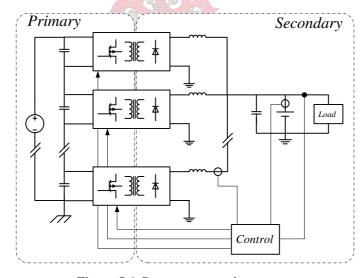

| 2.5.3              | Series stacked full-bridge topology                                     | 15 |

| 2.6 Su             | JMMARY                                                                  | 16 |

| CHAPTER 3          | HIGH FREQUENCY, COAXIALLY WOUND TRANSFORMER                             | 17 |

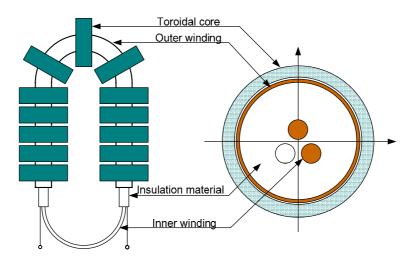

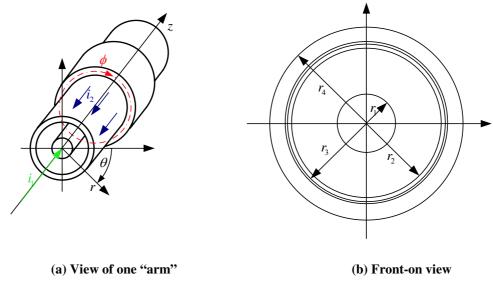

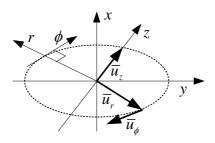

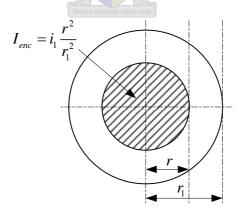

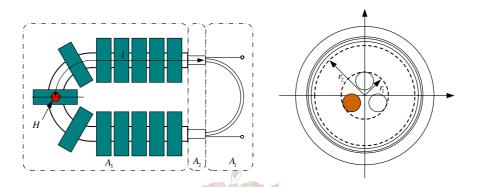

| 3.1 IN             | TRODUCTION                                                              | 17 |

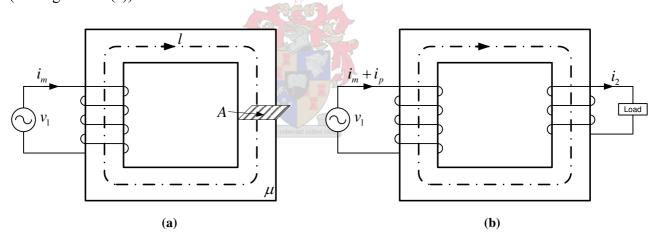

|                    | ONVENTIONAL TRANSFORMER                                                 |    |

| 3.2.1              | Operating principle                                                     |    |

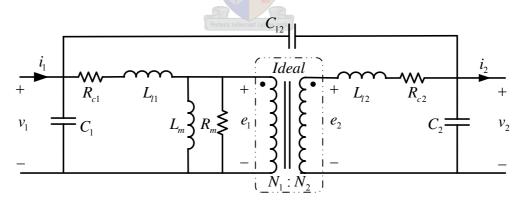

| 3.2.2              | Equivalent circuit analysis                                             |    |

| 3.3 Co             | DAXIALLY WOUND TRANSFORMER                                              | 20 |

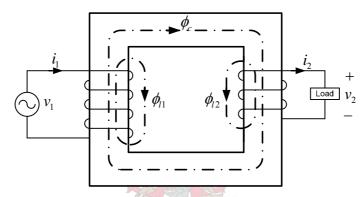

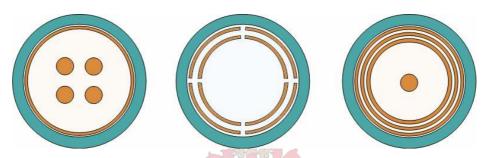

| 3.3.1              | Operating principle                                                     | 20 |

| 3.3.2              | Equivalent circuit analysis                                             | 22 |

| 3.3.2.             | 0                                                                       |    |

| 3.3.2.2            | T                                                                       |    |

|                    | OWER LOSS                                                               |    |

| 3.4.1.1<br>3.4.1.2 |                                                                         |    |

|                    | 4.1.2.1 DC resistance                                                   |    |

|                    | 4.1.2.2 AC resistance (Skin effect and Proximity effect)                |    |

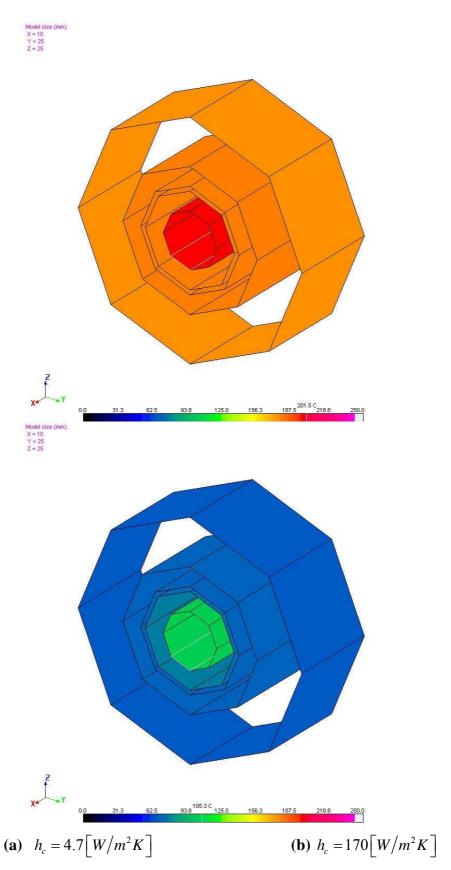

| 3.4.2              | Thermal analysis                                                        |    |

| 3.4.2.             |                                                                         |    |

| 3.4.2.2            | rr J &                                                                  |    |

|                    | ESIGN PROCESS                                                           |    |

| 3.5.1              | Design inputs                                                           |    |

| 3.5.2              | Core cross-sectional area                                               |    |

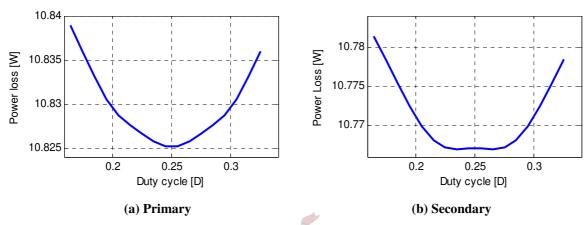

| 3.5.3              | Power loss                                                              |    |

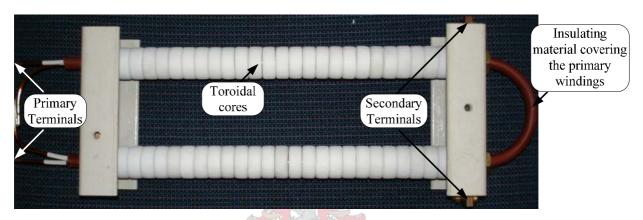

| 3.5.4<br>3.6 PR    | ACTICAL RESULTS                                                         |    |

|                    | JMMARY                                                                  |    |

| CHAPTER 4          |                                                                         |    |

|                    |                                                                         |    |

|                    | TRODUCTION                                                              |    |

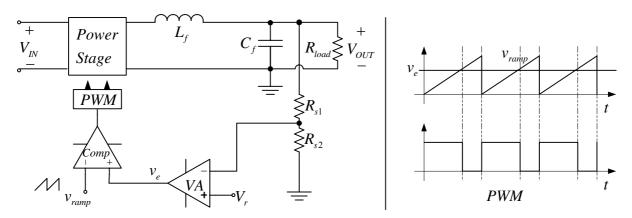

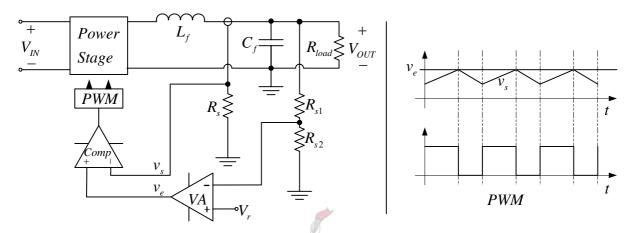

|                    | C-DC CONTROL SCHEMES                                                    |    |

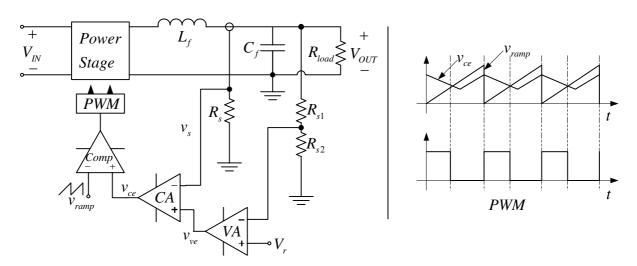

| 4.2.1              | Voltage mode control                                                    |    |

| 4.2.2<br>4.2.3     | Peak current mode control                                               |    |

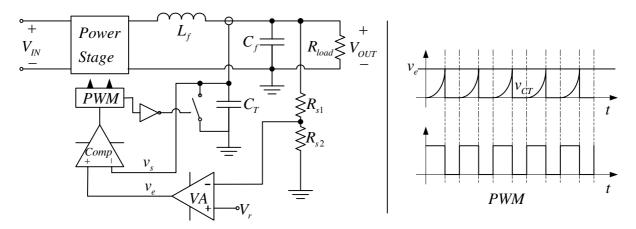

| 4.2.3<br>4.2.4     | Charge control                                                          |    |

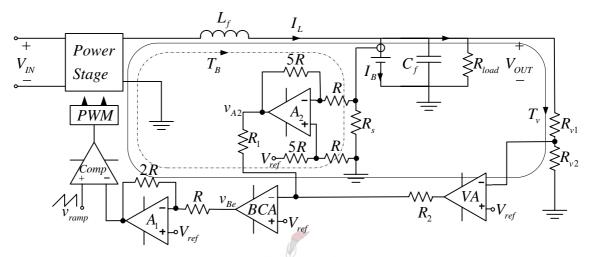

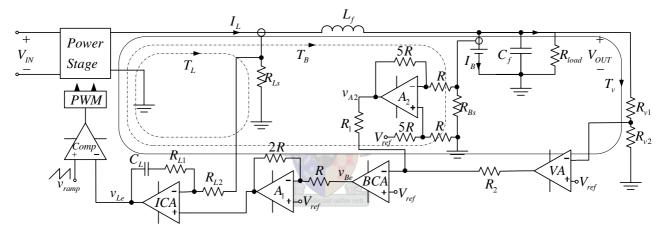

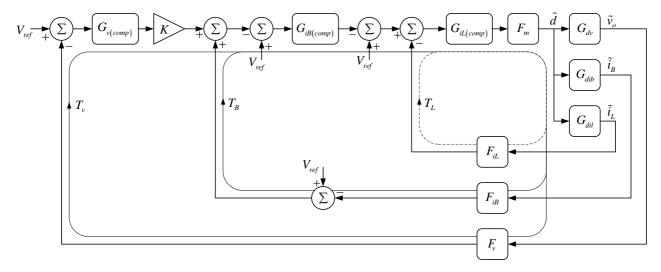

|                    | ONTROLLER IMPLEMENTATION                                                |    |

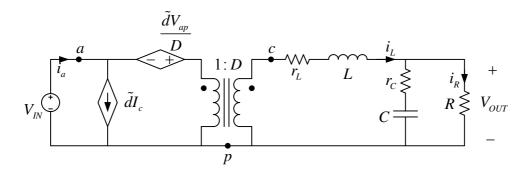

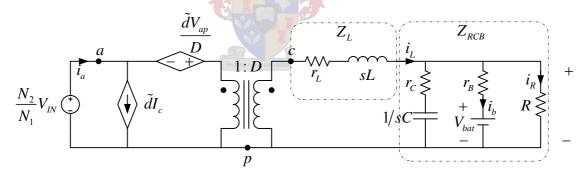

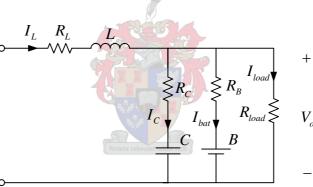

| 4.3.1              | Linnearisation of the power stage of the full-bridge converter topology |    |

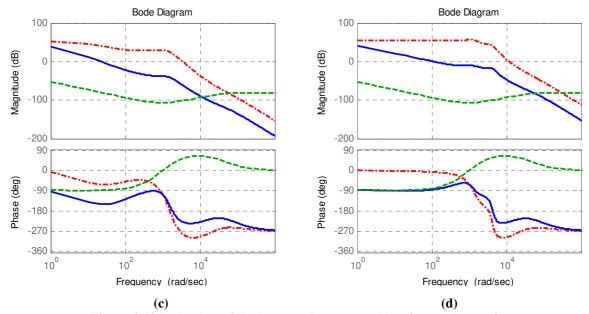

| 4.3.2              | Duty cycle to output voltage transfer function $G_{dv}(s)$              |    |

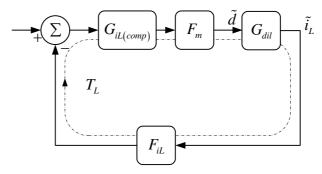

| 4.3.3              | Duty cycle to inductor current transfer function $G_{dil}(s)$           |    |

| 4.3.4          | Duty cycle to battery current transfer function $G_{dib} \left(s ight)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 56  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

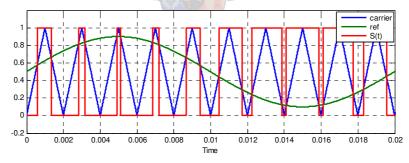

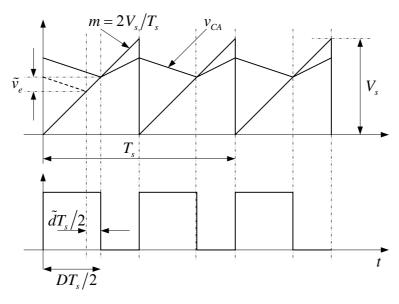

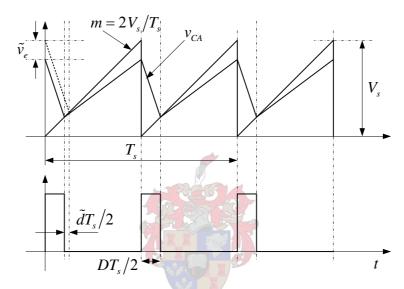

| 4.3.5          | Pulse width modulator transfer function $F_{_{m}}(s)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 56  |

| 4.3.0          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

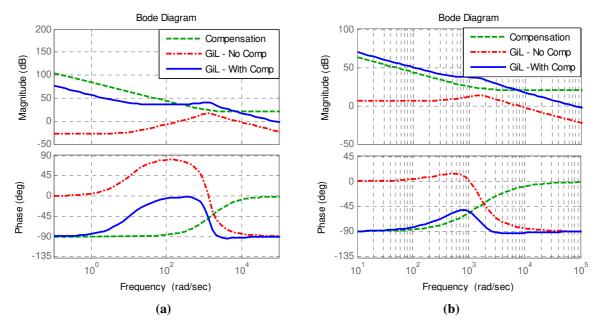

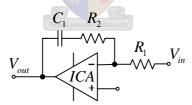

| 4.4            | Compensation design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| 4.4.           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

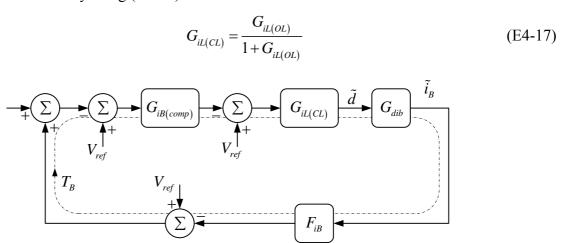

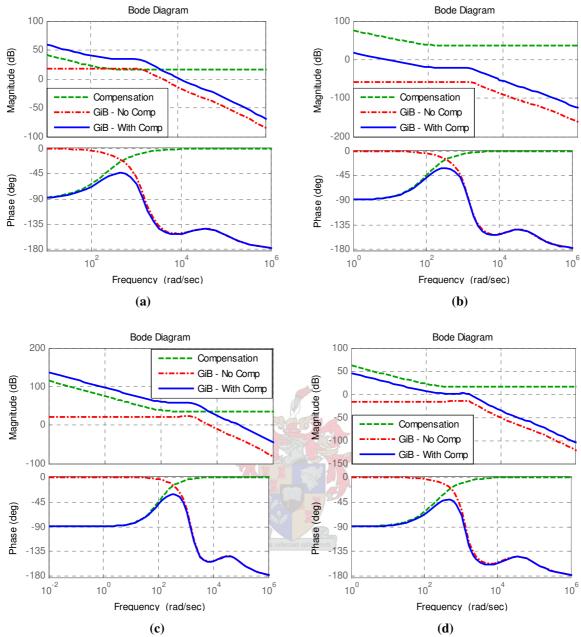

| 4.4.2          | Battery current control loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60  |

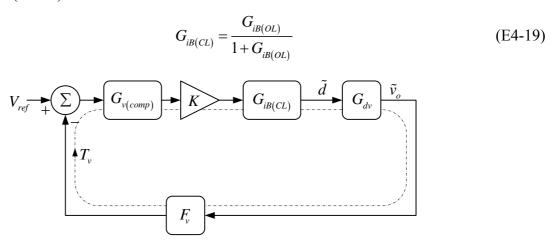

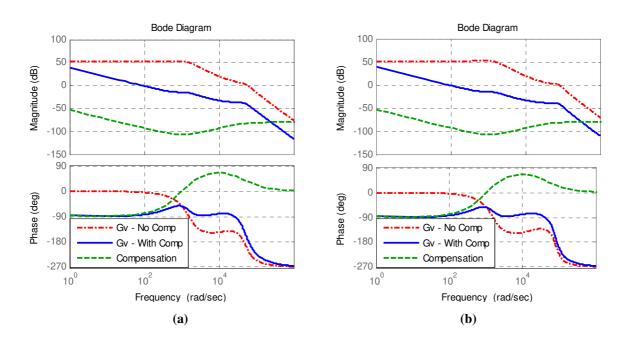

| 4.4.3          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 4.5            | CONTROLLER INPLEMENTATION – DIGITAL VS ANALOGUE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

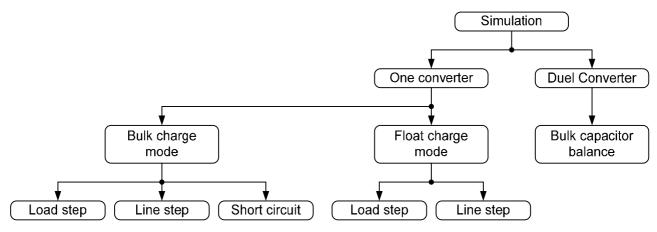

| 4.6            | SIMULATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

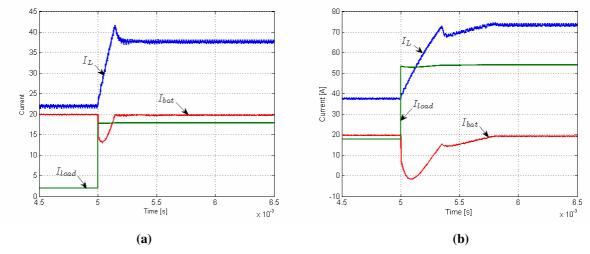

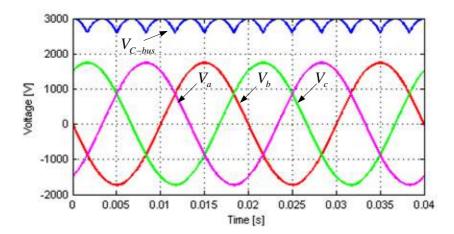

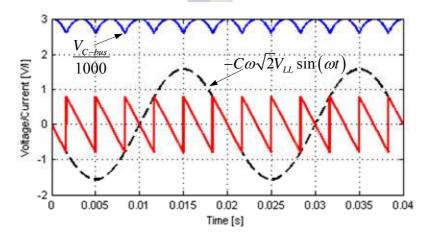

| 4.6.1          | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| 4.6.2          | O Company of the Comp |     |

| 4.6.3<br>4.6.4 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 4.7            | SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| ,<br>CHAPTE    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 5.1<br>5.2     | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 5.2.1          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 5.2.2          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

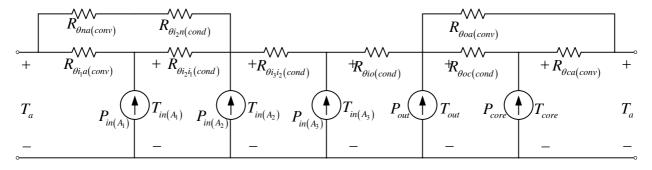

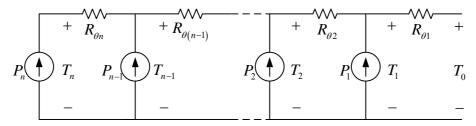

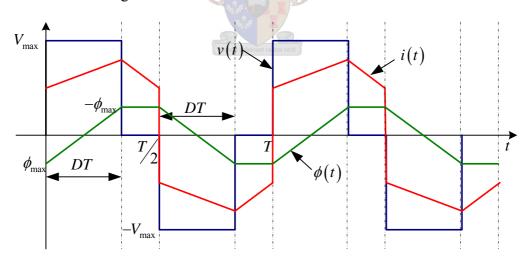

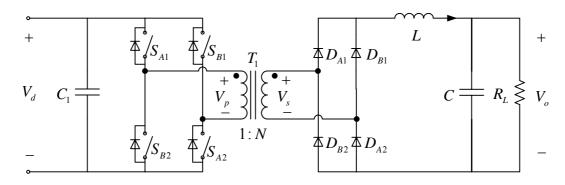

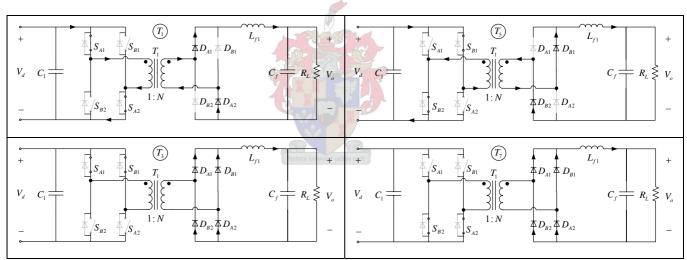

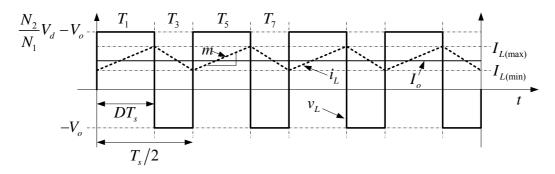

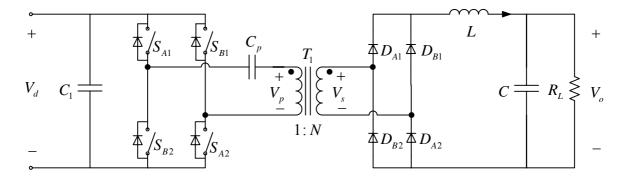

| 5.3            | FULL-BRIDGE CONVERTER OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

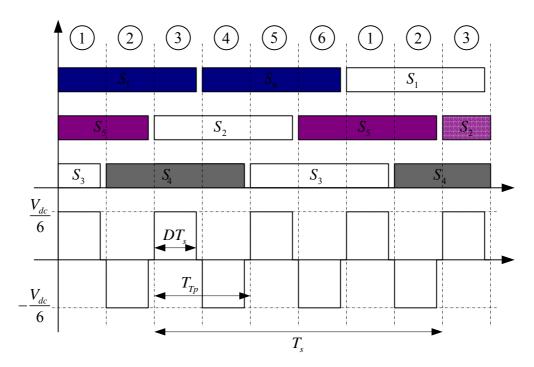

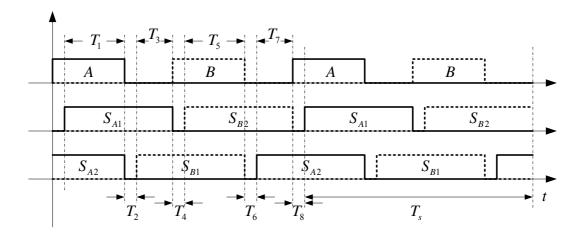

| 5.4            | SWITCHING STRATEGY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

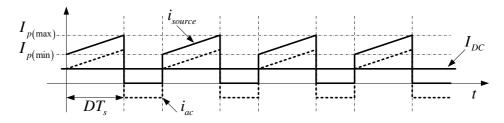

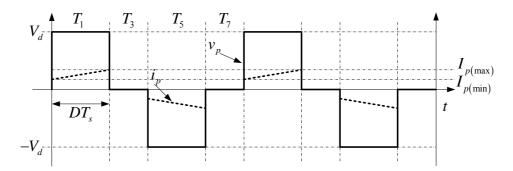

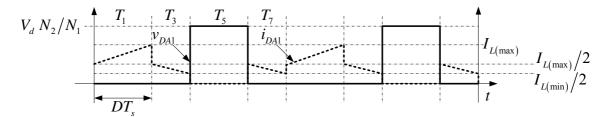

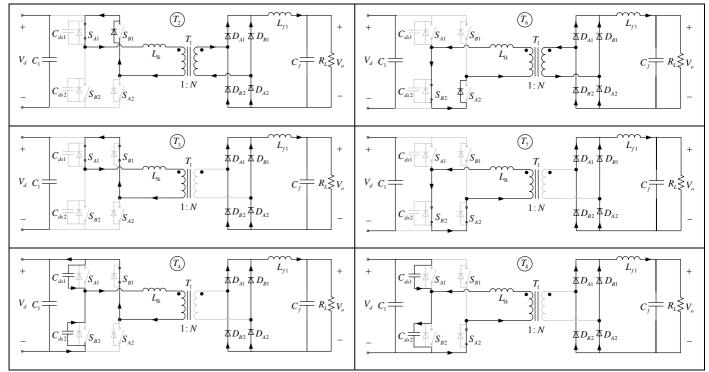

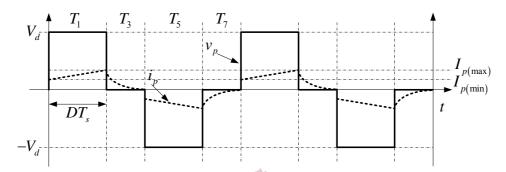

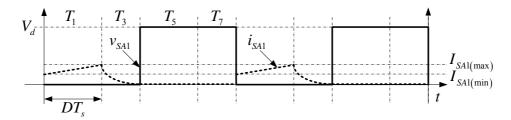

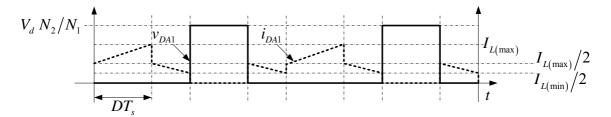

| 5.5            | OPERATING STATES AND CIRCUIT WAVEFORMS – IDEAL CASE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

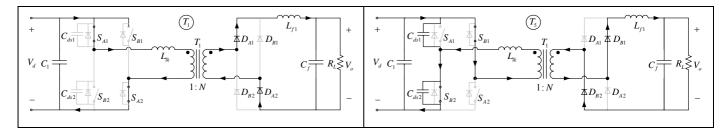

| 5.6            | OPERATING STATES AND CIRCUIT WAVEFORMS – NON-IDEAL CASE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

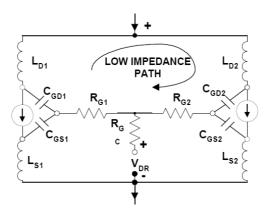

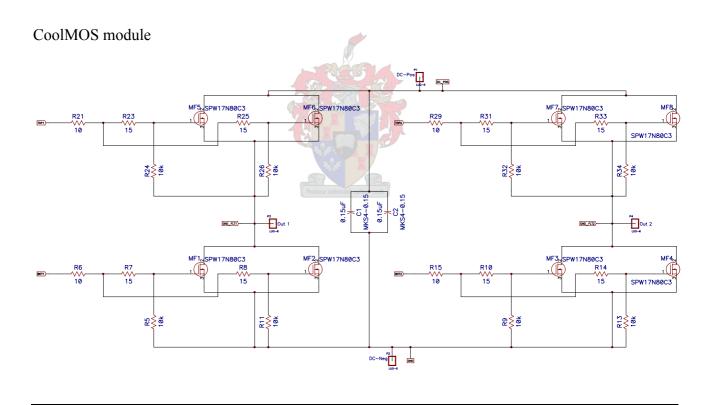

| 5.7            | PARALLELING OF POWER MOSFETS AND DIODES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 5.8            | POWER LOSS CALCULATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 5.9            | HEAT SINK DESIGN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 94  |

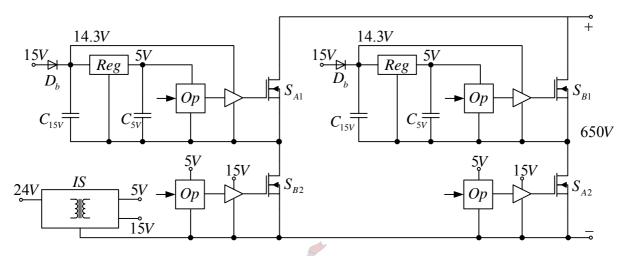

| 5.10           | DRIVER CIRCUITRY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| 5.10           | .1 MOSFET gate resistance and dead time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 97  |

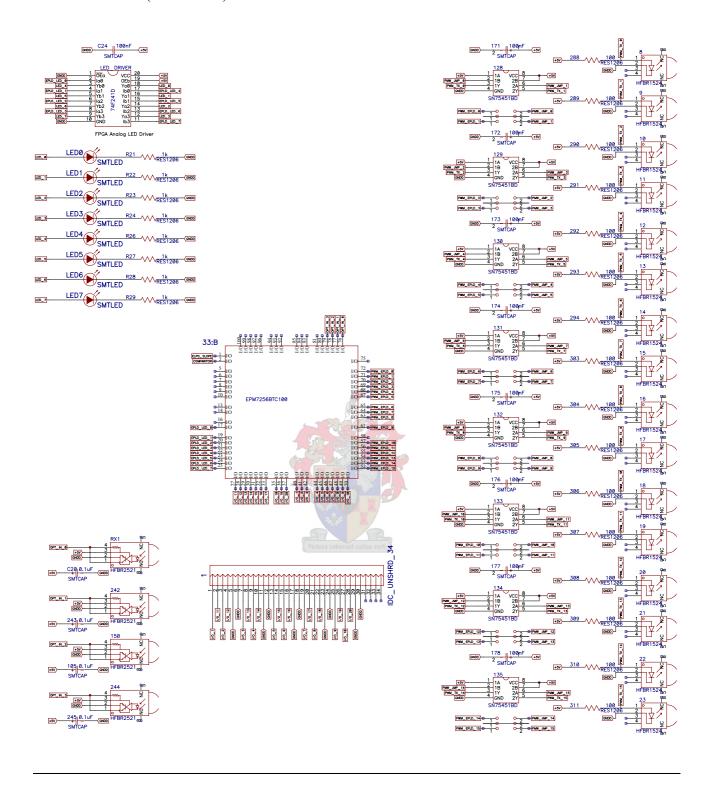

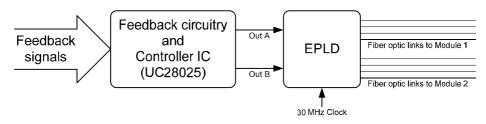

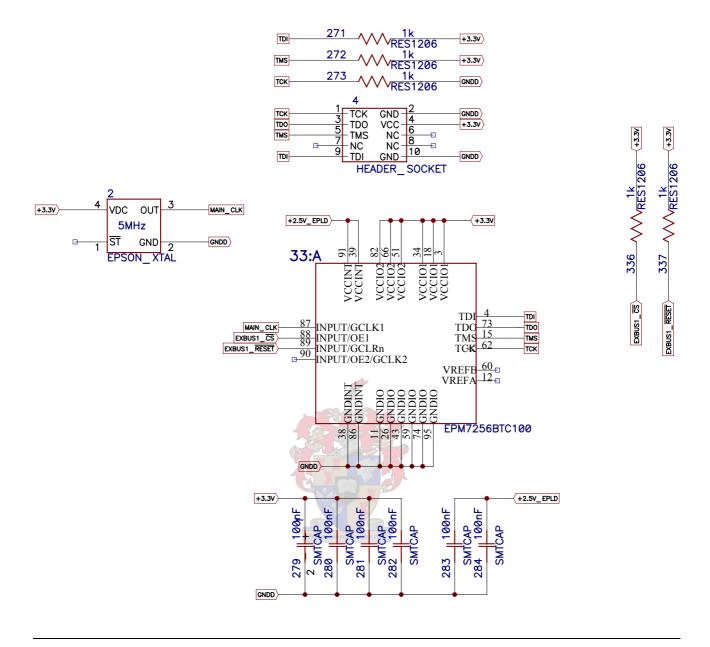

| 5.11           | CONTROLLER BOARD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

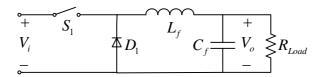

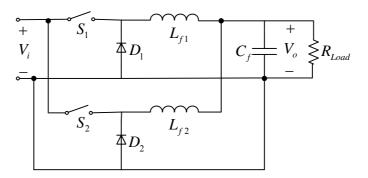

| 5.12<br>5.13   | OUTPUT FILTER DESIGNISOLATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| 5.13           | DC CAPACITOR TO ELIMINATE CORE SATURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 5.14           | SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| CHAPTE         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 6.1            | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |