# High-Voltage Multilevel Converter With Regeneration Capability

José Rodríguez, *Senior Member, IEEE*, Luis Morán, *Senior Member, IEEE*, Jorge Pontt, *Member, IEEE*, Juan L. Hernández, *Senior Member, IEEE*, Leopoldo Silva, César Silva, *Student Member, IEEE*, and Pablo Lezana

Abstract—This paper presents a multilevel converter with regeneration capability. The converter uses several power cells connected in series, each working with reduced voltage and with an active front end at the line side. This paper presents the following: 1) the control method of each cell; 2) the use of phase-shifting techniques to reduce the current and voltage distortion; and 3) criteria to select the connection of the cells. The converter generates almost sinusoidal currents at the load and at the input and works with very high power factor.

Index Terms—Medium-voltage drives, multilevel converter, multilevel inverter, power converters.

#### I. Introduction

N RECENT YEARS, multilevel converters have presented an important development to reach higher power with increasing voltage levels [1]–[3]. A very attractive family of multilevel converter is the multicell configuration, which considers the series connection of several power cells, each one operating with reduced voltage [1], [4], [5].

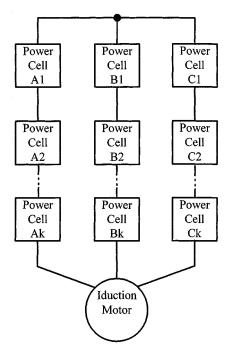

Fig. 1 shows a multicell voltage-source inverter, which is used very successfully in medium-voltage motor drives [4]. This inverter has shown the following in the field: reduced harmonics in the output voltage and in the input current, competitive cost, and an efficiency comparable with alternative converters. In this converter, each power cell includes a single-phase inverter at the output and a three-phase noncontrolled six-pulse rectifier at the input side. The presence of a diode rectifier with a capacitive filter generates important current harmonics at the input of each cell. These harmonics are reduced by introducing several phase-shifted secondaries in the input transformer, resulting in a more complicated construction and higher cost. In addition, the diode rectifier does not permit the regeneration of power from the load to the source.

This paper presents the development of a regenerative cell, which allows a bidirectional power flow between load and source. Modulation and control techniques have been devel-

Manuscript received September 21, 2001; revised December 30, 2001. Abstract published on the Internet May 16, 2002. This work was supported by the Chilean Research Fund (CONICYT) under Grant 1990837, Grant 1980463, and Grant 1010096 and by the Universidad Técnica Federico Santa María. This paper was presented at the 30th IEEE Power Electronics Specialists Conference (PESC'99), Charleston, SC, June 27–July 1, 1999.

- J. Rodríguez, J. Pontt, J. L. Hernández, L. Silva, C. Silva, and P. Lezana are with the Departamento de Electronica, Universidad Técnica Federico Santa María, Valparaiso, Chile (e-mail: jrp@elo.utfsm.cl; jpo@elo.utfsm.cl).

- L. Morán is with the Departamento de Ingenieria Eléctrica, Universidad de Concepción, Concepción, Chile.

Publisher Item Identifier 10.1109/TIE.2002.801238.

Fig. 1. Power circuit of a multicell inverter.

oped to minimize the distortion in the load current and in the input current of the converter.

#### II. POWER CIRCUIT OF THE REGENERATIVE CONVERTER

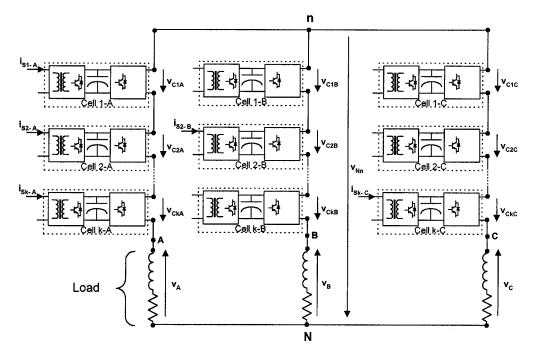

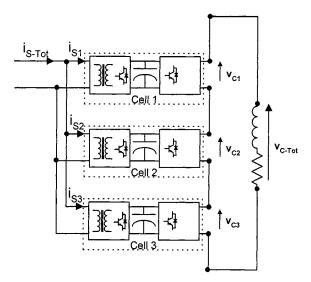

Fig. 2 shows the power circuit of the three-phase regenerative converter, having three or more cells per phase. Each cell works with reduced voltage. Higher voltages can be reached by connecting a higher number of cells in series.

Each cell contains a single-phase inverter at the output side and a pulsewidth-modulated (PWM) rectifier at the input side. The output side inverters of the cells are connected in series, while the input side rectifiers are connected in parallel through the input transformer.

#### III. POWER CIRCUIT OF THE REGENERATIVE CELL

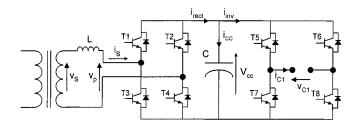

Fig. 3 shows the power circuit of the regenerative cell, which includes the following:

- 1) secondary of the input transformer;

- 2) filter inductance *L*;

- 3) PWM rectifier composed of T1, T2, T3, and T4;

Fig. 2. Power circuit of the multilevel regenerative converter.

Fig. 3. Power circuit of the regenerative cell.

- 4) dc-link filter capacitor C;

- 5) output single-phase inverter composed of T5, T6, T7, and T8

The regenerative cell has the input voltage  $v_s$ , the input current  $i_s$ , and delivers the output voltage  $v_{C1}$ . The inverter and the input rectifier allow the power to flow in both directions between load and source and, consequently, the cell has regeneration capability.

A single-phase active front end (AFE), instead of a threephase one, has been considered at the input side of each cell for the following reasons: 1) less power semiconductors and 2) simpler control.

## IV. CONTROL OF A CELL

#### A. Control of the Output Inverter

The control of the inverter at the output must fulfill the following requirements.

- 1) It must deliver three voltages:  $+V_{\rm cc}$ , 0, and  $-V_{\rm cc}$ . In this way, the addition of the output voltages of the different cells will generate a higher number of levels and, consequently, a reduction in the distortion of the load current.

- 2) The carrier signal of the modulator must be synchronized with the carrier signals of the other cells, to reduce the dis-

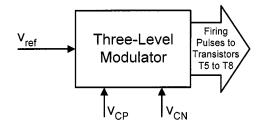

Fig. 4. Three-level modulator.

tortion of the load current. The phase-shifting technique will be used to achieve this goal [2], [6].

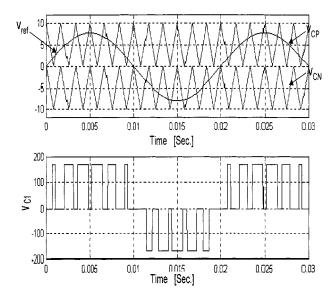

Fig. 4 shows the basic structure of the three-level modulator, which receives the modulating or reference signal  $v_{\rm ref}$  and two carrier signals  $v_{\rm CP}$  and  $v_{\rm CN}$ . The modulator delivers the firing pulses for transistors T5–T8.

Fig. 5 shows the waveforms used to explain the modulation principle applied to generate a three-level output voltage. The modulation scheme uses two vertically shifted carrier signals: the positive carrier  $v_{\rm CP}$  and the negative carrier  $v_{\rm CN}$ , as shown in Fig. 5.

The modulation principle works as follows.

- 1) If  $v_{\text{ref}} \ge 0$  and  $v_{\text{ref}} \ge v_{\text{CP}}$ , then  $v_{C1} = +V_{\text{cc}}$ .

- 2) If  $v_{\rm ref} \geq 0$  and  $v_{\rm ref} < v_{\rm CP}$ , then  $v_{C1} = 0$ .

- 3) If  $v_{\text{ref}} < 0$  and  $v_{\text{ref}} > v_{\text{CN}}$ , then  $v_{C1} = 0$ .

- 4) If  $v_{\rm ref} < 0$  and  $v_{\rm ref} \le v_{\rm CN}$ , then  $v_{C1} = -V_{\rm cc}$ .

## B. Control of the PWM Rectifier

The PWM rectifier must fulfill the following requirements.

1) The voltage  $v_p$  must have three levels:  $+V_{\rm cc}$ , 0, and  $-V_{\rm cc}$ . For a given switching frequency, a PWM rectifier with three levels has less current distortion than a two-level rectifier using only  $+V_{\rm cc}$  and  $-V_{\rm cc}$ .

Fig. 5. Generation of the three-level voltage at the output of each cell.

Fig. 6. Control system of the PWM rectifier.

2) The commutations of the several rectifiers must be synchronized when they are connected in parallel through the transformer. In this way, an important reduction of the ripple in the input current will be obtained. This is achieved by using the phase-shifting technique of the carrier signals [2], [6], [8].

Fig. 6 shows the block diagram of the control system for the PWM rectifier. The three-level modulator used to generate the three-level voltage  $v_p$  at the input of the rectifier is the same used for the output inverter. In Fig. 6, PI-1 is the proportional—integral controller for the capacitor voltage  $V_{\rm cc}$  and PI-2 is the proportional—integral controller used to control the input current  $i_s(t)$ . The control strategy of the PWM single phase input rectifier is well known and is explained with more detail in [7].

#### C. Power Balance in One Cell

At the output of the cell, the voltage  $v_{C1}$  has a fundamental component  $v_{C1f}(t)$  and a fundamental current  $i_{C1f}(t)$ . For these components, the instantaneous output power is

$$P_{\text{out}}(t) = v_{C1f}(t) \cdot i_{C1f}(t)$$

$$= \widehat{V}_{C1f} \sin(\omega_{\text{out}}t) \cdot \widehat{I}_{C1f} \sin(\omega_{\text{out}}t + \varphi)$$

$$= \frac{\widehat{V}_{C1f} \cdot \widehat{I}_{C1f}}{2} \cdot \cos(\varphi)$$

$$- \frac{\widehat{V}_{C1f} \cdot \widehat{I}_{C1f} \cdot \cos(2\omega_{\text{out}}t)}{2} \cdot \cos(\varphi)$$

$$+ \frac{\widehat{V}_{C1f} \cdot \widehat{I}_{C1f} \cdot \sin(2\omega_{\text{out}}t)}{2} \cdot \sin(\varphi) \qquad (1)$$

Fig. 7. Voltage and current at the output of a cell with an output frequency of 50 Hz.

where  $\omega_{\rm out}$  is the output angular frequency of the cell  $(\omega_{\rm out}=2\pi f_{\rm out})$ . The output power  $P_{\rm out}$  will be delivered by the single phase source and by the dc-link filter capacitor C. Consequently, the voltage of the filter capacitor  $V_{\rm cc}$  will have a component of frequency  $2\cdot\omega_{\rm out}$  in addition to a component of  $2\cdot\omega_{\rm in}$ , where  $\omega_{\rm in}$  is the frequency of the single-phase source.

The amplitude of the input current  $i_s(t)$  will be modulated by the frequency  $2 \cdot \omega_{\rm out}$ . This means that the input current  $i_s(t)$  will have harmonics of frequencies  $\omega_{\rm in} + 2 \cdot \omega_{\rm out}$  and  $\omega_{\rm in} - 2 \cdot \omega_{\rm out}$ . The  $2\omega_{\rm in}$  harmonic present in the dc-link voltage will pass through the PI-1 controller and will be multiplied by  $v_s$ , originating a harmonic of frequency  $3\omega_i$  in the reference current  $i_s^*$ . If the dc-link capacitor is large enough and/or the bandwidth of PI-1 is not too wide, this last harmonic can be reduced. Additionally to these low frequency harmonics, the input current  $i_s$  will have a ripple originated by the switching frequency of the transistors of the PWM rectifier.

## V. PERFORMANCE OF THE CONVERTER

## A. Behavior of a Single Cell

The behavior of a single cell has been studied under the following conditions:

source:  $v_s(t) = \sqrt{2} \cdot 110 \cdot \sin(2\pi 50t)$ ; filters: L = 12 mH, C = 5 mF; load:  $L_{\rm load} = 10$  mH,  $R_{\rm load} = 30~\Omega$ ; switching frequency inverter: 2.5 kHz; switching frequency rectifier: 2.5 kHz; dc-link voltage:  $V_{\rm cc} = 170~{\rm V}$ .

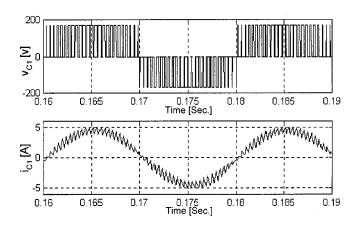

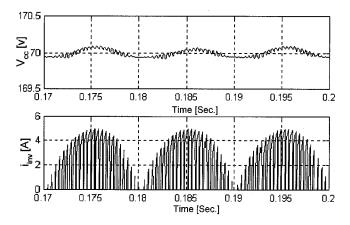

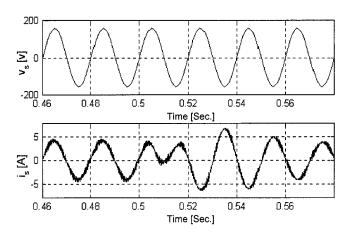

Fig. 7 shows the voltage  $v_{C1}$  and the load current, when the load frequency has a value of  $f_{\rm out}=50$  Hz. Fig. 8 shows the behavior of the dc-link voltage  $V_{\rm cc}$  and current  $i_{\rm inv}$  for the same conditions of Fig. 7.

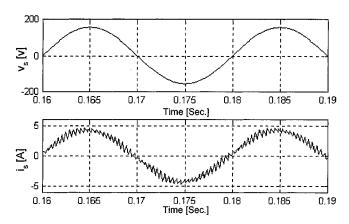

Fig. 9 presents the voltage and the current at the input of the cell, for the same conditions of Fig. 7. The input current  $i_s$  is approximately sinusoidal and in phase with the source voltage  $v_s$ . The frequency of the single-phase mains is  $f_{\rm in} = 50$  Hz.

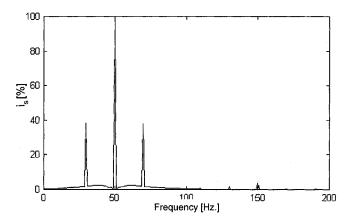

Fig. 10 shows the voltage  $v_s$  and current  $i_s$  at the input of the cell, when the output inverter generates a sinusoidal current of frequency  $f_{\rm out}=10$  Hz. In this case, the input current  $i_s$  has low-frequency harmonics of frequencies  $f_{\rm in}+2\cdot f_{\rm out}=10$

Fig. 8. Voltage and current in the dc link with an output frequency of 50 Hz.

Fig. 9. Voltage and current at the input of the cell with an output frequency of 50 Hz.

Fig. 10. Voltage and current at the input of the cell with an output frequency of 10 Hz.

$50 + 2 \cdot 10 = 70$  Hz and  $f_{\text{in}} - 2 \cdot f_{\text{out}} = 50 - 2 \cdot 10 = 30$  Hz. This is confirmed in the frequency spectrum shown in Fig. 11.

Fig. 12 shows the behavior of the cell when the active power reverses its direction. In the regenerating mode, the input current  $i_s$  is  $180^{\rm o}$  out of phase with respect to the source voltage  $v_s$  and has a sinusoidal waveform.

## B. Series Connection of the Cells

The circuit of Fig. 13 was used to study the behavior of series-connected cells. The objective of the modulation is to re-

Fig. 11. Frequency spectrum of current  $i_s$  shown in Fig. 10.

Fig. 12. Change in the direction of power flow in one cell.

Fig. 13. Three cells in series connection.

duce, as much as possible, the distortion in the load voltage and current, working with a reduced switching frequency. The carrier signals were shifted to minimize the distortion of the load voltage  $v_{C-Tot}$ .

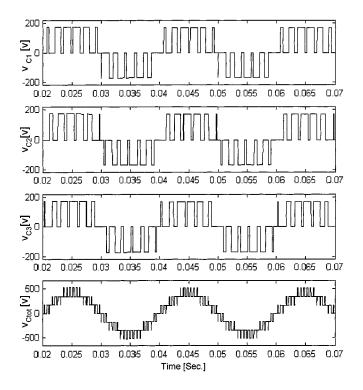

Fig. 14 shows the voltages of the different cells and the total voltage  $v_{\rm C-Tot}$  applied to the load when the carrier signals of the different cells have a phase displacement of 120 degrees.

Fig. 14. Voltages of three cells in series connection with carriers having  $120^{\circ}$  of phase displacement (switching frequency of inverters = 600 Hz).

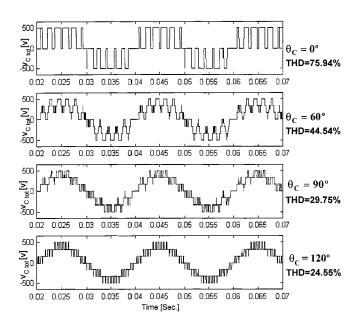

Fig. 15. Total voltage of three cells in series connection for different phase displacement in the carriers.

Fig. 15 shows the behavior of the total voltage  $v_{\rm C-Tot}$  for different displacement angles  $\theta_C$  between the carriers of the cells. The optimum displacement angle is

$$\theta_{Copt.} = \frac{360^{\circ}}{\text{Number of cells}} = \frac{360^{\circ}}{3} = 120^{\circ}.$$

(2)

This value is confirmed in Fig. 15.

Fig. 16. Input currents of the cells in Fig. 2, with an output frequency of  $f_{\rm out}=20$  Hz, according to connection of (3).

#### C. Parallel Connection of the Input Rectifiers

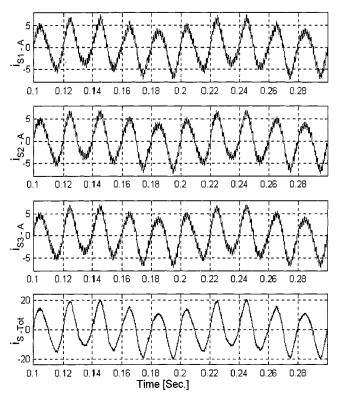

The operation of the PWM rectifiers at the input of the different cells must be synchronized to achieve a reduction of the ripple in the total input current, for a given switching frequency. In relation to the circuit of Fig. 2, when the PWM rectifiers of three cells connected in series are connected to the same phase of the power supply, the resulting current is

$$i_{S-Tot} = i_{S1-A} + i_{S2-A} + i_{S3-A}.$$

(3)

This is the case when the PWM rectifiers corresponding to one phase of the load are connected to the same phase of the source through secondary windings of the input transformer. The three-level modulators of the rectifiers use carrier signals shifted in  $120^{\circ}$  to reduce the ripple in the total input current  $i_{\rm S-Tot}$ .

Fig. 16 presents the input currents of the circuit shown in Fig. 2, when the rectifiers are connected according to (3) and the cells deliver a sinusoidal current of  $f_{\rm out}=20$  Hz to the load. Each rectifier operates with a switching frequency of 800 Hz. The total current  $i_{\rm S-Tot}$  is almost free of ripple, confirming the efficacy of the phase-shifting technique. However, the total input current has a low-frequency distortion, due to the modulation generated by the frequency of the load current.

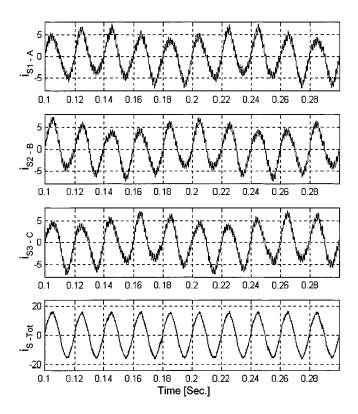

This problem can be avoided by using a different arrangement in the parallel connection of the input rectifiers. As a matter of fact, (1) shows that the components of frequency  $2 \cdot f_{\text{out}}$  present in the output power will have a displacement of  $120^{\circ}$  for the different phases of the load. Consequently, the components of

Fig. 17. Input currents of the cells in Fig. 2, with an output frequency of  $f_{\rm out}=20~{\rm Hz}$ , according to connection of (4).

frequency  $f_{\rm in} \pm 2 \cdot f_{\rm out}$  present in the input current can be eliminated by connecting in parallel rectifiers corresponding to cells of different load phases.

In the converter of Fig. 2, with three cells per phase, cells 1-A, 1-B, and 1-C have the same carrier signals  $v_{\rm CP}$  and  $v_{\rm CN}$ . On the other hand, cells 2-A, 2-B and 2-C have the same carrier signals, but shifted in 120° with respect to cells 1-A, 1-B, and 1-C. The same concept is valid for cells 3-A, 3-B, and 3-C. The PWM rectifiers of cells 1-A, 2-B, and 3-C are connected to the same phase of the source, so that the total input current  $(i_{\rm s-Tot})$  is

$$i_{S-Tot} = i_{S1-A} + i_{S2-B} + i_{S3-C}.$$

(4)

With this arrangement, the high-frequency ripple is reduced and the low-frequency harmonics of frequency  $2 \cdot f_{\rm out}$  are eliminated from the total input current  $i_{\rm S-Tot}$ . This is confirmed by the results shown in Fig. 17, obtained for an output frequency of 20 Hz, with the arrangement given by (4).

# VI. EXPERIMENTAL RESULTS

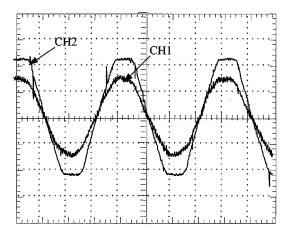

The power circuit of one cell shown in Fig. 3 has been studied experimentally, connected to an ac voltage of 46 V, 50 Hz. The cell was controlled using the Hitachi SH7045F microcontroller. The capacitor of the cell is  $C=3\,\mathrm{mF}$  and the dc-link voltage is 100 V.

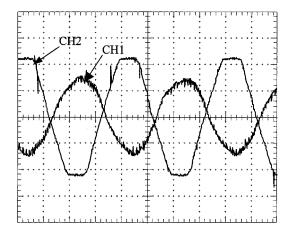

Fig. 18 shows the input current  $i_s$  and the voltage  $v_s$  of the cell with the power flowing from the ac power supply. Fig. 19 shows the waveforms in the regeneration mode.

Fig. 18. Motoring mode wafeforms of  $i_s$  (CH1 5 A/div) and  $v_s$  (CH2 25 V/div).

Fig. 19. Regeneration mode, wafeforms of  $i_s$  (CH1 5 A/div) and  $v_s$  (CH2 25 V/div).

## VII. COMMENTS AND CONCLUSION

The aim of this investigation has been to study some basic principles related to the operation of a multicell inverter with regeneration capability.

A very simple modulation principle has been presented to achieve three-level operation in a single-phase cell. The operation with carrier signals of fixed frequency allows the synchronization of several cells. The use of the phase-shifting technique for the carrier signals of the different cells in series connection produces a significant reduction in the distortion of the resulting voltage.

In addition, the effective switching frequency of the load voltage is n times the switching frequency of each cell, where n is the number of series-connected cells. This results in a a more sinusoidal load current.

On the other hand, the same three-level modulation principle has been used at the input PWM rectifier of the cell. The phase-shifting principle for the carrier signals is also very effective for the reduction of ripple in the total input current of PWM rectifiers operating in parallel. The resulting input current has a significantly reduced ripple, even though the fundamental components of the input current in the different cells have different instantaneous values.

The results of this work have been obtained with a large dc-link capacitor. A smaller filter capacitor makes the solution more realistic, reducing size and cost, but it will make the selection of the controller parameters more critical. This is an important subject for future research.

Low-frequency harmonics in the input current of the threephase converter can be totally eliminated by connecting the cells properly. The construction of the input transformer is drastically simplified in comparison to the transformer used in nonregenerative multicell converters.

The cancellation of the low-frequency harmonics in the current at the primary side of the input transformer as proposed in this paper can be obtained if the number of series-connected cells is a multiple of three. The operation of this method with two, four, or five cells in each phase is an interesting topic for future research work.

The resulting converter has reduced harmonics at the output and at the input and presents regeneration capability. In summary, the presented multilevel converter is an excellent alternative for medium-voltage regenerative drives.

#### REFERENCES

- J. S. Lai and F. Z. Peng, "Multilevel converters—A new breed of power converters," *IEEE Trans. Ind. Applicat.*, vol. 32, pp. 509–517, May/June 1996

- [2] B. Mwinyiwiwa, Z. Wolanski, Y. Chen, and B. T. Ooi, "Multimodular multilevel converters with imput/output linearity," *IEEE Trans. Ind. Applicat.*, vol. 33, pp. 1214–1219, Sept./Oct. 1997.

- [3] F. Z. Peng, J. McKeever, and D. J. Adams, "A power line conditioner using cascade multilevel inverter for distribution systems," in *Conf. Rec. IEEE-IAS Annu. Meeting*, 1997, pp. 1316–1321.

- [4] P. Hammond, "A new approach to enhance power quality for medium voltage AC drives," *IEEE Trans. Ind. Applicat.*, vol. 33, pp. 202–208, Jan./Feb. 1997.

- [5] G. Joos, X. Huang, and B. T. Ooi, "Direct-coupled multilevel cascaded series VAR compesators," in *Conf. Rec. IEEE-IAS Annu. Meeting*, 1997, pp. 1608–1615.

- [6] V. Agedelis and M. Calais, "Application specific harmonic performance evaluation of multicarrier PWM techniques," in *Proc. IEEE PESC'98*, 1998, pp. 172–178.

- [7] J. Rodríguez and E. Wiechmann, "High power factor rectifiers," in *Proc. European Power Electronics Conf. (EPE'95)*, 1995, pp. 2670–2676.

- [8] L. Li, D. Czarkowski, Y. Liu, and P. Pillay, "Multilevel selective harmonic elimination PWM technique in series-conected voltage inverters," in Conf. Rec. IEEE-IAS Annu. Meeting, 1998, pp. 1454–1461.

José Rodríguez (M'81–SM'94) received the Engineer degree from the Universidad Técnica Federico Santa María, Valparaiso, Chile, in 1977 and the Dr.-Ing. degree from the University of Erlangen, Erlangen, Germany, in 1985, both in electrical engineering.

Since 1977, he has been with the Universidad Técnica Federico Santa María, where he is currently a Professor and Head of the Department of Electronic Engineering. During his sabbatical leave in 1996, he was responsible for the Mining Division of Siemens

Corporation in Chile. He has extensive consulting experience in the mining industry, especially in the application of large drives like cycloconverter-fed synchronous motors for SAG mills, high-power conveyors, controlled drives for shovels, and power quality issues. His research interests are mainly in the areas of power electronics and electrical drives. Recently, his main research interests have been multilevel inverters and new converter topologies. He has authored or coauthored more than 100 refereed journal and conference papers and contributed to one chapter in *Power Electronics Handbook* (New York: Academic, 2001).

Luis Morán (S'79–M'81–SM'94) was born in Concepción, Chile. He received the Degree in electrical engineering from the University of Concepción, Concepción, Chile, in 1982, and the Ph.D. degree from Concordia University, Montreal, QC, Canada, in 1990

Since 1990, he has been with the Electrical Engineering Department, University of Concepción, where he is currently a Professor. He is also a Consultant for several industrial projects. His main areas of interests are in power quality, active power

filters, facts, and power protection systems. He has authored more than 20 papers on active power filters and static var compensators published in various IEEE TRANSACTIONS.

Prof. Morán was the principal author of the paper that received the IEEE Outstanding Paper Award from the Industrial Electronics Society for the best paper published in the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS during 1995. From 1997 to 2001, he was Associate Editor of the IEEE TRANSACTIONS ON POWER ELECTRONICS.

**Jorge Pontt** (M'00) received the Ing. and the Master of Electrical Engineering degrees from the Universidad Técnica Federico Santa María (UTFSM), Valparaíso, Chile, in 1977.

Since 1977, he has been a Professor in the at the Department of Electrical Engineering and Department of Electronics, UTFSM, He has had scientific stays in Germany at the Technische Hochschule Darmstadt (1979–1980), University of Wuppertal (1990), and University of Karlsruhe (2000–2001). Since 1980, he has been engaged in applied research

and consulting in industrial applications. His current research interests include harmonic analysis, power electronics, drives, and mineral processing.

**Juan L. Hernández** (M'86–SM'88) received the tittle of Civil Electrical Engineer from the Universidad Técnica Federico Santa María (UTFSM), Valparaiso, Chile, in 1952 and the Ph.D. degree in electrical engineering from the University of Pittsburgh, Pittsburgh, PA, in 1962.

He is an Emeritus Professor at UTFSM in the Department of Electronics. He has taught numerous undergraduate and graduate courses in electrical/electronics engineering and in the areas of automatics and control. He has authored more than 250 publications,

mostly in university magazines and congress proceedings. His present areas of interest are recent methods of automatics, of automatic control, and of computational intelligence.

Prof. Hernández is a member of several professional societies.

**Leopoldo Silva** received the Engineer degree in electronic engineering from the Universidad Técnica Federico Santa María (UTFSM), Valparaíso, Chile, in 1971.

He is currently a Full Professor in the Department of Electronics, UTFSM.

His main interests are digital systems, microprocessors, and teaching methods in engineering.

César Silva (S'01) was born in Temuco, Chile, in 1972. He received the Eng. degree in electronic engineering from the Universidad Técnica Federico Santa María, Valparaiso, Chile, in 1998. He is currently working toward the Ph.D. degree in the Power Electronics, Machines and Control Group, School of Electrical and Electronic Engineering, University of Nottingham, Nottingham, U.K.

His research interests include sensorless position control of PM machines, variable-speed ac motor drives, direct ac-ac power converters, and different

inverter circuit topologies.

Pablo Lezana is working toward the Magister degree at the Universidad Técnica Federico Santa María, Valparaiso, Chile.