### Purdue University Purdue e-Pubs

Birck and NCN Publications

Birck Nanotechnology Center

2-2010

# High-Voltage n-Channel IGBTs on Free-Standing 4H-SiC Epilayers

Xiaokun Wang Purdue University - Main Campus

James A. Cooper Birck Nanotechnology Center, Purdue University, james.a.cooper.1@purdue.edu

Follow this and additional works at: https://docs.lib.purdue.edu/nanopub Part of the <u>Nanoscience and Nanotechnology Commons</u>

Wang, Xiaokun and Cooper, James A., "High-Voltage n-Channel IGBTs on Free-Standing 4H-SiC Epilayers" (2010). *Birck and NCN Publications*. Paper 647. https://docs.lib.purdue.edu/nanopub/647

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

## High-Voltage n-Channel IGBTs on Free-Standing 4H-SiC Epilayers

Xiaokun Wang and James A. Cooper, Fellow, IEEE

Abstract—In this paper, we describe a process for fabricating high-voltage n-channel double-diffused metal–oxide– semiconductor insulated gate bipolar transistors (IGBTs) on free-standing 4H silicon carbide (SiC) epilayers. In this process, all critical layers are epitaxially grown in a continuous sequence. The substrate is then removed, and device fabrication takes place on the carbon face of a free-standing epilayer having a total thickness of about 180  $\mu$ m. For a drift layer with doping and thickness values capable of blocking 20 kV, the n-channel IGBT carries 27.3-A/cm<sup>2</sup> current at a power dissipation of 300 W/cm<sup>2</sup>, with a differential ON-resistance of 177 m $\Omega \cdot \text{cm}^2$ . To our knowledge, this is the first detailed report of device fabrication on free-standing SiC epilayers.

*Index Terms*—Free-standing epilayer, high voltage, insulated gate bipolar transistor (IGBT), silicon carbide (SiC).

#### I. INTRODUCTION

T HE RECENT emphasis on clean renewable energy and more efficient energy utilization has lead to renewed interest in distributed energy sources, hybrid electric vehicles, and intelligent power distribution grids, all of which require power semiconductor devices. In many of these applications, operating voltages are sufficiently high that complex multilevel converters are required if silicon power devices are used. Silicon carbide (SiC) devices are capable of operating at higher voltages than silicon, eliminating the need for multilevel circuits in many applications.

Since the early 1990s, the SiC power MOSFET has been the primary focus of research, and significant progress has been made. By 2004, the blocking voltage of SiC power MOSFETs had reached 10 kV, with specific ON-resistances as low as 123 m $\Omega \cdot \text{cm}^2$  [1]. However, the drift region resistance of MOSFETs increases as the square of the blocking voltage, and at high voltages, this resistance begins to limit the range of applications that can be addressed. As blocking voltages increase, the SiC insulated gate bipolar transistor (IGBT) becomes an attractive choice to replace the SiC MOSFET, particularly in low-frequency switching applications [2].

The authors are with the School of Electrical and Computer Engineering and Birck Nanotechnology Center, Purdue University, West Lafayette, IN 47907-2057 USA (e-mail: cooperj@purdue.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2009.2037379

In principle, n-channel IGBTs are preferred over p-channel IGBTs for their higher performance [2], but n-channel IGBTs require p-type substrates, which introduce a high resistance  $(0.8-1.0 \ \Omega \cdot cm^2)$  in series with the device. The first SiC n-IGBTs were reported in 1996 [3], but their performance was inferior to MOSFETs of that day because of the high substrate resistance. Recently, a 13-kV n-IGBT has been reported by Cree, Inc. [4], [5], but their paper does not discuss removal of the substrate and provides no details about the formation of the  $p^+$  collector region. To solve this problem, we have developed a novel inverted-growth process that, in principle, could allow all critical epilayers to be grown in a continuous sequence on an original growth substrate ( $\sim 400 \ \mu m$ ), which is subsequently removed by polishing. Continuous epigrowth has been shown to minimize basal plane dislocations that form at interrupted-growth interfaces and nucleate stacking faults during operation [6], [7]. In our process, device fabrication takes place on a free-standing epilayer with a total thickness of about 180  $\mu$ m. The thick p<sup>+</sup> substrate is replaced by a thin  $p^+$  epilayer, and the collector resistance is reduced by almost two orders of magnitude. The process is demonstrated by fabricating n-IGBTs on epilayers with doping and thickness values capable of blocking 20 kV. To our knowledge, this is the first detailed report of SiC devices fabricated on free-standing SiC epilayers.

#### **II. DEVICE DESIGN AND FABRICATION**

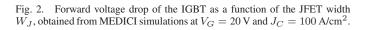

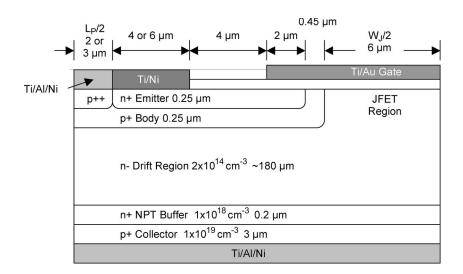

Fig. 1 shows a schematic cross section of the fabricated device. The junction field-effect transistor (JFET) region width  $W_J$  is selected based on the MEDICI simulations shown in Fig. 2. As the JFET width is reduced, the forward voltage increases due to the increasing resistance of the narrow JFET region. As shown, for  $W_J$  greater than 12  $\mu$ m, the forward voltage drop  $V_F$  is relatively constant; thus, we select  $W_J = 12 \ \mu$ m for these devices.

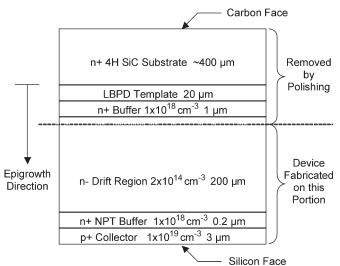

The epitaxial growth process is illustrated in Fig. 3. Starting wafers are 75 mm n<sup>+</sup> (8° off-axis) 4H-SiC substrates purchased from Cree, Inc. First, a low-basal-plane-defect (LBPD) template layer and a standard 1- $\mu$ m n<sup>+</sup> buffer layer are grown on the Si-face. Then, three layers are grown in succession: a 200- $\mu$ m 2 × 10<sup>14</sup> cm<sup>-3</sup> n<sup>-</sup> drift layer, a 0.2- $\mu$ m 1 × 10<sup>18</sup> cm<sup>-3</sup> n<sup>+</sup> nonpunchthrough buffer layer, and a 3- $\mu$ m 1 × 10<sup>19</sup> cm<sup>-3</sup> p<sup>+</sup> collector layer. This inverted-growth procedure makes it possible to continuously grow all critical layers, minimizing the introduction of basal plane dislocations during growth (however, continuous growth was not used for the

Manuscript received November 5, 2009. Current version published January 22, 2010. This work was supported by the Defense Advanced Research Project Agency (DARPA/Microsystems Technology Office) under Grant N00014-05-1-0437 through the Office of Naval Research. The review of this paper was arranged by Editor M. A. Shibib.

Fig. 1. Schematic cross section of one cell of the fabricated device.

T = 23 °C

15

20

10

JFET Width (µm)

5

devices reported here). The ambipolar lifetimes in the drift layer of two small pieces from one wafer are measured by microwave photoconductivity decay and time-resolved photoluminescence and are found to be greater than 1  $\mu$ s over large portions of the wafer. The n<sup>+</sup> substrate, LBPD layer, and n<sup>+</sup> buffer layer are then removed by polishing at NovaSiC, and the wafer is inverted, with the p<sup>+</sup> collector at the bottom and the n<sup>-</sup> blocking layer at the top. Devices are fabricated on the top surface (carbon face) of the n<sup>-</sup> drift layer, as illustrated in Fig. 3.

To produce a short-channel MOSFET, we use the selfaligned technique of Matin *et al.* [8], slightly adapted for the carbon face of SiC. First, 100 nm of silicon nitride is deposited by low-pressure chemical vapor deposition (LPCVD) at 825 °C to prevent the SiC from being oxidized in a later step. Then, a 1.5- $\mu$ m polysilicon layer is deposited by LPCVD at 600 °C and patterned by reactive ion etching in SF<sub>6</sub> using a Ti/Ni mask. This polysilicon layer serves as the mask for the p-well implantation. The p-well is formed by a retrograde implantation of Al at 650 °C with (doses/energies) of 2.7 × 10<sup>12</sup>/90, 3.1 ×

Fig. 3. Inverted-growth process. Epigrowth takes place on the Si-face of an  $n^+$  4H-SiC substrate. In principle, all layers can be grown in a continuous manner, minimizing basal plane dislocations that can nucleate stacking faults. After growth, the substrate, LPBD template, and  $n^+$  buffer layer are removed by polishing, and device fabrication takes place on the carbon face of the free-standing epilayers.

10<sup>12</sup>/140, 5.6 × 10<sup>13</sup>/360 (cm<sup>-2</sup>/keV), respectively. This is followed by a shallow implantation of nitrogen at 650 °C with a dose of  $8.8 \times 10^{12}$  cm<sup>-2</sup> and energy of 45 keV to reduce the threshold voltage. After the p-well and thresholdadjust implants, Ti/Ni is stripped, and the sample receives a 9-h wet oxidation at 1000 °C, which horizontally expands the polysilicon by about 0.45  $\mu$ m [8]. The expanded oxidized polysilicon and a separate optical Ti/Au p<sup>+</sup> block mask are used to define the n<sup>+</sup> emitter implantation. To form the emitter, nitrogen is implanted at 650 °C with (doses/energies) of (9.5 ×  $10^{14}/50$ ,  $1.4 \times 10^{15}/90$ ,  $2.0 \times 10^{15}/150$ ) (cm<sup>-2</sup>/keV). The MOS channel length is controlled by the horizontal expansion of the polysilicon implant mask and is around 0.45  $\mu$ m. After removing all layers from the SiC top surface, a Ti/Au layer is deposited, patterned, and used as the mask for the

16

14

12

10

8

6 4

2

0

0

Forward Voltage Drop (V)

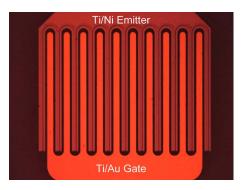

Fig. 4. Completed device. This device has ten fingers, with an active area of  $3.4 \times 10^{-4}$  cm<sup>2</sup>.

p<sup>+</sup> body-contact implantation. The body contact is formed by implanting Al at 650 °C with (doses/energies) of  $(1.0 \times 10^{14}/40, 2.0 \times 10^{14}/100, 4.0 \times 10^{14}/180)$  (cm<sup>-2</sup>/keV). All the implants are annealed in Ar for 30 min at 1600 °C under a graphite cap.

Following the implant anneal, the sample is oxidized in a pyrogenic system at 1100 °C for 20 min to form the gate oxide. A NO postoxidation anneal is then performed at 1175 °C for 70 min to reduce the interface trap density and improve the mobility [9]. The oxide thickness is around 45 nm after the NO anneal. We use a lower oxidation temperature and a shorter oxidation time on the carbon face because the oxidation rate is about ten times faster than on the silicon face.

Ohmic contacts are formed by depositing (33-nm Ti/ 167-nm Al/50-nm Ni) as the p<sup>+</sup> body contact and (33-nm Ti/ 167-nm Al/~100-nm Ni) on the back side as the p<sup>+</sup> collector contact. These metals are annealed in vacuum to form ohmic contacts. The target temperature for the p<sup>+</sup> contact anneal was 1000 °C, but the actual temperature reached during anneal is not precisely known due to equipment problems during annealing. However, as will be discussed in the next section, the annealed contacts are ohmic, suggesting that the peak temperature is well above 800 °C.

Emitter ohmic contacts and gates in these devices are formed using a modified fabrication sequence. In preliminary processing runs, we had observed high oxide leakage, thought to be caused by surface roughness from the implant anneals, which were uncapped in those runs. In this processing run, we wanted to preserve the option of subsequently depositing a thick low-temperature oxide (LTO) on top of the thermal oxide if the thermal oxide proved to be leaky. For this reason, we deposited a metal gate that could easily be removed to allow LTO deposition, if needed. Accordingly, (50-nm Ti/100-nm Ni) and (50-nm Ti/100-nm Au) are deposited and patterned as the n<sup>+</sup> emitter contact and the gate, respectively, and the emitter contacts are not annealed (previous experiments [10] had shown that unannealed Ti/Ni forms a low-resistance ohmic contact to a heavily doped  $n^+$  material). Because the implants were annealed under a graphite cap in this run, surface roughness was minimal, and probe testing indicated that the thermal gate oxides were not leaky. As a result, LTO deposition was not needed, and the devices were ready for characterization. Fig. 4 is a photograph of the finished device.

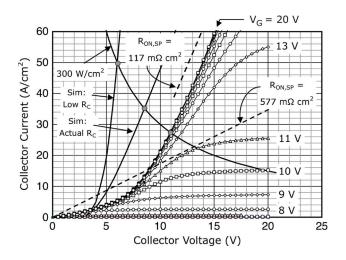

Fig. 5. ON-state characteristics of an n-channel IGBT with an active area of  $1.48 \times 10^{-3}$  cm<sup>2</sup>, measured at room temperature. The gate voltage ranges from 0 to 20 V in 1-V intervals. Two simulations are also shown: one with the actual n<sup>+</sup> and p<sup>+</sup> contact resistivities obtained from TLM measurements on the device wafer, and one with contact resistivities that can normally be obtained on 4H-SiC. Both simulations assume an ambipolar lifetime of 1  $\mu$ s and  $V_G = 20$  V (oxide field of 4 MV/cm). The dashed lines show the specific ON-resistance of the n<sup>-</sup> drift layer if no conductivity modulation was present (0.577  $\Omega \cdot \text{cm}^2$ ) and the actual differential ON-resistance of the entire IGBT (0.177  $\Omega \cdot \text{cm}^2$ ), demonstrating that significant conductivity modulation is occurring.

#### **III. DEVICE CHARACTERIZATION**

Fig. 5 shows the ON-state characteristics of an n-channel IGBT at room temperature. At a gate voltage of 20 V (oxide field of 4 MV/cm), the collector current  $J_{300}$  at the 300-W/cm<sup>2</sup> power limit is 27.3 A/cm<sup>2</sup>. The figure also shows two MEDICI simulations of the IGBT. The first uses resistivities for the n<sup>+</sup> and p<sup>+</sup> contacts derived from TLM measurements on the actual devices  $(1.2 \times 10^{-2} \text{ and } 1.9 \times 10^{-2} \Omega \cdot \text{cm}^2$ , respectively), and the second uses resistivities that can typically be obtained on 4H-SiC (5  $\times$  10<sup>-4</sup> and 5  $\times$  10<sup>-3</sup>  $\Omega \cdot$  cm<sup>2</sup>, respectively). Both simulations assume an ambipolar lifetime of 1  $\mu$ s and a gate voltage of 20 V, corresponding to an oxide field of 4 MV/cm. At the 300-W/cm<sup>2</sup> power limit, the  $J_{300}$  current density for the simulated device with low contact resistivities is  $50 \text{ A/cm}^2$ , the  $J_{300}$  for the device with contact resistivities of the actual device is 35 A/cm<sup>2</sup>, and the  $J_{300}$  of the actual device is 27.3 A/cm<sup>2</sup>.

The dashed lines in Fig. 5 correspond to the specific ON-resistance of the 180- $\mu$ m n<sup>-</sup> drift layer *without* conductivity modulation (577 m $\Omega \cdot cm^2$ ) and the differential ON-resistance of the actual device at  $V_G = 20$  V (177 m $\Omega \cdot cm^2$ ). Since the resistance of the entire device is  $3 \times 1000$  that the resistance of an unmodulated drift region, it is clear that substantial conductivity modulation is taking place. We also note that the differential resistance of the actual device at  $V_G = 20$  V is the same as predicted by the simulations, suggesting that the assumed lifetime of 1  $\mu$ s is reasonable. A possible explanation for the lateral voltage shift of the actual device is that the p<sup>+</sup> collector contact on the back side of the device may not be fully ohmic (note that this contact cannot be measured by TLM structures on the test chip). At low collector currents, the differential resistance of the p<sup>+</sup> back contact appears to

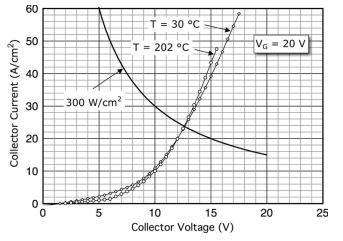

Fig. 6. ON-state characteristics of an n-channel IGBT at 30 °C and 202 °C.  $V_G = 20$  V in both cases. The I-V characteristics and  $J_{300}$  are essentially unchanged at elevated temperatures due to the increase in lifetime with temperature, which compensates for the decrease in mobility.

be high, shifting the current–voltage (I-V) characteristic of the measured device to the right compared with the simulations. This results in a lower  $J_{300}$  than predicted by the simulations.

Fig. 6 shows the ON-state characteristics of an n-IGBT at 30 °C and 202 °C. The gate voltage is 20 V in both cases. As shown,  $J_{300}$  at elevated temperatures is essentially unchanged from its room-temperature value. In an IGBT, the current density depends on the ambipolar diffusion length, i.e., the square root of the ambipolar diffusion coefficient times the ambipolar lifetime. Although the ambipolar diffusion coefficient decreases with temperature, the ambipolar lifetime increases by almost the same factor, leaving the ambipolar diffusion length virtually unchanged. This is in contrast to the MOSFET, where the ON-resistance depends on the electron mobility in the drift region, which decreases with temperature, leading to much higher ON-resistances. The temperature dependence is important because, when the devices are operated at the package limit of 300 W/cm<sup>2</sup>, the junction temperatures will be much higher than ambient.

The fabricated IGBTs exhibit several problems, some of which may be associated with processing on the carbon face of the epilayers. As already mentioned, the contact resistivities for both  $n^+$  and  $p^+$  ohmic contacts are high and clearly limit performance. We believe that the high resistances are due to specific processing problems on these devices and are not inherent in fabrication on the carbon face. In addition, a small gate leakage current is observed in some devices. Separate measurements of the emitter, body, and collector currents indicate that when the gate is biased at 20 V and all other contacts grounded, about 90% of the gate leakage current passes through the oxide over the  $n^+$  emitter region, 9.8% through the oxide over the n<sup>-</sup> JFET region, and about 0.2% through the oxide over the  $p^+$  body region. Measurements at Vanderbilt University [11] indicate that thermal oxides on the carbon face of SiC have a lower breakdown field ( $\sim$ 5.5 V/cm) than oxides on the silicon face ( $\sim 10$  MV/cm). The breakdown field may be even lower for oxides on implanted regions. To investigate this, we measured oxides on MOS capacitors over the  $n^+$  emitter implants, p-type body implants, and  $n^-$  JFET regions on the same wafer as the IGBTs. The breakdown field of the oxide over  $n^+$  regions is around 2.7 MV/cm (corresponding to a gate bias of 12 V), and over the p-type body and  $n^-$  JFET regions, the breakdown field is slightly above 4 MV/cm. The reduced breakdown strength of oxides on the carbon face is an issue that needs to be addressed in future device work.

The n<sup>-</sup> drift layer has doping  $(2 \times 10^{14} \text{ cm}^{-3})$  and thickness (180  $\mu$ m) values designed to give a theoretical parallel-plane breakdown voltage of 25 kV. With proper edge terminations, it should be possible to achieve 80% of this value, or 20 kV, in actual devices. Since none of the test devices had edge terminations, we did not attempt to measure the blocking voltage on these devices.

#### **IV. CONCLUSION**

n-Channel double-diffused MOS IGBTs with  $180-\mu m$  drift layers capable of blocking 20 kV have been designed and fabricated on the carbon face of 4H SiC free-standing epilayers. The devices show good conductivity modulation, and the collector current at 300 W/cm<sup>2</sup> is 27.3 A/cm<sup>2</sup>. To our knowledge, this is the first detailed report of device fabrication on free-standing SiC epilayers.

#### ACKNOWLEDGMENT

The authors would like to thank Prof. M. Capano, Purdue University, from providing valuable advice and technical support, as well as Dr. J. Caldwell, Dr. P. Klein, Dr. E. Glaser, Dr. B. Stahlbush, and Dr. K. Liu, Naval Research Laboratory, for extensive lifetime measurements.

#### REFERENCES

- S.-H. Ryu, S. Krishnaswami, M. O'Loughlin, J. Richmond, A. Agarwal, J. Palmour, and A. R. Hefner, "10-kV 123-mOhm cm<sup>2</sup> 4H-SiC power DMOSFETS," *IEEE Electron Device Lett.*, vol. 25, no. 8, pp. 556–558, Aug. 2004.

- [2] Y. Sui, G. G. Walden, X. Wang, and J. A. Cooper, "Device options and design considerations for high-voltage (10–20 kV) SiC power switching devices," *Mater. Sci. Forum*, vol. 527–529, pp. 1449–1452, 2006.

- [3] N. Ramungul, T. P. Chow, M. Ghezzo, J. Kretchmer, and W. Hennessy, "A fully planarized, 6H-SiC UMOS insulated-gate bipolar transistor," in *Proc. IEEE Device Res. Conf.*, Santa Barbara, CA, Jun. 24–26, 1996.

- [4] M. K. Das, J. Zhang, R. Callanan, C. Capell, J. Clayton, M. Donofrio, S. K. Haney, F. Husna, C. Jonas, J. Richmond, and J. J. Sumakeris, "A 13 kV 4H-SiC n-channel IGBT with low R<sub>diff,on</sub> and fast switching," in *Proc. Int. Conf. SiC Related Mater.*, Otsu, Japan, Oct. 14–19, 2007.

- [5] M. K. Das, J. Zhang, R. Callanan, C. Capell, J. Clayton, M. Donofrio, S. K. Haney, F. Husna, C. Jonas, J. Richmond, and J. J. Sumakeris, "A 13 kV 4H-SiC n-channel IGBT with low R<sub>diff,on</sub> and fast switching," *Mater. Sci. Forum*, vol. 600–603, pp. 1183–1186, 2009.

- [6] S. Y. Ha and J. P. Bergman, "Degradation of SiC high-voltage pin diodes," MRS Bull., vol. 30, no. 4, pp. 305–307, Apr. 2005.

- [7] S. Ha, M. Skowronski, and H. Lendenmann, "Nucleation sites of recombination-enhanced stacking fault formation in silicon carbide p-i-n diodes," *J. Appl. Phys.*, vol. 96, no. 1, pp. 393–398, Jul. 2004.

- [8] M. Matin, A. Saha, and J. A. Cooper, "A self-aligned process for high voltage, short-channel vertical DMOSFETs in 4H-SiC," *IEEE Trans. Electron Devices*, vol. 51, no. 10, pp. 1721–1725, Oct. 2004.

- [9] G. Y. Chung, C. C. Tin, J. R. Williams, K. McDonald, R. K. Chanana, R. A. Weller, S. T. Pantelides, L. C. Feldman, O. W. Holland, M. K. Das,

and J. W. Palmour, "Improved inversion channel mobility for 4H-SiC MOSFETs following high temperature anneals in nitric oxide," *IEEE Electron Device Lett.*, vol. 22, no. 4, pp. 176–178, Apr. 2001.

- [10] A. Saha, "SiC short-channel power DMOSFET: An optimized design," Ph.D. dissertation, Purdue Univ., West Lafayette, IN, Dec. 2006.

- [11] L. C. Feldman, private communication.

**James A. Cooper** (S'66–M'69–SM'85–F'93) received the Ph.D. degree from Purdue University, West Lafayette, IN, in 1973.

From 1973 to 1983, he was a Member of Technical Staff with Bell Laboratories, Murray Hill, NJ, where he was a Principal Designer of AT&T's first CMOS microprocessor and developed a time-of-flight technique for investigating high-field transport in silicon inversion layers. In 1983, he joined the faculty at Purdue University, where he was the Founding Director of the Purdue Optoelectronics Research

Center and is currently the Jai N. Gupta Professor of Electrical and Computer Engineering. Since 1990, he has been exploring device technology in the wide-bandgap semiconductor SiC. His group demonstrated the first monolithic integrated circuits in SiC in 1993, the first planar DMOS power transistors in 1996, and the first lateral DMOS power transistors in 1997 and introduced the first self-aligned short-channel DMOSFETs in 2003. In his 26 years at Purdue University, he has graduated 25 Ph.D. and 10 M.S. thesis students and was a Founding Codirector of the \$58 million Birck Nanotechnology Center. He has coauthored more than 250 technical papers and conference presentations and five book chapters. He is the holder of 14 U.S. patents.

Prof. Cooper served as an Associate Editor of the IEEE TRANSACTIONS ON ELECTRON DEVICES from 1983 to 1986 and as a Guest Editor of the 1999 and 2008 Special Issues of the IEEE TRANSACTIONS ON ELECTRON DEVICES. He currently serves on the Editorial Advisory Board of IEEE PROCEEDINGS.

Integration Engineer.

Xiaokun Wang received the B.S. degree in electronics and information system from Peking University, Beijing, China, in 1999 and the M.S. degree in physics, the M.S. degree in electrical and computer engineering, and the Ph.D. degree in electrical and computer engineering from Purdue University, West Lafayette, IN, in 2000, 2002, and 2007, respectively. From 2007 to 2008, she was with Silvaco Inter-

national, Santa Clara, CA, as a TCAD Application Engineer. Then, she worked for a short period of time with Western Digital, Fremont, CA, as a Process