## University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange

**Doctoral Dissertations**

**Graduate School**

5-2016

# High Voltage Point of Load Converter for Data Center Power Supplies

Yutian Cui University of Tennessee - Knoxville, ycui7@vols.utk.edu

Follow this and additional works at: https://trace.tennessee.edu/utk\_graddiss

Part of the Power and Energy Commons

#### **Recommended Citation**

Cui, Yutian, "High Voltage Point of Load Converter for Data Center Power Supplies. " PhD diss., University of Tennessee, 2016. https://trace.tennessee.edu/utk\_graddiss/3690

This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Yutian Cui entitled "High Voltage Point of Load Converter for Data Center Power Supplies." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Leon M. Tolbert, Major Professor

We have read this dissertation and recommend its acceptance:

Fred Wang, Daniel J. Costinett, Andrew W. Wereszczak

Accepted for the Council:

Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

## High Voltage Point of Load Converter for

**Data Center Power Supplies**

A Dissertation Presented for the Doctor of Philosophy Degree The University of Tennessee

> Yutian Cui May 2016

Copyright © 2016 by Yutian Cui

All rights reserved.

## ACKNOWLEDGEMENT

First of all, I would like to take this opportunity to express my sincere gratitude and respect to my advisor, Dr. Leon M. Tolbert. He guided me into this research area and taught me how to do research with his broad vision, profound knowledge, and great patience. I feel blessed to have such a great advisor in my Ph.D studies, without his support, this dissertation would never been possible.

I would like to extend my gratitude to Dr. Fred Wang and Dr. Daniel J. Costinett, for their help and suggestions during the meetings as well as the discussion and feedback on this dissertation.

I would like to thank Dr. Andrew A. Wereszczak for serving on my committee and offering me great suggestions on my dissertation.

I would like to thank all the colleagues in the power electronics lab in the University of Tennessee, Knoxville. They are Dr. Shengnan Li, Dr. Bailu Xiao, Dr. Dong Jiang, Dr. Lijun Hang, Dr. Jingxin Wang, Dr. Wanjun Lei, Dr. Faete Filho, Dr. Mithat Can Kisacikoglu, Dr. Lakshmi Reddy Gopi Reddy, Dr. Zhuxian Xu, Dr. Fan Xu, Dr. Ben Guo, Dr. Zheyu Zhang, Dr. Jing Xue, Dr. Zhiqiang Wang, Dr. Jing Wang, Dr. Xiaojie Shi, Dr. Liu Yang, Dr. Weimin Zhang, Dr. Sheng Zheng, Mr. Bradford Trento, Mr. Yalong Li, Mr. Wenchao Cao, Mr. Yiwei Ma, Ms. Yang Xue, Mr. Bo Liu, Mr. Saeed Anwar, Mr. Edward Jones, Mr. Siyao Jiang, Mr. Yiqi Liu, Mr. Tong Wu, Mr. Shuoting Zhang, Mr. Chongwen Zhao, Ms. Ling Jiang, and Mr. Ren Ren. Special thanks to Mr. Fei Yang, for his encouragement during my darkest days.

Last but not least, I would like to thank my parents for their unconditional love and support. Without them, this work would never been possible.

## ABSTRACT

With the increased cloud computing and digital information storage, the energy requirement of data centers where a large number of computer systems are housed keeps increasing. However, most of the data centers today are operated inefficiently, both economically and environmentally. Efforts including improving power delivery architecture, power conversion efficiency and thermal management have been made to increase the power delivery efficiency from grid to point of load.

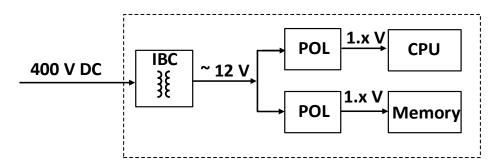

In this dissertation, a new power delivery architecture, high voltage point of load (HV POL) architecture, has been proposed in order to improve power conversion and distribution efficiency for data center power supplies.

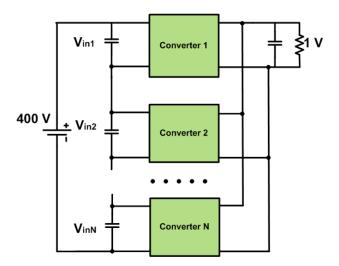

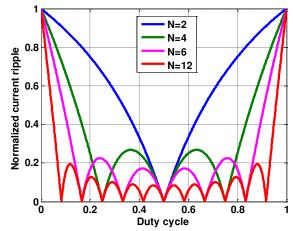

First, the conversion structure has been selected as input series and output parallel (ISOP) to fulfill the high ratio (400:1) conversion and mitigate the step down stress of a single converter. Also, with multiple output phases, interleaving control technique can be applied to increase equivalent switching frequency and allows smaller output inductor.

Then, two different types of converter topologies have been chosen for evaluation in the ISOP structure: phase shift full bridge (PSFB) and half bridge current doubler. High efficiency driven converter design and control method have been performed on both topologies. In PSFB, the impact of primary side MOSFETs' output junction capacitances on the converter's efficiency has been studied. For half bridge current doubler, a novel control method enabling soft switching over the entire load range with auxiliary circuit is proposed and verified in experiments.

A six phase ISOP connected half bridge current doubler converter was built and tested to realize the single stage 400 V to 1 V conversion. Adaptive voltage positioning (AVP) control is analyzed and performed on the ISOP system to meet the on-board power supply requirement. Also, the impact of mismatches in the ISOP connected modules are calculated and simulated for both static and dynamic performance, and it is shown that the ISOP system is relatively immune to circuit's mismatches. Therefore, the concept of using the single stage ISOP connected converter has been shown to be feasible as a high efficiency on-board power supply with good transient performance.

# **TABLE OF CONTENTS**

| 1. | Inti  | oduc  | tion                                                                | 1  |

|----|-------|-------|---------------------------------------------------------------------|----|

|    | 1.1.  | Cha   | llenge of power supplies in data centers                            | 1  |

|    | 1.2.  | Higl  | h efficiency power supplies                                         | 2  |

|    | 1.3.  | Mot   | ivation and strategy                                                | 4  |

|    | 1.3.  | 1.    | Innovation of power supplies architecture                           | 4  |

|    | 1.3.  | 2.    | Improved power converter efficiency                                 | 5  |

|    | 1.4.  | Diss  | sertation outline                                                   | 7  |

| 2. | Lite  | eratu | re Review                                                           | 8  |

|    | 2.1   | Data  | a center power supply architecture                                  | 8  |

|    | 2.1.  | 1     | Intermediate bus architecture                                       | 8  |

|    | 2.1.  | 2     | Factorized power architecture                                       |    |

|    | 2.2   | Higl  | h efficiency PWM DC/DC converter                                    |    |

|    | 2.2.  | 1.    | Device selection                                                    |    |

|    | 2.2.  | 2     | Soft switching techniques of PWM converters                         | 15 |

|    | 2.3   | Con   | trol of input series and output parallel (ISOP) connected converter |    |

|    | 2.3.  | 1     | Common duty cycle control                                           | 25 |

|    | 2.3.  | 2     | Active control                                                      | 27 |

|    | 2.4   | Sum   | nmary                                                               |    |

| 3. | Alte  | ernat | ive Power Supplies Architecture Design                              |    |

|    | 3.1   | 400   | V on-board distribution voltage architecture                        |    |

|    | 3.2   | Bus   | voltage optimization of intermediate bus architecture               |    |

|    | 3.2.  | 1.    | Bus converter efficiency with different bus voltage                 |    |

|    | 3.2.  | 2.    | POL efficiency with different bus voltage                           |    |

|    | 3.2.  | 2     | IBA efficiency with different bus voltage                           |    |

|    | 3.3   | HV    | POL Architecture                                                    |    |

|    | 3.3.  | 1     | Structure of HV POL                                                 |    |

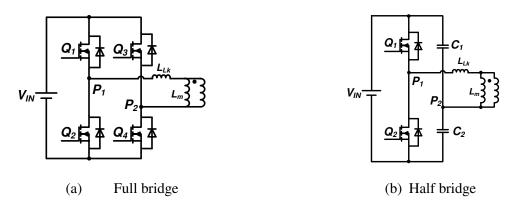

|    | 3.3.  | 2     | Topology selection for HV POL                                       | 41 |

|    | 3.3.  | 3     | Comparison between IBA and HV POL                                   |    |

|    | 3.4   | Sum   | nmary                                                               |    |

| 4. | Pha   | se Sh | nift Full Bridge DC/DC Converter in HVPOL                           |    |

|    | 1 110 |       |                                                                     |    |

|    | 4.1   |       | nsformer design                                                     |    |

|    |       | Trar  |                                                                     | 47 |

| 4.1      | .3      | Transformer winding structure                                                   | 52   |

|----------|---------|---------------------------------------------------------------------------------|------|

| 4.2      | Prin    | nary side device selection                                                      | 61   |

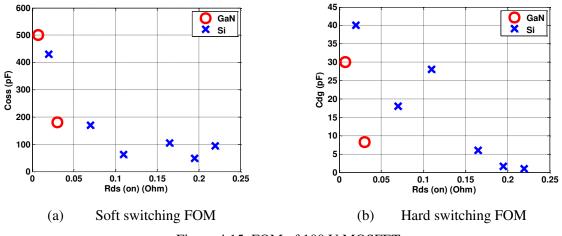

| 4.2      | 2.1     | Device figure of merit comparison                                               | 62   |

| 4.2      | 2.2     | Operation principle of PSFB converter considering output junction capacitance   | 63   |

| 4.2      | 2.3     | Primary side device loss analysis                                               | 69   |

| 4.3      | Seco    | ondary side device selection                                                    | 70   |

| 4.4      | Outp    | put inductor selection                                                          | 71   |

| 4.5      | Exp     | erimental verification                                                          | 73   |

| 4.6      | Sum     | imary                                                                           | 75   |

| 5. Lo    | ad De   | pendent Soft Switching Method for Half Bridge Current Doubler Converter in H    | IV   |

| POL      |         |                                                                                 | 77   |

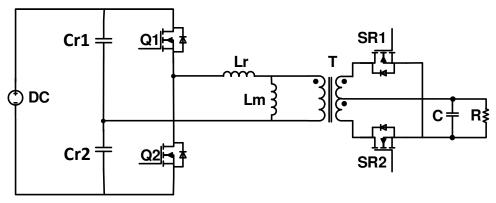

| 5.1      | Con     | trol of half bridge current doubler                                             | 78   |

| 5.1      | .1      | Asymmetrical control                                                            | 78   |

| 5.1      | .2      | Symmetrical control                                                             | 79   |

| 5.1      | .3      | Comparison between two control methods                                          | 80   |

| 5.2      | Ope     | ration principle of proposed zero voltage switching half bridge current doubler | 82   |

| 5.3.     | Loa     | d dependent charging time analysis and controller design                        | 90   |

| 5.3      | 8.1.    | Losses under constant charging time of auxiliary inductor                       | 90   |

| 5.3      | 8.2.    | Proposed load dependent charging time method                                    | 92   |

| 5.4.     | Con     | verter design for proposed method                                               | 97   |

| 5.4      | l.1.    | Power stage design                                                              | 97   |

| 5.4      | l.2.    | Auxiliary circuit design                                                        | 99   |

| 5.5.     | Exp     | erimental verification                                                          | 101  |

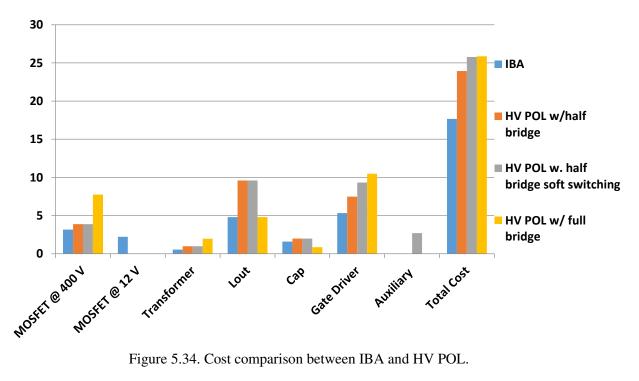

| 5.6.     | Cost    | t analysis                                                                      | 108  |

| 5.7.     | Sum     | ımary                                                                           | 110  |

| 6. Inj   | put Se  | ries Output Parallel Connected Half Bridge Current Doubler with Adaptive Vol    | tage |

| Position | ning (A | AVP) Control                                                                    | 112  |

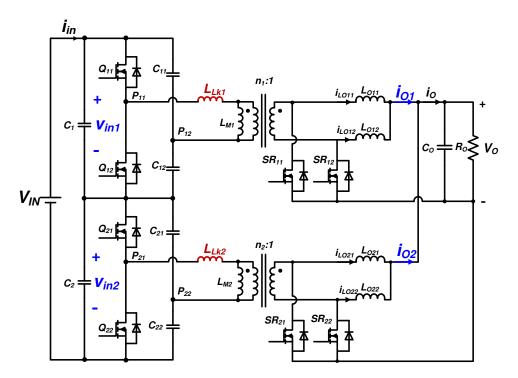

| 6.1.     | Mod     | leling of ISOP connected half bridge current doubler                            | 113  |

| 6.1      | .1.     | Modeling of single half bridge current doubler                                  | 113  |

| 6.1      | .2.     | Modeling of input series and output paralleled (ISOP) converter                 | 118  |

| 6.2.     | Ada     | ptive voltage positioning (AVP) control of half bridge current doubler          | 120  |

| 6.3.     | Con     | nmon duty cycle control of ISOP converter with mismatches                       | 126  |

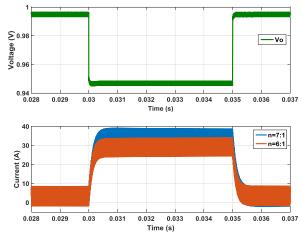

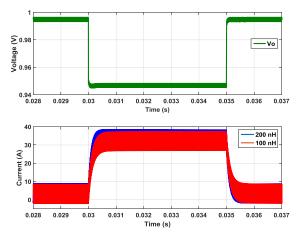

| 6.3      | 8.1.    | Sharing among phases with mismatches                                            | 127  |

| 6.3      | 3.2.    | Impact on output performance of ISOP system with mismatches                     | 131  |

| 6.4.     | Experimental verification |  |

|----------|---------------------------|--|

| 6.5.     | Summary                   |  |

| 7. Con   | clusion and Future Work   |  |

| 7.1.     | Conclusions               |  |

| 7.1.     | 1. Summary of the work    |  |

| 7.1.     | 2. Contributions          |  |

| 7.2.     | Future work               |  |

| Referenc | e                         |  |

| VITA     |                           |  |

# LIST OF TABLES

| Table 2.1. Suitability of common ratio cycle scheme [57].    26                                       |

|-------------------------------------------------------------------------------------------------------|

| Table 3.1. Loss for 12 Vdc distribution on motherboard for 1600 W load.       31                      |

| Table 3.2. Loss for 400 Vdc distribution on motherboard for 1600 W load                               |

| Table 3.3. Primary side device comparison for LLC converter                                           |

| Table 3.4. Transformer design of different output voltage in LLC converter.    34                     |

| Table 3.5. Si SR devices selection for different output voltage                                       |

| Table 3.6. MOSFET selection for different output voltage in POL.       36                             |

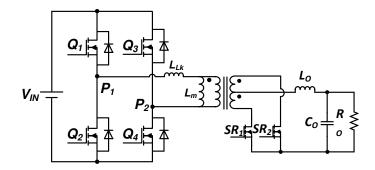

| Table 3.7. Primary circuit comparison: half bridge compared with full bridge                          |

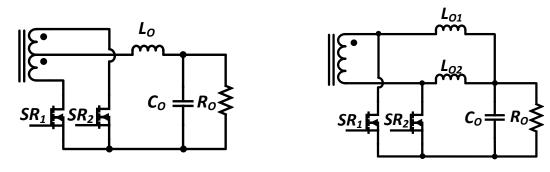

| Table 3.8. Secondary circuit comparison: full wave compared with current doubler                      |

| Table 4.1. Specifications of a single PSFB converter used in HV POL converter                         |

| Table 4.2. Transformer AC resistance and leakage inductance comparison among different structures. 58 |

| Table 4.3. Leakage inductance comparison between calculation and measurement.       59                |

| Table 4.4. Key parameters of two primary MOSFETs.    62                                               |

| Table 5.1. Specification of half bridge current doubler.    97                                        |

| Table 5.2. Components in half bridge current doubler.    99                                           |

| Table 6.1. Specification of ISOP system.       112                                                    |

| Table 7.1. Comparison between Oscon and ceramic capacitors    143                                     |

# LIST OF FIGURES

| Figure 1.1. Number of transistors on Intel's microprocessors [1].                       | 1  |

|-----------------------------------------------------------------------------------------|----|

| Figure 1.2. Roadmap of Intel microprocessors [5].                                       | 2  |

| Figure 1.3. Data center installed based and spending [7].                               | 3  |

| Figure 1.4. Power delivery for data centers [9].                                        | 4  |

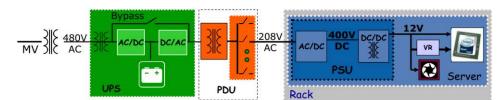

| Figure 1.5. Conventional 208 V AC power delivery architecture [8]                       | 5  |

| Figure 1.6. High voltage DC power deliver architecture [8].                             | 5  |

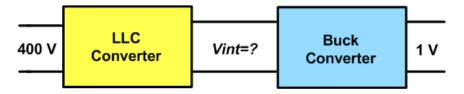

| Figure 2.1. Intermediate bus architecture for data center power supplies.               | 9  |

| Figure 2.2. LLC resonant converter as IBC.                                              | 9  |

| Figure 2.3. Synchronous buck converter as POL.                                          | 9  |

| Figure 2.4. Two stage buck architecture                                                 | 10 |

| Figure 2.5. Buck converter as first stage in two stage POL in Figure 2.4.               | 10 |

| Figure 2.6. Multi-phase buck as second stage in two stage POL in Figure 2.4.            | 11 |

| Figure 2.7. Switch capacitor as second stage in two stage POL in Figure 2.4.            | 11 |

| Figure 2.8. Sigma connected POL converter.                                              | 12 |

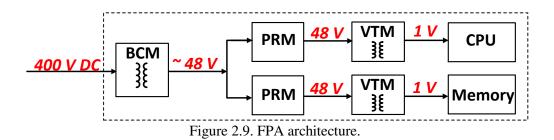

| Figure 2.9. FPA architecture                                                            | 13 |

| Figure 2.10. Voltage, current and gate charge during turn on transient.                 | 14 |

| Figure 2.11. Equivalent MOSFET model with junction capacitances                         | 15 |

| Figure 2.12. Synchronous buck converter with current direction of switches and inductor | 16 |

| Figure 2.13. Half bridge current doubler converter.                                     | 17 |

| Figure 2.14. Inductor assist soft switching two phase buck converter [37][38].          | 19 |

| Figure 2.15. ZVS buck converter with coupled inductor [40].                             | 20 |

| Figure 2.16. Waveforms of i <sub>1</sub> and i <sub>R</sub> [40].                       | 20 |

| Figure 2.17 ZVT buck converter proposed in [45].                                        | 21 |

| Figure 2.18. Theoretical waveforms of ZVT converter [45].                               | 21 |

| Figure 2.19. Turn off waveforms with snubber capacitor                                  | 22 |

| Figure 2.20. Quasi-resonant ZCS converter.                                              | 23 |

| Figure 2.21. Operational waveforms of quasi-resonant converter                          | 23 |

| Figure 2.22. ZCS converter with pulse width modulation capability.                      | 23 |

| Figure 2.23. Operational waveforms of PWM ZCS converter.                                | 24 |

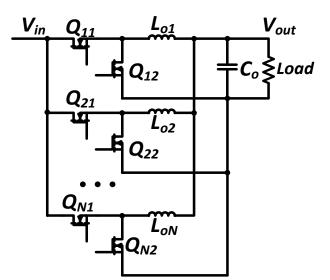

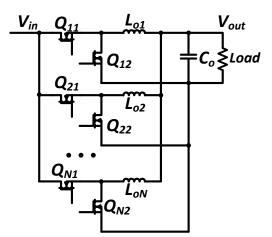

| Figure 2.24. ISOP connected converters                                                  | 25 |

| Figure 2.25. Common duty cycle control.                                                 | 27 |

| Figure 3.1. 12 V distribution voltage.                                                  |    |

| Figure 3.2. 400 V distribution voltage                                                  |    |

| Figure 3.3. Intermediate bus architecture (IBA).                                                          | 32 |

|-----------------------------------------------------------------------------------------------------------|----|

| Figure 3.4. LLC resonant converter                                                                        | 33 |

| Figure 3.5. LLC efficiency at different bus voltages.                                                     | 35 |

| Figure 3.6. Multiphase synchronous buck converter.                                                        | 36 |

| Figure 3.7. Buck efficiency at different bus voltage                                                      | 37 |

| Figure 3.8. Overall system efficiency of IBA at different bus voltage                                     | 38 |

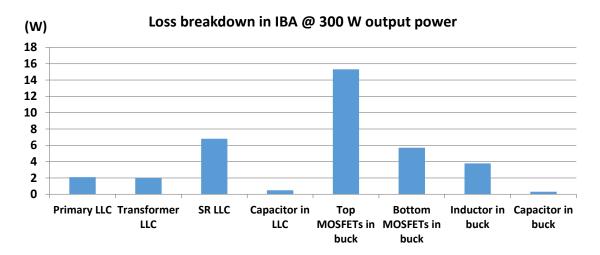

| Figure 3.9. Loss breakdown of 300 W IBA                                                                   | 39 |

| Figure 3.10. Structure of ISOP connected HV POL.                                                          | 40 |

| Figure 3.11. Ripple current cancellation with respect to interleaved phase number and duty cycle          | 41 |

| Figure 3.12. Primary circuit configuration.                                                               | 42 |

| Figure 3.13. Secondary circuit configuration.                                                             | 43 |

| Figure 3.14. Full bridge with full wave rectification.                                                    | 44 |

| Figure 3.15. Half bridge with current doubler.                                                            | 44 |

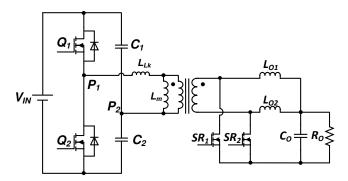

| Figure 3.16. Comparison of loss distribution between IBA and HV POL.                                      | 45 |

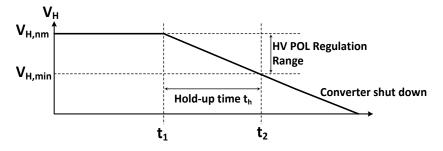

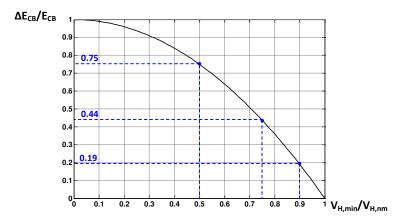

| Figure 4.1. Indication of hold up capacitor                                                               | 48 |

| Figure 4.2. Voltage waveform of hold-up capacitor                                                         | 48 |

| Figure 4.3. Normalized delivered energy from hold up capacitor during hold-up time as a function of       |    |

| hold-up voltage                                                                                           | 49 |

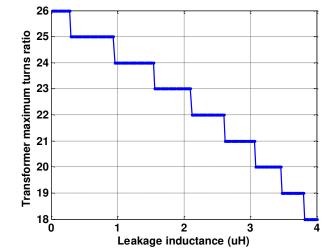

| Figure 4.4. Relationship between leakage inductance and transformer turns ratio                           | 50 |

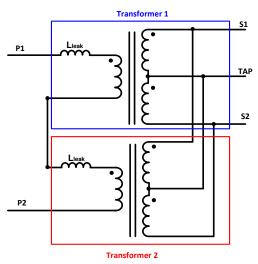

| Figure 4.5. ISOP connected transformer                                                                    | 51 |

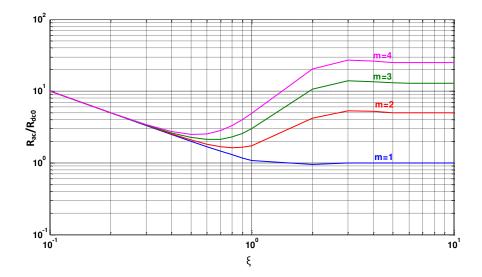

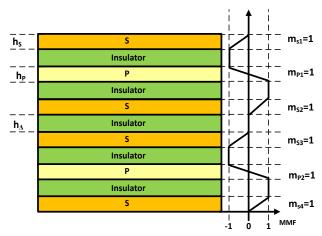

| Figure 4.6. AC resistance relative to DC resistance in a layers with $\xi=1$                              | 53 |

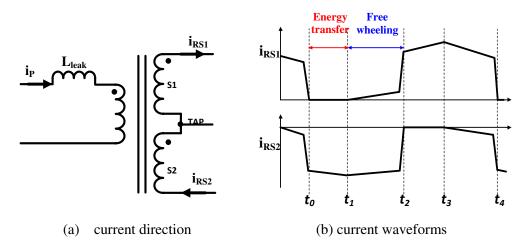

| Figure 4.7. Secondary side current of center tapped transformer in a phase shift full bridge converter.   | 55 |

| Figure 4.8. AC current of secondary side winding in PSFB converter                                        | 55 |

| Figure 4.9. Interleaved winding structure                                                                 | 56 |

| Figure 4.10. Non-interleaved winding structure.                                                           | 57 |

| Figure 4.11. Half-interleaved winding structure                                                           | 57 |

| Figure 4.12. Equivalent circuit used to calculate R <sub>eq</sub>                                         | 59 |

| Figure 4.13. AC winding resistance verification of primary device #1 ( $R_{ds(on)}=110 \text{ m}\Omega$ ) | 61 |

| Figure 4.14. AC winding resistance verification of primary device #2 ( $R_{ds(on)}=5.6m\Omega$ )          | 61 |

| Figure 4.15. FOM of 100 V MOSFETs                                                                         | 62 |

| Figure 4.16. Operational waveforms of phase shift full bridge converter.                                  | 65 |

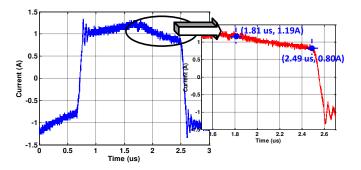

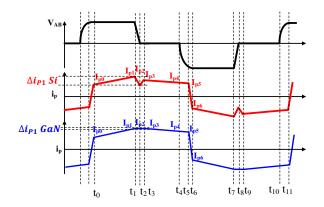

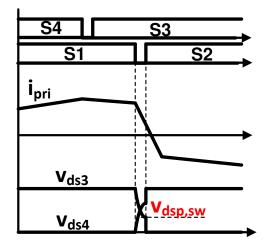

| Figure 4.17. Current step down for both Si and GaN during interval 2                                      | 66 |

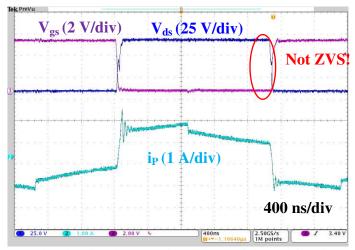

| Figure 4.18. Partial soft switching of primary MOSFETs                                                    | 69 |

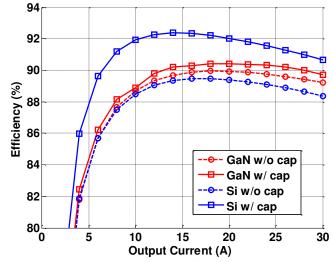

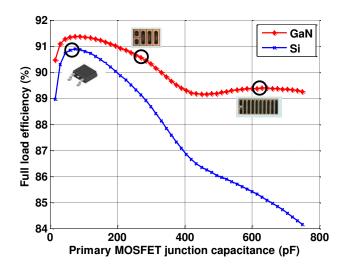

| Figure 4.19. Estimated PSFB converter efficiency with Si and GaN devices.                                 | 72 |

| Figure 4.20. Estimated PSFB converter full load efficiency with respect to output junction capacitance |       |

|--------------------------------------------------------------------------------------------------------|-------|

|                                                                                                        |       |

| Figure 4.21. Testing lagging leg waveforms under full load for Si converter                            |       |

| Figure 4.22. Testing transformer voltage and current waveforms under full load for GaN converter.      |       |

| Figure 4.23. Transformer primary side current comparison between Si and GaN.                           | 75    |

| Figure 4.24. Measured efficiency of Si and GaN based converter.                                        | 75    |

| Figure 5.1. Half bridge with current doubler converter.                                                |       |

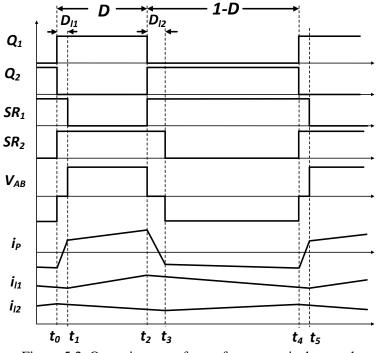

| Figure 5.2. Operation waveform of asymmetrical control                                                 | 78    |

| Figure 5.3. Operation waveforms of symmetrical control of converter                                    | 80    |

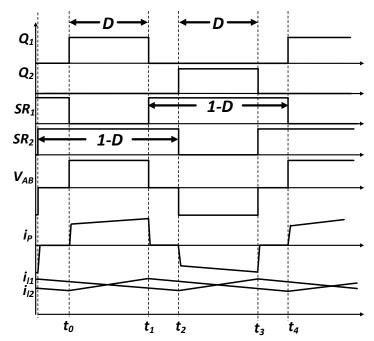

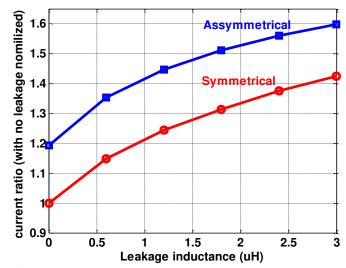

| Figure 5.4. Transformer current comparison between asymmetrical and symmetrical control                | 81    |

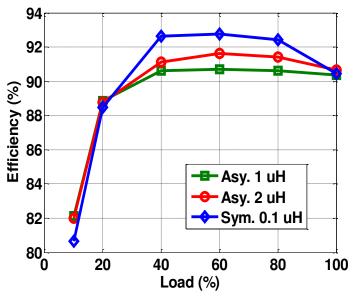

| Figure 5.5. Efficiency comparison between asymmetrical and symmetrical control.                        | 81    |

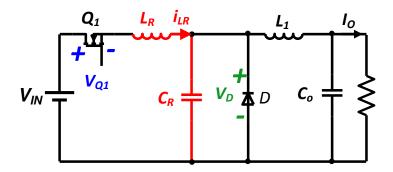

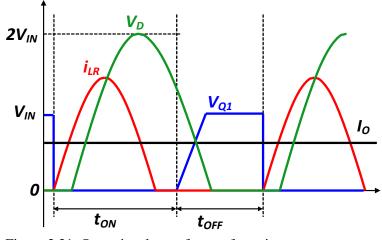

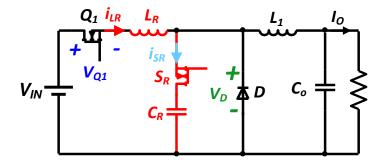

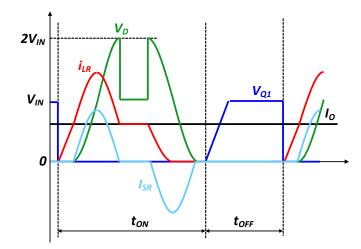

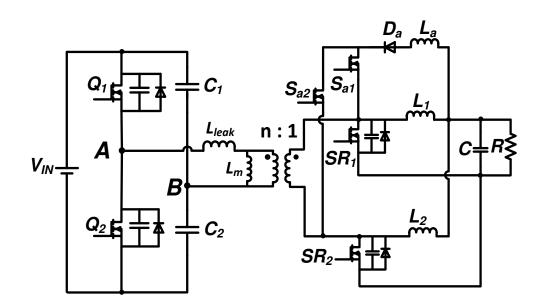

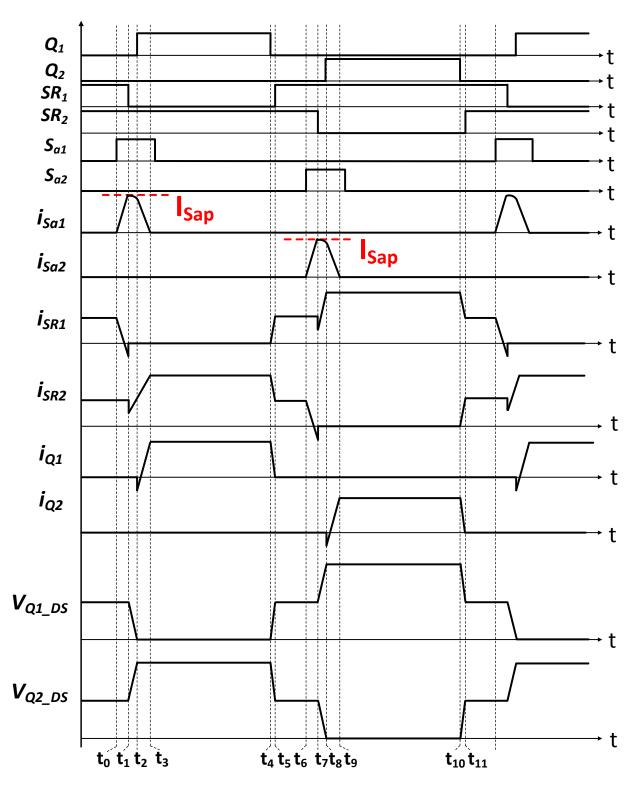

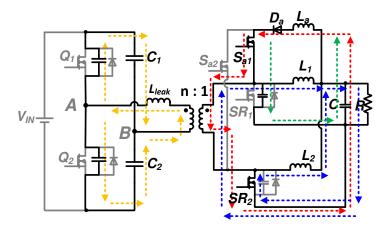

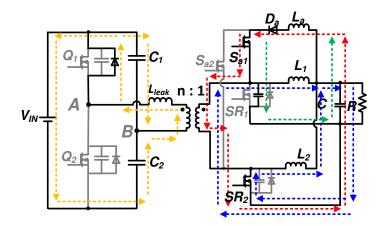

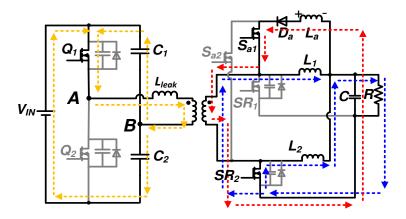

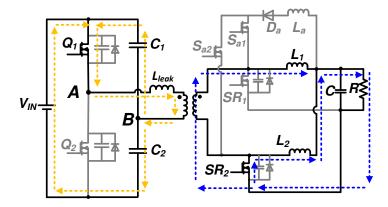

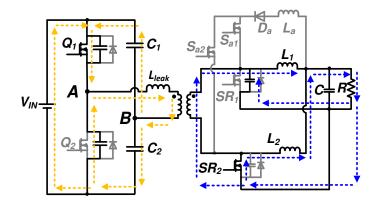

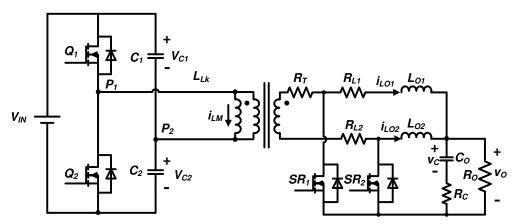

| Figure 5.6. Proposed zero voltage switching circuit for half bridge current doubler.                   | 82    |

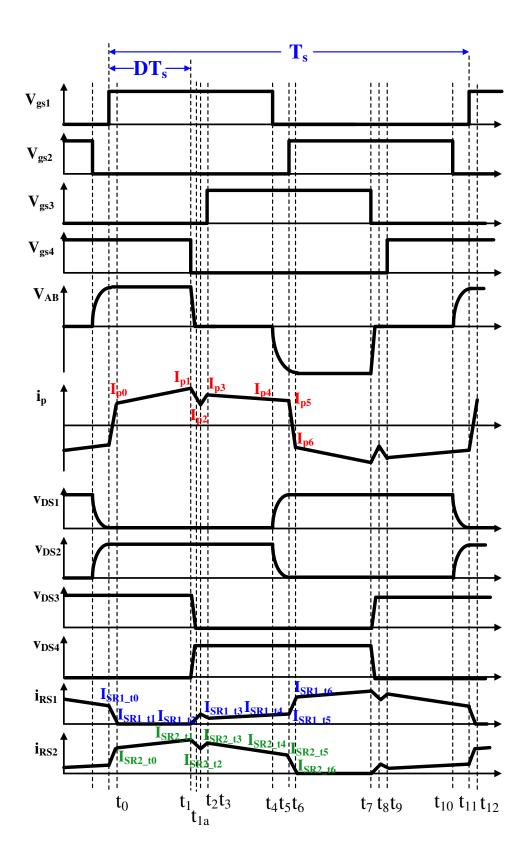

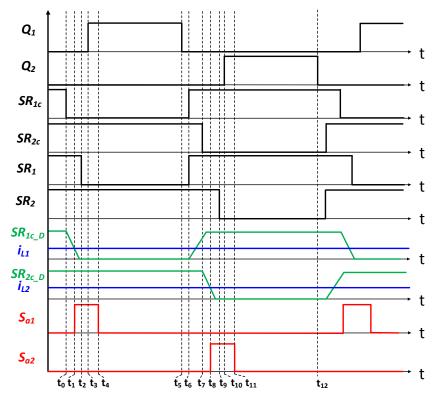

| Figure 5.7. Operational waveform of proposed soft switching method for half bridge current doubler.    | 84    |

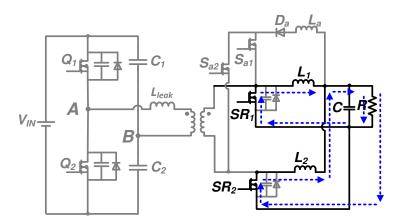

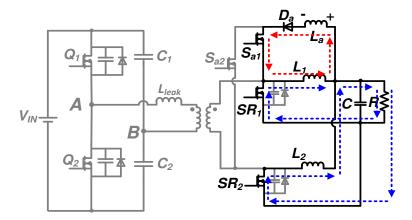

| Figure 5.8. Equivalent circuit prior to $t_0$                                                          | 85    |

| Figure 5.9. Equivalent circuit from $t_0 - t_1$                                                        | 85    |

| Figure 5.10. Equivalent circuit from $t_1 - t_2$                                                       | 86    |

| Figure 5.11. Primary body diode conduction between $t_1 - t_2$                                         | 87    |

| Figure 5.12. Equivalent circuit from $t_2 - t_3$                                                       | 88    |

| Figure 5.13. Equivalent circuit from $t_3 - t_4$                                                       | 89    |

| Figure 5.14. Equivalent circuit from $t_4 - t_5$ .                                                     | 89    |

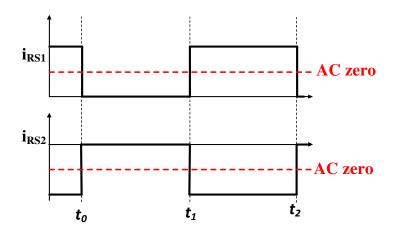

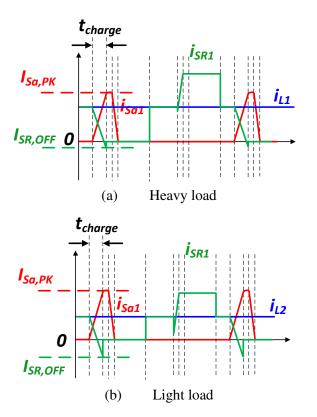

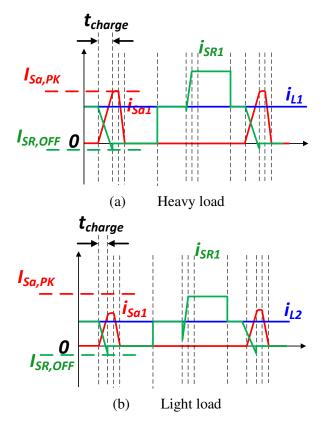

| Figure 5.15. SR waveforms under different load conditions with constant charging time method           | 92    |

| Figure 5.16. SR waveforms under different load conditions with load dependent charging time method     | od.   |

|                                                                                                        | 94    |

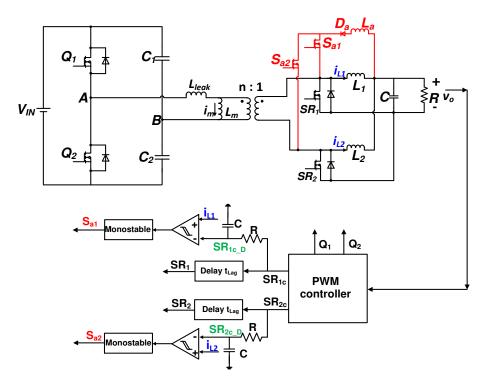

| Figure 5.17. Control scheme of load dependent soft switching method                                    | 96    |

| Figure 5.18. Gate signal sequence for load dependent soft switching half bridge current doubler        | 96    |

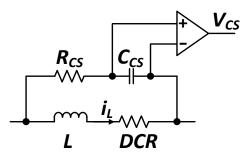

| Figure 5.19. DCR current sensing of output inductor current.                                           | 97    |

| Figure 5.20. Interleaved winding structure                                                             | 98    |

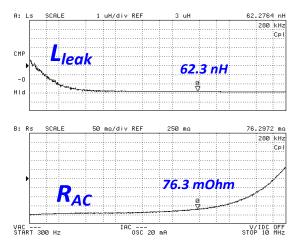

| Figure 5.21. Measured transformer leakage inductance and AC resistance.                                | 98    |

| Figure 5.22. Relationship between auxiliary inductance and the ratio between desired auxiliary charg   | ging  |

| current and output inductor's current                                                                  | . 100 |

| Figure 5.23. Equivalent resonant circuit during interval 2 (as in Figure 5.7).                         | . 101 |

| Figure 5.24. Relationship between the leakage inductance and resonance time $(t_2-t_1)$ in Figure 5.7  | . 101 |

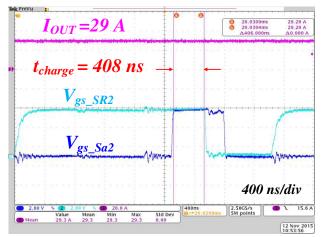

| Figure 5.25. ZVS for primary device with 29 A load current                                             | . 102 |

| Figure 5.26. Charging time for auxiliary inductor with 29 A load current                               | . 103 |

Figure 4.20. Estimated PSFB converter full load efficiency with respect to output junction capacitance.

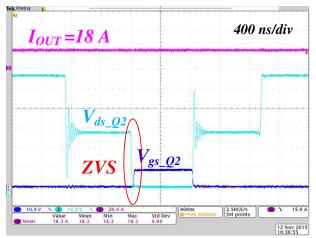

| Figure 5.27. ZVS for primary device with 18 A load current                                   | 103 |

|----------------------------------------------------------------------------------------------|-----|

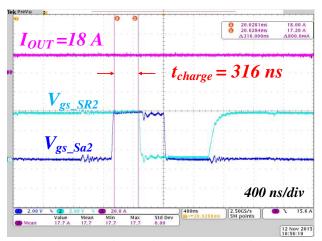

| Figure 5.28. Charging time for auxiliary inductor with 18 A load current                     | 103 |

| Figure 5.29. ZVS for primary device with 6 A load current                                    | 104 |

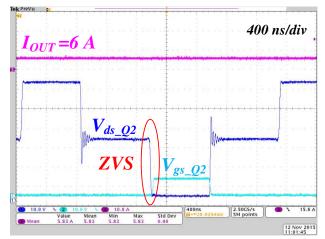

| Figure 5.30. Charging time for auxiliary inductor with 6 A load current                      | 104 |

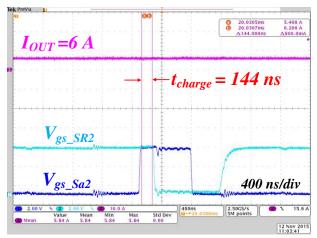

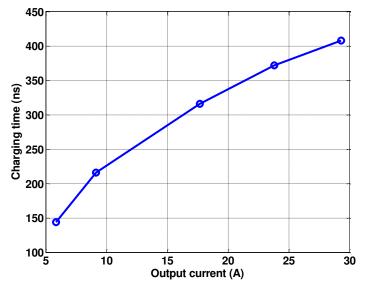

| Figure 5.31. Experimental charging time under different load conditions.                     | 105 |

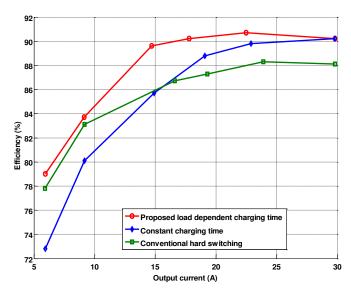

| Figure 5.32. Experimental efficiency comparison among proposed load dependent charging time, | ,   |

| constant charging time and conventional hard switching                                       | 106 |

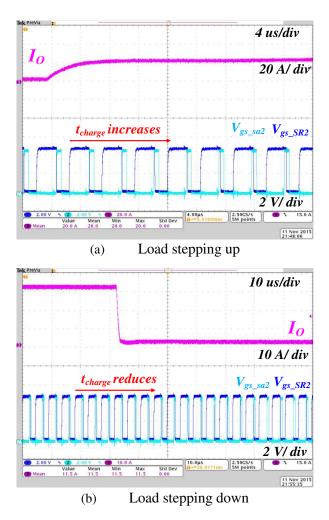

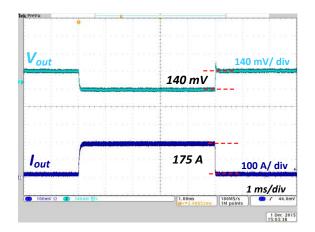

| Figure 5.33. Transient of proposed load dependent charging method                            | 107 |

| Figure 5.34. Cost comparison between IBA and HV POL                                          | 109 |

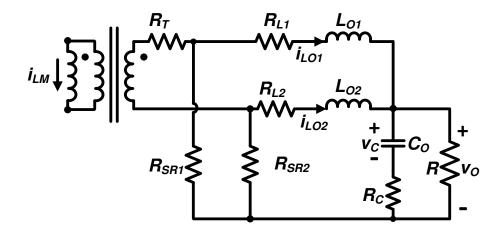

| Figure 6.1. Half bridge current doubler with state space variables                           | 113 |

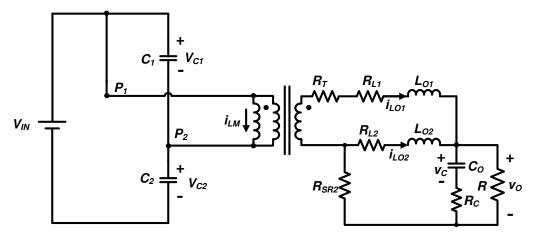

| Figure 6.2. Mode I: $Q_1$ is ON and $Q_2$ is OFF                                             | 114 |

| Figure 6.3. Mode II: $Q_1$ is OFF and $Q_2$ is ON.                                           | 115 |

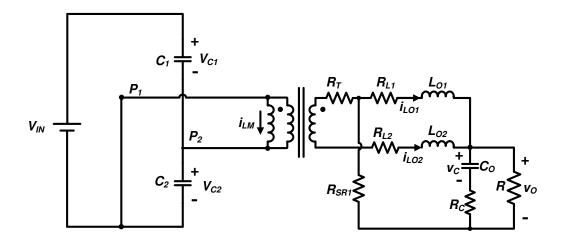

| Figure 6.4. Mode III: Both $Q_1$ and $Q_2$ are OFF                                           | 116 |

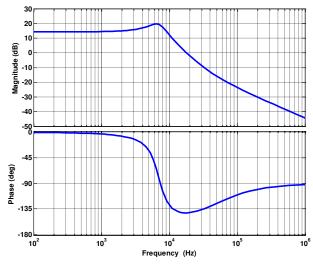

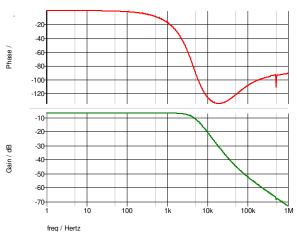

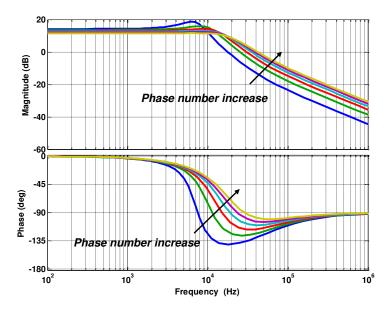

| Figure 6.5. Bode plot of half bridge current doubler.                                        | 117 |

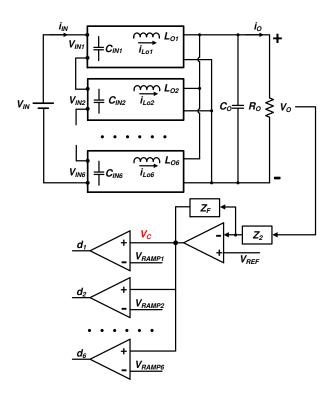

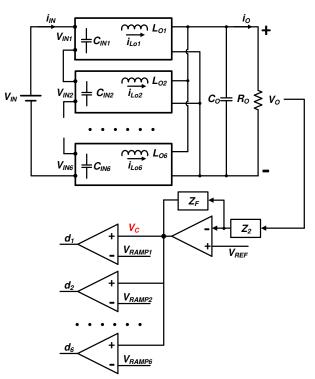

| Figure 6.6. Control diagram of common duty cycle controlled ISOP converter                   | 118 |

| Figure 6.7. Bode plot of two phase interleaved half bridge current doubler                   | 119 |

| Figure 6.8. Bode plot of equivalent single phase half bridge current doubler                 | 119 |

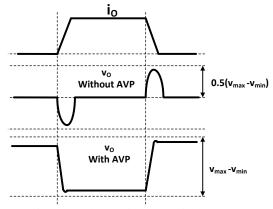

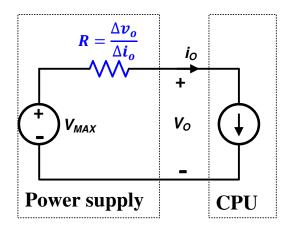

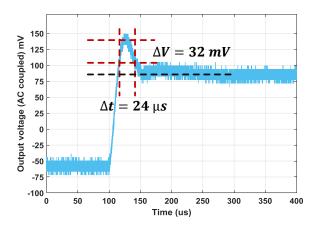

| Figure 6.9. Transient with and without AVP control                                           | 120 |

| Figure 6.10. Equivalent circuit of POL converter                                             | 120 |

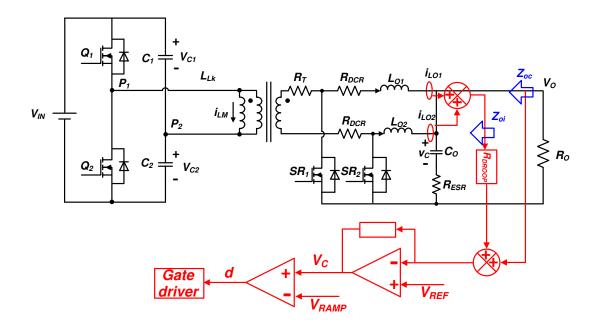

| Figure 6.11. Implementation of AVP control of half bridge current doubler                    | 121 |

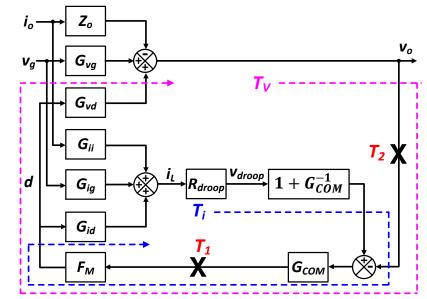

| Figure 6.12. Small signal block diagram of closed loop half bridge current doubler           | 122 |

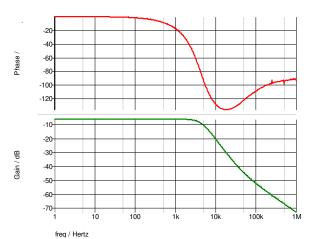

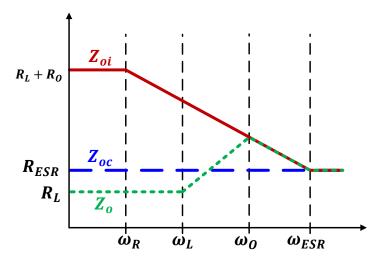

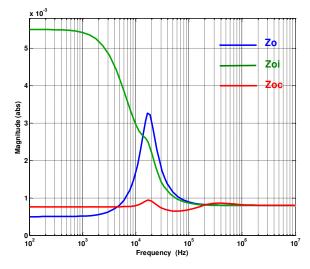

| Figure 6.13. Comparison of $Z_o$ , $Z_{oi}$ and $Z_{oc}$ .                                   | 123 |

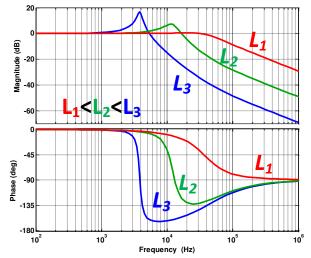

| Figure 6.14. $G_{ii}(s)$ comparison with different output inductance                         | 125 |

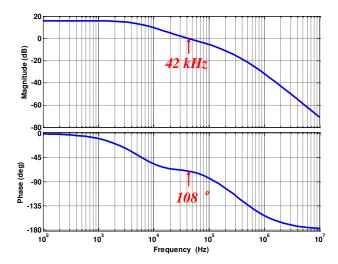

| Figure 6.15. Outer loop gain $T_2(s)$ .                                                      | 125 |

| Figure 6.16. Analytical output impedance comparison among $Z_o$ , $Z_{oi}$ and $Z_{oc}$ .    | 126 |

| Figure 6.17. Two phase ISOP connected half bridge current doubler                            | 127 |

| Figure 6.18. Output current sharing for different turns ratio.                               | 129 |

| Figure 6.19. Output current sharing for different leakage inductance.                        | 130 |

| Figure 6.20. Output current sharing for different output inductance.                         | 131 |

| Figure 6.21. ISOP system with unbalanced transformer turns ratios                            | 133 |

| Figure 6.22. ISOP system with unbalanced leakage inductance                                  | 134 |

| Figure 6.23. ISOP system with unbalanced output inductors                                    | 135 |

| Figure 6.24. Transfer function of multiphase ISOP connected converter.                       | 136 |

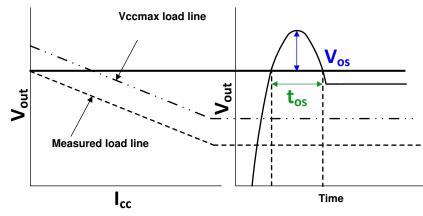

| Figure 6.25. Overvoltage requirement during load transient.                                  | 137 |

## **1.** Introduction

#### 1.1. Challenge of power supplies in data centers

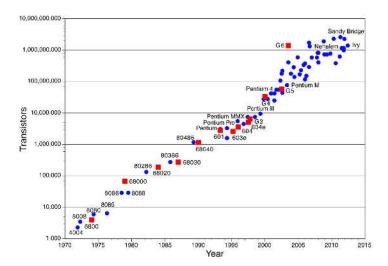

The number and performance of microprocessors keeps increasing in computer systems, which require more transistors to be integrated in the microprocessors. The increase of transistors is expected to follow Moore's law [1], which predicted that the number of components used in the integrated circuit will be doubled every two years. Figure 1.1 shows the number of transistors used in Intel's microprocessors [1], indicating the rapid growth of transistor number.

Figure 1.1. Number of transistors on Intel's microprocessors [1].

The fast increasing number of components in microprocessors challenges power supplies used in them. The power requirement is roughly proportional to the clock's frequency (f), the total lumped capacitances of the transistors (C), and the square of the core voltage ( $V_{cc}$ ) [2][3], as indicated in (1-1), where AV is the activity factor [4] which indicates the actual frequency with respect to the clock's frequency.

$$P_{CPU} = AV \cdot f \cdot C \cdot V_{CC}^2 \tag{1-1}$$

The clock frequency keeps increasing in order to get a higher operation frequency. The total lumped capacitance is also growing larger with increased component number. Therefore, the power required by the central processing unit (CPU) keeps increasing. All the power consumed by the CPU eventually turns into heat, which challenges the thermal management of the CPU as well.

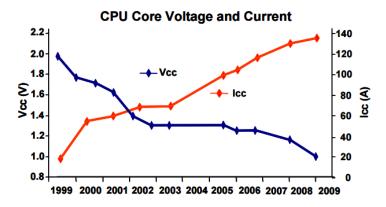

Several methods have been proposed to reduce power consumption by the CPU. One way is to reduce the core voltage  $V_{cc.}$  As indicated in (1-1), the power consumption reduces greatly with reduced  $V_{cc.}$  Figure 1.2 shows the core voltage and corresponding current, which clearly indicates that the core voltage is reducing over time [5][6]. However, with reduced core voltage, the current demand is increasing dramatically. With increased current and reduced voltage, it makes the voltage conversion ratio keeps increasing from the grid to the CPU, which further challenges the power supply used in data center.

Figure 1.2. Roadmap of Intel microprocessors [5].

#### 1.2. High efficiency power supplies

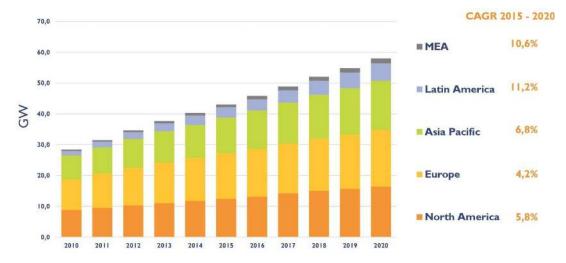

Based on earlier discussion, the energy used in data centers and processed by power supplies keeps increasing. Figure 1.3 shows the power used for data centers from 2010 to 2020

[7]. Based on the data, over 350 billion kW hours of electricity has been used for data centers in the year 2014.

Figure 1.3. Data center installed based and spending [7].

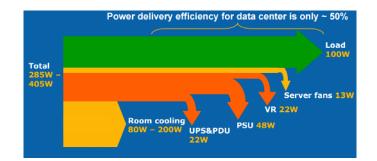

In the meantime, most of power supplies used in data centers are operated inefficiently at this time. Combining the large electricity usage in the data centers, considerable amount of energy is lost during the power conversion and distribution process from grid voltage to the point of load. Figure 1.4 is the path of power flow in data centers [8][9]. Out of 405 W input power, 200 W is provided to the cooling system, and 205 W is processed by the power supplies. Only 100 W is usable to the microprocessors from 205 W at the beginning of the power supply chain, with the remainder lost during the power delivery process, such as with power supply unit (PSU), voltage regulator (VR), and also the fans and cooling system. The overall power delivery efficiency is roughly 50 % [9]. Combining the with 350 billion kW hours used in the year 2014 and assuming 40 % of the power is used for the cooling system in the data center (which is within the range defined in Figure 1.4), around 100 billion kW hours are lost in the power supplies.

Figure 1.4. Power delivery for data centers [9].

Because of the low power delivery efficiency and large amount of electricity usage, with a 10% point loss reduction of power supplies, the electricity bill savings can be as much as \$480 million per year, and the  $CO_2$  production can be reduced as well. In the meantime, the power supplies losses reduce, the cooling requirement also decrease which would further reduce the energy used in the cooling system and reduce the energy usage for the data centers.

#### **1.3.** Motivation and strategy

Efficiency requirements for data center power supplies have been proposed by different information technology (IT) companies, such as Google [11], IBM [12], and Intel [13], with targeted efficiency above 85 %. Great efforts have been made to improve the efficiency of power supplies and reach the target, from different aspects.

#### **1.3.1.** Innovation of power supplies architecture

Figure 1.5 shows the conventional AC architecture, including a two-stage uninterruptable power supply (UPS) and a power delivery unit (PDU) which provides 208 V AC voltage to the rack. Inside the rack, another two-stage conversion in power supply unit (PSU) converts the 208 V AC to 12 V DC and feeds voltage regulators (VR) which further steps down the 12 V into 5 V, 3.3 V or 1 V depending on the load condition [8]. It is clear that the conventional AC architecture contains redundant power conversion stages, which leads to a low overall

efficiency. Therefore, removing unnecessary power conversion stages is one method to improve the system efficiency.

Figure 1.5. Conventional 208 V AC power delivery architecture [8].

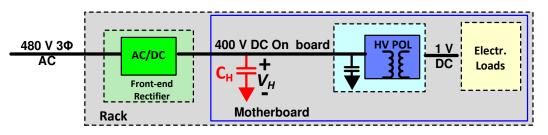

Facility voltage DC architecture (shown in Figure 1.6) is proposed for better efficiency as the DC/AC conversion stage is removed from the UPS and the AC/DC stage is removed from the PSU. At first, 48 V DC distribution voltage was used. However, as discussed earlier, the current demand is large and keeps increasing, with 48 V distribution voltage, the distribution current limits the power rating for large data centers [8]. In order to increase power capability, a higher distribution voltage is used in data center. At this time, 350 V - 400 V distribution voltage is used for the high voltage DC (HVDC) architecture [8].

Figure 1.6. High voltage DC power deliver architecture [8].

#### **1.3.2.** Improved power converter efficiency

Besides implementation of less power conversion stages architecture, another method to improve system efficiency is to use high efficiency power converters within HVDC architectures.

#### (1) AC/DC stage in UPS

Different topologies can be used as the three phase rectifier, such as voltage source rectifier, Z-source rectifier [14], current source rectifier [15][16], and Delta rectifier [17]. Wide band gap (WBG) devices are also implemented to further improve the efficiency [15][16]. Commercial product efficiency of front end rectifier is 97 % [18]. University prototypes can reach higher efficiency, up to 99 % [15][16].

#### (2) DC/DC stage in PSU

Isolated DC/DC converter is used in PSU inside the rack. Mostly, resonant LLC converter [19], or pulse-width modulated converter [20] can be used as the DC/DC converter. The efficiency is up to 95 % with commercial products [21] and up to 96.5 % with research prototypes [22].

#### (3) Voltage regulator

Synchronous buck converter is usually used as the voltage regulator (VR). Because of transient requirement, multi-phase buck converter with interleaved gate signal is used. Commercial product's efficiency is around 88 % at 15 A output current and 600 kHz switching frequency [23] and around 86.5 % at 15 A output current and 1 MHz switching frequency [24].

As the efficiency of each stage in the HVDC architecture was discussed, it clearly shows that most of the loss during power delivery is within the PSU and VR. Therefore, in this proposal, rack level delivery from 400  $V_{DC}$  to 1  $V_{DC}$  is being studied.

#### **1.4.** Dissertation outline

According to the discussed strategy discussed above, the outline of this proposal is as follows:

Chapter 2 is the literature review of current power delivery architecture and converter topologies used within data center architectures. Also, device selection criteria, soft switching and input series and output paralleled converter control techniques are discussed.

Chapter 3 further studies the widely used intermediate bus architecture (IBA) with different bus voltage. Also, a high voltage point of load (HV POL) has been proposed, and a comparison between the proposed HV POL and IBA has been made.

Chapter 4 provides the design of a phase shift full bridge converter which is used in HV POL targeting high efficiency. The impact of the primary side MOSFETs' output junction capacitance on the converter's operation and efficiency has been studied thoroughly.

Chapter 5 discusses a half bridge current doubler circuit which is another converter topology used in HV POL. A load dependent soft switching technique has been proposed with auxiliary components that can achieve zero voltage switching (ZVS) for the entire load range.

Chapter 6 provides the implement of the proposed method to achieve the adaptive voltage positioning (AVP) which is a common requirement for on-board power supplies. The impact of mismatches among modules in the ISOP is simulated as well.

Chapter 7 summarizes the work that has been done in this dissertation and the significance of the work. Possible future work is also described.

## 2. Literature Review

This chapter provides a literature review of different methods to improve the power conversion and distribution efficiency in data centers from different aspects. First, different power supply architectures are summarized. Then, different methods for efficiency improvement of the pulse width modulated (PWM) DC/DC converter which can be used in the power supplies are discussed, including device selection and soft switching method. At last, the control methods to ensure stable operation of an input series output parallel (ISOP) connected system are summarized.

#### 2.1 Data center power supply architecture

#### 2.1.1 Intermediate bus architecture

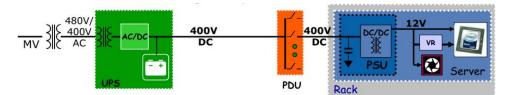

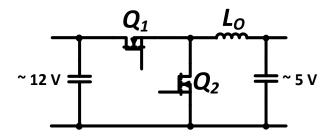

Intermediate bus architecture (IBA) [8] is a widely used architecture at this time as shown in Figure 2.1 where 1.x V is between 1.0 V and 1.9 V based on load requirement. IBA includes two power conversion stages: intermediate bus converter (IBC) and a point of load (POL) converter. IBC is usually a resonant converter and performs as a DC voltage transformer (DCX) without regulation (Figure 2.2) [25][26][27]. POL is usually a multiphase synchronous buck converter which further steps down the bus voltage from unregulated 12 V to the required voltage with regulation (Figure 2.3) [28][29]. Interleaving control is applied to the multiphase buck converter with several advantages: 1) reduces both input and output current ripple; 2) faster transient response because a smaller inductor can be used; and 3) distribute power and heat evenly [6]. The conversion efficiency of the power supply chain from 400 V to 1 V is 83.1 % based on Vicor's products [21] at room temperature and under full load condition.

Figure 2.1. Intermediate bus architecture for data center power supplies.

Figure 2.2. LLC resonant converter as IBC.

Figure 2.3. Synchronous buck converter as POL.

Some alternative converter topologies have been proposed to improve the efficiency in the POL stage and are discussed in the following section.

(1) Two-stage POL

To improve the efficiency of POL with 12 V input voltage, a two-stage POL is proposed as shown in Figure 2.4 [4][6][30]. The first stage steps down the 12 V bus voltage from IBC to a lower bus voltage, where a synchronous buck converter is implemented (shown in Figure 2.5). The second stage further steps down the 5 V bus voltage to the required voltage. For this stage, a multiphase buck converter, similar to conventional POL with lower voltage rating devices, can be implemented. Also, a switch capacitor converter, shown in Figure 2.6 is also proposed as the second stage in the two stage architecture [6]. To improve light load efficiency, the bus voltage between first and second stage is varied based on load condition. When load is light, the bus voltage is also low (3 V), and as the load increases, the bus voltage is between 3 V to 6 V.

$$\xrightarrow{\sim 12 \text{ V}} \text{Stage 1} \xrightarrow{\sim 5 \text{ V}} \text{Stage 2} \xrightarrow{1.x \text{ V}}$$

Figure 2.4. Two stage buck architecture.

Figure 2.5. Buck converter as first stage in two stage POL in Figure 2.4.

Figure 2.6. Multi-phase buck as second stage in two stage POL in Figure 2.4.

Figure 2.7. Switch capacitor as second stage in two stage POL in Figure 2.4.

#### (2) Sigma connected POL converter

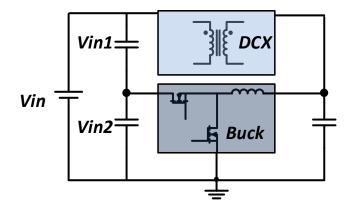

Another alternative architecture within IBA of POL is sigma connected POL as shown in Figure 2.8 [6]. Instead of parallel connected multiphase phase buck converter, Sigma architecture is implemented with one resonant converter (DCX) and a buck converter with input series connection. DCX handles power transfer while buck converter fulfills voltage regulation of the POL. Also sigma architecture allows lower voltage rating devices for both DCX and buck converter because the series input connection.

The efficiency of Sigma architecture can be calculated as (2-1).

$$\eta_{Sigma} = \frac{P_{DCX}}{P_{Sigma}} \eta_{DCX} + \frac{P_{buck}}{P_{Sigma}} \eta_{buck}$$

(2-1)

Figure 2.8. Sigma connected POL converter.

#### 2.1.2 Factorized power architecture

Vicor proposed factorized power architecture (PFA) composed with bus converter module (BCM), pre-regulated module (PRM) and voltage transformation module (VTM) as shown in Figure 2.9 [21]. PRM is buck-boost type converter which can be soft switched over the entire operational range. VTM performs as the DC voltage transformer and requires no regulation capability. Since the VTM has no regulation capability, therefore, the transient performance dependents on PRM and is more complex than IBA. The power conversion efficiency of FPA from 400 V to 1 V based on Vicor's website is 81.7 % [21] at room temperature and under full load condition. However, the distribution losses of both IBA and FPA are not included in the efficiency calculation. In FPA, a higher voltage (48 V) is used for the on board distribution voltage compared with IBA (12 V); therefore, the distribution loss in FPA is 16 times smaller compared with IBA for the same dimension board and delivering the same amount of power.

#### 2.2 High efficiency PWM DC/DC converter

Losses in the PWM DC/DC converter include: active devices losses and passive components losses. Methods to achieve the low active device losses are reviewed in this section. First, device selection criteria have been reviewed. Next, to reduce switching loss, soft switching method can be implemented. Different soft switching methods are reviewed here.

#### 2.2.1. Device selection

#### (1) Hard switching figure of merit (FOM)

Semiconductor losses in converter include three parts: conduction loss ( $P_{cond}$ ), switching loss ( $P_{sw}$ ), and gate driving loss ( $P_{gate}$ ), all of which can be expressed as the following equations.

$$P_{cond} = R_{ds(on)} I_{rms}^2 \tag{2-2}$$

$$P_{sw} = \frac{1}{2} I_{don} V_{ds} (t_{ir} + t_{vf}) f_s + \frac{1}{2} I_{doff} V_{ds} (t_{if} + t_{vr}) f_s$$

(2-3)

$$P_{gate} = V_{gate} Q_g f_s \tag{2-4}$$

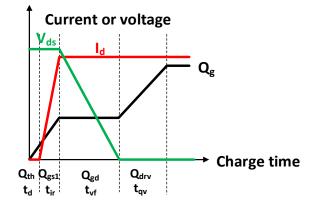

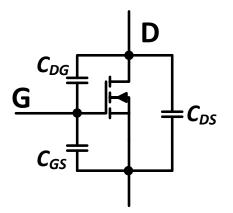

where  $R_{ds(on)}$  is the on-state resistance of MOSFET,  $I_{rms}$  is the root mean-square (RMS) current in MOSFET,  $I_{don}$  and  $I_{doff}$  are the current value at turn on and turn off transient,  $V_{ds}$  is the voltage when MOSFET is off,  $t_{ir}$  and  $t_{vf}$  are current rising and voltage falling during turn on transient,  $t_{if}$  and  $t_{vr}$  are current falling and voltage rising during turn on transient,  $V_{gate}$  is the turn on gate voltage,  $Q_g$  is the gate charge of the MOSFET, and  $f_s$  is the switching frequency of the MOSFETs. Turn on transient without considering parasitics in devices and the circuit is plotted in Figure 2.10 [31][32]. Based on [31], the charging and discharging time of the gate to drain capacitance ( $C_{gd}$  in Figure 2.11) is the dominant switching loss during each switching period, which means  $t_{ir} \ll t_{vf}$  during turn on and  $t_{if} \ll t_{vr}$  during turn off. Therefore, the switching loss of a power device can be simplified into (2-5).

$$P_{loss} \cong R_{ds(on)} I_{rms}^2 + I_d V_{ds} t_v f = \frac{R_{ds,sp} I_{rms}^2}{A} + \frac{I_d V_{ds} f Q_{dg,sp} A}{i_{g,avg}}$$

(2-5)

where  $R_{ds,sp}$  and  $Q_{dg,sp}$  are specific on-state resistance and specific gate to drain charge,  $t_v$  is the sum of voltage rise time and voltage fall time in turn off and turn on transient, and A is the effective area of MOSFET.

Based on [31], in order to get minimum loss,  $\frac{dP}{dA} = 0$  is desired. Therefore, the figure of merit (FOM) can be expressed in (2-6).

$$FOM = \frac{1}{\sqrt{R_{ds,sp}Q_{dg,sp}}} = \frac{1}{\sqrt{R_{ds}Q_{dg}}}$$

(2-6)

In first quadrant, the square root function is monotonic; therefore, figure of merit in (2-7) is used to compare devices.

$$FOM_{HS} = \frac{1}{R_{ds}Q_{dg}}$$

(2-7)

Figure 2.10. Voltage, current and gate charge during turn on transient.

Figure 2.11. Equivalent MOSFET model with junction capacitances.

#### (2) Soft switching FOM

With soft switching technique, switching loss can be minimized in devices loss; therefore, the FOM derived in (2-7) is not accurate for device selection anymore. In ZVS switching, the output charge ( $Q_{oss}$ ) in the MOSFET can be recovered and not dissipated as switching loss. However,  $Q_{oss}$  directly impacts the energy required to achieve soft switching. Based on this, soft switching figure of merit (FOM) has also been developed to select device in soft switching converters [33] as in (2-8).

$$FOM_{SS} = \frac{1}{R_{ds,on}Q_{OSS}}$$

(2-8)

With hard and soft switching figure of merit defined, they can be used to evaluate devices in a power converter targeting low losses. The higher FOM, lower device losses or lower energy to achieve ZVS is expected.

#### 2.2.2 Soft switching techniques of PWM converters

As discussed earlier, switching loss is one of the major losses in power semiconductor devices, and it increases linearly with switching frequency and becomes more significant under lighter load. For PWM converters, phase shift and asymmetrical control is widely used in order to archive zero voltage switching (ZVS), however, these methods depend on energy stored

within leakage inductance of the transformer to archive ZVS. Therefore, ZVS is lost as the load gets lighter. Also, increased leakage inductance leads to larger duty cycle loss which limits high frequency operation. Therefore, a number of methods have been proposed in order to achieve ZVS for a wider range without depending on the leakage inductance.

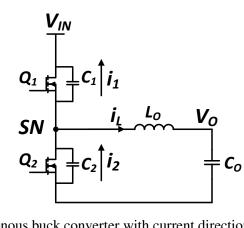

Figure 2.12 is the synchronous buck converter with junction capacitances ( $C_1$  and  $C_2$ ) of both devices ( $Q_1$  and  $Q_2$ ). Based on buck converter's operation, after the channel of  $Q_1$  is turned off, the body diode of  $Q_2$  starts to conduct the inductor current ( $i_L$ ) which is in the direction from source to drain of  $Q_2$ . Therefore,  $Q_2$  is turned on with zero voltage transition.

Figure 2.12. Synchronous buck converter with current direction of switches and inductor.

Similarly, in order to achieve soft switching of  $Q_I$ , before turn on of  $Q_I$ , the current of  $i_L$  direction at switch node (*SN*) should be the opposite of arrowed direction shown in Figure 2.12. As it is from load to source, it is called negative inductor current in the following section of this dissertation. Therefore, all the soft switching methods are implemented to generate negative inductor current before turning on  $Q_I$ .

A variety of soft switching methods have been proposed. Many of them are used in buck or buck derived circuits, which is the topology used in this dissertation. These methods have been separated into two types, first one is no active components assist method and the second one is the active switches assist method.

One straightforward method to have negative inductor current is to reduce output inductance so that large current ripple will lead to a negative inductor current at the end of the freewheeling period [19][34][35], which is called quasi-square waveform (QSW) [19][34] as in Figure 2.13. Another benefit of QSW is that the two SR devices are turned off with channel conducting instead of body diode; therefore, the body diode reverse recovery is eliminated.

Figure 2.13. Half bridge current doubler converter.

The first drawback of QSW is that the reduced output inductance leads to an increased current ripple which will further lead to an increased RMS current and conduction loss in devices and transformer and an increased turn off loss for both primary and secondary side switches. Therefore, the QSW method has a tradeoff between conduction loss and primary side devices' switching loss. The other drawback is that the output inductance is designed to allow negative current under full load, therefore, as load current reduces, the negative current peak

will increase. As the SR devices is turning off with negative peak current, the turn off loss increases as load current reduces, which reduces the converter's light load efficiency.

In order to solve the increased turn off loss of  $Q_2$ , in [23], a clamping circuit is placed in parallel with the output inductor so the current is clamped at a desired value instead of keep increasing until  $Q_1$  is turned on. In [36], an emulated diode rectification of synchronous rectifier is implemented, but it requires a zero current crossing detection to turn off the SR MOSFET, which increases the complexity of the circuit.

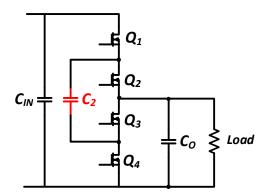

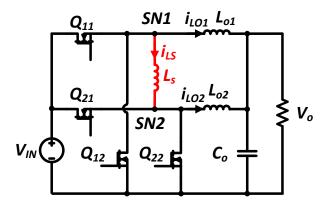

In order to solve the increased core loss of output inductor in QSW, other methods have been proposed with auxiliary components. Figure 2.14 shows the circuitry of two phase interleaved buck converter with one auxiliary inductor to assist soft switching [37][38][39]. In [37], non-synchronous buck converter (diodes are used as  $Q_{12}$  and  $Q_{22}$ ), while the method proposed in [38] is working with synchronous buck converter when duty cycle is greater than 0.5. In [39], similar method has been applied to an input series and output paralleled phase shift full bridge converter. The main idea is that when  $Q_{11}$  or  $Q_{12}$  is on while the other one is off, the auxiliary inductor will be charged and discharged based on voltage direction. Therefore, the current value before  $Q_{11}$  and  $Q_{12}$  turns on is  $(I_{LO} - I_{LS})$ . To have the auxiliary inductor current greater than the output inductor current, the current at switch node will be in the opposite direction. The apparent drawback of this method is the auxiliary inductor loss as the auxiliary inductor is conducting continuously regardless of loading condition.

Figure 2.14. Inductor assist soft switching two phase buck converter [37][38].

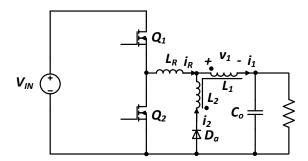

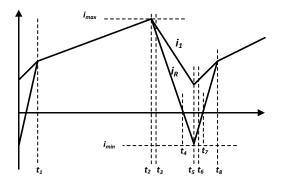

Another way to realize ZVS is implementing a coupled inductor as shown in Figure 2.15 [40]-[43]. Soft turn on of the two switches ( $Q_1$  and  $Q_2$ ) can be achieved with an auxiliary circuit branch containing an additional winding of the output inductor ( $L_2$ ), a smaller inductor ( $L_R$ ), and a diode ( $D_a$ ) in Figure 2.15. The basic idea is to provide anther power flow channel in addition to the output inductor so that the current through  $L_R$  will be negative before the turn on of  $S_1$  as in Figure 2.16. Similar to previous methods, the magnitude of the negative current peak ( $i_{min}$ ) keeps increasing as the load decreases; therefore, turn off loss of  $S_2$  increases as load reduces. Also, the constant additional power loss in auxiliary branch limits the light load efficiency of the converter. In [43], this constant auxiliary loss is solved by reducing the resonant inductor so that the current in  $L_R$  will be discontinuous as  $D_a$  blocks any negative current. However, this method changes the zero voltage turn on of  $S_1$  to zero current turn on, which means the energy stored in the output junction of capacitance of  $S_1$  will be lost in the channel instead of being recovered.

Figure 2.15. ZVS buck converter with coupled inductor [40].

Figure 2.16. Waveforms of  $i_1$  and  $i_R$  [40].

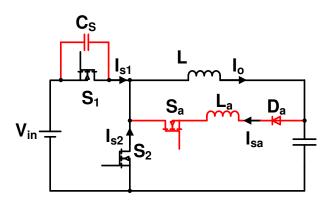

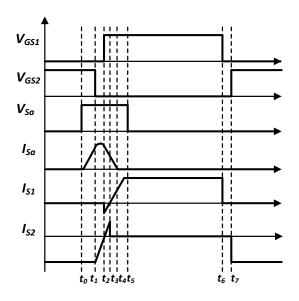

In [44]-[48], soft switching of main switch in a buck converter has been proposed with an auxiliary MOSFET, diode and inductor in parallel with output inductor as in Figure 2.17. In [44], this method is applied for a diode rectification buck converter which limits the duty cycle of the converter to be less than 0.5. In [45][46], by applying synchronous rectification, the duty cycle can be greater than 0.5, yet the operating principle is the same. Before the turn off of synchronous device  $S_2$ , the auxiliary switch  $S_a$  is turned on. Current in arrow direction will start to build up across the auxiliary inductor. As the inductor current across the output inductor L cannot change immediately, the current flowing through  $S_2$ ,  $I_{s2}$ , starts to reduce while the current  $I_{sa}$  starts to increase. Based on KCL, the sum of  $I_{s2}$  and  $I_{sa}$  equals to  $I_0$ . The charging  $I_{sa}$  will continue until the current  $I_{s2}$  becomes negative. When  $S_2$  is turned off with current flowing

though drain to source, the body diode conduction is prevented. Therefore, during the dead-time between  $S_2$  turn off and  $S_1$  turn on, resonance happens between the auxiliary inductor  $L_a$  and the snubber capacitor  $C_s$ . With enough energy stored in  $L_a$ ,  $C_s$  can be fully discharged before the turn on of  $S_1$ . Therefore, soft switching turn on of  $S_1$  can be achieved. The snubber capacitor is placed in parallel with main switch  $S_1$  so that zero voltage turn off can be achieved for  $S_1$  and  $S_2$ . The constant auxiliary circuit loss would also limit the light load efficiency of this method. In [47], a look up table (LUT) is implemented in digital controller to adjust the gate signal timing of auxiliary inductor to improve light load efficiency.

Figure 2.17 ZVT buck converter proposed in [45].

Figure 2.18. Theoretical waveforms of ZVT converter [45].

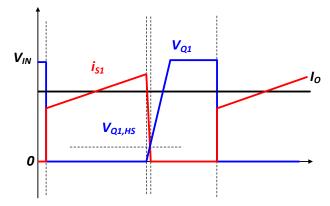

In addition to turn on loss reduction, different methods of turn off loss reduction have been proposed as well. A snubber capacitor is placed in parallel with either top switch or rectifier switch as  $C_s$  shown in Figure 2.17. During the turn off transient of  $S_1$ , the current flowing through  $S_1$  is charging  $C_s$ , therefore, the voltage to be hard switched is  $V_{Q1,HS}$  in Figure 2.19. The amount of required capacitance depends on the hard voltage  $V_{Q1,HS}$  and peak inductor current. The larger the current or the lower the hard switch voltage, the larger the snubber capacitor needs to be. However, larger snubber capacitance limits high frequency operation and also increases the capacitance loss during the turn on process.

Figure 2.19. Turn off waveforms with snubber capacitor.

In [49], a quasi- resonant method with a LC resonant circuit has been proposed as in Figure 2.20 with the operation waveforms shown in Figure 2.21. When LC is selected, the resonant frequency is also fixed; therefore, quasi resonant converter is controlled with constant on time. In order to control duty cycle, the frequency is changed, so this is a frequency regulated converter. Frequency resonant converter complicates the output filter design, therefore, pulse width modulated converter with ZCS has been proposed [50][51] as shown in Figure 2.22 and the operational waveforms in Figure 2.23. By adding a MOSFET in series with resonant capacitor  $C_R$ , the resonance time can be controlled.

Figure 2.20. Quasi-resonant ZCS converter.

Figure 2.21. Operational waveforms of quasi-resonant converter.

Figure 2.22. ZCS converter with pulse width modulation capability.

Figure 2.23. Operational waveforms of PWM ZCS converter.

However, the ZCS methods all require higher voltage rating SR devices and a higher resonant current, which will undermine the efficiency improvement by eliminating the turn off losses of the top MOSFET.

#### 2.3 Control of input series and output parallel (ISOP) connected converter

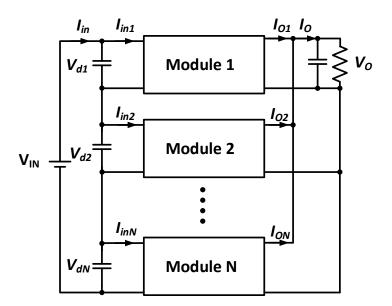

For high input voltage low output voltage application, input series and output parallel (ISOP) connected converter has several advantages compared with single converter [52]: 1) Step down ratio is greatly reduced which leads to simpler converter design. 2) Lower switching frequency can be used compared with a single converter by interleaved gating signal. 3) Higher efficiency as a result of using low voltage rating devices in the circuit.

For input series and output paralleled converter as shown in Figure 2.24, one issue is to ensure input voltage and output current sharing and prevent converters from runaway (which means one phase takes the entire input voltage and output current). A number of methods have been proposed to achieve stable operation of ISOP connected converters. The methods can be divided into two categories: common duty cycle control and active control.

Figure 2.24. ISOP connected converters.

#### 2.3.1 Common duty cycle control

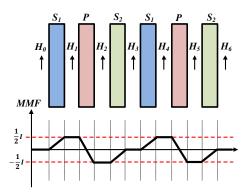

Common duty cycle control is one of the simplest and most straightforward control method in the input-output connected converters, where all the converters are fed with the same duty cycle, and only time shift the gate signal for each individual converter (shown in Figure 2.25) [52]-[58]. The ramp signal ( $V_{ramp}$ ) is phase shifted between one and another; therefore, the gate signal for each converter is also phase shifted and interleaved. Table 2.1 shows the stability of input-output connected converters with common duty cycle control with different transformer turns ratio [57] where the transformer turns ratio is n:1. For input series and output parallel connected converter, even with circuitry mismatch, such as transformer turns ratio difference, the common duty cycle control can prevent circuit from runaway where one converter in the ISOP system carrying the entire input voltage and output current, which is called self-correcting mechanism [57]. For example, in ISOP connected converter, the output voltage has to be equal. When the duty cycle is also the same, which means the average rectifier voltage is also the same. Converter with higher turns ratio will withstand higher input voltage automatically. Assuming ISOP connected converters' efficiency is comparable with each other, converter with higher turns ratio will conduct higher output current as well [57]. In the meantime, clear shown in Table 2.1, IPOP and ISOS are not stable with common duty cycle control; therefore, active control is required for them.

However, when mismatches (like transformer turns ratio, device turn on time, parasitic inductances and etc.) exist in the circuit, even sharing of input voltage and output current is lost. Converter with higher turns ratio carries slightly lower input voltage and output current [52][56][57]. Other studies also show that with common duty cycle control, runaway can be eliminated for both steady state and transient with mismatches in transformer turns ratio and leakage inductance [52]. The magnitude of difference in input voltage and output current sharing relies on how well matched each module is.

| Mode | Stability | Output current                                                    | Output voltage                                                    | Input current                                                     | Input voltage                                                    |

|------|-----------|-------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------|

| IPOP | Unstable  | Converter with <b>'n'</b><br>lower carries<br>entire load current | Equal due to<br>parallel<br>connection                            | Converter with<br>lower 'n'<br>carries entire<br>current          | Equal due to<br>parallel<br>connection                           |

| IPOS | Stable    | Equal due to series connection                                    | Converter with<br>lower 'n' carries<br>slightly higher<br>voltage | Converter with<br>lower 'n'<br>carries slightly<br>higher current | Equal due to<br>parallel<br>connection                           |

| ISOP | Stable    | Converter with<br>lower 'n' carries<br>slightly lower<br>current  | Equal due to<br>parallel<br>connection                            | Equal due to<br>series<br>connection                              | Converter with<br>lower 'n' carries<br>slightly lower<br>voltage |

| ISOS | Unstable  | Equal due to series connection                                    | Converter with<br>higher 'n' carries<br>entire voltage            | Equal due to<br>series<br>connection                              | Converter with<br>higher 'n' carries<br>entire voltage           |

Table 2.1. Suitability of common ratio cycle scheme [57].

Figure 2.25. Common duty cycle control.

#### 2.3.2 Active control

In order to make sure each module has even input voltage sharing (IVS) and output current sharing (OCS) with mismatch presented in the circuit, active control is required. Different methods of active IVS and OCS have been proposed.

One of the most widely used active sharing methods contains an input voltage feed-forward loop [59][60][61][62] in addition to the converter outer voltage and inner current loop. In [59], the input voltage is added to the reference voltage of the converter's output voltage and due to the positive output voltage gradient characteristic, IVS can be obtained. In [60], a common duty cycle is generated with the outer voltage feedback loop, and the duty cycle is further modified with input voltage sharing regulating (IVSR) loop for the first m-1 modules, and the m<sup>th</sup> module is modified with the entire error signals from the other modules. Similarly, in [61], within the

inner current loop, a common current reference is generated with the common outer voltage loop and adjusted with the input voltage sharing loop. In [62], a charge control technique used in addition with input voltage feedforward loop.

However, even though those methods can achieve an accurate input voltage and output current sharing among modules in an ISOP converter, they all required a complicated and dedicated input voltage sharing control loop, which increases circuit control complexity and reduces reliability.

## 2.4 Summary

In this chapter, a literature review on power supplies used in data centers at the rack level has been provided, including two of the most widely used architectures, IBA and FPA and some alternatives under IBA. The advantages and disadvantages of the architecture have been discussed as well.

Next, several high efficiency PWM DC/DC converters design and control methods are reviewed because they are essential parts of power delivery, including device selection criteria and soft switching technique. Figure of merit (FOM) of devices allows a simple yet effective way to select a device with possible low combination of losses (conduction and switching losses). Switching losses is one of the major contributions of device losses in PWM converters. The advantages and disadvantages of different soft switching methods have been discussed.

The last part in this chapter is the control method for the input series and output parallel (ISOP) connected converter to ensure stable operation. Two major methods have been categorized here: common duty cycle and active sharing method with pros and cons provided.

# 3. Alternative Power Supplies Architecture Design

Different types of power conversion architectures in power supplies have been discussed in the previous chapter. Besides power conversion losses, power distribution losses is nonnegligible because of the continually increasing load current requirement in servers, which in turn makes the  $I^2R$  loss continue to increase for any given distribution voltage.

In this chapter, alternative power supply architectures with potential to improve efficiency are investigated. First, on-board distribution voltage's impact on efficiency has been studied where 400 V on-board distribution voltage is proposed to greatly reduce distribution losses.

Then, different bus voltages between IBC and POL in IBA have been investigated in order to determine how much efficiency gain can be obtained by varying the bus voltage within the IBA architecture.

At last, a single stage high voltage point of load (HV POL) architecture which converts 400 V to 1 V directly has been proposed to achieve high efficiency. Converter topologies have been selected for HV POL, and a comparison between HV POL and IBA is performed.

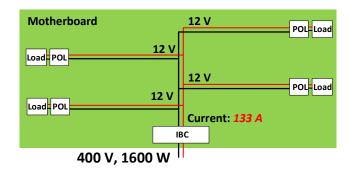

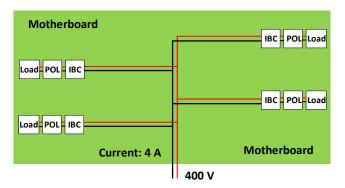

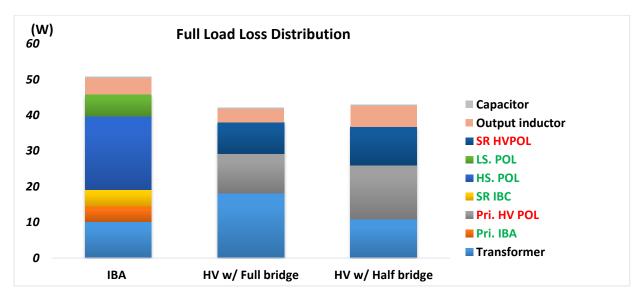

### 3.1 400 V on-board distribution voltage architecture

Based on the discussion in Chapter 1, the core voltage continues to decrease as the CPU core loss is proportional to the core voltage square [2][3]. With the low voltage and high current demands from the processor, on-board distribution losses ( $P_{dis} = I_{dis}^2 \cdot R_{copper} = \frac{P}{V_{dis}^2} \cdot R_{copper}$ ) cannot be ignored with 12 V distribution voltage which is widely used in IBA [63].

A simple case study has been performed to indicate the considerable distribution losses under low distribution voltage. A 12 V and 400 V distribution voltage that handles 1600 W power for multiple CPUs is studied as in Figure 3.1 and Figure 3.2, respectively. The size of the motherboard is selected as  $0.305 \text{ m} \times 0.244 \text{ m}$ , which is the standard Advanced Technology eXtended (ATX) size developed by Intel [64].

Figure 3.1. 12 V distribution voltage.

Figure 3.2. 400 V distribution voltage.

Table 3.1 shows the distribution loss of 12 V distribution voltage with different combinations of copper thickness and width, which indicates that the distribution loss is non-negligible. Even though distribution loss can easily be reduced by using thicker or wider copper, this will increase the cost the system. By increasing the distribution voltage from 12 V to 400 V, the distribution loss can reduce greatly as shown in Table 3.2 compared with losses listed in Table 3.1.

| Width<br>Thickness | 700 mils | 1 inches | 2 inches |

|--------------------|----------|----------|----------|

| 0.5 oz             | 477.7 W  | 334.4 W  | 167.2 W  |

| 1 oz               | 238.9 W  | 167.2W   | 83.6 W   |

Table 3.1. Loss for 12 Vdc distribution on motherboard for 1600 W load.

Table 3.2. Loss for 400 Vdc distribution on motherboard for 1600 W load.

| Width<br>Thickness | 700 mils | 1 inches | 2 inches |

|--------------------|----------|----------|----------|

| 0.5 oz             | 0.43 W   | 0.3 W    | 0.15 W   |

| 1 oz               | 0.21 W   | 0.15 W   | 0.075 W  |

To be fair, the drawback of high voltage on-board distribution voltage includes reliability and safety required by the system, which needs a more thorough design [63].

The following discussion is based on 400 V on-board distribution voltage, and distribution loss is reasonably ignored (less than 0.03 % of the load power) from the system's efficiency calculation.

#### **3.2** Bus voltage optimization of intermediate bus architecture

As intermediate bus architecture (IBA) is the most widely used architecture at this time, a study has been performed on IBA when the bus voltage is treated as one variable. Figure 3.3 shows the structure of intermediate bus architecture (IBA) where the two stages are connected in series. For most current IBA, 12 V is selected as intermediate bus voltage because fans in servers usually are powered by 12 V; therefore, no further conversion is required for the fans. However, for all other loads in servers, a voltage regulator (VR) is required to further step down

12 V to a lower voltage (5 V, 3.3 V or 1 V), which is usually fulfilled by multi-phase synchronous buck converters.

In this section, only 1 V output voltage is considered. The overall efficiency from 400 V to 1 V is the combination of the two stages efficiency as shown in (3-1), where  $\eta$  is the overall efficiency,  $\eta_{IBC}$  is the IBC's efficiency and  $\eta_{POL}$  is the POL's efficiency. A selection of intermediate bus voltage is performed to achieve high overall system's efficiency as increasing the bus voltage favors IBC but worsens POL and vice versa. The bus converter is rated at 300 W which will be connected to power two POL converters each rated at 150 W for the following studies.

$$\eta = \eta_{IBC} * \eta_{POL} \tag{3-1}$$

Figure 3.3. Intermediate bus architecture (IBA).

#### **3.2.1.** Bus converter efficiency with different bus voltage

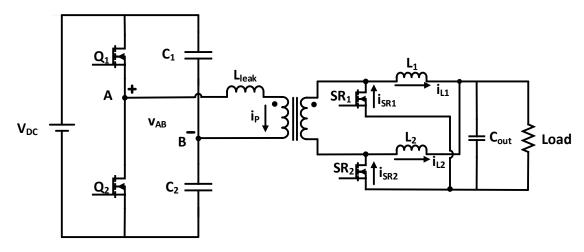

LLC resonant converter shown in Figure 3.4 is selected here as for the IBC. The input voltage is 400 V and the output bus voltage is varied from 4 V to 24 V. The switching frequency of the bus converter is 1 MHz.

(1) Primary side device selection

Table 3.3 shows the primary side device comparison of 600 V MOSFET including both Si and GaN [22]. Devices listed in Table 3.3 [22] have comparable  $R_{ds(on)}$ , but it is clear that GaN FETs have lower output charge which lead to smaller RMS current though primary side devices

and transformer and also lower gate charge current. Therefore, 600 V GaN HEMT is selected as primary side devices in the LLC converter. Similar to the investigation of alternative architectures, replacing Si MOSFETs with GaN HEMTs in the IBC converter is an effective way to increase the converter's efficiency [22].

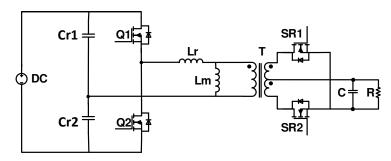

Figure 3.4. LLC resonant converter.

| Device           | $R_{ds(on)}(\Omega)$ | Output charge (nC) | Gate charge (nC) |

|------------------|----------------------|--------------------|------------------|

| TPH3006PS (GaN)  | 0.15                 | 52                 | 6.2              |

| IPP60R165CP (Si) | 0.15                 | 105                | 39               |

| FCH170N60 (Si)   | 0.15                 | 91.2               | 42               |

| AOT27S60 (Si)    | 0.14                 | 106                | 26               |

Table 3.3. Primary side device comparison for LLC converter [22].

#### (2) Transformer design

The transformer is the most lossy part among all the components in the LLC converter [22]. Different transformers have been designed based on the output voltage, and the summary in Table 3.4 includes copper thickness, core selection and the corresponding transformer turns ratio to step down the input voltage to designed output voltage. Lower output voltage from LLC converter means a higher transformer turns ratio. The losses of the transformer include both core

loss and winding loss. Skin effect and proximity effect are being considered in winding loss calculation [65] [66].

| Output Voltage | Copper     | Core Type    | Turns ratio   |  |

|----------------|------------|--------------|---------------|--|

| Output Voltage | Thickness  | core rype    | Turns Tatio   |  |

| 24 12 10 98    | Primary:   | E22/6/16     | 8, 16, 20, 24 |  |

| 24, 12, 10, 8V | 2 Oz       | PLT22/16/2.5 | 8, 10, 20, 24 |  |

| 6 A N          | Secondary: | 2 *E18/4/10  | 22 49         |  |

| 6, 4 V         | 2 Oz       | PLT18/10/2   | 32, 48        |  |

Table 3.4. Transformer design of different output voltage in LLC converter.

## (3) Secondary side device selection

The secondary side MOSFETs of LLC resonant converter are being turned on with zero voltage across them and turned off with zero current [22]; therefore, switching loss is ignored for SR MOSFETs.

| Output voltage | Device voltage (V) | $R_{ds(on)}(\Omega)$ | $Q_{g}(nC)$ |

|----------------|--------------------|----------------------|-------------|

| 4              | 25                 | 1.0                  | 31          |

| 6              | 25                 | 1.0                  | 31          |

| 8              | 30                 | 1.3                  | 20          |

| 10             | 40                 | 1.2                  | 19          |

| 12             | 40                 | 1.2                  | 19          |

| 24             | 80                 | 2.5                  | 15          |

Table 3.5. Si SR devices selection for different output voltage.

The SR devices losses include conduction loss and gate driving loss, which can be represented by  $R_{ds (on)}$  and  $Q_g$  in Table 3.5.

## (4) IBC's efficiency

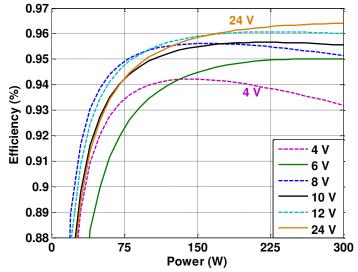

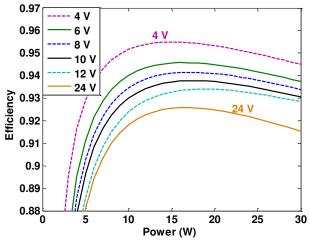

With devices selected and transformer designed in the above sections, the efficiency of the LLC converter can be calculated with different output voltage and plotted in Figure 3.5. Full load efficiency reduces with a decreased bus voltage as more output current is handled by the transformer and SR devices.

Figure 3.5. LLC efficiency at different bus voltages.

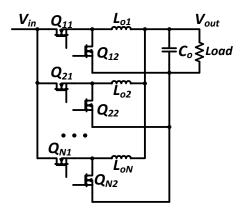

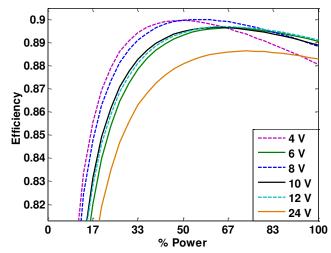

## 3.2.2. POL efficiency with different bus voltage

POL converter with five phase synchronous buck converter (shown in Figure 3.6) will be designed and discussed in this section. The switching frequency is 200 kHz for each phase, which makes the effective switching frequency 1.0 MHz. The output power is 150 W for all the cases. Table 3.6 summarizes devices selection for different input voltage with the large figure of merit (FOM)  $\left(\frac{1}{R_{ds(on)} \cdot Q_{gd}}\right)$  as discussed in Chapter 2. The same MOSFET is used for 6 V through 12 V, which is mainly because 25 V MOSFETs have more choices than 10 V though 20 V,

therefore, a better performance MOSFET at 25 V is actually available compared with lower voltage rating MOSFETs.

Figure 3.6. Multiphase synchronous buck converter.

| Input voltage (V) | Device voltage (V) | $R_{ds(on)}(\Omega)$ | Q <sub>gd</sub> (nC) |

|-------------------|--------------------|----------------------|----------------------|

| 4                 | 7                  | 1.25                 | 2                    |

| 6                 | 25                 | 0.95                 | 4.9                  |

| 8                 | 25                 | 0.95                 | 4.9                  |

| 10                | 25                 | 0.95                 | 4.9                  |

| 12                | 25                 | 0.95                 | 4.9                  |

| 24                | 40                 | 4                    | 2.2                  |

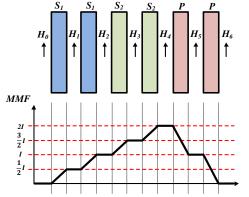

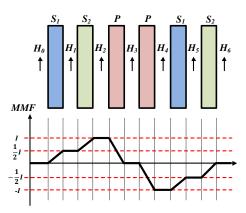

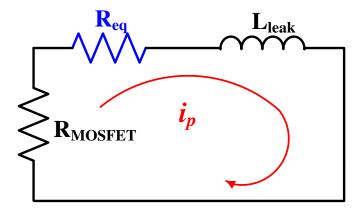

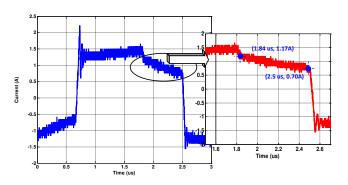

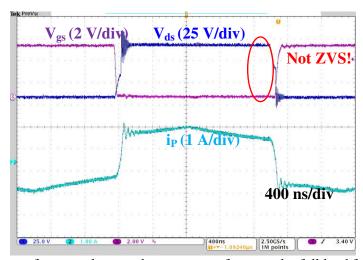

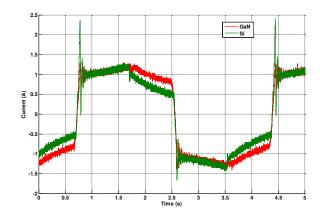

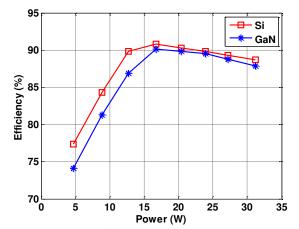

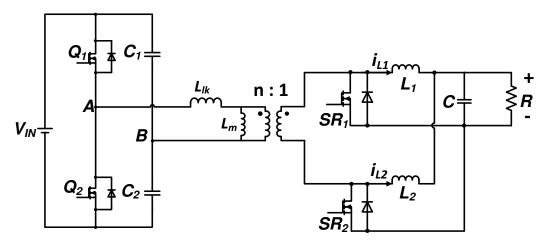

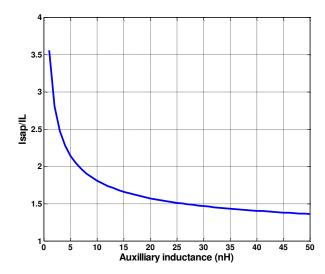

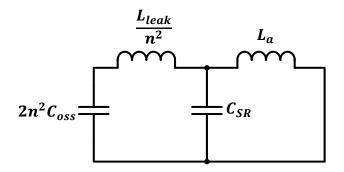

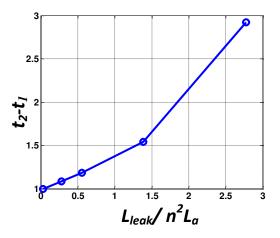

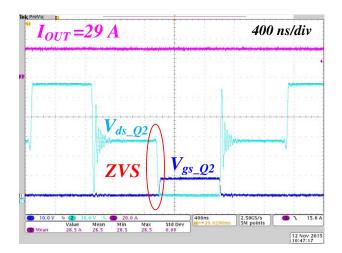

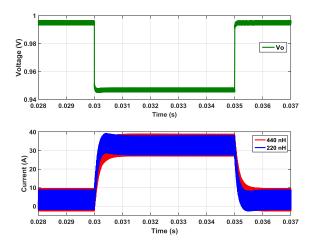

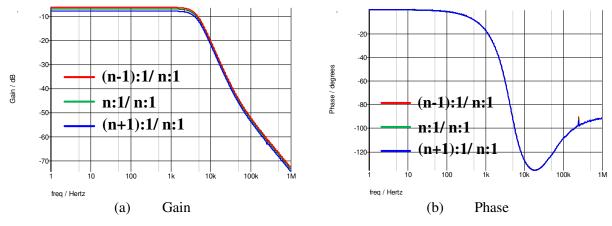

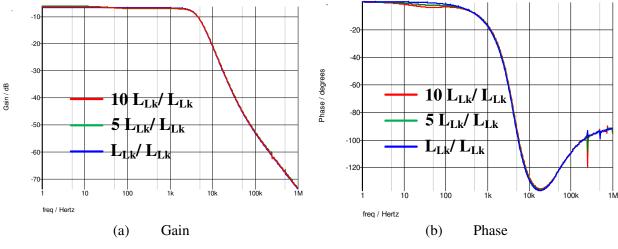

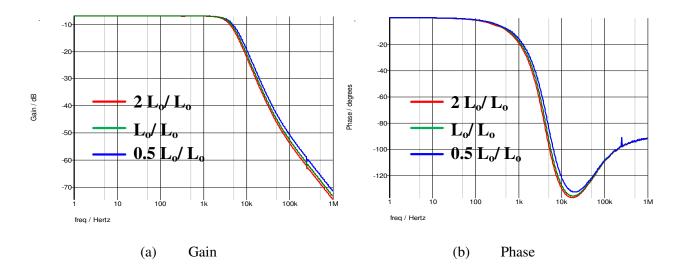

Table 3.6. MOSFET selection for different output voltage in POL.