#### Higher levels of a silicon compiler

Citation for published version (APA):

Stok, L., Born, van den, R., & Janssen, G. L. J. M. (1986). Higher levels of a silicon compiler. (EUT report. E, Fac. of Electrical Engineering; Vol. 86-E-163). Eindhoven University of Technology.

#### Document status and date:

Published: 01/01/1986

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 23. Aug. 2022

# Eindhoven University of Technology Netherlands

Department of Electrical Engineering

## Higher Levels of a Silicon Compiler

by L. Stok R. van den Born G.L.J.M. Janssen

EUT Report 86-E-163 ISBN 90-6144-163-3 ISSN 0167-9708 November 1986

### Eindhoven University of Technology Research Reports EINDHOVEN UNIVERSITY OF TECHNOLOGY

Department of Electrical Engineering

Eindhoven The Netherlands

#### HIGHER LEVELS OF A SILICON COMPILER

bу

L. Stok

R. van den Born

G.L.J.M. Janssen

EUT Report 86-E-163 ISBN 90-6144-163-3 ISSN 0167-9708 Coden: TEUEDE

> Eindhoven November 1986

COOPERATIVE DEVELOPMENT OF AN INTEGRATED, HIERARCHICAL AND MULTIVIEW VLSI-DESIGN SYSTEM WITH DISTRIBUTED MANAGEMENT ON WORKSTATIONS. (Multiview VLSI-Design System ICD). Code: 991.

Report on activity 5.1.A: Select functional description language: assemble a set of architectural components to study the mappings onto those components.

This report was accepted as a M.Sc. Thesis of L. Stok by Prof. Dr.-Ing. J.A.G. Jess, Automatic System Design Group, Department of Electrical Engineering, Eindhoven University of Technology. The work was performed in the time from 1 January 1986 to 28 August 1986 and was supervised by Drs. R. van den Born and ir. G.L.J.M. Janssen.

CIP-GEGEVENS KONINKLIJKE BIBLIOTHEEK, DEN HAAG

Stok, L.

Higher levels of a silicon compiler / by L. Stok, R. van den Born, G.L.J.M. Janssen. - Eindhoven: University of Technology. - Fig., tab. - (Eindhoven University of Technology research reports / Department of Electrical Engineering, ISSN 0167-9708; 86-E-163)

Met lit. opg., reg.

ISBN 90-6144-163-3

SISO 664.3 UDC 621.382:681.3.06 NUGI 832

Trefw.: elektronische schakelingen; computer aided design.

### COOPERATIVE DEVELOPMENT OF AN INTEGRATED, HIERARCHICAL AND MULTIVIEW VLSI-DESIGN SYSTEM WITH DISTRIBUTED

#### MANAGEMENT ON WORKSTATIONS.

(Multiview VLSI-design System ICD)

code: 991

#### **DELIVERABLE**

Report on activity 5.1.A: Select functional description language: assemble a set of architectural components to study the mappings onto those components.

#### Abstract:

The approach presented here to map an algorithmic description onto a hardware structure is the following: the algorithm is parsed and translated into a syntax tree. From this tree a special data flow graph, the demand graph, is derived. On this graph several optimisations can be done to make the graph structure better realisable. Several inefficiencies introduced by the designer may also be removed. Essential is that the optimisations transform a demand graph in a semantically equivalent demand graph.

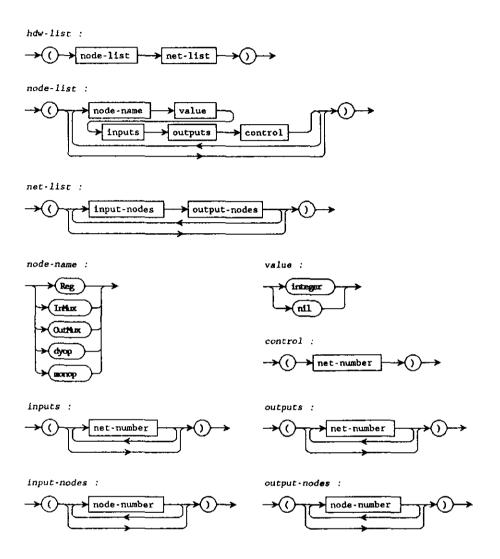

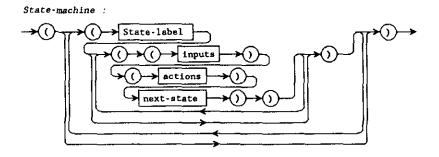

Further the demand graph is compiled into a hardware structure. This hardware structure consists of a <u>data path</u> and a <u>finite state machine</u>. The compilation is done by generating alternative implementations, using a dynamic programming technique, and choosing the optimal implementation. This choice is made with the information provided by the module library, concerning the area, dissipation and speed of the modules.

The algorithms described in this report are coded in CommonLisp.

deliverable code: WP 5, task: 5.1, activity: 5.1.A.

<u>date</u>: 01 - 11 - 1986

<u>partner</u>: Eindhoven University of Technology

author: L. Stok, R. v.d. Born, G.L. Janssen.

#### Abstract

The main problem discussed in this report is: given an algorithm represented as a program in some high level language, how do we map that algorithm onto a hardware structure that implements the algorithm.

The approach presented here is the following: The algorithm is parsed and translated into a syntax tree. From this tree a special data flow graph, the demand graph, is made. On this graph several optimisations can be done to make the graph structure better realisable. Several inefficiencies introduced by the designer may also removed. Essential is that the optimisations transform a demand graph in a semantically equivalent demand graph.

Further the demand graph is compiled into a hardware structure. This hardware structure consists of a list of modules with their interconnections and a state machine. The compilation is done by generating alternative implementations, using a dynamic programming technique, and choosing the optimal implementation. This choice is made with the information provided by the module library, concerning the area, dissipation and speed of the modules.

The algorithms described in this report are coded in CommonLisp. The module list and state machine have automatically been generated for some algorithms.

Stok, L. and R. van den Born, G.L.J.M. Janssen

HIGHER LEVELS OF A SILICON COMPILER.

Department of Electrical Engineering, Eindhoven University of

Technology, 1986.

EUT Report 86-E-163

#### Address of the authors:

ŀ

Automatic System Design Group,

Department of Electrical Engineering,

Eindhoven University of Technology,

P.O. Box 513,

5600 MB EINDHOVEN,

The Netherlands

#### PREFACE

This report is the result of my work done during my graduated period in the Automatic System Design Group (ES) of the department of Electrical Engineering at the Eindhoven University of Technology.

This group has several research projects concerning the development of tools for VLSI design. Some of these projects are contributions to the NELSIS/ICD (NEderlands ontwerpSysteem voor geIntegreerde Schakelingen / Integrated Circuit Design) project, which is a cooperation of the Dutch Universities of Technology and several companies in Great-Britain, Germany and the Netherlands.

The ESPRIT-991 project concerns Silicon Compilation. Silicon compilation is the automatic translation of a behavioural (algorithmic) description of a circuit into an implementable layout. Silicon compilation becomes increasingly important with the development of the IC technology. The technology enables to design very complex systems. These large systems cannot be designed by hand. Consequently, there will be a large market for silicon compilers in the near future.

At this place I would like to thank the group ES for the support given. Especially I would like to thank prof. J.A.G. Jess, who made this research project possible, and drs. R. v.d. Born and ir. G.L.J.M. Janssen for their useful discussions and continuous support. Furthermore I thank R. v.d. Born for proofreading this report and the suggestions he made for improvements.

Leon Stok

#### CONTENTS

| Abstract                                                                                                                                                                                            |                                                                                                                                                                          |                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preface                                                                                                                                                                                             |                                                                                                                                                                          |                                                                                                                                                                                              |

| List of figures                                                                                                                                                                                     |                                                                                                                                                                          |                                                                                                                                                                                              |

| 1.2.4. Hardware<br>1.3. Related systems                                                                                                                                                             | on level language aph constructor aph optimisations generation                                                                                                           | 1<br>1<br>2<br>4<br>6<br>7<br>8<br>9                                                                                                                                                         |

| 2.5.2. Chainer a 2.5.3. Implement 2.5.3.1. 2.5.3.2. 2.5.3.4. 2.5.3.5. 2.5.3.6. 2.5.3.7. 2.5.3.8. 2.5.3.9. 2.5.3.10. 2.5.3.11. 2.5.3.12. 2.5.3.13. 2.5.3.14. 2.5.3.15. 2.5.3.15. 2.5.3.16. 2.5.3.16. | flow analysis  ons  s and functions  or  n  o-machine                                                                                                                    | 10<br>11<br>12<br>12<br>12<br>13<br>13<br>13<br>14<br>18<br>18<br>19<br>20<br>20<br>21<br>22<br>22<br>23<br>23<br>23<br>24<br>24<br>25<br>25<br>26<br>27<br>29<br>30<br>31<br>34<br>34<br>34 |

| 3.1. Introduction 3.2. Dead node elimin 3.3. Code motion 3.4. Remove algebraid 3.5. Redundant subexy 3.6. Constant folding 3.6.1. Implement                                                         | epplications of the demand graph 1.1. Introduction 1.2. Dead node elimination 1.3. Code motion 1.4. Remove algebraic identities 1.5. Redundant subexpression elimination |                                                                                                                                                                                              |

| 4.4.1. Algorithm                                                                                                                                                                                    | tates n decisions ctions or generation of states                                                                                                                         | 43<br>44<br>45<br>45<br>47<br>48<br>49<br>50                                                                                                                                                 |

| 5. | Hardy | vare sym | nthesis                                                         | 53 |

|----|-------|----------|-----------------------------------------------------------------|----|

|    | 5.1.  | Introdu  | uction                                                          | 53 |

|    | 5.2.  | Diffic   | ulties during hardware generation                               | 53 |

|    | 5.3.  | The pro  | ocessing unit                                                   | 54 |

|    | 5.5.  | Hardwa.  | re description and register transfer languages                  | 58 |

|    | 5.6.  |          | alculations                                                     | 58 |

|    |       | 5.6.1.   | General cost functions                                          | 58 |

|    |       |          | Implementation costs                                            | 60 |

|    | 5.7.  |          | re transformations                                              | 61 |

|    |       |          | Assumptions about the hardware                                  | 61 |

|    |       | 5.7.2.   | Implementation of simple nodes                                  | 61 |

|    |       |          | 5.7.2.1. Implementation of a constant node                      | 62 |

|    |       |          | 5.7.2.2. Implementation of an operator                          | 62 |

|    |       | 5.7.3.   | Implementation of complex nodes                                 | 63 |

|    |       |          | 5.7.3.1. Generation of new state machine cycles                 | 63 |

|    |       |          | 5.7.3.2. Normal new cycle generation                            | 63 |

|    |       |          | 5.7.3.3. A new cycle on account of a conditional                | 64 |

|    |       |          | 5.7.3.4. A new cycle on account of a loop                       | 66 |

|    |       |          | 5.7.3.5. A new cycle on account of a procedure or function call |    |

|    | 5.8.  | Exampl   | e                                                               | 70 |

| 6. | Conc. | lusions  | and future research                                             | 73 |

|    | Refe  | rences   |                                                                 | 74 |

|    | Apper | ndix A:  | Syntax tree                                                     | 76 |

|    | Apper | ndix B:  | Summary of used symbols with their properties                   | 79 |

|    | Anner | ndiv C.  | Node treatment in the dynamic process                           | 81 |

|    | whher | IUIA C.  | 1. Treatment of simple nodes                                    | 81 |

|    |       |          | 2. Treatment of loops                                           | 81 |

|    |       |          | 3. Treatment of conditionals                                    | 83 |

|    |       |          | 4. Treatment of procedures and functions                        | 83 |

|    |       |          | -                                                               |    |

|    | Apper | ndix D:  | State description                                               | 85 |

#### - vii -

#### LIST OF FIGURES

| Fig. | 1.1.  | System overview                                 | Page | 3  |

|------|-------|-------------------------------------------------|------|----|

| Fig. | 2.1.  | Euclid's algorithm in PASCAL                    |      | 15 |

| Fig. | 2.2.  | Euclid's algorithm in LISP                      |      | 16 |

| Fig. | 2.3.  | Syntax tree for Euclid's algorithm              |      | 17 |

| Fig. | 2.4.  | Demand graph for Euclid's algorithm             |      | 18 |

| Fig. | 2.5.  | Demand graph for constant                       |      | 22 |

| Fig. | 2.6.  | Demand graph for put and get nodes              |      | 24 |

| Fig. | 2.7.  | Demand graph for the monadic expression: NOT(a) |      | 25 |

| Fig. | 2.8.  | Demand graph for the dyadic expression: a+b     |      | 26 |

| Fig. | 2.9.  | Demand graph for the expression: X AND Y        |      | 26 |

| Fig. | 2.10. | Demand graph for the expression: X OR Y         |      | 27 |

| Fig. | 2.11. | Demand graph for if statement                   |      | 28 |

| Fig. | 2.12. | Demand graph for while statement                |      | 30 |

| Fig. | 2.13. | Demand graph for procedure with procedure call  |      | 33 |

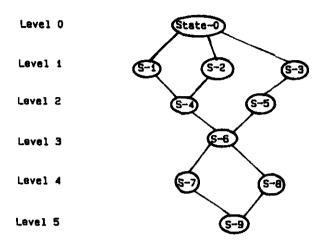

| Fig. | 4.1.  | Dynamic process lattice                         |      | 45 |

| Fig. | 4.2.  | Numbered GCD demand-graph                       |      | 51 |

| Fig. | 4.3.  | Process lattice for the GCD demand-graph        |      | 52 |

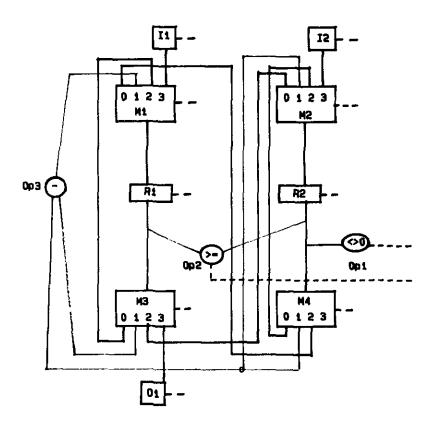

| Fig. | 5.1.  | Hardware structure                              |      | 55 |

| Fig. | 5.2.  | The control unit                                |      | 57 |

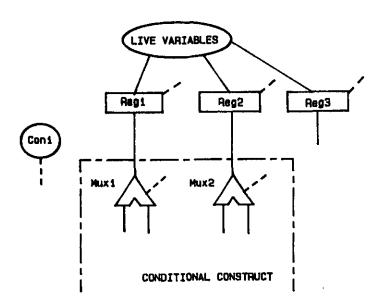

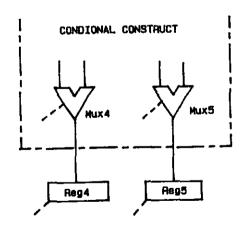

| Fig. | 5.3.  | Implementation of merge-nodes                   |      | 64 |

| Fig. | 5.4.  | Implementation of branch nodes                  |      | 65 |

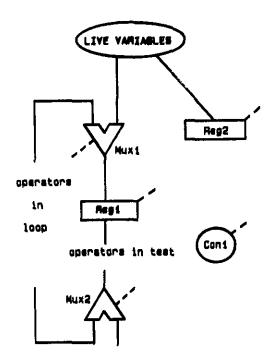

| Fig. | 5.5.  | Implementation of a loop                        |      | 67 |

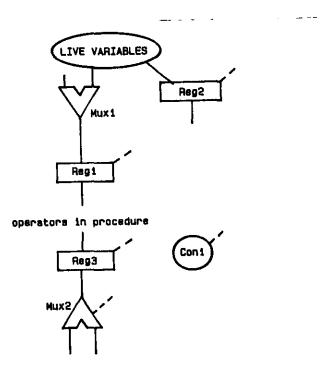

| Fig. | 5.6.  | Implementation of a procedure                   |      | 69 |

| Fig. | 5.7.  | Hardware for the GCD machine                    |      | 71 |

| Fig. | 5.8.  | State machine for the GCD machine               |      | 72 |

|      |       |                                                 |      |    |

#### 1. Hardware synthesis systems.

#### 1.1 Introduction.

The continuing improvements in the integrated circuit technology have made possible to integrate increasingly complex circuits. The design of systems currently implementable on a single integrated circuit requires extensive use of design aids for such tasks as simulation and design verification. These tools typically aid in analysing a design once it has been specified. Missing at the systems level of design are those aids which help in creating or synthesising a design. The need for such design aids will grow because nowadays the complexity of the designs increases.

Although design synthesis was formerly considered to be the realm of the creative designer, automatic and semi-automatic programs are now being developed. As we move into the VLSI era, the demand for more capable system IC's requires even greater productivity at all levels of the design process. Thus, development of synthesis tools for the creative design process has become an important research area.

Synthesis is the creation of a detailed design from an abstract specification. Digital system design actually consists of many synthesis steps, each adding more detail.

Their use promises further benefits.

- More design alternatives. Designers can specify parts

of the design and have the synthesis program fill in

details quickly, or they can change constraint

specifications so the synthesis aid specifies a

different design.

- Correctness by construction. Human designers can make errors in the synthesis steps. When it is proved that a synthesis program correctly implements a specification, such design errors are avoided.

- Multi level representations. Synthesis programs can maintain correlations between abstract specifications and detailed design in the form of a representation with multiple levels of abstraction. The representation supports the use of powerful design aids such as mixed level simulators and timing verifiers.

Another advantage of automatic synthesis is the availability of IC technology also to the non expert designer, which offers not only economic advantages but also the possibility

of protecting know-how.

Automatic design systems may be particularly of use if instead of speed and/or area the main criteria are design costs, and especially design time. Design time for new circuits can be reduced to a few days. Special purpose chips to implement certain algorithms in silicon are applications for this approach. Examples are network suited controllers, operating system functions, signal processing applications, special processors, etc. The applicability of silicon compilers will primarly be in the fabrication of circuits that do not stretch existing technology to its limits. For example: it will be very difficult for a silicon compiler to use the speed of the circuits to their limits. There always has to be a safety margin. On the other side a silicon compiler gives the designers the opportunity to use the advantages of the new technologies. The more abstract level of thinking about the design makes it possible to create more complex designs. The class of systems for which a silicon compiler can be used is large enough to merit further research.

#### 1.2 System description.

The goal of our project is to develop a system synthesising a circuit from a high level description of a system. The high level description is a behavioural description. Usually the behaviour of a circuit is described using natural language. This description deals with the functions to be implemented and the requirements concerning power, reliability, pin-out, timing, technology etc. to fulfilled. A formal description is nowadays often restricted to finite automata or function tables. Compared to contextfree languages they do not allow a comfortable description of modular or hierarchical systems. We propose a more general approach by using a description of the algorithm in a context-free language similar to common programming languages. This high-level-description is given in a language like Pascal, C or LISP.

A silicon compiler is a set of tools able to transform such a description into a realisable layout. First we present globally what a silicon compiler does. We will describe a relation between the algorithm and the hardware.

1. The processing unit will take care of the variables, of the procedures and functions and of the assignments; intuitively the variables can be associated with registers and the function names will be assigned combinational logic circuits. Finally, the assignments will become functional register transfers

of the type

R:=F(R);

meaning that the contents of the set of registers R is to be loaded with a function F of the content of these registers.

2. The control unit will take care of the program itself i.e. of the constructs while ... do, if ... then ...else, etc., of their sequencing and of the condition variables, i.e. of the binary variables providing the truth value of the conditions to be evaluated.

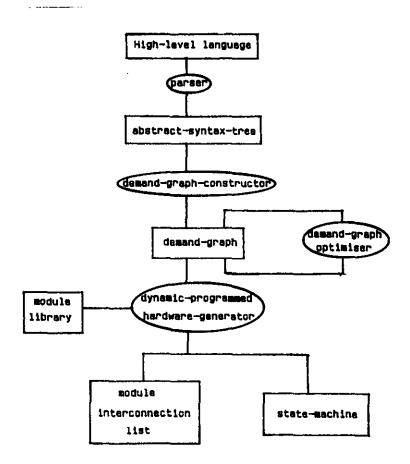

Figure 1.1. System overview.

The system is partitioned in several intermediate results and tools. The tools (shown in ellipses) convert the intermediate results (shown in boxes) to each other. This partitioning of the system has several advantages: (see

#### fig: 1.1)

- The implementation of the system can be done in several steps.

- Between all stages we can display the intermediate results and make tools to interfere in these results. This can be useful when the design system is not fully automatic, and interaction with the designer is needed to synthesise a more optimal circuit.

- Libraries can be linked together into the system at several stages. This is important when complicated designs have to be made. We can use the results gathered in earlier designs. For example: we can make a procedure library at the language level and a library containing a set of demand graphs at the demand graph level.

- The demand graph can be translated into hardware by several hardware generators. We can use an expert system, an interactive system or a system that translates the whole demand graph at once, like our present-day system does.

This report describes the transformation from the syntax tree to the demand graph and from here to the symbolic hardware representation. These transformations are coded in CommonLisp during this project. Before going into detail in the following chapters we will shortly describe the components of the system.

#### 1.2.1 The high level language.

"The symbol-making function is one of man's primary activities, like eating, looking, or moving about. It is the fundamental process of the mind, and goes on all the time."

S.K. Langer

"Man's achievements rest upon the use of symbols."

A. Korzybski

"Language ... makes progress possible."

S.I. Hayakawa

From "Language in Thought and Action" by S.I. Hayakawa, Harcourt, Brace and Company, 1949

As indicated by the quotations, languages give people the possibility to express and communicate their ideas. The

purpose of a design language is to permit efficient communication between the designer and the application design tools. But not only the communication with the machine is important. Nowadays designs are such complex that they cannot be made by one man. Thus some communication has to take place between the designers in the project team. The design language has to be suitable for this purpose too. The availability of application design tools to be used with a language is essential to the acceptance of the language by the design community.

There are several advantages when using a high level language and a high level silicon compiler:

- 1. Time consuming low level simulation and circuit verification are no longer needed when the system design is started from a high level.

- 2. The language gives the designers a communication and documentation medium. Formal description of a design is then possible.

- 3. The designers can think about their design at a more abstract level, therefore the time to develop a complex system is decreased considerably.

Once a design language is defined, it can serve as a basis for many design tools. But when defining a language we have to take care of supporting the following language features:

- Both human and machine readable functional specifications and documentation must be generated.

- Design management. The design data has to be subdivided into parts, conform to the way the designer thinks about the design.

- Behavioural descriptions. The algorithms, when expressed in the language, must reflect the designer thoughts about the algorithm. The designer has to be able to express in the language the way he thinks about the design.

- Description of a design's environment. The design has

to fulfill certain specifications, as timing, signal

levels and dissipation. Some special language

constructs are needed to express these constraints put

on the design by its environment.

- When the language is also used to serve the silicon compiler with more structural descriptions, it must be

possible to express a structural description and a timing description. It would be nice if the language is extensible.

A Behaviour Description Language (BDL) is used as the input to our silicon compiler. In this stage of our project we did neither develop a new language nor decided what existing language we could use. Instead we use the syntax tree of the language as input. The definition of the syntax tree is given in chapter 2. The syntax tree puts some constraints on the input language but there is a certain degree of freedom in choosing our language. This strategy has the advantage that we can add language structures during the project without the need to rewrite the parser each time. When all language elements are known the language can be defined or chosen. From this language a syntax tree is build using conventional compiler techniques [Aho86]. During the research described in this report the syntax tree is used as the input to the silicon compiler. Because we use a user friendly description of the syntax tree (see Appendix A), it does not raise too many difficulties to express an algorithm in the syntax tree.

#### 1.2.2 Demand graph constructor.

The next intermediate result (see fig. 1.1) is the demand graph. The demand graph represents both data flow and control flow of the system described in the BDL. Nodes represent both the operations on the data and the direction in which the data flows. The edges represent the relation between a definition and a use of a variable. The role of the nodes and the edges will become clear in chapter 2.

The demand graph is, in a sense, independent from the specification given by the designer: different BDL specifications may lead to the same demand graph. So the graph does not directly represent the BDL description, but merely represents the intention the designer has put in the description.

Because of the nature of the data flow representation, the synthesis programs can change the order of operations specified in the high-level description - so long as data dependencies are satisfied - and can change design parallelism.

The tool which converts the syntax tree to the demand graph is the demand graph constructor. The constructor traverses the syntax tree and generates the appropriate nodes and edges of the demand graph.

#### 1.2.3 Demand graph optimisations.

The optimiser converts a demand graph to a functionally equivalent demand graph. These conversions are done because they will result in a more efficient implementation of the Certain optimisations are made to improve the description made by the designer. The designer can use some elements in his description to make the description more readable. For example the use of constants can make a description easier to read but will cause inefficiencies in the implementation. The demand graph is a useful representation for these optimisations. Most optimisations are similar to those used in optimising compilers. We will optimisations here. The implemented describe some optimisations are discussed in chapter 3. A survey of optimisations used in optimising compilers can be found in [Kenn81].

Some optimisations:

- Redundant subexpression elimination. If two operators that both compute the expression A \* B are separated by code which contains no store into either A or B, then the second operator can be eliminated if the result of the first is saved.

- Constant folding. If all the inputs to an operator are constants whose values are known, the result of the operator can be computed at compile time and stored instead of the operator.

- Code motion. Operators that depend upon variables whose values do not change in a loop may be moved out of the loop, improving performance by reducing the operators 'frequency of execution.

- Strength reduction. Operators that depend on the loop induction variable cannot be moved out of the loop, but sometimes they can be replaced by less expensive operators.

- Variable folding. Statements of the form A:-B will become useless if B can be substituted for subsequent uses of A.

- Dead code elimination. If transformations like variable folding are successful, there will be many operators whose results are never used. Dead code elimination detects and deletes such operators.

- Procedure integration. Under certain circumstances, a procedure call can be replaced by the body of the

procedure being called.

Some other techniques from the optimising compilers can be used during the hardware generation. For example register allocation, scheduling of operations and detection of parallelism.

#### 1.2.4 Hardware generation.

The last step consists of transforming the nodes of the optimised data flow graph into circuit components during the dynamic programming pass. The technique of dynamic programming is used to generate the alternative hardware configurations. Chapter 4 will cover the dynamic programming while chapter 5 describes the generated hardware.

The generated hardware system appears as decomposed in two interconnected parts: the control unit and the data path (processing unit). The two units cooperate by exchanging various signals: the control unit provides the processing unit with command signals, to inform the latter of the next operation to be carried out. Typically, command lines correspond to control variables of programmable computation resources or to register control. On the other hand the processing unit provides the control unit with binary signals called condition variables. These condition variables provide the control unit with the relevant information about the past history of the computation to allow decisions about the next step of the computation.

The synthesis can be done using high level primitives such as:

- registers of width n

- adders of width n plus m

- multipliers of width n times m

- n to m multiplexers

- ALU's of width n

That means that no fixed set of hardware modules exists in the library, but there exists a basis set that can be extended according to the specific design needs. Thus for each operator node in the demand graph a hardware operator can be generated by a structure generator. This can be done by taking a module from the library, modifying it and combining it with other library modules until the function of the demand graph node is attained.

The control synthesis is done during the synthesis of the data path. If some operators have to be used twice or more, they have to be multiplexed and controlled. Second, the need for an explicit control of the data path, originates from the control nodes. Control synthesis is performed by constructing a finite state machine. Once the data path structure is allocated, the control signals are fixed (e.g. load inputs in registers, select inputs in multiplexers, comparators, etc.). outputs from States and transitions are assigned according to the predecessor successor relation in the demand graph. The data path description and the finite state machine description serve as input for the underlying tools in the silicon compiler.

#### 1.3 Related systems

In this section we describe a few research projects, concerning VLSI-design, starting at the highest level of the IC-design: the algorithmic description in a high level At Carnegie-Mellon University [Hitch83], [Thom83] and [Black85] research is done on implementation of behavioral descriptions. Another project is within the Fifth Generation Computer Systems (FGCS) Project in Japan [Mano85]. An expert system is used to translate a description in OCCAM to a CMOS layout. The last research project we will mention is from University [Camp85], [Rosen85] and [Rosen84].

#### 2. Demand graph construction.

#### 2.1 High level data flow analysis.

For the data flow analysis we want to perform, we can rely on the results of the research done for optimising compilers. The overwhelming majority of previous research in data flow analysis is concerned with low level analysis. Such analysis algorithms act upon a program representation, in which the only control flow structures are conditional jumps [Al170]. The structure of the program disappears in the control flow graph representing the algorithm. In a control flow graph nodes represent basic blocks, which are to be executed in linear fashion, and the arcs represent possible flows of control.

But presently new techniques are developed. They operate on a program representation, typically a parse tree or an abstract syntax tree, which includes all of the high level control flow structures present in the source program. High level data flow analysis techniques can be found in [Rose77], [Babi78], [Kenn81] and [Veen85].

The main reason for performing a high level data flow analysis is that the structure of the program is preserved. But there are some other advantages:

- With a good data flow technique it is possible to locate the concurrency of the algorithm represented by the syntax tree. We need this information to be able to exploit the parallelism in the algorithm.

- Several optimisations can be done during the data flow analysis. These optimisations offer the possibility to make the algorithm more suitable for implementation. Very important during the hardware generation is the analysis of dead variables. We must decide which variables have to be stored and which variables are not used anymore at a given moment.

We have chosen the demand graph [Veen85] as the representation for our algorithms. The demand graph method is used to perform this data flow analysis that results in the demand graph.

The demand graph method consists of four phases: syntactic-analysis, demand-graph construction, application and extraction. The syntactic analysis is performed by the parser, while the demand graph constructor performs the second phase.

The demand graph is a convenient program representation to carry out various flow analysis applications. The application analysis consists of depositing initial information in the demand graph nodes and propagating the information through the demand graph, combining the information when appropriate. The analysis has to be concerned only with data flow, since all control flow operators have already been interpreted.

After the demand propagation all information is stored in the nodes and arcs. Extraction can take place and all information can be extracted and interpreted in the right manner to be valuable.

The structure of this chapter is as follows: first general descriptions of the syntax tree and the demand graph are given in the following two sections. Then an example of an algorithm with its syntax tree and demand graph are treated. In the remainder of this chapter the implementation of the demand graph method is explained. These sections also contain exact information about the outlooks of the syntax tree and the demand graph in this implementation in CommonLisp.

#### 2.2 Syntax tree.

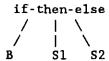

The syntactic analysis is straightforward and converts a program into a syntax tree representation. This analysis is done by a parser. A parser removes all information, that makes the program more readable for humans, but does not contain useful information. The (abstract) syntax tree is a condensed form of the parse tree useful for representing language constructs. The production:

might appear in the syntax tree as:

In the syntax tree, operators and keywords do not appear as leaves, but rather are associated with the interior node that would be the parent of those leaves in the parse tree. In this report both the forms parse tree and syntax tree will be used to indicate the abstract syntax tree.

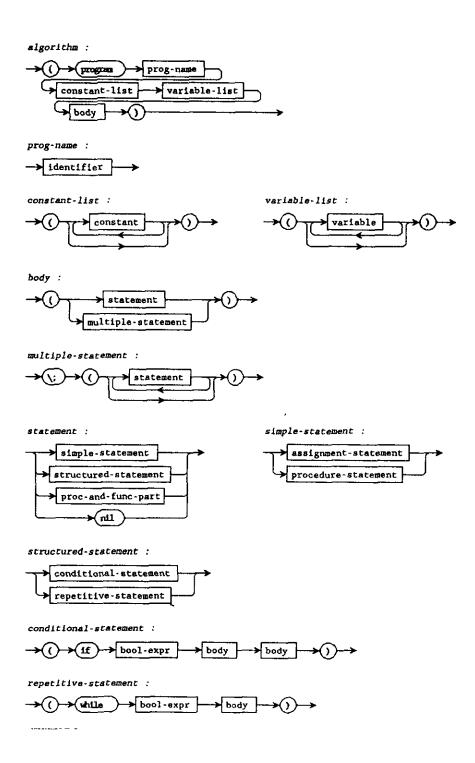

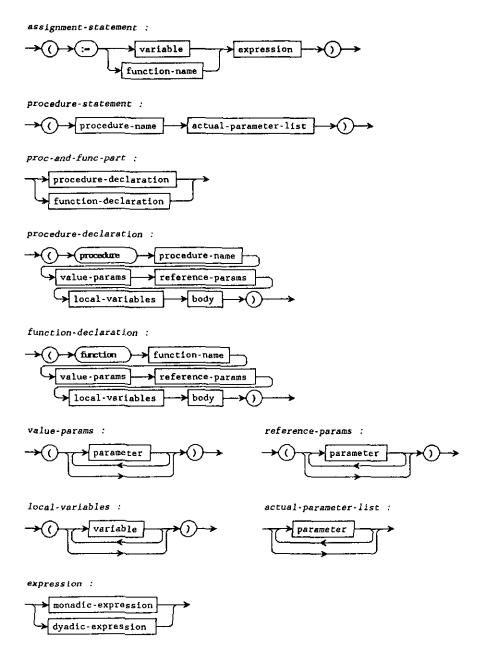

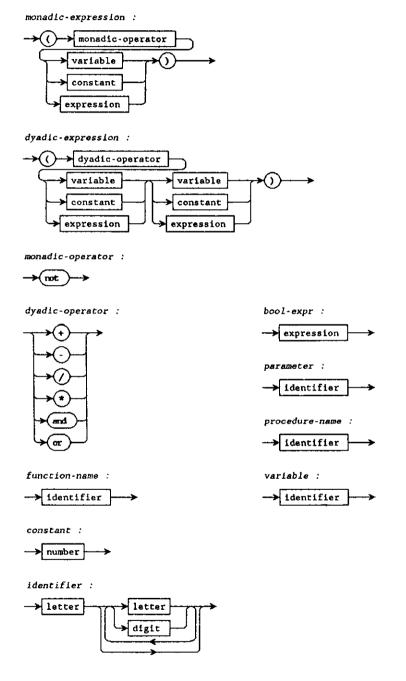

A complete summary of the abstract syntax tree, the demand graph constructor can work upon, is given in Appendix A. An algorithm is a list which starts with the symbol "program". The name of the algorithm is followed by some declarations and the program body. In this body procedures and functions can be declared and called, the usual dyadic and monadic operators can be used and some special control structures can be specified.

Here we will describe some semantics of the syntax tree. These are properties of the language, not reflected in the syntax tree, but determined by the interpretation of the program, made by the demand graph constructor.

#### 2.2.1 Declarations.

The syntax tree is expected to be free from declarations of variables and constants. These have to be put in special tables when building the syntax tree from the program description. It's expected that the declaration of all variables and constants is checked before building the demand graph. The lists connected to the "program" identifier indicate only which variables are used, so they contain only symbols that are seen as variable or constant names. The symbols that indicate a constant name are identified by the property value, which has the value of the constant. This value is used in the demand graph instead of its constant name, currently only integer values are supported. Constants may only be declared in the program environment. They can not be declared locally in the procedures.

#### 2.2.2 Procedures and functions.

The interpretation of the definition of functions and procedures is made within a global environment. Thus, procedures defined in another procedure may be called from outside that procedure. This is a result of the current implementation but can easily be altered if desired.

#### 2.2.3 And and Or.

And and or are in essence dyadic operators, but are treated in a special way. When for example the evaluation of the expression A in A or B delivers the true value, expression B is not evaluated. Thus we perform a conditional evaluation from left to right. The same holds for and if the first expression delivers the value false.

#### 2.2.4 Arrays.

Arrays are not allowed in the current syntax tree. Considering it is a hardware language, the implementation of arrays has to be one of the first extensions made in the future.

#### 2.2.5 *Types*

There are more constraints on the input language, not determined by the demand graph constructor, but by considering it as a hardware description language. One of these constraints is concerned with the types of the variables. Proposed is to use only one type : integer. can define the precision of the integer by describing how many bits should be used. This information can be entered in the graph in the constant nodes and the get nodes. The information can then be propagated through the whole graph, until each processing node knows how many bits it has to process. Thus only at the entrances of the graph (constant and get nodes) you have to specify the bit width. The design system then calculates the bit widths of all the data paths and operators in the data paths. This information is not present in the syntax tree. The parser has to make some additional lists, during the translation of the algorithm to the syntax tree, in which this additional information about the variables is stored.

#### 2.3 The demand graph.

The demand graph is a graph which describes the data flow in a program. It does not contain any explicit control structures: these have all been interpreted during the data dependency analysis and their effects have been expressed in interface nodes. Interface nodes encode the static ambiguity of data dependency: they appear wherever data dependency is influenced by conditional control flow.

The demand-graph-construction transforms the syntax tree in a demand-graph. This is done by adding extra nodes and arcs that encode data dependencies, and by removing control flow nodes that are not essential to the meaning of the program. Nodes that do not in some way construct a new value are not part of the demand-graph: Variable and Assign nodes, for instance, are left out, while a plus node constructs a new value and is therefore part of the demand graph.

#### 2.4 Example: The GCD-machine.

In the example some terms are used that will be declared later. These will become clear when the remainder of this chapter is read. However, the reason the example is presented here is to give the reader an idea of what is going on during the demand graph construction.

The well-known Euclid's algorithm to calculate the greatest common divisor (GCD), is taken as example for the demand graph construction.

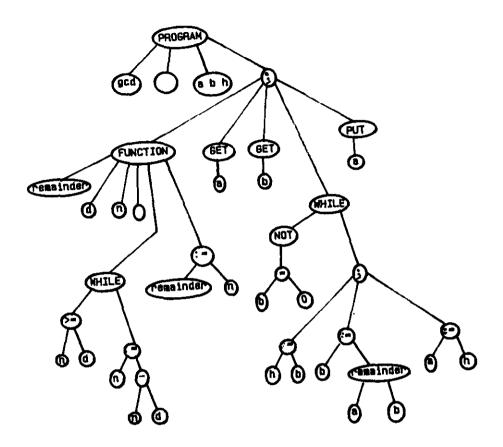

The algorithm is described in two input languages Pascal (see fig. 2.1) and LISP. (see fig. 2.2) These descriptions can be translated into the same syntax tree (see fig. 2.3). When we look at the syntax tree, we recognise the function that calculates the remainder. Furthermore, the two while-loops, the get and put operations with their arguments and the call to the function remainder can be found.

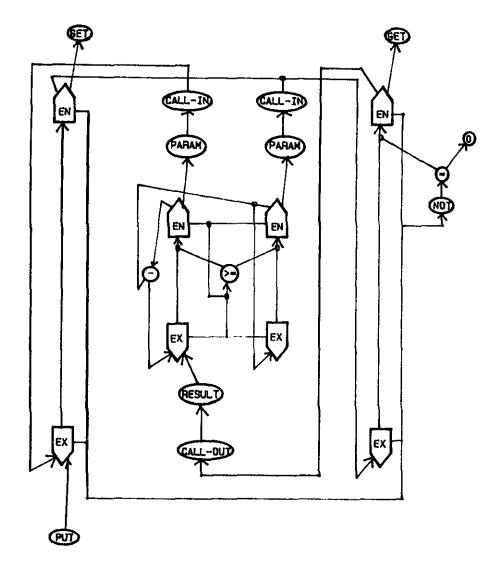

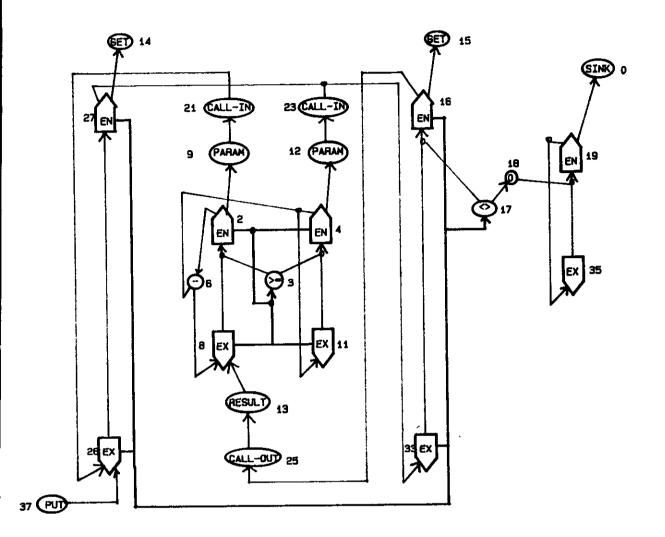

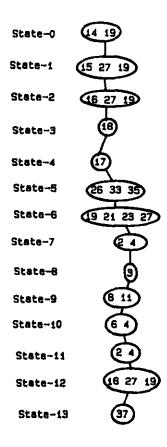

This syntax tree is transformed to the demand graph (see fig. 2.4) by the demand graph constructor. In the demand graph we find the data flow of the algorithm. First the two variables a and b are read by the get node. The get nodes represent the IO-protocol needed. These values are entered through entry nodes (EN) in a loop. This loop exchanges the values for a and b and calls the function remainder (call-in nodes) while the output of the test node (NOT) is true. Through the param nodes the values reach the second loop. Here the value of d is unchanged (direct connection between entry and exit node in the rightmost EN-EX nodes). The value of d is subtracted from n each time the loop is traversed, by the - node, as long as the >= nodes output remains true. When false, the value of n is transported through the exit node to the result node and through the call-out node back to the main loop. After finishing this loop, the put node produces the value of a, which is the greatest common divisor of the initial a and b.

```

program gcd (input, output);

var a, b, h : integer;

function remainder (n, d: integer): integer;

begin

while n >= d do

\mathbf{n} := \mathbf{n} - \mathbf{d};

remainder := n;

end; {remainder}

begin {gcd}

readln(a, b);

while b <> 0 do

begin

h := b;

b := remainder(a, b);

a := h;

end; [while]

writeln(a);

PASCAL PROGRAM

end.

```

Figure 2.1. Euclid's algorithm in PASCAL.

#### **EUCLID'S ALGORITHM**

Figure 2.2. Euclid's algorithm in LISP.

Figure 2.3. Syntax tree for Euclid's algorithm.

Figure 2.4. Demand graph for Euclid's algorithm.

#### 2.5 Demand graph method.

#### 2.5.1 Mechanism for descending the syntax-tree.

The demand-graph constructor has as its input the abstract syntax tree description of the program. The conversion is achieved during a recursive descend of the tree. The algorithm is best understood if each node is considered to be an active object that can alter the graph by adding new nodes and arcs. This process is called attaching the node to the demand graph. The algorithm is implemented by a collection of attach-procedures, one for each kind of node in the syntax tree, including the nodes that will not become part of the demand graph. The construction is started by

attaching the program node and proceeds by recursively attaching all its descendants in an order corresponding to the left to right evaluation order. The descend of the parse tree is achieved by going through the list structure, defining the syntax tree, and calling the appropriate attach procedures.

#### 2.5.2 Chainer and cocoon mechanism.

#### Chainers.

The complicated part of the demand graph construction is the building of the appropriate use-definition graphs. This is controlled by a set of objects called chainers and cocoons. Each chainer contains a deflist and an uselist. During the construction one chainer is always designated as the current-chainer. In the deflist of this current-chainer a variable is stored when it is defined. Defining a variable means: giving the variable a new value. So in the deflist are stored the variable name and the node identifier of the node in which it was last defined. In general this will be an assignment node. When a variable is used one can look up in the deflist where it was last defined and make a new arc from the use to the definition of the variable. If in a sequence definition-usesequential code segment the definition-use for one variable occurs, the first use is connected to the first definition and the second use to the second definition. The two definitions are unrelated and the fact that the two groups employ the same variable name has no influence on the demand graph.

In the deflist there are other items than variable names. These are called pseudo-variables. They are used to store a reference to a certain node. For example, the node identifier corresponding to the pseudo-variable 'Value, is the node which produced the last new value. This is used in assignments where the left hand side has to point to the last produced value of the right hand side.

A variable is said to be exposed used if it is used in an environment in which it is not earlier defined. The variable is put in the current-uselist, and an interface node is made for this variable. So the uselist contains pairs, with in each pair a variable name and a node identifier. The function of the uselist seems a little bit strange at the moment, because normally it is not allowed to use a variable before it is given a value (defined). But in the next section the role of the uselist will become clear.

Cocoons.

There are expressions that need special treatment because of effect on use-definition analysis. For example procedures, loops and conditionals. Whenever during the traversal of the syntax tree such an expression is encountered a new cocoon is created. The creation of a new cocoon is implemented by making a new deflist uselist environment. In this new environment the subgraph corresponding to the expression can be attached in isolation from the remainder of the demand graph. There are different kinds of cocoons corresponding to the different kinds of special expressions. Each special expression contains one or more subexpressions, called branches. For each branch a new chainer is created, which is designated as the current chainer when that branch is attached. When all branches are analysed a series of separate demand graphs, one for each branch is available. Each branch contains two lists: a deflist and a uselist. The deflist contains the last declaration of all variables within that branch, called the exposed definitions. The uselist contains all variables which are used in the branch before they are defined, called the exposed uses.

After all branches have been analysed the cocoon is dissolved, which involves the creation of two series of interface nodes, one for the outputs and one for the inputs, and the connection of these to the subgraph and the surrounding graph. For the exposed uses, input nodes are made and these are connected to the use in the branch and to the previous definition in the surrounding graph. For the exposed definitions, output nodes are made and connected to the defining nodes in the branch. They are not yet connected in the surrounding graph but they are put in the deflist, corresponding to the surrounding graph, so they can be connected later.

The chainer and cocoon mechanism for each kind of expression are explained in the next sections where the attaches of all kind of expressions are described.

#### 2.5.3 Implementations of the attach procedures.

#### 2.5.3.1 Implementation in LISP.

In this section the implementation of the syntax tree and the demand graph in CommonLisp are described.

The syntax tree is implemented as a list in which the arcs are represented by "(", indicating that a new level in the parse tree is entered, and ")", indicating that a level is terminated and the closest higher level is entered again. The exact syntax of each tree element can be found in the

descriptions of the attach procedures.

A special graph structure is developed for the demand graph. A graph is a LISP symbol with two properties: the node-list and the edge-list. The node-list contains the nodes, identified by a LISP symbol with prefix Node- and suffix a unique number. The same holds for edges with the prefix Edge-. A node has the properties: type, indicating the node type (constant, operator), in-edges, a list of incoming edges and out-edges, a list of outgoing edges. An edge has the from-node and to-node properties, besides the type property.

Furthermore the various stacks and deflists and uselists are implemented as LISP lists.

2.5.3.2 Form in which the attach-descriptions are given.

The attach-procedures for each kind of expression that is allowed in the syntax tree are given in the next sections. The descriptions will be presented in two parts:

- The syntax of the expression in the syntax tree, in EBNF.

- 2. How the expression is attached to the demand graph.

Some attach-procedures are explained in a figure. The abbreviations used in the nodes have the following meaning:

Dx : Node which defines a variable x. Ux : Node which uses a variable x.

The following drawing convention is used in the figures: Operator and constant nodes are circled, control nodes look like "houses" and ellipses are special nodes with their meaning in it. (see fig. 2.5).

In the following sections some references to the implementation will be made. Names surrounded by asterisks (\*) reference to the names of LISP structures used in the implementation. Names preceded by a quote (') reference to names used in LISP to indicate a certain property or its value.

Detailed information about the demand graph is given in Appendix B.

#### 2.5.3.3 Attach of constant.

#### 1. <integer>

2. A node with the value of the constant is created with an outgoing arc, which has the 'type 'source to the sink-node: Node-0 (see fig. 2.5). and the node is placed in the \*current-deflist\* under the pseudovariable name 'Value. The sink-node is the node to which all constant nodes are connected. It is only used for initialisation purposes. When a constant node is attached within a special construct, an interface node to the surrounding environment is created. These interface nodes will eventually lead to the sink.

Figure 2.5. Demand graph for constant.

#### 2.5.3.4 Attach of a symbol.

#### 1. <symbol>

If <symbol> is a member of the property list 'constant-list of the \*program-name\*, it is a name for a symbolic constant and attached as the value of that constant (see previous section). Otherwise it is treated as a variable.

2. If the variable 'is-a-def(inition) then the <symbol> is put in the \*current-deflist\* with node use('Value), else the pseudo-name 'Value is made to point to the last definition of the variable <symbol> found by use(<symbol>).

- 2.5.3.5 Attach of assignment.

- 1. "(" ":=" <left-hand-side> <right-hand-side> ")"

<left-hand-side> has to be a symbol describing a

single variable. <right-hand-side> may be any

expression that creates a value which can be assigned

to the <left-hand-side>.

- 2. The <left-hand-side> has to be a single variable because a value is assigned to it. The property 'isa-def of the variable is set true because the variable is defined here. First the <right-hand-side> is attached and use('Value) contains the node that delivers the value to be assigned to the <left-hand-side>. This is done during the attachment of the <left-hand-side>. See also the next section.

- 2.5.3.6 Attach of a sequence.

- 1. "(" "\;" {<arg>} ")"

- 2. Calls the attach procedure for all its arguments from left to right.

- 2.5.3.7 Attach of a get.

- 1. "(" "get" (<variable>) ")"

<variable> is a symbol, defined in a variable list.

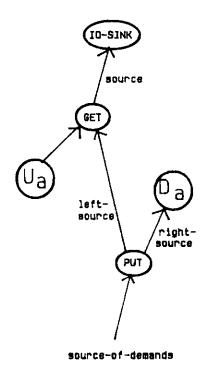

2. There is a special path for the get and the put nodes. This path represents the succession of the read (get) and write (put) operations specified in the algorithm. This path is controlled by the pseudo variable 'Standard-IO. The first get or put node is connected to 'Node-1 which is the 'IO-sink. The following nodes are connected to their ancestors with a source edge. In this way a path of get and put nodes is formed. When the graph construction is finished the property 'source-of-demands of the \*program-name\* is set to the last definition of the 'Standard-IO variable. This property marks the beginning of the IO path. The get node is defined in the \*current-deflist\* together with the variable it gets. Each variable gets its own get node. (see fig. 2.6).

#### 2.5.3.8 Attach of a put.

1. "(" "put" {<variable>} ")"

<variable> is a symbol, defined in a variable list.

2. For each variable a put node is made. This node is put in the IO chainer with its left-source edge as described in the previous section. Further the node is connected to the last definition of the variable, that has to be put, with its right-source edge (see fig. 2.6).

Figure 2.6. Demand graph for put and get nodes.

#### 2.5.3.9 Attach of a monadic operator.

1. "(" <monop> <arg> ")" ,

<monop> is defined in \*monop-set\*. <arg> must deliver a value.

Makes a new node with 'type <monop> and connects this node to the value delivered by the <arg> with an arc 'source and defines 'Value as the node itself (see fig. 2.7).

Figure 2.7. Demand graph for the monadic expression: NOT(a).

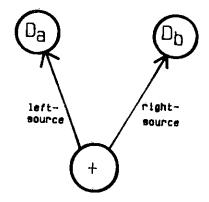

#### 2.5.3.10 Attach of a dyadic operator.

1. "(" <dyop> <argl> <arg2> ")"

<dyop> is defined in \*dyop-set\*. \*dyop-set\* contains

all dyadic operators except for the and and or

operators, treated in the next two sections. <argl>

and <arg2> must deliver a value, acceptable to the

<dyop> operator.

Makes a new node with 'type <dyop> and connects this

node to the value delivered by the <argl> with an arc

'left-source and to the value delivered by <arg2> with

an arc 'right-source and defines 'Value as the node

itself (see fig. 2.8).

#### 2.5.3.11 Attach of an and.

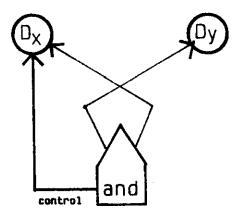

1. "(" "and" <arg1> <arg2> ")"

<argl> and <arg2> must deliver a boolean value.

2. Makes a new node with 'type 'and. This is a branch node. Connects both control and outlink-failure to the value delivered by <arg1> and the outlink-success to the value delivered by <arg2> (see fig. 2.9).

Figure 2.8. Demand graph for the dyadic expression: a+b.

Figure 2.9. Demand graph for the expression: X AND Y.

#### 2.5.3.12 Attach of an or.

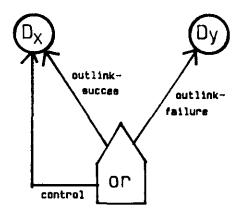

- 1. "(" "or" <arg1> <arg2> ")"

- <argl> and <arg2> must deliver a boolean value.

- 2. Makes a new node with 'type 'or. This is a branch node. Connects both control and outlink-success to the value delivered by <argl> and the outlink-failure to the value delivered by <arg2> (see fig. 2.10).

Figure 2.10. Demand graph for the expression: X OR Y.

#### 2.5.3.13 Attach of conditionals.

1. "(" "if" <test> <then-chainer> <else-chainer> ")"

<test> must deliver a boolean value.

<then-chainer> and <else-chainer> may be nil but may

never be omitted. They consist of a statement or a

multiple statement.

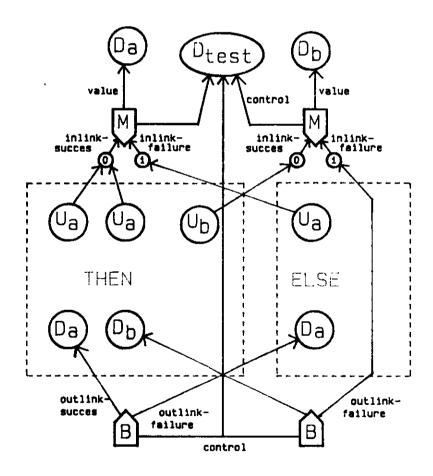

2. The <test> is attached to the demand-graph in the \*current-deflist\*. The 'Value it delivers is later connected to the control of the conditional cocoon, but first the conditional cocoon is made. This is done by creating two new deflists and two new uselists. The \*current-deflist\* and the \*current-uselist\* are pushed on their stacks. Then the <then-chainer> is attached in the branch-chainer with one deflist and one uselist and the <else-chainer> is attached in the else-branch. For all exposed-uses ( (see fig. 2.11): U-nodes) new nodes are made. Nodes with 'type 'Link-in-0 for the then branch and 'link-in-1 for the else branch.

Now we can dissolve the conditional cocoon. Branch nodes ( (see fig. 2.11): B-nodes) are created for all names that occur in some of the two deflists. These branch-nodes are connected to their definition (D-nodes) in the then-chainer with edge 'outlink-success and in the else-chainer with edge 'outlink-failure. If one of the two definitions does not exist then a new node, type 'link-in-0 (definition in then non-existent) or 'link-in-1 (definition in else non-existent), is made. The 'link-in-1 nodes are put in

the uselist of the then branch, and the 'link-in-0 nodes are put in the uselist of the else branch. All branch nodes are placed in the \*export-list-branch\* of the conditional cocoon. Now merge (M) nodes are made for all names that occur in some of the two uselists. The merge nodes are connected with 'inlink-success edges to the 'link-in-1 nodes. If one of these nodes does not exist then it is not connected. All merge nodes are put in the export-list-merge and they are connected to previous definitions (D) in the surrounding demand-graph with 'value edges after popping the deflist and uselist from their stacks. At the end the control is linked to all branch and merge nodes with 'control edges and the branch nodes are defined in the \*current-deflist\* of the surrounding demand graph.

Figure 2.11. Demand graph for if statement.

# 2.5.3.14 Attach of loops.

1. "(" "while" <test> <body> ")"

<test> has to deliver a boolean value. <body> may be

nil but may never be omitted.

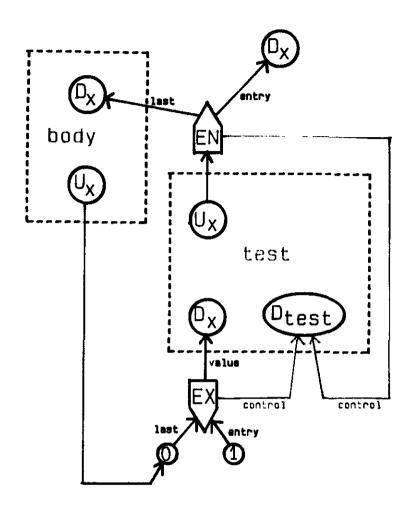

2. A loop-cocoon is created. This means that the \*current-deflist\* and the \*current-uselist\* are pushed and two new deflists and two new uselists are created. The <test> branch is attached first within its own chainer. The loop-control is set to the value that is created by attaching the <test> branch (see fig. 2.12).

When there are exposed uses in the <test>, nodes of the type 'entry (EN) are made for the concerning variables. Now the <body> branch is attached. If there are exposed uses in the <body> 'link-in-0 nodes are made. All these exposed uses appear of course in the uselist corresponding to the branch in which they are used. When dissolving the loop-cocoon for each name that occurs in some deflist or uselist of the loopcocoon an 'exit (EX) node is made. The 'exit node is linked to the definition in the <test> with edge 'value. If no definition is available then there will be no 'entry node, thus one is made and put in the All names in the uselist of the <test> branch. uselist of the <test> branch have 'entry nodes. These 'entry nodes are connected to the surrounding graph with an edge 'entry, and with an edge 'last to the definition in the <body>. If there is no definition in the body than a 'link-in-0 node is made, in the same way as if it was an exposed use in the <body>.

All names in the uselist of the <body> branch have 'link-in-0 nodes. These nodes are connected to the 'exit node with edge 'last. When the loop cocoon is dissolved all 'exit nodes are connected with an 'entry edge to 'link-in-1 nodes. These 'link-in-1 nodes are placed in the \*current-deflist\* and connections to them can be made, when used later.

Figure 2.12. Demand graph for while statement.

# 2.5.3.15 Attach of procedures.

<name> is a symbol, which identifies the procedure.

<value-params> <reference-params> <local-variables>

when omitted nil has to be given in their place.

<body> may be nil but may never be omitted. It may be

any sequence of expressions.

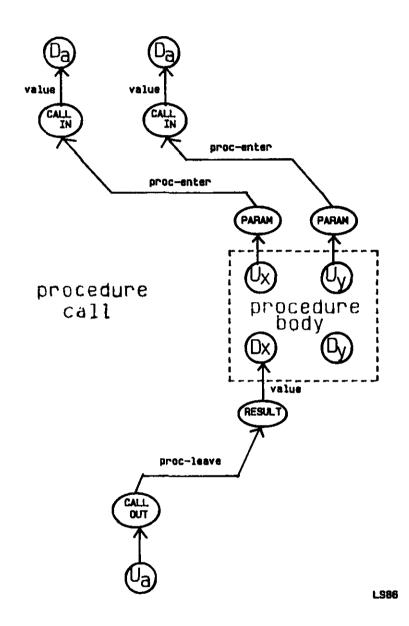

Attaching a procedure starts with checking if there is not already another procedure in the program with the same name. If not, the <name> is stored in the \*program-name\*'s list 'procedure-list. The sets of <value-params>, <reference-params> and <localvariables> are stored as property lists of the symbol <name>. A new cocoon is created with in it one new deflist and one new uselist. These become current lists when attaching the <body> of the procedure after pushing the other lists. When the body is attached the deflist contains all definitions that have to be exported to the surrounding graph. For all definitions that correspond to reference parameters and global variables 'result nodes are made (see fig. 2.13). These are connected to their definitions with edges of type 'value. Later, when calling the procedure, these nodes can be connected to 'call-in nodes. For local variables and value parameters no result nodes are made because they have no influence their on environment. All 'result nodes are stored in a property list 'outputs belonging to the symbol <name>.

The uselist contains all exposed uses. Exposed use can occur for <value-params>, <reference-params> and global variables. Exposed uses for <local-variables> are put in a \*signal-list\* and will be reported when the program finishes. For the other exposed uses, 'param nodes are made while attaching the body. Now these 'param nodes are put in the 'inputs property of the procedure <name>. Dissolving the procedure cocoon is ended with popping the deflist-stack and the uselist-stack.

# 2.5.3.16 Attach of procedure calls.

1. "(" <name> {<param>} ")"

<name> is a symbol in \*programs-name\* property list

'procedure-list.

{{{cyaram>} is a sequence with exactly the number of

symbols as in the procedure definition are in the

<value-params> and <reference-params> lists. The first

symbols in <params> are seen as the value params,

until no corresponding parameter is found in the

<value-params>. The resulting params are reference

params.

When a procedure is called it is checked if the procedure is already attached. If no error is signaled, for each node in the 'outputs property a 'call-out node is made. This 'call-out node is connected to the 'result node with an edge 'procleave. The 'call-out node is stored in the \*current-deflist\* under the name self if it is a global variable or under the corresponding name in the procedure call heading in case of a reference parameter.

For each node in the 'inputs property a 'call-in node is made. This node is connected to the corresponding 'param node. The 'call-in node is connected to the last definition of the variable in case of a global variable and to the definition of the corresponding name in the

cparams

list in case of a value param or a reference param (see fig. 2.13).

Figure 2.13. Demand graph for procedure with procedure call.

## 2.5.3.17 Attach of a function.

Functions are attached in exactly the same manner as procedures. Only the function name itself is treated as a reference-param when the function exits. Thus a 'result node is made for the variable with the name: function name.

# 2.5.3.18 Attach of a program.

1.

cprogram-name> is a symbol that identifies the current

program.

<constant-list> ,<variable-list> when omitted nil has

to be given in their place.

<body> may be nil but may never be omitted. It may be

any sequence of expressions.

## 3. Applications of the demand graph.

#### 3.1 Introduction

The demand graph can be optimised in many ways. Essential to these improvements is that the demand graph is transformed in an equivalent demand graph. Thus the demand graph represents the same algorithm but its structure is altered, resulting in a better implementation. The outcome is that you can compile the demand graph into hardware at the moment it is generated, or after some improvements. This makes it possible to add more applications on the graph structure afterwards.

### 3.2 Dead node elimination

Dead nodes are nodes with no predecessors or nodes of whose predecessors are all dead. If these nodes represent dyadic or monadic operators, no following operation requires the values they produce. It is useless to produce these values and the operators can be omitted. If a control node has no more edges that carry values connected to it, it can be removed too. After removing dead nodes it is possible that other nodes become dead and can be removed. Thus when a node is removed, it has to be checked whether any of its predecessors are dead now.

### The algorithm : Dead code elimination

- 1. All nodes without incoming edges are put in a list.

- 2. From this list one node is taken and it is removed together with its outgoing edges.

- The list is updated by removing the node processed under 2 and adding new nodes that became dead by removing edges under 2.

- As long as the list is not empty, goto step 2.

Another approach to eliminate superfluous nodes is the following: Useless nodes are all nodes that do not contribute in anyway to the output. In the demand graph the output is represented by put nodes. We check which nodes influence the data, produced by the put nodes, and mark these. All unmarked nodes can be removed afterwards.

## The algorithm: Useless node elimination

Follow the IO path and for each put node do the Markprocedure. The Mark-procedure: For each outgoing edge of a node mark the destination node of the edge and call recursively the Mark-procedure for the destination node.

#### 2. Remove all unmarked nodes.

The second algorithm covers all nodes that would be removed by the first algorithm. The reverse of this assertion is not true.

#### 3.3 Code motion.

A special kind of expressions can be removed from the inside of loops. These are called invariant-expressions. An expression is an invariant-expression in a loop if none of the variables in the expression can be modified by execution of the loop. When such an expression is evaluated outside the loop, it is only evaluated once, while inside the loop it may be evaluated many times.

## 3.4 Remove algebraic identities

Some operations on data do not influence the value of the data. For example the operations:

X := X + 0 X := X \* 1X := X / 1

can be removed without changing the value of X afterwards. This can be extended to other operators.

# 3.5 Redundant subexpression elimination.

Repeated operations are the same operations on data, that has not changed meanwhile. Unchanged data in this context means either constants that have the same value or variables that did not change their value. The unchanged variables can be detected quite easily in the demand graph. The outgoing edges of a repeated operator points to the same definition node as the outgoing edge of the first operator. The similarity between constants can be established by comparing their values. When two operators have been classified as being repeated one of them can be removed and its incoming edges can be connected to the other one.

The algorithm: Redundant subexpression elimination.

For each type of operator do:

Make a list of all nodes with operators of the same type.

For each node in the list do:

If a node is a repetition of one of the other nodes in the

list remove the repeating operator and remove the node from list.

### 3.6 Constant folding

If all inputs to an instruction are constants whose values are known, the result of the instruction can be computed when traversing the demand graph. The constants are propagated through the instruction. That is why it is sometimes called constant propagation.

Here we shortly list the meaning of the constant folding for the different statements. A full description is given in the section where the graph transformations are covered.

### • Operators

The operators and the input constants can be replaced by a new constant with the value that results when the operation is performed on the two constants.

## • If TEST then A else B

If TEST of a conditional statement delivers a constant value, one of the branches (A when test is false) is never reached. This branch can be removed from the demand graph.

There is another possibility for constant folding here. When a variable is defined as the same constant in both A and B it can be moved outside the if statement.

### • While TEST do A

There are two possibilities when the TEST of a loop appears to be a constant. First the TEST is false, then the loop is never traversed and can be removed. Second the TEST delivers the true value for ever and a warning can be reported to the designer during the constant propagation.

Furthermore, when a variable holds the same constant value, during the loop as when entering the loop, it can be defined outside the loop.

### • Procedure (a b)

When a and b get the same constant value in all procedure calls the variables can be defined in the procedure.

3.6.1 Implementation of the constant folding.

The algorithm for constant folding is described below:

The Algorithm : Constant folding

```

PILE := all constant nodes in the demand graph;

while PILE is not empty

Take a NODE1 from the pile;

Remove NODE1 from the pile;

For each input-edge of NODE1

NODE2 := start node of the input-edge;

If PROPAGATE-THROUGH(NODE2)

put NODE2 on the PILE;

REPLACE(NODE1);

```

The procedure PROPAGATE-THROUGH(node) delivers the value true if the constants can be propagated through the node. The criteria for this propagation are given in the following section. The procedure REPLACE(node) replaces the node by the above described structure and performs the actions.

The function "const-propagation" returns a list of all the nodes through which constants are propagated. As a side effect it alters the demand-graph by removing these nodes and replacing them by equivalent structures.

There is another algorithm for finding the nodes through which constants can be propagated. The only entrance for variables in the graph are the get nodes. Thus, when we start a mark procedure, similar to the mark procedure of the dead code elimination, from the get nodes we can find all nodes that can be reached from the get nodes. The remaining nodes cannot be reached from the get nodes and cannot be supplied with variables. Through these nodes constants can be propagated.

#### The algorithm: Find foldable nodes

1. Follow the IO path and for each get node do the Mark-procedure.

The Mark-procedure: For each incoming edge of a node mark the departure node of the edge and call recursively the Mark-procedure for the departure node.

Through all unmarked nodes constants can be propagated.

## 3.6.2 Graph transformations during constant folding.

Constant propagation asks for special actions for each node type. A special description has been developed to describe these actions. First this description will be introduced.

- Node names are surrounded by \*'s, for example \*dyop\* means a node which represents a dyadic operator.

- In front of the node name its output edges are given in a list surrounded by "(" and ")".

- Behind the node name the input edges are given in a list similar to the output edges.

- Edges inside "[" and "]" mean that the node to which this edge leads has to be a constant node.

- L --> R means: L is transformed to R

- The actions which have to be done during the transition

--> are described in between "{" and "}".

We will describe the transformation of a DYOP node as an illustration to the transformations given below.

When a DYOP its outputs, left-source and right-source, both lead to a constant node (indicated by the brackets "[" and "]") then this node can be replaced by a constant node C. The inputs of the DYOP node (V1..Vn) are connected to the constant node C. The calculation of the constant C is done by applying the function of DYOP to both constants, as indicated by the action inside the brackets "{" and "}".

Here follows the table with the descriptions for each node type.

```

DYOP:

([left-source] [right-source]) *dyop* (V1 .. Vn)

--> *C* (V1 .. Vn)

( *C* = function of *dyop* (left-source, right-source) )

MONOP:

([source]) *monop* (V1 .. Vn) -->

*C* (V1 .. Vn)

{*C* = function of *monop* (source) }

AND, OR:

(outlink-success, outlink-failure, [control]) *and/or* (V1 .. Vn)

--> *N*

(V1 .. Vn)

{ if control=1 then *N* = ('to-node of outlink-success)

else *N* = ('to-node of outlink-failure) }

BRANCH(1):

(outlink-success, outlink-failure, [control]) *branch* (V1 .. Vn)

--> *N*

(V1 .. Vn)

{ if control=1 then *N* = ('to-node of outlink-success)

else *N* = ('to-node of outlink-failure) )

BRANCH(2):

([outlink-success], [outlink-failure], control) *branch* (V1 .. Vn)

--> *C* (V1 .. Vn) | \epsilon

VAL ('to-node outlink-success) -

(if

VAL ( 'to-node outlink-failure)

then *C* | 'to-node of outlink-success

else nothing happens )

MERGE(1):

(value, [control]) *merge* (inlink-success, inlink-failure)

--> *C* (inlink-success) | *C* (inlink-failure)

{ *C* = 'to-node of value;

Ιf

control-1

```

```

then *C* (inlink-success)

else *C* (inlink-failure);

delete (other-link) }

Remark:

Delete means removing all nodes, starting with 'from-node

of delete-link until a branch node with the same control as

the merge-node is reached.

MERGE(2):

([value], control) *merge* (inlink-success, inlink-failure)

--> *C* (inlink-success, inlink-failure)

{ *C* = 'to-node value }

LINK-IN-O or LINK-IN-1 or CALL-IN or CALL-OUT:

([value-in]) *node* (value-out) --> value-out = value-in

{ remove link-in-node }

Remark:

*node* = link-in-0 or link-in-1 or call-in or call-out

ENTRY(1):

(entry, last, [control]) *entry* (value)

--> (error | entry-exit - entry)

(if control=1 then error: endless loop

else (entry-edge of exit)=entry, delete-loop)

ENTRY(2):

([entry], last, control) *entry* (value) --> *C* (value) | \epsilon

(if type('to-node last)= type('to-node entry) or

- link-in-0

then *C* = 'to-node entry

else nothing happens)

Remark:

Delete-loop deletes all nodes in between an entry and an exit loop.

EXIT:

(value, [control]) *exit* (last, entry)

--> (value, [control]) *exit* (last, entry)

```

## 4. The dynamic programming approach

### 4.1 Introduction