## **Purdue University**

# Purdue e-Pubs

Department of Computer Science Technical Reports

Department of Computer Science

1982

# Highly Parallel Processing of Relational Databases (Thesis)

Ching-Chih Hsiao

Report Number: 83-460

Hsiao, Ching-Chih, "Highly Parallel Processing of Relational Databases (Thesis)" (1982). *Department of Computer Science Technical Reports*. Paper 379. https://docs.lib.purdue.edu/cstech/379

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

ч.

----

ここと

# HIGHLY PARALLEL PROCESSING OF RELATIONAL DATABASES

2

÷

¢

ï

A Thesis

by

Ching-Chih Hsiao

Dedicated to my parents, my wife, and my family

This work is part of the Blue CHiP Project. It is supported in part by the Office of Naval Research Contracts N00014-80-K-0816 and N00014-81-K-0360. The latter is Task SR0-100.

## ACKNOWLEDGEMENTS

1.7

Deepest appreciation is expressed to my major professor, Lawrence Snyder. His encourgement and guidance in my research and writing has been invaluable. I am very grateful to Professors Janice Cuny, Dennis Gannon, and Vincent Shen for serving on my graduate committee and their help throughout this research work. I am also indebted to Jeremy Epstein for some early, stimulating discussions.

Thanks are also extended to Professor S. Bing Yao who was my advisor before he left Purdue and Tom Putnan who was my supervisor when I worked at CINDAS.

Many thanks go to all the friends that have made my stay in West Lafayette so enjoyable, especially Kye Hedlund, Tom Rafetto, Steve Thebaut, Andrew Wang, and all the Blue CHiPpers. I would also like to thank Julie K. Hanover, the secretary of the Blue CHiP project.

Last but not least, I want to thank my parents, my brothers, and my sister for their support. My wife Nien-Tsu also deserves special thanks for her love and understanding.

This research is partially supported by the Office of Naval Research under Contract N00014-80-K-0816 and Contract N00014-81-K-0360, Special Research Opportunities Program Task SRO-100.

ii

Ci

## TABLE OF CONTENTS

\$

ı,

f

à

| Page                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------|

| LIST OF TABLES                                                                                                                       |

| LIST OF FIGURES                                                                                                                      |

| ABSTRACT                                                                                                                             |

| CHAPTER 1 - INTRODUCTION                                                                                                             |

| <ul> <li>1.1 Goal and Methodology.</li> <li>1.2 Definitions and Notation</li> <li>1.3 Organization of the Thesis</li> </ul>          |

| CHAPTER 2 - HIGHLY PARALLEL DATABASE MACHINES                                                                                        |

| 2.1 Background                                                                                                                       |

| CHAPTER 3 - AN EFFICIENT PRIMITIVE OPERATION                                                                                         |

| 3.1 POP-SORT, a Special Example213.2 Implementation and Performance223.3 POP-SORT, in General313.4 Application to Join Operations31  |

| CHAPTER 4 - OPTIMALITY OF THE PRIMITIVE OPERATION40                                                                                  |

| 4.1 Collapsing the Complexity Hierarchy424.2 Comparison Functions and Computation Models                                             |

| CHAPTER 5 - BITONIC SORT ON THE CHIP COMPUTERS                                                                                       |

| 5.1 Reordering Between Indexing Schemes625.2 Sorting with Shadow Regions665.3 Improvements on the Data Routing695.4 K-fold Sorting72 |

üi

i

ł

.

## Page

| CHAPTER 6 - QUERY EMBEDDING            |

|----------------------------------------|

| 6.1 Embedding of Operation Trees80     |

| 6.2 Buddy System Allocation            |

| 6.3 Query Amelioration                 |

| 6.4 Extensions                         |

| CHAPTER 7 - SUMMARY AND CONCLUSIONS    |

|                                        |

| 7.1 Main Contributions100              |

| 7.2 Future Research101                 |

|                                        |

| LIST OF REFERENCES103                  |

|                                        |

| APPENDIX A - Batcher's Bitonic Sort109 |

| A 4 mb - Diteria Manage 100            |

| A.1 The Bitonic Merge                  |

| A.2 Effects of Propagation Delay111    |

| APPENDIX B - Sprinkle Algorithm        |

| APPENDIX C - The Lacing Technique117   |

| VITA                                   |

ĉ,

¢

7

í

ί

# LIST OF TABLES

;

7

ι

| Table          | , Pi                                                                             | age |

|----------------|----------------------------------------------------------------------------------|-----|

| 2-1            | Algorithms of database operations on<br>highly parallel machines                 | 14  |

| Appe:<br>Table |                                                                                  |     |

| A-1            | Effects of propagation delay on the bitonic sort with different interconnections | 112 |

e C

## LIST OF FIGURES

| Figur | e Page                                                                                 |          |

|-------|----------------------------------------------------------------------------------------|----------|

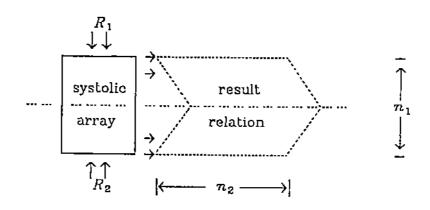

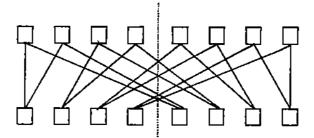

| 2-1   | The system configuration of highly<br>parallel database machines9                      |          |

| 2-2   | The systolic array system for performing database operations15                         |          |

| 2-3   | The BK-tree machine16                                                                  |          |

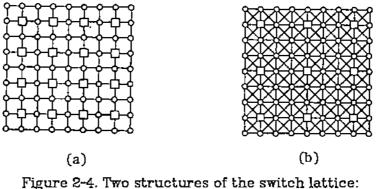

| 2-4   | Two structures of the switch lattice:<br>(a) $w = 1$ , $d = 4$ ; (b) $w = 2$ , $d = 8$ |          |

| 3-1   | State diagram for two idempotent<br>marking functions31                                |          |

| 3-2   | A "shift-copy and compare" scheme for<br>detecting duplicates in a sorted sequence33   | I        |

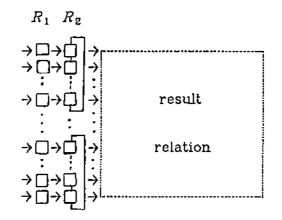

| 3-3   | Logical structure of the easy-catch system<br>for performing join operations           | I        |

| 3-4   | Two configurations on a CHiP computer for implementing the easy-catch system           | 1        |

| 4-1   | Collapsing the time-complexity hierarchy<br>implying the optimality of POP-SORT43      | <b>i</b> |

| 4-2   | PIM machine as a model of<br>parallel computation46                                    | ŝ        |

| 4-3   | The function of enumeration comaprison methods:<br>table filling and row computation49 | )        |

| 4-4   | The total ordering contained in<br>the semi-digraph53                                  | 3        |

| 4-5   | A general comparison network55                                                         | >        |

\$

÷

١

I

: •••

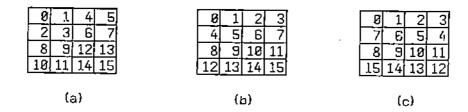

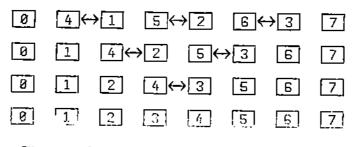

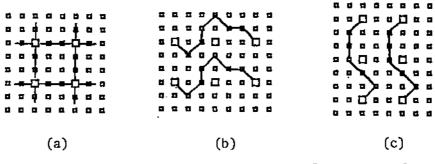

| 5-1          | (a) Shuffled row-major indexing. (b) Row-major<br>indexing. (c) Snake-like row-major indexing62                             |

|--------------|-----------------------------------------------------------------------------------------------------------------------------|

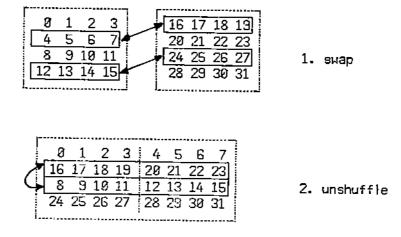

| 5-2          | Rearrangement merge of two 4×4 regions                                                                                      |

| 5-3          | A triangular interchange scheme<br>to perform unshuffle                                                                     |

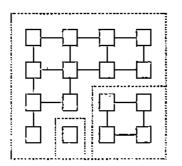

| 5-4          | Sorting 176 data items with 4×4<br>and 8×8 shadow regions67                                                                 |

| 5-5          | The interconnection patterns $I_{1,2}$<br>composed of three sub-patterns:<br>(a) $I_1$ , (b) $I_{2h}$ , and (c) $I_{2v}$ 71 |

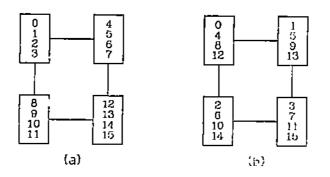

| 5-6          | Indexing 16 data items on 4 processing<br>elements: (a) Aggregation scheme,<br>and (b) Projection scheme                    |

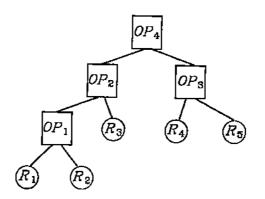

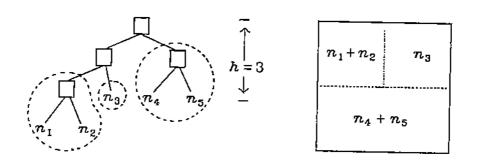

| 6-1          | An operation tree from parsing a query81                                                                                    |

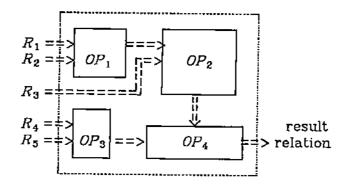

| 6-2          | A general scheme of composing algorithms<br>(operations) for query embedding82                                              |

| 6-3          | An example of buddy system allocation                                                                                       |

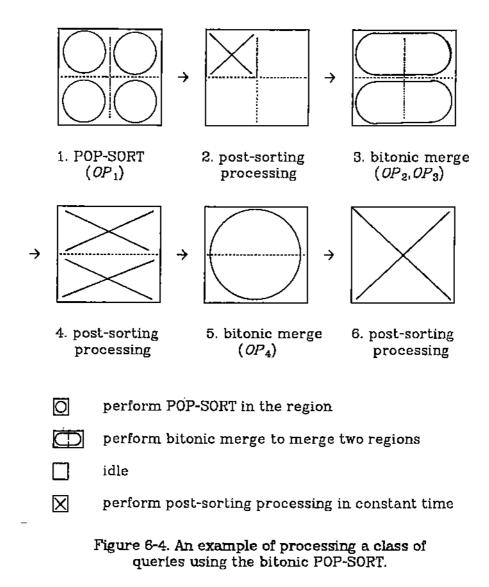

| 6-4          | An example of processing a class of<br>queries using the bitonic POP-SORT                                                   |

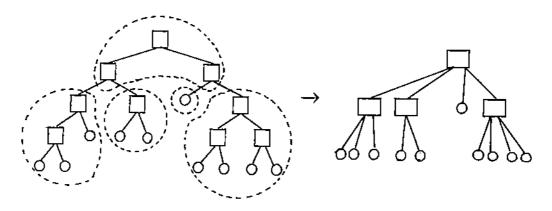

| 6-5          | Transfroming an operation tree into a quaternary<br>tree for more compact allocation91                                      |

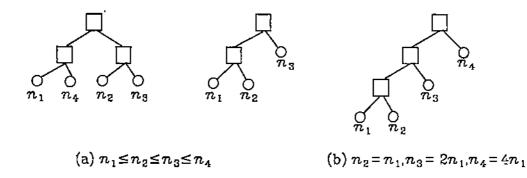

| 6-6          | Weight-balanced trees94                                                                                                     |

| 6-7          | Systolic method of Cartesian product96                                                                                      |

| 6-8          | Cartesian product in a square region97                                                                                      |

| Appe<br>Figu | endix<br>re                                                                                                                 |

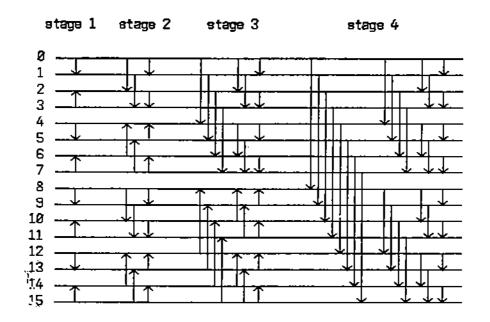

| A-1          | Sorting network for Batcher's bitonic sort                                                                                  |

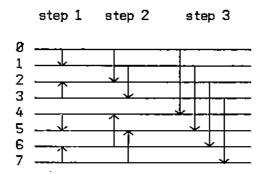

| B-1          | The communication scheme of $\log n$ steps applied<br>in the Sprinkle Algorithm for $n = 8$ 114                             |

| C-1          | The schematic perfect shuffle of $n$ data<br>items between two rows of $n/2$ processors<br>for $n = 16$                     |

|              |                                                                                                                             |

2

•

J

٩,

ł

ł

Y)

|     | An embedding of the perfect shuffle for $n = 32$ on a CHiP switch lattice |

|-----|---------------------------------------------------------------------------|

| C-3 | Some basic components constructing the<br>embedding in Figure C-2         |

.

:

5

ι

7

:

## ABSTRACT

Ching-Chih Hsiao, Ph.D., Purdue University, December 1982. Highly Parallel Processing of Relational Databases. Major Professor: Lawrence Snyder.

New computer architectures are feasible because of the advances in VLSI design and fabrication technologies. Among them, highly parallel structures coordinate hundreds of thousands of processing elements that function cooperatively. These structures are especially useful in solving computationally intensive problems. This thesis applies the highly parallel approach to improve the efficiency in processing relational database queries. High-performance algorithms for basic relational operations are explored. Efficient composition of these algorithms to process whole queries is also investigated.

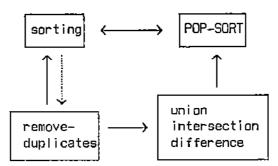

Regularity and uniformity are necessary in order to make the highly parallel computing cost-effective. An efficient primitive, called POP-SORT, is proposed to unify the relational operations such as sorting, duplicateremoval, union, intersection, and difference. The three latter operations are even allowed to have multisets as operands. POP-SORT is based on an easy scheme which adapts any highly parallel and regular sorting algorithm to perform all these database operations. The primitive is compared favorably,

This work is part of the Blue CHiP Project. It is supported in part by the Office of Naval Research Contracts N00014-80-K-0816 and N00014-81-K-0360. The latter is Task SRO-100.

in terms of time complexity, with existing algorithms for the five operations. The optimality of POP-SORT is also proved for a restricted but reasonable type of parallel computation. Furthermore, sublinear time performance is possible for join operations if argument relations are preconditioned by POP-SORT.

For processing a whole query, the operation tree parsed from the query can be executed by composing individual algorithms for the operations. The Configurable, Highly Parallel (CHiP) computers have the flexibility to provide programmable processor interconnections for composing algorithms. Query embedding is a method of executing whole operation trees to explore maximum parallelism on the CHiP computers. It involves the processor allocation and the embedding of appropriate interconnections. With the bitonic POP-SORT, which is a generalization of Batcher's bitonic merge sort, the query embedding can be simplified significantly.

х

5

÷.

c C

## CHAPTER 1

## INTRODUCTION

Computer architects have been attempting to avoid the von Neumann structure that a single CPU serially fetches, processes, and restores data items. Due to the advances of VLSI fabrication and design technologies, computer architectures are no longer strictly confined by the cost of computing hardware. In the near future it will be feasible to implement highly parallel computers consisting of hundreds of thousands of processing elements [Hayn82]. With the use of so many processing elements operating cooperatively, a speed-up ratio as substantial as many orders of magnitude is possible.

The highly parallel structures are known to be useful for solving some computationally intensive problems in the areas like meteorology, cryptography, image processing, ...etc. However, integrating many processing elements to implement a reliable and cost-effective system is extremely difficult. Problems suitable for highly parallel computing must show a high degree of regularity and uniformity.

Relational data model [Codd70] not only provides a simple view of databases but also calls for a particular feature named relational processing capability [Codd82]. This feature entails the definition of relational

1

Q

operations which treat whole relations as operands. It is of interest to study the application of highly parallel architectures and algorithms to the implementation of relational operations.

Historically, efficiency of database processing has been stressed, but convenience and expressiveness have been of less concern. Application programmers' productivity is thus far behind the demands from end users of database systems. A relational data model, by raising the user interface from physical details to a higher logical level, provides improved convenience and expressiveness. E. F. Codd [Codd82] also remarked that the relational processing capability is a key factor leading the relational model toward a practical foundation for improved productivity. It is therefore very important to implement a relational processing capability that achieves high performance.

#### 1.1 Goal and Methodology

The goal of this work is to take advantage of the VLSI computation power and the highly parallel architectures to improve relational database processing. We are concerned both with high-performance implementations of individual relational operations and efficient processing of whole queries.

Highly parallel computing relies crucially on efficient communication to achieve a successful exploitation of parallelism. For solving problems with parallel computation, more communication time is often required than the actual computation time [Lint81]. Processor interconnections, hardwired or software-controlled, on highly parallel computers are usually selected to support efficient communication. Therefore, it is important to identify

2

r

٦.

communication schemes which are efficient for solving many problems.

Sorting is a necessary operation in many applications. Highly parallel sorting has been vigorously studied and several efficient algorithms exist [Batc68, Ston71, Thom77, Nass79; Mull75, Hirs78, Prep78]. For highly parallel processing of relational databases, we unify several operations on a single communication scheme by reducing those operations to sorting. The primitive operation POP-SORT (Primitive OPeration SORT) is thus proposed for the database operations such as sorting, union, intersection, difference, and duplicate-removal. We also apply POP-SORT to solve join operations in sublinear time.

POP-SORT presents the possibility of adapting any sorting algorithm to become a primitive for the five database operations. For merge-oriented sorting methods, the adaptation can be easily done by replacing the simple comparison function with a slightly modified one. The simple comparison function is extended to have marking capability that marks one of the two argument items when they are found to be equal. Comparison functions acting only in the local computation at processing elements do not effect the communication among the processing elements at all. For sorting methods in general, the adaptation can be done by two marking processes that both take constant time. The marking processes require communication only as simple as a linear array.

The efficiency of POP-SORT in performing the five database operations is demonstrated by an instance called the bitonic POP-SORT. It is a generalization of Batcher's bitonic merge sort [Batc68]. The performance of the bitonic POP-SORT compares favorably with existing algorithms (upper bounds) for the five database operations. To further evaluate the optimality of POP-SORT, we look into the reducibility relationships between it and the database operations.

The CHiP (Configurable Highly Parallel) computers are capable of providing dynamic and programmable interconnections [Snyd82]. It is thus possible to embed required connections for processing whole queries. To expand the spectrum of parallelism to process whole queries, we explore the feasibility of the query embedding on the CHiP computers. In [Snyd82] Snyder showed that the CHiP computers have the flexibility to compose algorithms to solve large and computationally intensive problems. Employing the bitonic POP-SORT as a primitive for several database operations, the composition of algorithms to process whole queries can be simplified significantly.

#### 1.2 Definitions and Notation

1 .....

$\mathbb{P}_{L^{*}}$

A relation is normally a set of unique tuples and each tuple consists of an ordered sequence of components. As duplicates are artifacts of certain relational operations, we allow relations to be multisets consisting of duplicate tuples. Basic relational operations like sorting, restriction (selection), join, Cartesian product, and quotient are defined as those in text books (see, for example, [Ullm80]). Projection, duplicate-removal, union, intersection, and difference are defined slightly differently in this work.

For remove-duplicates we do not insist on discarding the duplicate items. Given n data items  $x_0, x_1, \ldots, x_{n-1}$ , the goal of duplicate-removal is to compute the mark bits  $\mu(0), \mu(1), \ldots, \mu(n-1)$  for these items. In the

sequence  $x_0^{\mu(0)}, x_1^{\mu(1)}, \dots, x_{n-1}^{\mu(n-1)}$ , we distinguish  $x_i^{\mu(i)}$  as a duplicate item if  $\mu(i) = 1$ . An additional operation segregation can be used to pack and separate marked and unmarked data items in the sequence [Schw80]. To perform projection on a relation, we assume that duplicate-removal is not automatically invoked. The operations union, intersection, and difference may be relaxed to allow multisets as operands. Without further notice, they are just set operations as usual.

A highly parallel processor is a processing device which integrates many processing elements. By "processor" we may refer to a single processing element or a system of coordinated processing elements. Usually it means a processing element unless further indicated by the context. For example, the CHiP "processor" is a "highly parallel processor" in the collective sense.

The following notation is used throughout this thesis.

| $\log^x y$   | the base two logarithm $(\log_2 y)^z$ .                     |

|--------------|-------------------------------------------------------------|

| [x ]         | the least integer greater than or equal to $m{x}$ .         |

| [ <i>x</i> ] | the greatest integer less than or equal to $oldsymbol{x}$ . |

| $t_R$        | time required for one data routing step.                    |

| tc           | time required for one comparison step.                      |

| PE           | processing element which may have some local memory.        |

| $A \cup B$   | the union of two sets $A$ and $B$ .                         |

| $A \cap B$  | the intersection of two sets $A$ and $B$ .      |  |  |  |  |

|-------------|-------------------------------------------------|--|--|--|--|

| A-B         | the difference of two sets $A$ and $B$ .        |  |  |  |  |

| union(A,B)  | the union of two multisets $A$ and $B$ .        |  |  |  |  |

| inter(A,B)  | the intersection of two multisets $A$ and $B$ . |  |  |  |  |

| differ(A,B) | the difference of two multisets $A$ and $B$ .   |  |  |  |  |

| rmdup(A)    | the duplicate-removal on multiset A.            |  |  |  |  |

#### 1.3 Organization of the Thesis

In Chapter 2, we look at the conventional approaches of database machine designs. The conventional approaches do not solve the computebound operations satisfactorily. Several highly parallel structures for solving the compute-bound operations are thus proposed by researchers. We also discuss those structures and the algorithms proposed to be executed on them.

Chapter 3 presents a methodology to apply parallel sorting to solve other problems. By reducing union, intersection, difference, and duplicateremoval to sorting, these operations are unified by the primitive operation POP-SORT. Two adaptations are shown to extend merge-oriented and other sorting methods to become POP-SORT. The adaptation overhead is shown to be negligible. We also show that POP-SORT can be used to perform join operations in sub-linear time. This application of POP-SORT is especially

٦.

suitable for easy join operations that produce only small result relations.

The efficiency of POP-SORT is investigated in Chapter 4. A complexity hierarchy showing the reducibility relationships among POP-SORT and the five database operations is first established. The complexity hierarchy indicates that the optimality of POP-SORT relies on the reducibility of sorting to duplicate-removal. We therefore look into the reducibility of sorting to duplicate-removal by considering two types of comparison functions, the weak comparison  $(=, \neq)$  and the strong comparison (<, =, >).

Chapter 5 deals with some interesting aspects of performing the bitonic sort with the mesh interconnection on the CHiP computers. We design an efficient algorithm that rearranges n sorted data items among three major indexing schemes in less than  $(3\sqrt{n})t_R$  time. Sorting with shadow regions is a technique that allows the allocation of exactly n processing elements for sorting n data items (n is an arbitrary integer). We also demonstrate how data communication can be improved by properly programming the switching elements on the CHiP computers. Two different methods of sorting  $k \cdot n$ data items on a CHiP region of n processing elements are also analyzed.

Processing whole queries on the CHiP computers is the subject of Chapter 6. Relational algebraic queries are considered. The idea of embedding whole operation trees parsed from database queries is explored. With the bitonic POP-SORT, we demonstrate that query embedding is simplified significantly. We also discuss several optimization strategies to improve query embedding on the CHiP computers.

## CHAPTER 2

## HIGHLY PARALLEL DATABASE MACHINES

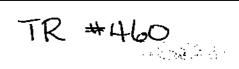

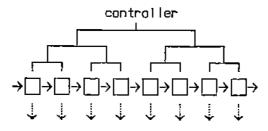

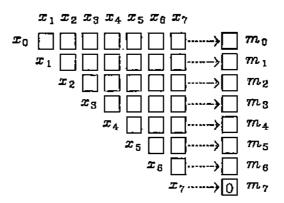

Database machines are specialized computers dedicated to executing database management functions. They are usually connected to generalpurpose computers as back-end machines. If a database machine is enhanced with a highly parallel processor to solve compute-bound database operations, we call it a highly parallel database machine. In Figure 2-1 we show the configuration of a back-end system consisting of a highly parallel database machine.

In the back-end system, the host computer acts as the interface between users and the database machine. It is responsible for taking users' requests, translating the high-level data manipulation programs into database machine commands, instructing the database machine to perform the commands, and returning the response to the users. Besides the highly parallel processor, there are two major components in the database machine: the back-end controller and the mass storage. The back-end controller serves as the interface to the host computer. The mass storage is content addressable in order to perform searching and update operations as well as other 1/O-bound database operations efficiently. Between the mass storage and the highly parallel processor there is a wide data channel to

В

support rapid data loading and unloading. This bandwidth is also needed in associative processor systems [Berr79] and array processor systems [Batc80].

Figure 2-1. The system configuration of highly parallel database machines.

This chapter presents a brief overview of the principal approaches in conventional database machine designs. The inability of conventional approaches to solve compute-bound database operations is discussed. Highly parallel processors are then proposed as a means of extending the computation power of database machines. Next, we review some highly parallel structures and their algorithms that have been reported to be useful for database applications. All this serves as a benchmark for evaluating our research work.

### 2.1 Background

ķ

As database management techniques are shown to be helpful, users want them to be larger and more inclusive. But as databases become progressively larger, conventional general-purpose computers fail to meet the response time requirements of many applications. With the adoption of high-level data models and data manipulation languages, high-performance implementation of database management systems becomes even more crucial. Two well-known implementations of relational database management systems. System R [Astr76] and INGRES [StoB76], amply demonstrate the complexity and difficulty of query processing under these circumstances.

Since software techniques on conventional, general-purpose computers cannot implement database management systems efficiently enough, researchers have turned to alternative computer architectures and specialpurpose hardware. Canaday [Cana74] proposed that database management functions be placed on a dedicated back-end processor which has exclusive access to the database. By limiting the back-end processor to the performance of only database management functions, it can have the advantage of efficiency through specialization. But the implementation of the eXperimental Database Management System (XDMS) [Cana74] failed to show that the use of a general-purpose computer as back-end is a good approach. Specialized database machines are, therefore, designed to serve as the back-end computers [Bane79, DeWi79, Schu79].

Many hardware organizations have been proposed to facilitate database processing although they are not all complete designs of database machines. Two objectives are involved. One is to improve the non-query aspects of

10

processing such as searching, retrieval, insertion, deletion, and modification. The other is to speed up the query aspects of processing which may involve some compute-bound operations.

There is a consensus that content addressable memory is desirable for efficient searching and updating. But storing databases entirely in associative memory is infeasibly expensive. Fortunately, the "logic-per-track" approach proposed by Slotnick [Slot70] provides a practical solution for implementing a large-volume memory with content addressability. Many designs have applied some type of the logic-per-track approach to achieve the associativity and parallelism for fast searching and updating [Lang78]. Among them are the Content-Address Segment Sequential Memory (CASSM) [Su75, Su79], the Content Addressed File Store (CAFS) [Babb79], the Data Base Computer (DBC) [Bane78, Bane79], the Relational Associative Processor (RAP) [Ozka75, Schu79], and the Rotating Associative Relational Store (RARES) [Lin76].

One useful strategy to reduce the overhead of data movement is to process data in place if it is possible. By placing some processing capability at the mass storage level, the logic-per-track approach performs not only searching and updating effectively but other operations as well. I/O-bound relational operations like restriction and projection (without removing duplicates) can be performed at the memory level. Other operations, however, are not easily supported [Song81, DeWi82]. Sorting, duplicate-removal, union, intersection, difference, join, and Cartesian product all require that one data item interact with many others. These operations require complex processor interconnections that cannot be easily implemented using the

J

logic-per-track approach. This is because of the physically dispersed character of the read/write heads. Implementing these operations on the secondary storage level, it seems to require some kind of looping or iteration.

Several techniques help to improve query processing on compute-bound operations. The overhead incurred by the time-consuming secondary memory accesses can be reduced by using intelligent file systems and memory management. Unnecessary database information can be filtered out before it is submitted to the processor. The use of special processing devices is yet another weapon with which researchers attack the computebound problems. Much special-purpose hardware has been proposed for performing the operations join and sorting. In addition, in the DBC design several compute-bound functions or "post-processing functions" [HsiD79] are performed by a multiprocessor system. These post-processors are linearly connected, and each has its own local memory. Also in [DeWi79] a multiprocessor architecture called DIRECT was designed to support relational query processing.

Special hardware for a few operations respectively do not solve the problem completely or uniformly. The multiprocessor systems proposed demonstrate reasonably good, but restricted, performance improvement. Application of highly parallel processors has thus been proposed for database processing [Kung80, Song80, HsiC81, Lehm81].

#### 2.2 Highly Parallel Processors

A highly parallel processor may consist of hundreds of thousands of processing elements which function cooperatively to solve compute-bound

12

.

problems. The computation power of the processing elements is limited to that required by database management queries. The instruction set is thus small and can be tuned to perform query processing more efficiently. When the highly parallel processor is implemented by VLSI chips, less area for computing logic implies that more area can be dedicated to the local memory logic or the processor interconnection circuitry. Being more important, a larger scale integration of processing elements is possible if more chip area is available for processor interconnections.

In highly parallel structures, inter-processor communication is the key to successful exploitation of the available computing power. The processor interconnection problem has motivated much research recently. An important question that needs to be addressed for general computation and data processing alike is:

## What are the most effective interconnection paths for communicating PEs to process database queries?

This section discusses several structures of highly parallel processors and their algorithms. The highly parallel processors addressed here are: the systolic array system, the double tree machine, the Ultracomputer, and the CHiP computer. The first three represent different processor interconnections, and the last one has the flexibility to provide them (as well as the mesh interconnection).

5

In Table 2-1 we first summarize the time complexities of certain database operations on these machines. POP-SORT is the primitive operation proposed in this thesis which can perform the other five operations (Chapter 3). The complexity is measured by assuming that the argument relations

$\alpha$

have n tuples. Except for the systolic arrays and the tree machine, we assume that the data is already in the processing device. The effect of propagation delay is ignored here for the tree machine and the Ultracomputer.

| operations           | U             | $\cap$                | _             | rmdup       | sort               | POP-SORT                     |

|----------------------|---------------|-----------------------|---------------|-------------|--------------------|------------------------------|

| -<br>Systolic arrays | 0(n)          | 0(n)                  | O(n)          | 0(n)        | -                  | -                            |

| Tree machine         | <b>0</b> (n)  | 0(n)                  | $\Theta(n)$   | $\Theta(n)$ | $\Theta(n)$        | 0(n)                         |

| Mesh computer        | -             | -                     | -             | -           | $\Theta(\sqrt{n})$ | $\Theta(\sqrt{\pi})$         |

| Ultracomputer        | $O(\log^2 n)$ | 0(log <sup>2</sup> n) | $O(\log^2 n)$ | -           | $O(\log^2 n)$      | $O(\log^2 n)$                |

| CHiP                 |               |                       |               |             | -                  | $O(\frac{\sqrt{n}}{s})^{**}$ |

Table 2-1. Algorithms of database operations on highly parallel machines.

- An instance of POP-SORT, the bitonic POP-SORT, is used to calculate the time complexities (Chapter 3.1).

- \*\* A technique is applied on the CHiP computers to achieve the speed-up factor s over the mesh-connected computers (Section 5.3), where  $s \leq w * c$ .

#### Systolic Arrays

Systolic arrays have been proposed for many applications [Kung79, Fost80, Kung82]. Kung and Lehman [Kung80] used systolic arrays to implement relational database operations. Lehman [Lehm81] also applied systolic arrays to processing simple queries.

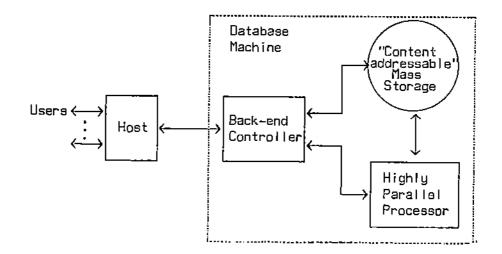

They presented two types of systolic arrays to implement database operations (Figure 2-2). A two-dimensional comparison array and a onedimensional accumulation array were used for union, intersection, difference, and duplicate-removal. The comparison array alone is used for join operations. Argument relations are "staged" into the comparison array ì.

in a component-parallel and tuple-serial fashion. Tuples from different relations flow in the opposite directions in the comparison array so that they will always pass by each other. The comparison results move from left to right. They are recorded as a bit matrix for join or shifted to the accumulation array to generate a bit string for the other operations.

Figure 2-2. The systolic array system for performing database operations.

In the systolic arrays, the processing elements perform only simple functions and the interconnections are very regular. Both of the arrays can be implemented with only a few types of simple cells. Another advantage is that computations are pipelined elegantly so that the processing time is completely overlapped with the I/O time. However, from an algorithmic point of view, the benefit of data ordering is totally ignored in [Kung80]. The systolic arrays are fundamentally structures of linear time performance.

Systolic arrays are algorithmically specialized processors [Snyd82]. The functions performed by systolic arrays are predetermined and rigidly manufactured into VLSI products. Programmability is minimal. To implement all the operations required by query processing, an integrated system

iΩ

containing several systolic arrays is needed [Song81].

## The BK-tree Machine

والمحقو فكرفان

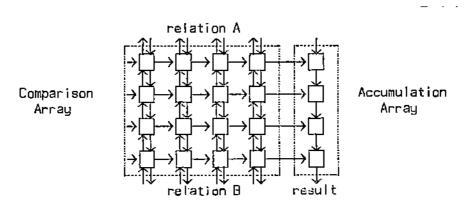

The BK-tree, or double tree, was proposed by Bentley and Kung [Bent79] for pipelining searching operations such as retrieval, insertion, deletion, and modification. On an n-processor version of this machine, a set of n data items can be maintained such that all the searching problems are processed in  $2\log n$  steps. Tree-structured machines have also been proposed as general-purpose processing devices by Browning [Brow80] and many other researchers. In [Song80, Song81] this architecture was applied to implement additional basic database functions.

Figure 2-3. The BK-tree machine.

A BK-tree<sup>†</sup> machine is composed of three kinds of processing elements: O-nodes, [l-nodes, and  $\nabla$ -nodes (see Figure 2-3). The [l-nodes contain the data items to be processed. The O-nodes are responsible for broadcasting sequences of instructions and data to the [l-nodes. Parallel computation is carried out by the [l-nodes. Partial results produced are then collected by t An interesting interpretation of "BK" is that "B" is mnemonic for broadcasting information

16

У

T An interesting interpretation of "BK" is that "B" is mnemonic for broadcasting information and "K" for collecting information.

the  $\nabla$ -nodes. At last the final result emerges from the output root node.

Sorting can be easily implemented on a tree machine using the heap sort algorithm [Mead80]. To perform union, intersection, and join on relations A and B, Song employed two solutions [Song80]. One is to sort the two argument relations using the tree machine and to perform further processing elsewhere. The other is to load one relation in []-nodes and then broadcast the other relation onto the I]-nodes to perform the required operation. Partial results produced in the []-nodes may have to be saved before they can be accepted by the  $\nabla$ -nodes (e.g. in performing join). The potential bottlenecks were resolved by a request/acknowledge communication convention [Song80].

The BK-tree machine is very efficient in pipelining successive searching operations which take a single data item as the operand. However it does not perform as well on database operations which take whole relations as operands. Again, the BK-tree machine is fundamentally a linear time bounded structure. The performance barrier is inherited from the general restriction of tree structures that only one data value at a time can flow into and out of the tree through the root node. Furthermore, the VLSI layouts of large trees are susceptible to the propagation delay problem [Pate81].

#### The Ultracomputer

Ultracomputers [Schw80] are those with powerful and physically realized interconnection patterns. They are composed of a large number of processing elements each connected with a fixed number of others. The Ultracomputer in [Schw80] is based on the perfect shuffle interconnection

Г. Г. [Ston71]. Other powerful interconnections like the Cube-Connected-Cycles (CCC) [Prep81] are also in this category which we refer to as ultracomputers.

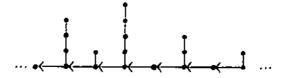

On the Ultracomputer with the perfect shuffle interconnection, all the permutations of data among processing elements can be realized in  $\log n$  routing steps. Sorting, union, intersection, and difference can thus be solved in logarithmic time. No results about duplicate-removal and join are reported in [Schw80]. While the ultracomputer is efficient in solving certain compute-bound operations, it is expensive to implement. Expandability is poor because the interconnection complexity grows at least as a function  $n^2/\log^2 n$  of the number of processing elements n [Thom80]. Moreover propagation delay problems and synchronization difficulties can become more severe when n is large.

### The CHiP Computer

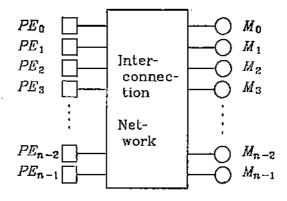

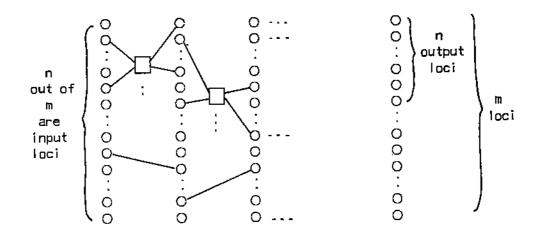

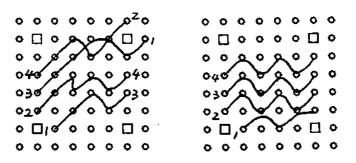

A Configurable, Highly Parallel (CHiP) [Snyd82] processor permits the processor interconnections to be dynamically programmed. It does not limit the communication to one fixed structure among the processing elements. Nor does it rely on a single interconnection capable of simulating others to achieve the flexibility of communicating processing elements. It provides a lattice of programmable switching elements with which dynamic and flexible interconnections can be specified.

The processing elements are connected to the switch lattice at regular intervals. The interval determines an important parameter w of the switch lattice which is called the corridor width. Two more parameters of the

switch lattice which are important to this research work are the degree (or the number of incident data paths) d and the cross-over capability c of the switches. The cross-over capability denotes the maximum number of independent data paths that can pass through a switching element. In Figure 2-4 we show two structures of the switch lattice. The circles represent switches and the squares represent processing elements.

Figure 2-4. Two structures of the switch lattice: (a) w = 1, d = 4; (b) w = 2, d = 8.

At each switching element there is some local memory for storing a fixed number of switch settings. The controller broadcasts a command to the switches and the switches then make connections according to a particular switch setting stored. The total effect of making connections at the switches constitutes the designated interconnection. The processing elements then communicate with each other assuming that the right interconnections are realized by the switches. (See [Snyd82] for more detailed description of the CHiP computer; See [Snyd81] for a discussion of programming processor interconnections.)

$(\mathfrak{I})$

The CHiP computer can be easily configured to be a mesh-connected computer. With the mesh interconnection, sorting can be done in  $O(\sqrt{n})$ time using adapted algorithms of Batcher's bitonic sort [Batc68, Kung77, Nass79]. In Chapter 3 we shall present a primitive operation POP-SORT which can perform the five database operations listed in Table 2-1. POP-SORT does not require the special architecture of the CHiP computer. On the contrary, it represents a methodology of applying parallel sorting to solve other database operations. POP-SORT can be implemented on the tree machine, the Ultracomputer, the mesh-connected computer, and the CHiP computer. If sorting can be implemented with systolic arrays then the systolic arrays can also be easily modified to implement POP-SORT.

## CHAPTER 3

## AN EFFICIENT PRIMITIVE OPERATION

Highly parallel algorithms for database operations have been widely studied. Several algorithms that perform sorting in sub-linear time exist [Batc68, Ston71, Thom77, Nass79; Mull75, Hirs78, Prep78]. The set operations union, intersection, and difference are best solved by performing sorting first [Schw80]. For duplicate-removal and join, there are linear-time bounded algorithms [Kung80, Song81]. Mentioned above are different algorithms and different machine architectures (see Table 2-1).

VLSI implementation of specialized devices has been vigorously proposed [Kung79, Fost80, Kung80, Kung82]. However, cost-effectiveness of VLSI implemented systems depends fundamentally on regularity and uniformity. The initial development expenses of VLSI systems must be offset by volume production. Thus, for VLSI implementation of highly parallel versions of database operations, it is important to identify a nucleus of processing steps common to the many database operations.

On general-purpose, highly parallel computers, programmability of algorithms again depends on regularity and uniformity. It is extremely expensive to develop software for highly parallel computers. Therefore, for performing database operations on highly parallel computers, it is also

important to identify an efficient primitive operation.

Much work on highly parallel sorting has been reported and has demonstrated some efficient solutions [Batc68, Ston71, Thom77, Nass79; Mull75, Hirs78, Prep78]. To identify primitive processes for database operations, we thus apply algorithmic approach to reduce many database operations to a sorting-based primitive. Whatever sorting algorithm and machine architecture are chosen, we then always have a unified treatment of those operations by implementing them with the primitive operation.

In this chapter we shall present POP-SORT (Primitive OPeration SORT) as a primitive operation for sorting, duplicate-removal, union, intersection, and difference. The latter three operations are relaxed to have multisets as operands. This relaxation, surely based on the versatility of POP-SORT on the one hand, has much practical merit in the context of query processing on the other hand. For natural join and equi-join, sub-linear time algorithms are possible if relations are preconditioned by using POP-SORT.

In Section 3.1 we present a special family of POP-SORT which is based on merge-oriented sorting methods. Employing a new comparison function, any merge-oriented sorting method becomes POP-SORT. An efficient implementation of the new comparison function and the overall performance of the POP-SORT are shown in Section 3.2. In Section 3.3 we present a general adaptation scheme that modifies any sorting algorithm to become POP-SORT. We then show the application of POP-SORT to the natural join and equi-join operations in Section 3.4.

#### 3.1 POP-SORT, a Special Example

Among the fast and highly parallel sorting algorithms, we are most interested in constructive, potentially logarithmic time, and nonprobabilistic algorithms. There are two categories of comparison-based sorting algorithms that rely fundamentally on pairwise comparisons. One category can be modeled as sorting networks [Knut73, p.220] that are constructed from comparator modules [Batc68, Ston71, Thom77, Nass79]. The other is based on the enumerating comparison method that each item is compared with each of the others [Mull75, Prep78]. While the former is conjectured to require  $O(\log^2 n)$  levels of network depth, the latter is able to reduce the time complexity to  $O(\log n)$ . However a considerable drawback with the enumeration sort is the requirement of  $O(n^2)$  computing components or the assumption of a shared, random access memory.

Batcher's bitonic merge sort [Batc68], described as a sorting network in Appendix A-1, is one of the most famous. There are many adapted versions of the bitonic sort. It requires  $O(\sqrt{n})$  time using mesh interconnection [Thom77, Nass79] or  $O(\log^2 n)$  steps using shuffle interconnection [Ston71]. The number of computing components needed for these adapted algorithms may be as small as O(n).

In this section we shall present a special example of POP-SORT called the bitonic POP-SORT. This instance of POP-SORT uses a new comparison function in Batcher's bitonic sorting method. The scheme that adapts the bitonic sort to become POP-SORT relies on the merge-oriented nature of the bitonic sort. Therefore, the adaptation scheme is immediately extended to all the merge-oriented sorting methods.

÷.

23

ы

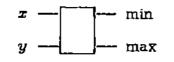

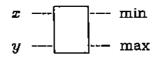

Bitonic sort is based on a simple local operation together with a regular and efficient way of pairwise data communication (Figure A-1). The local operation is a simple comparison function which can be described as:

1. 1. 19 19 1 1 1

```

(x,y) \rightarrow (\min(x,y), \max(x,y));

when x = y, min = max.

```

The communication scheme, from another point of view, is actually a sequence of perfect shuffle on different numbers of data items. Perfect shuffle is so powerful that it can simulate many important communication functions in time proportional to the logarithm of the number of data items [Schw80]. It should be able to solve other database operations if the simple comparison is replaced by more sophisticated ones.

**Definition** The compare-and-mark<sub>1</sub> operation performs comparison as well as marking duplicates, and the marking process is idempotent:

(1)

$$(x, y) \rightarrow (\min(x, y), \max(x, y))$$

when  $x \neq y$ ;

(2)  $(x, x), (x^{-}, x), \text{ or } (x, x^{-}) \rightarrow (x^{-}, x)$  and

$(x^{-}, x^{-}) \rightarrow (x^{-}, x^{-}).$

The basic operation compare-and-mark<sub>1</sub> preserves the ordering among distinct elements as usual. By marking a duplicate of x as  $x^-$  the basic operation enforces an ordering rule such that  $x^-$  is a little smaller than xbut never smaller than any y for y < x. The ordering among the marked

: 1

duplicates  $x^{-1}$ 's is arbitrary. The marking capability of the basic operation is to magnify the computation power of the bitonic sort to performing duplicate-removal. Rather than proving this for the bitonic sort only, we would prove a more general application of *compare-and-mark*<sub>1</sub> to all the merge-oriented sorting methods in the following theorem.

**Theorem 3-1.** Using the compare-and-mark  $_1$  operation, any merge-oriented sorting method can mark off all the duplicates.

[Proof] Consider any comparison-based method which merges two ordered sub-lists. Every pair of neighboring elements in the result list must have been compared directly, unless both elements are from the same sub-list. If both sub-lists have duplicates marked off. before merge then the result list must have all the duplicates marked by using the *compare-and-mark*<sub>1</sub> operation. For any merge-oriented sorting method that starts with merging sub-lists of length one, it guarantees no duplicates at all in the very beginning. By induction, all the duplicates must have been marked off in the final sorted list.  $\blacksquare$

In addition to performing duplicate-removal, any merge-oriented sorting method using *compare-and-mark*<sub>1</sub> is able to perform union. Performing union is the same as performing duplicate-removal on the totality of the two groups of data items. If our purpose is to unify sorting, duplicate-removal, and union then *compare-and-mark*<sub>1</sub> is powerful enough. However we are aiming at identifying a primitive for more database operations. Intersection and difference take two sets of data items as operands. One fundamental requirement is that we must be able to distinguish data items from the two groups in order to perform these two operations. We therefore extend the *compare-and-mark*, operation to handle two groups of data items.

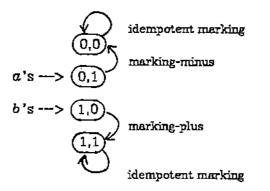

**Definition** Let A and B be multisets,  $a \in A$  and  $b \in B$ . The compare-andmark<sub>2</sub> operation, in addition to performing the simple comparison, enforces marking duplicates and three ordering rules:

(1) Idempotent marking-minus:

$(a,a), (a^-,a), \text{ or } (a,a^-) \rightarrow (a^-,a);$

- $(a^{-}, a^{-}) \rightarrow (a^{-}, a^{-}).$

- (2) Idempotent marking-plus:

$(b,b) \rightarrow (b^+,b), \text{ or } (b,b^+) \rightarrow (b,b^+);$  $(b^+,b^+) \rightarrow (b^+,b^+).$

(3) Quasi-stability:

(a, b) or  $(b, a) \rightarrow (a, b)$  for a = b (marked or unmarked).

Similar to that shown in Theorem 3-1 the marking capability of the compare-and-mark<sub>2</sub> extends the computation power of the bitonic sort to performing duplicate-removal and union. Moreover, two separate marking rules allow us to mark duplicates for two multisets separately. The rule of quasi-stability insists that A-elements precede B-elements if they all have the same value. With the local operation having two separate marking mechanisms and being quasi-stable, the execution of the bitonic sort will end up with a sorted sequence like  $...a^{-}a^{-}a^{-}a^{-}b^{+}b^{+}...$ , where a = b. We then can detect and manipulate all the  $..a^{-}b$ . pairs in constant time. The bitonic communication scheme together with the compare-and-mark<sub>2</sub> operation therefore can also implement the intersection and difference operations too. The three operations union, intersection, and difference are even relaxed to have multisets as operands. We have thus proved the following theorem.

**Theorem 3-2. (POP-SORT)** With the *compare-and-mark*<sub>2</sub> operation, any merge-oriented sorting method can be used for duplicate-removal, union, intersection, and difference.

How do we unify the operations that take a single multiset as operand and the others that take two multisets? It requires some initial processing on input operands. In algorithm 3-1, execution of the database operations is partitioned into three phases: initialization, primitive, and completion. The input to the algorithm may be one or two multisets. The input conflict is resolved in the initialization phase. Only in the completion phase may the database operations invoke different constant-time post-sorting processing. The output from the algorithm is that all the undesired data are marked off, either marked as  $x^-$  or  $x^+$ .

Algorithm 3-1: The bitonic: POP-SORT.

INTPUT: Data items from one or two multisets A and B. OUTPUT: All the unmarked data items.

- A. Initialization phase

- 1. Data items are arbitrarily labeled as A-elements for sorting, duplicate-removal, and union.

- 2. For intersection and difference, A-elements and B-elements are labeled differently in order to distinguish them throughout the whole processing.

- B. Primitive phase

- 1. Run the bitonic sort using the compare-and-mark<sub>2</sub> operation.

- C. Completion phase

- 1. Remove-duplicates, sorting, and union do not need any further processing.

- 2. For intersection and difference, the constant-time processing in this phase is shown as a program segment in the following.

```

(* completion phase *)

for all i do (* x_{n+1} = \infty is a dummy *)

compare x_i with x_{i+1}

if both unmarked then

case

intersection: mark x_i^-;

if not equal then mark x_{i+1}^+;

difference: mark x_{i+1}^+;

if equal then mark x_i^-;

```

The relaxation that union, intersection, and difference take multisets as operands of course relies on the versatility of POP-SORT. The practical consideration is that multisets are artifacts of operations such as projection and concatenation. Evidently many query languages (SEQUEL, QUEL, and QBE [Ullm80]) provide operators for working with multisets. On many occasions in database query processing, duplicate-removal and union (intersection, or difference) are executed subsequently. For example, projection is first requested before two relations are to be joined,  $\Pi(R_1) \cup \Pi(R_2)$ , where  $\Pi$  denotes projection. In order to perform the set operation  $\cup$ , duplicate tuples produced by the operation projection must be removed. We have the following:

> union  $(A, B) = rmdup(A) \cup rmdup(B)$ , inter  $(A, B) = rmdup(A) \cap rmdup(B)$ , differ (A, B) = rmdup(A) - rmdup(B),

With the relaxation the two operations are combined together and a single run of sorting is enough. However, without the relaxation, performing the two operations sequentially is necessary. The sequential execution in this case may imply more data movement and programming overhead.

The result sequence could be sparse due to the marked-off duplicates. The marked-off duplicates can be filtered out while outputting the sequence. Alternatively, in some applications one might want to compress the sequence internally so that the marked duplicates are squeezed out. Schwartz presented an ingenious method to separate and pack marked data on the Ultracomputer in  $O(\log n)$  time [Schw80]. If the shuffle-exchange interconnection is available the compression job can then be best done by Schwartz's pack algorithm. A desirable solution might be running POP-SORT again using another comparison function which treats the marked duplicates as  $+\infty$ .

#### 3.2 Implementation and Performance

Different interconnection patterns among processing elements for the bitonic sort and their implementations have been reported in the literature [Batc68, Ston71, Thom77, Nass79, Schw80, Prep81]. The local operation at each processing element is the crucial part that may extend a mergeoriented sorting algorithm to perform other database operations. We shall consider only the implementation of the local operation in this section.

An efficient implementation of the compare-and-mark<sub>1</sub> operation uses one extra bit for marking. The mark bit, initially set to be 1, is appended to each data item as the least significant bit. The operation works simply to

С;

clear one least significant bit whenever two elements are found to be equal.

Similarly the compare-and-mark<sub>2</sub> can be implemented using two mark bits, one for distinguishing A-elements from B-elements and the other for marking duplicates. The mark bits are tagged to each data item as the two least significant bits. Let a and b be *l*-bit data items concatenated with the two mark bits,  $a \in A$  and  $b \in B$ . Their binary representations are  $(a_{l-1}, a_{l-2}, ..., a_1, a_0, a_{-1}, a_{-2})$  and  $(b_{l-1}, b_{l-2}, ..., b_1, b_0, b_{-1}, b_{-2})$  respectively. Initially, we have the mark bits set in such a manner that  $(a_{-1}, a_{-2}) = (0, 1)$ and  $(b_{-1}, b_{-2}) = (1, 0)$ . The compare-and-mark<sub>2</sub> function can be described as:

if x = y then  $x_{-2} \leftarrow x_{-1}$ ; min  $\leftarrow \min(x, y)$ , max  $\leftarrow \max(x, y)$ ;

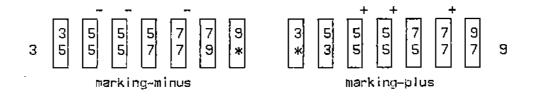

The compare-and-mark<sub>2</sub> function can be interpreted more clearly using a state diagram as shown in Figure 3-1. Define the state of a data item as the value of its two mark bits. There are only four possible states, with (0,1) the initial state for all the A-elements and (1,0) for B-elements. The rule of marking-minus changes the state (0,1) to (0,0) for A-elements. Since the marking is idempotent, once a data item reaches the (0,0) state it remains in that state. The rule of idempotent marking-plus works in the same way for B-elements.

Figure 3-1. State digram for two idempotent marking functions.

After the completion phase of POP-SORT, all the desired data items may be in the state either (0,1) or (1,0). Suppose we arbitrarily choose (0,1) as the final state of all the desired data items. To separate and pack all the unmarked data using POP-SORT again, we need some more bit manipulation capability.<sup>†</sup> First, reset the states (1,0) and (1,1) to (0,0). We then may rotate each data item such that all the desired data has the most significant bit 1. Alternatively, we may design the second mark bit with some flexibility so that it may be programmably tagged to each data item as the least or most significant bit.

Several adapted versions of the bitonic sort show that more data routing time is required than comparison time. Suppose that a merge-oriented sorting algorithm takes  $T_1(n) * t_R + T_2(n) * t_C$  time, where  $T_1(n)$  is the number of data routing steps and  $T_2(n)$  the number of comparison steps. The POP-SORT based on this sorting algorithm then requires  $T_1(n) * t_R + T_2(n) * t'_C$  time. The only difference is the step size  $t'_C$ . That is,  $\frac{1}{t}$  Unfortunately the bitonic sort is not stable. Otherwise, performing sorting on the two merk bits would be able to separate marked and unmarked data items.

31

- 2 -

the processing time for one local operation is changed. The marking function, on one or two bits, of the local operation usually takes less time than the comparison function (l bits). The ratio of  $t'_{C}$  to  $t_{C}$  is bounded by a small constant, actually close to one.

$$\rho \leq \frac{lc}{lc} < 2$$

where  $\rho = \frac{l+2}{l}$  for bit serial design,

or  $\rho = \frac{log(l+2)}{\log l}$  for bit parallel design.

In summary, the bitonic POP-SORT, based on Batcher's bitonic merge sort, performs as well as the bitonic sort. It compares favorably with other algorithms known for the five basic database operations (Table 2-1). The bitonic POP-SORT outperforms Kung's and Song's duplicate-removal algorithms dramatically. For the other operations, we do not sacrifice any efficiency by using it. Since the bitonic POP-SORT serves as a primitive for many operations, the overall system performance may improve substantially (e.g. query embedding in Chapter 6). The program loading is no longer necessary for every single operation. Data movement can be reduced because data may stay longer for more processing.

#### 3.3 POP-SORT, in General

Batcher's bitonic merge sort has been shown easily adaptable to become POP-SORT. The  $s^2$ -way merge sort performs even better than bitonic sort on a mesh-connected computer when the number of data items is large [Thom77]. According to Theorem 3-2, we already have the first order generalization that any merge-oriented sorting algorithm can employ the compare-and-mark<sub>2</sub> operation to become POP-SORT. Of course  $s^2$ -way merge sort can be another base sorting algorithm for POP-SORT. However, can we also adapt other sorting methods to become POP-SORT?

In this section, we shall show a general scheme to employ any sorting algorithm as a POP-SORT. The general scheme again involves extending some marking capability to a base sorting algorithm. In its most general sense, POP-SORT thus presents an idea to adapt any sorting algorithm to become an efficient primitive for many database operations.

The computation power of the basic operation *compare-and-mark*<sub>2</sub>, in addition to the simple comparison function, comes from enforcing the ordering rules of quasi-stability, marking-minus, and marking-plus. For a sorting algorithm that is not merge-oriented, it might not be able to incorporate all the ordering rules into the comparison function. Nevertheless, given a sorted sequence of data items, a "shift-copy and compare" scheme, shown in Figure 3-2, is able to detect and mark all the duplicates. If the linear interconnection is available then the marking process requires only O(1) time.

Figure 3-2. A "shift-copy and compare" scheme for detecting duplicates in a sorted sequence.

Suppose that newSORT is a new and faster-than-ever parallel sorting algorithm. Whether newSORT is merge-oriented or not, it can be adapted to become POP-SORT according to the general scheme described in Algorithm 3-2. The general scheme is composed of four phases: initialization, sorting, marking, and completion. A general POP-SORT is exactly the same as a merge-oriented POP-SORT in the initialization and completion phases. For a merge-oriented POP-SORT, the second and the third phases of a general POP-SORT is combined together due to the reinforced computation power of *compare-and-mark*<sub>2</sub>.

Algorithm 3-2: A general POP-SORT.

INTPUT: Data items from one or two multisets A and B.

OUTPUT: All the unmarked data items.

- A. Initialization phase

- 1. Data items are arbitrarily labeled as A-elements for sorting, duplicate-removal, and union.

- 2. For intersection and difference, A-elements and B-elements are labeled differently in order to distinguish them throughout the whole processing.

- B. Sorting phase

- 1. Sort the data items, labeled as A-elements or B-elements, according to the quasi-stability rule using newSORT.

- C. Marking phase

- 1. If not performing sorting then continue.

- 2. Mark duplicates according to the rules of marking-minus and marking-plus using the "shift-copy and compare" scheme.

- D. Completion phase

- 1. If not performing duplicate-removal then continue.

- 2. Intersection and difference will invoke constant-time but different processing as in Algorithm 3-1.

The theoretical lower bound of the time complexity of newSORT is  $\Omega(\log n)$ . The marking phase requires only O(1) time if linear interconnection is provided. The first and the last phases also requires only constant processing time. Therefore the POP-SORT using newSORT as its base also shares the same time complexity as newSORT. This even generalizes Theorem 3-2 -- Any sorting algorithm can be adapted to a four-phased POP-SORT without introducing any significant overhead.

Similar to a merge-oriented POP-SORT, an efficient implementation for a general POP-SORT needs two mark bits. One of the mark bits is used for distinguishing two multisets, and the other is for marking duplicates. In a general POP-SORT the quasi-stability, marking-minus, and marking-plus rules are still enforced using the two mark bits. The bit manipulation capability needed in a general POP-SORT is thus no less than that in a mergeoriented one.

## 3.4 Application to Join Operations

6.6

. 1

The number of result tuples after joining two relations A and B denotes the minimum totality of computing work needed for join. Assuming each relation of size n for simplicity, the figure may rarely become as large as  $O(n^2)$ . Using O(n) processing elements, Kung's [Kung80] and Song's [Song81] linear time algorithms are optimal in the sense of handling the worst case. For most situations, the result relation has many fewer tuples. An A-tuple may have to join with only some B-tuples. By applying POP-SORT to precondition the relations, a join system shown in this section can perform the natural join and equi-join operations in sublinear time.

۰.

Any sorting algorithm can bring together all the elements of the same value. The groups of elements of the same values are called *aggregates*. We first sort the relations over the joining attributes using POP-SORT. The primitive operation is quasi-stable. It produces aggregates as well as insists that all the *A*-tuples precede *B*-tuples in each aggregate. We then can perform natural join and equi-join simply by shifting all the *B*-tuples in one direction to join with *A*-tuples. This process is called "easy-catch".

output result tuples

Figure 3-3. Logical structure of the easy-catch system for performing join operations.

Define d as the longest distance that a *B*-tuple needs to shift in order to catch all the joinable *A*-tuples. For easy-catch d is the largest size of the aggregates. To reach the goal of having sublinear time performance the catching process is better terminated after d shift steps. Unfortunately d is usually not known beforehand. In Figure 3-3 we show a solution to halting the catching process by superimposing a tree interconnection on top of the processing elements. A halting controller located at the root of the tree interconnection supervises all the processing elements. The tree interconnection provides the communication paths between the controller and the processing elements. Each processing element is responsible for reporting its

.

activity by sending a "busy" or "idle" message up to the controller. The controller will broadcast the "halt" message when it decides all the processing elements are idle. If a halting message is received, the processing elements stop.

The programming of the join system is extremely simple. All the processing elements execute the same program and the program is nothing but a looping over after some initialization. Suppose there are two registers,  $\alpha$ and b, capable of holding A and B tuples<sup>†</sup> in each processing element. The processing elements execute the looping program as follows:

```

for all i do

(* initialization *)

a<sub>i</sub>, b<sub>i</sub> ← nil;

if A-tuple then load a<sub>i</sub> else load b<sub>i</sub>;

(* easy-catch: shift and join *)

repeat forever

receive(msg);

if msg = "halt" then stop;

shift; (* b<sub>i</sub> ← b<sub>i+1</sub> *)

if a<sub>i</sub> match b<sub>i</sub> then {perform join; send("busy")}

else send("idle");

```

The controller detects that all the processing elements are idle after a  $\log n$  time delay. Another  $\log n$  time delay is necessary for broadcasting the "halt" message to all the processing elements. The time for performing the natural join and equi-join is thus the total time for POP-SORT, easy-catch, and the halting delay.

$T = T(POP - SORT) + O(d) + O(\log n) \text{ where } d \le n.$

<sup>7</sup> The tuple may only consist of tuple-id and the values for the joining attributes.

Since POP-SORT needs only sublinear time, the join operations can be done in sublinear time as long as d is less than O(n). If  $d = O(\sqrt{n})$  then the join operations can be done in  $O(\sqrt{n})$  time using the bitonic POP-SORT.

199

The CHiP computers are good candidates for implementing the join system. Suppose that data items from both A and B are sorted by POP-SORT in a quasi-stable fashion into snake-like row-major order (see Chapter 5.) Two co-existing configurations shown in Figure 3-4 are feasible if there is a cross-over capability on switches. We assume that fan-in on switches behaves like a logic "AND", and switches also have fan-out capability to perform broadcasting. The linear and tree interconnections for the join system hence are provided by the two configurations.

|                                    | • • • • • • • • • • • |

|------------------------------------|-----------------------|

|                                    | ◦□◦□◦□◦               |

|                                    | 000000000             |

| ० <u>□-०-</u> ⊡- <del>०-</del> ⊡-० | ° 🗆 ° 🗖 👌 🗖 ° 🗖 °     |

| 0 0 0 0 0 0 0 0 ¢                  | · • • • • • • • • • • |

| ┍╼┎╼╍┎╼╍                           | 。白々日々日々日。             |

| 40000000                           | 0000000000            |

| ᠔᠆᠋᠆ᡐ᠆᠋᠆ᡐ᠆᠋᠆ᡐᢩ᠊᠋᠆ᢩ                 |                       |

| 000000000                          |                       |

| °⊡-°-⊡-°-⊡-°                       |                       |

|                                    | 000000000             |

Figure 3-4. Two configurations on a CHiP computer for implementing the easy-catch system.

For the purpose of area-economy, the join system is implemented as above in a square CHiP region. Unfortunately, only perimeter processing elements have I/O ports to the peripheral storage devices. There would be a problem of non-uniform distribution of result tuples since they would accumulate at some PEs. We call this the *hot spots problem*. If there is enough memory space in processing elements, the hot spots problem does not do any harm as long as the result relation is to be dumped out of the CHiP processor. For some cases, the result relation is to be processed further (see query embedding in Chapter 6.) Then the hot spots problem can be solved by the Sprinkle Algorithm as shown in Appendix B. The Sprinkle Algorithm employs the same communication scheme as a single stage of the bitonic merge. Let k be the maximum number of result tuples at hot spots. The Sprinkle Algorithm requires  $O(\frac{k}{2} \cdot \sqrt{n})$  time using mesh interconnection. The algorithm works especially well when k has small values.

This join system can perform other join operations too. The le-join and ge-join can be implemented exactly in the same way as natural join and equi-join, except that d is no longer the largest size of the aggregates. To perform ne-join, we need "two-way-catch", shifting B tuples in both directions to join with A tuples. The join system is especially suitable for natural join and equi-join because the value of d is more likely small for the two types of join operations.

In summary, the join system in Figure 3-4 provides adaptive performance for join operations. "Easy" joins that requires B-tuples join with only limited numbers of A-tuples are suitable for easy-catch implementation. They can be done with much better performance by avoiding executing them as "difficult" joins.

## CHAPTER 4

## OPTIMALITY OF THE PRIMITIVE OPERATION

The order of data items often has a profound influence on the speed and simplicity of algorithms which manipulate them [Knut73]. As a consequence, sorting has been found to be very useful as a pre-processing step for a wide variety of applications. It is well known that a considerable portion of the computer running time was and still is spent on sorting.

Although sorting is useful, in some cases it is overused. For example, selection of the median of n data items requires only  $\Theta(n)$  comparisons, although the more expensive sorting is a common way to solve it. Moreover, sorting is completely useless in some other cases. Researchers found that the benefit of data ordering yields its ground to the computing power of parallel hardware on the searching problems (insertion, deletion, and update) [Bent79]. Despite these observations, the usefulness of sorting might be underestimated in the context of parallel computation.

While the usefulness of sorting might be over-emphasized in the sequential case, the feasibility of applying sorting in the parallel case needs more careful exploration. POP-SORT presents a mechanism to extend sorting to performing many other database operations. A methodology for applying parallel sorting to the solution of other problems is thus demonstrated. In

order that POP-SORT be an optimal primitive, parallel sorting must be an optimal way to implement those database operations. However, is parallel sorting an optimal way of performing those database operations?

In this chapter we shall investigate the optimality of the primitive operation POP-SORT. We show how the reducibility of sorting to duplicateremoval plays a crucial role in determining the optimality. We then concentrate on studying the reducibility of sorting to duplicate-removal. Two comparison functions are considered: the strong comparison (<, =, >) and the weak comparison  $(=, \neq)$ . We prove the reducibility for all the computations based on the weak comparison function. We also prove the reducibility for a subclass of computations based on the strong comparison function.

Section 4.1 establishes a time-complexity hierarchy representing the reducibility relationships among POP-SORT and the other five database operations. These relationships show that the hierarchy would collapse if sorting is reducible to duplicate-removal. A collapsed hierarchy implies the optimality of POP-SORT. The important relationship between sorting and duplicate-removal is then studied. A special model of parallel computation suitable for our study and two types of comparison functions are discussed in Section 4.2. In Section 4.3 and 4.4, we investigate the reducibility of sorting to duplicate-removal on the computation model with the two comparison functions respectively.

## 4.1 Collapsing the Complexity Hierarchy

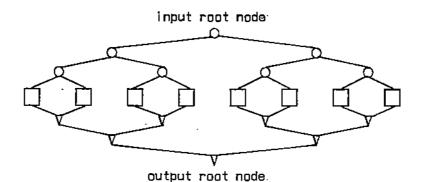

By enforcing some extra ordering rules, any sorting algorithm can be extended to become POP-SORT without any significant overhead. POP-SORT serves as a primitive operation for sorting, duplicate-removal, union, intersection, and difference. The bitonic POP-SORT, an instance of the primitive operation, improves the upper bound for duplicate-removal over the algorithms in [Kung80] and [Song81]. Also, the fastest algorithms known for union, intersection, and difference apply sorting as a pre-processing step [Schw80]. Therefore POP-SORT does not sacrifice any efficiency for unifying these operations.

However, is POP-SORT an optimal primitive for performing these five database operations? To evaluate the optimality of the primitive operation, we investigate the complexity relationships between it and the five operations. The relationships are measured in terms of reducibility. Let  $P_1$  and  $P_2$  be two problems, and  $\psi_1$  be any algorithm for solving the problem  $P_1$ . The problem  $P_2$  is said to be reducible to  $P_1$  iff there is an algorithm  $\psi_2$ which applies  $\psi_1$  to solve  $P_2$ . We are most interested in the case when both algorithms have time complexities of the same order. i.e.  $O(T(\psi_1)) = O(T(\psi_2)).$

Some important reducibility relationships are summarized in the following:

- All the five operations are reducible to POP-SORT. Chapter 3 presents POP-SORT as a primitive operation which can perform sorting, duplicate-removal, union intersection, and difference.

- *POP-SORT is reducible to sort.* A "shift-copy and compare" scheme is shown in Chapter 3 to perform the marking-minus and marking-plus functions. A general mechanism based on the scheme is presented to

adapt any sorting algorithm to POP-SORT. The "shift-copy and compare" scheme takes only constant time. The adaptation overhead is thus negligible.

• Duplicate-removal is reducible to union, intersection, and difference. The operations union, intersection, and difference are allowed to take multisets as operands. Duplicate-removal thus can be implemented as:  $rmdup(A) = union(A, \varphi) = inter(A, A) = differ(A, \varphi)$ , where  $\varphi$  is the empty set.

Figure 4-1. Collapsing the time complexity hierarchy implying the optimality of POP-SORT.

The above reducibility relationships are also depicted as a time complexity hierarchy in Figure 4-1. The arrow "->" in the figure denotes the relationship "is reducible to". To collapse the complexity hierarchy would imply the optimality of POP-SORT. The relationship represented by the dotted arrow ".....>" therefore plays an important role in collapsing the complexity hierarchy. For POP-SOPT to be an optimal primitive, sorting must be an optimal way to perform duplicate-removal. The key to unifying the five operations by POP-SORT is the extension of sorting to mark off duplicate items. Hence there is no surprise that the optimality of POP-SORT relies on the optimality of sorting to perform duplicate-removal.