# **ARTICLE**

Received 10 Apr 2012 | Accepted 3 Sep 2012 | Published 2 Oct 2012

DOI: 10.1038/ncomms2110

# Highly transparent nonvolatile resistive memory devices from silicon oxide and graphene

Jun Yao<sup>1,\*</sup>, Jian Lin<sup>2,\*</sup>, Yanhua Dai<sup>3</sup>, Gedeng Ruan<sup>4</sup>, Zheng Yan<sup>4</sup>, Lei Li<sup>4</sup>, Lin Zhong<sup>5,6</sup>, Douglas Natelson<sup>3,5</sup> & James M. Tour<sup>2,4,6</sup>

Transparent electronic memory would be useful in integrated transparent electronics. However, achieving such transparency produces limits in material composition, and hence, hinders processing and device performance. Here we present a route to fabricate highly transparent memory using  $\mathrm{SiO}_X$  as the active material and indium tin oxide or graphene as the electrodes. The two-terminal, nonvolatile resistive memory can also be configured in crossbar arrays on glass or flexible transparent platforms. The filamentary conduction in silicon channels generated in situ in the  $\mathrm{SiO}_X$  maintains the current level as the device size decreases, underscoring their potential for high-density memory applications, and as they are two-terminal based, transitions to three-dimensional memory packages are conceivable. As glass is becoming one of the mainstays of building construction materials, and conductive displays are essential in modern handheld devices, to have increased functionality in form-fitting packages is advantageous.

<sup>&</sup>lt;sup>1</sup> Applied Physics Program through the Department of Bioengineering, 6100 Main Street, Houston, Texas 77005, USA. <sup>2</sup> Department of Mechanical Engineering and Material Science, 6100 Main Street, Houston, Texas 77005, USA. <sup>3</sup> Department of Physics and Astronomy, 6100 Main Street, Houston, Texas 77005, USA. <sup>4</sup> Department of Chemistry, Center for Nanoscale Science and Technology, 6100 Main Street, Houston, Texas 77005, USA. <sup>5</sup> Department of Electrical and Computer Engineering, 6100 Main Street, Houston, Texas 77005, USA. <sup>6</sup> Department of Computer Science, Rice University, 6100 Main Street, Houston, Texas 77005, USA. \*These authors contributed equally to this work. Correspondence and requests for materials should be addressed to D.N. (email: natelson@rice.edu) or to J.M.T. (email: tour@rice.edu).

otential technological advances from visibly transparent circuits have aroused extensive interest and motivated various studies<sup>1,2</sup>. Progress has been made by using wide-bandgap semiconductors or nanowires to construct transparent transistors<sup>3-6</sup>. For the realization of a fully integrated transparent circuit, high transparency is also desirable in one of the other circuitry elements: the memory unit. Although charge-based transparent memory can be constructed based on the transistor structure<sup>7–9</sup>, it comes with the tradeoff in nonvolatility due to the limitations in achieving both high transparency and efficient charge trapping in the floating gate. This sacrifice can be eliminated using resistive switching memory that functions on a non-charge-based mechanism<sup>10</sup>, provided that transparency is achieved both in the resistance-change (active) material and the electrodes. Although this search has recently been done in metal oxides and organic materials<sup>11-13</sup>, a hightransparency memory device based on more conventional materials is desirable for processing and application reasons. Using silicon oxide (SiO<sub>x2</sub>  $x\sim2$ ) and graphene, the former a ubiquitous material favoured by the semiconductor industry and the latter a promising two-dimensional conductor<sup>14</sup>, we demonstrate here a nonvolatile memory device featuring both high transparency and robust retention, further implemented on a flexible plastic substrate. This new set of physical parameters, transparency with flexibility, could open the door for greater functionality in form-conforming packages.

For optical transparency without sacrificing the memory density or capacity, intrinsic transparency is required in the single memory unit. This requirement precludes many resistance-change materials with a bandgap < 3.1 eV (ref. 1). For the vertical sandwiched structure adopted in resistive switching memory<sup>10</sup>, the transparency can be further compromised by the top and bottom electrodes. For this reason, although transparent solid electrolytes can be involved in some metallic programmable cells<sup>10,15</sup>, the need for a metal electrode as the filament-injection source limits the transparency in the device unit. Similarly, the requirement of a specific electrode-material interface in some other resistive switching systems<sup>16</sup> restricts the choice of transparent electrode materials. As the mechanisms in many resistive switching systems have not yet been fully understood<sup>16</sup>, particularly with respect to the role of the electrode, the assessment of the potential application in transparent electronics depends on the actual demonstration.

As one of the backbones of the semiconductor industry,  $\mathrm{SiO}_x$  comes with the advantages in both its material composition and facile processing. With a large bandgap (~9 eV), it also features high transparency. Instead of merely serving as a passive solid electrolyte in metallic programmable  $\mathrm{cells^{15}}$ , an active role of  $\mathrm{SiO}_x$  in constructing resistive switching memory was recently revealed:  $\mathrm{SiO}_x$  itself can serve as the source of the formation of metallic-phase silicon filaments as well as the surrounding supportive  $\mathrm{matrix^{17,18}}$ . The result is a memory effect that is intrinsic to  $\mathrm{SiO}_x$  and largely electrode independent  $\mathrm{^{19,20}}$ . This intrinsic memory effect in  $\mathrm{SiO}_x$  relaxes the restriction on the choice of electrode materials, making high-transparency memory devices feasible.

## **Results**

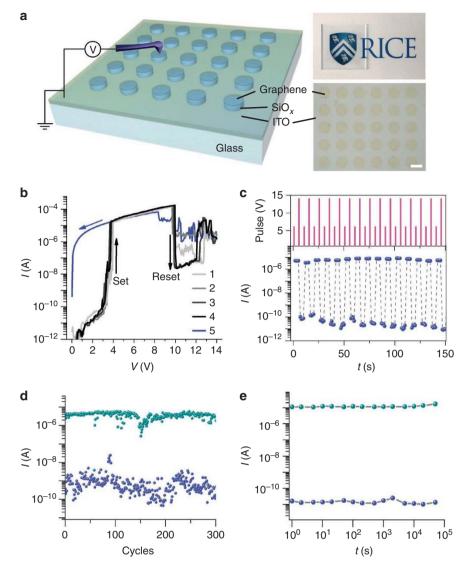

**Graphene/SiO**<sub>x</sub>/**indium tin oxide (ITO) devices.** We first chose graphene and ITO as the top and bottom electrode materials, respectively. Graphene represents a new class of two-dimensional material that is promising for future transparent electronics<sup>21</sup>, whereas ITO represents the mainstream choice for transparent conductive materials. The combination of the two electrode materials in a single device demonstrates the versatility of the  $SiO_x$ -based memory with respect to the choice of transparent electrode materials. Vertical sandwiched pillar structures of  $G/SiO_x/ITO$  (here G denotes graphene) were defined on a glass substrate (Fig. 1a). Specifically, the  $SiO_x$  layer (~70 nm thick) was prepared by physical vapour deposition on a glass substrate coated with a layer of ITO

(~120 nm thick), with the top electrode consisting of bilayer graphene prepared by the chemical vapour deposition method and transfer process<sup>22</sup>. Photolithography and reactive ion etching were then used to define the circular  $G/SiO_x/ITO$  memory units at a diameter of ~100  $\mu$ m for an easy probe-tip landing (Supplementary Fig. S1). The electrical characterizations were performed in vacuum (10<sup>-5</sup> Torr) at room temperature in a probe station connected to an Agilent 4155C semiconductor parameter analyser.

Figure 1b shows a series of current-voltage (I-V) curves from a G/SiO<sub>v</sub>/ITO device after the electroforming process (Supplementary Fig. S2). In the characteristic I-V curve (black curve), starting from a high-resistance (OFF) state, the current level suddenly increases at ~4 V to a low-resistance (ON) state and then decreases at  $\sim \! 10 \, \text{V}$ . The current or conductance increase and decrease define the set and reset values, respectively 17,20, indicating unipolar resistive switching behaviour. The resistance or memory state can be read at a low-voltage bias (<3 V) without altering its value, featuring the nonvolatile property. Figure 1c,d shows a series of memory cycles using +1, +6 and +14V as read, set and reset voltages, respectively. Note that more detailed mechanistic discussions with respect to the phenomenological behaviours of the set and reset processes can be found in ref. 18. The nonvolatility or memory retention was tested by continuous memory-state readout at + 1 V, which showed no degradation after 5×10<sup>4</sup>s (Fig. 1e). This is consistent with our previous study showing that the memory state is robust in ambient environment for more than 3 months<sup>23</sup>. After testing more than 20 devices, a device yield of ~70% was achieved for the tested memory units, discounting the possibility of a contamination-related memory effect. The device failure is defined as either the failure to electroform the device (up to 40 V) or a state of non-switchable conducting (short circuited) after the attempt of electroforming. However, this depressed yield compared with that achieved in devices with polysilicon electrodes<sup>17</sup> is likely caused by the atomically thin nature of the graphene electrode, as structural damage in the graphene layer might result during the processing and/or the probe-tip landing processes, during which the contacting pressure could not be well monitored (Fig. 1a). The resultant damage could cause sliding of the graphene electrode towards the etched edge region of the device or the direct puncture and penetration of oxide, and hence, shorting of the devices, thereby lowering the yield. Note that the possibility of extrinsic switching through metal filament formation from the tungsten probe tip in contact with the top electrode was ruled out by control experiments in which memory switching could not be achieved in devices that were devoid of the top graphene electrodes (Supplementary Fig. S3). Note that the *I–V* curves in the reset region generally involve current fluctuations<sup>23</sup> (blue curve, Fig. 1b), which prevent a clear definition of the threshold value of the reset voltage. The current fluctuations are indications of the dynamic and competing effects between the set and reset processes 18. We therefore performed a series of measurement on the set voltages, as well as the ON and OFF currents, showing a comparatively narrow distribution of the set voltages (4.26±0.54 V) and the ON/OFF ratios are between 10<sup>3</sup> and 10<sup>6</sup> (Supplementary Fig. S4).

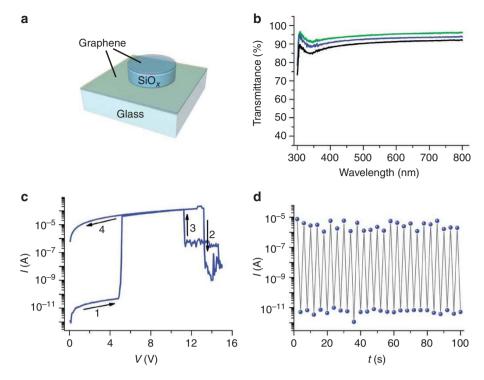

$G/SiO_x/G$  devices. The intrinsic memory switching in  $SiO_x$  enables the construction of completely metal-free transparent memory devices by using graphene as the only electrode material. For the fast progress in synthesis and abundance in the carbon sources<sup>24–26</sup>, graphene has become a promising candidate for transparent electrode materials<sup>21,25</sup>. The use of graphene and  $SiO_x$ , another low-cost and industry-standard material, as the only materials for constructing memory devices, therefore, comes with the advantages both in the material composition and processing. This is in contrast to other transparent resistive switching memory based on traditional metal-oxide materials<sup>11–13</sup>, for which low-cost replacements such as graphene have been sought<sup>21,25</sup>. As shown in Fig. 2a, vertical

Figure 1 | Memory effect in a  $G/SiO_x/ITO$  device. (a) Left panel: schematic of the  $G/SiO_x/ITO$  device arrays on a glass substrate and the setup for electrical characterization. The top right panel shows the  $G/SiO_x/ITO$ -layered structure on a glass substrate and the bottom right panel shows the optical images of the  $G/SiO_x/ITO$  devices; scale bar,  $100 \,\mu\text{m}$ . (b) I-V curves from an electroformed  $G/SiO_x/ITO$  device, with the numbers indicating the voltage-sweep orders. Curves 1-4 are forward voltage sweeps  $(0\rightarrow14\,V)$ , and curve 5 is backward voltage sweep  $(14\rightarrow0\,V)$ . The voltage sweep rate is  $2.8\,V\,s^{-1}$  for this and the other I-V curves in this paper. (c) (Top panel) A series of voltage pulses of  $+6\,V$ , +1V (five times) and  $+14\,V$  serve as set, read (five times) and reset operations, respectively. (Bottom panel) Currents corresponding to each read pulse in the top panel. (d) 300 memory cycles in a  $G/SiO_x/ITO$  device. (e) Retention of the memory state tested by continuous +1V voltage pulses (at a rate of 1 pulse per second) for both an ON and an OFF state.

sandwiched pillar structures of G/SiO<sub>x</sub>/G with the same diameters (~100 μm) were defined on the glass substrate (Supplementary Fig. S5), which shows 90% transparency at 550 nm (Fig. 2b). Specifically, bilayer graphene sheets were used for both the top and bottom electrodes with the  $SiO_x$  thickness ~70 nm. The devices showed similar resistive switching I-V curves and memory property (Fig. 2c,d) to those exhibited in Fig. 1 at a yield of 65% with over 20 devices being tested; the 35% non-operating devices being short circuited. The use of graphene as both top and bottom electrodes further indicates the intrinsic memory property of  $SiO_x$  by excluding the possibility of metal filament formation from the electrode materials. Note that although graphene and graphene oxide have been used in some resistive switching systems, the inevitable use of metal electrodes limits the transparency of the memory devices<sup>27,28</sup>. Because of the low optical absorbance in graphene<sup>29</sup>, uniform transmittance as high as ~90% over the entire visible range is achieved

in the G/SiO<sub>x</sub>/G devices (Fig. 2b). Note that here bilayer graphene was used for both the top and bottom electrodes for the purpose of better coverage. It is not due to an intrinsic limit with respect to the resistance. In fact, as the ON-state resistance of SiO<sub>x</sub> is  $\gg 10\,\mathrm{k}\Omega$  (Fig. 2d), doped monolayer graphene (<1 k $\Omega$  sq  $^{-1}$ )<sup>21</sup> can serve as the electrode material. As a result, the transmittance can be further increased to ~95% (blue curve, Fig. 2b), which is higher and more uniform than those achieved in other systems  $^{11-13,30}$ .

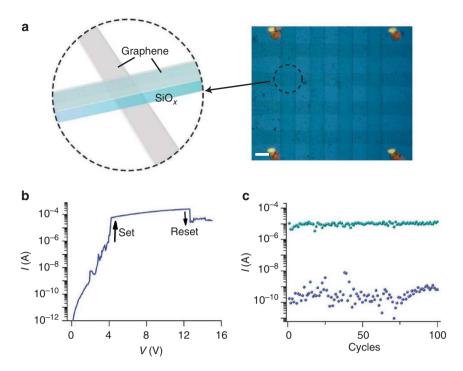

Although the vertical pillar structures adopted above are frequently used for single-device testing purpose  $^{16}$ , the implementation of the memory device relies on the construction of crossbar arrays  $^{10,16}$ . We further demonstrate the transparent  $\mathrm{SiO}_x$  crossbar memory arrays with graphene serving as both the electrode and interconnect material, in this case constructed atop a silicon/silicon oxide substrate. Figure 3a shows a 4×4  $\mathrm{SiO}_x$  crossbar structure with the  $\mathrm{SiO}_x$  (~70 nm thick) sandwiched between the top and

Figure 2 | Memory effect in a G/SiO<sub>x</sub>/G device. (a) Schematic of the G/SiO<sub>x</sub>/G device on glass. (b) Optical transmittance in G/SiO<sub>x</sub>/G-layered structures with different layer thicknesses of graphene. The green, blue and black curves correspond to the transmittance in MLG/SiO<sub>x</sub>/MLG, MLG/SiO<sub>x</sub>/BLG and BLG/SiO<sub>x</sub>/BLG structures. Here BLG and MLG denote bilayer graphene and monolayer graphene, respectively. (c) Characteristic *I-V* curves from an electroformed G/SiO<sub>x</sub>/G device. The arrows indicate the voltage-sweep directions and the numbers indicate the order. (d) Corresponding memory cycles from the device using +6 and +15 V as set and reset voltages, respectively. The programming current is not shown here and the memory states (current) were recorded at +1V.

bottom bilayer graphene lines. Figure 3b,c show the typical I-V curve and memory switching cycles from one of the crossbar units  $(20\times20\,\mu\text{m}^2)$ , featuring the same switching characteristics as those shown in the vertical pillar structures. The observed ON and OFF currents fall into the same range as those observed in vertical pillar structures (Supplementary Fig. S4). The crossbar structure with both the top and bottom electrodes extended through the graphene lines avoids the direct contact between the probe tip and the memory unit during the electrical testing, which eliminates the possibility of metal contamination from the probe tip and, hence, further confirms the intrinsic memory effects in  $SiO_x$ . This may have also contributed to an increased device yield to ~80% (16 of 20 devices) due to the absence of damage from the probe tip to the graphene electrodes as discussed before. The  $SiO_x$  memory here features low programming current levels (~0.1 mA, Fig. 3b), more than one order of magnitude lower than those in other transparent resistive memory systems<sup>11–13,30</sup>. Consequently, despite a working voltage up to 15 V, the devices still feature an approximately tenfold reduction in the power-consumption factor (the product of current and voltage) during programming compared with those in other transparent resistive memories<sup>11–13</sup>. The reduced programming currents lower the current densities in the interconnects, providing more area for the transparent interconnects for a transparent circuit.

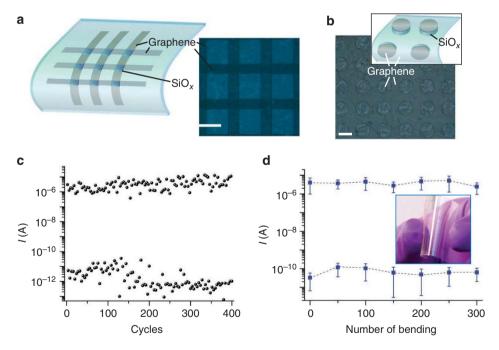

The versatile transfer process of graphene to various substrates  $^{21}$  also enables the fabrication of the memory devices on plastic transparent films. We fabricated  $G/SiO_x/G$  devices using both crossbar and pillar structures on a plastic (fluoropolymer, PFA) substrate (Fig. 4a,b). Here a fluoropolymer was chosen as the plastic substrate for its comparatively high-melting point (>280 °C) in order to sustain the current local heating involved during the initial electroforming process in the  $G/SiO_x/G$  devices. The electroformed devices

showed the same memory switching characteristics (Fig. 4c and Supplementary Fig. S6a) as those from devices on rigid substrates. Similar device yields of ~70% were achieved in the crossbar structures (Fig. 4a). The yield was comparatively low (~20%) for the pillar structures (Fig. 4b); the lowered yield in the pillar structure was largely due to the direct contacting between the probe tip and the memory unit during electrical characterization. Unlike the rigid substrate, the flexibility in the plastic substrate made control of the contacting pressure between the probe tip and device surface difficult, and probe-tip-induced local curvature of the device likely resulted in damage to the  $\mathrm{SiO}_{x}$  layer and, hence, the decreased yield. Both structures showed no memory-state degradation on bending the flexible plastic substrate (Fig. 4d and Supplementary Fig. S6b), demonstrating the feasibility of both transparent and flexible memory applications.

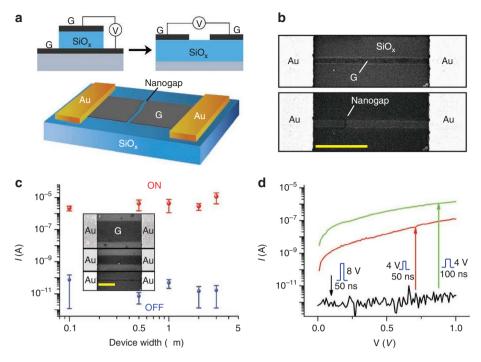

**Planar G–SiO**<sub>x</sub>–**G nanogap devices**. Although the transparent memory devices demonstrated above all use the common vertical sandwiched structures, they can also be made in the planar configuration. Topologically, the vertical G–SiO

<sub>x</sub>–G structure is equivalent to the planar G–SiO

<sub>x</sub>–G nanogap system (Fig. 5a). For the demonstration, we transferred graphene onto a silicon substrate capped with 500-nm-thick SiO

<sub>2</sub>. The graphene layer was patterned with electron-beam lithography and then etched into stripes and then contacted by electrodes (2 nm Ti/30 nm Au) with a channel length ~2  $\mu$ m (top panel, Fig. 5b). Electrical breakdown was induced (Supplementary Fig. S7a) in the graphene stripe to generate a narrow disruption region or nanogap (bottom panel, Fig. 5b). The size of the nanogap is usually 10–60 nm, close to the thickness of SiO

<sub>x</sub> layer used in the vertical G/SiO

<sub>x</sub>/G devices. The electroforming of SiO

<sub>x</sub> in the nanogap (Supplementary Fig. S7b) region usually occurs

Figure 3 | Memory effect in a  $G/SiO_x/G$  crossbar structure. (a) Optical image of the  $4\times4$   $G/SiO_x/G$  crossbar structure (right panel), with the illustration showing the perspective view of the memory unit. Scale bar,  $20 \,\mu\text{m}$ . (b) Characteristic I-V curves from an electroformed crossbar memory unit. (c)  $100 \, \text{memory}$  cycles from the device using  $+5 \, \text{and} +15 \, \text{V}$  as set and reset voltages, respectively. The programming current is not shown here and the memory states (current) were recorded at  $+1 \, \text{V}$ .

Figure 4 | Flexible transparent memory devices. (a) (Left panel) Schematic of the  $G/SiO_x/G$  crossbar structures on a plastic (fluoropolymer) substrate and (right panel) the optical image of the structures. Scale bar,  $20\,\mu\text{m}$ . (b) Optical image of the  $G/SiO_x/G$  pillar structures with the inset showing the schematic image. Scale bar,  $100\,\mu\text{m}$ . (c) Memory cycles from one of the crossbar devices using +5 and  $+14\,\text{V}$  as set and reset voltages, respectively. The programming current is not shown here and the memory states (current) were recorded at  $+1\,\text{V}$ . (d) Retention of both ON and OFF memory states (read at  $+1\,\text{V}$ ) from a crossbar device is shown on bending the plastic substrate around a -1.2-cm diameter curvature; the central devices on the sheet being tested throughout the bending cycles. The inset shows the actual transparent memory devices using the pillar structures on the plastic substrate.

immediately after the breakdown event in the graphene stripe, most likely due to the existence of local confinement so that high field is easily attained locally. It features a reduced electroforming

voltage compared with the typical value obtained from the pristine vertical structure (Supplementary Fig. S2). This material-assisted local-field enhancement offers another route to bring down the

**Figure 5 | Device scaling and switching speed.** (a) Schematics of the topological equivalence between a vertical  $G/SiO_x/G$  structure and a planer nanogap system. The bottom panel is a perspective view of the planar structure. (b) (Top panel) Scanning electron microscopy (SEM) image of the as-made graphene stripe device before electrical characterization. (Bottom panel) SEM image of the same device after electrical breakdown in the graphene stripe, showing a voltage-induced disruption region or nanogap; scale bar,  $1\mu m$ . (c) ON and OFF currents with respect to different lateral constrictions (widths) in the  $G/SiO_x/G$  planar nanogap switching systems. The memory states were read by +1V voltage. The inset shows a series of devices with different widths in the graphene stripes; scale bar,  $1\mu m$ . (d) Switching-speed test from one of the  $G/SiO_x/G$  devices. The arrows indicate the directions of the memory-state transitions. The rising edge and falling edge of the pulses were 10 ns.

electroforming voltage apart from thermal annealing  $^{17}$ . As a result, a thin layer of conducting molecules or carbon materials could be coated over the  $\mathrm{SiO}_x$  surface region to induce local-field enhancement for reduction of the electroforming voltage  $^{20}$ . The switching properties obtained in this planar nanogap configuration are similar to those from vertical structures, confirming the same switching mechanism intrinsic to  $\mathrm{SiO}_x^{18}$ . Note that more detailed discussions about this intrinsic  $\mathrm{SiO}_x$  switching mechanism are covered in our previous studies  $^{17-20}$ .

### **Discussion**

This planar  $G\text{-}SiO_x\text{-}G$  structure offers an easy way to study the current-scaling property by varying the widths of the graphene stripes. As shown in Fig. 5c, both the ON and OFF currents stayed at the same level when reducing the width from 3  $\mu$ m to 100 nm. And these current levels are similar to those obtained in vertical structures having dimensions  $\geq 10 \, \mu$ m. This non-scaling feature in the current indicates that the memory switching is through a highly localized filament. Indeed, the metallic silicon filament was revealed to be sub-10 nm in size<sup>17,18</sup>, being a possible harbinger of aggressive device scaling. This confined nanoscale switching along with the intrinsic transparency shows the possibility of high-density transparent memory applications.

We further performed a switching-speed test in the  $G/SiO_x/G$  devices by using a voltage-pulse generator (Agilent, B1525A). For the three  $G/SiO_x/G$  devices tested, they all could be reset by a 50-ns 8 V pulse (black curve, Fig. 5d). The set process was found to be in the range of 50–500 ns, showing variations between devices and individual switching events in the same device. The switching speed differences indicate structural and, hence, switching dynamics variations in the silicon filaments. Figure 5d shows the typical trend that a shorter (50 ns, 4 V) pulse can partially set the device (red curve),

whereas a longer one (100 ns, 4 V) fully sets the device into the ON state (green curve). Note that our recent in situ imaging study<sup>18</sup> revealed that the switching is due to the transition between the metallic form and amorphous form in the silicon filament, with the set and reset processes largely being field driven and thermal driven, respectively. Our test indicates that the reset process (amorphization of silicon by a thermal process<sup>18</sup>) is generally faster than the set process (crystallization of the silicon by a field process<sup>18</sup>). This trend is analogous to that in phase-change materials, in that the set process generally requires longer programming time<sup>31</sup>. The partially set process (or intermediate state) by shorter pulse indicates a continuous structural evolution instead of a threshold change in the filament during the set (crystallization) process. It further bespeaks of the possibility for multi-states on a singular device. Note that Fig. 1b (blue curve) indicates that a backward voltage sweep ( $V_{\text{reset}} \rightarrow 0 \text{ V}$ ) at a slow rate (~3 V s<sup>-1</sup>) sets the device ON, as it bypasses the set region. As the falling edge in a reset pulse is analogous to a backward sweep (Supplementary Fig. S8), the fast set process observed here indicates that a fast-falling edge is necessary for the reset process (Supplementary Discussion).

In summary, we have demonstrated transparent nonvolatile memory devices based on  $SiO_x$  and graphene, which feature high transparency, long retention time and low programming currents. The underlying mechanism is a memory switching intrinsic to  $SiO_x^{17,18}$ , so that it is not limited to the choice of electrode materials. Graphene offers advantage of transparency, flexibility and potential low cost. The process of self-limiting nanogap generation in the graphene layer in the planar  $G-SiO_x-G$  memory system is an advantage of graphene that otherwise may not be assumed by other transparent materials. Given the unique role of  $SiO_x$  in the semiconductor industry and the promising future of graphene as a transparent electrode material, the  $SiO_x$ -graphene memory system

demonstrated here features its advantages in both transparent materials composition and processing.

#### **Methods**

**Material preparation**. The graphene films were synthesized directly on 25 μm thick copper foils (Alfa Aesar, 99.8%) via the chemical vapour deposition method  $^{24}$ . The process began with the thermal annealing of the copper foil at 1,035 °C under  $\rm H_2$  flow (500 sccm) for 20 min for grain coarsening. Then at the stabilized temperature of 1,035 °C and pressure of 10 Torr, CH<sub>4</sub> precursor gas (4 sccm) was introduced into the growth tube for graphene growth (40 min). After that, the CH<sub>4</sub> flow was turned off and the furnace was cooled down to room temperature. Protected with poly(methyl methacrylate), the graphene-coated copper film was then etched in a Fe(NO<sub>3</sub>)<sub>3</sub> solution (0.5 M), followed by thoroughly cleaning in a 5% HNO<sub>3</sub> solution and deionized (DI) water.

**Fabrication of G/SiO**<sub>x</sub>/**ITO pillar structure**. The schematic of the fabrication is presented in Supplementary Fig. S1. A glass substrate coated with an ITO layer (120 nm, ~100  $\Omega$  sq  $^{-1}$ ) was used as the starting substrate. A layer of SiO<sub>x</sub> (~70 nm thick) was deposited by electron-beam evaporation. Then monolayer graphene film was transferred (twice for bilayer) on to the SiO<sub>x</sub>/ITO/glass substrate to form the graphene top electrode. For the definition of the circular patterns, photolithography was used to define circular resist (Microposit S1813) patterns (diameters ~100 μm) as the sacrificial mask. Reactive ion etching (RIE, using CHF<sub>3</sub>/O<sub>2</sub>) was then used to vertically etch the graphene and SiO<sub>x</sub> layer at the region unprotected by the resist. The resist mask was then removed by acetone. Note that an etched vertical SiO<sub>x</sub> (red arrow, Supplementary Fig. S1) is necessary for the electroforming process and the subsequent memory switching, as the etched surface is expected to be more defected compared with the rest bulk region in the SiO<sub>x</sub> layer and, hence, provides the localized region for the self-limiting process of silicon filament formation <sup>17</sup>.

Fabrication of G/SiO<sub>x</sub>/G pillar structure. The schematic of the fabrication is presented in Supplementary Fig. S5. To form the layered structure of G/SiO<sub>x</sub>/G, a bilayer graphene film (using layer-by-layer transferred technique) was first transferred onto the glass substrate. A layer of  $SiO_x$  film with the thickness of 70 nm was deposited by electron-beam evaporation. The top bilayer graphene film was then transferred on to the SiO<sub>x</sub> layer. Circular resist patterns (diameters  $\sim$ 100  $\mu$ m) were then defined by photolithography as described above. Oxygen plasma was used to etch the top graphene film at the region unprotected by the resist mask. RIE (CHF<sub>3</sub>/O<sub>2</sub>) was then used to partially etch the SiO<sub>r</sub> layer followed by further  $SiO_x$  etching by buffered oxide etch (10:1). The reason for adopting the two-step SiO<sub>x</sub> etching is to protect the bottom graphene electrodes from RIE etching while still define the vertical SiO<sub>x</sub> edge that facilitates the electroforming <sup>17</sup>. The resist was then removed with acetone. The fabrication of G/SiO<sub>x</sub>/G pillar structures on the plastic substrate followed the similar procedure. In addition, the fluoropolymer (operational temperature larger than 280 °C; purchased from McMaster) plastic substrate was treated with oxygen plasma for 90 s to increase its wettability to acetone, before the transfer of the bottom bilayer graphene films. After the oxygen plasma treatment, the measured contact angle with acetone decreases from 69.3° to 25.7°. For easier handling of the plastic substrate, it was fixed on a silicon substrate during the fabrication process.

**Fabrication of G/SiO<sub>x</sub>/G crossbar structure**. The G/SiO<sub>x</sub>/G crossbar structure was fabricated on a silicon substrate ( $\rho$ >5,000  $\Omega$  cm) and plastic substrate (fluoropolymer). The bottom bilayer graphene was first transferred on to the silicon substrate or plastic substrates. Transferring bottom graphene to plastic substrates follows the same procedure for the fabrication of G/SiO<sub>x</sub>/G pillar structures on fluoropolymer. Photolithography was used to define the resist mask, and then oxygen plasma was used to etch and define the bottom graphene lines as shown in Fig. 3a. Metal electrode (Au/Ti = 20 nm/2 nm, 100×100 μm<sup>2</sup>) was patterned at the end of each graphene line by photolithography, electron-beam evaporation and lift-off processes, serving as the bottom electrical contact for the probe tip. A layer of SiO<sub>x</sub> film (~70 nm) was then deposited by electron-beam evaporation. The top bilayer graphene film was then transferred onto the  $SiO_x$  layer. Photolithography was used to define the sacrificial layer for the top graphene lines, followed by the two-step SiO<sub>x</sub> etching method described before. Finally, top-metal electrode (Au/Ti = 30 nm/5 nm, 100×100 µm<sup>2</sup>) was also patterned at the end of each top graphene line to form electrical contact for the upper probe tip.

#### References

- 1. Thomas, G. Invisible circuits. Nature 389, 907-908 (1997).

- 2. Wager, J. F. Transparent electronics. Science 300, 1245-1246 (2003).

- Nomura, K. et al. Thin-film transistor fabricated in single-crystalline transparent oxide semiconductor. Science 300, 1269–1272 (2003).

- Nomura, K. et al. Room-temperature fabrication of transparent flexible thinfilm transistors using amorphous oxide semiconductors. Nature 432, 488–492 (2004).

- Ju, S. et al. Fabrication of fully transparent nanowire transistors for transparent and flexible electronics. Nat. Nanotech. 2, 378–384 (2007).

- Artukovic, E. et al. Transparent and flexible carbon nanotube transistors. Nano Lett. 5, 757–760 (2005).

- Suresh, A. et al. Transparent indium gallium zinc oxide transistor based floating gate memory with platinum nanoparticles in the gate dielectric. Appl. Phys. Lett. 94, 123501 (2009).

- Yoon, S.- M. et al. Fully transparent non-volatile memory thin-film transistors using an organic ferroelectric and oxide semiconductor below 200 °C. Adv. Funct. Mater. 20, 921–926 (2010).

- Yu, W. J. et al. Ultra-transparent, flexible single-walled carbon nanotube non-volatile memory device with an oxygen-decorated graphene electrode. Adv. Mater. 23, 1889–1893 (2011).

- Waser, R. & Aono, M. Nanoionics-based resistive switching memories. Nat. Mater. 6, 833–840 (2007).

- Seo, J. W. et al. Transparent resistive random access memory and its characteristics for nonvolatile resistive switching. Appl. Phys. Lett. 93, 223505 (2008).

- Zeng, K. et al. An indium-free transparent resistive switching random access memory. IEEE Electron Dev. Lett. 32, 797–799 (2011).

- 13. Lee, L. & Kim, O. Nonvolatile resistive memory device based on poly(3,4-ethylenedioxythiophene): poly(styrene sulfonate) thin film for transparent and flexible applications. *Jpn. J. Appl. Phys.* **50**, 06GF01 (2011).

- Geim, A. K. & Novoselov, K. S. The rise of graphene. *Nat. Mater.* 6, 183–191 (2007).

- Schindler, C., Weides, M., Kozicki, M. N. & Waser, R. Low current resistive switching in Cu-SiO<sub>2</sub> cells. Appl. Phys. Lett. 92, 122910 (2008).

- Sawa, A. Resistive switching in transition metal oxides. *Mater. Today* 6, 28–36 (2008).

- Yao, J., Sun, Z., Zhong, L., Natelson, D. & Tour, J. M. Resistive switches and memories from silicon oxide. *Nano Lett.* 10, 4105–4110 (2010).

- Yao, J., Zhong, L., Natelson, D. & Tour, J. M. In situ imaging of the conducting filament in a silicon oxide switch. Sci. Rept. 2, 242 (2012).

- 19. Yao, J. et al. Resistive switching in nanogap systems on  ${\rm SiO_2}$  substrates. Small 5, 2910–2915 (2009).

- Yao, J., Zhong, L., Natelson, D. & Tour, J. M. Silicon oxide: a non-innocent surface for molecular electronics and nanoelectronics studies. *J. Am. Chem.* Soc. 133, 941–948 (2011).

- Sukang, B. et al. Roll-to-roll production of 30-inch graphene films for transparent electrodes. Nat. Nanotech. 5, 574–578 (2010).

- Sun, Z. et al. Growth of graphene from solid carbon source. Nature 468, 549–552 (2010).

- Yao, J., Zhong, L., Natelson, D. & Tour, J. M. Intrinsic resistive switching and memory effects in silicon oxide. *Appl. Phys. A* 102, 835–839 (2011).

- Li, X. et al. Large-area synthesis of high-quality and uniform graphene films on copper foils. Science 324, 1312–1314 (2009).

- Soo, K. K. et al. Large-scale pattern growth of graphene films for stretchable transparent electrodes. Nature 457, 706–710 (2009).

- 26. Ruan, G. et al. Growth of graphene from food, insects, and waste. ACS Nano 5, 7601–7607 (2011).

- Jeong, H. Y. et al. Graphene oxide thin films for flexible nonvolatile memory applications. Nano Lett. 10, 4381–4386 (2010).

- Gang, L. et al. Bistable electrical switching and electronic memory effect in a solution-processable graphene oxide-donor polymer complex. Appl. Phys. Lett. 95, 253301 (2009).

- Nair, R. R. et al. Fine structure constant defines visual transparency of graphene. Science 320, 1308 (2008).

- Kim, H.- D., An, H.- M., Seo, Y. & Kim, T. G. Transparent resistive switching memory using ITO/AlN/ITO capacitors. *IEEE Electron Dev. Lett.* 32, 1125–1127 (2011).

- Hudgens, S. & Johnson, B. Overview of phase-change chalcogenide nonvolatile memory technology. MRS Bull. 29, 829–832 (2004).

#### **Acknowledgements**

D.N. acknowledges the support of the David and Lucille Packard Foundation.

L.Z. acknowledges support from the Texas Instruments Leadership University Fund and National Science Foundation Award No. 0720825. J.M.T. acknowledges support from the Army Research Office through the SBIR program administrated by PrivaTran, LLC.

# **Author contributions**

J.Y. conceived the project and he and J.L. performed the experiments and analyses and they wrote the paper. Y.D. performed experiments on the crossbar structure on glass, though optimized by J.L. and further performed by him for plastic. G.R., Z.Y. and L.L. contributed to the graphene growth. D.N., L.Z. and J.M.T oversaw the project and revised the manuscript. J.M.T. led the effort to completion.

## **Additional information**

**Supplementary Information** accompanies this paper at http://www.nature.com/naturecommunications

Competing financial interests: J.Y., D.N., L.Z. and J.M.T. are inventors of  $SiO_{X}$ -switching intellectual property that is Rice University-owned, and J.Y. and J.M.T. are inventors of similar transparent-based intellectual property, again the property

being Rice University-owned. J.L., Y.D., G.R., Z.Y. and L.L. have no competing financial interests

$\textbf{Reprints and permission} \ information \ is \ available \ online \ at \ http://npg.nature.com/reprints and permissions/$

How to cite this article: Yao, J. et al. Highly transparent nonvolatile resistive memory devices from silicon oxide and graphene. *Nat. Commun.* 3:1101 doi: 10.1038/ncomms2110 (2012).