INSTITUT NATIONAL DE RECHERCHE EN INFORMATIQUE ET EN AUTOMATIQUE

## HIPPCO: A High Performance Protocol Code Optimizer

Claude Castelluccia, Walid Dabbous

N° 2748

Décembre 1995

\_\_\_\_\_ PROGRAMME 1 \_\_\_\_\_

## HIPPCO: A High Performance Protocol Code Optimizer

Claude Castelluccia, Walid Dabbous

Programme 1 — Architectures parallèles, bases de données, réseaux et systèmes distribués

Projet RODEO

Rapport de recherche n°2748 — Décembre 1995 — 76 pages

**Abstract:** This report presents HIPPCO, an High Performance Protocol Code Optimizer. HIPPCO belongs to the HIPPARCH compiler. HIPPARCH is a tool which proposes to generate automatically from the application communication requirements and the network characteristics an efficient implementation of a customized protocol.

HIPPCO is the last stage of this protocol compiler. It takes as input a description of the protocol automaton, optimizes it and generates an implementation in C.

HIPPCO decomposes the protocol automaton in two parts: the common and uncommon path. It then uses this decomposition to apply a set of optimizations toward a good code speed/code size tradeoff.

In the first part of this report, the code speed optimizations are described. Those optimizations reduces the number of executed instructions and improves the instruction cache and pipeline behaviors. In the second part, a comparaison of HIPPCO automatically generated implementations of TCP are compared with the BSD implementation. We show that the HIPPCO generated codes requires up to 70% less instructions than its BSD counterpart.

Key-words: Code optimization, Automated Protocol Generation, ALF

$(R\acute{e}sum\acute{e}:tsvp)$

# HIPPCO: Un optimiseur haute performance de code de protocole

Résumé: Ce rapport décrit l'architecture de HIPPCO, un optimiseur et générateur d'implémentation de protocoles de communication. HIPPCO fait parti du compilateur de protocoles HIPPARCH. Ce compilateur propose de génèrer automatiquement, à partir des besoins de communication d'une application distribuée et des caractéristiques du réseau sous-jacent, le protocole spécialisé correspondant.

HIPPCO est la dernière passe du compilateur HIPPARCH. Il génère à partir de la description de l'automate du protocole, une implémentation optimisée en C.

HIPPCO décompose l'automate de communication en deux parties distinctes: le chemin fréquent et le chemin rare. Utilisant cette décomposition, un ensemble d'optimisations est appliqué pour obtenir le meilleur compromis entre la vitesse d'exécution et la taille du code.

Ce rapport est structuré en 2 parties: La première détaille les différentes optimisations utilisées pour l'amélioration de la vitesse d'exécution du code. Ces optimisations sont basées sur une réduction du nombre d'instructions à exécuter, sur une meilleure utilisation du cache d'instruction et du pipelining.

Dans le seconde partie, une implémentation automatique du protocole TCP est detaillée. Les performances de cette implémentation sont comparées avec celles de la version BSD de TCP.

Mots-clé: Optimisation de code, Génération automatique de protocoles, ALF

## 1 Introduction

The emergence of new distributed computing applications and of new networking technologies is driving the need of more specialized communication protocols. Generating and implementing those new protocols manually in an efficient way is very often a complex and time-consuming task.

One option, that has been extensively studied in the last few years, is to automate or semi-automate the protocol design and implementation phases. This is usually performed by selecting a set of predefined modules, which generally implement the basic protocol mechanisms, and combining them into the final communication system using configuration tools like ADAPTIVE or x-kernel [BSS92, NL88, OP91]. This approach has the advantage over the manual approach to generate a modular and configurable system.<sup>1</sup>

However, this approach has not encountered yet the success that was expected. The main reason is that the modularity of those systems introduces a performance penalty on the generated protocol implementation. In fact, those configuration tools very often derive the implementation directly and naively from the specification. As a result, the generated protocol implementation is composed of several modules that communicate and interact via some kind of interfaces. These module interaction mechanisms are usually very costly and are the source of performance penalties that overtake the gain achieved by the configuration.

Another limitation of these configuration tools is that they generally use a bottom-up approach: i.e. they configure a communication system based on the mechanisms provided by current "transport protocol". The granularity of those tools is then very often coarse.

In the HIPPARCH project, we propose to build a protocol compiler which automatically generates the communication system of a distributed application. This approach is interesting only if the generated implementations are performant. The efficiency of the implementations was therefore one of our main goals. To reach this objective, the HIPPARCH compiler has been built around the following properties:

• Synchrony: The HIPPARCH compiler is built around a synchronous language, Esterel. Esterel generates from a set of concurrent modules an integrated automaton. In this automaton, all the specification building blocks are merged together and communicate directly without interfaces.

<sup>&</sup>lt;sup>1</sup>A system is said to be *modular* if it is composed by a number of functional entities called modules which interact together. A system is said to be *configurable* or *flexible* if it is relatively easy to add or remove a functionality without modifying the whole system.

- Configurability: The HIPPARCH compiler selects the protocol mechanisms according to the application requirements and networks characteristics. The HIPPARCH approach is application-led (top-down): the communication requirements of several applications (such as JPEG photo server [C. 95], secure login, multicast video and audio, WWW transactions, multimedia multicast mail delivery, large scale multicast image dissemination [A. 95]) have been studied and analyzed. The compiler should generate the complete communication system for such applications.

- **HIPPCO:** The HIPPARCH compiler features a *code optimizer*, called HIPPCO, which optimizes the structure of the automaton and generates highly optimized code in C. HIPPCO uses profiling information provided by the protocol designer to dynamically identify the *common path* and apply a set of optimizations. Those optimizations are specific to the automaton structure and are not redundant with optimizations that may be performed by existing low-level compilers. The goal of HIPPCO is to generate protocol code that can efficiently be compiled and optimized by current C compilers. It optimizes a program execution time by reducing the number of instructions on its common path and generating code that exhibits good cache and pipeline behaviors.

In this report, we describe the design of HIPPCO and present some performance results of TCP automatically generated implementations. We show that automatically generated protocol code can be faster than the best optimized hand-coded implementations. This report is composed of 6 main sections. Section 2 introduces the HIPPARCH project and gives some insights on the Esterel language. Section 3 presents HIPPCO concepts and describes its optimization principles. Section 4 details the design of HIPPCO. In this section, we present the various optimizations that are performed by HIPPCO. Section 5 evaluates the performance of HIPPCO automatically generated codes. We compare the instruction counts, i-cache and pipeline performance of some HIPPCO generated TCP implementations with the BSD implementation. We also evaluate the individual effects of each proposed optimization. We, finally, conclude in section 6.

## 2 Context: The HIPPARCH Protocol Compiler

## 2.1 General Presentation

The work presented in this report was done in the context of the HIPPARCH project [CCD<sup>+</sup>94]: an European-Australian collaboration action which proposes to study

a novel architecture for communication protocols based on the Application Level Framing (ALF) and Integrated Layer Processing (ILP) concepts [Cla90]. Its final objective is to build a compiler which generates the communication system of a distributed application. This tool uses application-specific knowledge to configure this communication system for improved performance [Cas94a].

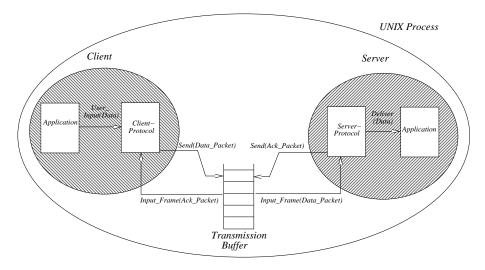

The HIPPARCH compiler is composed of 2 tools: the ALF and ILP compiler. The ALF compiler generates from the application requirements and the networks characteristics an automaton representing the control part. This control part contains the application and protocol control parts. The idea of HIPPARCH is to integrate the application and its communication subsystem within a single automaton. This integration removes a lot of interfaces and leads to more performant systems. In this report, for simplicity reason, we separate the control part of the application from the control part of the communication subsystem. This allows us to generate existing protocols and compare their performance to their manually implemented counterparts. The ILP compiler is a stub compiler, which combines the data manipulations functions in an ILP manner.

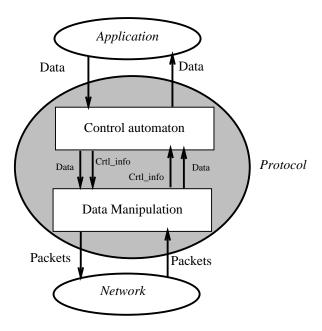

The control automaton and the data manipulation functions are combined together to form the complete protocol implementation as illustrated in figure 1. Whenever the application sends a piece of data to a remote correspondant, it calls the protocol output procedures which process the control part of the protocol. The protocol control variables (sequence number, timers, transmission window,...) are then updated and the data manipulation functions are called with the data and some control information as arguments. This control information depends on the generated protocol. It may be composed of some fields of the protocol control block that are used to build the protocol header or to process some of the manipulation functions. After the data manipulation operations (checksum, encryption, marshalling, ....) are performed, packets are built and sent on the network. At the other side, when a packet is received, it is first marshalled, decrypted ans checksummed. The processed information (data and control information) is then handed to the control automaton. The protocol control variables will then be updated, a packet possibly sent, and data is delivered to the application.

Separating the data manipulation functions from the control flow processing has the advantage of isolating the problems and simplifying the overall compiler design. It also allows to consider each part independently and apply more specific optimizations. In this report, we do not consider the ILP compiler (i.e. how the data manipulation functions are implemented). We describe the HIPPCO tool which optimizes the control automaton, and therefore is a part of the ALF compiler.

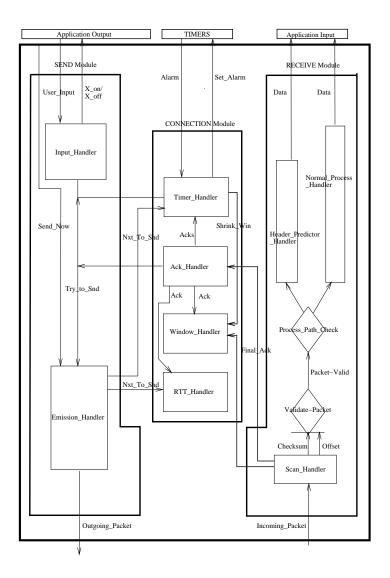

Figure 1: Protocol Structure

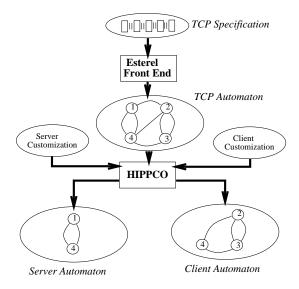

The ALF compiler is designed around a synchronous language, Esterel ([Ber89], [Ber92]). It is composed of 4 main parts (figure 2-a):

- a library of predefined modules in Esterel. It is a collection of various protocol building blocks.

- a parser which combines the application specification written in Esterel with selected library modules, to generate an Esterel specification of the communication stack and some profiling information.

- an Esterel Front-End: compiles the Esterel specification into an integrated automaton.

- HIPPCO: optimizes the generated automaton and generates an efficient implementation in a target language (C in HIPPARCH).

Although HIPPCO is developed in the context of the HIPPARCH project, it was designed independently of the other HIPPARCH compiler tools. HIPPCO takes as input any automaton description in a standard language called Oc and generates an implementation in the C language. Therefore HIPPCO can in principle

be used to optimize the output of any tool generating  $\mathbb{O}$ c automata, independently of the high-level specification language. To illustrate this, we describe in figure 2-b, an alternative way to use HIPPCO. The proposed architecture optimizes existing communication system implementations provided that an integrated automaton generator exists. This automata generator takes as input the different C protocol implementations of a communication stack, and generate an integrated automaton in the  $\mathbb{O}$ c language, which is feeded into HIPPCO to produce an integrated and optimized implementation of the communication system.

Figure 2: Protocol Compiler Architectures

In the HIPPARCH compiler, HIPPCO takes as input an automaton description generated by the Esterel compiler. In the following, we introduce the Esterel language and describe the generated automaton format.

## 2.2 Esterel

## 2.2.1 The Esterel Language

Programs can basically be divided into three classes: (1)transformational programs that compute results from a given set of inputs, (2) interactive programs which interact at their own speed with users or other programs and (3) reactive programs that interact with the environment, at a speed determined by the environment, not by the program itself.

Synchronous languages were specifically designed to implement reactive systems. The Esterel language is one example [BdS91, BG89]; others include languages such as Lustre [], Signal [], Sml [] and Statecharts [].

Protocols are good examples of reactive systems; they can be seen as *black boxes*, activated by input events (such as incoming packets) and reacting by producing output events (such as outgoing packets). Other systems e.g. window servers such as X, NeWs and MS Windows, can be considered as reactive systems and may be specified using synchronous languages.

The Esterel language was chosen as the specification language within the HIP-PARCH project [].

Esterel programs are composed of parallel modules, which communicate and synchronize using signals. The output signal of a module is broadcast within the whole program and can be tested for presence and value by any other module. This communication mechanism provides a lot of design flexibility, because modules can be added, removed or exchanged without perturbing the overall system. A module is defined by its inputs (the signals that activate it, they can potentially be modified by the module), sensors (input signals used only for consultation, they can not be modified) and outputs (signals emitted). The inputs of a module can either be the outputs of another one (modules executed sequentially) or external signals (such as incoming packets). The design of an Esterel program is then performed by combining and synchronizing the different elementary modules using their input, sensor and output signals.

Synchronous languages are used to implement the control part of a program, the computational and data manipulation parts are performed by functions implemented in another language (C for example). Data declarations are encapsulated, so that only the visible interface declarations are provided in Esterel (i.e. type, constant, function and procedure names). These declarations can then be freely implemented independently of the Esterel program design. They will be linked with the automaton generated in the last phase, when executable code is produced.

Esterel makes the assumption of perfect synchrony: program reactions can not overlap. There is no possibility of activating a system while it is still reacting to the current activation. This assumption makes Esterel programs deterministic, since their behaviors are reproducible; the generated automaton can then be tested for correctness using validation tools [RdS90].

At compile time, the Esterel program is translated into a sequential finite automaton; the code of the different modules is sequentialized according the program concurrency and synchronization specifications.

However the synchronous approach cannot be considered as a stand-alone solution, principally because the synchronous assumption is not a valid one in the real implementation world. A so-called *Execution Machine* is required [AMP91]. This machine is aimed at interfacing the asynchronous environment to the synchronous automaton. It collects the inputs and outputs and activates the automaton only when it is not executing; the "synchronous assumption" is then respected.

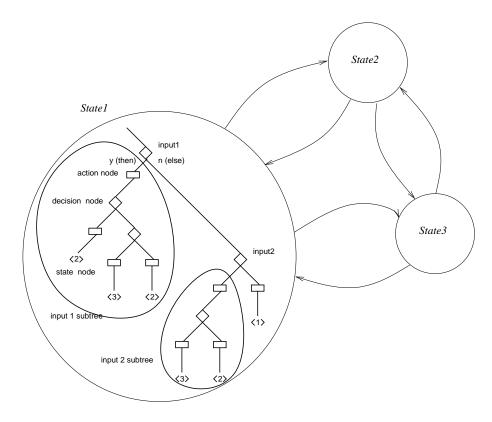

## 2.2.2 The Esterel Tree Representation

The Esterel front-end generates from the specification an automaton in a standard language called Oc. The generated automaton is usually composed of several states. Each of those states are described by a state-tree (figure 3). Trees, unlike graphs, do not contain any loop. This property facilitates dependency analysis and simplifies optimizations design and implementation. As we will show later in this report, trees can be easily modified for better performance. However the tree representation generally leads to large code size. In fact in a tree representation, lots of actions are duplicated in the different branches. A graph representation usually leads to a smaller code size.

Each state-tree is composed of initialization actions followed by independent subtrees processing the different types of input events. A test at the root of each subtree determines whether the incoming event should be processed by this subtree. If that is the case, the backward branch (then branch) is executed, otherwise the subtree exits. The state-tree is generated by cascading those different subtree's roots as shown in figure 3. An incoming event will then be processed by a sequence of tests until the appropriate subtree is found.

We define a set of notations that will be used throughout the whole report. They are illustrated by the figure 3. A state-tree is composed of a collection of cascaded nodes. There are three types of nodes: decision\_nodes, state\_nodes and action\_nodes:

Figure 3: The Tree Structure

- In Esterel, a decision\_node is composed of three elements: test, then and else. The test is the predicate to test. then is a pointer on the node to execute if the test is correct. else is a pointer on the node to execute if the test is uncorrect. We added two more elements: per and CP. These two elements will be used by HIPPCO. Per is an integer which indicates the execution probability of the then branch. CP is a flag, used by the common path identification algorithm.

- A state\_node is composed of one element nstate, an integer that indicates the number of the next state the automaton is going to. The state\_nodes are the leaves of tree, but as we will see later in this report, every leaves are not state\_nodes. In fact, some leaves may be references to other trees.

• An action\_node is a node that performs an action or a set of actions, such as variable assignements and/or function calls. It is composed of two elements: the action itself (elt\_action) and a pointer on the following node to execute (nnext).

We adopt the following conventions in the tree figures. Decision nodes will be drawn as diamonds. The backward branch of a decision node (the then branch) is its left branch. Action nodes will be drawn as rectangles. State nodes will be drawn as two brackets containing the value of the nstate variable (<>). After code size optimisations, some trees are ponting on others trees. A reference to a tree labeled n is coded as [n]. In this report, some of these details will be omitted if this does not affect the figure clarity.

## 3 HIPPCO: High Performance Protocol Code Optimizer

## 3.1 Presentation and General Concepts

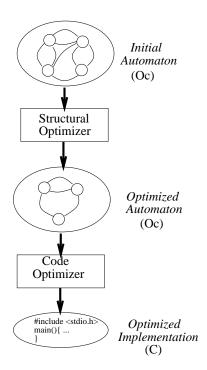

The optimizer operates in two phases (see figure 4): the first stage, the structural optimizer, modifies the structure of the internal automaton, reschedules the different actions according to the optimization constraints and generates an optimized automaton customized to the application that is being designed. The second stage, the code optimizer generates, from this automaton representation, the final code.

The structural or automaton optimizer is independent of the final target language. It takes as input the automaton representation in Oc and generates an other automaton in Oc. The code optimizer is independent of the automaton optimizer, it takes as input an automaton description (optimized or not) and generates code in a target language (such as C). The optimization performed by those two stages are quite different. The first stage generates optimizations that modify the software structure: optimizations like header prediction [Jac88] should be taken into account at this stage. The code optimizer applies code optimization techniques that are more language-specific such as inlining. Separating these two kinds of optimizations into two different stages has the advantage of isolating them and therefore leads to more efficient algorithms.

HIPPCO design follows four basic concepts:

Figure 4: HIPPCO Architecture

• Complementary to low-level compiler optimizations: Existing low-level compilers <sup>2</sup> perform a lot of optimization techniques. Those optimizations transform the code to generate faster code without information on the semantic of the application. They are applied either as a result of a static analysis of the program or systematically, such as inlining very small functions.

The HIPPCO optimizations uses profiling information provided by the application designer. It can therefore perform more aggressive and specific optimizations. However some optimizations are more efficient when they are performed at the low-level, such as *Basic Block Rescheduling* ([McF89]) for better cache utilization. As a consequence, the approach that we followed in the design of HIPPCO was to implement optimizations that are not redundant with the ones present in the low-level compiler but that are complementary. HIPPCO was not designed to replace the existing low-level optimizers, but to help them. In

$<sup>^2</sup>$  We call low level compiler, a compiler that generates executable code from a high level language such as the C compiler.

HIPPCO, we transform the code in order to make the low-level optimizations more efficient. For example, when the *Common Branches Extension* algorithm is applied (see section 4.2.3), it generates code on the common path that is straightline. This code is faster because of the suppression of the function call overheads but also because the streamlined structure of the common path gives to the low-level compiler more optimization opportunities.

- Synchrony: Most of languages and code generators currently used for protocol specification and design, such as SDL or Estelle, are asynchronous ([Hof93], [Leu94]): modules are specified and implemented as separate processes communicating via asynchronous queues. We believe that the synchronous approach is more attractive for the generation of high performance implementation: synchronous languages compile parallel or sequential specification modules into a single automaton using the language semantic, the data and control dependencies. This automaton can be implemented by a single process, removing inter-module communication overhead. This approach has in addition the advantage of facilitating the verification of the generated code [RdS90].

- Configurability: A possible way to enhance a communication system performance is to reduce the protocol functionalities (i.e. the number of protocol operations) to the minimum required by the application. This leads to a communication system configured to meet the application needs. In HIPPCO, profiling information provided by application designer are used to generate a configured version of this system.

- Common/Uncommon path separation: Another way to enhance the performance is to reduce the amount of processing per operation. Improving the performance of the protocol operations is classically achieved by optimizing the operations that are on the common path [HH93, CH95]. The common path, also called the critical path or the fast path, is the part of the code that is the most frequently executed. By optimizing this path, the execution time of the overall program under normal conditions will be optimized. This optimization technique has been widely utilized to increase the performance of protocol code. The TCP BSD header prediction is probably the best known example of an optimized common path protocol implementation [CJRS89]. The concept of separating the common and uncommon path for protocol code optimization is motivated by three reasons:

1. Optimizing the execution speed a program is a difficult process, it is then important to focus the optimization effort on the most profitable parts of the code. The common path is only a small part of the whole program but it is executed more frequently than the rest. Therefore, optimizing the common path generates relatively higher performance gain. In fact, the average number of instructions executed by a program can be evaluated by the following formula:

$$IC_{Av} = IC_{CPath} * freq_{CPath} + IC_{UCPath} * freq_{UCPath}$$

where  $IC_{CPath}$  is the number of instructions that are executed when the incoming event follows the common path and  $IC_{UCPath}$  is the number of instructions that are executed when the incomming event follows the uncommon path. The variables  $freq_{CPath}$  and  $freq_{UCPath}$  define the execution frequencies of each path.  $freq_{CPath}$  is expected to be close to 1.0, whereas  $freq_{UCPath}$  close to 0.0.

The gain achieved by reducing the number of instructions on the common path is then  $freq_{CPath}/freq_{UCPath}$  times larger than the gain achieved by the reducing the number of instructions by the same amount on the uncommon path <sup>3</sup>.

- 2. Code optimizations involve somehow tradeoffs. A classic example is the inlining optimization, which reduces the number of instructions by replacing each function call by the body of the corresponding routines. This optimization, if performed systematically, can generate very large codes which lead to very bad instruction cache behavior and very poor performance (see section 5.5.6). A solution to this problem is to perform those optimizations selectively on the common path.

- 3. In protocol implementation, the distinction between the common and uncommon path is clear (this is not the case for all types of programs). There are many paths through the protocol codes, however there is only one common path which is usually only composed of few tens of instructions ([CJRS89]). The code to be optimized corresponds to the normal case. In this case, the protocol behavior is generally predictable. In addition, there is no need to optimize the path followed when a error occurs,

<sup>&</sup>lt;sup>3</sup>In this analyse, we neglected the performance penalty added to the uncommon path by the optimization the common path. We expect the product of this penalty with the execution frequency of the uncommon path to be very small.

such as a packet loss. In fact, in those cases, the bottleneck is not the protocol code but the network or the interface. Optimizing that path will have a minimal effect on the protocol performance. HIPPCO makes intensive usage of this common/uncommon path distinction.

## 3.2 Optimization Principles

HIPPCOs' primary goal is to generate protocol code that has very fast execution time and small code size. This optimization goal has been divided into two parts:

- code execution speed optimization

- code size optimization

These two optimizations can not be treated individually because they are not completely independent. As we show in this report, some code speed optimizations increase the code size and similarly some code size optimization imply some speed penalties. This report only presents the code speed optimization algorithms. The results of the work on code size optimization algorithms will also be cited, but the details will be presented in another paper [Cas95b]. The goal of the code speed optimization is to reduce the number of cycles that a program takes to execute. This is a complex task, because the execution speed of a code depends on several components that interact together. The number of cycles required to execute the program is given by the following formula [HP90, Cas95a]:

$Cycles_{total} = IC * CPI_{Execution} + Memory\_accesses * Miss\_rate * Miss\_penalty$

where IC is the number of instructions executed,  $CPI_{Execuction}$  the average number of cycles per instruction,  $Memory\_accesses$  the total number of memory accesses within the program,  $Miss\_rate$  the rate of memory references which are not in the cache and  $Miss\_penalty$  the penalty, expressed in cycles, encountered when a memory access is performed.

The number of cycles is composed of the sum of the cycles spent executing the instructions of the program and the cycles spent waiting for the memory system (memory stalls).

In this evaluation, it is assumed that the memory stalls are all due to the cache. Although this is not true for all machines, the stall due to the cache always dominate the effect of other stall sources.

We also consider, in this formula, that the cycles for caches accesses are part of the CPU-execution cycles and are therefore included in  $CPI_{execution}$ .

According to this formula, a program execution time depends on three components:

- The instruction count (IC)

- The memory stall cost (Memory\_accesses \* Miss\_rate \* Miss\_penalty)

- The number of cycles per instructions (CPI)

Optimizing the global execution speed involves optimizing each of its components. We will present in the three following subsections the general program optimization principles for each of those components. In section 4, we describe how these principles are applied to protocol code optimizations in HIPPCO.

## 3.2.1 Instruction Counts Optimizations

The optimizations that improve program performance by eliminating instructions are widely used in today's compilers. However most of those optimizations are limited, because they are only based on static analysis (control flow, dependency analysis). Compiler optimizers that use profiling data are not very commonly used yet. In this subsection, we described the approach that is commonly used to optimize programs through high-level transformations. We will discuss machine level optimizations (such as register allocation,...), or optimizations that can be performed by lower-level compilers such as loop unrolling, redundancy elimination. We present optimization techniques that uses additional informations about the application behavior to reduce the instruction count.

The optimizations that tend to reduce the number of instructions to perform are usually performed on the most frequently executed parts of the code. Those optimizations can be classified in two categories: first, those modifying the structure of the program and which are independent of the programming language, we will call them the *structural optimizations*. Second, the optimizations that reduce the number of instructions by some programming techniques. We call them *code optimizations*.

The structural optimizations consist of restructuring a program such that the most frequently path is scheduled at the beginning of the program. Events that follow the common path are then detected earlier. All processings that belong to the uncommon path are scheduled out of the common path stream. Such an optimization is very desirable in the case of communication protocols is the cyclic usage behavior of these protocols (e.g. bulk transfer TCP has same size, in order packets 95 % of the time on most networks). A classic structural optimization is the

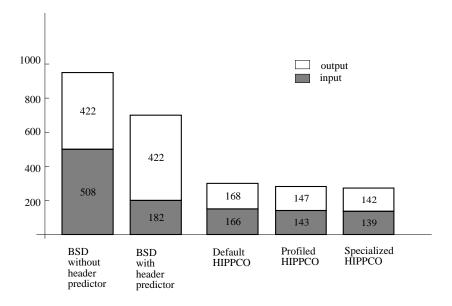

TCP header prediction [CJRS89] implemented in TCP BSD. It predicts the values of the fields of the next incoming packet, such that the reception of in order packets can be processed in few instructions. Some experiments that we performed, and which are presented in section 5.5.2, showed that the TCP header prediction reduces the average number of instructions, necessary to process an incoming packet, from 508 to 186.

The code optimization that is the most usually used in programming language such as C is the inlining technique. Inlining involves a space/speed tradeoff, therefore it should be applied selectively. The effect of inlining on program performance has been extensively studied [CHT91, DH92, Hos95]. The issue of how function inlining can be automated has been addressed several times in previous research [DH92, Hos95]. Current low-level compilers feature inlining optimizations. Usually those compilers only inline simple and small functions. The heuristics used can not perform very aggressive inlining because the frequencies of execution of each functions is difficult to evaluate at the low-level.

In section 4.1, we show how the automatic common path identification and the intermediate program representation facilitates the application of structural optimizations in HIPPCO. We also show how the prediction information provided by the application designer provides more opportunities to perform efficient code optimizations. Heuristics based on the predictions of the different code part execution frequency are used to apply inlining in the most optimal way.

## 3.2.2 Memory Stall Optimizations

Traditional optimization techniques improve program performance by reducing the number of instructions. Those optimizations have been designed at the time where most of the cycles were used to execute the program instructions.

However as the processor speeds increase at a much faster rate than the memory speeds, the bootleneck has been shifted to the memory system [CT90, GPSV91, Fel93].

The emergence of the RISC technology, which features very simple and uniform instructions, amplified the effect of the costly memory access for at least 2 reasons: first, programs running on a RISC processor are longer than the one running on CISC type processor and therefore perform more instruction memory references. Second, the uniform RISC instruction can be efficiently pipelined. However if one of this pipeline components, such as the *fetch* instruction, takes more time than the other, the pipeline efficiency is not optimal.

Optimizing the number of instructions is not enough anymore, optimizations of the memory bandwidth is also required.

As expressed in the previous section, the memory stall cost is estimated by :  $Memory\_accesses*Miss\_rate*Miss\_penalty$ . Optimizing this cost requires to:

1. Reduce the total number of memory accesses (Memory\_accesses)

The memory accesses are of two types: the data and instruction memory accesses.

Reducing the number of data memory accesses is performed by a technique called Integrated Layer Processing (ILP) [CT90]. The motivation of ILP came from the observation that data manipulations (checksum, presentation formatting, encryption) are very costly. The reason is that manipulating each byte of the messages, requires a memory load and a memory store, which are relatively slow operations on modern RISC architectures. Communication systems make extensive uses of data manipulations. Data manipulations are even more frequent in naive implementations of layered systems which code protocol layers by different functions communicating asynchronously. A data processed by the communication system is then processed sequentially by each of its layers. This implementation architecture multiplies data manipulations. The ILP technique consists of integrating all the manipulation functions of the different layers into an unique function. The motivation of layer and function integration is double: first, the number of memory accesses is reduced (the bytes are only read once, then all the data manipulation functions are pipelined, and the resulting data is written back in memory). Second, integration increases the data locality of the program, which improves the data cache behaviour. ILP has been extendively studied in the past few years [AP92, BD95, GPSV91]. [AP92] proposes a a technique to automize ILP functions implementation using a concept called the word filter. [BD95] shows that the ILP is not very easy to implement and that the gain achieved is less important than expected for various reasons. In this report, we are not considering ILP techniques. As detailed in section 2.1, the HIPPARCH compiler is composed of two tools: the first generates the control part of the protocol and the second the data manipulation functions. ILP techniques are considered in the second tool, whereas HIPPCO belongs to the first one.

The reduction of the the number of instruction memory accesses is principally performed in HIPPCO by the techniques proposed in section 4.2 (Instruction Count Optimizations). Those optimizations reduce the number of instructions to execute and consequently the number of *fetch* and *load* instructions.

## 2. Reduce the cost of each memory access (Miss\_rate)

Reducing the cost of memory accesses is performed by reducing the miss-rate through a better cache memory utilization.

Most of current architectures use a hierarchical memory system to reduce the memory bottleneck. Typically memory systems are now composed of a main memory and several memory caches. Cache memories are small, highspeed buffer memory used to hold parts of the code which is frequently refered [HP90, Smi92]. Information (data or instructions) located in cache memory can be acceded in much less time than that located in main memory. Thus, the CPU spends less time waiting for instructions and operands to be fetched and/or stored. There is of course a trade-off between small, high miss rate caches with fast access time and large caches that may increase processor cycle time. Caches work better when the program exhibit significant locality. Temporal locality exists when a program references the same memory location several times in a short period. Caches exploit temporal locality by retaining recently referenced data. Spatial locality occurs when the program access memory locations close to those it has recently accessed. Caches exploit spatial locality by fetching multiple contiguous words (a cache block) whenever a miss occurs. Optimizing the memory access cost is then achieved by increasing those localities and reducing cache misses.

Cache misses results from essentially two sources [GC90]:

- interference between instructions competing for the same block in the cache

- lack of room for some instructions. This lack of room is often caused by cache pollution. A cache can be polluted by instructions that are loaded and never executed. There are two causes that generates this pollution: First, if cache prefetching is used, instructions are loaded in the cache before they are referenced. Second, as cache blocks are usually larger than one instruction, some instructions are loaded and not executed.

If the cache is large enough to hold the entire program, cache pollution will not deteriorate the program performance. However, if the cache is smaller than the program size, cache pollution should be reduced to achieve high performance.

Many researchers worked on the problem of restructuring programs to improve their memory performances. Most of those works use some profiling information to restructure the object code of the programs to achieve better code locality. McFarling [McF89] proposed algorithms and heuristics that use profile data to guide in excluding some instructions from the cache to increase the performance of a direct mapped cache.

Pettis and Hansen [PH90] described techniques that pack the most frequently executed instructions and move the unfrequently executed instructions at the end of each function. Global analysis arranges functions to reduce inter-function cache conflicts.

In [GC90], the authors proposed to reduce instruction cache pollution by code repositioning. Contrary to the other works, no profiling data is used. The optimizations uses control flow and dependency analysis.

Profile guided code optimization is implemented in some of today's compilers. The C compiler for the Alpha CPU (distributed with OSF-1) features some of this profile guided optimizations. A study of the effect of profile guided optimization performed by commercial compiler (HP C compiler) on protocol codes (TCP and UDP) is presented in [SKP94]. This compiler implements the code restructuring algorithms described in [PH90]. Although the protocol throughput increased from 300 to 500KBit/s, the effect of those optimizations is limited. One reason is that the optimizations performed in this experiment only work at the procedure level and does not perform any cross-module optimizations.

The optimizations that we propose in section 4.4 are based on the techniques presented in [McF89, PH90, SKP94]. They differ however on several aspects:

- The analysis is performed using *prediction information* specified by the module designer and not from profiling data collected from a first implementation. This approach, which reduces the profiling collection process overhead, makes the compiling phase more efficient.

- global (cross-module) optimizations are performed. The optimizations are performed directly on the intermediate tree generated by the Esterel compiler. This compiler generates from a set of modules an integrated tree. The module abstraction does not exist anymore at this level of representation.

- the optimizations are performed at a higher level than the object code level. The goal of our optimizations is to generate good quality (language) code that can be optimally processed by the low-level compiler (C-compiler).

## 3.2.3 Cycle Per Instruction (CPI) Optimizations

Processors' speeds increased drastically over the last decade. The RISC architecture, which aims for both simplicity in hardware and synergy with compilers, is probably one of the most important factors of this improvement. In the RISC systems, each instruction is composed of micro-instructions which execute in a single cycle and are pipelined for better performance [HP90]. Pipelining is an implementation technique whereby multiple instructions are overlapped in execution. This is a technique used to make fast processors. A pipeline is often compared to an assembly line: each step in the pipeline completes a part of the instructions. An instruction can be implemented with five basic execution steps:

- IF- Instruction Fetch

- ID- Instruction Decode

- EX- Execution

- MEM- Memory access

- WB- Write back

Five instructions can be processed concurrently in the pipeline. One instruction is fed into the pipeline at the start of each clock cycle and moved one stage further with each clock cycle.

The low level compiler schedules the instructions to take advantage as much as possible of the pipelining. However there are situations, called *hazards*, that prevent the next instruction in instruction stream from executing during its designated cycle. For example, if an instruction to be fetched in the first stage is not in the cache, the processor stalls (waits) until the missing instruction is retrieved from the main memory. It is then important to have the code in the cache to fully take advantage of the pipelining behavior.

There are three classes of hazards:

- Structural hazards arise from resource conflicts

- Data hazards arise when a instruction depends on the result of a previous instruction

- Control hazards arise with instructions which change the Program Counter

The low-level compilers try to minimize those hazards with an optimum scheduling of the basic instructions. However low-level compiler do not have usually enough information on the program behavior to obtain the optimal performance. For example, when a branch instruction is executed the address of the next instruction depends on the test result and therefore can not be defined before the third step (instruction execution step). Three cycles are wasted for each branch of the program. Therefore to reduce this penalty, most of the processors make predictions: they make the assumption that the forward branch (else branch) is not taken and continue to fetch instructions as if the backward branch (then branch) were a normal instruction. If the prediction turns out to be invalid, the pipeline is stopped and restarted with the fetch of the new instruction. The branch penalty is then suppressed for each valid prediction.

Low-level compilers usually keep the branch order of the original code, by lack of information on the actual program behavior. Some researchers ([SKP94, PH90]) proposes to use profile information to reorder the basic blocks such that the most heavily used basic blocks are placed in an order which favors the hardware branch prediction logic. Those optimization techniques are usually cumbersome to use. They require to generate a first version of the code, then to instrument it, to run it in order to get some profiling information and finally to recompile the program.

In section 4.4.2, we show how HIPPCO uses the prediction information to reorder the tests' outcome in order to improve pipelining.

## 4 HIPPCO Design

In this section, we describe the details of HIPPCO design. We firstable describe the common path identification phase, which is based on a Markov analysis. We then present the various instruction count and the memory stall optimizations applied to the common path.

## 4.1 Common Path Identification by Markov Analysis

#### 4.1.1 General Presentation

For determining the execution frequency of different sections in a program, two alternative approaches are known from general compiler construction: code profiling [Cha91] and static analysis of the program code ([Bal93], [Wu94], [Wag94]). With code profiling, the program is executed using input data that is representative of the program's actual use. This has the advantage that a very accurate calculation

of the probability of executing different program sections can be achieved. However, profiling is a time consuming activity since it requires selecting representative input data, and then modifying the program code according to the calculated execution probabilities. An additional difficulty with protocol code is that profiling requires the execution of two working program modules over a network connection.

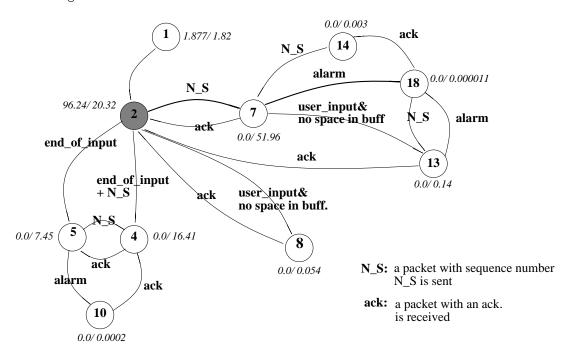

Thus, for protocol code, static analysis of the program control flow graph seems to be the more practical solution. Again, static analysis may be realized in several ways: by simple loop detection ([Aho86]) or by a full Markov analysis of the control flow graph ([Ram65], [Tri82], [Wag94]). While simple loop detection allows to determine a superset of program sections that will be executed with high frequency, the optimizations we consider (such as test outcomes rescheduling or function inlining) require more exact information on the execution frequency. We therefore use a full Markov analysis of the control flow graph of an Esterel program [CH95].

The general idea of Markov analysis is to regard the control flow graph of a program as a finite Markov chain. The control flow graph is composed of nodes connected by arcs. It is constructed as follows: the nodes in the graph correspond to sequential sequences of assignement statements or function calls. In accordance with standard terminology of compiler construction [Aho86], these nodes are referred to as basic blocks. The last statement in each basic block is either an if statement or an await statement.

The arcs in the graph correspond to possible transfers of control between basic blocks. In an Esterel program, a control transfer can occur in two different ways: first, each if statement introduces two arcs, one leading to the basic block that is executed when the if test is true, and one leading to the basic block that is executed when the if test is false. Second, each state in the Esterel program has one arc for each input event in the automaton. Again following standard compiler terminology, the arcs will be referred to as *branches* in the following.

For the purpose of Markov analysis, the basic blocks of the control flow graph are referred to as *mstates* (for Markov states, not to be confused, at this point, with the states of an Esterel automaton), and the branches as *transitions*. Markov analysis requires that the probability of traversing each transition is known. In other words, the probability of traversing each branch in the control flow graph must be determined. This is called *branch prediction*.

In our design, branch prediction for protocol code can be performed at two different points in time. First, the writer of the building blocks defines the probabilities for branches leading code sections for error handling and similar infrequent events. However, for some branches the execution frequency depends on conditions that are

only known when the building block is used in a particular protocol configuration. An example is the TCP protocol, where the authors of [Cla89] found that the branch probabilities vary when the protocol is used by a client or by a server module in a distributed application. In this case, the designer of the protocol library defines several different branch predictions, one for each case. Then, a configuration variable is introduced with one value for each case. This variable can be set by the user of the protocol library when configuring a particular protocol. In the example of the TCP code, the variable can be set to the values "Server" or "Client". Such variable is easily introduced by the means of keywords in the interface specification language.

The current version of the Esterel language does not allow to specify branch probabilities. We therefore implemented an extension to the Esterel compiler that allows specifying numerical probabilities for the input events of a module, and for the two outcomes of an if statement in an Esterel action.

Using this model, the execution frequency of the different parts in a configuration of protocol building blocks written in Esterel could work as follows. First, the OC code for the configuration is generated. Then the Oc code is split into basic blocks and branches in the way described above, and the branch probabilities are written into a transition matrix.

Let n be the number of basic blocks in control the flow graph, and let P(i,j) be the probability that control passes from basic block i to basic block j. It can then be shown [Tri82] that the number of times,  $V_i$ , that each of the basic blocks is visited can be calculated by solving the following system of n linear equations:

$$V_{j} = \delta_{1j} + \sum_{k=1}^{n} V_{k} P(k, j)$$

where  $\delta_{ij} = 1$  for i = j, and 0 otherwise.

## 4.1.2 HIPPCO Implementation

Applying this method directly on protocol code is not practical. In fact, the resulting matrix can become rather large. The amount of computation can be significantly reduced by making use of the Esterel code structure.

As described earlier, Esterel generates from a specification an automaton. This automaton is composed of a set of Esterel states, which are internally coded as trees. Therefore, there is no loop within a state. The execution probability of each state basic block can be determined by the hierarchical approach described hereafter:

1. Compute the state execution probabilities by a Markov analysis using the Esterel states as unit instead of the basic block (mstates = Esterel states)

2. Compute the probabilities of the basic blocks within each Esterel state, by multiplying the state probability with the probability of traversing each of the branches going from the root to the corresponding basic block.

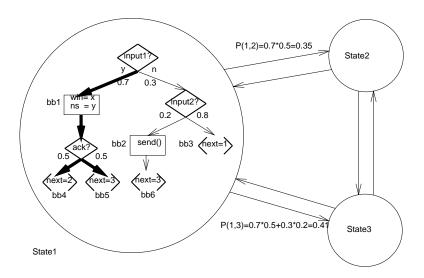

Figure 5: HIPPCO Markov Analysis

Once all the basic block probabilities have been computed, a heuristic should be used to identify those belonging to the common path. This approach has the major drawback that it requires the probability computations of all basic blocks, which is quite computing-intensive.

Generally, we expect the common path to be composed of a set of contiguous basic blocks. In fact, with the tree representation of the generated automaton, the execution control flows are contiguous, there are no loops. Based on this observation, we devise an algorithm that identifies the common path with a minimal amount of computations. The contiguity constraint makes the algorithm more stable and less sensitive to the branch prediction values. This algorithm has been implemented within HIPPCO for common path identification and it is composed of four steps:

1. Computation of the Transition matrix: (with mstates = Esterel states) In this step, the transition probilities P(i,j), which define the probabilities to go from  $mstate_i$  to  $mstate_j$  are defined. The probability P(i,j) is computed by considering the tree representation of  $mstate_i$  and selecting all the paths  $B_k^{ij}$  (k=1 to  $M^{ij}$ , where  $M^{ij}$  is the number of paths in  $mstate_k$  leading to

$mstate_j$ ). Each path  $B_k^{ij}$  is a sequence of  $L_k^{ij}$  branches. Each of these branches has a probability  $q_{kl}^{ij}$  (l=1 to  $L_k^{ij}$ ). P(i,j) is defined by:

$$P(i,j) = \sum_{k=1}^{M^{ij}} (\prod_{l=1}^{L_k^{ij}} q_{k,l}^{ij})$$

for i and j going from 1 to N, where N is the number of states in the automaton. We call S this set of states.

In the example of figure 5, P(1,3) is computed as follows: there are two paths leading to  $mstate_3$  ( $M^{13}=2$ ). The first path has an execution probability of 0.35 (0.7\*0.5) and the second of 0.06 (0.3\*0.2). P(1,3) is then equal to the sum of those two probabilities, thus 0.41.

$2. \ \ Computation \ of \ the \ state \ visit \ probabilities:$

Once the transition Matrix, P, has been computed, the state visit probabilities are computed, by solving the following system of linear equations:

$$V_j = \delta_{1j} + \sum_{k=1}^{N} V_k P(k, j)$$

for j = 1 to N, where N is the number of states in the automaton. In HIPPCO, this is performed using a Gaussian algorithm. The result vector V defines the visit count of each state.

The probability  $PS_i$  of visiting  $mstate_i$  (i = 1 to N), is then obtained by computing:

$$PS_i = V_i / \sum_{k=1}^N V_k$$

3. Identification of the common states:

The state visit probabilities,  $PS_i$ , are then used to identify the common states set CSS, which is the set of the states that are the "most frequently" visited of S. This identification is done with the following two-steps heuristic:

(a)  $mstate_i$  is automatically added to the CSS if:  $PS_i > SPT$ , where SPT is the state probability threshold above which a state is considered a "common" state. The value of this parameter has an impact on the size of the resulting code: if the value of SPT increases, less states will be

automatically selected as "common" states. In the present HIPPCO implementation, SPT is set to 0.15 but this can dynamically be changed at compilation time. Let  $N_{as}$  be the total number of the those automatically selected states.

(b) Let MST be the minimum selection threshold i.e. the minimum fraction of selected states (if the value of MST increases, more states are added to the CSS).MST is set to 0.25 in the current HIPPCO implementation. The second step of the heuristic is as follows:

```

while ((\sum_{i \in CSS} PS_i) < MST)

add the mstate_m in CSS s.t. PS_m = max_{i \in (S-CSS)} PS_i.

```

Consider the example of a four states-automaton with a state visit probability vector  $V = \{0.1, 0.16, 0.03, 0.01\}$ . The first step of the previous heuristic selects automatically  $mstate_2$ , which has a visit probability of 0.16. However as 0.16 is smaller than 0.25, the second step adds  $mstate_1$  to the CSS. As  $PS_1 + PS_2 \ge MST$  the algorithm stops. CSS is therefore composed of  $mstate_1$  and  $mstate_2$ .

### 4. Identification of the common branches:

The common branches of each state of CCS are then selected. This is performed by going from the root to the leaves, for each state-tree of CCS, and cutting off all the branches with an execution probability smaller than a "common path" threshold CPT, commonly 0.5 in HIPPCO. The remaining branches constitute the common branches. In figure 5, the common branches of  $mstate_1$  are shown by the thicker lines. The protocol common path is finally identified by the union of all the common branches.

In the following two subsections (4.2 and 4.3), we detail the Instruction Count optimizations that have been implemented in HIPPCO. Those optimizations that were applied to the common path are classified into two groups: the *Structural Optimizations* and the *Code Optimizations*.

## 4.2 Instruction Count Optimizations / Structural Optimizations

In this subsection, we present the tree transformations performed by the *structural* optimizer. Some of those optimizations are These transformations improve the common path performance by decreasing the average number of instructions. These optimizations are applied to the control flow graph of the program. They are thus independent of the target language.

As described in section 2.2.2, an Esterel state-tree is composed of cascaded independent subtrees. Each of those subtrees processes one of the possible automaton inputs. If the automaton can receive I different inputs in state k, the tree of state kwould be composed of I cascaded subtrees.

The number of instructions per input event i in state k is then the sum of two components:  $Cr_i^k$ , the cost to reach the subtree corresponding to the input, and  $Cp_i^k$ , the cost to actually process the input event.

The different inputs have different probabilities  $P_i^k$ . In fact, some events are more frequent than others. Typically *frames* from the network occur more often than the *alarm* signals. Therefore the average execution time of the state k can be modeled by the following formula:

$$C_{av}^{k} = \sum_{i=1}^{I} P_{i}^{k} * (Cr_{i}^{k} + Cp_{i}^{k})$$

or

$$C_{av}^{k} = \sum_{i=1}^{I} P_{i}^{k} * Cr_{i}^{k} + \sum_{i=1}^{I} P_{i}^{k} * Cp_{i}^{k}$$

In the rest of this subsection, we propose a set of algorithms that reduce the average number of instructions by reducing each of those two components. The *Inputs Rescheduling* optimization reduces the first component. The Common Branches Extension optimization reduces the second component. The *Branches Pruning* optimization reduces both of them.

### 4.2.1 Inputs Rescheduling

In this paragraph, we propose a transformation that optimizes the first component  $\sum_{i=1}^{I} P_i^k * Cr_i^k$ . This component can be rewritten as

$$\sum_{i=1}^{I} P_i^k * N_i * C_{test}$$

where  $N_i$  is the rank of subtree i in the state tree. It can easily be demonstrated that this sum is minimal when the subtrees corresponding to the most frequent events are scheduling first in the tree, i.e. the subtrees are sorted in decreasing event frequencies.

The *Inputs Rescheduling* optimization is based on this observation. It consists in rescheduling the subtrees handling the most frequent input-events before the subtrees handling the less frequent input-events. Input events belonging to the common

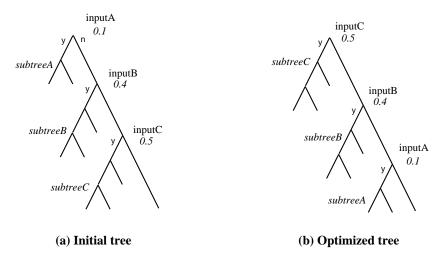

path would then be detected faster. The input frequencies are defined from the information provided by the protocol designer. Figure 6 illustrates this optimization. Subtree A (i.e. handling the input event A) has an execution probability of 0.1, subtree B of 0.4 and subtree C of 0.5. The Inputs Rescheduling optimization restructures the initial tree, by rescheduling subtree C at the root, followed by subtree B and then subtree A.

A problem may appear when several inputs can activate the automaton simultaneously. The subtrees are not then completely independent. In this case, the partial order between those inputs should be preserved in the optimized tree otherwise the generated tree will not be equivalent to the initial one. However, the HIPPARCH execution environment was designed, such that only one input at a time can activated the protocol automaton. The subtrees are then all independent in our case.

Figure 6: Inputs Rescheduling Optimization

## 4.2.2 Branches Pruning

In HIPPCO, the protocol designer can specify the probability of each input event and of each specification test's outcome. In some configurations, it may happen that some tests' outcomes are constant and that some inputs never occur. In this situation, the processing relative to those tests and inputs is unnecessary.

The *Branches Pruning* optimization configures a general protocol specification to a particular application. This optimization is performed in two steps:

- 1. all subtrees handling incoming events that are not possible for a given protocol configuration are removed,

- 2. within a subtree all tests with constant outcomes are detected and replaced by the predicted outcomes.

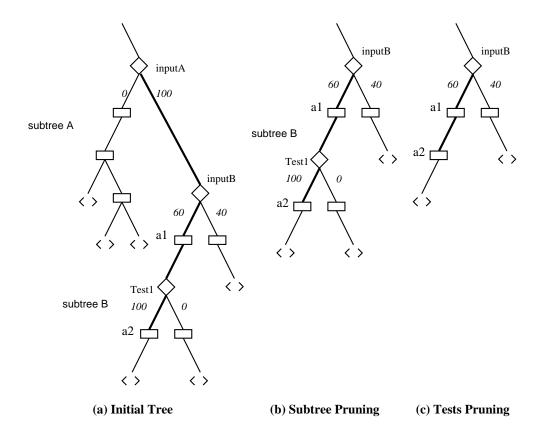

Figure 7 illustrates this optimization. Figure 7(a) displays the initial tree with the inputs and test outcomes' probabilities. Figure 7(b) shows the resulting tree when the subtrees handling impossible events have been removed. In this example, input A never occurs. Therefore the subtree handling input A is removed. The number of instructions to execute before reaching the subtree B is reduced. The presence test of input A is not performed anymore. Figure 7(c) shows the resulting tree when the tests within a subtree and with constant outcomes are removed. In this example, test1, is always correct. Test1 is then replaced by its backward outcome  $a_2$ . This reduces the proceesing cost of subtree B. In fact, by removing the unnecessary tests, the number of instructions to execute is reduced.

This optimization is performed on the initial tree representation, before any code size optimization is performed. It is performed everywhere, not only on the common path.

#### 4.2.3 Common Branches Extension

In order to reduce the code size of the generated code, the tree representation of Esterel is transformed into a graph representation by HIPPCO [Cas95b]. However, we may want not to perform this code size optimization is some cases e.g. on the common path.

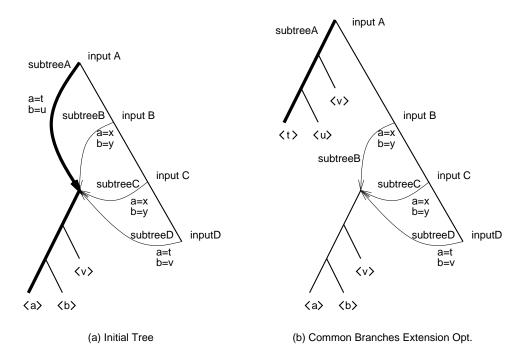

The Common Branches Extension optimization transforms the graph representation into a tree representation only on the common path. The generated common path is then straightlined. This optimization reduces the number of instructions on the common path (by removing the function calls overhead). It also improves i-cache (instruction-cache) behavior by improving the code locality of the common path.

The drawback of this optimization is that it increases the code size. However since the common path is only a small part of the total code, the code size increase is much smaller than the original Esterel code.

Figure 8 illustrates this optimization. In the initial tree, subtrees A, B, C and D are coded by a reference to an intermediary subtree with appropriate parameters. In the optimized tree, the subtree (or in general the parts of the subtrees) belonging to

Figure 7: Branch Pruning Optimization

the common path (thicker line) is extended. As a result, subtree A can be acceded directly without indirection.

## 4.3 Instruction Counts Optimizations / Code Optimizations

## 4.3.1 Inlining

Inlining consists of replacing a function call by a copy of the procedure body. Function inlining decreases execution time for two reasons: first, the overhead of the function call (instructions that save the status of the caller on the call stack) disappears. Second, by removing the function boundary, other optimizations can be performed by the low-level compiler (develop impact on i-cache). The penalty of inlining is a code size increase. Inlining is generally not a trivial optimization because

Figure 8: Common Branches Extension Optimization

it involves a code size/ code speed tradeoff. Inlining the wrong functions might have a bad impact on the i-cache performance and slow down program execution speed. The issue of how function inlining can be automated has been addressed several times in previous research []. If code size is not a direct constraint, inlining is beneficial in any of the following cases:

- the function is only called once,

- the size of the function is smaller or equal to the number of instructions required to call this function,

- the function is executed very often.

Our common/uncommon path approach makes the choice of functions to inline easier. In HIPPCO, in addition to the functions that comply to one of the two first properties listed previously, all the functions that belong to the identified common path are automatically inlined whatever their size in conformity to the third property.

## 4.4 Memory Stall Optimizations

In this section, we present the tree transformations, performed by the *structural* optimizer, that reduce the memory stall cost. These transformations improve the common path performance by increasing code locality.

### 4.4.1 Outlining

Protocol common path code sizes are usually smaller than i-cache (typically 8KB). In this case, i-cache misses are not due the a large code size, but to a synchronization problem. Two instructions generate a cache conflict (and therefore a miss) if their addresses are spaced by a multiple of the cache size. Reducing the number of misses can then be performed by restructuring the code blocks such that the most frequent one will not conflict.

This scheduling problem is difficult to solve at the language level, because the unit the cache handles, the cache block, is not defined at the user level. It seems easier to solve this problem at the machine level by lower level compiler. However the problem of identifying the block frequencies is not trivial at this level.

Outlining can be applied as a simple solution to this scheduling problem. It compacts the frequently executed instructions and moves unfrequent code out of the mainline of execution. The resulting code features a very spatially compact common path which can entirely fit into the cache. Instruction blocks of the common path do not interact anymore.

As explained in [MPO95], this optimization has its limits when it is performed manually. Only conservative predictions can then be made. Performing this optimization automatically, on customized protocols with more aggressive predictions, will generate better results. HIPPCO identifies automatically the common path and compacts it by coding all uncommon subtrees or branches as functions (in fact, branches are outlined only if they are larger than the number of instructions that is required to perform a function call). The remaining code, the common path, is then very compact.

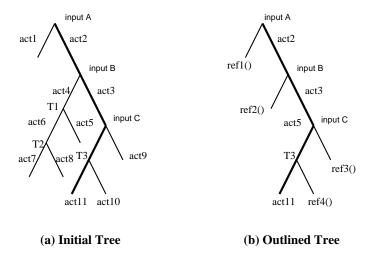

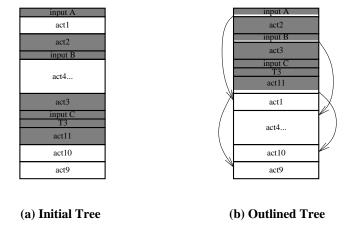

Figure 9 illustrates this optimization on a program tree. All uncommon branches such as  $act_1$ ,  $act_4$ ,  $act_{10}$  and  $act_9$ , which can be composed of a sequence of instructions, are replaced by a reference (function call) to separated subtrees  $ref_1()$ ,  $ref_2()$ ,  $ref_3()$  and  $ref_4()$ . The effect on the i-cache performance is shown in figure 10. The resulting tree is more compact and therefore has better icache behavior.

Figure 9: Outlining Optimization

Figure 10: i-cache layout

## 4.4.2 Test Outcomes' Rescheduling

This optimization is based on two observations. The first is that basic blocks are very often generated in the order of the corresponding source code lines. The second is that the execution of the forward branch (else-branch) of a test requires a jump,

whereas the code corresponding to the backward branch is streamlined. For example, the compiled code of the C program:

```

if (test)

then action1;

action2

```

will often be composed of the code of action1 with a conditional branch around it to handle the action2 code. The code of action2 is only reachable via a jump which break up the program pipeline. The execution of the forward branch leads to inefficient cache utilization and to wasted cycles due to processor stalls, a penalty which varies from a RISC processor to another.

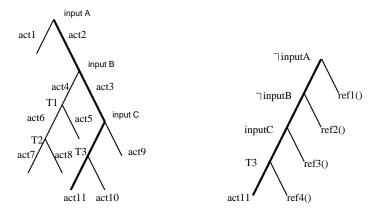

The proposed optimization restructures the test nodes in the decision tree such that the most frequently outcomes are on the left branch of the tree [PH90]. This transformation is performed by considering all the program trees nodes (on the common and uncommon path) and by reversing all the tests whose most frequent outcomes are on the forward (else) branch. The test reverse operation is performed by negating the test and interchanging the backward and forward branch.

Because we are using a tree representation, this optimization also increases the i-cache utilization by structuring the code such that the common path is completely separated from the uncommon path. The i-cache utilization is then maximum, i-cache pollution is then minized. The benefit on the i-cache utilization is bigger if this optimization is conjunctly executed with the Common Branches Extension optimization, which ensures that the code on the common path is straighlined.

This optimization also increases program pipelining. In fact, as we described in section 3.2, processors usually makes predictions on the tests' outcome to increase the pipelining gain. They usually predict that the forward branch is not taken. This Rescheduling optimization increases the processor prediction correctness rate and consequently the pipelining gain.

Figure 11 illustrates this optimization on the outlined tree of the previous section. In the example, the most frequently outcome of input A is on its forward branch. The transformation converts then input A into  $\neg$  input A and interchanges the backward and forward branches. The same transformation is performed on the test of input B. As a result of this transformation, all the tests along the common path have their most frequently used outcome on the backward branch (left branch).

Figure 12 shows the impact of this optimization on the i-cache layout. All the instructions of the common path (shaded) are contiguous in the memory layout. The uncommon path (included the reference to the uncommon subtrees) is mapped after it.

(a) Initial Tree

## (b) Outcome Rescheduled and Outlined Tree

Figure 11: tree transformation

| input A               |

|-----------------------|

| act1                  |

| act2                  |

| input B               |

| act4                  |

|                       |

| act3                  |

| input C               |

| act3<br>input C<br>T3 |

| input C               |

| input C<br>T3         |

(a) Initial Tree

# (b) Outcome Rescheduled and Outlined Tree

Figure 12: i-cache layout

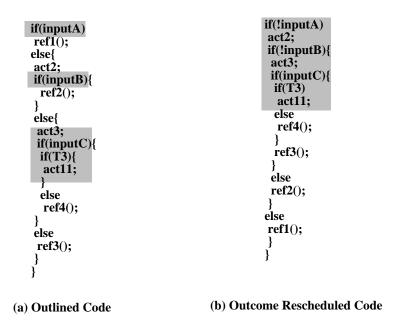

The corresponding code transformation is shown by figure 13 (the shaded parts show the common path).

Figure 13: Code Transformation

## 4.4.3 State Functions Rescheduling

This optimization is very similar to the outlining optimization, but works at the function level instead of the instruction level. HIPPCO generated code is composed of several functions. Each of them implements one of the automaton states. Those functions are scheduled in the same order in which they are defined by the automaton. The function implementing state 1 is just before the function coding state 2, which is just before the state 3 function and so on. This order is usually conserved by the low-level compilers.

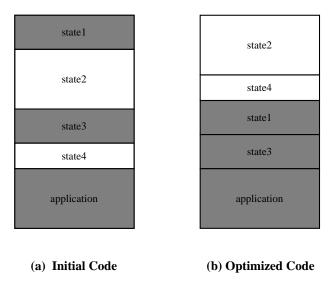

The State Functions Rescheduling optimization increases the code locality, by rearranging, in the protocol code, those functions from the less to the most frequently executed. As a result the most executed states are grouped and the program code locality is improved. Better i-cache utilization is achieved.

The motivation for this optimization is then same than for the Outlining optimization. If all the most frequently executed functions are spatially grouped, they do not interact too much. The synchronization problem expressed in section 3.2 is then minimized. The benefit of the proposed optimization is bigger if it is associated with the Outlining optimization. In fact, in this case, the frequently executed state

functions are smaller, because all the uncommon subtrees have been outlined, and have a larger probability to entirely fit in the instruction cache.

Also in general, the linker preserves the order in which the files are presented. For example, if two files are linked together, the basic blocks of the first file are ordered before the basic blocks of the second one in the final code. The order in which the files are linked has therefore a direct impact on the program memory layout and therefore on the i-cache performance.

To take advantage of this property, we schedule the most frequently visited statefunctions at the bottom of the protocol code, and link it with the application code in the order: protocol-application. The memory gap between the protocol and the application, source of i-cache pollution, is then minimized.

Figure 14 illustrates this optimization. State 1 and state 3, which are the most frequently executed, are scheduled at the bottom of the program, increasing the code locality. Also the i-cache pollution between the protocol and the application is reduced by relocating state 4.

Figure 14: Memory Layout

# 5 Evaluation

In this section, we present an evaluation of the optimization techniques that has been described in the previous sections. The test case and the experimental environment are first described, the results are then carefully analysed.

# 5.1 Test Case: A File Transfer Application

The experiments were performed with a file transfer application. This application is composed of a client and a server. This application is very simple, it can be thought off as a backup application: the client connects itself to a server to transmit a 4MB file. The data-transfer is unidirectional: the server receives pure data and sends pure acknowledgment packets.

This application uses the TCP protocol. The protocol implementations used for our experiments were generated by HIPPCO with different levels of optimization. A brief description of the protocol specification is presented in the following section.

In order to evaluate the impact of our optimizations, we performed the same experiment with a user level implementation of the BSD-TCP protocol that we developed at INRIA. The comparison criteria that we adopted (instruction count, i-cache miss rate, number of cycles per instruction and the code size) will be detailed in the end of section 5.4.

In our experiments, no packet loss was generated. Thus, incoming packets follow the header prediction path. This ensures that we are really measuring the performance on the common paths of the different implementations.

Because it is always difficult to compare two different implementations of a same protocol, we focused our analysis (at least for the instruction count) on the input processing of the server side (receives pure data and send acknowledgements) of our application and compared instructions by instructions those implementations to make sure that the comparaisons were fair. This means that we took into account the cost of the control part of the protocol and not of the execution environment. This is similar to the approach adopted in [CJRS89].

## 5.2 The Protocol Specification

The protocol implementations used were automatically generated from an Esterel specification. In this section, we give a brief overview of the specification of the transport protocol and also of the customization choices that we made for the experiments.

The protocol that has been specified is the data transfer part of TCP (we omit the connection establishment and termination phases). In this section, we address very briefly how the building blocks were designed and combined to generate the required protocol. A more detailed description of this specification is presented in [CD94].

Reusability and flexibility were our main design goals here. The building blocks have been designed so that they are meaningful to the designers and so that changes in the protocol specification only induce local changes in the architecture and the code. We implemented this example incrementally in order to satisfy the modularity property that we are aiming for. We started from a simple protocol and added modules step by step until we accomplished all required functionalities. Following the precepts of Object Oriented Programming we followed the rule one functionality-one module. An overview of the whole system is shown in figure 15. For clarity purposes, only the principal modules have been described and displayed.

Our data-transfer protocol is structured in three main concurrent modules: The Send Module: composed of two concurrent submodules:

- The User\_Input\_Handler module is a four states automaton. The first is the initialization state and the last the absorbing state. In the second state, the module is expecting data from the application. Whenever it receives some data, it processes and copies them into an internal buffer. If the buffer is full, it goes to the state 3, otherwise it broadcasts a Try-to-Snd signal and goes back to state 2. In state 3, this module is waiting for an acknowledgement packet. If this packet frees up some space in the buffer, the module goes back to state 2, otherwise it stays in state 3. The module returns to state 1 when a End of Connection signal is received.

- The Emission\_Handler module transmits packets on the network. It is a three states automaton. The first is the initialization state and the last the absorbing state. In the second state, the module can get activated by several signals, among them the try\_to\_send signal emitted by the previous module. The module then tries to send packets by evaluating the congestion window size, the silly window avoidance algorithm and the number of bytes waiting to be sent. It may then send one or several packets. The Send\_Now input forces the sending of a packet even though the regular sending criteria are not

Figure 15: Protocol Implementation Overview

satisfied (this is used to acknowledge data for example). If the module decides to send packets, the checksum is performed<sup>4</sup> and the header is completed.