# Hoare-Style Specifications as Correctness Conditions for Non-linearizable Concurrent Objects

Ilya Sergey<sup>†</sup> Aleksandar Nanevski<sup>‡</sup> Anindya Banerjee<sup>‡</sup> Germán Andrés Delbianco<sup>‡</sup>

$\label{eq:condon} ^\dagger \text{University College London, UK} \qquad ^\dagger \text{IMDEA Software Institute, Spain} \\ \text{i.sergey@ucl.ac.uk} \qquad \\ \text{\{aleks.nanevski, anindya.banerjee, german.delbianco\}@imdea.org}$

#### **Abstract**

Designing efficient concurrent objects often requires abandoning the standard specification technique of *linearizability* in favor of more relaxed correctness conditions. However, the variety of alternatives makes it difficult to choose which condition to employ, and how to compose them when using objects specified by different conditions.

In this work, we propose a *uniform* alternative in the form of Hoare logic, which can explicitly capture—in the auxiliary state—the interference of environment threads. We demonstrate the expressiveness of our method by verifying a number of concurrent objects and their clients, which have so far been specified only by non-standard conditions of *concurrency-aware linearizability*, *quiescent*, and *quantitative quiescent consistency*. We report on the implementation of the ideas in an existing Coq-based tool, providing the first mechanized proofs for all the examples in the paper.

Categories and Subject Descriptors D.3.1 [Programming Languages]: Formal Definitions and Theory; F.3.1 [Logics and Meanings of Programs]: Specifying and Verifying and Reasoning about Programs

General Terms Theory, Verification

*Keywords* Concurrency, Hoare logic, linearizability, quiescent consistency, counting networks, mechanized proofs.

## 1. Introduction

Linearizability [25] remains the most well-known correctness condition for concurrent objects. It works by relating a concurrent object to a sequential behavior. More precisely, for each concurrent history of an object, linearizability requires that there exists a mapping to a sequential history, such that the ordering of matching call/return pairs is pre-

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

OOPSLA'16, October 30–November 4, 2016, Amsterdam, Netherlands. Copyright © 2016 ACM 978-1-4503-4444-9/16/10...\$15.00. http://dx.doi.org/10.1145/2983990.2983999 served either if they are performed by the same thread, or if they do not overlap. As such, linearizability has been used to establish the correctness of a variety of concurrent objects such as stacks, queues, sets, locks, and snapshots—all of which have intuitive sequential specs.

However, as argued by Shavit [42], efficient parallelization may require the development of concurrent objects that are inherently *non-linearizable*: in the presence of interference, such objects exhibit behavior that is not reducible to any sequential behavior via linearizability. To reason about such objects, a variety of novel conditions has been developed: concurrency-aware linearizability (CAL) [21], quiescent consistency (QC) [4, 10], quasi-linearizability (QL) [2], quantitative relaxation [23], quantitative quiescent consistency (QQC) [28], and local linearizability [20], to name a few. These conditions, formulated as relations on execution traces, specify a program's behavior under concurrent interference. Some, such as QC, devote special treatment to the sequential case, qualifying the behavior in the quiescent (*i.e.*, interference-free) moments.

This proliferation of alternative conditions is problematic, as it makes all of them non-canonical. For any specific example, it is difficult to determine which condition to use, or if a new one should be developed. Worse, each new condition requires a development of its own dedicated program logic or verification tool. Furthermore, it is unclear how to combine the conditions/logics/tools, when different ones have been used for different subprograms. Finally, having criteria defined *semantically*, *e.g.*, in terms of execution traces, makes it challenging to employ them directly for reasoning about clients of the corresponding data structures.

#### 1.1 Concurrency Specification via Program Logics

In this paper, we propose an alternative, uniform, approach: a Hoare logic equipped with special *subjective* kind of auxiliary state [32] that makes it possible to name the amount of concurrent interference, and relate it to the program's inputs and outputs *directly*, without reducing to sequential behavior. We use Fine-grained Concurrent Separation Logic (FCSL) [35], designed to reason about higher-order concurrent programs, and has been recently implemented as a verification tool on top of Coq [40], but whose ability to address non-linearizable programs has not been observed previously.

1

More specifically, subjective auxiliary state permits that within a spec of a thread, one can refer to the private state (real or auxiliary) of *other* interfering threads *in a local manner*. This private state can have arbitrary user-specified structure, as long as it satisfies the properties of a partial commutative monoid (PCM). A particularly important PCM is that of *time-stamped histories*, which has previously been applied to linearizable objects [41], where it replaced call/return histories. A (logically) time-stamped history consists of entries of the form  $t \mapsto a$ , signifying that an atomic behavior a occurred at a time (or linearization point) t. A subjective specification further distinguishes the histories of the thread and its interfering environment, and usefully relates both to the thread's input and output.

Of course, Hoare-style reasoning about histories is a natural idea, exploited recently in several works [5, 16, 18, 22]. Here, however, we rely on the unifying power of PCMs, in combination with subjective specifications, to show that by generalizing histories in different ways—though all subject to PCM laws—we can capture the essence of several different conditions, such as CAL, QC and QQC in one-and-same *off-the-shelf* logical system and tool. More precisely, our histories need not merely identify a point at which an atomic behavior logically occurred, but can also include information about interference, or lack thereof. Moreover, we will use generic FCSL constructs for delimiting the scope of auxiliary state, to reason about quiescent moments.

# 1.2 Contributions and Outline

The ability to use FCSL for specifying and verifying linearizable objects (e.g., fine-grained stacks and atomic snapshots) has been recognized before [41]. In contrast, the main conceptual contribution of this work is an observation that the very same abstractions provided by FCSL are sufficient to ascribe non-trivial non-linearizable objects with specs that can hide object implementation details, but are sufficiently strong to be used in proofs of concurrent client programs, as we demonstrate in Section 2. Specifically, we recognize that auxiliary histories can be subject of user-defined invariants beyond mere adherence to sequential executions (e.g., be concurrency-aware [21]), and can be used to capture intermediate interference, allowing for quantitative reasoning about outcomes of concurrent executions (e.g., in the spirit of QQC [28]). These observations, surprisingly, enabled reasoning about non-linearizable data structures and their clients, which were never previously approached from the perspective of program logics or mechanically verified.

In this unified approach based on program logic, it seems inherently impossible (and contrary to the whole idea) to classify Hoare triples as corresponding to this or that correctness condition. Thus, instead of providing theorems that relate Hoare triples to existing conditions, we justify the adequacy of our approach by proof-of-concept verifications of concurrent objects and their clients.

Hence, as key technical contributions, we present *subjective specs and the first mechanized proofs* (in Coq) of (1) an elimination-based exchanger [39] (Section 3), previously specified using CAL, and (2) a simple counting network [4] (Section 6) that inspired definitions of QC and QQC. We then employ these specs to verify client programs (Sections 5 and 7). We discuss alternative design choices for specs and further applications of our verification approach in Section 8, and summarize our mechanization experience in Section 9. Section 10 compares to related work and Section 11 concludes.

#### 2. Main Ideas and Overview

We begin by outlining the high-level intuition of our specification approach, and summarize the main formalization steps. As the first motivating example, we consider the concurrent exchanger structure from java.util.concurrent [14, 39]. The main purpose of the exchanger is to allow two threads to efficiently swap values in a non-blocking way via a globally shared channel. The exchange might fail, if a thread trying to swap a value does not encounter a peer to do that in a predefined period of time.

For instance, the result of the two-thread program

can be described by the following assertion:<sup>1</sup>

$$r_1 = r_2 = \mathtt{None} \lor r_1 = \mathtt{Some} \ 2 \land r_2 = \mathtt{Some} \ 1 \qquad (2)$$

That is,  $r_1$  and  $r_2$  store the results of the execution of subthreads  $T_1$  and  $T_2$  correspondingly, and both threads either succeed, exchanging the values, or fail. The ascribed outcome is only correct under the assumption that no other threads besides  $T_1$  and  $T_2$  attempt to use the very same exchange channel concurrently.

Why is the exchanger not a linearizable data structure? To see that, recall that linearizability reduces the concurrent behavior to a sequential one [25]. If the exchanger were linearizable, all possible outcomes of the program (1) would be captured by the following two sequential programs, modelling selected interleavings of the threads  $T_1$  and  $T_2$ :

$$r_1 := \texttt{exchange 1}; \ r_2 := \texttt{exchange 2};$$

and

$$r_2 := \texttt{exchange 2}; \ r_1 := \texttt{exchange 1};$$

However, both programs (3) will *always* result in  $r_1 = r_2 = \text{None}$ , as, in order to succeed, a call to the exchanger needs another thread, running concurrently, with which to

<sup>&</sup>lt;sup>1</sup> We use ML-style option data type with two constructors, Some and None to indicate success and failure of an operation, correspondingly.

exchange values. This observation demonstrates that linearizability with respect to a sequential specification is too weak a correctness criterion to capture the exchanger's behavior observed in a truly concurrent context [21]: an adequate notion of correctness for exchange must mention the effect of interference.

Consider another structure, whose concurrent behavior cannot be related to sequential executions via linearizability:

The procedure flip2 takes a pointer x, whose value is either 0 or 1 and changes its value to the opposite, twice, via the atomic operation flip, returning the sum of the previous values. Assuming that x is being modified only by the calls to flip2, what is the outcome r of the following program?

$$r := flip2 x;$$

(5)

The answer depends on the presence of absence of interfering threads that invoke flip2 concurrently with the program (5). Indeed, in the absence of interference, flip2 will flip the value of x twice, returning the sum of 0 and 1, *i.e.*, 1. However, in the presence of other threads calling flip2 in parallel, the value of r may vary from 0 to 2.

What are the intrinsic properties of flip2 to be specified? Since the effect of flip2 is distributed between two internal calls to flip, both subject to interference, the specification should capture that the variation in flip2's result is subject to interference. Furthermore, the specification should be expressive enough to allow reasoning under bounded interference. For example, in the absence of interference from any other threads besides  $T_1$  and  $T_2$  that invoke flip2 concurrently, the program below will always result in r=2:

# 2.1 Abstract Histories of Non-linearizable Objects

Execution histories capture the traces of a concurrent object's interaction with various threads, and are a central notion for specifying concurrent data structures. For example, linearizability specifies the behavior of an object by mapping the object's global history of method invocations and returns to a sequence of operations that can be observed when the object is used sequentially [25]. However, as we have shown, neither exchange nor flip2 can be understood in terms of sequential executions.

We propose to specify the behavior and outcome of such objects in terms of *abstract concurrent histories*, as follows.

Instead of tracking method invocations and returns, our histories track the "interesting" changes to the object's state. What is "interesting" is determined by the user, depending on the intended clients of the concurrent object. Moreover, our specifications are subjective (*i.e.*, thread-relative) in the following sense. Our histories do not identify threads by their thread IDs. Instead, each method is specified by relating two different history variables: the history of the invoking thread (aka. *self*-history), and the history of its concurrent environment (aka. *other*-history). In each thread, these two variables have different values.

For example, in the case of the exchanger, the interesting changes to the object's state are the exchanges themselves. Thus, the global history  $\chi_{\mathcal{E}}$  tracks the successful exchanges in the form of pairs of values, as shown in below:

$$\chi_{\mathcal{E}} = [..., (1,2), (2,1), (4,5), (5,4), (9,8), (8,9), ...]$$

$$= \text{exchange ok} \quad \text{ex$$

The diagram presents the history from the viewpoint of thread  $T_1$ . The exchanges made by  $T_1$  are colored white, determining the *self*-history of  $T_1$ . The gray parts are the exchanges made by the other threads (e.g.,  $T_2$ ,  $T_3$ , *etc.*), and determine the *other*-history for  $T_1$ .

The subjective division between *self* and *other* histories emphasizes that a successful exchange is actually represented by *two* pairs of numbers (x, y) and (y, x), that appear consecutively in  $\chi_{\mathcal{E}}$ , and encode the two ends of an exchange from the viewpoint of the exchanging threads. We call such pairs *twins*. As an illustration, the white entry (2, 1) from the self-history of  $T_1$ , is matched by a twin gray entry (1, 2) from the other-history of  $T_1$ , encoding that  $T_1$  exchanging 2 for 1 corresponds to  $T_1$ 's environment exchanging 1 for 2.

The subjective division is important, because it will enable us to specify threads locally, i.e., without referring to the code of other threads. For example, in the case of program (1), we will specify that  $T_1$ , in the case of a successful exchange, adds a pair  $(1,r_1)$  to its self history, where Some  $r_1$  is  $T_1$ 's return value. Similarly,  $T_2$  adds a pair  $(2,r_2)$  to its self history, where Some  $r_2$  is  $T_2$ 's return value.

On the other hand, it is an important invariant of the exchanger object—but not of any individual thread—that twin entries are symmetric pairs encoding different viewpoints of the one-and-the-same exchange. This object invariant will allow us to reason about clients containing combinations of exchanging threads. Taking program (1) as an example again, the object invariant will imply of the individual specifications of  $T_1$  and  $T_2$ , that  $r_1$  must equal 2, and  $r_2$  must equal 1, if no threads interfered with  $T_1$  and  $T_2$ .

We can similarly employ abstract histories to specify flip2. One way to do it is to notice that the value of the shared counter x will be changing as  $0, 1, 0, 1, \ldots$ , and exactly two of these values will be contributed by each call to

flip2 made by some thread. We can depict a particular total history  $\chi_{\mathcal{F}}$  of the flip2 structure as follows:

$$\chi_{\mathcal{F}} = [ \ \dots, \ 1, \quad 0 \ , \quad 1, \quad 0 \ , \quad 1 \ , \quad 0 \ , \quad \dots ]$$

The two "white" contributions are made by thread  $T_1$ 's call to flip2, while the rest (gray) are contributions by  $T_1$ 's environment. Since the atomic flip operation returns the *complementary* (i.e., previous) value of the counter, the overall result of  $T_1$ 's call in this case is  $\bar{1} + \bar{1} = 0 + 0 = 0$ .

The invariant for the flip2 structure postulates the interleaving 0/1-shape of the history and also ensures that the last history entry is x's current value. This will allow us to reason about clients of flip2, such as (6). In the absence of interference, we can deduce that the two parallel calls to flip2 have contributed four *consecutive* entries to the history  $\chi_{\mathcal{F}}$ , with each thread contributing precisely two of them. For each of the two calls, the result equals the sum of the two complementary values for what the corresponding thread has contributed to the history, hence, the overall sum  $r_1 + r_2$  is 2.

#### 2.2 Hoare-style Specifications for exchange and flip2

The above examples illustrate that subjectivity and object invariants are two sides of the same coin. In tandem, they allow us to specify threads individually, but also reason about thread combinations. We emphasize that in our approach, the invariants are *object-specific* and *provided by the user*. For example, we can associate the invariant about twin entries with the exchanger structure, but our method will not mandate the same invariant for other structures for which it is not relevant. This is in contrast to using a fixed correctness condition, such as linearizability, QC, or CAL, which cannot be parametrized by user-defined properties.<sup>2</sup>

Subjective histories can be encoded in our approach as *auxiliary state* [36, 41]. Our Hoare triples will specify how programs modify their histories, while the invariants are declared as properties of a chunk of shared state (*e.g.*, resource invariants of [36]). With the two components, we will be able to describe the effects and results of programs *declaratively*, *i.e.*, without exposing program implementations.

A semi-formal and partial spec of exchange looks as follows, with the white/gray parts denoting *self/other* contributions to history, from the point of view of the thread being specified (we postpone the full presentation until Section 3):

The ellipsis  $(\ldots)$  stands for an existentially-quantified chunk of the history. The spec (7) says that a successful exchange adds an entry (v,w) to the self-history (hence, the entry is white). In the case of failed exchange, no entry is added. In the complete and formal specification in Section 3, we will have to add a timing aspect, and say that the new entry appears after all the history entries from the precondition. We will also have to say that no entries are removed from the other history (i.e., the exchanger cannot erase the behavior of other threads), but we elide those details here.

The spec of flip2 is defined with respect to history  $\chi_{\mathcal{F}}$ :

$$\begin{cases} \chi_{\mathcal{F}} = [\ \dots\ ] \} \\ \text{flip2} \ x \\ \left\{ \ \exists a \ b, \chi_{\mathcal{F}} = [\ \dots\ , a, \ \dots\ , b, \ \dots\ ], \text{res} = \bar{a} + \bar{b} \ \right\} \end{cases}$$

(8)

It says that the return value res is equal to the sum of binary complements  $\bar{a}+\bar{b}$  for the thread's two separate *self*-contributions to the history. Due to the effects of the interference, the history entries a and b may be separated in the overall history by the contributions of the environment, as indicated by  $\dots$  between them.

# 2.3 Using Subjective Specifications in the Client Code

The immediate benefit of using Hoare logic is that one can easily reason about programs whose components use different object invariants, whereas there is not much one can say about programs whose components require different correctness conditions. For example, Figure 1 shows a proof sketch for a toy program that uses both exchange and flip2. As each of these methods requires its own auxiliary history variable ( $\chi_{\mathcal{E}}$  for the exchanger, and  $\chi_{\mathcal{F}}$  for flip2), the combined program uses both, but the proof simply ignores those histories that are not relevant for any specific method (*i.e.*, we can "frame" the specs (7) and (8) wrt. the histories of the objects that they do not depend upon).

The program first forks two instances of flip2, storing the results in  $r_1$  and  $r_2$  (line 4). Next, two new threads are forked, trying to exchange  $r_1$  and  $r_2$  (line 8). The conditional (line 12) checks if the exchange was successful, and if so, assigns the sum of exchanged values to t (line 14); otherwise t gets assigned 2. We want to prove via the specs (7) and (8), that in the absence of external interference on the flip2's pointer x and the exchanger, the outcome is always t=2.

**Explaining the verification** In addition to the absence of external interference, we assume that the initial value of x is 0, and the initial *self*-histories for both flip2 and exchange are empty (line 1). Once the flip2 threads are forked, we employ spec (8) for each of them, simply ignoring (i.e.,

<sup>&</sup>lt;sup>2</sup> For example, linearizability does not allow users to declare history invariants on a per-object basis. The exchanger example motivated the introduction of the correctness condition CAL [21], which relaxes linearizability, and makes it somewhat more general in this respect, but still falls short of admitting user-defined invariants. flip2 can be specified using a variation of QC [28], but we show that a similar property can be expressed via subjectivity and a user-defined invariant.

```

2

3

4

\{\chi_{\mathcal{F}} = \text{perm}(a, b, c, d) = [1, 0, 1, 0], r_1 = \bar{a} + \bar{b}, r_2 = \bar{c} + \bar{d}\}

5

6

7

8

\{s_1 = \mathsf{Some}\ v_2 \wedge s_2 = \mathsf{Some}\ v_2 \implies \chi_{\mathcal{E}} = \mathsf{perm}((r_1, v_1), (r_2, v_2)) = \mathsf{perm}((v_1, r_1), (v_2, r_2))\}

10

\{s_1 = \mathsf{Some}\, v_2 \land s_2 = \mathsf{Some}\, v_2 \implies v_1 = r_2 \land v_2 = r_1\}

11

if s_1 is Some v_1 and s_2 is Some v_2 then

12

\{v_1 = r_2, v_2 = r_1, r_1 + r_2 = 2\}

13

t := v_1 + v_2 \quad \{t = 2\} \quad \text{else } t := 2 \quad \{t = 2\}

```

Figure 1. Verification of a concurrent client program using exchange and flip2 in the absence of external interference.

framing out)  $\chi_{\mathcal{E}}$ , as this history variable does not apply to them flip2. Upon finishing, the postconditions of flip2 in line 4 capture the relationship between the contributions to the history  $\chi_{\mathcal{F}}$  and the results  $r_1$  and  $r_2$  of the two calls.

Both postconditions in line 4 talk about the very same history  $\chi_{\mathcal{F}}$ , just using different colors to express that the contributions of the two threads are *disjoint*: a and b being white in the left thread, implies that a and b are history entries added by the left thread. Thus, they *must* be gray in the right thread, as they cannot overlap with the entries contributed by the right thread. The right thread cannot explicitly specify in its postcondition that a and b are gray, since the right thread is unaware of the specific contributions of the left thread.

Dually, c and d being white in the right thread in line 4, implies that they must be gray on the left. Thus, overall, in line 5, we know that  $\chi_{\mathcal{F}}$  contains all four entries in some permutation, and in the absence of intereference, it contains no other entries but these four. From the object invariant on  $\chi_{\mathcal{F}}$  it then follows that the entries are some permutation of [1,0,1,0], which makes their sum total  $r_1 + r_2 = 2$ .

Similarly, we ignore  $\chi_{\mathcal{F}}$  while reasoning about calls to exchange via spec (7) (lines 7 and 9). As before, we know that the entry  $(r_1,v_1)$ , which is white in the left postcondition in line 9, must be gray on the right, and dually for  $(r_2,v_2)$ . In total, the history  $\chi_{\mathcal{E}}$  must contain both of the entries, but, by the invariant, it must also contain their twins. In the absence of any other interference, it therefore must be that  $(r_1,v_1)$  is a twin for  $(r_2,v_2)$ , i.e.,  $r_1=v_2$  and  $r_2=v_1$ , as line 11 expresses for the case of a successful exchange. The rest of the proof is then trivial.

The sketch relied on several important aspects of program verification in FCSL: (i) the invariants constraining  $\chi_{\mathcal{F}}$  and  $\chi_{\mathcal{E}}$  were preserved by the methods, (ii) upon joining the

threads, we can rely on the disjointness of history contributions of the two threads, in order to combine the thread-local views into a specification of the parent thread, and, (iii) we could guarantee the absence of the external interference.

The aspect (i) is a significant component of what it means to specify and verify a concurrent object. As we will show in Sections 3 and 6, defining a sufficiently strong object invariant, and then proving that it is indeed an invariant, i.e., that it is preserved by the implementation of the program, is a major part of the verification challenge. We will explain FCSL rules for parallel composition and hiding in Section 4, justifying the reasoning principles (ii) and (iii).

# 2.4 Specifying Non-linearizable Objects in Three Steps

As shown by Sections 2.1–2.3, our method for specifying and verifying non-linearizable concurrent objects and their clients boils down to the following three systematic steps.

Step 1 (§2.1): Define object-specific auxiliary state and its invariants. The auxiliary state will typically include a specific notion of abstract histories, recording whatever behavior is perceived as essential by the implementor of the object. To account for the variety of object-specific correctness conditions, we do not fix a specific shape for the histories. We do not restrict them to always record pairs of numbers (as in the exchanger), or record single numbers (as in flip2). The only requirement that we impose on auxiliary state in general, and on histories in particular, is that the chosen type of auxiliary state is an instance of the PCM algebraic structure [41], thus providing an abstract, and user-defined, notion of disjointness between self/other contributions.

Step 2 (§2.2): Formulate Hoare-style specifications, parametrized by interference, and verify them. This step provides a suitable "interface" for the methods of the concur-

rent object, which the clients use to reason, without knowing the details of the object and method implementations. Naturally, the interface can refer to the auxiliary state and histories defined in the previous step. When dealing with non-linearizable objects in FCSL, it is customary to formulate the spec in a subjective way (*i.e.*, using *self/other*, dually white/gray division between history entries) so that the specification has a way to refer to the effects of the interfering calls to the same object. The amount of interference can be later instantiated with more specific information, once we know more about the context of concurrent threads in which the specified program is being run.

Step 3 (§2.3): Restrict the interference when using object specs for verification of clients. Eventually, thread-local knowledge about effects of individual clients of one and the same object, should be combined into a cumulative knowledge about the effect of the composition. To measure this effect, one usually considers the object in a quiescent (interference-free) moment [38]. To model quiescent situations, FCSL provides a program-level constructor for hiding. In particular, hide e executes e, but statically prevents other threads from interfering with e, by making e's auxiliary history invisible. Program e's other contribution is fixed to be empty, thus modeling quiescence.

# 3. Verifying the Exchanger Implementation

We now proceed with more rigorous development of the invariants and specification for the exchanger data structure, necessary to verify its real-world implementation [14], which was so far elided from the overview of the approach.

The exchanger implementation is presented in ML-style pseudo-code in Figure 2. It takes a value v:A and creates an *offer* from it (line 2). An offer is a pointer p to two consecutive locations in the heap. The first location stores v, and the second is a "hole" which the interfering thread tries to fill with a matching value. The hole is drawn from the type  $\mathtt{hole} = \mathsf{U} \mid \mathsf{R} \mid \mathsf{M} \ w$ . Constructor U signals that the offer is unmatched; R that the exchanger retired (*i.e.*, withdrew) the offer, and does not expect any matches on it; and  $\mathsf{M} \ w$  that the offer has been matched with a value w.

The global pointer g stores the latest offer proposed for matching. The exchanger proposes p for matching by making g point to p via the atomic compare-and-set instruction CAS (line 3). We assume that CAS returns the value read, which can be used to determine if it failed or succeeded. If CAS succeeds, exchanger waits a bit, then checks if the offer has been matched by some w (lines 6, 7). If so, Some w is returned (line 7). Otherwise, the offer is retired by storing R into its hole (line 6). Retired offers remain allocated (thus, exchanger has a memory leak) in order to avoid the ABA problem, as usual in many concurrent structures [24, 46]. If the exchanger fails to link p into g in line 3, it deallocates

```

\mathtt{exchange}\;(v:A):\mathtt{option}\;A\;=\;\{

p \leftarrow \texttt{alloc}(v, \mathsf{U});

2

b \leftarrow \texttt{CAS}(g, \texttt{null}, p);

3

4

if b == null then

sleep(50);

5

x \leftarrow \text{CAS}(p+1, U, R);

6

7

if x is M w then return (Some w)

8

else return None

9

else

10

dealloc p;

11

cur \leftarrow \mathtt{read}\ g;

if cur == null then return None

12

13

x \leftarrow \texttt{CAS}(cur+1, \mathsf{U}, \mathsf{M}\ v);

14

CAS (g, cur, null);

15

if x is U then w \leftarrow \text{read } cur; \text{return } (\text{Some } w)

16

17

else return None}

```

Figure 2. Elimination-based exchanger procedure.

the offer p (line 10), and instead tries to match the offer cur that is current in g. If no offer is current, perhaps because another thread already matched the offer that made the CAS in line 3 fail, the exchanger returns None (line 12). Otherwise, the exchanger tries to make a match, by changing the hole of cur into M v (line 14). If successful (line 16), it reads the value w stored in cur that was initially proposed for matching, and returns it. In any case, it unlinks cur from g (line 15) to make space for other offers.

# 3.1 Step 1: Defining Auxiliary State and Invariants

To formally specify the exchanger, we decorate it with auxiliary state. In addition to histories, necessary for specifying the observable behavior, the auxiliary state is used for capturing the coherence constraints of the actual implementation, *e.g.*, with respect to memory allocation and management of outstanding offers. The state is subjective as described in Section 2: it keeps thread-local auxiliary variables that name the thread's private state (*self*), but also the private state of all other threads combined (*other*).

The subjective state of the exchanger for each thread in this example consists of three groups of two components: (1) thread-private heap  $h_{\rm S}$  of the thread, and of the environment  $h_{\rm O}$ , (2) a set of outstanding offers  $\pi_{\rm S}$  created by the thread, and by the environment  $\pi_{\rm O}$ , and (3) a time-stamped history of values  $\chi_{\rm S}$  that the thread exchanged so far, and dually  $\chi_{\rm O}$  for the environment. In Section 2, we illustrated subjectivity by means of histories, white we used white and gray entries, respectively, to describe what here we name  $\chi_{\rm S}$  and  $\chi_{\rm O}$ , respectively. Now we see that the dichotomy extends beyond histories, and this example requires the dichotomy applied to heaps, and to sets of offers as well. In addition to *self/other* components of heaps, permissions and histories, we also need shared (aka. *joint*) state consisting of two components: a heap  $h_{\rm J}$  of storing the offers that have been made, and

$<sup>^3</sup>$  In our mechanization, we simplify a bit by making p point to a pair instead.

a map  $m_{\rm J}$  of offers that have been matched, but not yet collected by the thread that made them.

Heaps, sets and histories are all PCMs under the operation of disjoint union, with empty heap/set/history as a unit. We overload the notation and write  $x \mapsto v$  for a singleton heap with a pointer x storing value v, and  $t \mapsto a$  for a singleton history. Similarly, we apply disjoint union  $\cup$  and subset  $\subseteq$ , to all three types uniformly.

We next describe how the exchanger manipulates the above variables. First,  $h_J$  is a heap that serves as the "staging" area for the offers. It includes the global pointer g. Whenever a thread wants to make an offer, it allocates a pointer p in  $h_S$ , and then tries to move p from  $h_S$  into  $h_J$ , simultaneously linking g to p, via the CAS in line 3 of Figure 2.

Second,  $\pi_S$  and  $\pi_O$  are sets of offers (hence, sets of pointers) that determine offer ownership. A thread that has the offer  $p \in \pi_S$  is the one that created it, and thus has the *sole* right to retire p, or to collect the value that p was matched with. Upon collection or retirement, p is removed from  $\pi_S$ .

Third,  $\chi_S$  and  $\chi_O$  are exchanger-specific histories, each mapping a time-stamp (isomorphic to nats), to a pair of exchanged values. A singleton history  $t\mapsto (v,w)$  symbolizes that a thread having this singleton as a subcomponent of  $\chi_S$ , has exchanged v for w at time t. As we describe below, the most important invariant of the exchanger is that each such singleton is matched by a "symmetric" one to capture that another thread has *simultaneously* exchanged w for v. Classical linearizability cannot express this simultaneous behavior, making the exchanger non-linearizable.

Fourth,  $m_J$  is a map storing the offers that were matched, but not yet acknowledged and collected. Thus, dom  $m_J = \pi_S \cup \pi_O$ . A singleton entry in  $m_J$  has the form  $p \mapsto (t,v,w)$  and denotes that offer p, initially storing v, was matched at time t with w. A singleton entry is entered into  $m_J$  when a thread on the one end of matching, matches v with w. Such a thread also places the twin entry  $\bar{t} \mapsto (w,v)$ , with inverted order of v and w, into its own private history  $\chi_S$ , where:

$$\bar{t} = \left\{ \begin{array}{ll} t+1 & \text{if } t \text{ is odd} \\ t-1 & \text{if } t>0 \text{ and } t \text{ is even} \end{array} \right.$$

For technical reasons, 0 is not a valid time-stamp, and has no distinct twin. The pending entry for p resides in  $m_J$  until the thread that created the offer p decides to "collect" it. It removes p from  $m_J$ , and simultaneously adds the entry  $t\mapsto (v,w)$  into its own  $\chi_S$ , thereby logically completing the exchange. Since twin time-stamps are consecutive integers, a history cannot contain entries between twins.

Thus, two twin entries in the combined history including  $\chi_{S}$ ,  $\chi_{O}$  and  $m_{J}$ , jointly represent a single exchange, as if it occurred atomically. For example, the entries  $1\mapsto (v_{1},w_{1})$  and  $2\mapsto (w_{1},v_{1})$  will encode the end-points of the first exchange; the entries  $3\mapsto (v_{2},w_{2})$  and  $4\mapsto (w_{2},v_{2})$  will encode the end-points of the second exchange, etc., the entries at timestamps t and t+1, for odd t, will encode the end-points of the  $\frac{t+1}{2}$ -th exchange. Concurrency-aware

histories [21] capture this by making the ends of an exchange occur as simultaneous events. We capture it via twin timestamps. More formally, consider  $\chi = \chi_S \cup \chi_O \cup \|m_J\|$ . Then, the exchanger's main invariant is that  $\chi$  always contains matching twin entries:

$$t \mapsto (v, w) \subseteq \chi \iff \bar{t} \mapsto (w, v) \subseteq \chi$$

(9)

Here  $||m_J||$  is the collection of all the entries in  $m_J$ . That is,  $||\emptyset|| = \emptyset$ , and  $||p \mapsto (t, v, w) \cup m_J'|| = t \mapsto (v, w) \cup ||m_J'||$ .

In our implementation, we prove that atomic actions, such as CAS, preserve the invariant, therefore, the whole program, being just a composition of actions, doesn't violate it.

# 3.2 Step 2: Hoare-style Specification of Exchanger

We can now give the desired formal Hoare-style spec.

The precondition says that the exchanger starts with the empty private heap  $h_S$ , set of offers  $\pi_S$  and history  $\chi_S$ ; hence by framing, it can start with any value for these components.<sup>4</sup> The logical variable  $\eta$  names the initial history of all threads,  $\chi_O \cup \|m_J\|$ , which may grow during the call, thus, we use subset instead of equality to make the precondition stable under other threads adding entries to  $\chi_O$  or  $m_J$ .

In the postcondition, the self heap  $h_S$  and the set of offers  $\pi_S$  didn't change. Hence, if exchange made an offer during its execution, it also collected or retired it by the end. The history  $\eta$  is still a subset of the ending value for  $\chi_O \cup \|m_J\|$ , signifying that the environment history only grows by interference. We will make a crucial use of this part of the spec when verifying a client of the exchanger in Section 5.

If the exchange fails (i.e., res is None), then  $\chi_S$  remains empty. If it succeeds (either in line 7 or line 16 in Figure 2), i.e., if the result res is Some w, then there exists a time-stamp t, such that self-history  $\chi_S$  contains the entry  $t \mapsto (v,w)$ , symbolizing that v and w were exchanged at time t.

Importantly, the postcondition implies, by invariant (9), that in the success case, the twin entry  $\bar{t}\mapsto (w,v)$  must belong to  $\chi_0\cup \|m_J\|$ , *i.e.*, another thread matched the exchange (this was made explicit by the spec (7)). Moreover, the exchange occurred after the call to exchange: whichever  $\eta$  we chose in the pre-state, both t and  $\bar{t}$  are larger than the last time-stamp in  $\eta$ .

The proof outline for the exchanger is available in Appendix A. In Section 5, after introducing necessary FCSL background, we will illustrate *Step 3* of our method and show how to employ the subjective Hoare spec (10) for modular verification of a concurrent client.

<sup>&</sup>lt;sup>4</sup> Framing in FCSL is similar to that of separation logic, allowing extensions to the initial state that remain invariant by program execution. In FCSL, however, framing applies to any PCM-valued state component (*e.g.*, heaps, histories, *etc.*), whereas in separation logic, it applies just to heaps.

# 4. Background on FCSL

In order to formally present *Step 3* of our method, we first need to introduce some important parts of FCSL.

A Hoare specification in FCSL has the form  $\{P\}$  e  $\{Q\}$  @ $\mathcal{R}$ . P and Q are pre- and postcondition for partial correctness, and  $\mathcal{R}$  defines the *shared resource* on which e operates. The latter is a state transition system describing the invariants of the state (real and auxiliary) and atomic operations that can be invoked by the threads that simultaneously operate on that state. We elide the transition system aspect of resources here, and refer to [35] for detailed treatment.

An important secondary role of a resource is to declare the variables that P and Q may scope over. For example, in the case of exchanger, we use the variables  $h_{\rm S}, \pi_{\rm S}, \chi_{\rm S}, h_{\rm O}, \pi_{\rm O}, \chi_{\rm O}$ , and  $h_{\rm J}, m_{\rm J}$ . The mechanism by which the variables are declared is as follows. Underneath, a resource comes with only three variables:  $a_{\rm S}, a_{\rm O}$  and  $a_{\rm J}$  standing for abstract self state, other state, and shared (joint) state, but the user can pick their types depending on the application. In the case of exchanger,  $a_{\rm S}$  and  $a_{\rm O}$  are triples containing a heap, an offer-set and a history. The variables we used in Section 2 are projections out of such triples:  $a_{\rm S} = (h_{\rm S}, \pi_{\rm S}, \chi_{\rm S})$ , and  $a_{\rm O} = (h_{\rm O}, \pi_{\rm O}, \chi_{\rm O})$ . Similarly,  $a_{\rm J} = (h_{\rm J}, m_{\rm J})$ .

It is essential that  $a_S$  and  $a_O$  have a common type exhibiting the algebraic structure of a PCM, under a partial binary operation  $\cup$ . PCMs give a way, generic in  $\mathcal{R}$ , to define the inference rule for parallel composition.

$$\frac{\{P_1\} e_1 \{Q_1\}@\mathcal{R} \quad \{P_2\} e_2 \{Q_2\}@\mathcal{R}}{\{P_1 \circledast P_2\} e_1 \parallel e_2 \{[\mathsf{res}.1/\mathsf{res}]Q_1 \circledast [\mathsf{res}.2/\mathsf{res}]Q_2\}@\mathcal{R}}$$

(11)

Here, \* is defined as follows.

$$(P_1 \circledast P_2)(a_S, a_J, a_O) \iff \exists x_1 \ x_2. \ a_S = x_1 \cup x_2, P_1(x_1, a_J, x_2 \cup a_O), P_2(x_2, a_J, x_1 \cup a_O)$$

Thereby, when a parent thread forks  $e_1$  and  $e_2$ , then  $e_1$  becomes part of the environment for  $e_2$ , and vice-versa. This is so because the *self* component  $a_S$  of the parent is split into  $x_1$  and  $x_2$ ;  $x_1$  becomes the *self* part of  $e_1$ , but  $x_2$  is added to the *other* part  $a_O$  of  $e_1$  (and symmetrically for  $e_2$ ).

To reason about quiescent moments, we use one more constructor of FCSL: hiding. The program hide e operationally executes e, but logically installs a resource within the scope of e. In the case of the exchanger, hide e starts only with private heaps  $h_{\rm S}$  and  $h_{\rm O}$ , then takes a chunk of heap out of  $h_{\rm S}$  and "installs" an exchanger in this heap, allowing the threads in e to exchange values. hide e is quiescent wrt. exchanger, as the typechecker will prevent composing hide e with threads that want to exchange values with e.

The auxiliaries  $\pi_S$ ,  $\chi_S$ ,  $\pi_O$ ,  $\chi_O$ , and  $h_J$ ,  $m_J$ , belonging to the exchanger (denoted as resource  $\mathcal{E}$ ) are visible within hide, but outside, only  $h_S$  persists (denoted as a resource  $\mathcal{P}$  for private state). We elide the general hiding rule [35], and just show the special case for the exchanger.

```

\{P\}\ e\ \{Q\}@\mathcal{E}

```

```

\{h_{\mathsf{S}} = \Phi_1(h_{\mathsf{J}}), \Phi_1(P)\}\ hide e\ \{\exists \Phi_2. \ h_{\mathsf{S}} = \Phi_2(h_{\mathsf{J}}), \Phi_2(Q)\}@\mathcal{P} (12)

```

Read bottom-up, the rule says that we can install the exchanger  $\mathcal E$  in the scope of a thread that works with  $\mathcal P$ , but then we need substitutions  $\Phi_1$  and  $\Phi_2$ , to map variables of  $\mathcal E$  ( $h_S, \pi_S, \chi_S, etc$ ) to values expressed with variables from  $\mathcal P$  ( $h_S$  and  $h_O$ ).  $\Phi_1$  is an initial such substitution (user provided), and the rule guarantees the existence of an ending substitution  $\Phi_2$ . The substitutions have to satisfy a number of side conditions, which we elide here for brevity. The most important one is that *other* variable  $a_O = (h_O, \pi_O, \chi_O)$  is fixed to be the PCM unit (*i.e.*, a triple of empty sets). Fixing  $a_O$  to unit captures that hide protects e from interference.

At the beginning of hide e, the private heap equals the value that  $\Phi_1$  gives to  $h_J$  ( $h_S = \Phi_1(h_J)$ ). In other words, the hide rule takes the private heap of a thread, and makes it shared, *i.e.*, gives it to the  $h_J$  component of  $\mathcal{E}$ . Upon finishing, hide e makes  $h_J$  private again.

In the subsequent text we elide the resources from specs.

# 5. Verifying Exchanger's Client

We next illustrate how the formally specified exchanger from Section 3 can be used by real-world client programs, and how the *other* component, asserted by the spec to satisfy  $\eta \subseteq \chi_O \cup \|m_J\|$ , is crucial for their verification. We emphasize that the proof of the client does not see the implementation details, which are hidden by the spec (10).

While simple, our client is realistic, and has been used in java.util.concurrent [14]. It is defined as follows. First, the exchanger loops until it exchanges the value.

```

exchange' (v:A):A=\{ w'\leftarrow \text{exchange }v; if w' is Some w then return w else exchange' v \}

```

Next, exchange' is iterated to exchange a sequence in order, appending the received matches to an accumulator.

```

\begin{split} & \texttt{ex\_seq}\;(vs,ac:\texttt{seq}\;A):\texttt{seq}\;A = \{ & \texttt{if}\;\;vs\;\; \texttt{is}\;\;v::vs'\;\; \texttt{then} \\ & w \leftarrow \texttt{exchange'}\;v;\;\; \texttt{ex\_seq}\;(vs',\texttt{snoc}\;ac\;w) \\ & \texttt{else}\;\; \texttt{return}\;ac\; \} \end{split}

```

Our goal is to prove, via (10), that the parallel composition

$$e = \texttt{ex\_seq}(vs_1, \texttt{nil}) \parallel \texttt{ex\_seq}(vs_2, \texttt{nil})$$

exchanges  $vs_1$  and  $vs_2$ , *i.e.*, returns the pair  $(vs_2, vs_1)$ . This holds only under the assumption that e runs without interference (*i.e.*, quiescently), so that the two threads in e have no choice but to exchange the values between themselves.

We make the quiescence assumption explicit using the FCSL hide constructor, as described in Section 4. Thus, we

establish the following Hoare triple:

```

\{h_{\rm S}=g\mapsto {\rm null}\}\ \ {\rm hide}\ \ e\ \ \{g\in {\rm dom}\ h_{\rm S}, {\rm res}=(vs_2,vs_1)\} \eqno(13)

```

It says that we start with a heap where g stores null, and end with a possibly larger heap (due to the memory leak), but with the result  $(vs_2, vs_1)$ . The auxiliaries  $\pi_S$ ,  $\pi_O$ ,  $\eta_S$ ,  $\eta_O$ ,  $h_J$ ,  $m_J$  are visible inside hide, but outside, only  $h_S$  persists.

**Explaining the verification.** We illustrate the verification by listing the specs of selected subprograms. First, the spec of exchange' easily derives from (10) by removing the now-impossible failing case.

```

\begin{cases} h_{\mathsf{S}} = \emptyset, \pi_{\mathsf{S}} = \emptyset, \chi_{\mathsf{S}} = \emptyset, \eta \subseteq \chi_{\mathsf{O}} \cup \|m_{\mathsf{J}}\| \} \\ & \mathsf{exchange'}\ v \\ \begin{cases} h_{\mathsf{S}} = \emptyset, \pi_{\mathsf{S}} = \emptyset, \eta \subseteq \chi_{\mathsf{O}} \cup \|m_{\mathsf{J}}\|, \\ \exists t.\ \chi_{\mathsf{S}} = t \mapsto (v,\mathsf{res}), \mathsf{last}(\eta) < t, \bar{t} \end{cases}

```

Next, ex\_seq has the following spec:

$$\begin{cases} h_{\mathsf{S}} = \emptyset, \pi_{\mathsf{S}} = \emptyset, \chi_{\mathsf{S}} = \emptyset \rbrace \\ & \mathsf{ex\_seq} \ (vs, \mathsf{nil}) \end{cases}$$

$$\begin{cases} \exists ts. \ h_{\mathsf{S}} = \emptyset, \pi_{\mathsf{S}} = \emptyset, \chi_{\mathsf{S}} = \mathsf{zip} \ ts \ vs \ \mathsf{res}, \\ \mathsf{grows\_notwins} \ ts, \mathsf{zip} \ \overline{ts} \ \mathsf{res} \ vs \subseteq \chi_{\mathsf{O}} \cup \|m_{\mathsf{J}}\| \end{cases}$$

Here, ts is a list of time-stamps, and  $zip\ ts\ vs\ ws$  joins up the singleton histories  $t\mapsto (v,w)$ , for each t,v,w drawn, in order, from the lists ts,vs,ws. The spec says that at the time-stamps from ts, ex\_seq exchanged the elements of vs for those of res. That ts is increasing and contains no twins, follows from the spec of exchange, which says that the time-stamps t and  $\bar{t}$  that populate ts and  $\bar{t}s$ , are larger than anything in  $\eta$ , and thus only grow with iteration. From the same postcondition, it follows that  $\chi_O \cup \|m_J\|$  contains all the twin exchanges, by invariant (9), as commented in Section 2 about the spec for exchange.

Next, by the FCSL parallel composition rule (Section 4):

```

\begin{aligned} \{h_{\mathsf{S}} &= \emptyset, \pi_{\mathsf{S}} = \emptyset, \chi_{\mathsf{S}} = \emptyset\} \\ &= \mathsf{ex\_seq} \; (vs_1, \mathsf{nil}) \parallel \mathsf{ex\_seq} \; (vs_2, \mathsf{nil}) \\ &= \mathsf{d}ts_1 \; ts_2. \; \mathsf{grows\_notwins} \; ts_1, \; \mathsf{grows\_notwins} \; ts_2, \\ &h_{\mathsf{S}} &= \emptyset, \pi_{\mathsf{S}} = \emptyset, \chi_{\mathsf{S}} = \mathsf{zip} \; ts_1 \; vs_1 \; \mathsf{res}.1 \; \cup \; \mathsf{zip} \; ts_2 \; vs_2 \; \mathsf{res}.2, \\ &= \mathsf{zip} \; \overline{ts_1} \; \mathsf{res}.1 \; vs_1 \subseteq \mathsf{zip} \; ts_2 \; vs_2 \; \mathsf{res}.2 \; \cup \; \chi_{\mathsf{O}} \cup \|m_{\mathsf{J}}\|, \\ &= \mathsf{zip} \; \overline{ts_2} \; \mathsf{res}.2 \; vs_2 \subseteq \mathsf{zip} \; ts_1 \; vs_1 \; \mathsf{res}.1 \; \cup \; \chi_{\mathsf{O}} \cup \|m_{\mathsf{J}}\|. \end{aligned} \end{aligned}

```

To explain: ts and res from the left and right ex\_seq threads become  $ts_1$ ,  $ts_2$ , res.1 and res.2, respectively. The values of each self component  $h_S$ ,  $\pi_S$ ,  $\chi_S$  from the two threads are joined into the self component of the composition. At the same time, the *other* component  $\chi_O$  of the left (resp. right) thread equals the sum of  $\chi_S$  of the right (resp. left) thread, and the  $\chi_O$  of the composition. This formalizes the intuition that upon forking, the left thread becomes part of the environment for the right thread, and vice-versa.

The postcondition says that the self history of e contains both zip  $ts_1 \ vs_1 \ res.1$  and zip  $ts_2 \ vs_2 \ res.2$ . Thus,  $vs_1$  is exchanged for res.1, and  $vs_2$  for res.2. But we further want

```

\begin{array}{c|c} & 1 & \mathtt{getAndInc}() : \mathtt{nat} = \{\\ 2 & b \leftarrow \mathtt{flip}(bal);\\ 3 & \mathtt{res} \leftarrow \mathtt{fetchAndAdd2}(c_b);\\ 4 & \mathbf{return}\ \mathtt{res}\,\} \end{array}

```

Figure 3. Simple counting network

to derive res. $1 = vs_2$  and res. $2 = vs_1$ , *i.e.*, the lists are exchanged *for each other*, in the absence of interference.

We next explain how this desired property follows for hide e, from the two inequalities in e's postcondition

$$\operatorname{zip} \overline{ts_1} \operatorname{res}.1 \ vs_1 \subseteq \operatorname{zip} ts_2 \ vs_2 \operatorname{res}.2 \ \cup \chi_{\mathsf{O}} \cup \|m_{\mathsf{J}}\|, \quad (14)$$

$$\operatorname{zip} \overline{ts_2} \operatorname{res}.2 \ vs_2 \subseteq \operatorname{zip} ts_1 \ vs_1 \operatorname{res}.1 \ \cup \chi_{\mathsf{O}} \cup \|m_{\mathsf{J}}\|. \quad (15)$$

Notice that (14) and (15) are ultimately instances of the conjunct  $\eta \subseteq \chi_O \cup ||m_J||$  that was part of the specification (10), thereby justifying the use of subjective *other* variables.

We know that dom  $m_J = \pi_S \cup \pi_O$  (from Section 2), that  $\pi_S = \emptyset$  (from e's postcondition), and that by hiding,  $\pi_O = \chi_O = \emptyset$ . Thus, towards deriving the postcondition of hide e, we simplify (14) and (15) into:

$$zip \overline{ts_1} res.1 \ vs_1 \subseteq zip \ ts_2 \ vs_2 res.2$$

$zip \overline{ts_2} res.2 \ vs_2 \subseteq zip \ ts_1 \ vs_1 res.1$

Because  $ts_1$  and  $ts_2$  are increasing lists of time-stamps, and contain no twins, the above implies  $ts_2 = \overline{ts_1}$ . Hence:

$$zip \overline{ts_1} res.1 vs_1 = zip ts_2 vs_2 res.2$$

and thus res.  $1 = vs_2$ ,  $vs_1 = \text{res.} 2$ . We omit the remaining technical argument that explains how the heap  $h_J$ , with the pointer g, is folded into  $h_S$ , which ultimately obtains (13).

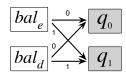

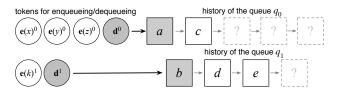

# 6. Specifying Counting Networks

We now show how to use subjective histories to specify another class of non-linearizable objects—counting networks. Counting networks are a special case of balancing networks introduced by Aspnes et al. [4], themselves building on sorting networks [3], aimed to implement concurrent counters in a way free from synchronization bottlenecks. The key idea is to decompose the workload between several counters, so that each of them is responsible for a disjoint set of values. A thread trying to increment first approaches the balancer, which is a logical "switch" that "directs" the thread, i.e., provides it with the address of the counter to increment. The balancers make counting networks' operations non-linearizable, as in the presence of interference the results of increments might be observed out of order.

Figure 3 presents a schematic outline and a pseudocode implementation of a counting network with a single balancer. The implementation contains three pointers: the balancer bal, which stores either 0 or 1, thus directing threads to the shared pointers  $c_0$  or  $c_1$ , which count the even and odd values, respectively. Threads increment by calling getAndInc, which works as follows. It first atomically changes the bit value of the balancer via a call to atomic operation flip (line 2). The flip operation returns the *previous* value b of the balancer as a result, thus determining which of the counters,  $c_0$  or  $c_1$ , should be incremented. The thread proceeds to atomically add 2 to the value of  $c_b$  via fetchAndAdd2 (line 3). The old value of  $c_b$  is returned as the result of the procedure.

Assuming that  $c_0$  and  $c_1$  are initialized with 0 and 1, it is easy to see that in a single-threaded program, the network will behave as a conventional counter; that is, consecutive invocations of getAndInc return consecutive nats. However, in the concurrent setting, getAndInc may return results out of order, as follows.

Example 6.1. Consider two threads,  $T_1$  and  $T_2$  operating on the network initialized with  $bal\mapsto 0,\ c_b\mapsto b.\ T_1$  calls getAndInc and executes its line 2 to set bal to 1. It gets suspended, so  $T_2$  proceeds to execute lines 2 and 3, therefore setting bal back to 0 and returning 1. While  $T_1$  is still suspended,  $T_2$  calls getAndInc again, gets directed to  $c_0$ , and returns 0, after it has just returned 1.

This out-of-order behavior, however, is not random, and can be precisely characterized as a function of the number of threads operating on the network [2, 28]. In the rest of this section and in Section 7, we show how to capture such bounds in the spec using auxiliary state of (subjective) histories in a client-sensitive manner. As a form of road map, we list the desired requirements for the spec of getAndInc, adapting the design goals of the criteria, such as QC, QQC and QL [2, 4, 28], which we will proceed to verify formally, following *Step 1* and *Step 2* of our approach, and then employ in client-side reasoning via *Step 3*:

- **R1:** Two different calls to getAndInc should return distinct results (*strong concurrent counter semantics*).

- **R2:** The results of calls to getAndInc, separated by a period of quiescence (*i.e.*, absence of interference), should appear in their sequential order (*quiescent consistency*).

- R3: The results of two sequential calls  $C_1$  and  $C_2$ , in a single thread should be out of order by no more than 2N, where N is the number of interfering calls that overlap with  $C_1$  and  $C_2$  (quantitative quiescent consistency).

# 6.1 Step 1: Counting Network's Histories and Invariants

To formalize the necessary invariants, we elaborate the counting network with auxiliary state: *tokens* (isomorphic to nats) and novel *interference-capturing histories*.

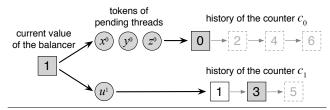

Figure 4. Tokens and histories of the simple network

A token provides a thread that owns it with the right to increment an appropriate counter [4]. In our example, a thread that performs the flip in line 2 of getAndInc will be awarded a token which it can then spend to execute fetchAndAdd2. Thus, any individual token represents a "pending" call to getAndInc, and the set of unspent tokens serves as a bound on the out-of-order behavior that the network exhibits. We introduce auxiliary variables for the held tokens:  $\tau_S$  keeps the tokens owned by the self thread, with its even and odd projections  $\tau_S^0$  and  $\tau_S^1$ , such that  $\tau_S = \tau_S^0 \cup \tau_S^1$ , administering access to  $c_0$  and  $c_1$ , respectively. Similarly,  $\tau_O$ , featuring the same projections, keeps the tokens owned by the other thread. We abbreviate  $\tau^i = \tau_S^i \cup \tau_O^i$  for i = 0, 1.

Figure 4 illustrates a network with three *even* tokens:  $x^0, y^0, z^0 \in \tau^0$ , held by threads that will increment  $c_0$ , and one *odd* token  $u^1 \in \tau^1$ , whose owner will increment  $c_1$ .

A history of the counting network is an auxiliary finite map, consisting of entries of the form  $t\mapsto (\hat\iota,z)$ . Such an entry records that the value t has been written into an appropriate counter  $(c_0 \text{ or } c_1, \text{ depending on the parity of } t)$ , at the moment when  $\tau^0$  and  $\tau^1$  held values of  $\hat\iota$ 's even/odd projections  $\hat\iota^0$  and  $\hat\iota^1$ , respectively. Moreover, in order to write t into a counter, the token z was spent by the thread. We will refer to z as the *spent* token. Notice that the entries in the history contain tokens held by both self and other threads. Thus, a history captures the behavior of a thread subjectively, i.e., as a function of the interfering threads' behavior.

Similarly to tokens, network histories are represented by the auxiliary variables  $\chi_S$ , tracking counter updates (even and odd) performed by the *self* thread, and dually  $\chi_O$  for the *other* thread. We abbreviate  $\chi^i = \chi^i_S \cup \chi^i_O$  for i = 0, 1.

Figure 4 illustrates a moment in network's history and how it relates to the state of the counters. Only 0 has been written to  $c_0$  so far (upon initialization), hence  $\chi^0$  only contains an entry for t=0 (we ignore at the moment the *contents* of the history entries). On the other hand,  $\chi^1$  has entries for 1 and 3, because after initialization, one thread has increased  $c_1$ . The gray boxes indicate that 0 and 3 are the current values of  $c_0$  and  $c_1$ , and thus also the latest entries in  $\chi^0$  and  $\chi^1$ , respectively. In particular, these values will be returned by the next invocations of fetchAndAdd2. The dashed boxes correspond to the entries to be contributed by the currently running threads holding tokens  $x^0$ ,  $y^0$ ,  $z^0$ ,  $u^1$ .

In addition to  $\tau$  and  $\chi$  which come in flavors private to *self* and *other* threads, we require the following shared variables:

<sup>&</sup>lt;sup>5</sup> In the counting network from Figure 3, the balancer itself might seem like a contention point. However, the flip operation is much less expensive than CAS as a synchronization mechanism. The performance can be further improved by constructing a *diffracting tree* of several balancers [24, §12.6], but we do not consider diffracting trees here.

(1)  $h_J$  for the joint heap of the network, and (2)  $b_J$ ,  $n_J^0$  and  $n_I^1$  for the contents of bal,  $c_o$  and  $c_1$ , respectively.

*Invariants of the counting network* The main invariant of the network relates the number of tokens, the size of histories and the value of the balancer:

$$|\chi^0| + |\tau^0| = |\chi^1| + |\tau^1| + b_J$$

(16)

The equation formalizes the intuition that out-of-order anomalies of the counting network appear if one of the two counters is too far ahead of the other one. The invariant (16) provides a bound on such a situation. One counter can get ahead temporarily, but then there must be a number of threads waiting to spend their tokens on the other counter. Thus, the other counter will eventually catch up.

The approaches such as quiescent and quantitative quiescent consistency describe this situation by referring to the number of *unmatched* call events in an event history [10, 28]. In contrast, we formalize this property via auxiliary state: the sets of tokens  $\hat{\iota}$  recorded in the entry for the number t determine the environment's capability to add new history entries, and thus "run ahead" or "catch up" after t has been returned. The other invariants of the counting network are as follows:

- (i)  $h_{\mathsf{J}} = bal \mapsto b_{\mathsf{J}} \cup c_0 \mapsto n_{\mathsf{J}}^0 \cup c_1 \mapsto n_{\mathsf{J}}^1$ .

- (ii) The histories contain disjoint time-stamps.

- (iii) The history  $\chi^0$  (resp.  $\chi^1$ ) contains *all* even (resp. odd) values in  $[0, n_J^0]$  (resp.  $[1, n_J^1]$ ). This ensures that  $n_J^0$  and  $n_J^1$  are the last time-stamps in  $\chi^0$  and  $\chi^1$ , respectively.

- (iv)  $\tau^{\bar{0}}$ ,  $\tau^1$  and spent  $(\chi_S \cup \chi_O)$  contain mutually disjoint tokens, where spent  $(t \mapsto (\hat{\iota}, z) \cup \chi') = \{z\} \cup \text{spent } \chi'$ , and spent  $\emptyset = \emptyset$ . In other words, a spent token never appears among the "alive" ones  $(i.e., \text{in } \tau^0 \cup \tau^1)$ .

- (v)  $t \mapsto (\hat{\iota}, z) \subseteq \chi_{\mathsf{S}} \cup \chi_{\mathsf{O}} \implies z \in \hat{\iota}$ .

- (vi) For any t,  $\hat{\iota}$ , z:

•

$$t\mapsto (\hat{\iota},z)\subseteq \chi^0 \implies t+2\,|\hat{\iota}\cap\tau^0| < n_{\mathtt{J}}^1+2\,|\hat{\iota}\cap\tau^1|+2,$$

and

•

$$t \mapsto (\hat{\iota}, z) \subseteq \chi^1 \implies t + 2|\hat{\iota} \cap \tau^1| < n_1^0 + 2|\hat{\iota} \cap \tau^0| + 2$$

.

The invariant (vi) provides quantitative information about the network history by relating the actual  $(n_J^0, n_J^1)$  and the past (t) counter values, via the current amount of interference  $(\tau)$  and the snapshot interference  $(\hat{\iota})$ . To explain (vi), we resort to the intuition provided by the following equality, which, however, being *not quite valid*, cannot be used as an invariant, as we shall see. Focusing on the first clause in (vi), if  $t \mapsto (\hat{\iota}, z) \subseteq \chi^0$ , then, intuitively:

$$t+2|\hat{\iota}^{0} \setminus \tau^{0}|+2|\hat{\iota} \cap \tau^{0}|=n_{J}^{1}+2|\hat{\iota} \cap \tau^{1}|+(2b_{J}-1)$$

The equality says the following. When t is snapshot from  $c_0$  and placed into the history  $\chi^0$ , the set of outstanding even tokens was  $\hat{\iota}^0$ . By the present time,  $c_0$  has been increased  $|\hat{\iota}^0 \setminus \tau^0|$  times, each time by 2, thus  $n_J^0 = t+2|\hat{\iota}^0 \setminus \tau^0|$ . What is left to add to  $c_0$  to reach the *period of quiescence*, when no threads interfere with us, is  $2|\hat{\iota} \cap \tau^0|$ . Similar reasoning applies to  $c_1$ . It is easy to see at the period of quiescence,  $c_0$  and  $c_1$  differ by  $2b_J - 1$ ; that is, the counter pointed to

```

\begin{cases} \tau_{S} = \emptyset, \chi_{S} = \eta_{S}, \eta_{O} \subseteq \chi_{O}, \\ \iota_{O} \subseteq \tau_{O} \cup (\text{spent } \chi_{O} \setminus \text{spent } \eta_{O}), \mathcal{I} \eta_{O} \iota_{O} \end{cases}

\text{getAndInc()}

\begin{cases} \exists \hat{\iota} \ z. \ \tau_{S} = \emptyset, \chi_{S} = \eta_{S} \cup (\text{res} + 2) \mapsto (\hat{\iota}, z), \\ \eta_{O} \subseteq \chi_{O}, \iota_{O} \subseteq \tau_{O} \cup (\text{spent } \chi_{O} \setminus \text{spent } \eta_{O}), \\ \text{last } (\eta_{S} \cup \eta_{O}) < \text{res} + 2 + 2 |\hat{\iota} \cap \iota_{O}|, \\ \text{ResPast } (\eta_{S} \cup \eta_{O}) \text{ res } \hat{\iota} \ z, \mathcal{I} \eta_{O} \iota_{O} \end{cases}

(17)

```

**Figure 5.** Hoare-style spec of a simple counting network.

by bal is behind by 1. However, the equality is invalid, as  $b_J$  can be read off only in the present, whereas the "intuitive" reasoning behind the equality requires a value of  $b_J$  from a quiescent period in the future. Hence, in order to get a valid property, we bound  $2b_J - 1$  by 2. For simplicity, we even further weaken the bounds by dropping  $|\hat{\iota}^0 \setminus \tau^0|$  to obtain (vi); as it will turn out, even such a simpler bound will suffice for proving **R1–R3**.

Allowed changes in the counting network The state of the counting network (auxiliary and real) can be changed in two possible ways by concurrent threads. These changes formalize the way the atomic operations flip and fetchAndAdd2 from Figure 3 (b) work with auxiliary state. Flipping alters the bit value  $b_J$  of bal to the complementary one,  $1 - b_J$ . It also generates a token z (of parity  $b_1$ ) and stores it into  $\tau_5$ . The token is fresh, i.e., distinct from all alive and spent tokens in  $\tau_S \cup \tau_O \cup \text{spent } (\chi_S \cup \chi_O)$ . *Incrementation* spends a token z from  $\tau_S$ , and depending on its i, it atomically increases the value  $n_1^i$  of  $c_i$  by two, while simultaneously removing z from  $\tau_S$  (thus, the precondition is that  $z \in \tau_S$ ). It also adds the entry  $(n_{\rm J}^i+2)\mapsto (\tau^0\cup\tau^1,z^i)$  to  $\chi_{\rm S}$ , thus snapshoting the values of  $\tau^0$  and  $\tau^1$ . It is easy to check that both these allowed changes preserve the state-space invariants (16), (i)–(vi), and that their effect on real state (with auxiliary state erased) are those of flip and fetchAndAdd2.

#### 6.2 Step 2: a Hoare Spec for getAndInc

Figure 5 provides a Hoare-style spec for getAndInc, verified in our proof scripts. We use the logical variable  $\iota$  and its variants to range over token sets, and  $\eta$  to range over histories.

The precondition starts with an empty token set  $(\tau_S = \emptyset)$ , and hence by framing, any set of tokens. The initial self-history  $\chi_S$  is set to an arbitrary  $\eta_S$ .<sup>6</sup> The precondition records the *other* components of the initial state as follows. First,  $\eta_O$  names (a subset of)  $\chi_O$ , to make it stable under interference, as in Section 2. Next, we use  $\iota_O$  to name the (subset of) initially live tokens  $\tau_O$ . However, as  $\tau_O$  may shrink due to other threads spending tokens, simply writing  $\iota_O \subseteq \tau_O$  is unstable. Instead, we write  $\iota_O \subseteq \tau_O \cup (\text{spent } \chi_O \setminus \text{spent } \chi_O \setminus \text{sp$

<sup>&</sup>lt;sup>6</sup> Alternatively, we could have also taken  $\chi_S = \emptyset$ , but the clients will require generalizing to  $\chi_S = \eta_S$  by the FCSL's frame rule [41]. To save space and simplify the discussion, we immediately frame wrt. the auxiliary  $\chi_S$ . Our examples do not require such client-side framing wrt.  $\tau_S$ .

spent  $\eta_O$ ) to account for the tokens spent by other threads as well. The set  $\tau_O \cup$  (spent  $\chi_O \setminus$  spent  $\eta_O$ ) only grows under interference, as new live tokens are generated, or old live tokens are spent, making the inclusion of  $\iota_O$  stable. Indeed, one cannot take *any* arbitrary  $\eta_O$  and  $\iota_O$  to name the *other* components of the initial state. Therefore, we constrain these two variables by the invariant  $\mathcal{I}$ , that relates them to the *self*-components of the actual state and to each other according to the invariants (ii)–(vi). This is natural, since, as we will see in Section 7, all clients instantiate  $\eta_O$  and  $\iota_O$  with the *other*-components of the actual pre-state, respecting (ii)–(vi).

The postcondition asserts that the final token set  $\tau_S$  is also empty (*i.e.*, the token that getAndInc generates by flip, is spent by the end). The history  $\chi_S$  is increased by an entry (res + 2)  $\mapsto$  ( $\hat{\iota},z$ ), corresponding to writing the value of the result (plus two) into one of the network's counters, snapshoting the tokens of that moment into  $\hat{\iota}$ , and spending the token z on the write.  $\eta_O$  is a subset of the new value of  $\chi_O$ , and  $\iota_O$  is a subset of the new value of  $\tau_O \cup$  (spent  $\chi_O \setminus$  spent  $\eta_O$ ), by the already discussed stability.

The next inequality describes where the entry for res +2 is placed wrt. the pre-state history  $\eta=\eta_{\rm S}\cup\eta_{\rm O}$ .  $\eta$  may have gaps arising due to out-of-order behavior of the network, and res +2 may fill one such gap. However, there is a bound on how far res (and hence res +2) may be from the tail of  $\eta$ . We express it as a function of  $\iota_{\rm O}$  and  $\hat{\iota}$ , derived from the bounds in (vi), taking res +2 for t and over-approximating the instant value  $n_{\rm J}^i$  of the incremented counter via last  $(\eta_{\rm S} \cup \eta_{\rm O})$ . The inequality weakens the invariant (vi), making it hold for even and odd entries by moving  $2 |\hat{\iota} \cap \iota_{\rm O}^i|$  (for i=0,1) to the right side of < and joining them, since  $\iota_{\rm O}^0 \cap \iota_{\rm O}^1 = \emptyset$ .

Finally, the predicate ResPast provides more bounds that we will need in the proofs of the client code's properties.

ResPast

$$\eta$$

res  $\hat{\iota} z = \hat{\iota} \subseteq \tau_0 \cup (\text{spent } \chi_0) \cup \{z\},$

$\forall \iota . t \mapsto (\iota, -) \subseteq \eta \Rightarrow z \notin \iota, \ t < \text{res} + 2 + 2 (|\hat{\iota} \cap \iota|)$  (18)

When instantiated with  $\eta=\eta_{\rm S}\cup\eta_{\rm O}$ , ResPast says the following. The token set  $\hat{\iota}$  snapshot when res+2 was committed to history, is a subset of all the tokens in post-state, including the live ones  $(\tau_{\rm O})$ , and spent ones (spent  $\chi_{\rm O}\cup\{z\}$ ). Moreover, if t is an entry in  $\eta$ , with contents  $(\iota,-)$ , then: (1)  $z\notin\iota$ , because z is a token generated when getAndInc executed flip. Hence, z is fresh wrt. any token-set from the pre-state history  $\eta$ ; and (2) t and t satisfy the same bounds wrt. res+2, as those described for the last history entry and  $t_{\rm O}$ .

How will the spec (17) be used? The clause  $\chi_S = \eta_S \cup (\text{res} + 2) \mapsto -\text{ of (17)}$ , in conjunction with the invariant (ii), ensures that any two calls to getAndInc, sequential or concurrent, yield different history entries, and hence different results. This establishes **R1**, which we will not discuss further.

The inequality on last  $(\eta_S \cup \eta_O)$  will provide for **R2** in client reasoning. To see how, consider the particular case

```

\begin{cases} \tau_{\mathsf{S}} = \emptyset, \, \chi_{\mathsf{S}} = \eta_{\mathsf{S}}, \eta_{\mathsf{O}} \subseteq \chi_{\mathsf{O}}, \mathcal{I} \, \eta_{\mathsf{O}} \, \iota_{\mathsf{O}}, \\ \iota_{\mathsf{O}} \subseteq \tau_{\mathsf{O}} \cup (\mathsf{spent} \, \chi_{\mathsf{O}} \setminus \mathsf{spent} \, \eta_{\mathsf{O}}) \end{cases} \\ \mathsf{getAndInc}() \ \| \ e_i \\ \begin{cases} \exists \hat{\iota} \, \eta_i. \, \tau_{\mathsf{S}} = \emptyset, \, \chi_{\mathsf{S}} = \eta_{\mathsf{S}} \cup \eta_i \cup (\mathsf{res}.1 + 2) \mapsto (\hat{\iota}, -) \,, \\ \eta_{\mathsf{O}} \subseteq \chi_{\mathsf{O}}, \iota_{\mathsf{O}} \subseteq \tau_{\mathsf{O}} \cup (\mathsf{spent} \, \chi_{\mathsf{O}} \setminus \mathsf{spent} \, \eta_{\mathsf{O}}), \mathcal{I} \, \eta_{\mathsf{O}} \, \iota_{\mathsf{O}}, \\ \mathsf{last} \, (\eta_{\mathsf{S}} \cup \eta_{\mathsf{O}}) < \mathsf{res}.1 \ + 2 + 2 \, |\hat{\iota} \cap \iota_{\mathsf{O}}| \end{cases}

```

**Figure 6.** Parallel composition of getAndInc and  $e_i$  in (20).

when  $\iota_{O}$  is empty, *i.e.*, the pre-state is quiescent. In that case, the intersection with  $\hat{\iota}$  is empty, and we can infer that res +2, is larger than either counter's value in the pre-state. As we shall see in Section 7, this captures the essence of QC.

Finally, the predicate ResPast (18) establishes a bound for the "out-of-order" discrepancy between the result res and any value t committed to the history in the past, via  $2 \mid \hat{\iota} \cap \iota \mid$ . We will further bound this value using the size of  $\hat{\iota}$ , and the inclusion  $\hat{\iota} \subseteq \tau_0 \cup \text{spent } \chi_0 \text{ from (18)}$ . These bounds will ultimately enable us to derive the requirement  $\mathbf{R3}$ .

# 7. Verifying Counting Network's Clients

Following Step 3 of our verification method, we now illustrate requirements R2 and R3 from the previous section via two different clients which execute two sequential calls to getAndInc. Both clients are higher-order, i.e., they are parametrized by subprograms, which can be "plugged in". The first client will exhibit a quiescence between the two calls, and we will prove that the call results appear in order, as required by R2. The second client will experience interference of a program with a N concurrent calls to getAndInc, and we will derive a bound on the results in terms of N, as required by R3.

Both our examples will rely on the general mechanism of hiding, presented in Section 4, as a way to logically restrict the interference on a concurrent object, in this case, a counting network, in a lexically-scoped way. To "initialize" the counting network data structure, we provide the starting values for the shared heap  $(h_0)$  and for the history  $(\eta_0)$ , assuming that the initial set of tokens is empty:

$$h_0 \triangleq bal \mapsto 0 \cup c_0 \mapsto 0 \cup c_1 \mapsto 1 \eta_0 \triangleq \{0 \mapsto (\{0\}, 0), 1 \mapsto (\{1\}, 1)\}$$

(19)

That is,  $\eta_0$  provides the "default" history for the initial values 0 and 1 of  $c_0$  and  $c_1$ , with the corresponding tokens represented by numbers 0 and 1. As always with hiding, the post-condition of the hidden program will imply that  $\tau_0$  and  $\chi_0$  are both empty, as there is no interference at the end.

<sup>&</sup>lt;sup>7</sup> That is,  $\eta_{\rm O}$  and  $\iota_{\rm O}$  take the role of  $\chi_{\rm O}$  and  $\tau_{\rm O}$  in invariants (ii)–(vi), with  $n_{\rm J}^i = {\sf last} \ (\chi_{\rm S} \cup \eta_{\rm O})^i$ . The formal definition of  ${\cal I}$  is in our proof scripts.

#### 7.1 Exercising Quiescent Consistency

Our first client is the following program  $e_{qc}$ :

1

$$(res_1, -) \leftarrow (getAndInc() || e_1);$$

2  $(res_2, -) \leftarrow (getAndInc() || e_2);$

3 **return**  $(res_1, res_2)$  (20)

Each of the calls to getAndInc interferes with either  $e_1$  or  $e_2$ , but in the absence of *external* interference, the quiescent state is reached between the lines 1 and 2. Hence, after executing hide  $e_{qc}$ , it should be  $res_1 < res_2$ , following **R2**.

The programs  $e_1$  and  $e_2$  can invoke getAndInc and modify the counters concurrently with the two calls of  $e_{qc}$ , which we capture by giving both the following generic spec:

$$\{ \chi_{\mathsf{S}} = \emptyset, \tau_{\mathsf{S}} = \emptyset, \iota \subseteq \tau_{\mathsf{O}} \cup \mathsf{spent} \ \chi_{\mathsf{O}} \}$$

$$e_{i}$$

$$\{ \exists \eta_{i}. \ \chi_{\mathsf{S}} = \eta_{i}, \tau_{\mathsf{S}} = \emptyset, \iota \subseteq \tau_{\mathsf{O}} \cup \mathsf{spent} \ \chi_{\mathsf{O}} \}$$

$$(21)$$

The postcondition allows for a number of increments via calls to getAndInc, which is reflected in the addition  $\eta_i$  to  $\chi_S$ . However, all such calls are required to be *finished* by the end of  $e_i$  ( $\tau_S = \emptyset$ ). As customary by now, we use the logical variable  $\iota$  to name the initial set of *other* tokens.

Figure 6 provides a spec for each of the parallel compositions in the program (20), proved via the corresponding FCSL inference rule for parallel composition (11). The spec is very similar to (17) with the differences highlighted via gray boxes: (a) the self-history  $\chi_{\rm S}$  is increased by  $e_i$ 's contribution  $\eta_i$  in addition to the entry, introduced by <code>getAndInc</code>, (b) the result of the parallel composition is a pair, but we only constrain its first component res.1, resulting from the left subprogram. We also drop the last conjunct with ResPast from (17), which we won't require for this example.

Next, we use the spec from Figure 6 to specify and verify the program  $e_{qc}$ , so far assuming external interference.

```

\left\{ \begin{array}{l} \text{Fig. 6's precondition with } \eta_{\text{S}} := \eta_{0}, \, \eta_{\text{O}} := \chi_{\text{O}}, \, \text{and } \iota_{\text{O}} := \tau_{\text{O}} \, \right\} /\!\!/ \, P \\ & (\text{res}_{1}, -) \leftarrow (\text{getAndInc}() \mid\mid e_{1}); \\ & \exists \eta_{1}. \, \tau_{\text{S}} = \emptyset, \, \chi_{\text{S}} = \eta'_{\text{S}}, \, \dots \\ & \text{where } \quad \eta'_{\text{S}} = \eta_{0} \cup \eta_{1} \cup (\text{res}_{1} + 2) \mapsto - \,, \, \eta_{\text{O}} := \chi_{\text{O}} \, \text{and } \iota_{\text{O}} := \tau_{\text{O}} \right\} \\ & (\text{res}_{2}, -) \leftarrow (\text{getAndInc}() \mid\mid e_{2}); \\ & \left\{ \exists \eta_{1} \, \eta_{2} \, \hat{\iota}. \, \tau_{\text{S}} = \emptyset, \, \iota_{\text{O}} \subseteq \tau_{\text{O}} \cup (\text{spent } \chi_{\text{O}} \setminus \text{spent } \eta_{\text{O}}) , \\ & \left\{ \exists \eta_{1} \, \eta_{2} \, \hat{\iota}. \, \tau_{\text{S}} = \emptyset, \, \iota_{\text{O}} \subseteq \tau_{\text{O}} \cup (\text{spent } \chi_{\text{O}} \setminus \text{spent } \eta_{\text{O}}) , \\ & \left\{ \exists \eta_{1} \, \eta_{2} \, \hat{\iota}. \, \tau_{\text{S}} = \emptyset, \, \tau_{\text{O}} \subseteq \tau_{\text{O}} \cup (\text{spent } \chi_{\text{O}} \setminus \text{spent } \eta_{\text{O}}) , \\ & \left\{ \exists \eta_{1} \, \eta_{2} \, \hat{\iota}. \, \tau_{\text{S}} = \emptyset, \, \tau_{\text{O}} \subseteq \tau_{\text{O}} \cup (\text{spent } \chi_{\text{O}} \setminus \text{spent } \eta_{\text{O}}) , \\ & \left\{ \exists \eta_{1} \, \eta_{2} \, \hat{\iota}. \, \tau_{\text{S}} = \emptyset, \, \tau_{\text{O}} \subseteq \tau_{\text{O}} \subseteq \tau_{\text{O}} \right\} \right\}

```