Received 19 August 2018; revised 10 October 2018; accepted 14 October 2018. Date of publication 17 October 2018; date of current version 1 March 2019. The review of this paper was arranged by Editor S. Chakrabarti.

Digital Object Identifier 10.1109/JEDS.2018.2876618

# Homo-Junction Bottom-Gate Amorphous In–Ga–Zn–O TFTs With Metal-Induced Source/Drain Regions

# YANG SHAO<sup>®</sup><sup>1</sup>, XIAOLIANG ZHOU<sup>®</sup><sup>2</sup>, HUAN YANG<sup>1</sup>, BAOZHU CHANG<sup>1</sup>, TING LIANG<sup>1</sup>, YI WANG<sup>2</sup>, AND SHENGDONG ZHANG<sup>®</sup><sup>1,2</sup>

1 School of Electronic and Computer Engineering, Shenzhen Graduate School, Peking University, Shenzhen 518055, China 2 Institute of Microelectronics, Peking University, Beijing 100871, China

CORRESPONDING AUTHOR: S. ZHANG (e-mail: zhangsd@pku.edu.cn)

This work was supported by the National Natural Science Foundation of China under Project 61574003 and Project 61774010.

**ABSTRACT** A fabrication process for homo-junction bottom-gate (HJBG) amorphous In–Ga–Zn–O (a-IGZO) thin-film transistors (TFTs) is proposed, in which the a-IGZO section as source/drain (S/D) regions is induced into a low resistance state by coating a thin metal Al film and then performing a thermal annealing in oxygen, with the channel region protected from back etching by depositing and patterning a protective layer. The experimental results show that with a 5 nm Al film and annealing at 200 °C, the sheet resistance of the S/D a-IGZO is reduced to 803  $\Omega/\Box$ , and keeps stable during a subsequent thermal treatment. In addition, the thin Al<sub>2</sub>O<sub>3</sub> film generated by the annealing contributes to an improved thermal stability and ambient atmosphere immunity for the fabricated HJBG TFTs.

**INDEX TERMS** Amorphous indium–gallium–zinc oxide, thin-film transistors, homo-junction, aluminum reaction.

### I. INTRODUCTION

Amorphous In–Ga–Zn–O (a-IGZO) thin-film transistors (TFTs) have been intensively investigated since being reported in 2004 by Nomura *et al.* [1]. Such transistors exhibit superior performances compared to conventional silicon-based TFTs and are thereby considered a promising active device for next-generation display applications [1]–[4]. In particular, their fabrication process is potentially comparable to existing amorphous silicon (a-Si) TFT production technology in terms of manufacturing cost and simplicity [5].

A TFT can either have a top-gate or bottom-gate structure. For a bottom-gate structure, two processes are mainly used for the fabrication of a-IGZO TFTs at present: back channel etching (BCE) process and etch stop layer (ESL) process [6], [7]. The BCE process is usually preferable due to the fewer photolithographic masks and fabrication steps [6], [7]. However, the back channel etching step turns out to be very difficult to handle and usually substantially degrades the device performances [8]–[10]. The ESL-based process produces a channel layer that is free of back etching, enabling a high device performance [8], [9], [11]. However, it usually requires more masks, leading to a highly increased production cost [6], [7]. In particular, this process also induces a large parasitic capacitance and makes it difficult to shrink the TFT channel length [6]–[8]. These factors largely limit its application in high-end products.

Recently, an alternative process called a homo-junction bottom-gate (HJBG) process was proposed to address the issues associated with the BCE and ESL processes mentioned above [12]–[14]. In the HJBG structure, both source/drain (S/D) and channel sections are composed of the same oxide semiconductor layer such as a-IGZO, and the S/D section is heavily doped to be highly conductive. This is different from the BCE and ESL cases, where the S/D section is a stack of metal and oxide films. The methods proposed thus far for the forming of the homo-junction S/D regions include Ar [14], [15] or H<sub>2</sub> plasma treatments [14]

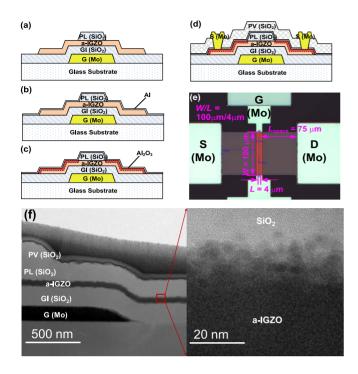

FIGURE 1. (a)–(d) Schematic fabrication steps for a homo-junction bottom-gate a-IGZO TFT, (e) top view of a fabricated a-IGZO TFT, (f) TEM image of a fabricated a-IGZO TFT.

and hydrogen diffusion from  $SiN_x$  [12], [13], [16]. For the Ar plasma approach, the initially induced low resistance S/D regions could not be well maintained since the oxygen vacancies induced by ion bombardment are largely reduced during the subsequent thermal process [17], [18]. Although the thermal stability of the Ar plasma treated S/D regions could be improved by applying an appropriate substrate bias power during the plasma treating process, a narrow process window was resulted [19]. For the hydrogen-related doping methods, the stability and uniformity, as well as the scalability of the fabricated devices, are the main concerns due to the high diffusivity of hydrogen atoms [20]–[23]. Therefore, the HJBG processes proposed thus far are unlikely to be applicable for mass production. Recently, a metallic S/D forming method was proposed for the fabrication of self-aligned top-gate oxide TFTs [18], [24]-[26]. Though top-gate technology is able to minimize the parasitic capacitance, it needs a back light shielding layer for the channel region, leading to a complex process.

In this work, we propose a new HJBG fabrication process for a-IGZO TFTs. The metal Al reaction is employed to form the high conductive S/D regions of the bottom gate TFT. It will be demonstrated that the fabricated HJBG a-IGZO TFTs in this process have a high electrical performance, strong channel-length scalability, excellent thermal stability in S/D resistance, and high immunity to ambient-atmosphere.

## **II. EXPERIMENTAL DETAILS**

Fig. 1 (a)-(d) show cross-sectional schematic fabrication steps for the proposed HJBG a-IGZO TFTs. First,

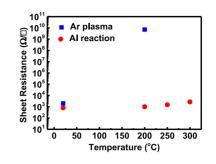

FIGURE 2. Sheet resistance of the source/drain regions treated by Ar plasma or Al reaction versus the post thermal treatment temperature.

a 120 nm Mo film was deposited as the gate electrode (GE) by direct-current (DC) sputtering. Then, a 200 nm SiO<sub>2</sub> film was deposited as the gate insulator (GI) at 300 °C by plasma-enhanced chemical vapor deposition (PECVD). Then, a 50 nm a-IGZO film was deposited by DC sputtering at room temperature and patterned to form the active island by wet etching. Next, PECVD was used to deposit a 200 nm SiO<sub>2</sub>film at 150 °C as the protection layer (PL), followed by removal of the PL section on the S/D regions by dry etching (Fig. 1(a)). Then, a 5 nm Al film was sputtered onto the exposed a-IGZO layer as the S/D regions (Fig. 1(b)) before thermal annealing in oxygen ambient at 200 °C for 1.5 hours. During the annealing process, the Al reacted with the underlying a-IGZO, generating the Al<sub>2</sub>O<sub>3</sub> film on the surface and oxygen vacancies in the a-IGZO (Fig. 1(c)). Thus, the S/D a-IGZO section was highly conductive and self-aligned to the SiO<sub>2</sub> PL. Afterwards, 200 nm of SiO<sub>2</sub> was deposited as the passivation layer at 150 °C by PECVD. Finally, S/D electrodes were formed by Mo via contact holes (Fig. 1(d)). It is seen from the process that the active layer does not encounter any etching step, similar to the case of the ESL process, with the channel length (L) defined by the PL length and the parasitic capacitance determined by the underlap length between the GE and PL, similar to the case of the BCE process. Therefore, the proposed process has the advantages of both BCE and ESL processes.

For comparison, a-IGZO TFTs with S/D regions treated by Ar plasma instead of the Al reaction were also fabricated. The Ar plasma treatment was performed immediately after dry etching the SiO<sub>2</sub> PL. The treatment time was 90 s at room temperature with a radio frequency power of 50 W.

The electrical characteristics of the TFTs were measured using an Agilent B1500 semiconductor parameter analyzer at room temperature in the dark.

#### **III. RESULTS AND DISCUSSION**

Fig. 2 shows the sheet resistance of Al- and Ar plasmatreated a-IGZO films versus the post thermal annealing temperature. The annealing was carried out in oxygen ambient for 1 hour. It is seen that the sheet resistance of the Al-treated a-IGZO increased slightly from 803  $\Omega/\Box$  to 2724  $\Omega/\Box$ . In contrast, the sheet resistance of the Ar plasma treated a-IGZO

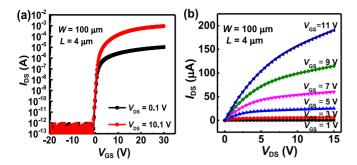

**FIGURE 3.** Current–voltage (I - V) characteristics of a TFT fabricated using the proposed AI reacted HJBG process, with (a) transfer and (b) output characteristics shown.

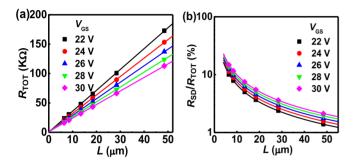

**FIGURE 4.** (a) Total resistance ( $R_{TOT}$ ) and (b) ratio of source/drain parasitic resistance to the total resistance ( $R_{SD}/R_{TOT}$ ) versus channel length for varying gate voltages.

increased drastically by more than six orders of magnitude, from 1994  $\Omega/\Box$  to 7.14 × 10<sup>9</sup>  $\Omega/\Box$ , after the thermal annealing at 200 °C. The depth profile analysis by secondary ion mass spectrometry (SIMS) revealed that Al diffused into the a-IGZO layer by a depth of approximately 13 nm after the one hour annealing (data not shown here), which is similar to the result reported by Morosawa *et al.* [18].

Fig. 3 shows the current–voltage (I - V) characteristics of a HJBG TFT fabricated using the proposed process, with (a) the transfer and (b) output characteristics. The a-IGZO TFT with a channel length of 4  $\mu$ m shows a subthreshold swing (SS) of 0.26 V/decade, a field-effect mobility  $(\mu_{\text{FET}})$  of 9.24 cm<sup>2</sup>/V·s, a threshold voltage ( $V_{\text{TH}}$ ) of 2.11 V, and an on-to-off current ratio ( $I_{\text{ON}}/I_{\text{OFF}}$ ) exceeding 1 × 10<sup>9</sup> at  $V_{\text{DS}} = 10.1$  V. From the output characteristics, no current crowding phenomenon is observed in the linear region, indicating that the source/drain parasitic resistance ( $R_{\text{SD}}$ ) is low.

Fig. 4 shows (a) the total resistance ( $R_{TOT}$ ) and (b) the ratio of  $R_{SD}$  to  $R_{TOT}$  versus channel length at different  $V_{GS}$ .  $R_{TOT}$ is calculated from the transfer characteristics at  $V_{DS} = 0.1$  V with various channel lengths. The width normalized  $R_{SD}$ ( $R_{SD}W$ ) can be extracted from the intercept of the fitting lines by the transfer length method (TLM), and is evaluated to be 24  $\Omega$ ·cm, which is comparable to that (10.4  $\Omega$ ·cm) of BCE-type a-IGZO TFT with Al-doped ZnO S/D electrodes in our previous work [10]. For a conventional ES-type a-IGZO TFT with metal S/D electrodes, the typical  $R_{SD}W$

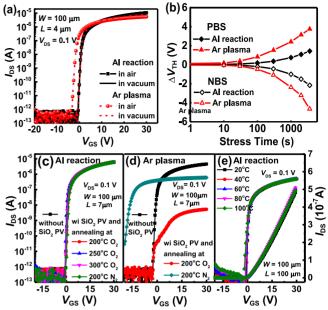

FIGURE 5. (a) Transfer characteristics of the Al- and Ar plasma-treated a-IGZO TFTs without passivation measured in air and in vacuum, (b) time-dependent threshold voltage shifts  $(\Delta V_{TH})$  of the Al- and Ar plasma-treated a-IGZO TFTs without passivation under both 20 V positive-bias stress (PBS) and -20 V negative-bias stress (NBS) for 3600 s measured in air, (c) and (d) transfer characteristics evolutions of the Aland Ar plasma-treated a-IGZO TFTs respectively after passivation and annealing, and (e) transfer characteristics evolution of the Al-treated a-IGZO TFTs under different working temperatures.

value was about 100  $\Omega \cdot \text{cm}$  [11]. Moreover, as shown in Fig. 4(b), the  $R_{\text{SD}}/R_{\text{TOT}}$  ratio is about 23 % at  $V_{\text{GS}} = 30$  V for the device with  $L = 4 \,\mu\text{m}$ . The ratio is slightly large. It is worth mentioning that the  $R_{\text{SD}}$  in this work was surely overestimated due to the non-optimized layout design. Note that the distance from the metal contact to the a-IGZO channel is approximately 75  $\mu$ m, which is much longer than what is necessary, as shown in Fig. 1(e). With an optimal layout, the  $R_{\text{SD}}$  could be definitely further reduced. In addition, the shrinkage of the channel length  $\Delta L$  is evaluated to be around 0.5  $\mu$ m, much smaller than that for S/D regions formed by H doping [12]. This result implies that the incorporation of hydrogen into the S/D regions during PECVD of the SiO<sub>2</sub> layer can be effectively blocked by the generated Al<sub>2</sub>O<sub>3</sub> film.

For comparison, Ar plasma-treated TFTs with and without a passivation layer were also fabricated. For the passivated device, following the Ar plasma treatment, a 200 nm SiO<sub>2</sub> passivation layer was deposited, and a thermal annealing was subsequently performed at 200 °C in oxygen for 1.5 hours. For the device without passivation, Mo contact electrodes were formed immediately after the Ar plasma treatment, without subsequent thermal treatment. Fig. 5 (a) shows the transfer characteristics measured in air and in vacuum for the Al- and Ar plasma treated a-IGZO TFTs without passivation, respectively. While the Ar plasma-treated TFT shows a lower  $V_{\text{TH}}$  in air, the Al-treated TFT shows nearly identical characteristics in both cases. The lower  $V_{\text{TH}}$  for the Ar plasma-treated TFT in air can be explained by the adsorption of water molecules on the a-IGZO back channel surface [27]. This result implies that the SiO<sub>2</sub> PL alone cannot protect a-IGZO TFTs from the invasion of water molecules. For the Al-treated TFT, the thin Al<sub>2</sub>O<sub>3</sub> layer formed by thermal oxidation of the thin Al film enhances the passivation effect, leading to excellent environmental stability. In addition, it is seen that the Al-treated TFT shows a higher on-current compared to the Ar plasma-treated TFT. The extracted  $R_{SD}W$ values for Al- and Ar plasma-treated TFTs are 24  $\Omega$ ·cm and 124  $\Omega$ ·cm, respectively. The lower  $R_{SD}$  for the Al-treated TFT is responsible for the higher on-current.

Fig. 5(b) shows the time-dependent threshold voltage shifts ( $\Delta V_{\text{TH}}$ ) of the Al- and Ar plasma treated a-IGZO TFTs without passivation measured in air under both the positive-bias stress (PBS) and the negative-bias stress (NBS). As shown, the Al-treated a-IGZO TFT shows better stability under both the PBS and NBS. The stability improvement in the Al-treated devices can also be explained by the prevention of the ambient effect due to the effective protection of the channel layer by the thin Al<sub>2</sub>O<sub>3</sub> layer [28].

Fig. 5(c) and (d) show the evolutions of the transfer characteristics of the Al- and Ar plasma treated a-IGZO TFTs after deposition of the SiO<sub>2</sub> passivation layer and annealing in O<sub>2</sub> or N<sub>2</sub> for 1.5 hours. For the Al-treated TFT, no noticeable change in the transfer curves is observed after passivation and annealing. In contrast, for the Ar plasmatreated TFT, the on-current is significantly lowered after passivation and annealing, which results from a remarkably increased S/D resistance. This result suggests that the annealing induces a significant reduction of the oxygen vacancies previously generated in the source and drain regions by the Ar plasma treatment. Fig. 5(e) shows the transfer characteristics evolution of the Al treated a-IGZO TFTs under different temperatures. A slight increase in subthreshold current with temperature is observed, which can be ascribed to the thermally activated carriers from traps in the band gap of a-IGZO. The evolution is similar to that observed in a-IGZO TFTs with metal S/D electrodes [29], [30], implying that the Al-treated S/D regions do not bring about additional temperature instability issue.

# **IV. CONCLUSION**

We have demonstrated a novel process for fabricating homojunction bottom-gate a-IGZO TFTs. By coating a thin Al film and then performing thermal annealing, the fabricated HJBG TFTs have been demonstrated to exhibit a low S/D sheet resistance, which is comparable to or even lower than that obtained for TFTs fabricated using a conventional ES process. In addition, the thermally oxidized thin Al<sub>2</sub>O<sub>3</sub> film can block hydrogen diffusion and H<sub>2</sub>O invasion and can thus enhance the passivation effect. As a result, the HJBG TFTs fabricated using the proposed process show excellent electrical performance, high thermal stability, and strong immunity to ambient atmosphere. This work was conducted in the Shenzhen TFT and Advanced Display Lab.

#### REFERENCES

- K. Nomura *et al.*, "Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors," *Nature*, vol. 432, no. 7016, pp. 488–492, Nov. 2004, doi: 10.1038/nature03090.

- [2] E. Fortunato, P. Barquinha, and R. Martins, "Oxide semiconductor thin-film transistors: A review of recent advances," *Adv. Mater.*, vol. 24, no. 22, pp. 2945–2986, Jun. 2012, doi: 10.1002/adma.201103228.

- [3] T. Kamiya, K. Nomura, and H. Hosono, "Present status of amorphous In–Ga–Zn–O thin-film transistors," *Sci. Technol. Adv. Mater.*, vol. 11, no. 4, pp. 1–23, Aug. 2010, doi: 10.1088/1468-6996/11/4/044305.

- [4] T. Kamiya, K. Nomura, and H. Hosono, "Origins of high mobility and low operation voltage of amorphous oxide TFTs: Electronic structure, electron transport, defects and doping," *J. Display Technol.*, vol. 5, no. 7, pp. 273–288, Jul. 2009, doi: 10.1109/JDT.2009.2021582.

- [5] T. Matsuo, S. Mori, A. Ban, and A. Imaya, "Advantages of IGZO oxide semiconductor," in *SID Symp. Dig. Tech. Papers*, vol. 45, no. 1, pp. 83–86, Jun. 2014, doi: 10.1002/j.2168-0159.2014.tb00023.x.

- [6] J.-Y. Kwon, D.-J. Lee, and K.-B. Kim, "Transparent amorphous oxide semiconductor thin film transistor," *Electron. Mater. Lett.*, vol. 7, no. 1, pp. 1–11, Mar. 2011, doi: 10.1007/s13391-011-0301-x.

- [7] J. Y. Kwon and J. K. Jeong, "Recent progress in high performance and reliable n-type transition metal oxide-based thin film transistors," *Semicond. Sci. Technol.*, vol. 30, no. 2, pp. 1–16, Feb. 2015, doi: 10.1088/0268-1242/30/2/024002.

- [8] J. U. Bae *et al.*, "Development of oxide TFT's structures," *SID Symp. Dig. Tech. Papers*, vol. 44, no. 1, pp. 89–92, Jun. 2013, doi: 10.1002/j.2168-0159.2013.tb06148.x.

- [9] J.-Y. Kwon *et al.*, "The impact of device configuration on the photon-enhanced negative bias thermal instability of GaInZnO thin film transistors," *Electrochem. Solid-State Lett.*, vol. 13, no. 6, pp. H213–H215, Apr. 2010, doi: 10.1149/1.3381023.

- [10] W. Deng *et al.*, "A back-channel-etched amorphous InGaZnO thinfilm transistor technology with al-doped ZnO as source/drain and pixel electrodes," *IEEE Trans. Electron Devices*, vol. 63, no. 5, pp. 2205–2209, May 2016, doi: 10.1109/TED.2016.2542862.

- [11] M. Kim *et al.*, "High mobility bottom gate InGaZnO thin film transistors with SiO<sub>x</sub> etch stopper," *Appl. Phys. Lett.*, vol. 90, no. 21, pp. 1–3, May 2007, doi: 10.1063/1.2742790.

- [12] A. Sato et al., "Amorphous In–Ga–Zn–O coplanar homojunction thinfilm transistor," Appl. Phys. Lett., vol. 94, no. 13, pp. 1–3, Mar. 2009, doi: 10.1063/1.3112566.

- [13] E. K.-H. Yu, K. Abe, H. Kumomi, and J. Kanicki, "AC bias-temperature stability of a-InGaZnO thin-film transistors with metal source/drain recessed electrodes," *IEEE Trans. Electron Devices*, vol. 61, no. 3, pp. 806–812, Mar. 2014, doi: 10.1109/TED.2014.2302411.

- [14] B. D. Ahn, H. S. Shin, H. J. Kim, J. S. Park, and J. K. Jeong, "Comparison of the effects of Ar and H<sub>2</sub> plasmas on the performance of homojunctioned amorphous indium gallium zinc oxide thin film transistors," *Appl. Phys. Lett.*, vol. 93, no. 20, pp. 1–3, Nov. 2008, doi: 10.1063/1.3028340.

- [15] J. Park *et al.*, "Self-aligned top-gate amorphous gallium indium zinc oxide thin film transistors," *Appl. Phys. Lett.*, vol. 93, no. 5, pp. 1–3, Aug. 2008, doi: 10.1063/1.2966145.

- [16] C.-H. Wu, H.-H. Hsieh, C.-W. Chien, and C.-C. Wu, "Selfaligned top-gate coplanar In-Ga-Zn-O thin-film transistors," J. Display Technol., vol. 5, no. 12, pp. 515–519, Dec. 2009, doi: 10.1109/JDT.2009.2026189.

- [17] H. S. Shin, B. D. Ahn, K. H. Kim, J.-S. Park, and H. J. Kim, "The effect of thermal annealing sequence on amorphous InGaZnO thin film transistor with a plasma-treated source–drain structure," *Thin Solid Films*, vol. 517, no. 23, pp. 6349–6352, Oct. 2009, doi: 10.1016/j.tsf.2009.02.071.

- [18] N. Morosawa, Y. Ohshima, M. Morooka, T. Arai, and T. Sasaoka, "Self-aligned top-gate oxide thin-film transistor formed by aluminum reaction method," *Jpn. J. Appl. Phys.*, vol. 50, no. 9, pp. 1–4, Sep. 2011, doi: 10.1143/JJAP.50.096502.

- [19] Y. Magari, H. Makino, and M. Furuta, "Carrier generation mechanism and origin of subgap states in Ar- and He-plasma-treated In–Ga–Zn–O thin films," *ECS J. Solid-State Sci. Technol.*, vol. 6, no. 8, pp. Q101–Q107, Aug. 2017, doi: 10.1149/2.0031709jss.

- [20] R. Chen, W. Zhou, M. Zhang, M. Wong, and H.-S. Kwok, "Self-aligned indium-gallium-zinc oxide thin-film transistor with phosphorus-doped source/drain regions," *IEEE Electron Device Lett.*, vol. 33, no. 8, pp. 1150–1152, Aug. 2012, doi: 10.1109/LED.2012.2201444.

- [21] H.-Y. Jeong *et al.*, "Coplanar amorphous-indium-gallium-zincoxide thin film transistor with He plasma treated heavily doped layer," *Appl. Phys. Lett.*, vol. 104, no. 2, pp. 1–5, Jan. 2014, doi: 10.1063/1.4862320.

- [22] S.-H. K. Park et al., "Bilayered etch-stop layer of Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> for high-mobility In-Ga-Zn-O thin-film transistors," Jpn. J. Appl. Phys., vol. 52, no. 10, pp. 1–3, Oct. 2013, doi: 10.7567/JJAP.52.100209.

- [23] S.-H. K. Park *et al.*, "Double-layered passivation film structure of Al<sub>2</sub>O<sub>3</sub>/SiN<sub>x</sub> for high mobility oxide thin film transistors," *J. Vac. Sci. Technol. B*, vol. 31, no. 2, pp. 1–6, Mar. 2013, doi: 10.1116/1.4789423.

- [24] N. Morosawa *et al.*, "High-mobility self-aligned top-gate oxide TFT for high-resolution AM-OLED," *J. Soc. Inf. Display*, vol. 21, no. 11, pp. 467–473, Nov. 2013, doi: 10.1002/jsid.206.

- [25] N. Morosawa, Y. Ohshima, M. Morooka, T. Arai, and T. Sasaoka, "Novel self-aligned top-gate oxide TFT for AMOLED displays," *J. Soc. Inf. Display*, vol. 20, no. 1, pp. 47–52, Jan. 2012, doi: 10.1889/JSID20.1.47.

- [26] T. Toda, G, Tatsuoka, Y. Magari, and M. Furuta, "Highperformance top-gate and self-aligned In–Ga–Zn-O thin-film transistor using coatable organic insulators fabricated at 150 °C," *IEEE Electron Device Lett.*, vol. 37, no. 8, pp. 1006–1009, Aug. 2016, doi: 10.1109/LED.2016.2582319.

- [27] J.-S. Park, J. K. Jeong, H.-J. Chung, Y.-G. Mo, and H. D. Kim, "Electronic transport properties of amorphous indium-gallium-zinc oxide semiconductor upon exposure to water," *Appl. Phys. Lett.*, vol. 92, no. 7, pp. 1–3, Feb. 2008, doi: 10.1063/1.2838380.

- [28] J. K. Jeong, H. W. Yang, J. H. Jeong, Y.-G. Mo, and H. D. Kim, "Origin of threshold voltage instability in indium-gallium-zinc oxide thin film transistor," *Appl. Phys. Lett.*, vol. 93, no. 12, pp. 1–3, Sep. 2008, doi: 10.1063/1.2990657.

- [29] B. Kim *et al.*, "Origin of threshold voltage shift by interfacial trap density in amorphous InGaZnO thin film transistor under temperature induced stress," *Appl. Phys. Lett.*, vol. 99, no. 6, pp. 1–3, Aug. 2011, doi: 10.1063/1.3615304.

- [30] K. H. Ji et al., "The effect of density-of-state on the temperature and gate bias-induced instability of InGaZnO thin film transistors," *J. Electrochem. Sci.*, vol. 157, no. 11, pp. H983–H986, Sep. 2010, doi: 10.1149/1.3483787.

**YANG SHAO** received the Ph.D. degree from the School of Electronic and Computer Engineering, Peking University Shenzhen Graduate School, Shenzhen, China, where she is currently a Post-Doctoral Researcher. Her current research interests include oxide semiconductor and thin-film transistors.

**HUAN YANG** is currently pursuing the M.S. degree with the School of Electronic and Computer Engineering, Peking University Shenzhen Graduate School, Shenzhen, China. His current research interest includes the fabrication technologies of metal oxide thin-film transistors.

**BAOZHU CHANG** is currently pursuing the M.S. degree with the School of Electronic and Computer Engineering, Peking University Shenzhen Graduate School, Shenzhen, China. His current research interest includes fabrication technologies of coplanar thin-film transistors.

**TING LIANG** is currently pursuing the M.S. degree with the School of Electronic and Computer Engineering, Peking University Shenzhen Graduate School, Shenzhen, China. Her current research interests include oxide semiconductor and thin-film transistor.

**YI WANG** received the M.S. and Ph.D. degrees from the Graduate School of Information Sciences, Tohoku University, Sendai, Japan, in 1997 and 2000, respectively. He joined the Institute of Microelectronics, Peking University, in 2001, where he is currently a Professor. His research focuses on oxide semiconductor TFTs and their device physics.

**XIAOLIANG ZHOU** is currently pursuing the Ph.D. degree with the Institute of Microelectronics, Peking University, Beijing, China. His current research interests include fabrication technologies and reliability of thin-film transistors.

**SHENGDONG ZHANG** received the Ph.D. degree in electrical and electronic engineering from Peking University, Beijing, China. He joined the Peking University Shenzhen Graduate School, Shenzhen, China, in 2002, where he is currently a Full Professor with the School of Electronics Engineering and Computer Science. His current research interests include thin-film transistor technology and ICs for system on panel.