# Hybrid Analytical Modeling Method for Split Power Bus in Multilayered Package

Youchul Jeong, Albert Chee W. Lu, *Member, IEEE*, Lai Lai Wai, Wei Fan, *Member, IEEE*, Boon K. Lok, Hyunjeong Park, and Joungho Kim, *Member, IEEE*

Abstract—As multiple chips are being integrated into a single package with increased operating frequency, switching noise coupling on power buses has become an important design issue. To reduce the noise coupling, a split power bus structure has been generally used in package substrates having multilayered power and ground planes. Consequently, there is an increasing need for an efficient method to analyze a split power bus in a multilayered package. This paper introduces a hybrid analytical modeling method for characterizing a split power bus in a multilayered package. The proposed method uses a resonant cavity model combined with a segmentation method. Furthermore, a port assignment technique and an associated calculation method for the equivalent circuit model parameter of the split gap are proposed. The proposed port assignment technique and the analytical equation make it possible to analyze a split power bus, especially in a multilayered package. To verify the proposed method, multilayered test packages are fabricated and tested by means of frequency-domain measurements. In addition, an optimal power bus design method was successfully demonstrated for suppressing noise coupling between chips on a single package. Finally, the proposed method and optimal power bus design method was verified using a series of frequency-domain and time-domain measurements.

*Index Terms*—Multilayered package substrate, resonant cavity model, segmentation method, simultaneous switching noise (SSN), split power bus.

#### I. INTRODUCTION

**R** ECENTLY, increases in the clock speed and power consumption of circuits and chips in high-performance systems have lead to occurrences of large and sudden current surges on power buses and to a significant amount of noise on power buses. This noise, known as simultaneous switching noise (SSN), has become a major source of electromagnetic interference, which severely degrades system performance [1]. Moreover, continuing demand for integration of different technologies and for reduction of total product cost has driven use of system on a package (SOP) [2], noise sensitive circuits [such as phase-locked loops (PLL)] placed close to noisy high-speed digital circuits. Therefore, reduction and isolation of the SSN on packages has become a very critical design issue, with regard to

Manuscript received April 25, 2005; revised October 15, 2005. This work was supported by the Center for Electronic Packaging Materials of Korea Science and Engineering Foundation.

Y. Jeong, H. Park, and J. Kim are with the Terahertz Interconnection and Package Laboratory, Division of Electrical Engineering, Department of Electrical Engineering and Computer Science, Korea Advanced Institute of Science and Technology, Daejeon 305-701, Korea (e-mail: teralab@ee.kaist.ac.kr).

A. C. W. Lu, L. L. Wai, W. Fan, and B. K. Lok are with the Singapore Institute of Manufacturing Technology, Singapore 638075 (e-mail: cwlu@simtech.astar.edu.sg; llwai@simtech.a-star.edu.sg; wfan@simtech.a-star.edu.sg; bklok@ SIMTech.a-star.edu.sg).

Digital Object Identifier 10.1109/TEMC.2006.870701

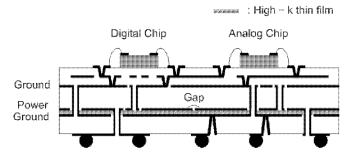

Fig. 1. Example of SOP. A digital chip and an analog chip are mounted on a single package, and a pair of power/ground planes with high-*k* thin film is used as an embedded decoupling capacitor. The power plane is split into two separate planes by a gap to isolate the simultaneous switching noise from the noisy digital chip to the noise sensitive analog chip.

improving system reliability and suppressing electromagnetic interference (EMI) [3]–[6].

For example, Fig. 1 illustrates an example of SOP, in which a digital chip and an analog chip are mounted together on a single package. In this package, additional ground and power planes are employed with a high-k dielectric thin film to implement a high-frequency embedded decoupling capacitor into the SOP substrate. In addition, the power plane is split into two separate planes by a gap to isolate a power bus of noise sensitive analog circuits or chips from a power bus of noisy digital circuit coupled with a noise sensitive analog circuit, such as a PLL or an analog-to-digital converter (ADC), can cause significant timing jitter [7], [8].

As implied in the SOP structure of Fig. 1, several design elements, such as the decoupling capacitor, via, and gap, determine the various characteristics of the power bus, including its impedance, switching noise generation, and switching noise isolation in the multilayered package. Among the design elements, the split power bus in the multilayered package is essential for noise isolation because it is the most cost-effective method for the reduction of the noise coupling. Accordingly, analysis of the split power bus in the multilayered package should precede package design.

Several methods have been used to analyze split power buses in multilayered packages similar to that shown in Fig. 1; these methods include transmission-line modeling methods [9], [10] and two-dimensional (2-D) or three-dimensional (3-D) fullwave numerical methods, such as FDTD, FEM, and MOM [11], [12]. However, a uniform grid step in the transmission-line modeling method causes simulation errors when components or sources are connected to the model [13] and the full-wave numerical methods are relatively complex and require significant simulation time and resources. Although there are many analytical modeling methods to analyze solid power buses in multilayered packages [14], [15], it is difficult to apply them directly to a split power bus in the multilayered package structure.

In this paper, we present a hybrid analytical modeling method to analyze a split power bus in a multilayered package by combining a resonant cavity model [14]–[16] and a segmentation method [17]-[20]. Although hybrid modeling methods based on a resonant cavity model and a segmentation method for isolation structures of a power bus in a two-layered PCB were successfully demonstrated in [21], [22], in this paper, the isolation structures of a power bus consisting of multilayered power and ground planes are analyzed using the hybrid modeling method for the first time. For the analysis of a multilayered structure, a port assignment technique and an analytical equation to model the split gap in multilayered package are proposed. The proposed port assignment technique and the analytical equation make it possible to apply the resonant cavity model and the segmentation method to the analysis of a split power bus in a multilayered package. Thus, we can accurately calculate the impedances  $(Z_{ii}, Z_{ij})$  of a split power bus in a multilayered package with the port assignment technique.

To verify the proposed method, we fabricated a series of multilayered test package substrates with embedded capacitor and two separated power planes. Then, the proposed hybrid analytical modeling method was successfully verified by means of impedance measurements in the frequency domain. In addition, the calculated self-impendence and transfer impedances  $(Z_{ii}, Z_{ij})$  show good agreement with the measured impedances. The proposed hybrid analytical modeling method is a gridless equation-based approach and so it is possible to calculate the impedances of the power buses at any port location. Finally, we demonstrate an optimal power bus design method based on the proposed modeling method for a split power bus with an embedded capacitor. We can accurately determine an optimal power bus configuration in a short time and with modest resource consumption. For example, we precisely calculated optimal via positions within 4 min, in contrast with the 2 h needed to complete the calculations using commercial 3-D full wave simulators.

Section II describes the proposed hybrid analytical modeling method for calculating the self-impedance  $(Z_{ii})$  and the transfer impedance  $(Z_{ij})$  of the split power bus in the multilayered package. We introduce the resonant cavity model and the segmentation method, and we propose the port assignment technique and the analytical equation to calculate the equivalent circuit model parameter of the split gap embedded between the two ground planes. Then, a split power bus in the multilayered package is analyzed using the proposed hybrid analytical modeling method. In Section III, we compare the self-impedance  $(Z_{ii})$  and the transfer impedance  $(Z_{ij})$  obtained from the hybrid analytical modeling method and impedance measurement to demonstrate the validity of the model. Finally, we present a power bus design method based on an optimal via position technique to reduce the transfer impedance  $(Z_{ij})$  of the split power bus with the embedded capacitor. The calculation

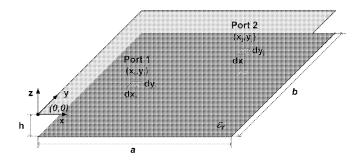

Fig. 2. Geometry of a rectangular power/ground plane structure. Port 1 and Port 2 are defined between the power plane and the ground plane, and are located at  $(x_i, y_i)$  and  $(x_j, y_j)$ , respectively.

results are well verified by a series of experiments involving frequency- and time-domain measurements.

#### II. HYBRID ANALYTICAL MODELING METHOD FOR ANALYSIS OF SPLIT POWER BUS IN MULTILAYERED PACKAGE

In this section, we introduce the resonant cavity model and the segmentation method that are used in the proposed hybrid analytical modeling method. In addition, a port assignment technique and an analytical equation for the split gap model are proposed to analyze a split power bus in a multilayered package. With the port assignment technique and the analytical equation, it is possible to apply the resonant cavity model and the segmentation method to an analysis of a split power bus in a multilayered package.

#### A. Resonant Cavity Model and Segmentation Method

As shown in Fig. 2, the most common power bus structure in a multilayered package is a rectangular cavity formed by a pair of power and ground planes. The impedance matrix elements of the rectangular power/ground planes can be obtained from a resonant cavity model described in [14]–[16], as shown in

$$Z_{ij} = j\omega\mu h \sum_{m=0}^{\infty} \sum_{n=0}^{\infty} \frac{C_m^2 C_n^2}{ab(k_{xm}^2 + k_{yn}^2 - k^2)} \\ \times \cos(k_{xm} x_i) \cos(k_{yn} y_i) \cos(k_{xm} x_j) \cos(k_{yn} y_j) \\ \times \sin c \left(\frac{k_{xm} dx_i}{2}\right) \sin c \left(\frac{k_{yn} dy_i}{2}\right) \sin c \left(\frac{k_{xm} dx_j}{2}\right) \\ \times \sin c \left(\frac{k_{yn} dy_j}{2}\right)$$

(1)

where the mode number m represents an mth mode associated with the x dimension and the mode number n represents an nth mode associated with the y dimension. The terms aand b are the metal plane widths in the x and y directions, respectively, and two ports are located at  $(x_i, y_i)$  and  $(x_j, y_j)$ with an electrically small size  $(dx_i, dy_i)$  and  $(dx_j, dy_j)$ , respectively. The constant  $C_m^2 C_n^2 = 1$ , for m = n = 0;  $C_m^2 C_n^2 = 2$ , for  $m = 0, n \neq 0$  or  $m \neq 0, n = 0$ ; and  $C_m^2 C_n^2 = 4$ , for  $m \neq 0$ ,  $n \neq 0$ . When considering a low-loss case,  $k = k_r - jk_i$  and  $k_i = (k_r/2)(\tan(\delta) + (r/d))$ , where  $k_r$  is  $\omega \sqrt{\mu\varepsilon}$ ,  $\tan(\delta)$  is the loss tangent in the dielectric, and r and d are the skin depth in the metal plane and the thickness of the metal plane, respectively.

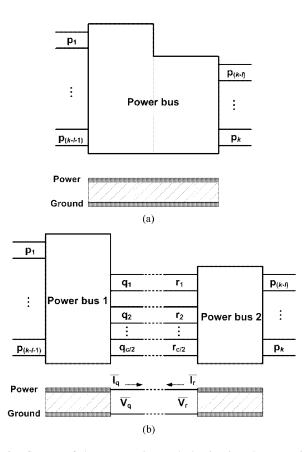

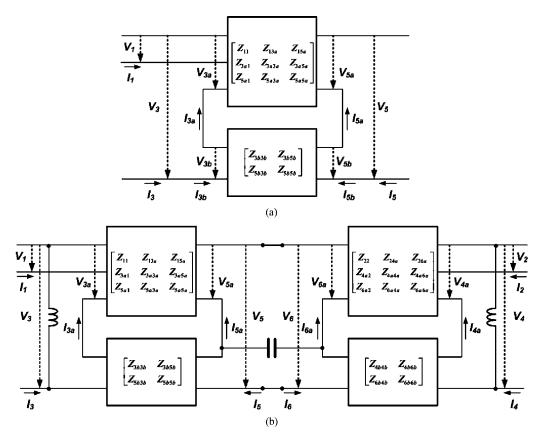

Fig. 3. Concept of the segmentation method using impedance matrices. (a) Irregular power bus including k external ports  $(p_1 \sim p_k)$ . (b) Equivalent representation of the irregular power bus using two rectangular power buses with internal c ports  $(q_1 \sim q_{c/2} \text{ and } r_1 \sim r_{c/2})$ .

The function  $\sin c(x) = 1$ , for x = 0, and  $\sin c(x) = \sin(x)/x$ , for  $x \neq 0$ . For  $(x_i, y_i) \neq (x_j, y_j)$ , the term  $Z_{ij}$  in (1) represents the transfer impedance between the two ports, and  $Z_{ii}$  represents the self-impedance at port  $(x_i, y_i)$ .

The impedance expression in (1) is very useful when characterizing a power bus consisting of a single rectangular power/ground cavity. However, in practical packages, a power bus will contain many rectangular power/ground plane cavities in a substrate. Furthermore, a power plane is often split into two planes by a gap to reduce noise coupling, as described in Fig. 1. Therefore, in this study, to analyze the split power bus in the multilayered package, we combined the resonant cavity model of (1) with a segmentation method, which was introduced in previous papers [17]–[20].

The segmentation method was originally proposed to analyze 2-D microwave planar circuits and to calculate the impedance, even when the power bus is a power/ground plane of an arbitrary shape. In the segmentation method, the power bus is segmented into rectangular power buses and the interconnections between the rectangular power buses are represented by a finite number of internal ports. The accuracy of the segmentation method is then determined by the number of ports used for the interconnections between the rectangular power buses.

Fig. 3 illustrates the concept of the segmentation method. When there is a power bus consisting of power/ground planes of arbitrary shape, like in Fig. 3(a), the power bus can be represented by a combination of two rectangular power buses and cinternal ports, as shown in Fig. 3(b). When the c internal connected ports are divided into two groups, q and r, Z matrices can be written for all ports as in

$$\begin{bmatrix} \bar{V}_p \\ \bar{V}_q \\ \bar{V}_r \end{bmatrix} = \begin{bmatrix} \tilde{Z}_{pp} & \tilde{Z}_{pq} & \tilde{Z}_{pr} \\ \tilde{Z}_{qp} & \tilde{Z}_{qq} & \tilde{Z}_{qr} \\ \tilde{Z}_{rp} & \tilde{Z}_{rq} & \tilde{Z}_{rr} \end{bmatrix} \begin{bmatrix} \bar{I}_p \\ \bar{I}_q \\ \bar{I}_r \end{bmatrix}$$

(2)

where  $\bar{V}_p$  and  $\bar{I}_p$  are the voltages and currents at the k external ports. In addition,  $\bar{V}_q$ ,  $\bar{V}_r$ ,  $\bar{I}_q$ , and  $\bar{I}_r$  are the voltages and currents at the c internal ports. The impedance matrices in (2) represent impedances between the voltages and the currents at the external ports and the internal ports.

The voltage and the current relation in (3) represents voltage and current conditions applied when the two rectangular power buses in Fig. 3(b) are connected to each other by the internal ports

$$\bar{V}_q = \bar{V}_r$$

$$\bar{I}_q + \bar{I}_r = 0.$$

(3)

Then, by substituting equations of (3) into (2) and by eliminating the internal ports  $\bar{V}_q$ ,  $\bar{V}_r$ ,  $\bar{I}_q$ , and  $\bar{I}_r$ , the external impedance matrix of the overall network is expressed as

$$\tilde{Z}_p = \tilde{Z}_{pp} + (\tilde{Z}_{pq} - \tilde{Z}_{pr})(\tilde{Z}_{qq} - \tilde{Z}_{qr} - \tilde{Z}_{rq} + \tilde{Z}_{rr})^{-1} \times (\tilde{Z}_{rp} - \tilde{Z}_{qp}).$$

(4)

The term  $Z_p$  in (4) describes the impedances between the voltages and the currents at the external ports when the internal ports q and r are connected. Then, the expression of (4) can be applied to an analysis of a power bus shaped like that shown in Fig. 3(a). The accuracy of the segmentation method has been demonstrated by showing close agreement between the calculated and the measured results in previous papers [17]–[20]. The expression for the impedance matrices of (4) is useful for the analysis of arbitrary power/ground planes and can be applied further to analyze a split power bus.

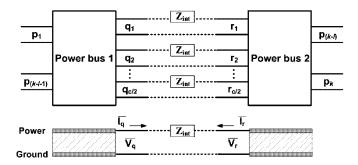

For example, a ground plane is shared by power bus 1 and power bus 2, and the two power planes are connected by c internal ports and by an impedance matrix  $\tilde{Z}_{int}$ , as shown in Fig. 4. The voltage and the current relations (3) are then modified to

$$\bar{V}_q = \bar{V}_r + \tilde{Z}_{int} \overline{I_q}$$

$$\bar{I}_q = -\bar{I}_r$$

(5)

where

$$\tilde{Z}_{\rm int} = \begin{bmatrix} Z_{\rm int} & 0 & \cdots & 0 \\ 0 & Z_{\rm int} & \cdots & 0 \\ \vdots & \vdots & \ddots & 0 \\ 0 & 0 & 0 & Z_{\rm int} \end{bmatrix} \quad (c/2 \text{ by } c/2 \text{ matrix}).$$

Now substituting (5) into (4), we obtain the Z matrix as

$$\tilde{Z}_p = \tilde{Z}_{pp} + (\tilde{Z}_{pq} - \tilde{Z}_{pr})(\tilde{Z}_{qq} - \tilde{Z}_{qr} - \tilde{Z}_{rq} + \tilde{Z}_{rr} + \tilde{Z}_{int})^{-1} \times (\tilde{Z}_{rp} - \tilde{Z}_{qp}).$$

(6)

Fig. 4. Concept of enhanced segmentation method using impedance matrices. When the power plane includes a discontinuity modeled by the impedance matrix  $\tilde{Z}_{int}$ , the overall impedances of the power bus can be calculated based on the current and the voltage relations at the internal ports  $q_1 \sim q_{c/2}$  and  $r_1 \sim r_{c/2}$ .

When a gap in a split power bus is modeled by an impedance matrix  $\tilde{Z}_{int}$  we can calculate the self-impedance  $(Z_{ii})$  and the transfer impedance  $(Z_{ij})$  of the split power bus.

In the next section, we will derive an analytical equation to calculate the model parameter of the split gap that is embedded between two ground planes. The analytical equation is to be applied to the analysis of a split power bus in a multilayered package.

## B. Lumped Circuit Modeling of Gap on Split Power Bus in Multilayered Package

In the previous section, we introduced the resonant cavity model and the segmentation method for calculating the impedances of arbitrary power bus structures. To apply the methods to the analysis of a split power bus in a multilayered package, a gap is modeled using an equivalent lumped circuit model and an analytical equation for the model is derived.

The split power bus has been used as a low-cost structure to prevent noise propagation from noise sources to susceptible devices. When there is no other conductive connection between the two power planes, capacitive coupling across the gap is the primary noise coupling mechanism between the two power planes. Therefore, a split power bus can be modeled by the coupling capacitance at the gap and two pairs of the power/ground planes.

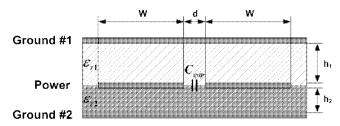

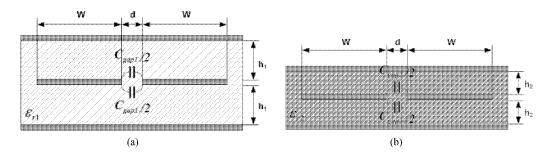

In this paper, we analyze a split power bus, the split power planes of which are embedded between two ground planes with dielectric insulators of different thicknesses  $(h_1 \text{ and } h_2)$  and different dielectric constants  $(\varepsilon_{r1} \text{ and } \varepsilon_{r2})$ , as shown in Fig. 5. We considered the two power planes embedded in the multilayered package as a parallel-coupled stripline and the capacitances  $(C_{\text{gap1}} \text{ and } C_{\text{gap2}})$  are segmented as shown in Fig. 6 in order to derive an analytical equation for the capacitance  $(C_{\text{gap}})$  of Fig. 5. The capacitance  $(C_{\text{gap}})$  is for a unit length of the gap.

The even-mode and odd-mode capacitances of the parallelcoupled striplines shown in Fig. 6 are provided by (7) and (8) [23]

$$C_{\text{even}} = 4\varepsilon_r \frac{K(k_e)}{K(k'_e)} (\text{F/m})$$

(7)

Fig. 5. Modeling of a gap between the power planes embedded in an inhomogeneous dielectric insulator with different thicknesses  $(h_1 \text{ and } h_2)$  and different dielectric constants ( $\varepsilon_{r1}$  and  $\varepsilon_{r2}$ ). Because the capacitive coupling is the dominant noise coupling path in the split power bus, the gap can be modeled by a capacitor  $C_{\text{gap}}$  (in farads per meter).

where

$$k_e = \tanh(\pi w/4h) \tanh(\pi/4(w+d/h))$$

and  $k'_e = \sqrt{1-k_e^2}$ , and

$$C_{\rm odd} = 4\varepsilon_r \frac{K(k_o)}{K(k'_o)} \,({\rm F/m}) \tag{8}$$

where  $k_o = (\tanh(\pi w/4h))/(\tanh(\pi/4(w+d/h)))$  and  $k'_o = \sqrt{1-k_o^2}$ .

Here, K(k) is a complete elliptical integral of the first kind

$$K(k) = \frac{\pi}{2} \sum_{n=0}^{\infty} \left[ \frac{(2n-1)!!}{2n!!} \right]^2 k^{2n}.$$

(9)

By the definition of the odd-mode and the even-mode capacitances in parallel-coupled stripline [24], the capacitance of the split gap is the difference between the odd-mode capacitance and the even-mode capacitance, as described in (10)

$$C_{\text{gap1}} = C_{\text{odd1}} - C_{\text{even1}}$$

=  $2\varepsilon_{r1} \left( \frac{K(k_{o1})}{K(k'_{o1})} - \frac{K(k_{e1})}{K(k'_{e1})} \right) \text{ (F/m)}$

$C_{\text{gap2}} = C_{\text{odd2}} - C_{\text{even2}}$

=  $2\varepsilon_{r2} \left( \frac{K(k_{o2})}{K(k'_{o2})} - \frac{K(k_{e2})}{K(k'_{e2})} \right) \text{ (F/m)}$  (10)

where

$$\begin{aligned} k_{e1} &= \tanh\left(\frac{\pi w}{4h_1}\right) \tanh\left(\frac{\pi}{4}\left(\frac{w+d}{h_1}\right)\right) \\ k'_{e1} &= \sqrt{1-k_{e1}^2} \\ k_{o1} &= \frac{\tanh\left(\frac{\pi w}{4h_1}\right)}{\tanh\left(\frac{\pi}{4}\left(\frac{w+d}{h_1}\right)\right)}, \quad k'_{o1} &= \sqrt{1-k_{o1}^2} \\ k_{e2} &= \tanh\left(\frac{\pi w}{4h_2}\right) \tanh\left(\frac{\pi}{4}\left(\frac{w+d}{h_2}\right)\right) \\ k'_{e2} &= \sqrt{1-k_{e2}^2} \\ k_{o2} &= \frac{\tanh\left(\frac{\pi w}{4h_2}\right)}{\tanh\left(\frac{\pi}{4}\left(\frac{w+d}{h_2}\right)\right)}, \quad k'_{o2} &= \sqrt{1-k_{o2}^2} \\ k'_{o2} &= \sqrt{1-k_{o2}^2}. \end{aligned}$$

Fig. 6. Modeling of the gap capacitance between two split power planes embedded in a substrate with a homogeneous dielectric insulator. The capacitance representing the model of the gap ( $C_{gap1}$  and  $C_{gap2}$ ) comprises two respective capacitors ( $C_{gap1}/2$  and  $C_{gap2}/2$ ).

Because the capacitance  $C_{\text{gap}}$  in Fig. 5 can be approximated by the sum of  $C_{\text{gap1}}/2$  and  $C_{\text{gap2}}/2$  shown in Fig. 6, the capacitance of the gap is given by

$$C_{\text{gap}} \cong \frac{C_{\text{gap1}} + C_{\text{gap2}}}{2}$$

=  $\varepsilon_{r1} \left( \frac{K(k_{o1})}{K(k'_{o1})} - \frac{K(k_{e1})}{K(k'_{e1})} \right)$

+  $\varepsilon_{r2} \left( \frac{K(k_{o2})}{K(k'_{o2})} - \frac{K(k_{e2})}{K(k'_{e2})} \right)$ (F/m). (11)

Using (11), we can calculate the capacitance representing the model of the gap  $C'_{\text{gap}}$  and the impedance matrix  $\tilde{Z}_{\text{int}}$  for an analysis of a split power bus in a multilayered package, resulting in

$$\tilde{Z}_{int} = \begin{bmatrix} \frac{1}{j\omega C'_{gap}} & 0 & \cdots & 0\\ 0 & \frac{1}{j\omega C'_{gap}} & \cdots & 0\\ \vdots & \vdots & \ddots & 0\\ 0 & 0 & 0 & \frac{1}{j\omega C'_{gap}} \end{bmatrix}$$

$$(c/2 \text{ by } c/2 \text{ matrix}). \quad (12)$$

### C. Analysis of Split Power Bus in Multilayered Package

In this section, we propose a port assignment technique for a split power bus in a multilayered package, and we combine this technique with the hybrid analytical modeling method, including the resonant cavity model and the segmentation method presented in the previous section.

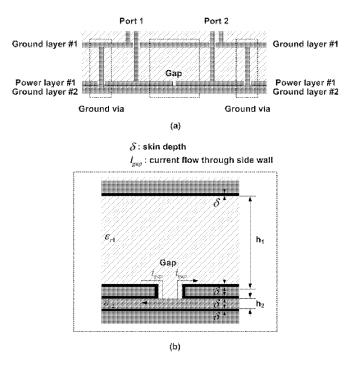

As the system-switching frequency increases, the frequency of interest in the power bus design also increases and then skin effect becomes evident, causing the surface current at the plane to decay rapidly as it penetrates a conductor surface. This skineffect approximation makes it possible to divide the multilayered power bus into multiple pairs of vertically two-layered power buses. Analytical modeling methods based on the skin-effect approximation for a multilayered solid power bus have been developed, and these modeling methods have been found to be experimentally valid when the conductor thickness  $t \ge 3\delta$ , where  $\delta$  is the skin depth [25].

Fig. 7. Cross section of a split power bus structure in a multilayered package, with the skin effect in the gap. (a) The power bus consists of three layers: two ground layers and one power layer. The power plane is split into two separate planes, which are embedded in inhomogeneous dielectric insulators with different thicknesses ( $h_1$  and  $h_2$ ) and different dielectric constants ( $\varepsilon_{r1}$  and  $\varepsilon_{r2}$ ), and two ports (Port 1 and Port 2) for impedance measurements are connected to each split power plane referenced to the upper common ground plane of ground layer 1. (b) The surface current at the power plane decays rapidly as it penetrates at high frequency because of skin effect; nevertheless, the current can be conducted vertically through the side wall of the gap in the split power planes embedded between two ground planes.

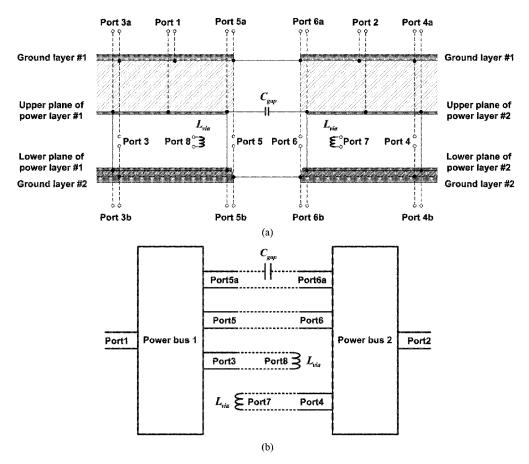

It is impossible to analyze the split power bus in the multilayered package with the same analysis assumptions used for a solid power bus. As shown in Fig. 7(a) and (b), the current can be conducted from the upper power plane of power layer 1 to the lower power plane of power layer 1 through the sidewall of the gap. Therefore, we cannot separate a split power bus in a multilayered package simply into two pairs of power buses with the skin-effect approximation of [25]. Hence, in this paper, we define virtual ports (Port 3, Port 4, Port 5, and Port 6) between ground layer 1 and ground layer 2, as shown in Fig. 8(a), so that the virtual ports enable the segmentation method to analyze the split power bus in the multilayered package by considering

Fig. 8. Model and ports assignment of a split power bus in a multilayered package. (a) Equivalent circuit model for a split power bus in a multilayered package; four virtual ports (Port 3, Port 4, Port 5, and Port 6) are assigned additionally to consider current flow. (b) Ports assignment for segmentation method.

the current flow through the sidewall of the gap. Of the virtual ports, Port 5 and Port 6 are defined for the slot, while Port 3 and Port 4 are defined to consider the ground via connecting the two ground layers, 1 and 2, because current can be conducted through the sidewall of the via void between the upper plane and bottom plane of power layer 1.

Fig. 8(b) shows the port assignments, including the virtual ports by which to apply the segmentation method to analyze a split power bus in a multilayered package. Using the proposed segmentation method and the impedance matrices at the ports described in Fig. 8(b), we can calculate the self-impedance  $(Z_{ii})$  and the transfer impedance  $(Z_{ij})$  at Port 1 and Port 2. When the internal connected ports are the same as group q (Port 3, Port 5a, Port 5, and Port 7) and group r (Port 4, Port 6a, Port 6, and Port 8), the Z matrices of all ports can be written as follows:

$$\begin{bmatrix} \bar{V}_p \\ \bar{V}_q \\ \bar{V}_r \end{bmatrix} = \begin{bmatrix} \tilde{Z}_{pp} & \tilde{Z}_{pq} & \tilde{Z}_{pr} \\ \tilde{Z}_{qp} & \tilde{Z}_{qq} & \tilde{Z}_{qr} \\ \tilde{Z}_{rp} & \tilde{Z}_{rq} & \tilde{Z}_{rr} \end{bmatrix} \begin{bmatrix} \bar{I}_p \\ \bar{I}_q \\ \bar{I}_r \end{bmatrix}$$

(13)

where

1

$$ar{V}_p = \begin{bmatrix} V_1 \\ V_2 \end{bmatrix}, \quad ar{V}_q = \begin{bmatrix} V_3 \\ V_7 \\ V_{5a} \\ V_5 \end{bmatrix}, \quad ar{V}_r = \begin{bmatrix} V_8 \\ V_4 \\ V_{6a} \\ V_6 \end{bmatrix}$$

Fig. 9. Equivalent network representation for a split power bus in a multilayered package. (a) Equivalent network representation of the left half on the split power bus. (b) Equivalent network representation of the split power bus, including via and gap model.

Then the overall impedance matrix is calculated by

$$\tilde{Z}_{p} = \begin{bmatrix} Z_{11\_overall} & Z_{12\_overall} \\ Z_{21\_overall} & Z_{22\_overall} \end{bmatrix} \\

= \tilde{Z}_{pp} + (\tilde{Z}_{pq} - \tilde{Z}_{pr})(\tilde{Z}_{qq} - \tilde{Z}_{qr} - \tilde{Z}_{rq} + \tilde{Z}_{rr} + \tilde{Z}_{int})^{-1} \\

\times (\tilde{Z}_{rp} - \tilde{Z}_{qp})$$

(14)

where

Г **с**

As a result, we can calculate the self-impedance  $(Z_{ii})$  and the transfer impedance  $(Z_{ij})$  at ports 1 and 2 on the split power bus in the multilayered package using (14) after we calculate the impedances in (14). Among the impedances in (14), we can calculate the self-impedances and the transfer impedances at all ports, except the virtual ports, using the resonant cavity model (1). Then, the impedance of the virtual ports (Port 3, Port 4, Port 5, and Port 6) should be calculated.

To calculate the impedance relating to the virtual ports, consider the left section of the power bus, including Port 1, in Fig. 8(a). The impedances for Port 1, Port 3a, and Port 5a are computed for the plane pair consisting of ground layer 1 and the  $\begin{bmatrix} V_1 \\ V_{3a} \\ V_{5a} \end{bmatrix} = \begin{bmatrix} Z_{11} & Z_{13a} & Z_{15a} \\ Z_{3a1} & Z_{3a3a} & Z_{3a5a} \\ Z_{5a1} & Z_{5a3a} & Z_{5a5a} \end{bmatrix} \begin{bmatrix} I_1 \\ I_{3a} \\ I_{5a} \end{bmatrix}.$  (15)

In addition, the impedance matrix for Port 3b and Port 5b for the plane pair composed of ground layer 2 and the lower plane of power layer 1 can be computed as

$$\begin{bmatrix} V_{3b} \\ V_{5b} \end{bmatrix} = \begin{bmatrix} Z_{3b3b} & Z_{3b5b} \\ Z_{5b3b} & Z_{5b5b} \end{bmatrix} \begin{bmatrix} I_{3b} \\ I_{5b} \end{bmatrix}.$$

(16)

In (15) and (16), we can calculate the impedances using the resonant cavity model.

The equivalent circuit representation for the left section of the power bus in Fig. 8(a) is shown in Fig. 9(a) [25]. From Fig. 9(a), the current-voltage relations for the plane structure are given as follows:

$$i_3 = i_{3a} = i_{3b}, \quad i_5 = i_{5a} = i_{5b}$$

$V_3 = V_{3a} + V_{3b}, \quad V_5 = V_{5a} + V_{5b}.$  (17)

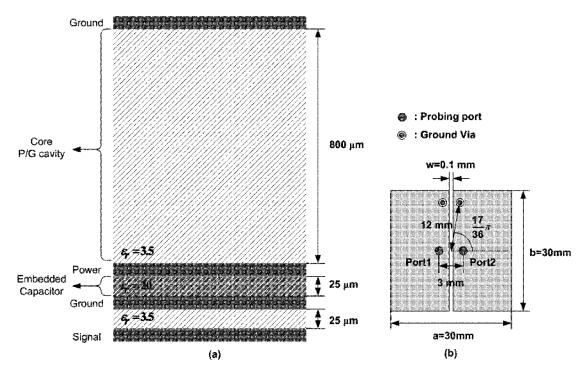

Fig. 10. Test package substrate structure with embedded capacitor. (a) Cross section of the test package substrate, where the thicknesses of the core substrate and the high-k thin film are 800 and 25  $\mu$ m, respectively, and their permittivities are 3.5 and 20, respectively. (b) The power plane is split into two power planes by a gap with dimensions of w = 0.1 mm and b = 30 mm.

Based on these relations, the impedance matrices (15) and (16) of the split power bus in Fig. 8(a), as follows: can be combined, resulting in an impedance matrix

$$\begin{bmatrix} Z_{11} & Z_{13} & Z_{15} & Z_{15a} \\ Z_{31} & Z_{33} & Z_{35} & Z_{35a} \\ Z_{51} & Z_{53} & Z_{55} & Z_{55a} \\ Z_{5a1} & Z_{5a3} & Z_{5a5} & Z_{5a5a} \end{bmatrix}$$

$$= \begin{bmatrix} Z_{11} & Z_{13a} & Z_{15a} & Z_{15a} \\ Z_{3a1} & Z_{3a3a} + Z_{3b3b} & Z_{3a5a} + Z_{3b5b} & Z_{3a5a} \\ Z_{5a1} & Z_{5a3a} + Z_{5b3b} & Z_{5a5a} + Z_{5b5b} & Z_{5a5a} \\ Z_{5a1} & Z_{5a3a} & Z_{5a5a} & Z_{5a5a} \end{bmatrix}.$$

(18)

For example, we can obtain  $Z_{15} = V_1/I_5 = V_1/I_{5b} =$  $V_1/I_{5a} = Z_{15a}$  using (17) and  $Z_{51} = Z_{15} = Z_{15a} = Z_{5a1}$ with reciprocal network assumption, and we can also ob- $Z_{35} = V_3/I_5 = V_{3a} + V_{3b}/I_5 = V_{3a}/I_5 + V_{3b}/I_5 =$ tain  $V_{3a}/I_{5a} + V_{3b}/I_{5b} = Z_{3a5a} + Z_{3b5b}$  using (17) and  $Z_{35} = Z_{53} = Z_{3a5a} + Z_{3b5b} = Z_{5a3a} + Z_{5b3b}$  with reciprocal network assumption.

From (18), the impedances between Port 1, Port 3, Port 5, and Port 5a can be calculated. For example, the transfer impedance  $Z_{13}$  between Port 1 and virtual Port 3 is equal to the transfer impedance  $Z_{13a}$  between Port 1 and Port 3a, and the transfer impedance  $Z_{35}$  between virtual Port 3 and virtual Port 5 is equal to sum of transfer impedance  $Z_{3a5a}$  and transfer impedance  $Z_{3b5b}$ . In addition, we can calculate the impedance matrix relating to Port 2, Port 4, Port 6, and Port 6a on the right section

$$\begin{bmatrix} Z_{22} & Z_{24} & Z_{26} & Z_{26a} \\ Z_{42} & Z_{44} & Z_{46} & Z_{46a} \\ Z_{62} & Z_{64} & Z_{66} & Z_{66a} \end{bmatrix}$$

$$= \begin{bmatrix} Z_{22} & Z_{24a} & Z_{26a} & Z_{26a} \\ Z_{4a2} & Z_{4a4a} + Z_{4b4b} & Z_{4a6a} + Z_{4b6b} & Z_{4a6a} \\ Z_{6a2} & Z_{6a4a} + Z_{6b4b} & Z_{6a6a} + Z_{6b6b} & Z_{6a6a} \\ Z_{6a2} & Z_{6a4a} & Z_{6a6a} & Z_{6a6a} \end{bmatrix}.$$

(19)

Fig. 9(b) shows the equivalent network representation for the split power bus in the multilayered package shown in Fig. 8(a), including the right-hand section of the split power bus and the lumped circuit models for the vias and the split gap. The impedance parameters in the boxes can be computed using the methods previously described. Then, the external impedance parameters  $(Z_{11}, Z_{12}, Z_{21}, Z_{22})$  of Port 1 and Port 2 are calculated from these impedances, using the proposed enhanced segmentation method.

## **III. VERIFICATION AND APPLICATION OF HYBRID ANALYTICAL** MODELING METHOD

#### A. Verification of Hybrid Analytical Modeling Method

To verify the proposed hybrid analytical modeling method, test package substrates were designed and fabricated for Z-parameter measurement, and the measured results were compared with the calculated results to verify the accuracy of the model. Fig. 10 illustrates the layout and the cross-section of the test package substrate.

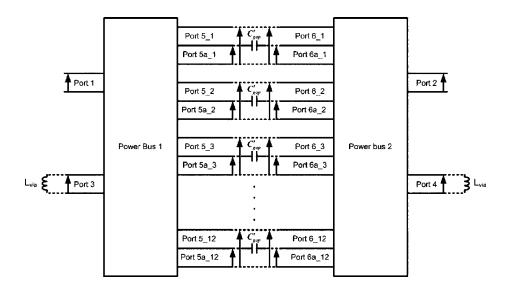

Fig. 11. Ports assignment and equivalent circuit model of the split power bus with the embedded capacitor. Port  $5_1$ -Port  $5_1$ -Port  $5_2$ -Po

As shown in Fig. 10(a), the test package substrate comprises four conductor layers with dimensions a = 30 mm and b = 30mm. BT resin was used as the dielectric material of the core substrates with permittivity  $\varepsilon_r = 3.5$  and thickness d = 0.8 mm. In addition, a high-k thin film with permittivity  $\varepsilon_r = 20$  and thickness d = 0.02 mm with a pair of power/ground planes was used for the embedded capacitor, which reduces switching noise on the power bus as a decoupling capacitor. When we set the origin at the center of the test package substrate in Fig. 10(b), two probing ports are located at (-1.5, 0 mm) and (1.5, 0 mm), and two vias connecting the two ground planes are located at (0.5, 12 mm) and (-0.5, -12 mm). The power plane is split into two planes by a gap with dimensions of w = 0.1 mm and b = 30 mm. An Agilent vector network analyzer 8753ES and a Cascade GS type microprobe with 400  $\mu$ m pitch were used to measure the S parameter for a frequency range from 10 MHz to 3 GHz; then, the measured S parameters were converted to Z parameters by the conversion relation [26].

The basic analytical modeling method was described in the previous section, and it was explained that the gap is modeled using a single capacitor. However, to apply this method to the calculation of the impedance for the test package substrate, the gap should be modeled as an array of capacitors, and the number of capacitors  $(C'_{\rm gap})$  in the array is dependent upon the maximum frequency of interest, which affects the accuracy of the model. In this study, because the maximum frequency was 3 GHz and the length of the gap was 30 mm, the split power bus was modeled using 12 internal ports per plane and 12 capacitors  $C_{\rm gap}' = (C_{\rm gap} \times 30 \, {\rm mm})/12$  (Farad). Then, the total ports were defined as shown in Fig. 11, and the impedance for each port was calculated by means of the methods described in the previous sections. In Fig. 11, the inductances representing the equivalent circuit models of the vias are analytically calculated [27] and the values are approximately 0.5 nH; the capacitance representing the equivalent circuit model of the slot is calculated by (11) and the value is 0.06 pF for each capacitor of the array.

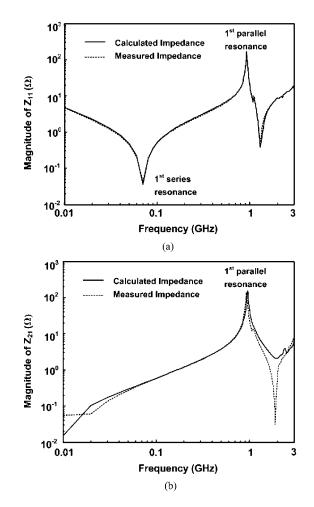

Fig. 12. Comparison of the calculated and the measured results. The solid line represents the impedances calculated using the proposed hybrid analytical modeling method, whereas the dotted line represents the impedances obtained from the measured S parameters. (a) Comparison of the calculation and the measurement of  $Z_{11}$  up to 3 GHz. (b) Comparison of the calculation and the measurement of  $Z_{21}$  up to 3 GHz.

Fig. 13. Dimensions and cross section of a test package substrate to demonstrate the optimal position of the via on the split power bus with an embedded capacitor. (a) Top view of the split power plane. (b) Cross section of the test package substrate and ports assignment.

Fig. 12 shows the self-impedance and the transfer impedances of the test package substrate shown in Fig. 10(b) obtained by both measurement and calculation. The calculated impedances show a good correlation with the measured impedances. In Fig. 12(a), the self-impedance  $(Z_{11})$  shows a series resonance at 70 MHz because of the capacitance of the embedded capacitor ( $\approx 3.47$  nF) and the effective inductance of the planes ( $\approx 1.49$  nH). In addition, the self-impedance  $(Z_{11})$  in Fig. 12(a) and the transfer impedance  $(Z_{21})$  in Fig. 12(b) show a parallel resonance at 1 GHz because of the effective inductance of the core plane cavity and the capacitance of the core plane cavity.

Fig. 12 illustrates that we can use the proposed hybrid analytical modeling method to characterize and analyze a split power bus in a multilayered package with high accuracy.

## *B.* Optimal Via Positioning for Suppression of Switching Noise Coupling on Split Power Bus With an Embedded Capacitor

In this section, we describe an optimal power bus design methodology based on the proposed hybrid modeling method to demonstrate the usefulness of the proposed modeling method. The resultant calculation results are verified by means of frequency and time-domain measurements.

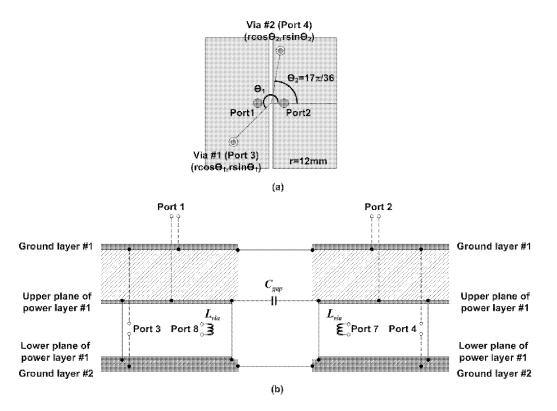

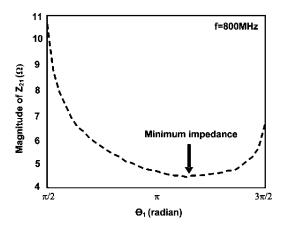

Positioning of the ground via that connects the two ground planes is a power bus design element for the test package substrate, shown in Fig. 13, used to verify the proposed hybrid analytical modeling method. We can minimize the magnitude of the transfer impedance  $Z_{21}$  by optimally positioning the via. In Fig. 13, we assume that via 1 and via 2 are located at  $(r \cos \theta_1, r \sin \theta_1)$  and  $(r \cos \theta_2, r \sin \theta_2)$  respectively. To simplify the optimization,  $\theta_2$  and r are fixed at  $17\pi/36$  and 12 mm, respectively. When  $\theta_1$  varies from  $\pi/2$  to  $3\pi/2$ , the transfer impedance  $Z_{21}$  between Port 1 and Port 2 changes. Therefore, the optimal position of via 1 can be found by scanning the calculated transfer impedances at a target frequency, using the hybrid analytical modeling method described in the previous section. Once the optimal positioning is chosen, when the target frequency is set below the first parallel resonance frequency, the impedance is minimized for a broad frequency range below the first parallel resonance frequency.

This is an efficient scheme to determine the optimal position of design elements such as the via, and it is often used in the other analysis methods, such as full-wave simulation. However, in full-wave simulation, an excessive amount of time is required to complete the calculation, because the mesh must be reconstructed and the impedance needs to be repeatedly calculated for varied port locations. In contrast, using the proposed analytical modeling method, only the impedances relating to Port 3 need to be updated to calculate the transfer impedances between Port 1 and Port 2, thereby greatly reducing the calculation time, while Port 3 indicates the position of via 1. For example, when  $\theta_1$  is changed from  $\pi/2$  to  $3\pi/2$  in 18 steps, it takes approximately four minutes to complete the computation using the proposed analytical modeling method; in contrast, the same computation takes two hours using the 3-D full-wave simulation.

Fig. 14. Calculated transfer impedance corresponding to the via 1 position at f = 800 MHz. From this graph, the optimized position of the via 1 can be obtained.

Fig. 15. Comparison of the calculation and the measurement of  $Z_{21}$  up to 3 GHz corresponding to the position of via 1. The transfer impedance is minimized at the optimized via position up to the first parallel resonance frequency when the target frequency is set at 800 MHz.

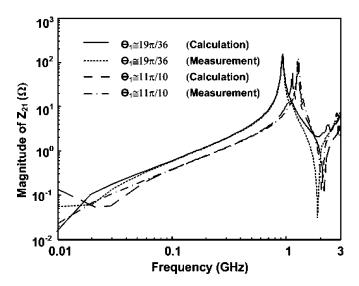

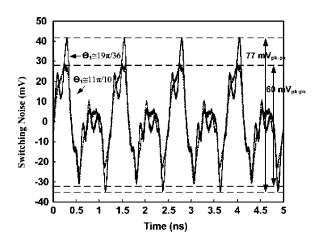

The transfer impedance was calculated using the method explained in the previous section, and Fig. 14 shows the calculated transfer impedance  $Z_{21}$  corresponding to the position of via 1 at f = 800 MHz. It was found that the transfer impedance is minimized at  $\theta_1 = 11\pi/10$ .

In Fig. 15, the measured transfer impedance  $(Z_{21})$  and the calculated transfer impedance  $(Z_{21})$  are compared when the via 1 is located at the worst position  $(\theta_1 = 19\pi/36)$  and at the optimal position  $(\theta_1 = 11\pi/10)$ . As shown in the graph, the results confirm the validity of the proposed design methodology, and it is well verified that the optimal via position reduces the magnitude of the transfer impedance  $Z_{21}$ , while  $Z_{21}$  represents the degree of switching noise coupling on the split power bus in the multilayered package. Furthermore, it is found that the first parallel resonance frequency is shifted to a higher frequency when the position of via 1 is optimized, because the optimized position of via 1 reduces the effective inductance of the plane.

Fig. 16. Calculated switching noise waveforms at Port 2 on the split power bus with an embedded capacitor. With the optimal via position ( $\theta_1 = 11\pi/10$ ), the switching noise at Port 2 was reduced from 80 to 53 mV<sub>pk-pk</sub>.

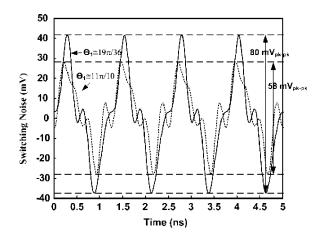

To verify the power bus design methodology using the proposed hybrid analytical modeling method in time domain, we have measured switching noise waveforms and have compared them with both the time-domain calculation data at the worst via position ( $\theta_1 = 19\pi/36$ ) and that at the optimal via position ( $\theta_1 = 11\pi/10$ ). For the time-domain calculation, a current profile on the power bus was extracted via a spice simulation, and the current spectrum was calculated using a fast Fourier transform. Subsequently, the noise voltage spectrum at Port 2 was obtained using the product of the current spectrum at port 1 and the transfer impedance of the power bus  $Z_{21}$ . Finally, the switching noise at Port 2 was calculated from the noise voltage spectrum at Port 2 using an inverse fast Fourier transform.

In this experiment, a commercial clock driver (TI CD-CVLP110) was mounted on the test package substrate as a noise source at Port 1 with 800 MHz differential clock inputs from a pulse pattern generator, and the noise was measured with an oscilloscope fitted with a high-impedance probe. Because the clock driver has differential I/O circuits, its switching noise is relatively low; therefore, we used 25- $\Omega$  and 75- $\Omega$  resistors to produce unbalanced termination conditions at differential outputs. Unbalanced termination increases the switching noise on the power bus.

The calculated switching noise waveforms are shown in Fig. 16. The chip is assumed to be located at Port 1 and the noise is calculated at Port 2 in the split power bus with an embedded capacitor. In this noise waveform, the voltage was reduced from 80 to 53 mV<sub>pk-pk</sub> by optimizing the position of via 2. Fig. 17 shows the measured switching noise waveforms, which are slightly different from the calculated result, because a commercial clock driver is used as the noise source, and it is infeasible to model the driver precisely. If a precise driver model could be provided, the switching noise could be calculated accurately from the current profile. In the measured result, the switching noise was reduced from 77 to 60 mV, and it is found that the optimization of via 1 reduces the switching noise efficiently.

Fig. 17. Measured switching noise waveforms at Port 2 on the split power bus with an embedded capacitor. With the optimal via position ( $\theta_1 = 11\pi/10$ ), the switching noise at Port 2 was reduced from 77 to 60 mV<sub>pk-pk</sub>.

#### **IV. CONCLUSION**

In this paper, a hybrid analytical modeling method for calculating the impedance of a split power bus in a multi-layered package was demonstrated, and the method was verified using fabricated test package substrates that included an embedded capacitor. The hybrid analytical modeling method used to analyze a split power bus in a multilayered package combines a resonant cavity model and a segmentation method. Especially for the analysis of a multilayered package, a port assignment technique considering vertical current flowing in the gap and an analytical equation to model the split gap were proposed. The proposed port assignment technique and the analytical equation make it possible to apply the resonant cavity model and the segmentation method to an analysis of a split power bus in a multilayered package. Subsequently, we can accurately calculate impedances of a split power bus in a multilayered package with the proposed port assignment technique. The calculated impedance shows a good correlation up to 3 GHz, and it is possible to increase the accuracy of the model when precise models of the non planar structures, such as the via and the gap, are given. Finally, the power bus design methodology was demonstrated using the hybrid analytical modeling method, and it was verified by means of frequency-domain and time-domain measurements. The measurement results show that we can effectively reduce the switching noise by means of optimal via distribution based on the proposed hybrid analytical modeling method. Using the proposed hybrid analytical modeling method, it is possible both to accurately characterize a split power bus in a multilayered package and to efficiently design a package to include a split power bus with low impedance.

#### REFERENCES

- R. R. Tummala, E. J. Rymaszewski, and A. G. Klopfenstein, *Microelectronics Packaging Handbook*, 2nd ed., New York: Chapman & Hall, 1997, part I, ch. 3.

- [2] R. R. Tummala et al., "The SOP for miniaturized, mixed-signal computing, communication, and consumer systems of the next decade," *IEEE Trans. Antennas Propag.*, vol. 27, no. 2, pp. 250–2672, May 2004.

- [3] H. Sasaki, et al., "Electromagnetic interference (EMI) issues for mixedsignal system-on-package (SOP)," in Proc. IEEE Electronic Components and Technology, 2004, pp. 1437–1441.

- [4] T. Sudo, H. Sasaki, N. Masuda, and J. L. Drewniak, "Electromagnetic interference (EMI) of system-on-package (SOP)," *IEEE Trans. Antennas Propag*, vol. 27, no. 2, pp. 304–314, May 2004.

- [5] H. Kim et al., "Significant reduction of power/ground inductive impedance and simultaneous switching noise by using embedded film capacitor," in *Proc. IEEE Topical Meeting Electrical Performance of Electronic Pack*aging, Oct. 2003, pp. 129–132.

- [6] H. Kim, B. K. Sun, and J. Kim, "Suppression of GHz range power/ground inductive impedance and simultaneous switching noise using embedded film capacitors in multilayer packages and PCBs," *IEEE Microw. Wireless Compon. Lett.*, vol. 14, no. 2, pp. 71–73, Feb. 2004.

- [7] P. Heydari and M. Pedram, "Analysis of jitter due to power-supply noise in phase-locked loops," in *Proc. IEEE Custom Integrated Circuit Conf.*, 2000, pp. 443–446.

- [8] , "Jitter-induced power/ground noise in CMOS PLLs: A design perspective," in *Proc. IEEE Custom Integrated Circuit Conf.*, 2001, pp. 209– 213.

- [9] H. H. Wu, J. W. Meyer, K. Lee, and A. Barber, "Accurate power supply and ground plane pair models," in *Proc. IEEE Topical Meeting on Electrical Performance of Electronic Packaging*, Oct. 26–28, 1998, pp. 163–166.

- [10] I. Novak, "Reducing simultaneous switching noise and EMI on ground/power planes by dissipative edge termination," *IEEE Trans. Antennas Propag*, vol. 22, no. 3, pp. 274–283, Aug. 1999.

- [11] S. Van den Berghe, F. Olyslager, D. De Zutter, J. De Moerloose, and W. Temmerman, "Study of the ground bounce caused by power plane resonances," *IEEE Trans. Electromagn. Compat.*, vol. 40, no. 2, pp. 111– 119, May 1998.

- [12] Y. Ji and T. H. Hubing, "EMAP5: A 3-D hybrid FEM/MOM code," Appl. Computat. Electromagn. Soc. J., vol. 15, no. 1, pp. 1–12, Mar. 2000.

- [13] I. Novak, "Accuracy considerations of power-ground plane models," in Proc. IEEE Topical Meeting Electrical Performance of Electronic Packaging, Oct. 1999, pp. 153–156.

- [14] G. T. Lei, R. W. Techentin, and B. K. Gilbert, "High-frequency characterization of power/ground-plane structures," *IEEE Trans. Microw. Theory Tech.*, vol. 47, no. 2, pp. 562–569, May 1999.

- [15] M. Xu and T. H. Hubing, "Estimating the power bus impedance of printed circuit boards with embedded capacitance," *IEEE Trans. Antennas Propag*, vol. 25, no. 3, pp. 424–432, Aug. 2002.

- [16] Z. L. Wang, O. Wada, Y. Toyota, and R. Koga, "Convergence acceleration and accuracy improvement in power bus impedance calculation with a fast algorithm using cavity modes," *IEEE Trans. Electromagn. Compat.*, vol. 47, no. 1, pp. 2–9, Feb. 2005.

- [17] T. Okoshi, Planar Circuits for Microwaves and Lightwaves. Munich, Germany: Springer-Verlag, 1985, ch. 2.

- [18] T. Okoshi, Y. Uehara, and T. Takeuchi, "The segmentation method— An approach to the analysis of microwave planar circuits," *IEEE Trans. Microw. Theory Tech.*, vol. 24, no. 10, pp. 662–668, Oct. 1976.

- [19] R. Chadha and K. C. Gupta, "Segmentation method using impedance matrices for analysis of planar microwave circuits," *IEEE Trans. Microw. Theory Tech.*, vol. 29, no. 1, pp. 71–74, Jan. 1981.

- [20] R. Sorrentino, "Planar circuits, waveguide models, and segmentation method," *IEEE Trans. Microw. Theory Tech.*, vol. 33, no. 10, pp. 1057– 1066, Oct. 1985.

- [21] Z. L. Wang, O. Wada, Y. Toyota, and R. Koga, "Modeling of gapped power bus structures for isolation using cavity modes and segmentation," *IEEE Trans. Electromagn. Compat.*, vol. 47, no. 2, pp. 210–218, May 2005.

- [22] L. Zhang, B. Archambeault, S. Conner, J. L. Knighten, J. Fan, N. W. Smith, R. Alexander, R. E. DuBroff, and J. L. Drewniak, "A circuit approach to model narrow slot structures in a power bus," in *Proc. IEEE Int. Symp. Electromagnetic Compatibility*, vol. 2, Aug. 2004, pp. 401–406.

- [23] D. Homentcovschi, A. Manolescu, A. M. Manolescu, and L. Kreindler, "An analytical solution for the coupled stripline-like microstrip line problem," *IEEE Trans. Microw. Theory Tech.*, vol. 36, no. 6, pp. 1002–1007, Jun. 1998.

- [24] K. G. Gupta, *Microstrip Lines and Slotlines*. Norwood, MA: Artech House, 1996, ch. 8.

- [25] N. Na, J. Choi, S. Chun, M. Swaminathan, and J. Srinivasan, "Modeling and transient simulation of planes in electric package," *IEEE Trans. Antennas Propag*, vol. 23, no. 3, pp. 340–352, Aug. 2000.

- [26] D. M. Pozar, Microwave Engineering. New York: Wiley, 1998, ch. 4.

- [27] H. W. Johnson and M. Graham, *High-Speed Digital Design—A Hand Book of Back Magic*. Englewood Cliffs, NJ: Prentice Hall, 1993, ch. 7.

**Youchul Jeong** received the B.S. and M.S. degrees from the Korea Advanced Institute of Science and Technology, Daejeon, Korea, in 1999 and 2001, respectively, both in electrical engineering.

He has been working with extraction of dielectric constant from blood glucose, reduction of EMI from PDP, design of power distribution network on package, and characterization of embedded capacitor. His current research interest includes power bus design for high-speed mixed mode system-on-package using embedded capacitor.

**Boon K. Lok** received the B.Sc. and M.Sc. degrees from the National University of Singapore, Singapore, in 1991 and 2000, respectively, both in physics.

He is currently a Senior Research Officer in the Micro-joining and Substrate Technology Group, Singapore Institute of Manufacturing Technology, Singapore. His research interests include the development of embedded passive manufacturing technology and micro-jetting for electronics applications.

Albert Chee W. Lu (S'96–M'98) received the B.Eng. and Ph.D. degrees in electrical engineering from UMIST, Manchester, U.K., in 1994 and 1998, respectively and is currently the Acting Group Manager and Research Scientist with the Micro-Joining and Substrate Technology Group at the Singapore Institute of Manufacturing Technology, Singapore. He spearheads research and development activities in package design, broadband modelling, signal integrity simulation, and high-speed characterization. Since 1999, he has also initiated and was the Project Leader for

major industry collaborations on optical networking, high-performance computing, and next-generation wireless applications including the High Density Substrate Consortium, Broadband Consortium, and Integrated Passives Consortium.

Dr. Lu is a Member of the IEEE CPMT and MTT Societies, Advisory Board Member for Globaltronics, and Singapore Chief Delegate for the Micromachine Summit 2005.

**Hyunjeong Park** received the B.S. degree in physics from the Yonsei University, Seoul, Korea, and the M.S. degree in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea. She is currently pursuing the Ph.D. degree in electrical engineering from KAIST.

Her current research interest includes the chip/ package comodeling and codesign of power/ground network for high-speed digital system.

Lai Lai Wai received the B.Eng. degree in electronics engineering from UMIST, Manchester, U.K., in 1994. She is a Senior Research Officer with Singapore Institute of Manufacturing Technology, Singapore. She is working on the development of design and modeling methodologies for interconnects and embedded passives in high-speed applications.

Joungho Kim (A'04–M'04) received the B.S. and M.S. degrees from the Seoul National University, Seoul, Korea, in 1984 and 1986, respectively, and the Ph.D degree from the University of Michigan, Ann Arbor, in 1993, all in electrical engineering. During his graduate study, he was involved in femtosecond time-domain optical measurement technique for high-speed device and circuit testing.

In 1993, he joined the Picometrix, Inc., Ann Arbor, to work as a Research Engineer, where he was responsible for development of picosecond sampling

systems and 70-GHz photoreceivers. In 1994, he joined the Memory Division of Samsung Electronics, Kiheung, Korea, where he was engaged in gigabit-scale DRAM design. In 1996, he moved to the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea. He is currently an Associate Professor in the Electrical Engineering and Computer Science Department. Since joining KAIST, his research has centered on modeling, design, and measurement of high-speed interconnection, packages, and PCBs. His research topics especially include design issues of signal integrity, power/ground noise, and radiated emission in high-speed SerDes channel, system-on-package, and multilayer PCBs. He was on sabbatical leave during the academic year from 2001 to 2002 at Silicon Image Inc., Sunnyvale, CA, as a Staff Engineer. He was responsible for low-noise package design of SATA, FC, and Panel Link SerDes devices. He has more than 160 publications in refereed journals and conferences.

Dr. Kim has been the Chair or the Cochair of the EDAPS workshop since 2002. Currently, he is an Associate Editor of the IEEE TRANSACTIONS ON ELECTROMAGNETIC COMPATIBILITY.

Wei Fan (M'02) received the B.Eng. and M.Eng. degrees from the Harbin Institute of Technology, China, in 1982 and 1986, respectively, both in electrical engineering.

As a Research Engineer with Micro-joining and Substrate Technology Group, Singapore Institute of Manufacturing Technology, Singapore, he is currently working on the design, modeling, and characterization of high-density substrate and high-speed interconnections over gigahertz frequency range. He also has many years of experience in the design and

applications of analog and digital circuits. Mr. Fan is a Member of the IEEE CPMT and MTT Societies.