# Hybrid atomic force/scanning tunneling lithography

Kathryn Wilder, a) Hyongsok T. Soh, Abdullah Atalar, b) and Calvin F. Quate E. L. Ginzton Laboratory, Stanford University, Stanford, California 94305-4085

(Received 16 January 1997; accepted 27 June 1997)

We present a new technique for performing lithography with scanning probes that has several advantages over standard methods. This hybrid lithography system combines the key features of the atomic force microscope (AFM) and the scanning tunneling microscope (STM) by incorporating two independent feedback loops, one to control current and one to control force. We demonstrate a minimum resolution of 41 nm and nanometer alignment capabilities. This lithography system is capable of writing continuous features over sample topography. Topography is often present in real patterning applications and poses problems for AFM and STM lithography. We report 100 nm resist features patterned over 180 nm of topography created by local oxidation of silicon. The hybrid AFM/STM system is designed as a robust scanning probe lithography tool, capable of high-speed patterning and suited for integrated circuit lithography applications. © 1997 American Vacuum Society. [S0734-211X(97)02005-2]

## I. INTRODUCTION

Scanning probe lithography (SPL) is an emerging area of research in which the scanning tunneling microscope (STM) or atomic force microscope (AFM) is used to pattern nanometer-scale features. A voltage bias between a sharp probe tip and a sample generates an intense electric field in the vicinity of the tip. This concentrated field is the enabling element for the two primary SPL methods: selective oxidation and electron exposure of resist materials.

The high field can be used to locally oxidize a variety of surfaces. On silicon, this process is called electric-fieldenhanced oxidation. The high field desorbs the hydrogen passivation on the silicon surface, allowing the exposed silicon to oxidize in air (the oxidation rate is enhanced by the presence of the accelerating field). In a related process called anodization, a metal sample such as titanium,<sup>2</sup> tantalum,<sup>3</sup> chromium,<sup>4</sup> or aluminum<sup>5</sup> can be locally oxidized. The high field at the tip causes a chemical reaction between the metal and adsorbed water on the surface, resulting in local oxide growth. These oxidation processes are powerful because of the fine resolution and the resistant oxide etch mask that is created. Patterning is slow, however, limited by the reaction rate at the surface. Writing speeds are typically under 10  $\mu$ m/s, making patterning of finite areas in reasonable times unmanageable. Local oxidation also results in significant tip wear.7

Another scheme for performing lithography with scanning probes involves the electron exposure of a resist material, such as an organic polymer or a monolayer resist. When a conducting tip is biased negatively with respect to a sample, electrons are field emitted from the tip. If a sample is coated with a thin resist, the emitted electrons traverse the resist. The resist absorbs energy from the electron radiation, which induces chemical changes in the resist. For organic polymer resists, the radiation scissions bonds (positive resist) or

cross-links molecules (negative resist). As a result, when the resist is submersed in a special solvent (the developer), only the irradiated areas are dissolved (for positive resists; opposite for negative resists). The resist pattern can then be transferred to the substrate using selective chemical etching or dry etching. Organic polymer resists provide an attractive option for SPL because many have a low threshold voltage, high sensitivity, sub 100 nm resolution, and good dry etch resistance. Moreover, these resists can be easily deposited on virtually any substrate, and many organic polymers are well characterized from their use in photolithography or electron beam (e-beam) lithography. It is also possible to pattern at higher speeds with this method. In one example, siloxene (spin on glass) was patterned with the tip scanning above 3 mm/s. Finally, the polymer surface is soft and pliable which should significantly reduce the tip wear.

Early SPL studies have been limited primarily to demonstrations of the technique's fine resolution. A few groups have created devices using SPL, 9-11 but such work has been directed toward creating a single working device suitable for research or exploration. Methods used by these groups suffer from speed constraints and poor repeatability. Thus it is unlikely they can easily be extended to large-scale fabrication applications. We have sought to establish a method of SPL more suited for widespread applications in the semiconductor industry. There are four factors which will dictate the viability of SPL as a patterning technology for the semiconductor industry: (1) resolution, (2) alignment accuracy, (3) reliability, and (4) throughput (wafers/h). In this article we present a new SPL technique designed to address these issues. Our lithography system, a hybrid between the AFM and STM using an organic polymer resist, is capable of patterning sub 100 nm features on a variety of substrates, with various tips, and over topography. It requires minimal characterization prior to patterning and is designed for highspeed lithography and the extension to multiple probes patterning simultaneously.

<sup>&</sup>lt;sup>a)</sup>Electronic mail: kwilder@leland.stanford.edu

b)On leave from Bilkent University, Ankara, Turkey 06533.

#### II. HYBRID AFM/STM LITHOGRAPHY

Organic polymer resists have been patterned with both the STM and AFM. In STM lithography, a fixed tip-sample bias is applied and the spacing is varied to maintain a constant current through the resist. 12-14 This system, however, suffers from poor alignment capabilities (imaging may expose the resist). 15 It is also tricky to determine the appropriate voltage bias for STM lithography. If the bias is set too high, the tip may move far from the sample resulting in beam spreading. If the bias is too low, the tip may in fact penetrate the resist in an attempt to achieve the set point current. 16 These factors make STM lithography of organic resists problematic. In AFM lithography, the force between the tip and resist is held constant while a fixed voltage bias is applied to generate the field-emitted current.<sup>17</sup> Constant voltage operation is not ideal since the required voltage is a function of the tip and sample materials, the tip shape, and the resist thickness. Therefore any change in tip shape or resist thickness varies the dose of electrons delivered to the resist. This results in nonuniform or unrepeatable patterns.

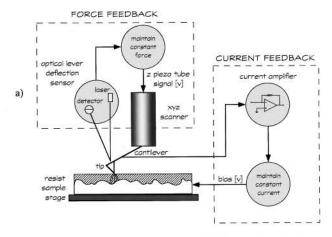

We have developed the hybrid AFM/STM lithography system, which combines the key features of the AFM and STM by incorporating two independent feedback loops [Figure 1(a)]. One loop keeps the tip on the surface of the electron-sensitive resist and maintains a constant small force between the tip and sample (typically 10 nN). This minimizes the beam spreading that limits the resolution of STM lithography. The force is detected by monitoring the cantilever deflection with a conventional optical lever beam-bounce system. A signal is sent to the piezo tube actuator to move the probe up or down to maintain the set point force.

The other feedback loop maintains a constant field emission current through the resist during exposure (generally in the range of 20 pA-1 nA). This custom-built analog feedback circuit, shown in Figure 1(b), uses integral gain to minimize the current error signal. The current through the resist is measured with picoAmpere sensitivity using a commercial current preamplifier. The current is measured at the tip for lowest noise operation. The feedback circuit compares the measured current to the set point current. A high voltage amplifier applies the necessary voltage to the sample (generally 20–100 V) to maintain the set point current. The bandwidth of this feedback system is limited to 1 kHz for maximum loop gain.

#### III. EXPERIMENT

We have demonstrated hybrid AFM / STM lithography by patterning Microposit SAL-601, a commercially available negative tone e-beam resist from Shipley Company. SAL-601 is a chemically amplified resist (CAR), which makes it highly sensitive to electron exposure. Electron radiation generates an acid in the resist. This acid causes further chemical reactions during a high-temperature activation step (post-exposure bake, PEB) leading to cross linking of the matrix polymer. We chose SAL-601 because it is negative tone, meaning that exposed areas remain after development and thus the resist patterns may be readily characterized. The

Fig. 1. (a) Schematic diagram of the hybrid AFM/STM lithography system incorporating dual feedback loops, one to maintain a constant force between the tip and sample and the other to keep a constant field-emission current through the resist. (b) Schematic diagram of the integral current feedback circuit, which changes the sample bias in order to maintain the set point current.

high resolution of SAL-601 has been previously demonstrated with x ray, <sup>18</sup> e-beam, <sup>19</sup> and STM<sup>12</sup> lithography.

We patterned SAL-601 resist on two substrates: (100) phosphorous-doped silicon and boron-doped polysilicon. The sample preparation steps are listed in Table I. Before resist coating, the native oxide was etched off the substrate in 50:1 hydrofluoric acid (HF). The substrate was then singed for 30 min in a 150 °C convection oven and vapor primed with hexamethyldisilazane (HMDS) adhesion promoter.

TABLE I. Sample preparation steps for hybrid AFM/STM lithography of SAL-601 e-beam resist.

| Step        | Equipment       | Temperature | Time         |

|-------------|-----------------|-------------|--------------|

| Oxide etch  | 50:1 HF         | RT          | 35 s         |

| Singe       | Convection oven | 150 °C      | 30 min       |

| Prime       | HMDS vapor      | 125 °C      | 30 s         |

| Resist spin | Thinned SAL-601 | RT          | 7 krpm, 30 s |

| Soft bake   | Hot plate       | 85 °C       | 1 min        |

| Pre-bake    | Convection oven | 90 °C       | 30 min       |

| Exposure    | Hybrid AFM/STM  | RT          | ≤2 h         |

| PEB         | Hot plate       | 115 °C      | 1 min        |

| Development | MF-322          | RT          | 10 min       |

| Post-bake   | Hot plate       | 115 °C      | 1 min        |

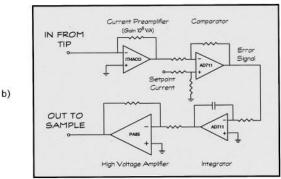

Fig. 2. TEM micrograph at  $19000 \times$  magnification of a doped silicon AFM tip coated with 20 nm evaporated Ti. The image shows that the Ti covers the entire tip. The inset, at  $120000 \times$  magnification, shows that the Ti balls up slightly at the end of the tip. The radius of the silicon tip is about 10 nm. With the Ti coating, the tip radius is approximately 30-40 nm.

SAL-601 diluted in Microposit thinner type A was spin coated on the wafer. Then the wafer was pre-baked (1 min, 85 °C hot plate followed by 30 min, 90 °C convection oven). The spun resist thickness was measured using the NanoSpec optical film thickness measurement system.

Exposure was performed in air using the Park Scientific Instruments (PSI) Autoprobe M5 operating in contact AFM mode modified with constant current feedback circuitry (as described in Section II). We used high-aspect-ratio dopedsilicon tips (PSI Ultralevers), some of which were coated with 20 nm of evaporated titanium (Ti), tantalum (Ta), or molybdenum (Mo). Figure 2 is a transmission electron microscopy (TEM) image of a Ti-coated tip, showing that the Ti covers the full length of the tip. The radius of the silicon tip is about 10 nm. With the Ti coating, the tip radius is approximately 30-40 nm. Tips were mounted on nonconducting holders and electrical connections were made to the cantilever chip with a thin line of silver paint. We chose this method to minimize the tip-sample capacitance. This capacitance becomes important when attempting to maintain constant current at high speeds or over topography (where the voltage must change rapidly). A positive voltage was applied to the sample with a metal clip. The tip was grounded through the preamplifier. We used PSI lithography software to specify the path and the speed of the tip. Patterns were written at a variety of scan speeds, bias conditions (current, dose), and over topography.

Immediately following exposure the wafer was given the PEB (1 min, 115 °C hot plate) and then submerged in MF-322 developer for 10 min. The final step is a postbake (1 min, 115 °C hot plate) to harden the resist. On some wafers

the resist lines were transferred into the substrate using a dry etch. All above steps were performed in quick succession in a clean-room environment to minimize resist contamination. SAL-601 was found to be sensitive to bake conditions and delay times. When the delay time between the pre-bake and development was greater than about 2 h we noticed delamination of the resist lines. After development, the substrate surface (silicon or polysilicon) should be hydrophobic. For delay times of more than 2 h the surface was hydrophillic, meaning that oxygen had diffused through the resist and grown a native oxide on the substrate. We attribute the resist delamination to this oxide growth, since SAL-601 does not adhere well to oxide.

The resist and etched lines were characterized using: (1) a 100X magnification optical microscope for preliminary inspection, (2) the PSI AFM operating in noncontact mode to determine line continuity and uniformity, and (3) the Dektak SXM critical dimension AFM (CD-AFM) for measuring linewidths. Noncontact mode AFM operation was adopted for line continuity and uniformity inspection. Contact mode operation was not acceptable since the scanning tended to damage the resist lines. The Dektak CD-AFM was operated in a two-dimensional noncontact scanning mode using a boot-shaped tip.<sup>20</sup> The tip shape is optimized to sense topography on vertical surfaces and can be used to profile vertical or even reentrant sidewalls (where conventional conical or pyramidal tips fail as a result of tip-sample convolution). The resolution of the CD-AFM is approximately 50 Å laterally. Previous studies have shown that CD-AFM linewidth and profile measurements correlate well with cross section scanning electron microscope (SEM) data.<sup>21</sup> An advantage of the CD-AFM is that it is capable of making these measurements nondestructively (without cleaving the wafer and preparing a cross section), and measurements and images can be obtained anywhere on the wafer (not just where the cross section was made).

# IV. RESULTS AND DISCUSSION

## A. Current-voltage characteristics

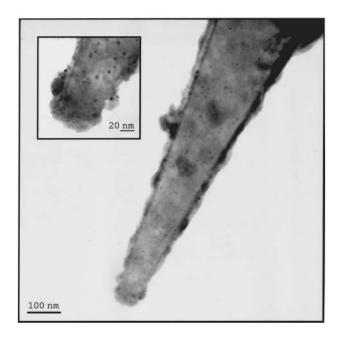

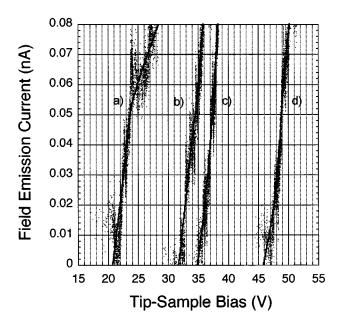

The hybrid AFM/STM system allows us to measure the field emission characteristics of the tip-resist-substrate system by varying the set point current and measuring the applied voltage. Figure 3 shows the typical dependence of the current on the tip-sample bias for four different resist thicknesses. Curve (a) corresponds to a spun resist thickness of 36.3 nm. Below about 21 V there is no measured current. Once the field becomes high enough for current to flow (above this 21 V "threshold"), the current increases dramatically with voltage. This I-V relationship depends critically on the tip shape and the resist thickness. For instance, a thicker resist requires a higher threshold voltage. Curve (d) corresponds to a spun resist thickness of 60.7 nm. Here the threshold voltage is nearly 46 V. Likewise, a more blunt tip would require a higher bias to reach the critical field for electron emission. Fowler and Nordheim predicted an exponential dependence of the field-emitted current on the bias voltage.<sup>22</sup> Data does indeed indicate an extreme sensitivity of

Fig. 3. Field-emission current as a function of tip-sample bias for different resist thicknesses: (a) 36 nm, (b) 42 nm, (c) 53 nm, and (d) 61 nm. The curves were acquired using the hybrid AFM/STM system by stepping the set point current and monitoring the applied voltage. The Ti-coated tip was kept in contact with the resist.

current on bias voltage, but the behavior is not exponential. The *IV* curves of Fig. 3 illustrate the difficulty of operating in a constant voltage mode.

We experimented with doped silicon and metal-coated tips and noticed little, if any, shift in the *I-V* curve as a function of tip material. The current signal from metal-coated tips, however, was cleaner (less noise), and therefore was preferable for current feedback. Most of our lithography has thus been performed with Ti-coated tips.

## **B.** Latent images

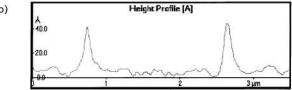

Following exposure but before the PEB the exposed areas were imaged with the AFM. The exposed regions were raised as much as 10 nm over the unexposed regions, where the amount of swelling seems to depend on the exposure conditions. Figure 4 shows the resist topography after patterning with an exposure dose of 1000 nC/cm. Here the exposed areas are raised about 4.5 nm over the unexposed regions. The thickness of the lines was even greater after development, suggesting additional resist swelling during the PEB and/or development steps. Table II lists the resist thickness change from spin on to development for four different initial resist thicknesses. The spun resist thickness was measured by the NanoSpec and the developed thickness by the CD-AFM. All were exposed at the same dose. The increased swelling for the thicker resist is likely due to the higher bias necessary to achieve the set point current. (For a spun resist thickness down to 36.3 nm we see no evidence of pinhole formation in the resist film.)

It has long been known that negative resists tend to swell during development, creating the characteristic reentrant profiles.<sup>23</sup> Swelling during exposure is not generally seen for

Fig. 4. Latent image in the resist after exposure but before the PEB. The lines were patterned with an exposure dose of 1000 nC/cm. The exposed areas are raised about 4.5 nm above the unexposed regions.

e-beam or deep-ultraviolet (DUV) exposure of CARs. Ocola et al. studied the latent image formation for e-beam lithography of SAL-605, a negative tone DUV CAR manufactured by Shipley.<sup>24</sup> They found that before the PEB the exposed regions are valleys (low regions) in the resist, while after the PEB the features are ridges (high regions). In other words, the cross linking induced by the PEB increases the resist volume. We confirmed the results reported by Perkins et al. 14 that SPL exposure can itself cause the cross linking of the matrix polymer. In fact, no PEB step is necessary to create features with SPL. This is likely due to the high area dose delivered during SPL. It may also be an indication of the polymer's greater sensitivity to low energy electrons. It is consistent with these results that we see resist swelling as a result of the exposure itself. This latent image formed in the resist film during exposure can be imaged with the AFM,

Table II. Resist swelling for different initial resist thicknesses. Initial resist thickness after spin-on  $(T_{\text{initial}})$ , final resist thickness after exposure and development  $(T_{\text{final}})$ , and the amount of resist swelling  $(\Delta_{\text{fi}})$  are shown. Also listed is the field-emission threshold voltage  $(V_t)$  dependence on resist thickness.

| $T_{\rm initial}$ (nm) | $T_{\rm final}$ (nm) | $\Delta_{fi} \; (nm)$ | $V_{t}$ |

|------------------------|----------------------|-----------------------|---------|

| 36.3                   | 42.0                 | 5.7                   | 21      |

| 42.1                   | 53.0                 | 10.9                  | 32      |

| 53.2                   | 65.0                 | 11.8                  | 35      |

| 60.7                   | 74.6                 | 13.9                  | 46      |

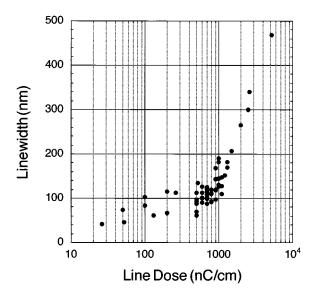

Fig. 5. Resist linewidth dependence on line dose.

suggesting the feasibility of *in situ* monitoring of the lithography process or aligning with previously written features.

## C. Resolution and throughput

Figure 5 shows the developed resist linewidth dependence on line dose. Here the spun resist thickness was about 61 nm. Data were taken at various scan speeds  $(1-20~\mu\text{m/s})$ , at different current settings (0.025-0.5~nA), and on both doped silicon and polysilicon substrates. From these data we conclude that the critical parameter for exposing an organic polymer with scanning probes is the dose of electrons deliv-

ered to the resist. In the case of SPL, the line dose (in Coulombs/cm) is the ratio of the current to the writing speed. The width of the exposed region depends critically on this line dose. Features can be patterned at higher speeds by increasing the current proportionally. Because of the current sensitivity to voltage (Figure 3), current can be increased by orders of magnitude with only a few volts change. Therefore this patterning technique can be extended to higher speed lithography. We have patterned at speeds up to  $200~\mu$ m/s and foresee no physical speed limitations to this patterning mechanism within reasonable scan speeds. The smallest lines we have patterned are 41 nm at a line dose of 26 nC/cm.

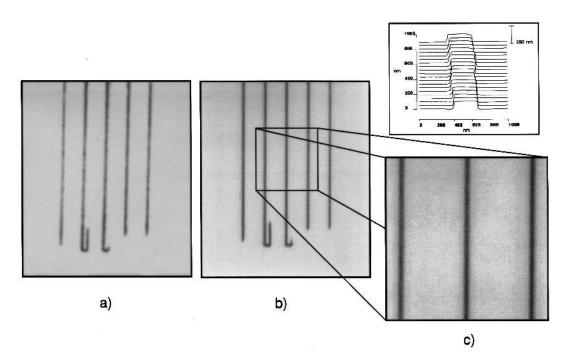

A resist thickness of 61 nm is more than sufficient to withstand a plasma etch. Figure 6(a) shows an optical micrograph of developed SAL-601 resist lines on polysilicon. The pattern was transferred into the 100-nm-thick polysilicon using an anisotropic SF<sub>6</sub>/Freon 115 dry etch and the resist was then stripped. Figure 6(b) shows the resulting etched lines. Figure 6(c), at  $100\times$  magnification, illustrates the excellent line uniformity and continuity achieved with this technique. A CD-AFM image of this line illustrates the line profile and shows the linewidth is approximately 210 nm. The developed resist features are slightly reentrant, with sidewall angles ranging from approximately  $93^{\circ}$  to  $110^{\circ}$ .

# D. Patterning over topography

Patterning over topography is a challenge for most forms of lithography. Resist spun on a wafer with topography tends to planarize, resulting in resist thickness variations across the sample. In photolithography, this causes linewidth variations due to the scattering of light off the topography and to the interference effect.<sup>25</sup> The resist thickness may in fact exceed

Fig. 6. Optical images of lithographed lines: (a) SAL-601 resist lines on polysilicon, (b) etched polysilicon lines on oxide, (c) 100× magnification of the etched polysilicon lines showing the line continuity and uniformity, and a CD-AFM image of the etched 220 nm lines showing the vertical feature profile.

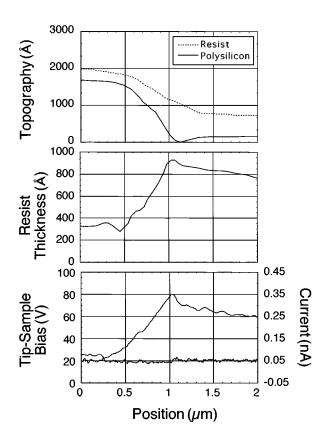

Fig. 7. (a) Polysilicon and resist topography created by LOCOS isolation, as measured with the AFM. (b) Resist thickness variation as a function of position resulting from the planarizing nature of resist. (c) Current and voltage data taken while writing over the above topography in hybrid AFM/STM lithography mode. The voltage varies from less than 20 V to more than 80 V in order to maintain a constant current of 0.05 nA.

the system's depth of focus in certain regions, particularly for high resolution lithography. It is also difficult to achieve uniform patterns over topography using e-beam lithography. This is a result of electrons backscattering from the substrate and changing the feature profile near a topographic step.<sup>26</sup> For different reasons, it is impractical to pattern a wafer with topography with either the STM or AFM. In STM lithography the problem is usually one of beam spreading causing linewidth variations between regions. A more aggressive attempt to limit beam spreading can cause the tip to penetrate the resist in the thicker regions. With the AFM, the chosen bias will likely pattern only one region (perhaps the thinner resist), but not expose another region at all. The hybrid AFM/STM lithography system was designed to circumvent these problems.

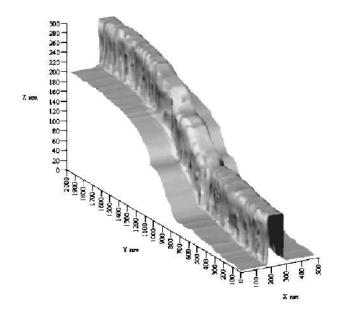

The hybrid AFM/STM system delivers a constant dose of electrons while maintaining a minimum tip-sample spacing. This allows patterning of continuous and uniform features over sample topography. Figure 7(a) is an AFM profile of 180 nm of polysilicon topography. This topography was created by a local oxidation of silicon (LOCOS) isolation process used in the semiconductor industry to electrically isolate neighboring active devices. Also shown is the SAL-601 resist topography after it was spun on the wafer. In Figure 7(b)

Fig. 8. CD-AFM image of an etched 100 nm polysilicon line over the topographic step.

the resulting resist thickness variation is plotted. Notice that the thickness changes abruptly from less than 30 nm to more than 90 nm within a micron.

Using the hybrid AFM/STM system we are able to pattern continuous lines over this topography in a single pass. Figure 7(c) shows the current and voltage data taken while writing over the topography with dual force/current feedback. The applied bias ranged from less than 22 V to more than 81 V in order to keep the current constant at 0.05 nA. We subsequently etched the polysilicon and stripped the resist. Figure 8 is the resulting polysilicon feature across the topographic step. This image, taken by the CD-AFM, shows the linewidth is 100 nm.

A change in voltage,  $\partial V/\partial t$ , generates a displacement current proportional to the capacitance between the probe and sample. The total current measured is thus a sum of the dc current through the resist and this capacitive current. If a significant fraction of the total current is capacitive, the dose of electrons delivered to the resist is not constant. In particular, whenever the voltage changes abruptly, there can be a break in the exposure. We measured the probe-sample capacitance as about 2.4 pF. We estimate a contribution to the total capacitance of less than  $1\times10^{-18}$  F from the tip itself (modeling the tip as a sphere after Sarid<sup>27</sup>). The cantilever, although quite close to the sample, is small in area (about  $1\times10^4 \ \mu\text{m}^2$ ) and therefore contributes only a few fF. Surprisingly, the major contribution to the tip-sample capacitance comes from the chip on which the cantilever is fabricated. The silicon chip is 3.6 mm×1.6 mm, made large enough for ease of handling. By reducing the size of this chip, we were able to reduce the total tip-sample capacitance to under 600 fF. This capacitance is small enough to allow continuous patterning over significant topography. To pattern at higher speeds over topography, a more elegant solution would be to separate out the two components of current, using an ac technique or an analog circuit for compensation, and provide current feedback only to the field-emitted current.

## V. CONCLUSIONS

The hybrid AFM/STM system is a robust lithography tool, capable of patterning a variety of materials, resists, and topography by simply setting the desired exposure dose. Constant force operation enables fine resolution lithography by minimizing beam spreading. Constant current operation delivers a fixed dose of electrons to the resist allowing reproducible and uniform lithography. Alignment accuracy of a few nanometers is possible with the hybrid AFM/STM lithography system because the underlying layer is first imaged in AFM mode. The electron dose is found to be the critical exposure parameter. Because of the sensitivity of field-emission current on voltage bias, writing speeds may be dramatically increased with only small changes in the voltage. Since the bias for field emission is less than 100 V, proximity effects often found in high energy e-beam lithography should be minimal. The dual feedback system is useful for patterning a flat wafer and essential for patterning over topography where the resist thickness changes as a function of position.

#### **ACKNOWLEDGMENTS**

The authors would like to acknowledge AMD's Advanced Process Development group, especially D. Kyser, W. H. Arnold, and B. Singh, for their technical support and for access to the CD-AFM. Thanks to R. Alvis at AMD for assistance with sample preparation techniques and TEM imaging. Thanks also to F. K. Perkins at NRL and M. McCord at Stanford for useful discussions. The authors would also like to thank the technicians at Stanford's Center for Integrated Systems, especially G. Sarmiento, R. King, P. Burke, and M. Prisbe. PSI provided technical support of the Autoprobe system and the lithography software. K. W. acknowledges AMD for financial support. This work was supported in part by DARPA, SRC, and NSF.

- <sup>2</sup>H. Sugimura, T. Uchida, N. Kitamura, and H. Masuhara, Appl. Phys. Lett. **63**, 1288 (1993).

- <sup>3</sup>T. Thundat, L. A. Nagahara, P. I. Oden, S. M. Lindsay, M. A. George, and W. S. Glaunsinger, J. Vac. Sci. Technol. A 8, 3537 (1990).

- <sup>4</sup>H. J. Song, M. J. Rack, K. Abugharbieh, S. Y. Lee, V. Khan, D. K. Ferry, and D. R. Allee, J. Vac. Sci. Technol. B **12**, 3720 (1994).

- <sup>5</sup>E. S. Snow, D. Park, and P. M. Campbell, Appl. Phys. Lett. **69**, 269 (1996).

- <sup>6</sup>Snow used a short pulse to oxidize silicon and from the length of the pulse inferred a maximum writing speed of 1 mm/s. See E. S. Snow and P. M. Campbell Appl. Phys. Lett. **64**, 1932 (1994). From our experience, however, oxidation does not occur at scan speeds in excess of about 10  $\mu$ m/s.

- <sup>7</sup>S. C. Minne, S. R. Manalis, A. Atalar, and C. F. Quate, J. Vac. Sci. Technol. B **14**, 2456 (1996).

- <sup>8</sup>S. W. Park, H. T. Soh, C. F. Quate, and S.-I. Park, Appl. Phys. Lett. 67, 2415 (1995).

- <sup>9</sup>E. S. Snow and P. M. Campbell, Appl. Phys. Lett. **66**, 1388 (1995).

- <sup>10</sup>S. C. Minne, H. T. Soh, P. Flueckiger, and C. F. Quate, Appl. Phys. Lett. 66, 703 (1995).

- <sup>11</sup>K. Matsumoto, M. Ishii, K. Segawa, Y. Oka, B. J. Vartanian, and J. S. Harris, Appl. Phys. Lett. **68**, 34 (1996).

- <sup>12</sup>M. A. McCord and R. F. W. Pease, J. Vac. Sci. Technol. B **6**, 293 (1988).

- <sup>13</sup>C. R. K. Marrian, F. K. Perkins, S. L. Brandow, T. S. Koloski, E. A. Dobisz, and J. M. Calvert, Appl. Phys. Lett. 64, 390 (1994).

- <sup>14</sup>F. K. Perkins, E. A. Dobisz, and C. R. K. Marrian, J. Vac. Sci. Technol. B 11, 2597 (1993).

- <sup>15</sup>C. R. K. Marrian and E. A. Dobisz, Proc. SPIE **1671**, 166 (1992).

- <sup>16</sup>C. R. K. Marrian, E. A. Dobisz, and R. J. Colton, J. Vac. Sci. Technol. A 8, 3563 (1990).

- <sup>17</sup>A. Majumdar, P. I. Oden, J. P. Carrejo, L. A. Nagahara, J. J. Graham, and J. Alexander, Appl. Phys. Lett. 61, 2293 (1992).

- <sup>18</sup>I. Y. Yang, H. Hu, L. T. Su, V. V. Wong, M. Burkhardt, E. E. Moon, J. M. Carter, D. A. Antoniadis, H. J. Smith, K. W. Rhee, and W. Chu, J. Vac. Sci. Technol. B 12, 4051 (1994).

- <sup>19</sup>A. Classen, S. Kuhn, J. Straka, and A. Forchel, Microelectron. Eng. 17, 21 (1992).

- <sup>20</sup>Y. Martin and H. K. Wickramasinghe, Appl. Phys. Lett. **64**, 2498 (1994).

- <sup>21</sup>K. Wilder, B. Singh, and W. H. Arnold, Proc. SPIE **2725**, 1996 ().

- <sup>22</sup>R. H. Fowler and L. Nordheim, Proc. R. Soc. London **114**, 173 (1928).

- <sup>23</sup>L. F. Thompson, L. E. Stillwagon, and E. M. Doerries, J. Vac. Sci. Technol. 15, 938 (1978).

- <sup>24</sup>L. E. Ocola, D. S. Fryer, G. Reynolds, A. Krasnoperova, and F. Cerrina, Appl. Phys. Lett. 68, 717 (1996).

- <sup>25</sup>W. H. Arnold, B. Singh, and K. Phan, Solid State Technol., 139 (1989).

- <sup>26</sup>L. Bauch, U. Jagdhold, and M. Bottcher, Microelectron. Eng. 30, 53 (1996).

- <sup>27</sup>D. Sarid, Scanning Force Microscopy (Oxford University Press, New York, 1991).

<sup>&</sup>lt;sup>1</sup>J. A. Dagata, J. Schneir, H. H. Harary, C. J. Evans, M. T. Postek, and J. Bennett, Appl. Phys. Lett. **56**, 2001 (1990).