# HYBRID MICROFLUIDIC COOLING AND THERMAL ISOLATION TECHNOLOGIES FOR 3D ICS

A Thesis Presented to The Academic Faculty

by

Yue Zhang

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology May 2015

Copyright © 2015 by Yue Zhang

# HYBRID MICROFLUIDIC COOLING AND THERMAL ISOLATION TECHNOLOGIES FOR 3D ICS

### Approved by:

Professor Muhannad Bakir, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Professor Oliver Brand School of Electrical and Computer Engineering Georgia Institute of Technology

Professor Sudhakar Yalamanchili School of Electrical and Computer Engineering Georgia Institute of Technology Professor Hua Wang School of Electrical and Computer Engineering Georgia Institute of Technology

Professor Yogendra Joshi School of Mechanical Engineering Georgia Institute of Technology

Date Approved: March 27, 2015

## **DEDICATION**

To my husband,

Ming Yi, my son, Oliver Yi,

and my parents,

Shuqiang Zhang and Dengwen Zhang,

for their unlimited love and support.

### ACKNOWLEDGEMENTS

The completion of this thesis would not be possible without the inspiration, support, guidance and help from many individuals. I would like to express my sincere gratitude toward them.

First of all, I would like to give special thanks to my advisor Dr. Muhannad Bakir for accepting me as a student in the Integrated 3D Systems Group and guiding me through my entire Ph.D. career. He has always been a great source of inspiration. His vision and advices have greatly impacted the direction of my research. All the accomplishments in my research could not be possible without his continuous support. I would like to thank him for his guidance that led to my successful moments. Even more, I would forever cherish his encouragement during tough times in my research. He has taught me how to become a good researcher. More importantly, he has taught me how to become a better person.

I also want to express my sincere gratitude to my Ph.D. dissertation committee members, Professor Oliver Brand, Professor Sudhakar Yalamanchili, Professor Hua Wang, and Professor Yogendra Joshi for giving me feedback and suggestions to improve my thesis.

I am very fortunate to have had the opportunity to work with the past and current Integrated 3D Systems Group members. I sincerely thank Dr. King and Mr. Zaveri for training me in the cleanroom and in the lab when I first joined the group. I would like to convey my special gratitude to Thomas Sarvey, Chaoqi Zhang, Yang Zhang, and Ashish Dembla for the close collaboration. My thanks are also extended to the other group members who are willing to share their knowledge with me: Hyung Suk Yang, Paragkumar Thadesar, Hanju Oh, Muneeb Zia, Xuchen Zhang, Prabha

Viswanathan, and Reza Abbaspour. I would like also to acknowledge the members from other groups for collaboration: Steven Isaacs, Yoon Jo Kim from Professor Yogendra Joshi's group, and Song Hu from Professor Hua Wang's group.

My experimental work in the cleanroom could not be possible without the Institute for Electronics and Nanotechnology (IEN) members. I would like to especially acknowledge Dr. Brand, Gary Spinner, John Pham, Vinny Nguyen, and Charlie Suh for answering my questions and solving my problems with the tools.

I would like to thank my parents for their endless love and support. It is their advice that made me pursue the Ph.D. degree in Georgia Tech. Also, none of this would happen without their financial support. I wouldn't have a chance to meet the most important person in my life, my husband, Ming Yi. Ming is not only my life partner, but he is also an excellent researcher who teaches me research skills such as how to create excellent schematics. Last but not least, I would like to thank my son Oliver for bringing so much happiness in my life.

# TABLE OF CONTENTS

| $\mathbf{DE}$ | DIC                 | ATION                                                                             | iii          |  |  |

|---------------|---------------------|-----------------------------------------------------------------------------------|--------------|--|--|

| AC            | ACKNOWLEDGEMENTS iv |                                                                                   |              |  |  |

| LIS           | <b>T O</b>          | F TABLES                                                                          | $\mathbf{x}$ |  |  |

| LIS           | <b>T O</b>          | F FIGURES                                                                         | xi           |  |  |

| $\mathbf{SU}$ | MM                  | ARY                                                                               | viii         |  |  |

| Ι             |                     | CKGROUND AND INTRODUCTION OF THERMAL CHAL-                                        | 1            |  |  |

|               | 1.1                 | Current 3D ICs Trend                                                              | 1            |  |  |

|               | 1.2                 | Thermal Challenges in Stacks Containing Multiple High- Power Chips                | 4            |  |  |

|               | 1.3                 | Thermal Challenge in Heterogeneous 3D Stacks                                      | 8            |  |  |

|               | 1.4                 | Organization of the Thesis                                                        | 14           |  |  |

| II            |                     | ERMAL-ELECTRICAL CO-ANALYSIS OF A TSV-COMPATI<br>CROFLUIDIC HEAT SINK             | BLE<br>16    |  |  |

|               | 2.1                 | Introduction                                                                      | 16           |  |  |

|               | 2.2                 | Literature Review of Microfluidic Heat Sink                                       | 17           |  |  |

|               | 2.3                 | Heat Transfer Theory for Micropin-fin Heat Sink                                   | 20           |  |  |

|               | 2.4                 | Electrical Parasitics of TSVs Embedded in microfluidic heat sink $$ . $$ .        | 22           |  |  |

|               | 2.5                 | Thermal Resistance and Pressure Drop Trade-off Analysis of Microfluidic Heat Sink | 24           |  |  |

|               | 2.6                 | Electrical-Thermal Trade-off Analysis of TSVs in Microfluidic Heat Sink           | 25           |  |  |

|               | 2.7                 | Alternative Methods to Reduce TSV Capacitance                                     | 29           |  |  |

|               |                     | 2.7.1 Novel Liner Material                                                        | 29           |  |  |

|               |                     | 2.7.2 Heterogeneous TSV Integration                                               | 32           |  |  |

|               | 2.8                 | Conclusion                                                                        | 33           |  |  |

| III           | TSV<br>35           | V-COMPATIBLE MICROPIN-FIN HEAT SINK EXPERIMENT                                    | $\Gamma S$   |  |  |

|    | 3.1 | Introd | uction                                                                     | 35 |

|----|-----|--------|----------------------------------------------------------------------------|----|

|    | 3.2 | Fabric | ation of the TSV–Compatible Micropin-Fin Heat Sink                         | 36 |

|    |     | 3.2.1  | Bonding Process Selection                                                  | 36 |

|    |     | 3.2.2  | Fabrication Process of MPFHS                                               | 39 |

|    |     | 3.2.3  | Integration of TSVs in MPFHS                                               | 44 |

|    | 3.3 | Test S | etup Description and Automated Data Collection in LabVIEW                  | 48 |

|    | 3.4 | _      | Layer Thermal Measurements and Benchmarked with Air-Cooled Sink            | 52 |

|    | 3.5 | Data l | Extrapolations and Analysis                                                | 54 |

|    | 3.6 | Conclu | asion                                                                      | 60 |

| IV |     |        | ECIFIC MICROFLUIDIC COOLING EVALUATION IN ACKS                             | 61 |

|    | 4.1 | Introd | uction                                                                     | 61 |

|    | 4.2 | Therm  | nal Testbed Preparation and Experimental Setup                             | 63 |

|    | 4.3 | Tier-S | pecific Microfluidic Cooling for Different Stacking Scenarios .            | 65 |

|    |     | 4.3.1  | Processor-on-Processor and Memory-on-Processor Stack                       | 65 |

|    |     | 4.3.2  | Tier-Specific Flow Rates in ICs with Different Power Dissipations          | 68 |

|    | 4.4 | Microf | fluidic Cooling in Multi-core Processor Stacking                           | 71 |

|    |     | 4.4.1  | Preparation of the Thermal Testbed and Experimental Test Setup             | 71 |

|    |     | 4.4.2  | Lateral Thermal Gradient                                                   | 72 |

|    |     | 4.4.3  | Electrical Implications Due to Lateral Thermal Gradient $$                 | 77 |

|    |     | 4.4.4  | Localized Coolant Delivery Method to Mitigate Lateral Thermal Gradient     | 82 |

|    |     | 4.4.5  | Microfluidic Cooling Under Nonuniform Power Dissipation .                  | 83 |

|    |     | 4.4.6  | Vertical Thermal Coupling                                                  | 85 |

|    | 4.5 | Valida | tion through ANSYS Simulations                                             | 86 |

|    |     | 4.5.1  | Initial Simulation of Repeatable Cell Rows Assuming Even Flow Distribution | 87 |

|    |     | 452    | Adjusted Simulation of Repeatable Cell Rows                                | 80 |

|    | 4.6 | Conclu | ısion                                                                         | 91   |

|----|-----|--------|-------------------------------------------------------------------------------|------|

| V  | TH  | ERMA   | L ISOLATION FOR HETEROGENEOUS 3D ICS                                          | 92   |

|    | 5.1 | Introd | uction                                                                        | 92   |

|    | 5.2 | Resist | ance Network Modeling                                                         | 94   |

|    |     | 5.2.1  | TSVs' Impact on Thermal Isolation                                             | 97   |

|    |     | 5.2.2  | MFI Thermal Resistance                                                        | 98   |

|    | 5.3 |        | Difference Modeling of the Proposed Stack with Thermal Iso-Technology         | 101  |

|    |     | 5.3.1  | Thermal Bridge                                                                | 103  |

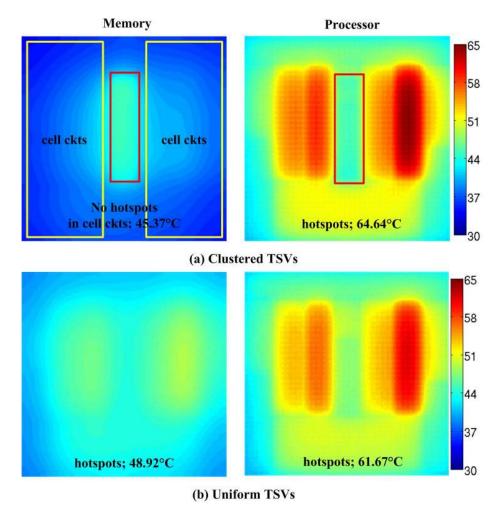

|    |     | 5.3.2  | Uniformly Distributed TSVs vs. Clustered TSVs                                 | 106  |

|    | 5.4 | Design | n of the Testbed                                                              | 109  |

|    | 5.5 | Testbe | ed Fabrication and Test Setup                                                 | 110  |

|    |     | 5.5.1  | Testbed fabrication                                                           | 110  |

|    |     | 5.5.2  | Assembly                                                                      | 113  |

|    |     | 5.5.3  | Thermal and Electrical Test Setup                                             | 116  |

|    | 5.6 | Therm  | nal and Electrical Experimental Results                                       | 118  |

|    |     | 5.6.1  | Thermal Testing I: Powering the high-power tier                               | 120  |

|    |     | 5.6.2  | Thermal Testing II: Minimize the Hotspot Coupling                             | 124  |

|    |     | 5.6.3  | Thermal Testing III: Bottom Tier Power Increases                              | 126  |

|    |     | 5.6.4  | Electrical Testing of MFIs                                                    | 129  |

|    | 5.7 | Valida | tion by Finite Difference Modeling                                            | 130  |

|    | 5.8 | Conclu | asion                                                                         | 134  |

| VI | SUI | MMAF   | RY AND FUTURE WORK                                                            | 137  |

|    | 6.1 | Summ   | ary of the Presented Work                                                     | 137  |

|    |     | 6.1.1  | Advanced Microfluidic Cooling Solution for 3D ICs Containing High Power Chips | 137  |

|    |     | 6.1.2  | Advanced Thermal Isolation Technology for Heterogeneous 3D ICs                | 139  |

|    | 6.2 | Dutum  | Worls                                                                         | 1.40 |

| REFERENCE | SS                                         | 145 |

|-----------|--------------------------------------------|-----|

| 6.2.3     | System Performance Implications            | 143 |

| 6.2.2     | Advancing the Thermal Isolation Technology | 141 |

| 6.2.1     | Explore a System with Interposer Cooling   | 140 |

# LIST OF TABLES

| 1  | Selected optimal heat sink dimensions from the literature                                                                                                                                      | 27  |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2  | Comparison of the area occupied by TSVs for homogeneous and heterogeneous TSV integration                                                                                                      | 33  |

| 3  | Comparison of the measured and modeled normalized thermal resistance at a power density of 100 $\rm W/cm^2$                                                                                    | 55  |

| 4  | Summary of the inlet water temperature $(T_{in})$ , the outlet water temperature $(T_{out})$ , and the chip junction temperature $(T_j)$ at $40 \text{ W/cm}^2$ for different water flow rates | 55  |

| 5  | Electrical implications due to lateral thermal gradient                                                                                                                                        | 81  |

| 6  | Summary of the simulation results vs. experimental results                                                                                                                                     | 88  |

| 7  | ANSYS simulated thermal resistance of a single MFI with various designs                                                                                                                        | 99  |

| 8  | Summary of the temperature of the top and bottom tiers under different scenarios (Part I)                                                                                                      | 120 |

| 9  | Summary of the temperature of the top and bottom tiers under different scenarios (Part II)                                                                                                     | 121 |

| 10 | Parameters used in the finite difference model                                                                                                                                                 | 130 |

| 11 | Boundary conditions assumed in the finite difference model                                                                                                                                     | 131 |

| 12 | Comparison between the measured and modeled junction temperatures 1                                                                                                                            | 131 |

# LIST OF FIGURES

| 1  | Schematic of a typical 3D IC with two stacks. The homogeneous stack contains two processor tiers. The heterogeneous stack contains several memory stacks on top of a processor tier | 2  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2  | Examples of current commercialized 3D IC products                                                                                                                                   | 3  |

| 3  | Proposed 3D IC prototype solving thermal challenges of lack of effective cooling and lack of effective thermal isolation                                                            | 4  |

| 4  | ITRS projections for the number of dice in a stack, number of TSVs, die thickness, and power of a single high-performance chip                                                      | 5  |

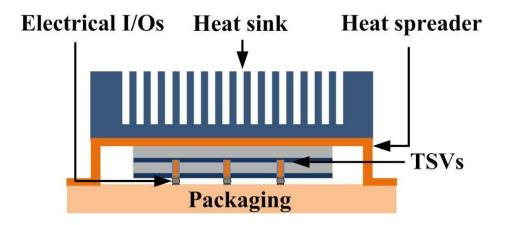

| 5  | Illustration of conventional air cooling technology                                                                                                                                 | 7  |

| 6  | Illustration of prior integrated microfluidic cooling technology                                                                                                                    | 7  |

| 7  | Illustration of the tier-specific microfluidic cooling technology in the present work                                                                                               | 7  |

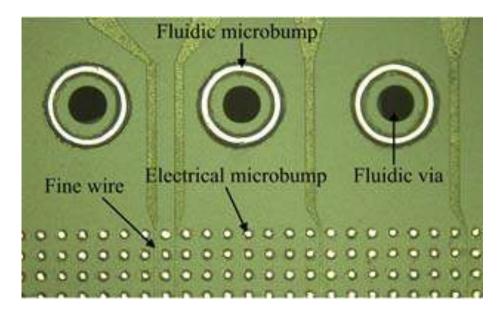

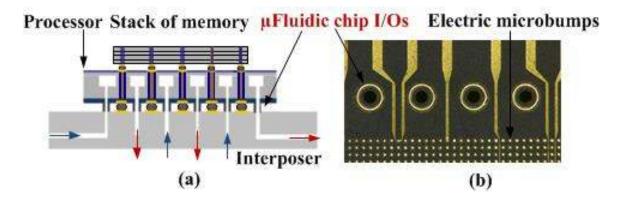

| 8  | Solder-based microfluidic chip I/Os and electric microbumps                                                                                                                         | 9  |

| 9  | (a) Illustration of a 3D stacked memory module containing SDRAM, photonic transceivers, and associated driver circuitry. (b) Temperature impact on microring resonance frequency    | 10 |

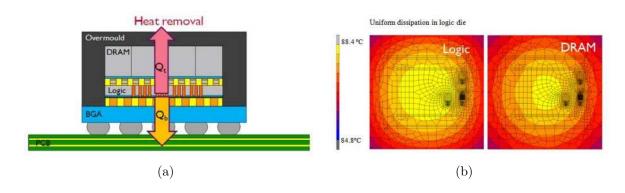

| 10 | (a) DRAM on logic stack in [24]. (b) Temperature contour of DRAM and logic when logic has a uniform power dissipation [24]                                                          | 11 |

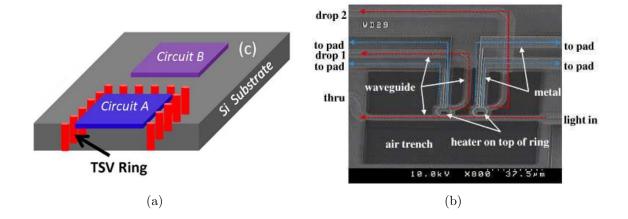

| 11 | (a) TSV guard ring to reduce thermal coupling [28] and (b) SEM for a two-channel (de)multiplexer with an air cavity beneath to reduce the thermal coupling [29]                     | 12 |

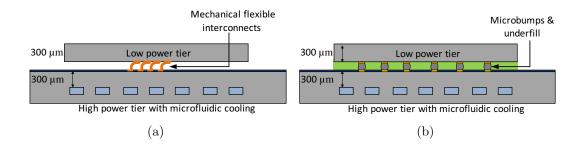

| 12 | Prototype shows the proposed thermal isolation technology that replaces microbumps and underfill with air gap and thermally degraded MFIs.                                          | 13 |

| 13 | Selected single-phase microfluidic heat sink geometries in the literature.                                                                                                          | 18 |

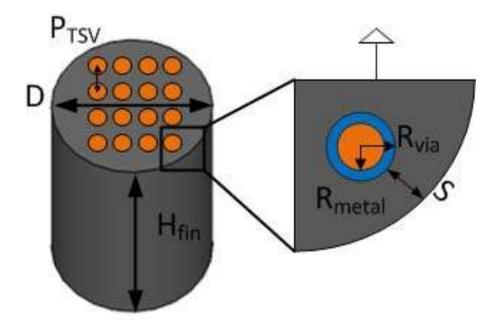

| 14 | TSV array integrated in a silicon micropin-fin                                                                                                                                      | 22 |

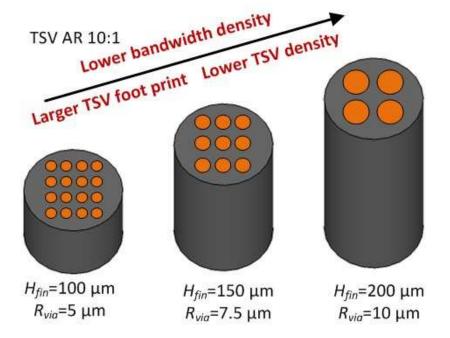

| 15 | Impact of $H_{fin}$ on TSV density and diameter                                                                                                                                     | 23 |

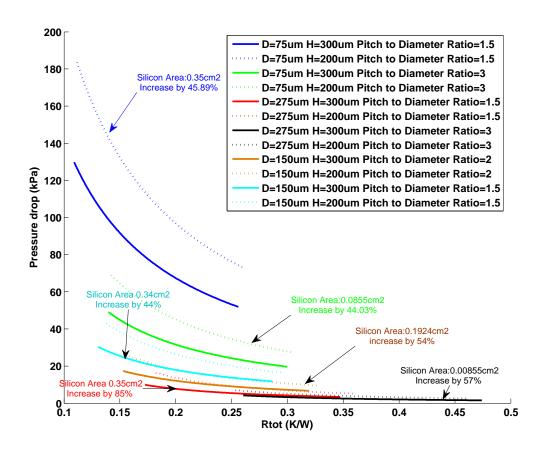

| 16 | Thermal resistance and pressure drop for different micropin-fin designs with flow rate 150 ml/min to 60 ml/min                                                                      | 26 |

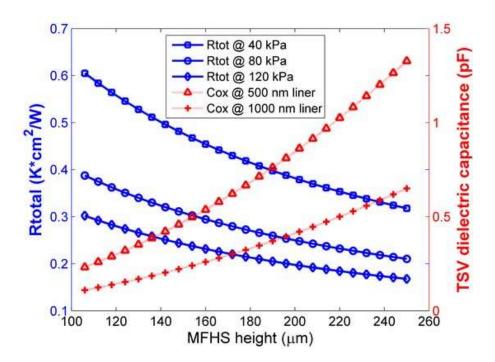

| 17 | Thermal resistance and TSV capacitance as a function of microfluidic heat sink height at different pressure drop values.                                                            | 28 |

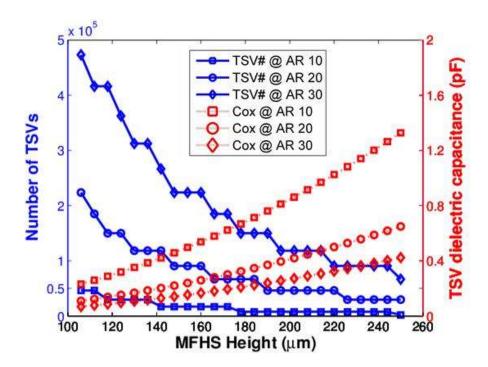

| 18 | The impact of microfluidic heat sink height on the number of TSVs and TSV capacitance                                                                                                            | 28 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

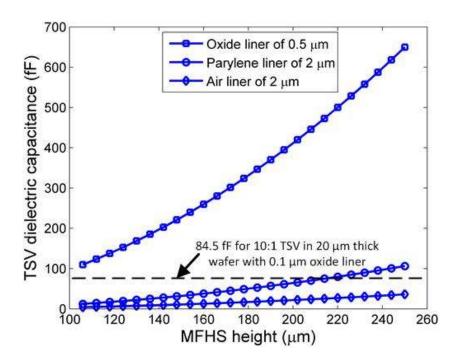

| 19 | TSV dielectric capacitance as a function of liner: oxide, Parylene-C, and air                                                                                                                    | 30 |

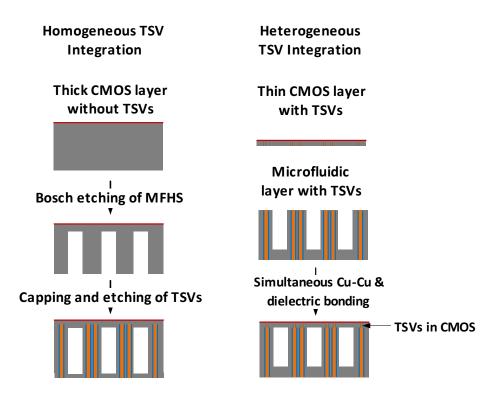

| 20 | Homogeneous and heterogeneous approaches for TSV integration into microfluidic cooled chip                                                                                                       | 31 |

| 21 | Two-tier 3D IC stack with microfluidic heat sink and TSVs                                                                                                                                        | 34 |

| 22 | Schematic of a three-microprocessor chip stack each with interlayer microfluidic cooling. A 3D stack of memory chips resides above the microprocessors. High AR TSVs are integrated in the MPFHS | 36 |

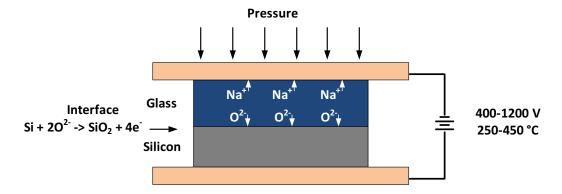

| 23 | Theory of anodic bonding                                                                                                                                                                         | 38 |

| 24 | Theory of fusion bonding.                                                                                                                                                                        | 39 |

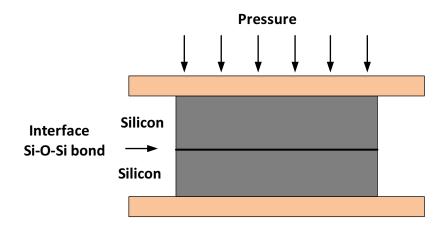

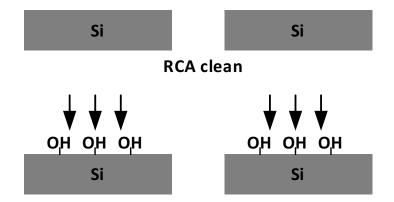

| 25 | Si–Si fusion bonding process                                                                                                                                                                     | 40 |

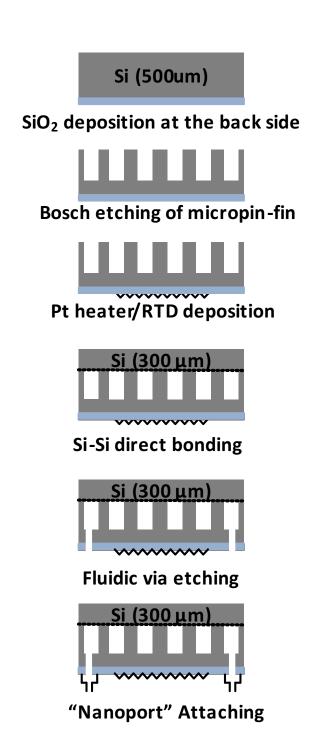

| 26 | Initial process flow of the MPFHS                                                                                                                                                                | 41 |

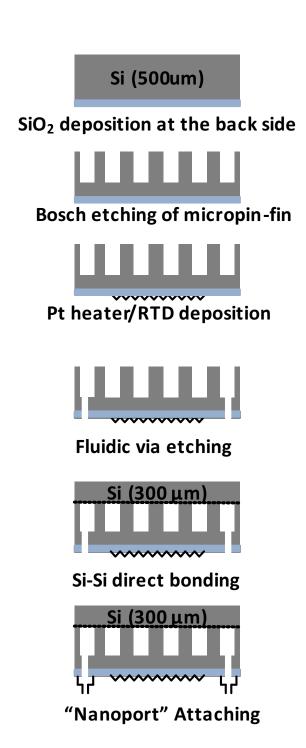

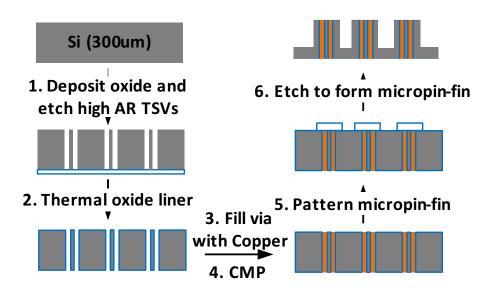

| 27 | Modified process flow of the MPFHS                                                                                                                                                               | 43 |

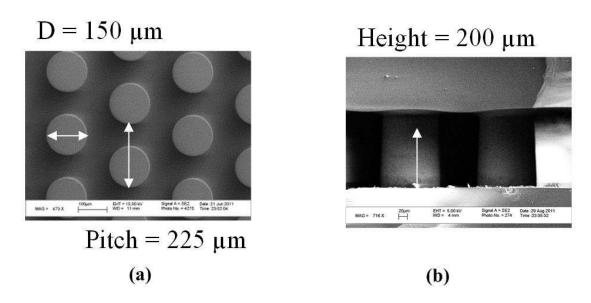

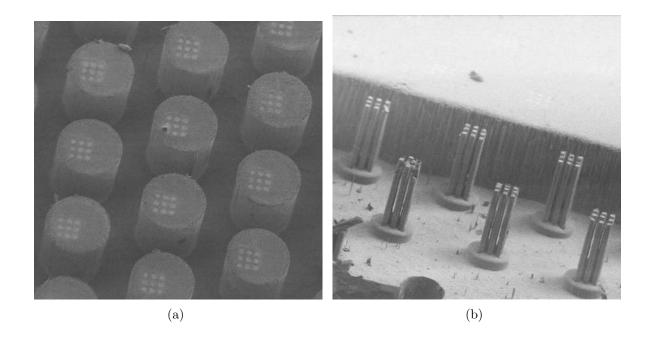

| 28 | SEMs of (a) the top and (b) cross-sectional view of the micropin-fin arrays                                                                                                                      | 44 |

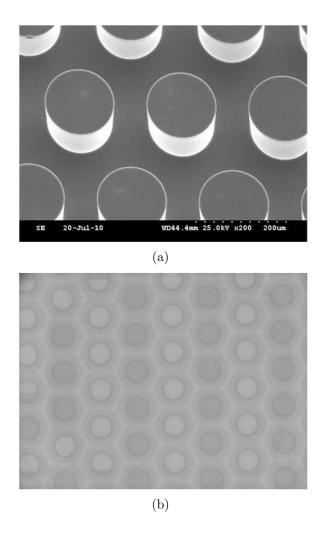

| 29 | (a) The tilted view of micropin-fins and (b) an infrared image of the bonded sample                                                                                                              | 45 |

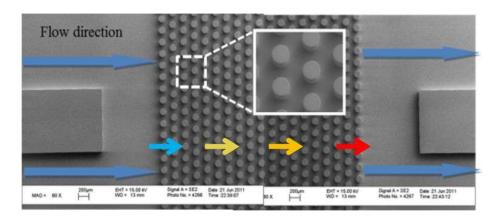

| 30 | Overview of the MPFHS with a magnified angled view of the micropin-<br>fins. Fluid flows from left to right                                                                                      | 46 |

| 31 | Process flow of high aspect ratio TSV integration into the MPFHS                                                                                                                                 | 46 |

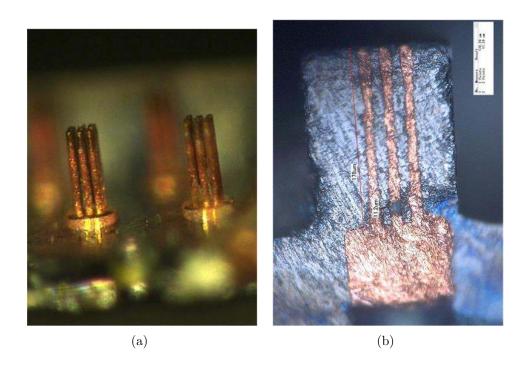

| 32 | SEMs of (a) high-AR TSVs integrated in micropin-fins and (b) free standing high-AR TSVs                                                                                                          | 47 |

| 33 | Optical images of (a) the free standing TSVs after removing the Silicon and (b) a cross section of high-AR TSVs integrated in micropin-fins.                                                     | 47 |

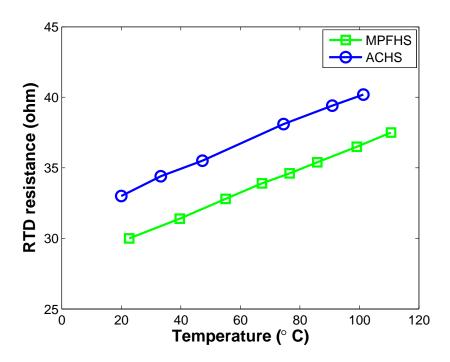

| 34 | Characterization of a RTD's resistance as a function of temperature                                                                                                                              | 48 |

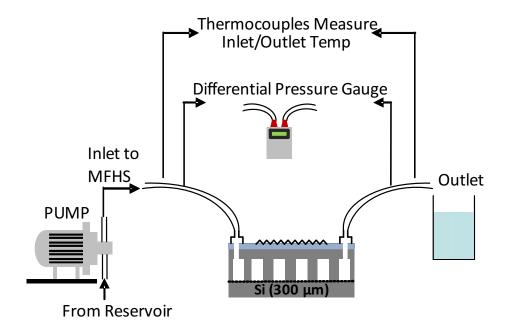

| 35 | The experimental test setup for single-layer microfluidic heat sink testing.                                                                                                                     | 49 |

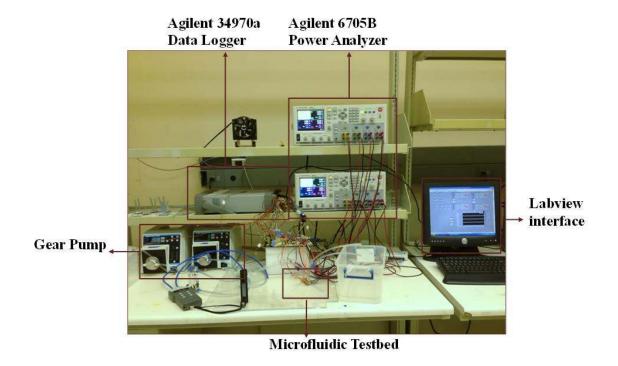

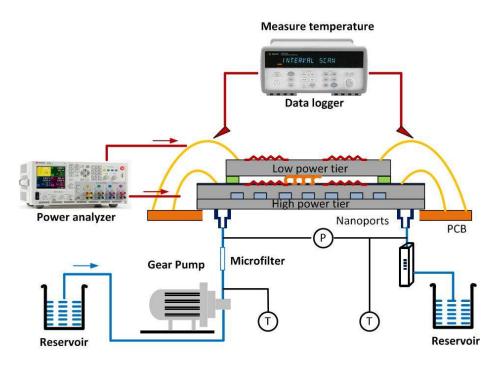

| 36 | A photo of the test setup for microfluidic heat sink testing. The key instruments in the test setup include power analyzer, gear pumps, data logger, and a LabVIEW interface for data collection | 51 |

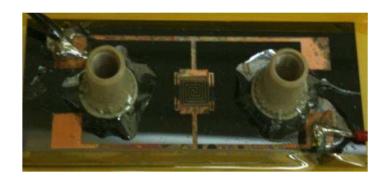

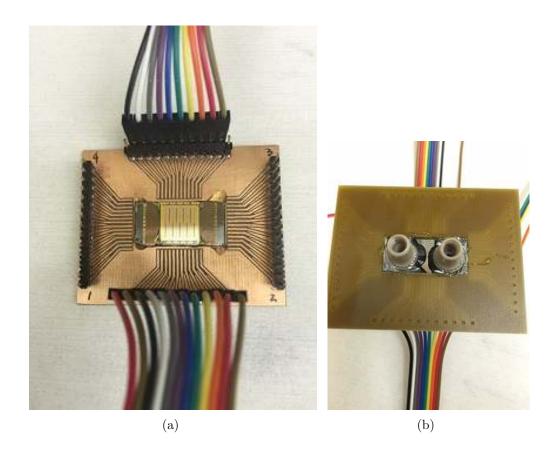

| 37 | Photo of the microfluidic testbed                                                                                                                                                                | 52 |

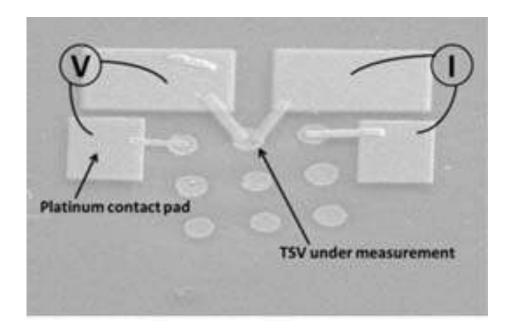

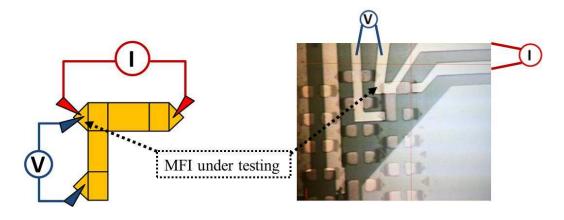

| 38 | Illustration of the resistance measurement of TSVs using four-point technique. The platinum pads are deposited selectively using focused ion beam (FIB) deposition  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

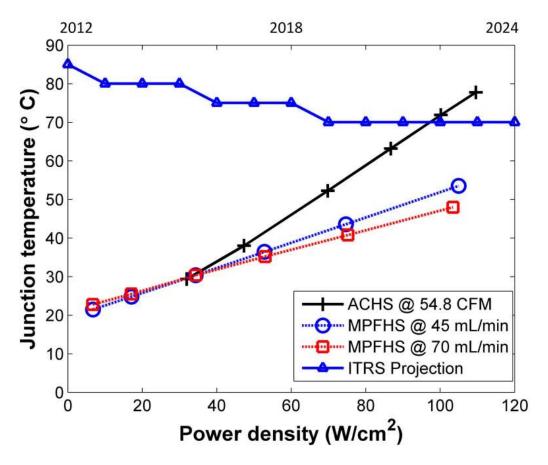

| 39 | Average junction temperature under air cooling and microfluidic cooling compared with ITRS projections                                                              |

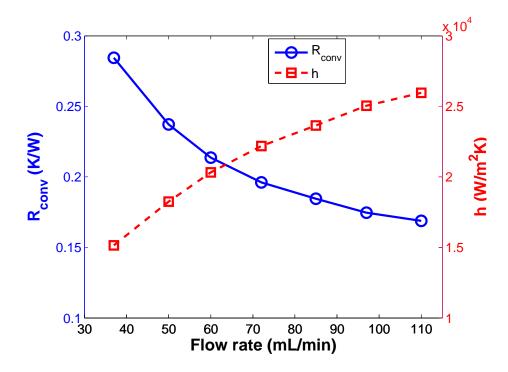

| 40 | Convective thermal resistance and heat transfer coefficient as a function of the flow rate                                                                          |

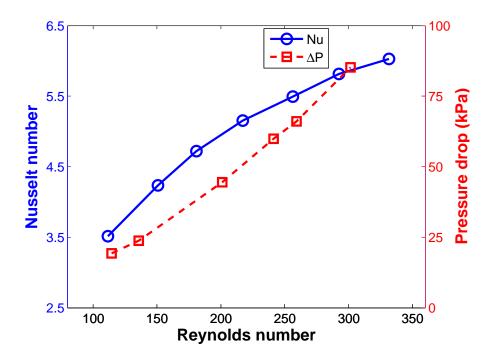

| 41 | Nusselt number and pressure drop as a function of Reynolds number.                                                                                                  |

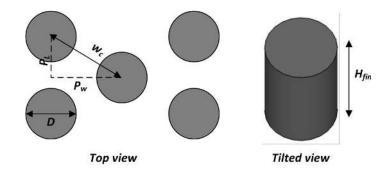

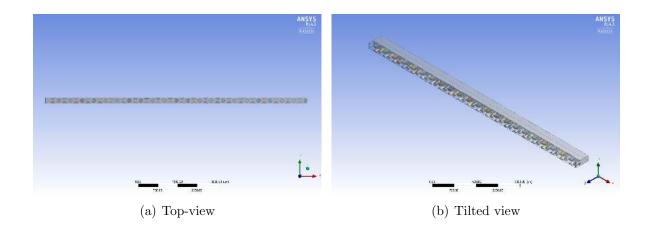

| 42 | Micropin-fin layout and dimensions (top and tilted view)                                                                                                            |

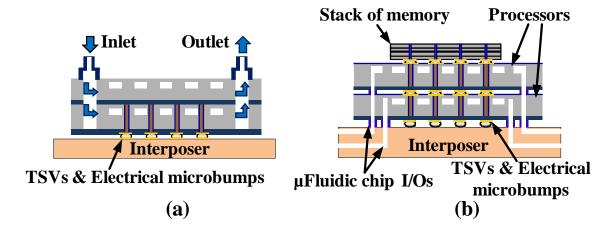

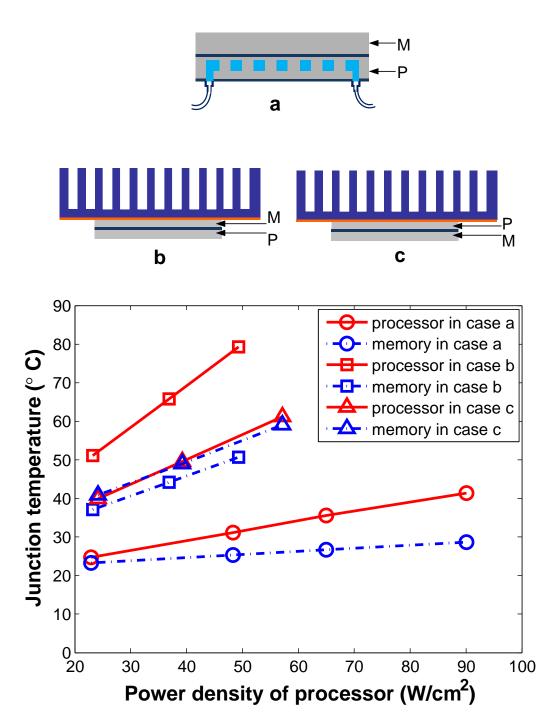

| 43 | Prototype of (a) a general embedded microfluidic heat sink and (b) our tier-specific microfluidic cooling within a 3D stack                                         |

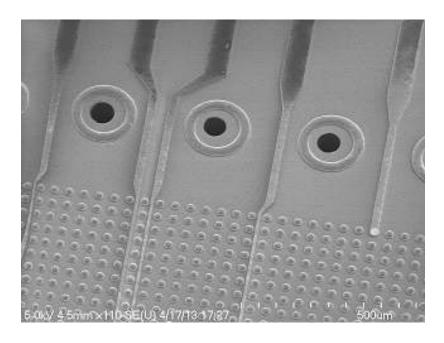

| 44 | SEM of solder microfluidic chip I/Os and electric microbumps                                                                                                        |

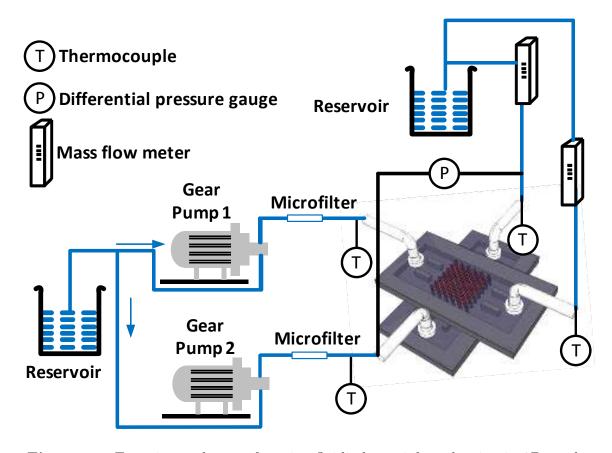

| 45 | Experimental setup for microfluidic heat sink evaluation in 3D stacks.                                                                                              |

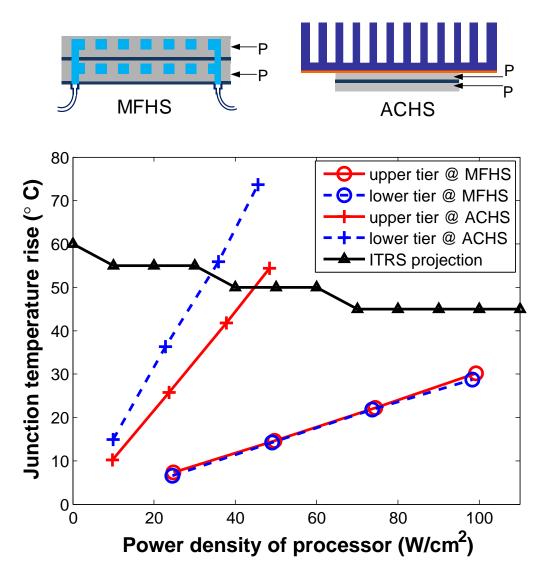

| 46 | Junction temperature rise in a memory–processor stack under microfluidic heat sink and ACHS                                                                         |

| 47 | Junction temperature rise in a processor–processor stack under microfluidic heat sink and ACHS                                                                      |

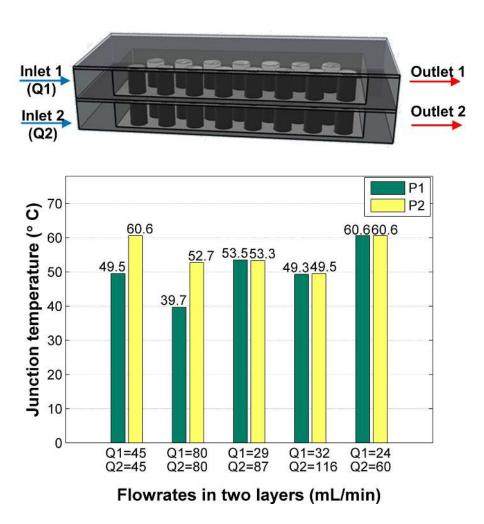

| 48 | Junction temperature of the top layer (P1) and the bottom layer (P2) as a function of the flow rates                                                                |

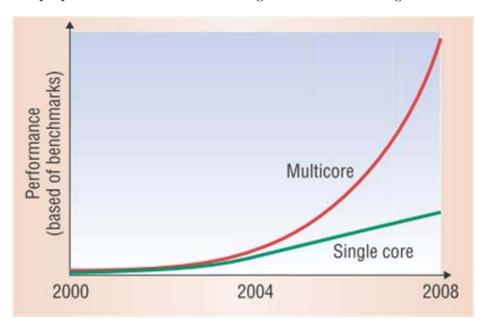

| 49 | Performance of multi-core processor compared with single-core processor [61]                                                                                        |

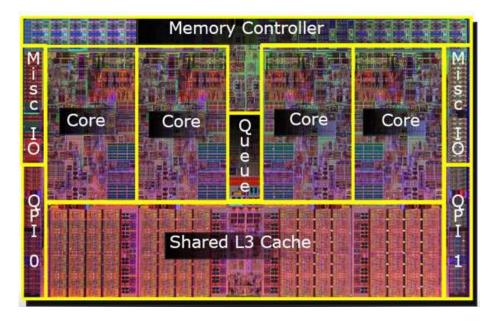

| 50 | Intel Core i7 Processor.                                                                                                                                            |

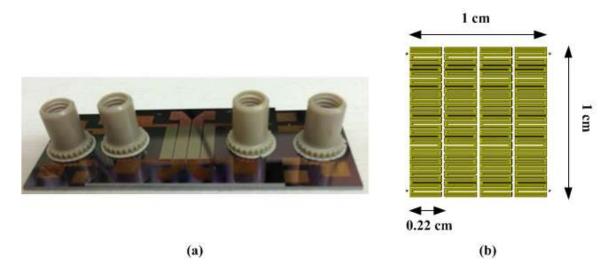

| 51 | (a) Image of the bonded two-tier thermal testbed and (b) layout of the four heaters                                                                                 |

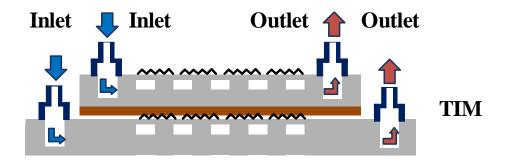

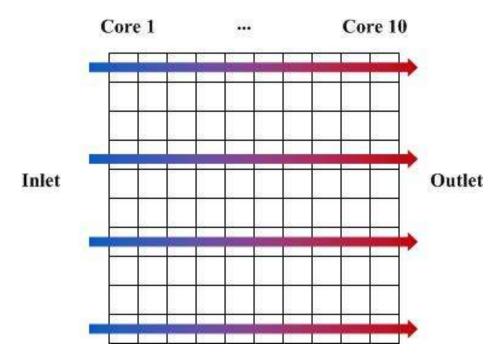

| 52 | Schematic of the tier-specific fluidic delivery mechanism                                                                                                           |

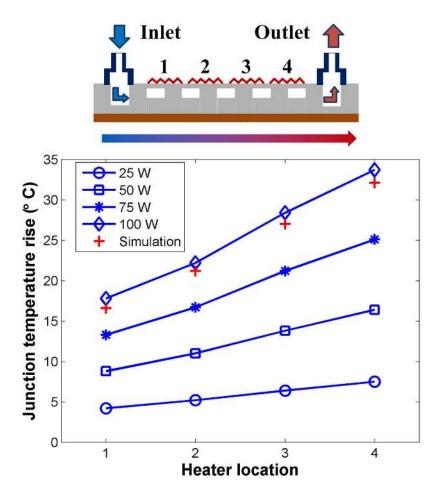

| 53 | Junction temperature rise at different heater locations on the chip for different power dissipations. ANSYS simulation for 100 W case is also plotted for reference |

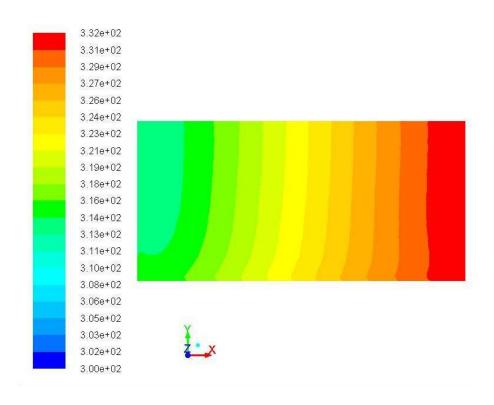

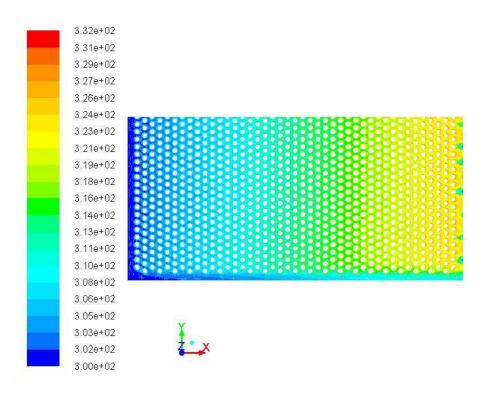

| 54 | Base temperature map in ANSYS simulation while the chip dissipates $100~\mathrm{W/cm^2}$                                                                            |

| 55 | Water temperature map in ANSYS simulation while the chip dissipates $100~\mathrm{W/cm^2}$                                                                           |

| 56 | Increase in leakage power as a function of chip temperature for a Intel 15 mm die with 100 nm technology [64].                                                      |

| 57 | Normalized leakage current as a function of temperature                                                                                                                                                                                                                                                   | 80 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 58 | A diagraph of Intel's Knights Landing CPU, consisting of up to 72 x86 cores for exascale supercomputing                                                                                                                                                                                                   | 80 |

| 59 | A diagraph illustration of the assumed 100-core CPU                                                                                                                                                                                                                                                       | 81 |

| 60 | (a) Prototype of 3D stack with microfluidic chip I/Os for localized coolant delivery and (b) solder based microfluidic chip I/Os and electric microbumps                                                                                                                                                  | 82 |

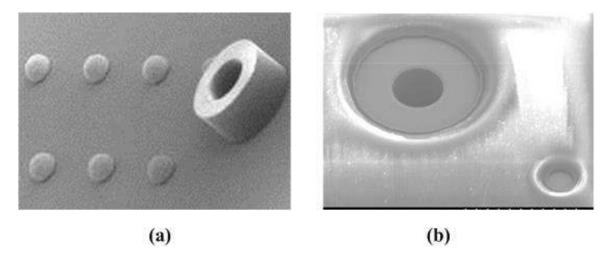

| 61 | (a) A polymer pipe and (b) a polymer socket for fluidic delivery                                                                                                                                                                                                                                          | 83 |

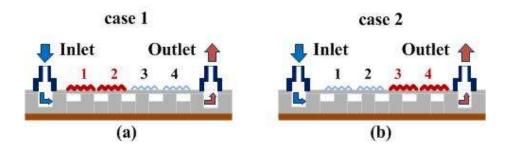

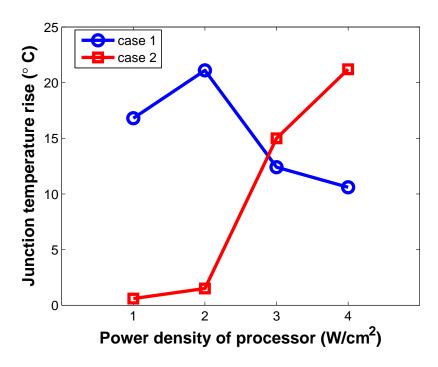

| 62 | Evaluation of microfluidic cooling in chips with nonuniform power dissipation: (a) case 1 where heater 1 and 2 dissipate $100 \text{ W/cm}^2$ and heater 3 and 4 are off and (b) case 2 where heater 3 and 4 dissipate $100 \text{ W/cm}^2$ and heater 1 and 2 are off                                    | 83 |

| 63 | Junction temperature rise of heater 1 to 4 under the two different test cases shown in Figure 62                                                                                                                                                                                                          | 84 |

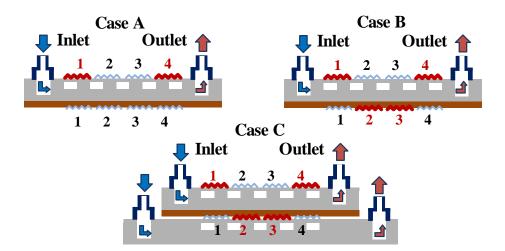

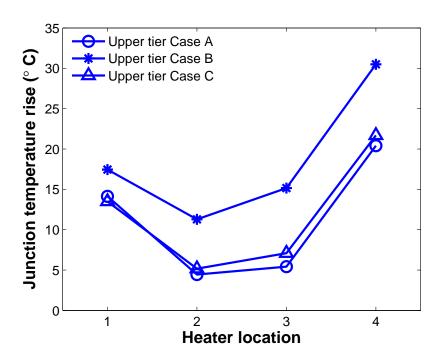

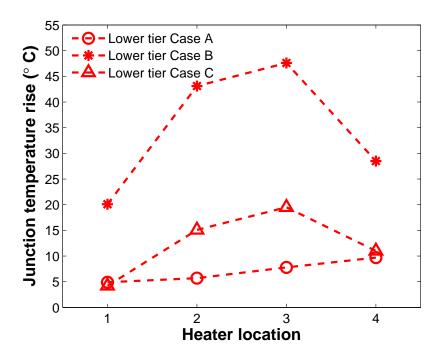

| 64 | Vertical thermal coupling test cases. (Case A) Heaters 1 and 4 in upper tier are powered. (Case B) Heaters 1 and 4 in upper tier and heaters 2 and 3 in lower tier are powered. (Case C) Heaters 1 and 4 in upper tier and heaters 2 and 3 in lower tier are powered with DI water pumped into both tiers | 85 |

| 65 | The junction temperature increase of the upper tier at different heater locations on the chip for the three cases                                                                                                                                                                                         | 86 |

| 66 | The junction temperature increase of the lower tier at different heater locations on the chip for the three cases                                                                                                                                                                                         | 87 |

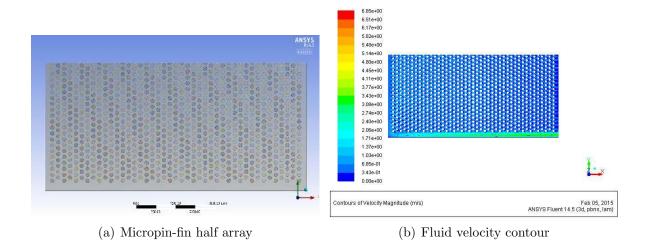

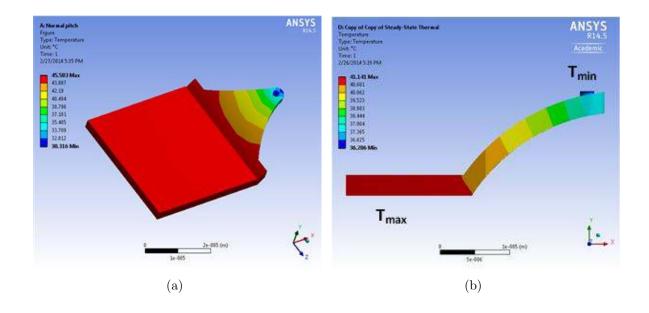

| 67 | Created cell row in ANSYS to simulate MPFHS in a single-layer chip.                                                                                                                                                                                                                                       | 88 |

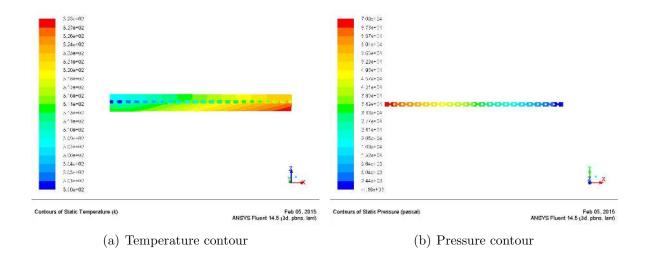

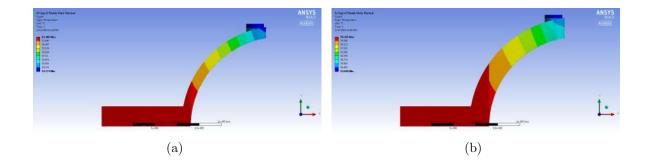

| 68 | The temperature and pressure contour profiles after initial simulation                                                                                                                                                                                                                                    | 89 |

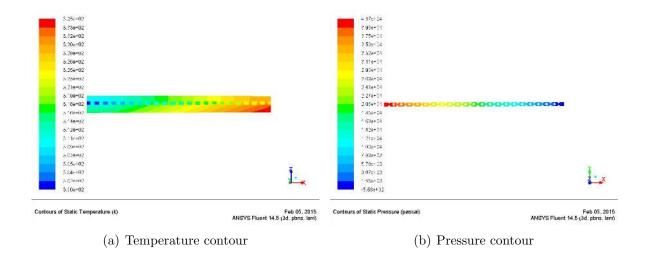

| 69 | The created cell row in ANSYS to simulate MPFHS sink in a single-layer chip.                                                                                                                                                                                                                              | 90 |

| 70 | The temperature and pressure contour profiles from the adjusted simulation                                                                                                                                                                                                                                | 91 |

| 71 | Prototype shows the proposed thermal isolation technology that replaces microbumps and underfill with air gap and thermally degraded MFIs                                                                                                                                                                 | 94 |

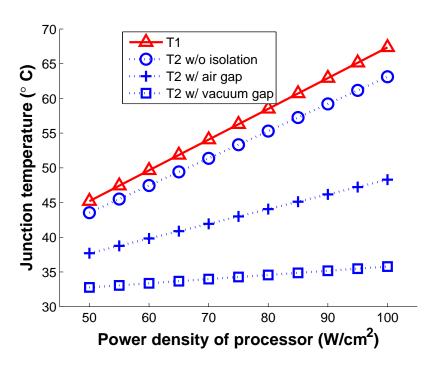

| 72 | (a) A 3D stack of processor and silicon nanophotonic chips with hybrid thermal management: within-tier microfluidic cooling in processor and air/vacuum cavity to thermally isolate the silicon nanophotonic chip.  (b) The corresponding thermal resistance network.                                     | 95 |

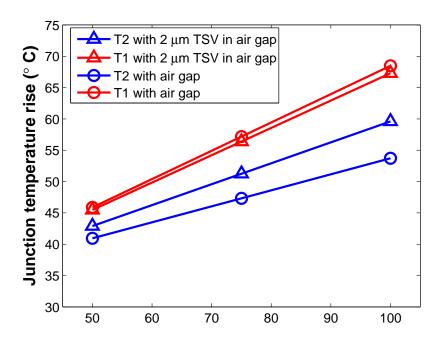

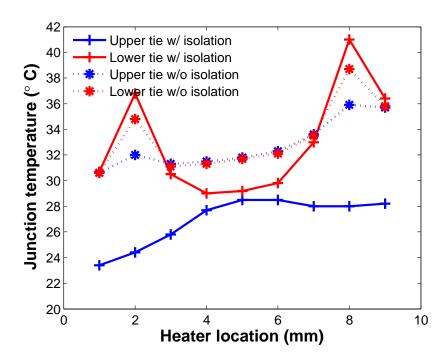

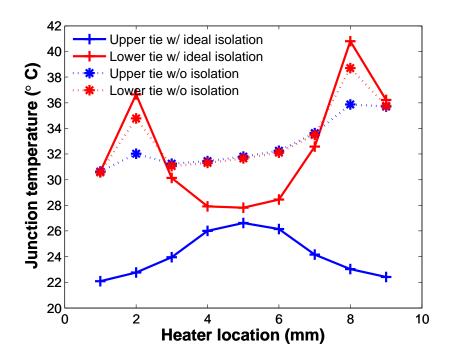

| 73 | The junction temperature increase of the upper tier at different heater locations on the chip for the three cases. T1 and T2 denote the temperature of the high-power and low-power tiers, respectively | 96  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

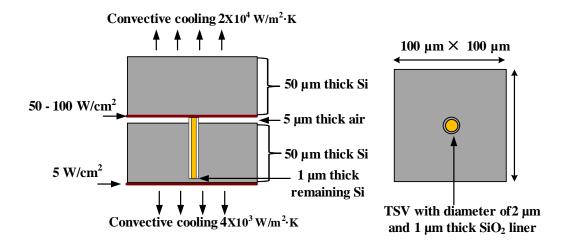

| 74 | Illustration of the cross-sectional (left) and top (right) view of the structures simulated in ANSYS to represent TSVs through air cavity.                                                              | 97  |

| 75 | Temperature of both tiers in the simulated structure shown in Figure 74. T1 and T2 denote the temperature of the high-power and low-power tiers, respectively                                           | 98  |

| 76 | (a) The MFI structure created in ANSYS and (b) the corresponding thermal profile in a static thermal simulation                                                                                         | 99  |

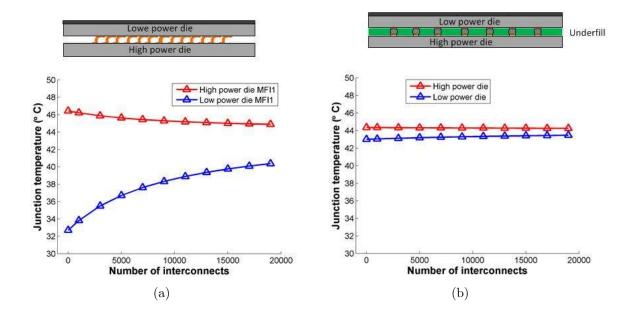

| 77 | Temperature of the high-power and low-power die with different interconnects: (a) Uniform MFIs within air gap and (b) microbumps and underfill.                                                         | 101 |

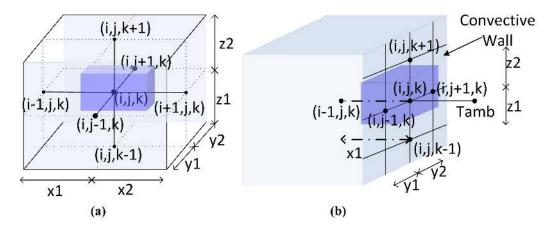

| 78 | Finite difference scheme: (a) general points inside the stack and (b) boundary points in the face of the stack [70]                                                                                     | 102 |

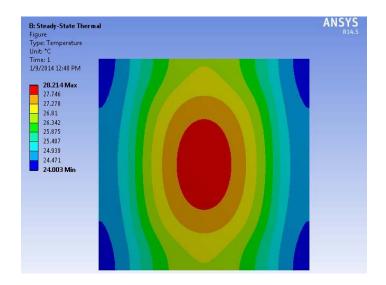

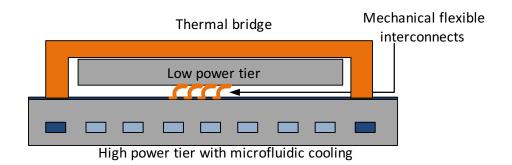

| 79 | Thermal bridge on top of a memory tier simulated in ANSYS                                                                                                                                               | 105 |

| 80 | Memory tier temperature map for the calculation of the thermal resistance of the thermal bridge                                                                                                         | 105 |

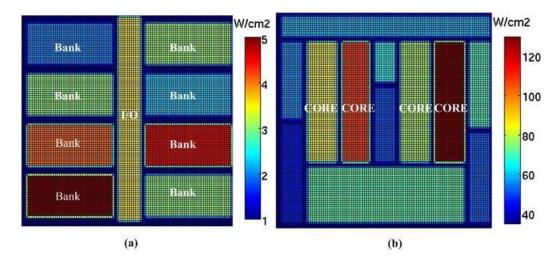

| 81 | Power maps of the memory and processor tiers used in the finite difference modeling                                                                                                                     | 106 |

| 82 | Power maps of the memory and processor tiers in (a) the clustered TSV case and (b) the uniform TSV case                                                                                                 | 107 |

| 83 | Schematic of the designed testbed for evaluation of the proposed thermal isolation technologies                                                                                                         | 108 |

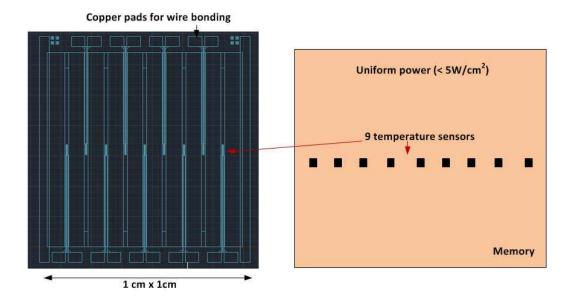

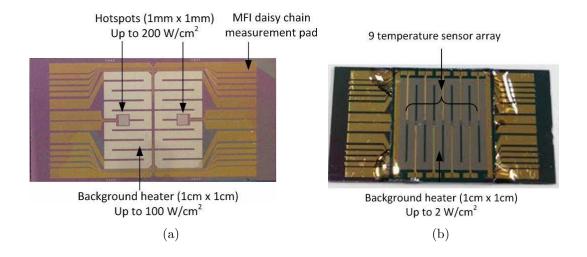

| 84 | Layout (left) and schematic (right) of the power map designs of the top tier (low-power tier)                                                                                                           | 108 |

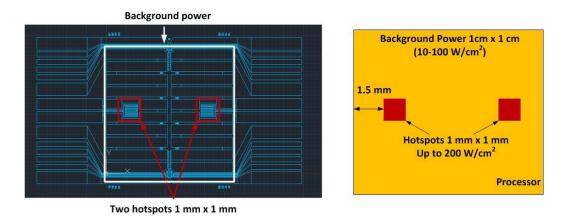

| 85 | Layout (left) and schematic (right) of the power map designs of the bottom tier (high-power tier)                                                                                                       | 109 |

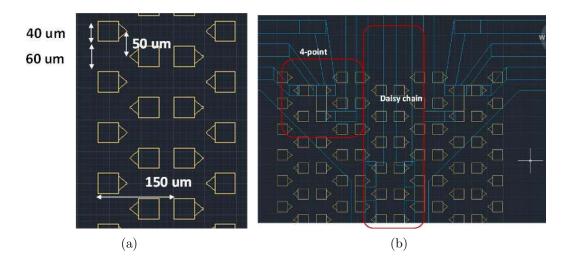

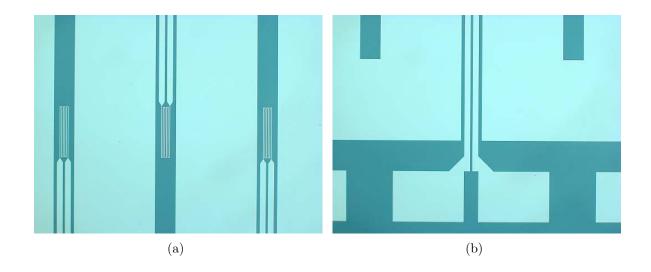

| 86 | Layout of (a) the MFI array and (b) the connections for daisy-chain resistance and four-point resistance measurements                                                                                   | 110 |

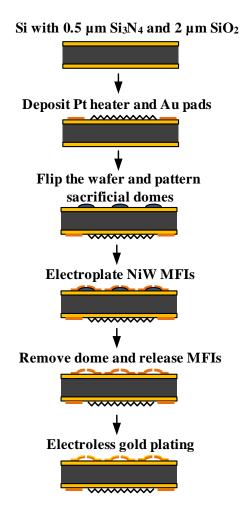

| 87 | Process flow for the low-power tier                                                                                                                                                                     | 111 |

| 88 | Images of (a) parts of the RTD array and (b) the pad of the RTD                                                                                                                                         | 113 |

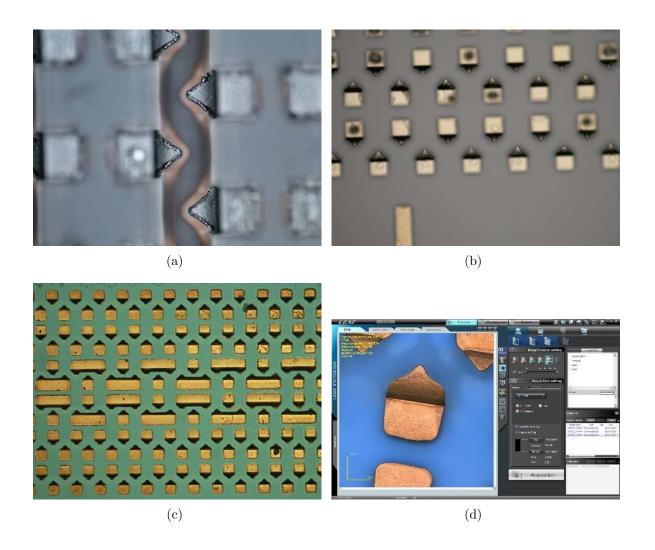

| 89 | Images of (a) the MFIs electroplated on top of the polymer dome, (b) the free standing MFIs after dome removal, (c) the MFI array with gold passivation, and (d) a single MFI with gold passiavtion     | 114 |

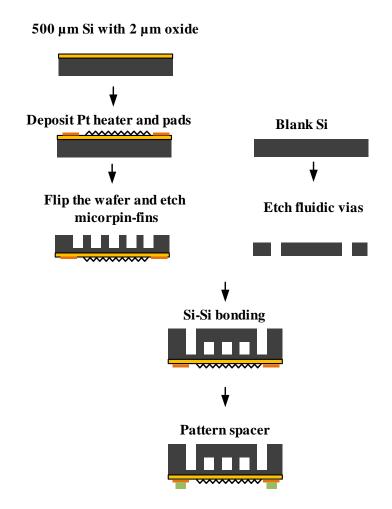

| 90  | Process flow for the high-power tier                                                                                                                                                                        | 115 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

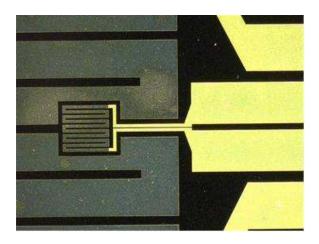

| 91  | Optical image of one hotspot on the high-power tier                                                                                                                                                         | 115 |

| 92  | Images of (a) the bottom tier after dicing and (b) the assembled two-tier testbed                                                                                                                           | 116 |

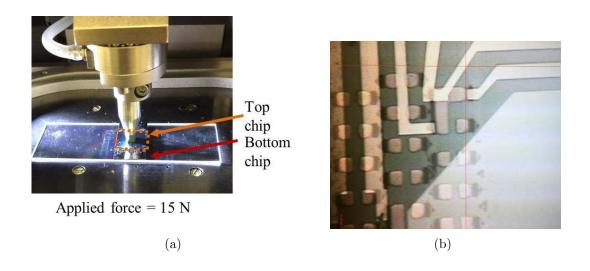

| 93  | (a) Flip chip bonding assembly and (b) the alignment between the two tiers                                                                                                                                  | 117 |

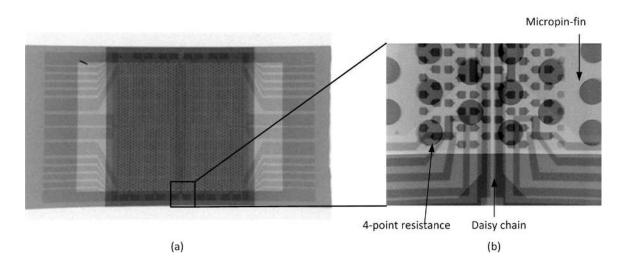

| 94  | X-ray of (a) overall view of the boned chip and (b) a magnified view.                                                                                                                                       | 117 |

| 95  | Microfluidic test setup to evaluate the thermal isolation technologies.                                                                                                                                     | 118 |

| 96  | (a) Top and (b) bottom view of the stack assembled to a PCB board using wire bonding                                                                                                                        | 119 |

| 97  | Four-point resistance measurement of MFI                                                                                                                                                                    | 119 |

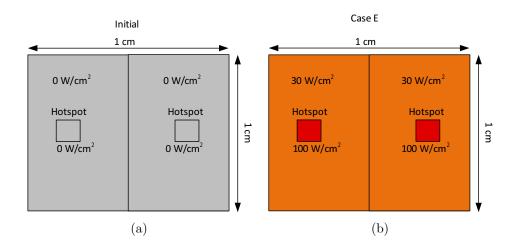

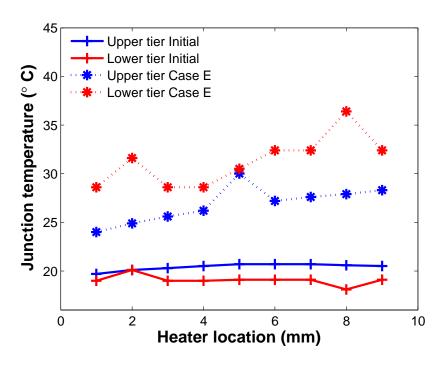

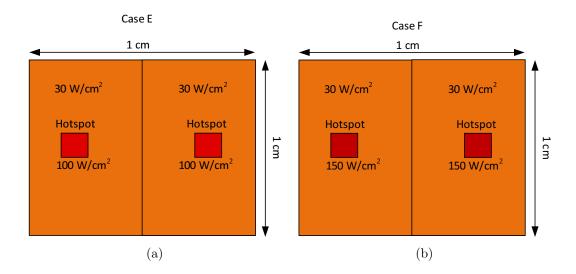

| 98  | (a) Initial case when the high-power tier dissipates 0 W and (b) Case E in Table 9 where the background power density is $30~\rm W/cm^2$ and the hotspot power density is $100~\rm W/cm^2$ .                | 122 |

| 99  | Junction temperature fluctuation before and after the high-power tier is powered                                                                                                                            | 123 |

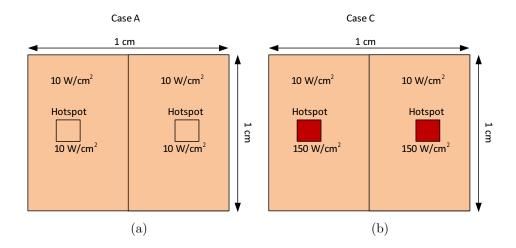

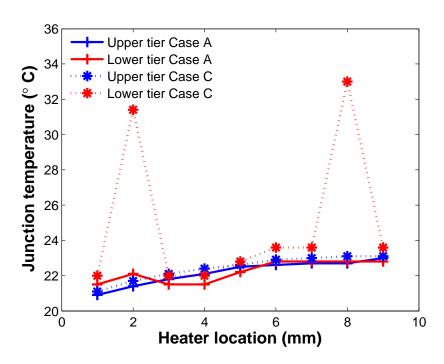

| 100 | (a) Uniform power density of $10~\rm W/cm^2$ in the bottom tier (Case A) and (b) background power of $10~\rm W/cm^2$ plus two hotspots each dissipates $150~\rm W/cm^2$ (Case C)                            | 124 |

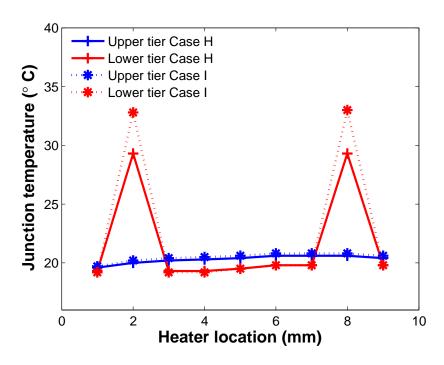

| 101 | Junction temperature fluctuation of top and bottom tiers in Case H and Case I in Table 9                                                                                                                    | 125 |

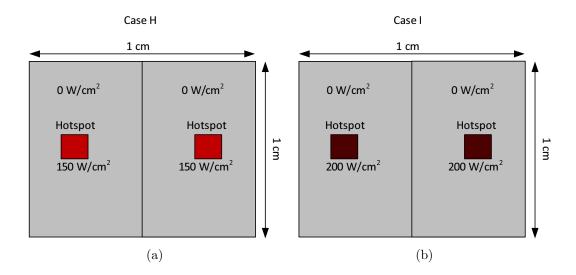

| 102 | (a) Zero background power with two hotspots each dissipates 150 $\rm W/cm^2$ (Case H) and (b) zero background power with two hotspots each dissipates 200 $\rm W/cm^2$ (Case I)                             | 126 |

| 103 | Junction temperature fluctuation of the top and bottom tiers in Case H and Case I in Table 9                                                                                                                | 127 |

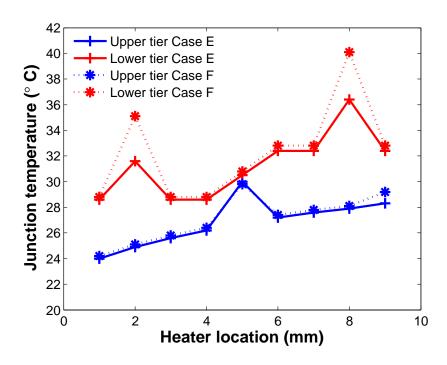

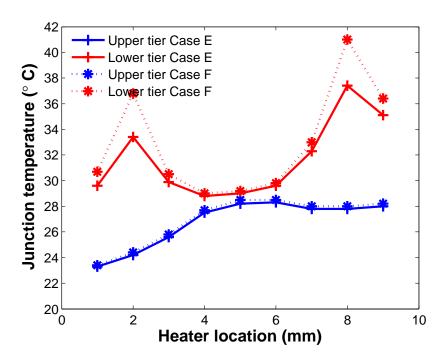

| 104 | (a) Background power of $30~\rm W/cm^2$ plus two hotspots each dissipates $100~\rm W/cm^2$ (Case E) and (b) background power of $30~\rm W/cm^2$ plus two hotspots each dissipates $150~\rm W/cm^2$ (Case F) | 128 |

| 105 | Junction temperature fluctuation of the top and bottom tiers in Case E and Case F in Table 9                                                                                                                | 129 |

| 106 | Junction temperature in Case E and Case F (as listed in Table 9 using the finite-difference model. This figure can be compared with the measured results shown in Figure 105                                | 132 |

| 107 | The modeled heterogeneous stack with (a) MFI and air cavity and (b) microbumps and underfill                                                                                | 133 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 108 | Junction temperature in both tiers with and without the thermal isolation. In the case without thermal isolation, microbumps and underfill are integrated between the tiers | 134 |

| 109 | A heterogeneous 3D stack with MFIs and independent microfluidic heat sink for the low-power die                                                                             | 135 |

| 110 | Benchmark the ideal thermal isolation technology with conventional 3D stacking approach                                                                                     | 135 |

| 111 | Illustration of a 3D stack with a microfluidic cooled interposer                                                                                                            | 141 |

| 112 | Illustration of multi-optimized microfluidic heat sinks                                                                                                                     | 142 |

| 113 | (a) MFI with a thickness of 2 $\mu$ m and (b) MFI with a thickness of 4.5 $\mu$ m                                                                                           | 143 |

### SUMMARY

A key challenge for three dimensional (3D) integrated circuits (ICs) is thermal management. There are two main thermal challenges in typical 3D ICs. First, in the homogeneous integration with multiple high-power tiers, a cooling solution that scales with the number of dice in the stack is needed. Second, in the heterogeneous integration, a thermal isolation solution is needed to 'protect' the low-power tier from the high-power tier. This research focuses to address these two thermal challenges through hybrid microfluidic cooling and thermal isolation technologies.

Within-tier microfluidic cooling is proposed and demonstrated to cool a stack with multiple high-power tiers. Electrical thermal co-analysis is performed to understand the trade-offs between through silicon via (TSV) parasitics and heat sink performance. A TSV-compatible micropin-fin heat sink is designed, fabricated and thermally characterized in a single tier and benchmarked with a conventional air-cooled heat sink. The designed heat sink has a thermal resistance of 0.269 K·cm<sup>2</sup>/W at a flow rate of 70 mL/min. High aspect ratios TSVs (18:1) are integrated in the micropin-fins. Within-tier microfluidic cooling is then implemented in 3D stacks to emulate different heating scenarios, such as memory-on-processor and processor-on-processor. Air gap and mechanically flexible interconnects (MFIs) are proposed for the first time to decrease the vertical thermal coupling between high-power (e.g. processor) and low-power tiers (e.g. memory or nanophotonics). A two-tier testbed with the proposed thermal isolation technology is designed, fabricated and tested. Compared with conventional 3D integration approach, thermal isolation technology helps reduce the temperature at a fixed location in the low-tier by 12.9 °C. The resistance of a single MFI is measured to be  $46.49 \text{ m}\Omega$ .

### CHAPTER I

# BACKGROUND AND INTRODUCTION OF THERMAL CHALLENGES IN 3D ICS

### 1.1 Current 3D ICs Trend

With the continued aggressive scaling of transistors, interconnect performance and power dissipation have become limiting factors for high-performance integrated circuits. This is true for both on-chip and off-chip interconnects. In the latter, the inability to provide high density off-chip wires with low latency, low energy-per-bit, and large bandwidth density has greatly exacerbated the memory wall problem for multi-core processors. This is critical because off-chip bandwidth between multiprocessors and DRAM impacts system performance. To overcome this interconnect limit, three-dimensional integrated circuits (3D ICs) technology has been pursued in recent years, as it represents a promising solution to the interconnect problem by significantly shortening the interconnect length as well as enabling heterogeneous integration of logic, memory, microelectromechanical systems (MEMS), and optoelectronics.

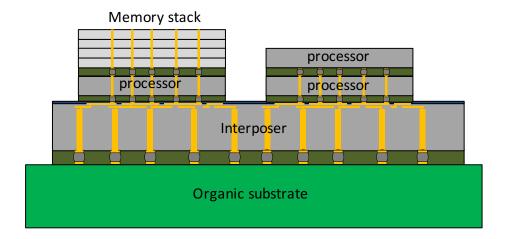

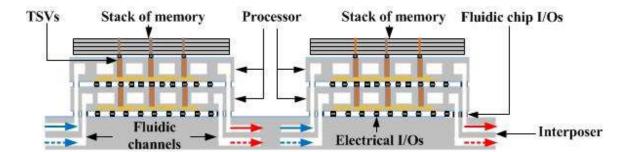

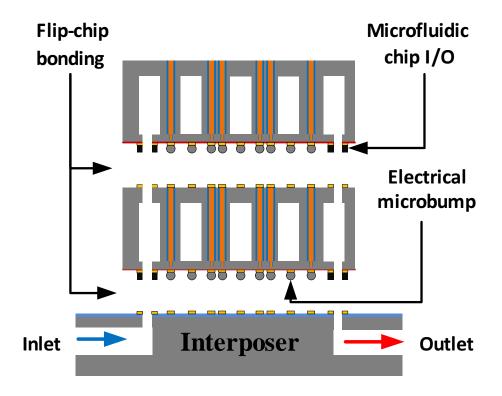

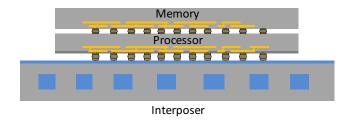

A typical 3D IC with homogeneous and heterogeneous stacks is shown in Figure 1. In the homogeneous 3D integration, two processor tiers are stacked as an example. In the heterogeneous integration, several memory tiers are stacked on top of a processor tier. Both stacks are bonded to a silicon interposer through microbumps and can communicate with each other through fine-pitch interposer-level interconnects.

A key challenge for such high-power 3D applications is thermal management. There are two main thermal challenges in a typical 3D IC system. First, in the homogeneous integration where more than one high-power tier is integrated, an effective cooling method that can scale with the number of tiers is needed. This is needed

**Figure 1:** Schematic of a typical 3D IC with two stacks. The homogeneous stack contains two processor tiers. The heterogeneous stack contains several memory stacks on top of a processor tier.

because the power density in 3D ICs and the thermal resistance of the dice within the stack increases as the number of tiers increases. The latter is due to the fact that the 'inner' dice do not have direct access to the top-attached heat sink. The second thermal challenge in the system shown in Figure 1 is the thermal coupling effect. This challenge is especially significant in heterogeneous integration where high-power tiers are stacked with low-power tiers, such as a memory stack on a processor stack, a processor on a silicon photonics stack, and MEMS on a processor stack. In 3D ICs, the thermal coupling between the vertical tiers is critical because 3D ICs bring dice closer than in conventional ICs. Without an effective thermal isolation between the tiers, the thermal coupling will cause the low-power tier to follow the same temperature trend as that of the high-power tier and degrade its performance.

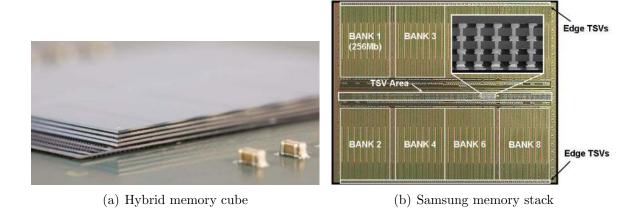

The performance and power consumption of high performance unit systems depends on the junction temperature. Currently, commercialized 3D IC products do not contain high power dice due to lack of effective cooling and thermal isolation technology. Figures 2(a) and 2(b) show examples of Micron Technology's hybrid memory cube (HMC) with four DRAM tiers stacked on top of a logic tier [1] and a stack of

Figure 2: Examples of current commercialized 3D IC products.

Samsung's dynamic random-access memories (DRAMs) [2], respectively. Note the central processing unit (CPU) is not included in the stack in either case because of thermal challenges. The objective of this research is to

- Demonstrate an effective cooling solution that scales with the number of dice.

- Demonstrate an effective thermal isolation solution that 'protects' the low-power tiers from the high-power tiers to enable heterogeneous 3D stacking.

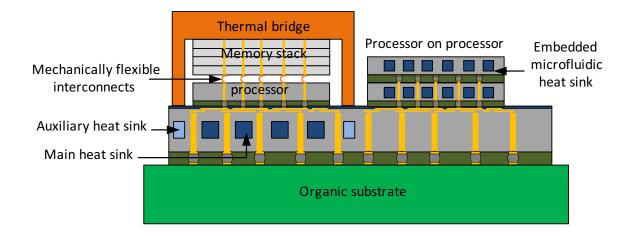

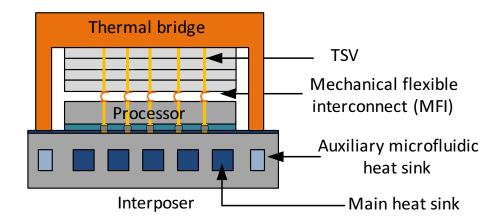

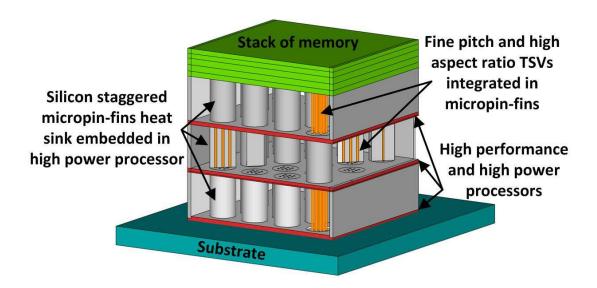

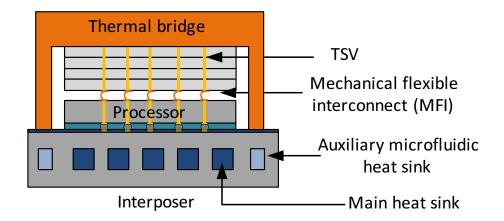

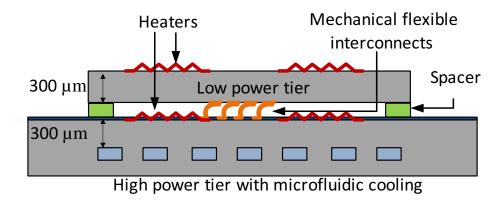

A schematic illustrating our proposed prototype that solves the two thermal challenges is shown in Figure 3. For the homogeneous stack, embedded microfluidic cooling is adopted. Each high-power tier has its own microfluidic heat sink. Since these heat sinks are microscale, they can be integrated into any high-power tier as needed. The detailed integration method for this idea is discussed in Section 1.2. In the heterogeneous stack, the proposed solution includes using an air cavity and mechanically flexible interconnects between the heterogeneous elements. The details of the proposed thermal isolation concept is discussed in Section 1.3.

**Figure 3:** Proposed 3D IC prototype solving thermal challenges of lack of effective cooling and lack of effective thermal isolation.

## 1.2 Thermal Challenges in Stacks Containing Multiple High-Power Chips

Three dimensional integration is considered to be a promising solution to continue Moore's Law in the vertical direction, and offer possibilities of increased device density, shorter interconnects, smaller foot print, and heterogeneous integration. Although the concept has been under research for several years since it was first introduced in the 1980s, the products in the market do not yet include high-power units in the stack. The thermal challenge is one of the biggest hurdles.

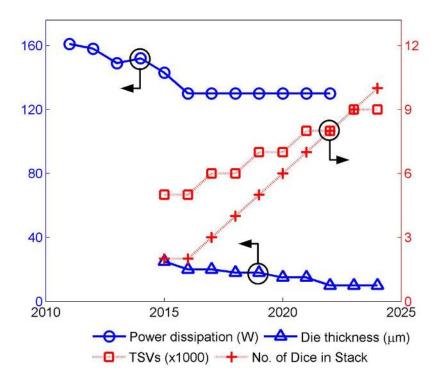

In applications where multiple high-power chips (e.g. processors) are stacked together, the thermal challenge is mainly due to the increased power density and thermal resistance of the 'inner' dice as the number of tiers increases. In these cases, conventional air cooling is not sufficient for the high power stack. In [3], dividing a traditional microprocessor design into two dice to form a logic+logic stack, the peak temperature increases by 14 °C while the total power remains the same. The problem is exacerbated when the power density and number of tiers increases. According to ITRS projections, each high-power unit will dissipate 130 W by 2020 and each stack may have six tiers (possibly a combination of high-power tiers and low-power tiers) [4].

**Figure 4:** ITRS projections for the number of dice in a stack, number of TSVs, die thickness, and power of a single high-performance chip.

Since air cooling has limited cooling capabilities [5], researchers have shown the possibility of using embedded within-tier microfluidic cooling for 3D ICs [6]–[10]. The advantages of interlayer microfluidic cooling compared to air cooling are as follows:

- 1. Microfluidic cooling has higher cooling capability since water has much higher heat capacity than air.

- 2. The fabrication of the interlayer microfluidic heat sink is compatible with current CMOS microfabrication technology.

- 3. Since the microfluidic heat sink is chip-scale, it has vertical stackability. The air-cooled heat sink (ACHS), on the other hand, can not scale with the number of tiers.

Heat removal (790 W) by a silicon microfluidic heat sink was first demonstrated by Tuckerman and Pease in 1981 [6]. Because of its relative ease of fabrication, single-phase cooling and two-phase cooling using the microchannel heat sink have been widely investigated [9], [11], [12]. Our research mainly focuses on single-phase microfluidic cooling. As microfabrication technology has advanced, more complex microfluidic heat sink designs have become possible, bringing the possibility of outperforming the microchannel heat sink [13]. One method to enhance single-phase cooling utilizes the fabrication of obstructions in the flow direction [8], [13]. In [8], multiple heat sink designs were analyzed and compared including microchannels, inline micropin-fins, and staggered micropin-fins. A staggered micropin-fin heat sink (MPFHS) is demonstrated to have the lowest thermal resistance at a constant flow rate [8].

Figure 6 depicts a typical chip configuration with embedded microfluidic heat sink in the literature, in which the fluid is supplied through a single inlet from the top of the stack [14], [15]. The authors of [14] and [15] have demonstrated the cooling of a four-tier and a two-tier stack with total power dissipation of 390 W and 200 W, respectively. With this approach, it is not possible to control or tailor the flow rate in each tier. However, in a realistic 3D stack, especially in a heterogeneous stack, the power dissipation in each tier may be different (workload dependent). Thus, one needs the capability to control the coolant flow rate in each tier independently. To address this need, wafer-level batch fabricated solder microfluidic chip I/Os and fine pitch electrical microbump I/Os have been recently demonstrated, as shown in Figure 8 [16]. Based on this innovative chip I/O technology, we propose and experimentally demonstrate tier-specific microfluidic cooling where the flow rate in each tier is chosen based on the power dissipation of each tier (Figure 7).

The height of most reported interlayer microfluidic heat sinks ranges from 200  $\mu$ m to 400  $\mu$ m. Because of the insertion of these microfluidic heat sinks, a wafer

Figure 5: Illustration of conventional air cooling technology.

Figure 6: Illustration of prior integrated microfluidic cooling technology.

**Figure 7:** Illustration of the tier-specific microfluidic cooling technology in the present work.

will have a typical thickness of a few hundred microns, which presents challenges to through silicon via (TSV) fabrication and electrical performance. Therefore, designing a microfluidic heat sink without considering TSV fabrication compatibility and TSV parasitics greatly diminishes the advantages of 3D ICs. There are very few studies focusing on designing a microfluidic heat sink while accounting for the impact on TSVs. In [7], microchannel dimensions were designed to maximize the TSV density while meeting the thermal constrains. In [17], a microchannel infrastructure with microchannel bends was designed to bypass the region that contains TSVs. However, to date, there has been neither an attempt to optimize the heat sink design while accounting TSV fabrication compatibility nor an attempt to analyze the corresponding impact of the microfluidic heat sink on the electrical performance of TSVs. In this work, electrical and thermal co-analysis of trade-offs between TSV parasitics and heat sink performance was done and the results are shown in Chapter II.

For TSVs in CMOS, where wafer thickness is typically less than 100  $\mu$ m, aspect ratios as high as 15:1 have been demonstrated [18], [19]. For thick silicon wafers (greater than 100  $\mu$ m), TSVs with aspect ratios greater than 10:1 have been shown for the application of silicon interposer [20]. TSVs with higher aspect ratio need to be developed for thicker silicon (with embedded microfluidic heat sinks). Moreover, experimental integration of fine-pitch and high aspect ratio TSVs within microfluidic heat sinks is missing from the literature. In Chapter III, integration of high aspect-ratio TSVs with microfluidic cooling will be shown.

### 1.3 Thermal Challenge in Heterogeneous 3D Stacks

Thermal coupling has always been an issue for ICs. Intra-socket thermal coupling has been investigated between CPU and DIMMs that are in the same socket [21]. Temperature increment was observed in memory when the workload of the CPU increases. Increased power dissipation in the CPU causes the heat sink temperature

Figure 8: Solder-based microfluidic chip I/Os and electric microbumps.

to increase and, thus, causes the downstream memory to become warmer. Withinchip thermal coupling between CPU and GPU has been studied in [22]. An AMD Trinity APU consisting of two CPU cores and one GPU core was used to study the thermal coupling. The moment the two CPU cores were allocated with more power, the GPU core power also increases because of the thermal coupling and the impact of temperature on leakage power. In 3D ICs applications, not only the above mentioned lateral thermal coupling need to be investigated, but the vertical dieto-die level thermal coupling is also critical because 3D ICs bring dice closer than conventional ICs [23], [24]. In applications where high-power chips (e.g. processors) are stacked along with low-power and temperature-sensitive components (memory or silicon nanophotonic chips, for example), thermal management will not only require effective cooling, but may also require effective thermal isolation to 'protect' the temperature-sensitive components from the high and time-varying power dissipation of other chips in the stack. By placing such tiers next to each other, the thermal coupling between them will be significant, leading to possibly undesirable junctiontemperature variation in the temperature-sensitive tier as a result of the high-power

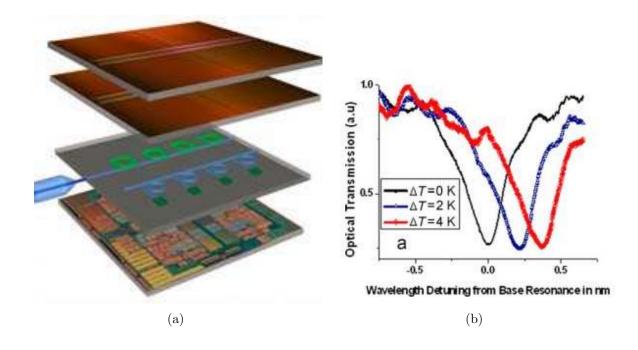

**Figure 9:** (a) Illustration of a 3D stacked memory module containing SDRAM, photonic transceivers, and associated driver circuitry. (b) Temperature impact on microring resonance frequency.

chips.

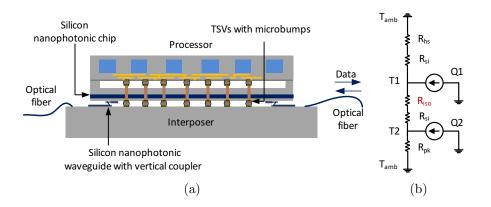

In the case of silicon nanophotonics, stacking such chips in a stack adjacent to logic and memory has been explored [25], [26]. Figure 9(a) shows an example of a 3D stacked memory module with optical interconnections [25]. However, the temperature sensitivity of the optical elements presents significant challenges for integration; for example, a microring modulator with 5  $\mu$ m diameter is reported to have a wavelength drift of 0.11 nm/°C in [27]. Figure 9(a) shows the transmission spectra with varying ambient temperature over 4 °C. A temperature change of 13.5 °C will result in a complete passband mismatch between transmitter–receiver pairs in 64-channel wavelength-division multiplexing (WDM) [26].

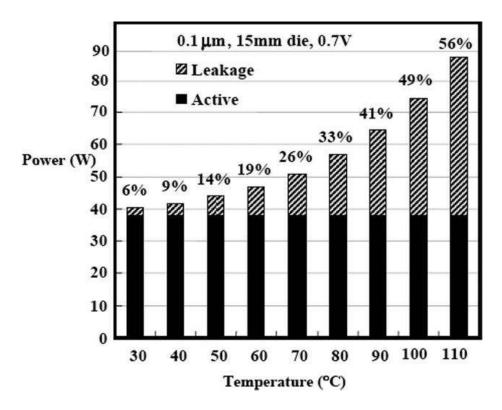

In applications involving a memory die, it has been shown that stacking logic on SRAM causes a 30 to 40 °C temperature increase in the SRAM die [23]. The increased temperature not only causes the leakage power to increase by approximately two times, but also causes the average cache access time to increase by 50 ps (28%)

performance degradation) [23]. A stack of DRAM-on-logic is investigated (Figure 10(a)) in [24]. When logic tier dissipates a uniform power, the temperature difference between the DRAM and logic is very small, as shown in Figure 10(b), which indicates strong thermal coupling between the two tiers. As such, there is a need for wafer-level batch-fabricated thermal isolation technologies in order to minimize thermal coupling between the high-power logic chip and the low-power and temperature-sensitive chips in the stack.

**Figure 10:** (a) DRAM on logic stack in [24]. (b) Temperature contour of DRAM and logic when logic has a uniform power dissipation [24].

There is very little effort to investigate thermal isolation in 3D ICs. Researchers have proposed to use a set of TSV guard rings to thermally isolate to some level two circuits side by side (Figure 11(a)) [28]. In their simulation, the bottom of the Si substrate is set to a constant temperature of 25 °C. Because of the high thermal conductivity of the TSVs, a large portion of the heat generated from circuit B tends to flow downwards to the bottom through TSVs rather than flows to the circuit A and, thus, creates thermal isolation between the two circuits. Circuit A has a ring oscillator, whose resonant frequency will shift because of the influence of circuit B. It is claimed that the TSV-based guard ring can alleviate the thermal coupling so that the resonant frequency shift is reduced by 65%. Because of the temperature sensitivity of silicon phonics devices, a local heater is often used to create a constant

**Figure 11:** (a) TSV guard ring to reduce thermal coupling [28] and (b) SEM for a two-channel (de)multiplexer with an air cavity beneath to reduce the thermal coupling [29].

temperature environment in a local region. Extra tuning power is needed from the heater if the generated heat spreads to the adjacent area because of thermal coupling. Researchers from Oracle [29] have demonstrated decreased thermal decoupling with an air trench right below the microring resonators and heaters (Figure 11(b)). The tuning power is reduced from 27 mW to 21 mW. However, the thermal isolation between tiers in 3D ICs is missing from the literature.

In the current technology, tiers in 3D ICs are bonded through microbumps. Two tiers in a stack may expand differently due to different junction temperature, and may cause stress on the microbumps which leads to cracking in thermal cycles. To address this issue, underfill is applied between the two tiers to alleviate the stress on the solder microbumps, as shown in Figure 1. However, the thermal conductivity of underfill is usually around 0.4 W/mK– 1.3 W/mK. This will introduce a small thermal resistance between the two tiers and cause thermal coupling between the tiers. Thus, we propose to integrate an air gap and thermally degraded mechanically flexible interconnects (MFIs) to replace both microbumps and underfill. The proposed prototype is shown in Figure 12. When the two tiers expand differently because of different junction temperatures, stress will occur on MFIs. Unlike rigid solder

**Figure 12:** Prototype shows the proposed thermal isolation technology that replaces microbumps and underfill with air gap and thermally degraded MFIs.

microbumps, MFIs will deform elastically under stress, which helps maintain the electrical connectivity between tiers. Thanks to this phenomenon, MFIs can help get rid of the underfill and thus reduce the thermal coupling between tiers. The thermally degraded MFIs are a type of MFI that are specially designed to have large thermal resistance and small electrical parasitics.

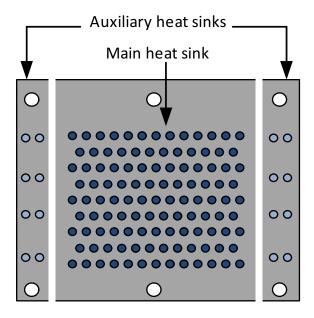

Once the low-power dice are thermally isolated from the high-power die, it is also isolated from the interposer-level cooling path. Therefore, a new cooling path is provided to the memory dice from the top. A thermal bridge is attached to the top of the memory and thermally interconnects the memory dice to the auxiliary microfluidic heat sink in the interposer. The thermal bridge can be made of metals of high thermal conductivity such as copper. Thermal interface material is applied between the thermal bridge and memories. Also to be noted, the interposer has multi-optimized microfluidic heat sinks. The main heat sink is for cooling the processor, and the auxiliary heat sink is dedicated to the memory stack. The dark blue color represents the heat sink dedicated for the processor, and the light blue color represents the auxiliary heat sink. The two heat sinks have separate flow paths and may have different flow rates and designs depending on their power loads. For example, the

auxiliary heat sink for the memory stack may be less dense and may have a smaller flow rate. The proposed concept is demonstrated with a two-tier thermal testbed. The thermal isolation technology with MFIs is implemented. The results will be shown in Chapter V.

### 1.4 Organization of the Thesis

In this thesis, a hybrid thermal management solution is proposed to overcome the above mentioned challenges. The key contributions of this work include:

- 1. A silicon micropin-fin heat sink (MPFHS) is designed to be TSV–compatible. Electrical-thermal trade-off analysis is performed to study the impact of heat sink design on cooling capability and electrical parasitics of TSVs. The selected design provides a thermal resistance of 0.2 K·cm²/W, a TSV dielectric capacitance of 0.4 pF, and a TSV density of 4× 10⁴ TSVs/cm².

- 2. The designed TSV-compatible MPFHS is thermally characterized in a single tier and benchmarked with a conventional air-cooled heat sink. High aspect ratio TSVs with a diameter of 10  $\mu$ m and a height of 178  $\mu$ m (18:1) are integrated in the micropin-fins.

- 3. Within-tier microfluidic cooling is then implemented in 3D stacks to emulate different heating scenarios, such as memory-on-processor, processor-on-processor with the same power load, and processor-on-processor with different power loads. The microfluidic heat sink maintains the stack temperature below 50 °C for a total power density of 200 W/cm² in a two-tier processor-on-processor stack.

- 4. A tier-specific cooling mechanism is proposed and implemented in a two-tier stack where the flow rate in each tier is chosen based on the power dissipation and temperature target for each tier. With tier-specific cooling, two tiers with different power levels can have the same junction temperature, mitigating the

thermal mechanical stress between the tiers. Pumping power reduction of 37.5% can be achieved by preventing over-cooling.

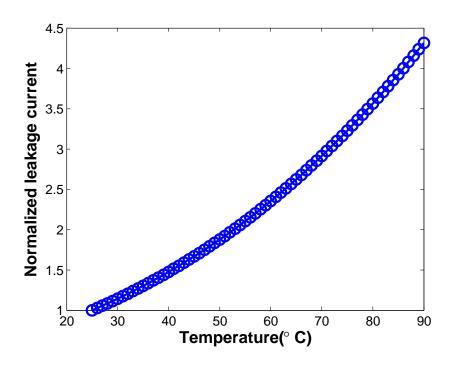

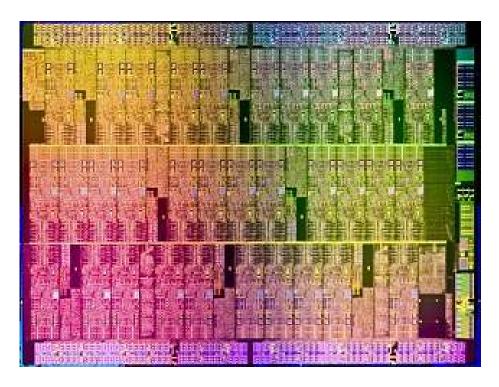

- 5. Within-tier microfluidic cooling is also implemented in a multi-core stack. The lateral and vertical thermal coupling are analyzed. The vertical thermal coupling is minimal when each tier contains its own microfluidic heat sink. The leakage power is analyzed with the presence of lateral thermal gradient.

- 6. A new heterogeneous architecture is proposed for the first time featuring thermal isolation technology using an air gap, thermally degraded MFIs, and novel cooling structures. The architecture is experimentally demonstrated with a two-tier testbed, and benchmarked with conventional 3D stacking approach.

The thesis is organized as follows. Chapter II discusses the electrical—thermal coanalysis of the microfluidic heat sink and TSV parasitics. Chapter III presents the

co-integration of the TSV—compatible microfluidic heat sink with 18:1 aspect ratio

TSVs. Thermal and electrical testing are also included in Chapter III. In Chapter

IV, the microfluidic cooling is evaluated in 3D stacks. Scenarios including processoron-processor, memory-on-processor, and processors with different power loads are

emulated. A tier-specific cooling mechanism is proposed and implemented to minimize

the vertical thermal coupling within the stack. Chapter V discusses the modeling and

experimental implementation of the thermal isolation technology based on air cavity

and MFIs.

### CHAPTER II

# THERMAL-ELECTRICAL CO-ANALYSIS OF A TSV-COMPATIBLE MICROFLUIDIC HEAT SINK

### 2.1 Introduction

Transistor scaling along with continued material innovation in ICs has propelled the semiconductor industry during the past 50 years in terms of improvements in IC performance, power dissipation, and cost [30]. However, with the continued aggressive scaling, interconnect performance and power dissipation have become limiting factors for higher-performance integrated circuits [31]. This is true for both on-chip and off-chip interconnects [32]. In the latter, the inability to provide high density off-chip wires with low latency, low energy-per-bit, and large bandwidth density has greatly exacerbated the memory wall problem for multicore processors. This is critical because off-chip bandwidth between multiprocessors and DRAM impacts system performance [33]. To overcome this interconnect limit, 3D IC technology has been pursued in recent years, as it represents a promising solution to the interconnect problem by significantly shortening the interconnect length as well as enabling heterogeneous integration of logic, memory, MEMS, and optoelectronics [34], [35].

TSVs are the key enabling technology for 3D ICs as they provide inter-layer communication and power delivery between stacked chips. Shorter TSVs (in thinner dice) have lower capacitance and, thus, lower latency and energy-per-bit. Therefore, thinner dice are preferred in 3D ICs. According to the International Technology Roadmap for Semiconductors (ITRS), die thickness is expected to decrease from 25  $\mu$ m to 10  $\mu$ m by 2024 [6] (Figure 4). A key challenge for high-power 3D applications is cooling. The reason is that both the power density in 3D ICs and the thermal resistance of

the dice within the stack increase as the number of tiers increases. The latter is due to the fact that the inner dice do not have direct access to a heat sink. Prior studies have shown the possibility of using interlayer microfluidic cooling instead of conventional air-cooling for 3D ICs to overcome this challenge [6]-[10]. The height of most reported interlayer microfluidic heat sinks ranges from 200  $\mu$ m to 400  $\mu$ m in [6]–[10]. Because of the insertion of these microfluidic heat sinks, a wafer will have a typical thickness of a few hundred micrometers, which presents significant challenges to TSV fabrication and electrical performance. Therefore, designing a microfluidic heat sink without considering TSV fabrication compatibility and TSV parasitics greatly diminishes the advantages of 3D ICs. Microchannel dimensions were designed to maximize the TSV density while meeting the upper limit of thermal constraints in [7]. A microchannel infrastructure with bent microchannels was designed to bypass the region that contains TSVs in [17]. However, to date, there has been neither an attempt to optimize the heat sink design while accounting TSV fabrication compatibility nor an attempt to analyze the corresponding impact of the microfluidic heat sink (MFHS) on the electrical performance of TSVs. This section of the thesis investigates the thermal and electrical co-design of an interlayer MFHS. Design trade-offs between heat removal capability and the associated TSV parasitics are analyzed.

### 2.2 Literature Review of Microfluidic Heat Sink

Figure 13 summarizes the evolution of microfluidic heat sink design. A few key efforts are included for comparison. Microfluidic heat sinks for heat removal from IC were first demonstrated by Tuckerman and Pease in 1981 [6]. In their work, a heat removal of 790 W is demonstrated in a 1 cm<sup>2</sup> area. The lowest thermal resistance that is reported in their work is 0.09 K/W under a pressure drop of 213.9 kPa (corresponding to 512 mL/min). The height of the heat sink is 302  $\mu$ m. Owing to advancement in microfabrication, more complicated structures can be designed to enhance the

| Structure                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Reference                                                 | Conclusions                                | Dimensions (µm)                                                        |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------|------------------------------------------------------------------------|

| Plain<br>Microchannel     | Company of the Property of the | D. B. Tuckerman and<br>R. F. W. Pease<br>(Stanford), 1981 | 0.09 K/W at 213.9<br>kPa (516 mL/min)      | W <sub>ch</sub> =50; W <sub>w</sub> =50;<br>H=302                      |

| Enhanced<br>Microchannel  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | E. G. Colgan et. al.<br>(IBM), 2005                       | 0.21 K·cm²/W at<br>27 kPa (1250<br>ML/min) | W <sub>ch</sub> =75; W <sub>w</sub> =25;<br>L <sub>w</sub> =250; H=195 |

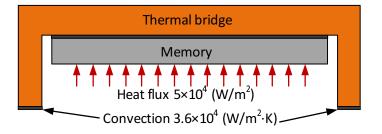

| Staggered<br>Micropin-fin | The state of the s | Y. Peles et. al. (RPI),<br>2005                           | 0.03 K/W at 203<br>kPa                     | D=100;<br>Porosity=0.65;<br>H=400                                      |