Open access · Journal Article · DOI:10.1063/1.4961936

## III/V nano ridge structures for optical applications on patterned 300 mm silicon substrate — Source link ☑

Bernardette Kunert, W Guo, Yves Mols, Bin Tian ...+7 more authors

Institutions: Ghent University, IMEC

Published on: 29 Aug 2016 - Applied Physics Letters (AIP Publishing)

Topics: Substrate (electronics), Silicon, Metalorganic vapour phase epitaxy, Epitaxy and Silicon oxide

Related papers:

- · Room-temperature InP distributed feedback laser array directly grown on silicon

- Site Selective Integration of III–V Materials on Si for Nanoscale Logic and Photonic Devices

- Optical pumped InGaAs/GaAs nano-ridge laser epitaxially grown on a standard 300-mm Si wafer

- · Electrically pumped continuous-wave III-V quantum dot lasers on silicon

- Growing antiphase-domain-free GaAs thin films out of highly ordered planar nanowire arrays on exact (001) silicon

## III/V nano ridge structures for optical applications on patterned 300mm Silicon

B. Kunert<sup>1</sup>, W. Guo<sup>1</sup>, Y. Mols<sup>1</sup>, B. Tian<sup>2</sup>, Z. Wang<sup>2</sup>, Y. Shi<sup>2</sup>, D. Van Thourhout<sup>2</sup>, M. Pantouvaki<sup>1</sup>, J. Van Campenhout<sup>1</sup>, R. Langer<sup>1</sup>, K. Barla<sup>1</sup>

<sup>1</sup>imec, Kapeldreef 75, 3001 Heverlee, Belgium

<sup>2</sup>Photonics Research Group, Ghent University, Sint-Pietersnieuwstraat 41, Ghent 9000, Belgium

We report on a new integration approach of III/V nano ridges on patterned Silicon (Si) wafers by metal organic vapor phase epitaxy (MOVPE). Trenches of different width ( $\leq$  500nm) were processed in a silicon oxide (SiO<sub>2</sub>) layer on top of a 300 mm (001) Si substrate. MOVPE growth conditions were chosen in a way to guarantee an efficient defect trapping within narrow trenches and to form a box shaped ridge with increased III/V volume when growing out of the trench. Compressively strained InGaAs/GaAs multi-quantum wells (MQWs) with 19 % Indium were deposited on top of the fully relaxed GaAs ridges as an active material for optical application. Transmission electron microcopy (TEM) investigation shows that very flat QW interfaces were realized. A clear defect trapping inside the trenches is observed whereas the ridge material is free of threading dislocations with only a very low density of planar defects. Pronounced QW photoluminescence (PL) is detected from different ridge sizes at room temperature. The potential of these III/V nano ridges for laser integration on Si substrates is emphasized by the achieved ridge volume which could enable wave guidance and by the high crystal quality in line with the distinct PL.

197 words <250words

Silicon Photonics is a rapid growing field of research, combining the advantages of the mature Silicon (Si) microelectronic technology and of optical data transmission [1] [2]. Having a low-cost integration scenario for an efficient laser diode on Si substrate is key to fully profit from optoelectronic integration circuits (OEICs). The main obstacle is that Si is a poor light emitter due to its indirect electronic band structure, therefore other active materials with high optical gain have to be transferred to Si substrates. Many different approaches are under investigation, which can be divided into two main routes: 1. Hybrid integration such as wafer- or chip-bonding [3] [4] [5] [6] [7], which allows for the best choice of laser material and device structure but is very likely a complex and expensive process flow. 2. Monolithic integration such as the direct epitaxial growth of laser materials on Si [8] [9] [10] [11] [12] [13] [14] [15]. A monolithic approach could lead to a collective integration process flow with CMOS, which is highly scalable and cost-efficient. But it suffers from the formation of misfit and threading dislocation density has been reported in literature, the remaining defect density still limits the device lifetime [16] [17]. Quantum dot laser is a promising approach, as it seems to degrade less rapidly under the presence of non-radiative defects [18] [19]. Hetero-epitaxial growth of GaNAsP/GaBP based laser diode lattice matched on Si circumvents the formation of misfit dislocation (MD) but bears new challenges due to the complexity of the involved new material systems such as dilute nitrides

and borides [20]. Up to now, the remaining defect density in the active material system was always preventing a sufficient laser diode lifetime in the monolithic integration approach.

In this paper we discuss a III/V laser integration approach on (001) Si, which is based on aspect ratio trapping (ART) [21] [22] in narrow oxide trenches starting with a V-shaped Si surface. A high aspect ratio allows for an efficient defect trapping whereas III/V nucleation on the {111} facets of the V-shape avoids the formation of anti-phase domains [23] [24]. The high potential of ART has been demonstrated in various recent publications [15] [25] [26]. However in the present work we want to benefit at most from ART by growing in very narrow trenches while still achieving a high III/V material volume for sufficient modal gain by growing out of the trench under conditions that lead to a clearly broadened III/V ridge. Pseudomorphically strained InGaAs/GaAs MQWs were deposited on box shaped GaAs ridges on top of a patterned 300 mm Si wafer. High crystal quality and distinct photoluminescence have been observed, emphasizing the potential of these III/V nano ridges for laser integration.

The epitaxial growth was performed by metal organic vapor phase epitaxy MOVPE in a 300 mm deposition chamber applying group-V and –III precursors such as tertiarybutyl arsine (TBAs), trimethylndium (TMIn), triethylgallium (TEGa) and trimethylgallium (TMGa).

Based on a standard STI (shallow trench isolation) process flow, Si trenches of different width and length were realized in a 300 nm thick SiO<sub>2</sub> layer on exact (001) 300 mm Si substrates. The trench structures investigated in this work have a length of 10  $\mu$ m whereas the width varies from 20 nm to 500 nm. Trenches with the same dimension are grouped as arrays within 600  $\mu$ m x 600  $\mu$ m fields. The ratio of the Si trench surface versus the total area is kept between 9-10 %. V-shape formation and exposure of {111} facets before epitaxial growth was achieved by a tetramethylammonium hydroxide (TMAH) wet-etch process. More details about the Si wafer treatment before deposition and a general introduction to the GaAs integration approach by MOVPE are published in [27]. For the current structures we applied a two steps GaAs monolithic deposition process. The GaAs nucleation layer was grown at 360 °C with TEGa whereas the main layer growth inside as well as outside the trench was performed at 580 °C with TMGa. Chosen V/III ratios were 70 and 15, respectively. The InGaAs QWs were also deposited at 580 °C with a V/III ratio of 18.

## Photoluminescence (PL) set up, pump spot etc

Transmission electron microcopy (TEM) was performed using a Titan (FEI) microscope operating at 300kV whereas a Helios (FEI) was used for the sample preparation (focus ion beam (fib) lift-out). Spin-on-carbon (SOC) and electron beam deposited Platinum (e-Pt) were used as a capping layer.

A low temperature seed is important to ensure a 2-dimensional GaAs nucleation layer on the {111} facets and at the same time to avoid the formation of planar defects such as stacking faults and twins. Growth at high temperature guarantees better GaAs crystal quality and enhances misfit defect nucleation and TD gliding, which are essential for full relaxation. The silicon oxide (SiO<sub>2</sub>) trench sidewalls lead to an efficient defect trapping. TDs laying in planes perpendicular to the STI walls are easily confined. But also TDs running in lattice planes parallel to the trench orientation can be trapped, if these defects glide along {111} planes such as 60° misfit dislocation preferably do. Due to the inclined angle of these {111} planes towards the vertical trench wall, each {111} plane will finally hit an oxide wall, if the aspect ratio is high enough. In the same way planar defects on {111} planes parallel to the trenches are trapped. Only planar defects laying in planes perpendicular to the trenches will never be blocked. Therefore it is of key importance to avoid the formation of stacking faults and twins from the beginning by an optimized seed layer and sufficient pre-cleaning of the Si surface, whereas the nucleation of misfit- and threading dislocations should be initiated as deep as possible in the trench, close to the Si surface, to benefit from a high aspect ratio.

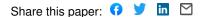

Under the chosen growth conditions all trenches defined by the mask pattern were filled uniformly with GaAs. Since the deposition was continued after reaching the trench top, a clear box shape formation was observed along each trench. The growth rate on the top (001) surface dominates the shape evolution but GaAs is also deposited on the formed {011} side walls, although with significantly lower growth rate. At the bottom of the rectangular box, {111} facets are formed. Figure 1 shows scanning electron microscopy (SEM) images of GaAs box shaped ridges. The basic rectangular shape evolution is the same for narrow and wide trenches while the total volume and ridge height is defined by the trench width. It is also important to emphasize, that the ridge courses are very straight and uniform with flat surfaces in all directions for the purpose of realizing a waveguide with low light scattering losses.

Figure 1: SEM pictures of box shaped ridges integrated on STI-patterned Si wafers. Top left: cross section of a 100 nm wide trench. Top right: Cross section of 20nm wide trenches. Bottom: inclined top-view of a 100 nm trench array.

Reciprocal space maps (RSM) indicate (not shown here), that these GaAs ridges are completely relaxed, thus the (001) GaAs surface was chosen as a buffer, providing the strain-free lattice constant of GaAs for the pseudomorphic growth of compressively strained InGaAs MQWs. In order to achieve efficient PL and high modal gain, a three-time InGaAs/GaAs QW structure with about 19% In was grown on these GaAs ridges.

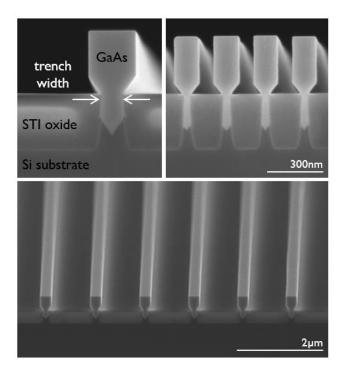

The InGaAs QWs are clearly noticeable in HAADF-STEM (high-angle annular dark-field scanning transmission electron microscopy) images, see Figure 2. The top-left picture is a cross-section of the full device ridge while the top-right image provides a higher magnification of the QW region. The straightness of the QWs becomes very obvious in the transverse HAADF-STEM section along the trenches, bottom picture in figure 2 (the GaAs inside the STI trenches has a slightly different contrast, because some STI material was also cut out during the fib (focus ion beam) lamella preparation). Energy-dispersive X-ray measurements (EDX) confirm the In content of about 19% for the 100 nm wide trenches.

The QW thicknesses on the (001) plane are 7.7 nm, 8.9 nm and 9.9 nm counting from the bottom to the top although the growth time was kept constant. The deposition time of the last three GaAs barrier layers was also fixed but it is very obvious in figure

2 (top-right), that the thickness is decreasing going from the bottom of the structure to the top. A close look at the magnification in figure 2 reveals, that InGaAs is also deposited on the {111} side walls, although the growth rate is significant smaller.

The III/V material supply for a given deposition time, coming from the gas phase as well as from loading effects on the STI mask, is distributed around the full box surface at which the growth rate on the top (001) surface dominates the ridge evolution. The increase in total surface over time leads to a clear reduction in growth rate with rising box size. This strong correlation between the effective (001) growth rate and the total ridge size requires well-adjusted MOVPE process conditions for the full device stack, which is possible once the growth rates are defined. On the contrary the side wall deposition leads to a very good lateral carrier confinement reducing non-radiative recombination channels at the QW side surfaces and is therefore desirable.

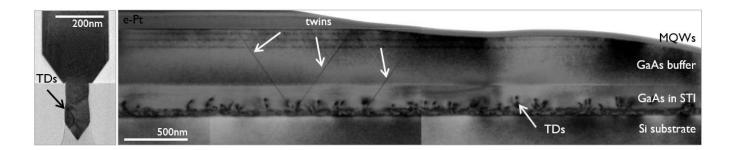

That ART leads to a very efficient defect trapping in 100 nm wide trenches has been confirmed by investigating high resolution HR-TEM and bight field BF(002) images in cross-section looking at several trenches as well as along a 5.5  $\mu$ m long transverse ridge lamella. All threading dislocations (TDs) are well confined inside the STI trench. No indication of any misfit and threading dislocations was found above the STI level or close to the MQW region. Only three planar defects such as twins are visible in a 5.5 $\mu$ m long transverse section, see figure 3.

The complete blocking of TDs within the trench region is a very important achievement towards laser integration with sufficient life time. The impact of planar defects on device performance might be less than for TDs, nevertheless, a further reduction in density is wanted. The formation of planar defects can have various sources. In our case we suspect that twins or stacking faults are caused by either a non-optimal GaAs seed layer or by residuals and contamination on the Si surface due to an insufficient cleaning procedure.

| e-Pt<br>soc<br>STI<br>200 nm | barrier<br>QW<br>barrier<br>QW<br>barrier<br>QW |

|------------------------------|-------------------------------------------------|

| InGaAs/GaAs QWs              |                                                 |

| GaAs buffer                  |                                                 |

| GaAs in STI                  |                                                 |

| Si substrate                 | 500nm                                           |

Figure 2: HAADF-STEM pictures of a box shaped GaAs ridge with three InGaAs QWs. Top-left: Cross-section of the full ridge. Top-right: Higher magnification of the QW region. Bottom: Transverse section along the trench. The GaAs inside the STI shows a slightly different contrast because the fib-sample preparation has also cut out some STI-oxide.

Figure 3: Left: Cross-section HR-TEM of the GaAs buffer. Right: Combined BF(002) images of a transverse section along the trench. The vertical lines visible in the Si substrate are caused by the image combination. Threading dislocations are clearly visible by the dark blurred contrast whereas planar defects cause a straight dark line in <111> directions.

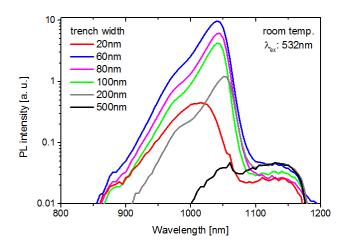

Figure 4: Room temperature PL spectra from different trench width in log-scale.

In order to have a first feedback about the optical properties of the QWs, room temperature PL measurements were carried out looking at different trench widths. A clear emission peak between 1000 nm and 1050 nm can be observed from all structures except for the 500 nm trench width. The photon emission is several orders of magnitude higher in intensity than from the doped Si substrate around 1140 nm. Figure 4 contains a selection of PL spectra in log-scale. Some spectra show a weak high-energetic shoulder around 980 nm, which could be related to radiative recombination from higher quantized states. For the widest trench size the QW-PL is still recognizable but very weak. With reducing trench width the corresponding PL intensity increases up to 60 nm wide trenches before going down again towards 20 nm wide trenches. But even for the narrowest trench width of 20 nm the PL intensity from the QWs is still very pronounced, see figure 4. Comparison of the PL intensity has to be done very carefully due to the following reason: The total III/V ridge volume on top of the trenches as well as the periodic arrangement of each trench within an array varies, therefore the absorption of the pump light will differ in each structure leading to different excited carrier densities. In addition the changing ratio of surface area over ridge volume for each type of trench will have a big impact on the effective carrier concentration in the QWs considering that non-radiative recombination processes at surface states are in competition to the radiative recombination in the active material. Although it is difficult to judge about the overall impact of these uncertainties, it is very likely that the decrease in PL intensity towards wide trenches is linked to an increase in TD density. The aspect ratio of trenches more than 100nm wide is quite low leading to an insufficient defect trapping. Hence, the remaining defect density in the ridge material of wider trenches could cause high carrier losses. The intensity decline towards narrow trenches could be related to a disproportional rise in ridge surface area or less pump light absorption.

The shift in PL-peak position can be explained by a change in In-concentration or in QW thickness for the different trenches, inducing an energetic shift in the quantized states. Both effects are very likely to occur because the MOVPE growth behavior on top of the ridge is very complex. Further investigation is necessary to evaluate both explanations.

The PL line width of the 100 nm wide structure is about 38meV under the chosen experimental conditions. TEM investigation of the 100nm wide trench structure revealed that the QW-thickness is not constant but varies.

This variation in QW width will have an impact on the PL line width of a single MQW stack due to contributions from different quantized states. This QW-thickness variation seems to be the strongest for the 20nm trenches, since the PL line width is clearly broadened in comparison to the others. However, the origin of this broadening can be easily avoided by adjusting the growth time for each QW.

In conclusion, we have introduced a new approach towards the integration of III/V nano ridge lasers based on selective area growth in narrow trenches by MOVPE. TEM investigation confirms a very efficient defect trapping in GaAs inside the trenches whereas the GaAs ridge on top of the trenches is completely free of threading dislocations. Only a few planar defects are still present. The growth of pseudomorphically strained InGaAs/GaAs MQWs with 19% In on top of these fully relaxed GaAs ridge leads to a pronounced PL peak around 1040nm, which emphasizes the potential for optical application. Despite of the narrow trench dimension the outgrown III/V ridge has reached a volume suitable for wave guidance, which points towards the realization of a laser diode. Currently the growth of a confining cap layer is being investigated to reduce carrier losses due to surface recombination.

2519 words

- [1] D. Liang and J. E. Bowers, "Recent progress in lasers on silicon," *Nature Photonics*, p. 511, 2010.

- [2] S. Lourdudoss, "Heteroepitaxy and selective area heteroepitaxy for silicon photonics," *Photonic Nanostructure Materials*, Bd. 16, p. 91, 2012.

- [3] M. J. R. Heck, J. F. Bauters, M. L. Davenport, J. K. Doylend, S. Jain, G. Kurcveil, S. Srinivasan, Y. Tang und J. E. Bowers, "Hybrid Silicon Photonic Integrated Circuits Technology," *IEEE Journal of selected topics in quantum electronics*, Bd. 19, p. 6100117, 2013.

- [4] J. Justice, C. Bower, M. Meitl, M. B. Mooney, M. A. Gubbins und B. Corbett, "Wafer-scale integration of group III-V lasers on silicon using transfer printing of epitaxial layers," *Nature Photonics*, p. 610, 2012.

- [5] H. Yang, D. Zhao, S. Chuwongin, J.-H. Seo, W. Yang, Y. Shuai, J. Berggren und Z. M. W. Z. Matthias Hammar, "Transfer-printed stacked nanomembrane lasers on silicon," *Nature Photonics*, Bd. 6, p. 615, 2012.

- [6] G.-H. Duan, "Hybrid III-V on Silicon Laser for Photonic Integrated Circuits on Silicon," *IEEE Journal of selected topics in quantum electronics*, Bd. 20, p. 6100213, 2014.

- [7] G. Morthier, T. Spuesens, P. Mechet, G. Roelkens und D. V. Thourhout, "InP Microdisk Lasers Integrated on Si for Optical Interconnects," *IEEE Journal of selected topics in quantum electronics*, Bd. 21, p. 1500610, 2015.

- [8] H. Chen, A. Ghaffari, H. Wang, H. Morkoc und A. Yariv, "Continuous-wave operation of extremely low-threshold GaAs/AlGaAs broad-area injection laser on (001) Si substrates at room temperature," *Optics Letters*, Bd. 12, p. 812, 1987.

- [9] H. Choi, C. Wang und N. Karam, "GaAs-based diode lasers on Si with increased lifetime obtained by using strained InGaAs active layers," *Applied Physics Letters*, Bd. 59, p. 2634, 1991.

- [10] M. E. Groenert, C. W. Leitz, A. J. Pitera, V. Yang, H. Lee, R. J. Ram und E. A. Fritzgerald, "Monolithic integration of room-temperature cw GaAs/AlGaAs lasers on Si substrates via relaxed grraded GeSi buffer layers," *Journal of Applied Physics*, Bd. 93, p. 362, 2003.

- [11] M. Sugo, H. Mori, Y. Sakai und Y. Itoh, "Stable cw operation at room temperature of a 1.5μm wavelength multiple quantum well laser on a Si substrate," *Applied Physics Letters*, Bd. 60, p. 472, 1992.

- [12] S. Chen, M. Tang, J. Wu, Q. Jiang, V. Dorogan, M. Benamara, Y. Mazur, G. Salamo, A. Seeds und H. Liu, "1.3μm InAs/GaAs quantum-dot laser monolithically grown on Si substrates operating over 100°C," *Electronics Letters*, Bd. 50, p. 1467, 2014.

- [13] T. Frost, S. Jahangir, E. Stark, S. Deshpande, A. Hazari, C. Zhao, B. S. Ooi und P. Bhattacharya, "Monolithic Electrically Injected Nanowire Array Edge-Emitting Laser on (001) Silicon," *Nano Letters*, Bd. 14, p. 4535, 2014.

- [14] H. Kataria, C. Junesand, Z. Wang, W. Metaferia, Y. Sun, S. Lourdudoss, G. Patriarche, A. Bazin, F. Raineri, P. Mages, N. Julian und J. Bowers, "Towards a monolithically integrated III-V laser on silicon: optimization of multi-quantum well growth on InP on Si," *Semicond. Sci. Technol.*, Bd. 28, p. 094008, 2013.

- [15] Z. Wang, B. Tan, M. Pantouvaki, W. Guo, P. Absil, J. V. Campenhout, C. Merckling und D. V. Thourhout, "Room-temperature InP distributed feedback laser array directly grown on silicon," *Nature Photonics*, p. 1, 2015.

- [16] P. Hutchinson und P. Dobson, "Climb asymmetry in degraded gallium arsenide lasers," *Philosophical Magazine A*, Bd. 41, p. 601, 1980.

- [17] J. v. d. Ziel, R. Dupuis, R. Logan und C. Pinzone, "Degradation of GaAs lasers grown by metalorganic chemical vapor deposition on Si substrates," *Applied Physics Letters*, Bd. 51, p. 89, 1987.

- [18] A. Y. Liu, R. W. Herrick, O. Ueda, P. M. Petroff, A. C. Gossard und J. E. Bowers, "Reliability of InAs/GaAs Quantum Dot Lasers Epitaxially Grown on Silicon," *IEEE Journal of selected topics in quantum electronics*, Bd. 21, p. 1900708, 2015.

- [19] S. Chen, W. Li, J. Wu, Q. Jiang, M. Tang, S. Shutts, S. Elliott, A. Sobiesierski, I. R. P. S. A. J. Seeds und H. Liu, "Electrically pumped continuous-wave III-V quantum dot lasers on silicon," *Nature Photonics*, 2016.

- [20] S. Liebich, M. Zimprich, A. Beyer, D. F. C. Lange, S. Chatterjee, N. Hossain, S. Sweeney, K. Volz, B. Kunert und W. Stolz, "Laser operation of Ga(NAsP) lattice-matched to (001) silicion substrate," *Applied Physics Letters*, Bd. 99, p. 071109, 2011.

- [21] J. Li, J. Bai, C. Major, M. Carroll, A. Lochtefeld und Z. Shellenbarger, "Defect reduction of GaAs/Si epitaxy by aspect ratio trapping," *Journal of Applied Physics*, Bd. 103, p. 106102, 2008.

- [22] E. Fitzgerald und N. Chand, "Epitaxial Necking in GaAs grown on pre-patterned Si Substrates," *Journal of Electronic Materials*, Bd. 20, Nr. 10, p. 839, 1991.

- [23] M. Paladugu, C. Merckling, R. Loo, O. Richard, H. Bender, J. Dekoster, W. Vandervorst, M. Caymax und M. Heyns, "Site Selective Integration of III-V Materials on Si for Nanoscale Logic and Photonic Devices," *Crystal Growth & Design*, Bd. 12, p. 4696, 2012.

- [24] Q. Li, K. W. Ng und K. M. Lau, "Growing antiphase-domain-free GaAs thin films out of highly ordered planar nanowire arrays on exact (001) silicion," *Applied Physics Letters*, Bd. 106, p. 072105, 2015.

- [25] R. Cipro, T. Baron, M. Martin, J. Moeyaert, S. David, V. Gorbenko, F. Bassani, Y. Bogumilowicz, J. Barnes, N. Rochat, V. Loup, C. Vizioz, N. Allouti, N. Chauvin, X. Bao, J. Pin und E. Sanchez, "Low defect InGaAs quantum well selectively grown by metal organic chemical vapor deposition on Si (001) 300nm wafers for next generation non planar devices," *Applied Physics Letters*, Bd. 104, p. 262103, 2014.

- [26] S. Li, X. Zhou, M. Li, X. Kong, J. Mi, M. Wang, W. Wang und J. Pan, "Ridge InGaAs/InP multiquantum-well selective growth in nanoscale trenches on Si (001) substrate," *Applied Physics Letters*, Bd. 108, p. 021902, 2016.

- [27] W. Guo, L. Date, V. Pena, X. Bao, C. Merckling, N. Waldron, N. Collaert, M. Caymax, E. Sanchez, E. Vancoille, K. Barla, A. Thean, P. Eyben und W. Vandervorst, "Selective metal-organic chemical vapor deposition growth of high quality GaAs on Si (001)," *Applied Physics Letters*, Bd. 105, p. 062101, 2014.