## III-V-on-nothing metal-oxide-semiconductor field-effect transistors enabled by top-down nanowire release process: Experiment and simulation

J. J. Gu, O. Koybasi, Y. Q. Wu, and P. D. Ye<sup>a)</sup>

School of Electrical and Computer Engineering and Birck Nanotechnology Center, Purdue University,

West Lafayette, Indiana 47907, USA

(Received 20 July 2011; accepted 22 August 2011; published online 15 September 2011)

III-V-on-nothing (III-VON) metal-oxide-semiconductor field-effect transistors (MOSFETs) are experimentally demonstrated with  $In_{0.53}Ga_{0.47}As$  as channel and atomic layer deposited  $Al_2O_3$  as gate dielectric. A hydrochloric acid based release process has been developed to create an air gap beneath the InGaAs channel layer, forming the nanowire channel with width down to 40 nm. III-VON MOSFETs with channel lengths down to 50 nm are fabricated and show promising improvement in drain-induced barrier lowering, due to suppressed short-channel effects. The top-down processing technique provides a viable pathway towards fully gate-all-around III-V MOSFETs. © 2011 American Institute of Physics. [doi:10.1063/1.3638474]

Recently, encouraging progress has been made on the understanding and improvement of oxide/III-V interfaces. As a result, high performance surface channel inversionmode InGaAs metal-oxide-semiconductor field-effect transistors (MOSFETs) with large current drivability have been demonstrated<sup>1-7</sup> and are considered as a strong candidate to replace conventional Si MOSFET at beyond 14 nm technology node. Besides the numerous efforts spent on reducing the interface trap density at the oxide/InGaAs interface, another major challenge of realizing an InGaAs MOSFET in the deep-submicron regime is the effective control of short channel effects (SCE).<sup>8–10</sup> Very recently, Intel has announced that 3-dimensional (3D) tri-gate transistors would be introduced at 22 nm technology node on Si complementary metal-oxide-semiconductor (CMOS) manufacturing. Due to the inherently lower bandgap and larger permittivity of III-V materials, III-V MOSFETs are more susceptible to SCE, making 3D structure a must for III-V logic applications. In fact, InGaAs fin field-effect transistors (FinFETs) (Refs. 11 and 12) as well as multiple gate InGaAs quantum well transistors<sup>13</sup> have been demonstrated, showing improved SCE control by 3D device structure. Further suppression of SCE requires more advanced device architecture that can offer a better gate electrostatic control. Silicon on nothing (SON) MOSFETs have been proposed<sup>14</sup> and experimentally demonstrated, <sup>15</sup> providing a solution for quasi-total suppression of SCE and drain induce barrier lowering (DIBL) with gate length down to 30 nm. The key fabrication processes for SON MOSFETs involve selective removal of the SiGe layer and formation of an air tunnel underneath the Si channel. Similarly, a SON counterpart on the III-V platform, namely III-V on nothing (III-VON), can also be realized if a selective etching process is developed to form an air gap underneath the III-V channel.

In this letter, we report the experimental demonstration of III-VON MOSFETs with  $In_{0.53}Ga_{0.47}As$  as the channel and atomic-layer-deposited (ALD)  $Al_2O_3$  as the gate dielectric.

The key fabrication has been enabled by well-controlled hydrochloric acid (HCl) based selective etching of InP over InGaAs. It is found that the InGaAs fins have to be patterned along [010] direction in order to achieve a channel release process, owing to the anisotropy of InP wet etching. III-VON MOSFETs with channel length ( $L_{\rm ch}$ ) down to 50 nm and fin width down to 40 nm were fabricated. A low DIBL of 45 mV/V at 50 nm gate length is observed experimentally, which is consistent with the numerical simulation results from 3D Synopsys Sentaurus Technology Computer-Aided Design (TCAD). This shows that the III-VON structure is effective at suppressing the SCE of III-V MOSFETs down to at least  $L_{\rm ch} = 50$  nm.

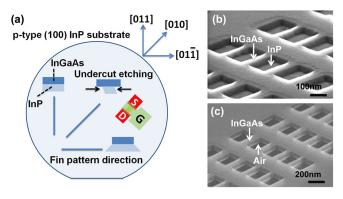

MOSFET fabrication started with a 2 in. p+ InP wafer. A 30 nm  $In_{0.53}Ga_{0.47}As$  layer with p-doping of  $2 \times 10^{16}$ cm<sup>-3</sup> was grown on InP substrate by molecular beam epitaxy as the channel layer. After surface treatment with NH<sub>4</sub>OH solution, a 10 nm Al<sub>2</sub>O<sub>3</sub> was grown by ALD as an encapsulation layer. Source/drain regions were then defined and Si ion implantation at energy of 20 keV and dose of  $1 \times 10^{14}$  cm<sup>-2</sup> was performed. The shortest L<sub>ch</sub> 50 nm was defined by the separation between source and drain regions. The metal gates were designed to be 50 nm longer than the  $L_{ch}$  with 25 nm extension on each side due to the non-self-aligned process. Dopant activation was done using rapid thermal annealing at 600 °C for 15 s in nitrogen ambient. 9,10 Next, the InGaAs fins were patterned along [010] direction as shown in Figure 1(a), using diluted ZEP520A electron-beam resist with a thickness of 200 nm. The fin etching was performed with BCl<sub>3</sub>/Ar gas using a Panasonic high density plasma etcher. <sup>11</sup> After removing the resist, the sample was treated sequentially with diluted buffered oxide etch (BOE) and diluted mixture of HCl and hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>). Then the channel release process was performed using HCl:H<sub>2</sub>O (1:2) solution. It is known that HCl based solution has high selectivity between InP and InGaAs. However, the InP etching is found to be highly anisotropic, and undercut etching is only possible along  $\langle 100 \rangle$  directions. Test fin structures along [011], [010], and  $[01\overline{1}]$  were patterned, followed by etching in diluted HCl. For different fin patterning directions, the

a) Author to whom correspondence should be addressed. Electronic mail: yep@purdue.edu.

FIG. 1. (Color online) (a) Schematic diagram of fin patterning direction, release etching profile, and device alignment to the substrate. (b) Tilted SEM image of fin test structures after fin dry etching and before wire release. (c) Tilted SEM image of fin testing structures after wire release.

etching profile varies as depicted in Figure 1(a). This is also confirmed in Ref. 17 where different emitter mesa surfaces were revealed for different emitter electrode orientations. Figures 1(b) and 1(c) show the tilted scanning electron microscopy (SEM) images for fin test structures before and after channel release process, respectively, where undercut etching was demonstrated. Patterning the fin along (100) directions is the key to realize the III-V channel release at the deep sub-micron scale. After channel release, a 5 nm Al<sub>2</sub>O<sub>3</sub> was regrown using ALD as the gate dielectric. Note that for the purpose of process demonstration, no pre-gate surface passivation such as (NH<sub>4</sub>)<sub>2</sub>S treatment was carried out here. The gate structure was formed by electron beam evaporation of Ni/Au and liftoff process. Due to the vertical directionality of the evaporation, the air gap naturally remains underneath the channel. Au/Ge/Ni source/drain metal was then evaporated and annealed at 350 °C in nitrogen ambient. Finally, test pads were deposited which concluded the fabrication processes. All patterns were defined by a Vistec VB-6 UHR electron beam lithography system.

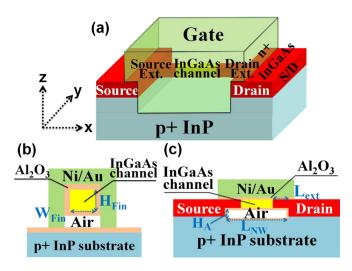

Figure 2(a) shows the schematic diagram of a finished III-VON device from a bird's eye view. Figures 2(b) and 2(c) depict the schematic cross section of the device in the y-z plane and the x-z plane, respectively. The fin height

FIG. 2. (Color online) (a) Schematic diagram of a III-VON MOSFET with  $In_{0.53}Ga_{0.47}As$  channel and  $Al_2O_3$  gate dielectric from a bird's eye view. (b) Cross sectional view of a III-VON MOSFET in x-y plane. (c) Cross sectional view of a III-VON MOSFET in x-z plane.

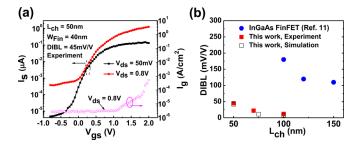

FIG. 3. (Color online) (a) Source current (left) and gate current (right) versus gate voltage for a  $L_{ch} = 50$  nm III-VON MOSFET with  $W_{Fin}$  of 40 nm. (b) DIBL versus  $L_{ch}$  for III-VON MOSFETs from experiment (square) and simulation (hollow square) compared to that of InGaAs FinFET (circle).

(H<sub>Fin</sub> = 30 nm) is determined by the initial InGaAs layer thickness. The smallest fin width (WFin) achieved is 40 nm. The nanowire length  $(L_{NW})$  in this work is fixed at 300 nm, yielding a source/drain extension length (Lext) of around 125 nm for a 50 nm L<sub>ch</sub> device. The smallest air gap height (H<sub>A</sub>) is around 40 nm, controlled by the release etching time. The L<sub>ch</sub> of the devices vary from 100 nm down to 50 nm. Figure 3(a) shows the transfer characteristic and gate leakage current versus gate voltage of a typical III-VON MOSFET with Lch of 50 nm, W<sub>Fin</sub> of 40 nm, and four wires in parallel. To better evaluate the intrinsic device performance, source current is used to eliminate the effect from non-ideal source/drain junction leakage current. The device operates in enhancement mode, with a threshold voltage of 0.36 V from linear extrapolation at a drain voltage of 50 mV. A low DIBL of 45 mV/V is obtained at the shortest gate length of 50 nm, thanks to the III-VON structure. As a comparison, a 100 nm channel length InGaAs FinFET has a DIBL of around 180 mV/V. 11 The subthreshold swing (SS) is found to be around 200 mV/dec, indicating relatively large interface trap density (Dit). Surface treatment before the formation of ALD Al<sub>2</sub>O<sub>3</sub> gate dielectric which could have improved the Dit was not performed since that was not our main purpose in this study. Gate leakage current at  $V_{ds} = 0.8$  V is similar to that in Ref. 11 and stays very low at gate voltage less than 1 V. The saturation current at a drain voltage of 1.6 V and a gate voltage of 2 V reaches 10  $\mu$ A/ $\mu$ m, normalized by the total width of the gated region, i.e.,  $W_G = 2 \times H_{Fin} + W_{Fin}$ . The current can be further improved by applying (NH<sub>4</sub>)<sub>2</sub>S pre-gate treatment<sup>18</sup> and reducing source/drain series resistance.

3D TCAD simulation was performed using Synopsys Sentaurus.<sup>19</sup> Device structures were created according to the experimental parameters, i.e.,  $W_{Fin} = 40$  nm,  $H_{Fin} = 30$  nm, etc. The poisson equation, electron and hole continuity equations were solved using a coupled solver at each mesh node to obtain various output parameters such as potential, electric field, electron and hole densities, etc. No interface traps were incorporated in the simulation. From the simulated transfer characteristics, DIBL was extracted and compared with the experimental data as shown in Figure 3(b). The experimental data agree well with the simulation results. Moreover, the DIBL obtained from InGaAs FinFETs in Ref. 11 is also plotted in the same figure. The III-VON structure shows significant improvement in DIBL reduction, confirming that the more advanced 3D structures are beneficial for the suppression of the SCE.

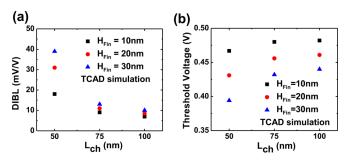

FIG. 4. (Color online) (a) DIBL versus  $L_{ch}$  for III-VON MOSFETs with different  $H_{\text{Fin}}$  from TCAD simulation. (b) Threshold voltage roll-off property of III-VON MOSFETs with different  $H_{\text{Fin}}$  from TCAD simulation.

Finally, the effect of channel layer thickness (H<sub>Fin</sub>) and source/drain extension length (Lext) on the device performance were simulated. H<sub>Fin</sub> was varied from 30 nm down to 10 nm. Figures 4(a) and 4(b) show the DIBL and saturation threshold voltage as a function of channel length with different H<sub>Fin</sub>. Smaller H<sub>Fin</sub> reduces DIBL and improves the threshold voltage roll-off property, due to a better gate electrostatic control of the channel. Devices with different Lext of 10 nm, 50 nm, and 125 nm were also simulated. The results show a clear trade-off between on-current and DIBL. By increasing the extension length, DIBL is reduced while the on-current drops, due to the increase in source/drain resistance. A  $2\times$  higher on-current is expected when  $L_{ext}$  is reduced from 125 nm to 10 nm, while DIBL increases by 30%. These simulation results provide a guideline for future experimental work.

In conclusion, III-VON MOSFETs are experimentally demonstrated. A HCl based release process has been developed to enable air gap formation beneath the InGaAs channel. A typical 50 nm gate length device shows a low DIBL of 45 mV/V, consistent with the results from TCAD simulation. The significant improvement in DIBL compared to the previous InGaAs FinFETs demonstrates better immunity to SCE using the III-VON architecture. This top-down process provides a viable pathway to realize gate-all-around (GAA) III-V MOSFETs which should show even better electrostatic control of the channel.<sup>20</sup>

The authors would like to thank R. Wang, A. T. Neal, M. Luisier, X. L. Li, M. S. Lundstrom, and D. A. Antoniadis

for valuable discussions. This work is supported by the FCRP MSD Center and National Science Foundation.

<sup>1</sup>Y. Xuan, Y. Q. Wu, and P. D. Ye, IEEE Electron Device Lett. **29**, 294 (2008).

<sup>2</sup>Y. Xuan, T. Shen, M. Xu, Y. Q. Wu, and P. D. Ye, Tech. Dig. - Int. Electron Devices Meet. **2008**, 371.

<sup>3</sup>T. D. Lin, H. C. Chiu, P. Chang, L. T. Tung, C. P. Chen, M. Hong, J. Kwo, W. Tsai, and Y. C. Wang, Appl. Phys. Lett. **93**, 033516 (2008).

<sup>4</sup>J. Lin, S. Lee, H.-J. Oh, W. Yang, G. Q. Lo, D. L. Kwong, and D. Z. Chi, Tech. Dig. - Int. Electron Devices Meet. **2008**, 401.

<sup>5</sup>D. Lin, G. Brammertz, S. Sioncke, C. Fleischmann, A. Delabie, K. Martens, H. Bender, T. Conard, W. H. Tseng, J. C. Lin, W. E. Wang, K. Temst, A. Vatomme, J. Mitard, M. Caymax, M. Meuris, M. Heyns, and T. Hoffmann, Tech. Dig. - Int. Electron Devices Meet. 2009, 327.

<sup>6</sup>U. Singisetti, M. A. Wistey, G. J. Burek, A. K. Baraskar, B. J. Thibeault, A. C. Gossard, M. J. W. Rodwell, B. Shin, E. J. Kim, P. C. McIntyre, B. Yu, Y. Yuan, D. Wang, Y. Taur, P. Asbeck, and Y.-J. Lee, IEEE Electron Device Lett. 30, 1128 (2009).

<sup>7</sup>H.-C. Chin, X. Liu, X. Gong, and Y.-C. Yeo, IEEE Trans. Electron Devices **57**, 973 (2010).

<sup>8</sup>Y. Q. Wu, W. K. Wang, O. Koybasi, D. N. Zakharov, E. A. Stach, S. Nakahara, J. C. M. Hwang, and P. D. Ye, IEEE Electron Device Lett. 30, 700 (2009).

<sup>9</sup>Y. Q. Wu, M. Xu, R. S. Wang, O. Koybasi, and P. D. Ye, Tech. Dig. - Int. Electron Devices Meet. **2009**, 323.

<sup>10</sup>J. J. Gu, Y. Q. Wu, and P. D. Ye, J. Appl. Phys. **109**, 053709 (2011).

<sup>11</sup>Y. Q. Wu, R. S. Wang, T. Shen, J. J. Gu, and P. D. Ye, Tech. Dig. - Int. Electron Devices Meet. 2009, 331.

<sup>12</sup>H.-C. Chin, X. Gong, L. Wang, H. K. Lee, L. Shi, and Y.-C. Yeo, IEEE Electron Device Lett. **32**, 146 (2011).

<sup>13</sup>M. Radosavljevic, G. Dewey, J. M. Fastenau, J. Kavalieros, R. Kotlyar, B. Chu-Kung, W. K. Liu, D. Lubyshev, M. Metz, K. Millard, N. Mukherjee, L. Pan, R. Pillarisetty, W. Rachmady, U. Shah, and R. Chau, Tech. Dig. - Int. Electron Devices Meet. 2010, 126.

<sup>14</sup>M. Jurczak, T. Skotnicki, M. Paoli, B. Tormen, J.-L. Regolin, C. Morin, A. Schiltz, J. Martins, R. Pantel, and J. Galvier, Tech. Dig. Pap. - Symp. VLSI Technol. **1999**, 29.

<sup>15</sup>S. Monfray, T. Skotnicki, Y. Morand, S. Descombes, M. Paoli, P. Ribot, A. Talbot, D. Dutartre, F. Leverd, Y. Lefriec, R. Pantel, M. Haond, D. Renaud, M.-E. Nier, C. Vizioz, D. Louis, and N. Buffet, Tech. Dig. - Int. Electron Devices Meet. 2001, 645.

<sup>16</sup>C. Seassal, J. L. Leclercq, and P. Viktorovitch, J. Micromech. Microeng. 6, 261 (1996).

<sup>17</sup>K. Kurishima, S. Yamahata, H. Nakajima, H. Ito, and N. Watanabe, IEEE Electron Device Lett. 19, 303 (1998).

<sup>18</sup>Y. Urabe, N. Miyata, H. Ishii, T. Itatani, T. Maeda, T. Yasuda, H. Yamada, N. Fukuhara, M. Hata, M. Yokoyama, N. Taoka, M. Takenaka, and S. Takagi, Tech. Dig. - Int. Electron Devices Meet. 2010, 142.

<sup>19</sup>See http://www.synopsys.com/tools/tcad/devicesimulation/pages/ sentaurusdevice.aspx for Synopsys Sentaurus Device Manuals.

<sup>20</sup>J. J. Gu, Y. Q. Liu, Y. Q. Wu, R. Colby, R. G. Gordon, and P. D. Ye (unpublished).