Alexoudi, T., Fitsios, D., Bazin, A., Monnier, P., Raj, R., Miliou, A., Kanellos, G. T., Pleros, N., & Raineri, F. (2016). III-V-on-Si Photonic Crystal Nanocavity Laser Technology for Optical Static Random Access Memories. *IEEE Journal of Selected Topics in Quantum Electronics*, *22*(6), [7517367]. https://doi.org/10.1109/JSTQE.2016.2593636

Peer reviewed version

License (if available): CC BY-NC

Link to published version (if available): 10.1109/JSTQE.2016.2593636

Link to publication record in Explore Bristol Research PDF-document

This is the accepted author manuscript (AAM). The final published version (version of record) is available online via IEEE at https://doi.org/10.1109/JSTQE.2016.2593636 . Please refer to any applicable terms of use of the publisher.

# University of Bristol - Explore Bristol Research General rights

This document is made available in accordance with publisher policies. Please cite only the published version using the reference above. Full terms of use are available: http://www.bristol.ac.uk/red/research-policy/pure/user-guides/ebr-terms/

## III—V-on-Si Photonic Crystal nanocavity laser technology for optical Random Access Memories (RAMs)

T.Alexoudi, D. Fitsios, A. Bazin, P. Monnier, R. Raj, A. Miliou, G.T. Kanellos, N. Pleros and F. Raineri

Abstract—Heterogeneous integration of III-V semiconductors on silicon has gained considerable momentum fueled by the need to implement fully functional photonic devices and circuits in a CMOS compatible platform. In this communication, we report on a III-V photonic crystal (PhC) nanocavity, heterogeneously integrated on a Silicon-on-Insulator (SOI) platform, to form a PhC nanocavity laser capable of exhibiting two elementary RAM cell functions individually, namely switching and latching operations under a high-speed, bit-level regime. As such, the PhC nanocavity laser is examined as a generic logic functions building block, suitable towards multi-Gb/s energy-efficient, optical Random Access Memory (RAM) cells with minimal footprint. The proposed device active layer is a nanobeam cavity of 650nm×285nm InP-based wire waveguide, allowing for a recordlow footprint of only 6.2 µm<sup>2</sup> among integrated optical memories so far presented. Bit-level RAM cell operation requires two elementary functions: the Access Gate (AG) switching function and Set-Reset Flip-Flop (SR-FF) latching function. At first, AG switching operation is evaluated through successful Wavelength Conversion (WC) at 10Gb/s, revealing a power penalty of 1dB at 10<sup>-9</sup> BER and a switching energy of only 4.8fJ/bit. Then, fully functional SR-FF memory operation is successfully demonstrated, exhibiting error-free operation with negative power penalty at 5Gb/s and switching energies of 6.4fJ/bit. Flip-Flop operation at higher speeds of 10Gb/s with reduced switching energy levels of 3.2fJ/bit is also experimentally investigated. Both logic operations were demonstrated separately with the same PhC nanocavity laser device exhibiting <50ps switching times and evaluated under realtype data traffic patterns, raising expectations for beyond 20Gb/s capabilities towards implementing energy-efficient, ultra-compact and high-speed true optical RAM setups.

Index Terms— Optical memories, Photonic Crystal nanocavity laser, Access Gate, Wavelength Conversion, Optical Flip Flop

#### I. INTRODUCTION

Silicon photonics have enabled the penetration of optical technology to the computing environment, starting from optical interconnection for rack-to-rack and board-level communications [1] towards photonic-electronic co-integration

Manuscript received February 01, 2016. This work has been supported in part by the European Commission through the FP7-ICT-FET Open project RAMPLAS (Contract No.207773) and also by the FP7-ICT-IP project PhoxTrot (Contract No. 318240).

T. Alexoudi, D. Fitsios, A. Miliou, G.T.Kanellos and N. Pleros are with the Department of Informatics, Aristotle University of Thessaloniki, 54124 Thessaloniki, Greece (e-mail: theonial@csd.auth.gr).

[2]-[4] and on-chip processing [5],[6]. Furthermore, recent progress on InP-on-Si integration technology has revealed great potential in developing novel photonic devices [7], [8] with advanced functionalities as heterogeneous integration of III-V semiconductors on silicon enables the fabrication of optically active devices on a CMOS-compatible platform, raising expectations for an even more powerful photonic integration technology platform. Such advanced photonic devices that would exhibit unique performance in terms of energy efficiency, high bandwidth and large scale integration capabilities could be employed in the near future to address demanding on-chip processing applications and tackle long-lasting problems in computing [9] towards enabling novel architectures [10] that can radically reform the shape of computer science.

One demanding application could be the alleviation of Von Neumann bottleneck, also known as the Memory Wall problem [9]. The root cause of this problem [9] extends along two primary bottlenecks degrading the overall system performance: the long access time of both static and dynamic electronic Random Access Memories (SRAMs and DRAMs, respectively) and the limited bandwidth of the processor-main memory electrical bus. Towards addressing the limited bandwidth problem of electrical bus, optically interconnected CPU-memory paradigms have been demonstrated, indicating that future processor-main memory systems can leverage optics to increase bandwidth through data parallelism [11]-[13]. On the other hand, the long access times of electronic SRAM circuitry will still persist even though optical bus solutions come at the foreground. Towards removing also this bottleneck, high-speed bit-level memory units are required. Recent advances in Chip-Multiprocessors (CMP) technology and the extensive use of parallelism[14],[15] have resulted in further enhancing the Von Neumann problem, as electronic RAMs have proved incapable to keep up with the required Read/Write memory access speeds [9] and their operational capabilities do not exceed 4.6GHz [16]. Today, the deployment of large twoor even three-level on chip cache memory hierarchies to ease

A. Bazin, P. Monnier, R. Raj and F. Raineri are with Centre National de la Recherche Nationale - Laboratoire de photonique et de nanostructures (LPN), France

F. Raineri is also with Université Paris Diderot, Sorbonne Paris Cité, 75207 Paris Cedex 13, France.

the limited off-chip bandwidth and the high main memory's response latency introduces new challenges as on-chip caches take up almost 40% of the total chip energy consumption [17] and more than 40% of chip real-estate [18] without contributing to main job of the CPU chip (i.e. processing).

Facing these problems, all-optical memory technology could be the drastic answer, not only due to its inherent advantage of offering faster response times and thus covering the need for significantly improved memory speeds and access times, but also because it would allow for better interconnection links directly in the optical domain. In this way, the critical latency sensitive memory-processor path could reap the benefits of optical interconnection including Wavelength Division Multiplexing (WDM) increased bandwidth and minimal transmission time. Such an alternative approach was recently proposed [19], suggesting the exploitation of both optical interconnect technology together with all-optical bit-level memory configurations towards an off-chip, high-speed optical cache memory architecture. This work [19] revealed that a performance speed-up of up to 40% can be achieved reducing at the same time the total cache capacity requirements by 84% for a certain benchmarking suite, indicating in this way that the use of all-optical memories can be the alternative way to relax the Von Neumann bottleneck.

In the way towards practical all-optical memories, a rich body of research activity has been reported [20]-[24] and several technologies have been pursued to deliver light-based storage, including polarization bistable VCSELs [20], integrated InP ring-lasers on SOI relying on light direction bistability [21], coupled laser-based [22] and switch-based [23],[24] "master-slave" configurations. Within this frame, photonic crystal (PhC) nanocavities have drawn significant attention due to their capabilities of delivering high integration densities together with increased energy efficiency compared to previous integrated optical memory demonstrations[20]-[24]. Optical memory devices based on PhC nanocavities have already been presented utilizing the InGaAsP/InP platform and relying on the bistability of PhC nanocavity lasers [25] with 60ps switching times at 70µW of switching power. Moreover, optical memory devices based on the bistability of InGaAsP/InP PhC switches [25]-[28] have been demonstrated requiring a switching energy of 13fJ/bit while exhibiting ~10µm² footprint [26]. The energy and footprint benefits come, however, at the cost of a slower fall time of 7.4ns rendering these optical memory implementations more suitable for buffering schemes in routing applications rather than for bitlevel high-speed caching in computing environments.

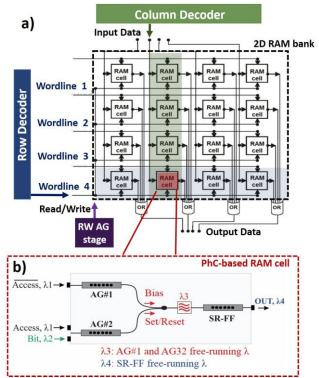

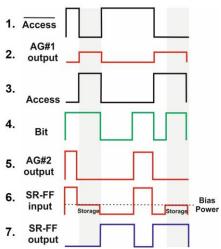

Even more, the realization of radically new all-optical memory architectural schemes in large-scale configurations requires a complete toolbox for the optical memory technology that extends simple latching/ Flip-Flop operation towards full-scale functional RAM memories. To highlight this, Fig. 1a) shows a typical two dimensional (2D) layout of 4×4 RAM bank [29] along with the peripheral circuits (i.e. Row/Column decoders) [30][31] that are usually required in such advanced implementations. As it can be seen, the RAM bank consists of 16 separate single RAM cells that not only implement the storing functionality, but they are also independently controlled by Access Signals to allow access to a specific single row for

**Fig. 1:** a) 4×4 Optical RAM bank layout with peripheral circuits and b) PhC-based RAM cell architecture where two PhC-based nanocavity lasers perform as the AGs and a single PhC-based nanocavity laser acts as the FF memory.

storing/retrieving a 4-bit word. This means that in order to build an independent optical RAM cell that can be accessed to perform Read/Write functionalities, a Flip-Flop (FF) latching mechanism serving as the storage unit has to be combined with two additional Access Gate (AG) elements that control the access of the incoming Bit sequences to the memory cell. On a RAM cell basis, as depicted in Fig.1b), Read operation is performed when the Access signal's logical state is one and no incoming Bit sequences are injected into the RAM cell. This allows only Bias pulses to enter the RAM cell to preserve its memory content. On the other hand, Write operation is performed when Access signal is logical zero, allowing Set/Reset pulses to change the memory state.

Although numerous optical FF implementations have been already reported, only a few demonstrations have addressed true all-optical static RAM cells implementations with Read/Write control by external Access signals [29],[32]. All these demonstrations managed to exhibit isolated performance or integration benefits but did not succeed so far to comply with all the demanding requirements (i.e. footprint, energy efficiency and high-speed operation at real data-traffic environments), simultaneously.

On the other hand, an InP-on-Si nanocavity configuration has been presented to perform high-speed Wavelength Conversion (WC) operation [36] while very recently we employed an InP-on-Silicon photonic crystal nanocavity laser to demonstrate Flip-Flop and WC principle of operation at 5Gb/s [37], [38]. This effort has revealed that the InP-on-Si PhC nanocavity laser technology holds great potential for providing a generic component capable to implement a functional RAM cell that combines all desired characteristics in terms of speed, footprint and power consumption. Such a PhC-based RAM cell concept

is illustrated in Fig.1b) where two PhC components serve as the AG elements and one PhC-based nanocavity laser is employed as the SR-FF. As it will be explained in Section III, the PhC-based SR-FF requires a three-level input signal ( $\lambda 2$ ) with highest and lowest power level representing the Set, Reset pulses, respectively, while the middle power level acts as the Bias pulses retaining the previous memory content. As can be observed in Fig. 1b) the first PhC-based AG (AG #1) is responsible for allowing/blocking the Set/Reset signals whereas the second AG (AG#2) creates the necessary Bias signal to the SR-FF memory unit.

In this paper, we report on a hybrid III-V on Si PhC-based nanocavity laser device capable to perform both fundamental logic functionalities, such as switching and latching, providing a generic building block towards implementing fully functional optical RAM cells with minimal footprint, enhanced energy efficiency and high-speed bit-level operation for real datatraffic computing environments. On that account, we introduce a novel RAM cell achitecture allowing memory control with Access signals, based explicitly on the PhC nanocavity laser device, and we evaluate separately combinational (AG) and sequential (SR-FF) operations of the proposed PhC nanocavity laser, required for the RAM cell configuration. The AG capability of the PhC nanocavity laser SR-FF was confirmed by successful Wavelength Conversion (WC) operation at 10Gb/s with 2<sup>31</sup>-1 PRBS signals, revealing an Extinction Ratio (ER) value of 10dB, at switching energies as low as of 4.8fJ/bit with a power penalty of 1dB. The SR-FF operation of the PhC nanocavity laser was verified at 5Gb/s and 10Gb/s with data patterns simulating true data-traffic. Experimental results at 5Gb/s, reveal an ER value of 12.7dB with switching energies as low as 6.4fJ/bit and error-free operation with a negative power penalty of -0.2dB while verification of PhC-based memory operation at 10Gb/s reveal an ER of 6dB halving the switching energy requirements. Moreover, as the device relies on the heterogeneous integration of a InP-based PhC nanocavity with SOI passive waveguides circuitry utilizing evanescent wave coupling between the two optical levels, it enables efficient interfacing of active nanophotonic elements to be densely integrated in a circuit with direct compatibility to CMOS electronics. The footprint of the device was a record value of 6.2µm<sup>2</sup>, achieving significant reduction compared to previous PhC nanocavity-based optical memory implementations. Memory state switching-ON and switching-OFF occur at time constants lower than 50ps, indicating bit-level operation capabilities up to 20Gb/s.

The rest of this paper is organized as follows: the fabrication of the hybrid PhC nanocavity laser is presented in section II, the complete PhC nanocavity laser-based optical RAM cell concept is introduced in section III, the experimental setup is described in section IV and the respective results of the WC and SR-FF operation are examined in section V. Then, a conclusion is reached in section VI.

### II. FABRICATION OF THE HYBRID PHC-BASED NANOCAVITY LASER

The structures under investigation are InP-based 1D PhC nanobeam cavities which are heterogeneously integrated onto 500nm×220nm (width×thickness) SOI wire waveguides. The

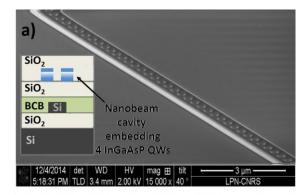

Fig. 2: SEM images of a) the photonic crystal nanocavity laser (inset with schematic view of the layers stack,) and b) fabricated silicon chip

cavities consist of 650nm×285nm (width×thickness) InP-based wires embedding four InGaAsP strained quantum wells, drilled with a row of equally-sized holes (radius=123nm). The distance between the holes is varied according to [39] in order to obtain a Gaussian field profile for the resonant mode which enables Q factors higher than  $10^4$  ( $10^6$  in simulations) with  $V\sim(\lambda/n)^3$ . The thickness of the BCB layer is 260nm. Besides energy efficiency and ultra-fast dynamics, these cavities are also particularly interesting as they exhibit small footprint [41][42] due to their natural ability to be coupled efficiently with wire waveguides. The cavity is positioned on top of a SOI waveguide whose width was chosen properly to enable a coupling efficiency greater than 90%. The structures are encapsulated in SiO<sub>2</sub> in order to improve heat sinking as well as the robustness of the systems.

The fabrication of these InP-on-SOI hybrid nanocavity lasers starts with the adhesive bonding using DVS-benzocyclobutene (BCB) of a 1cm<sup>2</sup> of the InP-based heterostructure grown by molecular beam epitaxy, onto an SOI die processed with waveguides into a CMOS pilot line (Epixfab). In order to set the distance between the SOI waveguides and the III-V materials to a value enabling an efficient evanescent wave coupling, the InP material is covered with a 400nm thick SiO<sub>2</sub> layer before the bonding. The cavities are then patterned right on top of the SOI wires [40] using electron beam lithography followed by inductively coupled plasma etching. The etched sidewalls of the cavity are then chemically passivated using ammonium sulfide in order to reduce non radiative surface recombination of electron-hole pairs and allow CW operation of the nanocavity lasers [41]. Finally, the sample is fully encapsulated in a 1µm-thick silica layer which decreases the overall thermal resistance of the devices and increases their

robustness [42]. The total length of the device is 9.54µm, while its width is 650nm, resulting in a total footprint of 6.2 µm<sup>2</sup> that is the smallest value among all PhC cavity-based optical memories reported so far. The laser was integrated with silicon photonic wire waveguides and Transverse Electric (TE) grating couplers at both input and output ends to enable fiber-to-fiber data transmission. The evaluated PhC nanocavity laser was part of a chip that incorporated 462 of PhC nanocavities emitting close to 1550nm occupying a total area of 4.2mm×250µm. This corresponds to an integration density of 440 devices/mm<sup>2</sup>. In Fig. 2 a), b) SEM images of the PhC nanocavity laser and the fabricated silicon chip with the PhC nanocavity lasers are shown, respectively while the inset in Fig.2a) depicts the respective schematic stuck of the layers of every single PhC nanocavity laser. Each SOI waveguide has three PhC cavities. The distance between the PhC cavities is 100µm while the distance between SOI waveguides is 25µm. The maximum integration density that can be achieved is related to the distance between the lasers needed to avoid any optical crosstalks. In the transverse direction, putting the cavities farther than 2µm is sufficient to prevent evanescent wave coupling. In the longitudinal direction, this distance must simply be greater than the half length of the laser.

#### III. PhC-based Nanocavity Laser memory concept

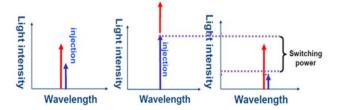

Both basic operations of the PhC-based nanocavity laser device rely on the interchanging of the laser emission state between a free-running mode (unlocked state) and an injection-controlled mode (injection-locked state), achieved through the injection of a wavelength detuned external optical signal into the device. This concept is represented graphically in Fig. 3. Initially, the PhC nanocavity laser emits at its free-running state signal, shown in red color in Fig. 3, as it is powered by an optical pump at 1180 nm. At the presence of a wavelength detuned input injection signal, called control signal, represented in blue color in Fig. 3, the laser starts emitting at the injection wavelength and not at its free-running mode wavelength when the control power increases above a specific threshold. This is called "locking" emission to the injection wavelength and it lasts until the control signal optical power is decreased below a cut-off level, where the laser emission returns to its free-running state. This process of injection locking is exploited in two different operational modes to provide: a) Access Gate (AG) by exploiting Wavelength Conversion (WC) and b) Flip-Flop (FF) operation by exploiting optical bistability, as described below.

#### A. InP-on-SOI PhC-based SR-FF operation

The operation of the device as a memory element relies on exploiting the bistability behavior that is exhibited in the PhC laser emission and is expressed by means of wavelength

Fig. 3: Process of injection locking of the bistable PhC nanocavity laser.

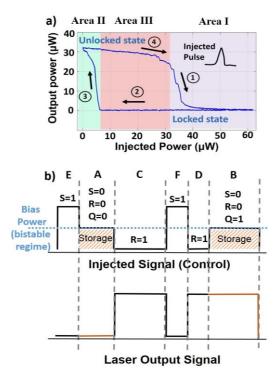

**Fig. 4:** a) Hysteresis loop and b) schematic representation of the SR-FF operation of the bistable PhC-based nanocavity laser device.

emission detuning controlled by the optical power of the injection signal. The bistability phenomenon occurs between the free-running mode (unlocked state) and the injection -controlled mode (injection-locked state), under specific injected optical signal power conditions. When a wavelength detuned input injection signal is inserted to the laser, it starts emitting at the injection wavelength when the control power increases above a specific threshold. However, as the control signal optical power decreases to a certain value at this state, the device enters a hysteresis loop retaining this emission state even when the control signal optical power is decreased to a certain cut-off level. Fig. 4 shows an indicative hysteresis loop formed by the PhC laser device for a given wavelength detuning. As it becomes evident, when the optical power of the injected signal

Fig. 5: Schematic representation of the two AGs and SR-FF operation towards PhC-based RAM cell operation of the bistable nanocavity laser device.

falls below this cut-off level, the laser emission returns to its free-running state. Consequently, the laser emission output has two states - locked and unlocked -, which depend on the ascending or descending direction of the injection signal power and memory operation can be achieved when operating within the bistable range of the device. Consequently, the device operates as a Set-Reset Flip-Flop (SR-FF) taking advantage of the three discrete areas of injection signal optical power levels shown in Fig. 4a): Area I where injection power levels allow for Set FF operation, as the laser output is changed from freerunning (unlocked) to injection-controlled (locked) state, Area II where injection power levels enable Reset FF operation as the laser output returns to the free-running (unlocked) state and Area III where injection power levels cover the bistable range and enable storing operation, as the laser emission retains its previous state. Fig.4b) shows a schematic diagram of the injected signal covering all possible states of the SR-FF. When a Set pulse is inserted into the device (timeslot E and F), the FF enters its locked state so that no optical power exits the FF at wavelength of its free-running emission corresponding to a logical '0' at its output. When a Reset signal is being inserted (timeslot C and D), the device returns to its unlocked state emitting a high-power level and as such a logical '1' is obtained at its output. Whenever the incoming signal has a power level equal to the Bias threshold (timeslot A and B), the FF retains its previous state, operating in its storage regime.

#### B. InP-on-SOI PhC-based AG operation

As described in Section I of this manuscript, a complete optical RAM cell requires AG functionality before the SR-FF storing operation to control the communication between the memory unit and the outer world, in order to guarantee true random memory access. In this respect, access to the FF memory element is controlled via the injection of external optical Access signals. According to Fig.1b) conceptual schematic, two AG are needed in order to interpret the Bit (data to be stored) signal and Access/Access (permission to be stored) signal RAM-cell inputs to the Set/Reset and the Bias signals respectively, required by the PhC-based SR-FF to operate.

In our case, the desired AG operations are performed through the employment of the wavelength conversion capabilities of the PhC nanocavity lasers. To make this more clear, Fig.5 shows a schematic diagram of the injected signal into the two Access Gates and the respective combined output that feeds the three-state SR FF to obtain complete optical RAM cell operation. The 1<sup>st</sup> and the 2<sup>nd</sup> row of Fig.5 correspond to the Inverted Access signal and the output of the first AG (AG#1), corresponding to a directly wavelength converted output signal. The inverted Access Bit pulse will force the laser to emit at the injection wavelength and not at its free-running mode wavelength, provided that its power is beyond a specific threshold. By monitoring the free-running wavelength, a logical "0" pulse will form. However, when the inverted Access Bit becomes "0", the laser emission returns to its free-running mode wavelength, forming in this way the "1" level pulse of the Bias signal.

The role of AG#2 is to produce the Set/Reset signal of the FF that encodes a NAND operation between the Bit and the Access signal. The Access Bit of logical "1" value will block communication between the memory cell and the outer world. When the Access Bit becomes "0", the Set/Reset signal is formed through the injection locking process induced by the logical value of the Bit signal. In this case, the PhC nanocavity laser is injected two optical control signals, the Bit and the Access signals. The 3rd, 4th and 5th rows of Fig.5 depict the Access signal, the Bit signal and the output of the second AG (AG#2). At the presence of either the injected Bit signal pulse, the Access signal pulse or both signals pulses, the nanocavity laser starts emitting at the injection wavelength and not at its free-running mode wavelength. In this case, the 6th row represents the combined output of both AGs that result in a three-level signal entering the FF. Finally, the 7<sup>th</sup> row depicts the final FF/RAM cell output.

As it is evident, both cases of AG operation proposed in the PhC-based optical RAM cell are based on the wavelength conversion operation capabilities of the nanocavity laser that rely on the laser injection locking properties of the device. As the injected external optical signal switches the laser output to the injection wavelength, the injection signal is inversely imprinted to the free-running wavelength, achieving in this way the required wavelength conversion. On that account, wavelength conversion operation of the PhC nanocavity laser is evaluated for monitoring single AG operation.

#### IV. EXPERIMENTAL SETUP

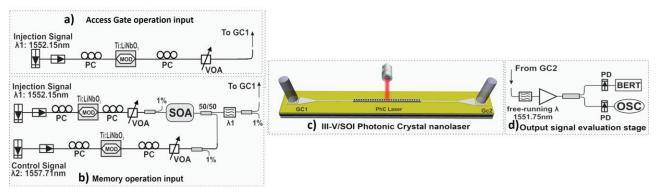

The proposed PhC nanocavity laser was experimentally evaluated as a Wavelength Conversion Access Gating element and also as a SR-FF to ensure its applicability in complete

Fig. 6: Experimental setup and signal generation for the: a) Wavelength Conversion-based AG operation b) Bit-level optical Set-Reset Flip Flop memory evaluation c) III-V/SOI PhC nanocavity with I/O grating couplers and d) Signal evaluation stage.

optical RAM-based systems. The experimental evaluation was performed utilizing signals with true repetition rates of up to 10Gb/s and employing PRBS-like data patterns, so as to demonstrate the device capabilities under real-type data-traffic environments. The following subsections describe the experimental setup employed for the verification of the PhC-based WC Access Gating and FF operation.

#### A. Wavelength Conversion (WC) operation at 10Gb/s

To evaluate the wavelength conversion performance of the PhC laser, the experimental setup shown in Fig.6a) was employed. The device was powered with an optical pump signal at 1180nm, which was injected vertically to the nanocavity laser using a 10× microscope objective, so as to adjust aperture and enhance the absorption of the pump signal. The pump power was set at 103.5µW, corresponding to 4.5 times the laser threshold. This value refers to the estimated absorbed pump power in the quantum wells. A laser at  $\lambda 1=1552.15$  nm was modulated with a 231-1 PRBS data pattern at 10Gb/s Non-Return-to-Zero (NRZ) line-rate in a Ti:LiNbO3 Mach-Zehnder modulator for the generation of the injection optical signal. The data signal was injected into the SOI motherboard through the input Grating Coupler (GC1) while a polarization controller was employed to compensate for the polarization dependence of the grating coupler, together with a VOA (Variable Optical Attenuator) to control the injected signal power levels. After the WC operation in the PhC nanocavity laser (Fig.6c), the product signal of the PhC laser was received at the output Grating Coupler (GC2). Lensed fibers with a spot size diameter of 5µm and anti-reflection coatings were used for injecting and collecting light at both grating couplers in order to avoid backreflections at cleaved fibers' facets. The coupling loss between the lensed fibers and each of the grating couplers was 7dB. As can be seen in Fig.6 d) the output signal was then filtered in a bandpass filter with a 3-dB bandwidth of 0.02nm, which was centered at the laser's free-running mode wavelength, prior to being amplified through an Erbium Doped Fiber Amplifier (EDFA) and recorded at a sampling oscilloscope. Finally, an Error Detector was used for performing Bit Error Rate (BER) measurements.

## B. Set Reset Flip-Flop (SR-FF) operation at 5Gb/s and 10Gb/s

To evaluate the performance of the PhC nanocavity laser as a SR-FF, different injection signal line rates were selected, namely 5 and 10 Gb/s. Again, the device was powered with 103.5µW of an optical pump signal at 1180 nm. For the generation of optical input signal that simulates the encoded Set and Reset signals of the SR-FF, an SOA was employed as a gating element to form the three-level signal containing the Set and Reset pulses as well as the Bias state. For this PhC control signal preparation, two individual lasers emitting light at  $\lambda 1=1552.15$  nm (Injection signal) and  $\lambda 2=1557.71$  nm (Control signal of the SOA), respectively, were modulated by a NRZ custom-made pattern in a Ti:LiNbO<sub>3</sub> Mach-Zehnder modulator, as can be observed in Fig.6 b). The line rate of the NRZ custom pattern was 5Gb/s and consequently 10Gb/s. This custom pattern was programmed appropriately, so as to evaluate its performance in fast memory state switching employing a

PRBS-resembling stream and also induce long periods of '1' or '0' to demonstrate the device's capability for long memory state holding. Again, the use of VOAs and PCs ensured proper signal input powers and compensation for the SOA's polarization gain dependence. The two signals were then injected into the SOA, with the Control signal at  $\lambda 2$  being the stronger one and inducing a Cross Gain Modulation (XGM) process in the SOA and reducing its gain. As a result, the amplitude of any Injection signal pulse that coincides in the SOA with a Control signal pulse was reduced. The pulses with reduced amplitude serve as the Bias signal that maintains the memory state of the device. The ratio between the amplitude of the unaffected Injection signal pulses and the suppressed Bias pulses was set to follow the hysteresis loop of the PhC nanocavity laser device. This amplitude ratio was properly adjusted through the optical power of both input signals of the SOA. An optical bandpass filter with a 3-dB bandwidth of 1nm was used at the output of the SOA to select only the injection Signal at  $\lambda 1$ . The PhC injection signal – now consisting of three levels, corresponding to Set, Reset and Bias- was then launched into the SOI motherboard through the input grating coupler (GC1) and into the bistable photonic crystal nanocavity laser. Again, a PC was employed to compensate for the polarization dependence of the grating coupler, while a VOA sufficiently attenuated the signal. The output signal of the bistable photonic crystal was then received at the output grating coupler (GC2). The rest of the SR-FF memory evaluation was the same with the WC case as presented in Fig.6 c) and d).

#### V. EXPERIMENTAL RESULTS

#### A. WC operation at 10Gb/s

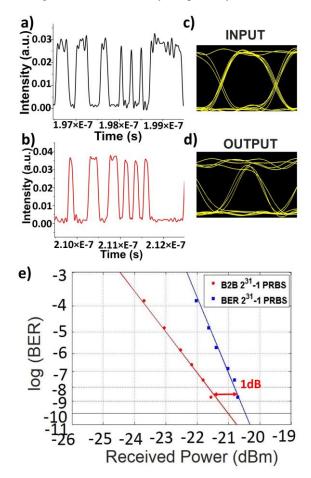

The experimental results of the evaluation of the PhC nanocavity laser device as a wavelength conversion access gating element are depicted in Fig.7. The pulse trace of the  $\lambda 1$ input signal of the PhC nanocavity laser (injection signal) at 10Gb/s is shown in Fig.7 a) while the pulse trace of the wavelength-converted signal at the  $\lambda 2$  free-running laser wavelength is illustrated in Fig.7 b), confirming the complementarity between the two signals and thus the successful operation of the PhC laser as an access gating element. The successful wavelength conversion operation of the proposed device can be also confirmed by the eye diagrams depicted in Fig.7 c) and d) for the input and output signals, respectively. An can be observed, a clear open eye diagram is obtained at the output with an Extinction Ratio (ER) of 12dB and an Amplitude Modulation (AM) of 1.5dB. The switching energy was calculated 4.8fJ/bit at 10Gb/s for average optical input power of 24µW. By taking into account the optical pump the power consumption for the AG is found to be 15.1fJ/bit at 10Gb/s. Fig.7 e) shows the BER curves versus the received power for the WC operation at 10Gb/s. Error-free operation was achieved for the  $\lambda 2$  wavelength-converted signal with a power penalty of 1dB.

#### B. SR-FF operation at 5Gb/s - 10Gb/s

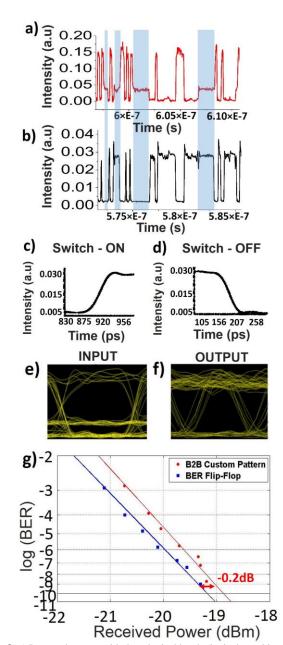

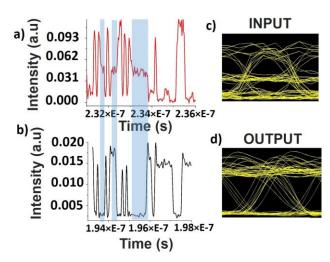

Successful experimental demonstration of the PhC-based laser operating as a SR-FF was achieved for several data patterns. Fig.8 shows an experimentally obtained data trace at the a)

input and b) output of the SR-FF confirming its successful operation at 5Gb/s at 1552.15nm. Fig. 8a) shows the input signal as obtained at the output of the SOA with three logical levels, the logical one, Bias and the logical zero imprinted as it is imprinted in the free-running laser wavelength at 1551.75nm while Fig. 8b) shows the final SR-FF memory content. When a bit of logical '1' Set signal is injected into the PhC laser, the SR-FF enters its locked state, resulting in a logical '0' state the output of the SR-FF. When a bit of logical "0" Reset pulse is inserted into the laser, it unblocks the free-running transmission state and the laser is switched back to its initial state of logical '1' value. In case of a Bias pulse, the SR-FF memory content remains unaltered retaining its last value. This situation is evident in the Bias pulses that are highlighted with blue color in Fig. 8a) and b), depicting four different cases of memory operation provided by the PhC nanocavity laser. The 1st highlighted area depicts two Bias pulses following a Set pulse resulting in a logical zero state for three consecutive bit slots at the SR-FF output, as shown in Fig. 8b). The 2<sup>nd</sup> highlighted area presents three Bias pulses after a single Reset pulse that result in logical one state for four bits at the output of the SR-FF as shown in Fig. 8b). The 3<sup>rd</sup> and the 4<sup>th</sup> highlighted areas show the retention time of the SR-FF memory after one Set and seven Reset pulses. Successful memory operation is observed in both cases in Fig. 8b) where memory output stays constant to a

**Fig. 7:** a) Input pulse trace inserted into the PhC nanocavity laser for WC operation, b) Output pulse trace obtained at the exit of the nanocavity laser, c) input d) output eye diagrams and e) BER curves for the wavelength conversion at 10Gb/s.

logical zero state for a duration of 8 bits, approximately 1.6ns, and to a logical one state for 15 bits corresponding to a memory time duration of 3ns, respectively. Fig.8 c) and d) illustrate the rise and fall times of the FF output pulses with 10%-to-90% values being approximately 50ps, indicating potential speed capabilities of up to 20Gb/s. Fig.8 e) and f) show the respective eye diagrams for the Set/Reset signal and the SR-FF output providing a more detailed look into the performance of the demonstrated device. Clear open eye diagram is obtained for the SR-FF operation at 5Gb/s with an ER of 12.7dB and an AM equal to 1dB. The input eye diagram exhibits three logical levels corresponding to the three logical states, the logical one, the Bias and the logical zero level as shown in the right inset and corresponds to an ER of 11.7dB and an AM of 0.8dB. Fig.8

**Fig. 8:** a) Input pulse trace with three logical levels (logical one, bias, logical zero) inserted into the PhC-based SR-FF, b) Output pulse trace obtained at the exit of the FF, c) Rise and d) Fall time of the FF output pulses e) input f) output eye diagrams and g) BER curves for PhC-based SR-FF at 5Gb/s.

**Fig. 9:** a) Input pulse trace with three logical levels (logical one, bias, logical zero) inserted into the PhC-based SR-FF, b) Output pulse trace at the exit of the SR-FF, c) input d) output eye diagrams for PhC-based SR-FF at 10Gb/s.

g) shows the BER curves obtained for the PhC-based SR-FF operation at 5GHz. Back-to-Back (B2B) measurement was obtained by using the same custom-made 127-bit pattern, employed to demonstrate SR-FF operation, transmitted through the system without entering the PhC-based laser, with no Bias level. Error free SR-FF operation at 10<sup>-9</sup> BER value was achieved for the device at 5Gb/s, revealing a negative power penalty of -0.2dB. The regenerative properties of the demonstrated laser device are mainly due to the improvement of noise in the "0" level, induced by the SOA used to construct the Set/Reset signal. The average optical Bias power was 8µW, the input optical power was measured to be 20µW and the average output power of the laser was 19.9µW taking into account the grating coupler losses in both cases. In the absence of any input signal, the laser emission was 34.6µW. PhC-based SR-FF memory operation was achieved with a switching energy of 6.4fJ/bit at 5GHz at the pump power of 103.5µW, for a given memory output ER of 12.7dB.

Then, the memory operation of the PhC nanocavity laser device was experimentally evaluated at 10Gb/s. Fig.9 shows an experimentally obtained data trace at the a) input and b) output of the SR-FF proving its successful operation at 10Gb/s. Fig.9 a) shows the input signal as obtained at the output of the SOA with three logical levels, the logical one, Bias and the logical zero imprinted at 1552.15nm while Fig. 9b) illustrates the final SR-FF memory content as it is imprinted in the free-running laser wavelength at 1551.75nm. The memory state holding of the device can be witnessed at the areas highlighted with blue color in Fig. 9a) and 9b). The first highlighted area depicts one Bias pulse following a Set pulse resulting in a logical zero memory state for two consecutive bit slots at the FF output, as shown in Fig.9 b). The second highlighted area presents two Bias pulses after a single Reset pulse resulting in logical one memory state retained for three bits at the FF output while the third highlighted area shows eight Bias pulses after one Set indicating that memory output stays constant to a logical zero state for a duration of 8 bits, corresponding to approximately 800ps. Fig. 9c) and d) show the eye diagrams for the input signal and the SR-FF output, respectively. The input signal exhibits an ER value as low as 7dB and an AM of 1.5dB,

whereas the SR-FF output signal exhibits an ER of 6dB and an AM of 0.8dB. The reduced performance of the SR-FF in terms of ER stems from the degraded SOA performance at 10Gb/s. In addition, employing the SOA to produce the required threelevel input signal at 10Gb/s leads to the appearance of severe pattern effects [43] in the three-level SR-FF input signal that are imprinted -among other- as jitter variation at the output signal of the SR-FF. As a result the input signal injected to the PhC nanocavity laser at 10Gb/s is of poorer quality compared to the input signals at 5Gb/s, hindering in this way the error-free performance of the SR-FF. To this end, the successful SR-FF memory operation at 10Gb/s was evaluated only with eyediagrams and as it retains the same operational conditions with 5Gb/s operation, it now yields a reduced switching energy of 3.2fJ/bit. By taking into account the optical pump the power consumption for the SR-FF is found to be 27fJ/bit and 13.5fJ/bit for 5Gb/s and 10Gb/s respectively. Moreover, as the device exhibits fast rise and fall times of approximately 50ps, the employment of faster SOAs or other alternative switching elements for the generation of the three-level SR-FF input signal can potentially lead to successful SR-FF operation in speeds of up to 20Gb/s. Recent advances [44] on electricallydriven PhC nanocavity lasers have demonstrated up to 11% wall-plug efficiency improving the power conversion efficiency of the demonstrated optically pumped PhC laser where only a fraction of the pump is absorbed resulting in pumping. The electrically pumped PhC laser device [44] requires a power consumption of 500µm, that corresponds to 25fJ/bit considering an operational speed of 20Gb/s and is also expected to improved heat sinking and stability of the device, occupying an area of less than 100μm<sup>2</sup>.

#### VI. CONCLUSION

We have presented an InP-on-Silicon PhC-based nanocavity laser that can serve as the fundamental building block for energy efficient, ultra-compact and high-speed RAM setups by exhibiting two individual elementary RAM functions: a) Access Gate and b) SR-FF operation. The AG operation was confirmed by successful WC at 10Gb/s requiring only 4.8fJ/bit switching energy. Moreover, successful SR-FF memory operation with the same device was achieved by exploiting the bistability behavior of the nanocavity laser both at 5Gb/s and 10Gb/s with record switching energies of 6.4fJ /bit and 3.2fJ/bit, respectively. By including the optical pump the power consumption for the SR-FF is found to be 27fJ/bit and 13.5fJ/bit for 5Gb/s and 10Gb/s respectively while the power consumption for the AG module is 15.1fJ/bit. The presented PhC laser device exhibits the smallest size among all integrated optical memory implementations with a total footprint of 6.2µm<sup>2</sup>, raising expectations for densely integrated optical memories. The device also offers ultra-fast dynamics with switching times of <50ps for both ON and OFF state, indicating bit-level memory capabilities in the order of 20 Gb/s.

#### ACKNOWLEDGMENT

This work was partially supported by the European FP7 ICT-RAMPLAS (ICT- FET no. 270773) project, the FP7-ICT-IP project PhoxTrot (Contract No. 318240), and FP7-PEOPLE-

2013-IAPP-COMANDER (CN 612257). Dimitrios Fitsios was supported by the IKY Foundation through the SIEMENS Fellowship of Excellence Program.

#### REFERENCES

- [1] M. M. A. Taubenblatt, "Optical Interconnects for High-Performance Computing" *IEEE J. of Light. Techn.*, Vol. 30, No. 4, Feb. 2012.

- [2] C. Sun, M. T. Wade, Y. Lee, J.S. Orcutt, L. Alloatti, M. S. Georgas, A. S. Waterman, J.M. Shainline, R.R. Avizienis, S. Lin, B. R. Moss, R. Kumar, F. Pavanello, A.H. Atabaki, H. M. Cook, A.J. Ou, J.C. Leu, Y.H. Chen, K. Asanović, R. J. Ram, M. A. Popović and V. M. Stojanović "Single-chip microprocessor that communicates directly using light", *Nat. Photon.*, Vol. 528, pp. 534-538, Dec. 2015

- [3] V. Stojanović, K.T. Settaluri, S. Lin, S. Moazeni, E. Timurdogan, C. Sun, M. Moresco, Z. Su, Y-H. Chen, G. Leake, D. LaTulipe, C. McDonough, J. Hebding, D. Coolbaugh, M. Watts, "High-density 3D Electronic-Photonic Integration", Fourth Berkeley Symposium on Energy Efficient Electronic Systems (E3S), 2015, 1-2 Oct. 2015.

- [4] Jason S. Orcutt, Anatol Khilo, Charles W. Holzwarth, Milos A. Popović, Hanqing Li, Jie Sun, Thomas Bonifield, Randy Hollingsworth, Franz X. Kärtner, Henry I. Smith, Vladimir Stojanović, and Rajeev J. Ram, "Nanophotonic integration in state-of-the-art CMOS foundries", Opt. Expr., Vol. 19, No. 3, pp. 2335-2346, 2011.

- [5] S. Rumley, D. Nikolova, R. Hendry, Q. Li, D. M. Calhoun, K. Bergman, "Silicon Photonics for Exascale Systems [Invited Tutorial]," *IEEE Journal of Light. Techn.*, Vol. 33, No. 4, Feb 2015.

- [6] A. Biberman, K. Preston, G. Hendry, N. Sherwood-Droz, J. Chan, J. S. Levy, M. Lipson, K. Bergman, "Photonic Network-on-Chip Architectures Using Multilayer Deposited Silicon Materials for High-Performance Chip Multiprocessors," ACM Journal on Emerging Technologies in Computing Systems, Vol. 7, No. 2, pp. 1-25, Jun. 2011.

- [7] W. Bogaerts, P. De Heyn, T. Van Vaerenbergh, K. De Vos, S. Selvaraja, T. Claes, P. Dumon, P. Bienstman, D. Van Thourhout, and R. Baets, "Silicon microring resonators", *Laser & Photonics Reviews*, Vol. 6, No. 1, pp. 47-73, Jan. 2012.

- [8] M. J. R. Heck, J. F. Bauters, M. Davenport, J. K. Doylend, S. Jain, G. Kurczveil, S. Srinivasan, Y. Tang, and J. E. Bowers, "Heterogeneous Silicon Photonic Integrated Circuit Technology", IEEE Journal of Selected Topics In Quantum Electronics, Vol. 19, No. 4, July/August 2013.

- [9] S. McKee, "Reflections on the Memory Wall," in Proceedings of the 1st Conf. on Comp. frontiers, Ischia, Italy, Apr. 2004.

- [10] A. Mendoza, "Intel Rack Scale Architecture Overview for EMC World", April 2015.

- [11] D. Brunina, D. Liu, and K. Bergman, "An Energy-Efficient Optically Connected Memory Module for Hybrid Packet- and Circuit-Switched Optical Networks", IEEE J. on Sel. Topics of Quantum Electron., Vol. 19, No. 2, 3700407, Mar./Apr. 2013.

- [12] D. Brunina, A. S. Garg, H. Wang, C. P. Lai, K. Bergman, "Experimental Demonstration of Optically-Connected SDRAM," in Proc. Photonics in Switching 2010, PMC5, July 2010.

- [13] Y. Yin, R. Proietti, X. Ye, S. J. B. Yoo, V. Akella, "Experimental Demonstration of optical Processor-Memory Interconnection", in Proc. AIAI2010, 213-216, Beijing, China, Oct. 2010.

- [14] J.Feehrer et al., "The Oracle Sparc T5 16-Core Processor Scales to Eight Sockets," *IEEE Micro*, Vol. 33, no. 2, pp. 48-57, Apr. 2013.

- [15] D.F. Wendel et al., "POWER7TM, a Highly Parallel, Scalable Multi-Core High End Server Processor," *IEEE Journal of Solid-State Circuits*, Vol. 46, no. 1, pp. 145-161, Nov. 2010

- [16] E. Karl, Y. Wang, Y. G. Ng, Z. Guo, F. Hamzaoglu, U. Bhattacharya, K. Zhang, K. Mistry and M. Bohr "A 4.6GHz 162Mb SRAM design in 22nm tri-gate CMOS technology with integrated active VMIN-enhancing assist circuitry" IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 230 232, San Francisco, CA, 19-23 Feb. 2012

- [17] K. Ali et.al., "Modified Hotspot Cache Architecture: A Low Energy Fast Cache for Embedded Processors," In *Proceedings of International Conference on Embedded Computer Systems: Architectures, Modeling and Simulation*, IC-SAMOS, pp. 35-42, 17-20 July 2006.

- [18] S. Borkar and A. A. Chien, "The future of microprocessors," Communications of the ACM, vol. 54, no. 5, pp. 67-77, May 2011.

- [19] P. Maniotis, D. Fitsios, G.T. Kanellos, N. Pleros, "Optical Buffering for Chip Multiprocessors: A 16GHz Optical Cache Memory Architecture," *IEEE J. of Lightwave Techn.*, Vol. 31, No.24, pp.4175-4191, 2013.

- [20] J. Sakaguchi, T. Katayama and H. Kawaguchi, "High Switching-Speed Operation of Optical Memory Based on Polarization Bistable Vertical-Cavity Surface-Emitting Laser," *J. of Quantum Electron.*, Vol. 46, No. 11, pp.1526-1534, 2010.

- [21] L. Liu, R. Kumar, K. Huybrechts, T. Spuesens, G. Roelkens, E. J. Geluk, T. de Vries, P. Regreny, D. Van Thourhout, R. Baets and G. Morthier "An ultra-small, low-power, all-optical flip-flop memory on a silicon chip," *Nat. Photon.*, Vol. 4, pp. 182 – 187, 2010.

- [22] M. T. Hill, H. J. S. Dorren, T. de Vries1, X. J. M. Leijtens, J. Hendrik den Besten, B. Smalbrugge, Y. S. Oei, H. Binsma, G.-Djan Khoe and M. K. Smit, "A fast low-power optical memory based on coupled micro-ring lasers," *Nature*, Vol. 432, pp. 206-209, 2004.

- [23] J. Wang, G. Meloni, G. Berrettini, L. Poti and A. Bogoni, "All-Optical Clocked Flip-Flops and Binary Counting Operation Using SOA-Based SR Latch and Logic Gates," J. Sel. Top. Quantum Electron., Vol. 16, No. 5, pp. 1486-1494, 2010.

- [24] C. Vagionas, et al., "Optical RAM and Flip-Flops Using Bit-Input Wavelength Diversity and SOA-XGM Switches," IEEE J. Lightw. Technol., Vol. 30, No. 18, pp. 3003-3009, Sept. 2012

- [25] C.H. Chen, S. Matsuo, K. Nozaki, A. Shinya, T. Sato, Y. Kawaguchi, H. Sumikura, and M. Notomi, "All-optical memory based on injection-locking bistability in photonic crystal lasers," *Opt. Expr.*, Vol. 19, No.4, pp. 3387-3395, 2011.

- [26] K. Nozaki, A. Shinya, S. Matsuo, Y. Suzaki, T. Segawa, T. Sato, Y. Kawaguchi, R. Takahashi and M. Notomi, "Ultralow-power all-optical RAM based on nanocavities," *Nat. Photonics*, Vol. 6, pp. 248–252, 2012.

- [27] E. Kuramochi, K. Nozaki, A. Shinya, K. Takeda, T. Sato, S. Matsuo, H. Taniyama, H. Sumikura and M. Notomi "Large-scale integration of wavelength-addressable all-optical memories on a photonic crystal chip", *Nature Photonics*, Vol. 8, pp. 474-481, 2014.

- [28] A. Shinya, S. Mitsugi, T. Tanabe, M. Notomi, I. Yokohama, H. Takara, and S. Kawanishi "All-optical flip-flop circuit composed of coupled two-port resonant tunneling filter in two-dimensional photonic crystal slab", *Opt. Expr.*, Vol. 14, No. 3, pp. 1230–1235, 2006.

- [29] N. Pleros, D. Apostolopoulos, D. Petrantonakis, C. Stamatiadis and H. Avramopoulos, "Optical Static RAM Cell", *IEEE Photon. Tech. Lett*, Vol. 21, No. 2, pp.73-75, 2009.

- [30] T. Alexoudi, S. Papaioannou, G.T. Kanellos, A. Miliou and N. Pleros, "Optical Cache memory Peripheral Circuitry: Row and Column Address Selectors for Optical Static RAM Banks", IEEE Journal of Lightwave Technology, special issue on Optical Interconnect, Vol. 31, No. 24, Dec. 2013.

- [31] T. Alexoudi, S. Papaioannou, G.T. Kanellos, A. Miliou and N. Pleros, "Optical RAM Row Access with WDM-Enabled All Passive Row/Column Decoders", IEEE Photonics Technology Letters, Vol. 26, No. 7, April 2014.

- [32] D. Fitsios, C. Vagionas, G.T. Kanellos, A. Miliou and N. Pleros, "Optical RAM cell with Dual-Wavelength Bit Input and three SOA XGM switches," Optical Fiber Communications Conf. (OFC) 2012, JW2A, Los Angeles, CA, USA, March 2012

- [33] Y. Naito, S. Shimizu, T. Kato, K. Kobayashi, and H. Uenohara, "Investigation of all-optical latching operation of a monolithically integrated SOA-MZI with a feedback loop" Opt. Express, Vol. 20, No. 26, pp. 339-349, Dec. 2012

- [34] A. Trita, G. Mezõsi, M. Sorel and G. Giuliani, "All-Optical Toggle Flip-Flop Based on Monolithic Semiconductor Ring Laser" Photon. Techn. Lett, Vol.26, No. 1, pp.1041-1135, Noev. 2013.

- [35] S. Pitris, C. Vagionas, G. Kanellos, R. Kisasic, T. Tekin, R. Broeke, and N. Pleros, ""Optical Fiber Communications Conf. (OFC) 2016, Tu2K.7, Anaheim, CA, USA, 20–22 March 2016

- [36] K. Lengle, T. N. Nguyen, M. Gay, L. Bramerie, J. C. Simon, A. Bazin, F. Raineri, and R. Raj, "Modulation contrast optimization for wavelength conversion of a 20 Gbit/s data signal in hybrid InP/SOI photonic crystal nanocavity", Opt. Lett., Vol. 39, No.8, 2298, 2014.

- [37] D. Fitsios, T. Alexoudi, A. Bazin, P. Monnier, R. Raj, A. Miliou, G.T. Kanellos, N. Pleros, and F. Raineri, "An ultra-compact III–V-on-Si Photonic Crystal memory for Flip-Flop operation at 5 Gb/s", Opt. Expr., Vol. 4, No. 4, pp. 4271-4277, Febr. 2016

- [38] T. Alexoudi, D. Fitsios, A. Bazin, P. Monnier, R. Raj, A. Miliou, G.T. Kanellos, N. Pleros and F. Raineri, "III-V/SOI Photonic Crystal nanolaser for high-speed wavelength conversion and memory operation", *Optical Fiber Comm. Conf. (OFC 2016)*, Tu2K.1, March 2016, Los Angeles, CA, USA

- [39] A. Bazin, R. Raj and F. Raineri, "Design of silica encapsulated high Q photonic crystal nanobeam cavity," J. Lightw. Techn., Vol. 32, No.5, pp. 952-58, 2014.

- [40] T. J. Karle, Y. Halioua, F. Raineri, P. Monnier, R. Braive, L. Le Gratiet, G. Beaudoin, I. Sagnes, G. Roelkens, F. van Laere, D. Van Thourhout and R. Raj, "Heterogeneous integration and precise alignment of InP-based photonic crystal lasers to complementary metal-oxide semiconductor fabricated silicon on insulator wire waveguides," J. Appl. Phys., Vol. 107, 063103, 2010.

- [41] G. Crosnier, A. Bazin, V. Ardizzone, P. Monnier, R. Raj, F. Raineri F., "Subduing surface recombination for continuous-wave operation of photonic crystal nanolasers integrated on Silicon waveguides," *Opt. Express*, Vol. 23, No.21, pp. 27953-9, 2015.

- [42] A. Bazin, P. Monnier, X. Lafosse, G. Beaudoin, R. Braive, I. Sagnes, R. Raj, and F. Raineri, "Thermal management in hybrid InP/silicon photonic crystal nanobeam laser," *Opt. Express*, Vol. 22, No.9, pp.10570-10578, 2014.

- [43] T. Alexoudi, G.T. Kanellos, S. Dris, D. Kalavrouziotis, P. Bakopoulos, A. Miliou and N. Pleros "Semiconductor Optical Amplifier (SOA)—Based Amplification of Intensity-Modulated Optical Pulses Deterministic Timing Jitter and Pulse Peak Power Equalization Analysis", Some Advanced Functionalities of Optical Amplifiers, Dr. Sisir Garai (Ed.), ISBN: 978-953-51-2237-1, InTech (2015).

- [44] G. Crosnier, D. Sanchez, P. Monnier, S. Bouchoule, G. Beaudoin, I. Sagnes, R. Raj and F. Raineri, "Electrically-driven 1D photonic crystal nanolaser integrated on silicon waveguides" SPIE Photonics West, 9767-34, San Francisco, CA, 13-18 Feb. 2016

**Theonitsa Alexoudi** received her M.Sc. and Ph.D. degrees in 2010 and 2015 respectively, from the Department of Informatics of Aristotle University of Thessaloniki. During her PhD studies, Dr. Alexoudi received the Excellence Grant for PhD students by Research Committee of Aristotle University of Thessaloniki (2014). In December 2015 she was appointed a Marie-Curie Fellowship in Phoenix BV in the Netherlands. Her research work has focused on WDM-enabled optical RAM architectures and WDM-enabled all-passive optical memory peripherals circuits for future high-speed and low-power optical CPU-memory interconnection implementations.

**Dimitrios Fitsios** received his M.Sc. and Ph.D. degrees from the Department of Informatics, Aristotle University of Thessaloniki, Greece in 2011 and 2015, respectively. His research focused in the design and experimental analysis of optical memory structures and devices for high-speed optical data processing as well as novel photonic computing architectures. He has also worked on dilute nitride semiconductor optical amplifier processing as a Visiting Scientist at the Tampere University of Technology, Finland. He was a recipient of the Photonics Society Graduate Student Fellowship in 2014.

**Alexandre Bazin** received the B.Sc., M.Sc degrees in physics, in 2005 and 2008, respectively, and the Ph.D. degree from Paris Diderot University, France in nanophotonics, in 2013. Since 2013, he works as a Postdoctoral Researcher at Tokyo University. His current research interests include nanophotonics and phononics.

**Paul Monnier** received his M.Sc. in optics from Paris-Diderot University of Science. He, then joined CNRS Laboratoire de Photonique et de Nanostructures, Marcoussis, France where he is currently providing technical support in the domains of scientific experiments, instruments interfaces design and programming, and maintenance.

Rama Raj received the B.Sc. and the M.Sc.degrees in physics from Bangalore University, in 1970 and 1972, respectively, and the Ph.D.

degree (1977) from Dehli University (India) in multiphotonic excitations of atoms. From 1977 to 1983, she worked as a junior Researcher in Laboratoire de Physique des Lasers (Villetaneuse, France) on nonlinear optics and atomic physics. From 1984 to 1999, she worked at CNET-France Telecom (Bagneux, France) as a Researcher on nonlinear optics on semiconductors quantum wells. Since 1999, she has been the Directeur de Recherche at CNRS Laboratoire de Photonique et de Nanostructures, Marcoussis, France. Her current research interests include fundamental features and limits for optics in communications and information processing, use of optics in switching, interconnection, computing systems and dense optical interconnection through III–V semiconductor on Silicon hybrid photonics.

Amalia Miliou received her M.Sc., Ph.D. in Electrical and Computer Engineering from the University of Florida, USA. She is currently Assistant Professor at the Department of Informatics, Aristotle University of Thessaloniki, Greece. She has published over 60 articles in scientific journals and international conferences including several invited contributions and contributed 3 chapters in edited books. She has participated in several research projects funded by the European Commission, NATO as well as the Greek government.

Dr. Miliou's research interests include all aspects of optical communications and photonic systems and, among others, research on simulation of optoelectronic circuits and their applications in optical signal processing and secure communications using chaos and chaotic cryptography.

George T. Kanellos received his Ph.D. in 2008 from the ECE-National Technical University of Athens, Greece (Photonics Communications Research Laboratory - PCRL). His research focused on merging photonic integration technology with novel all-optical key-system architectures towards high-performance, energy efficient, compact photonics. In 2010 Dr. Kanellos was appointed a Marie-Curie Fellowship in Bio-photonics. Since 2011, Dr. Kanellos is a Senior Researcher at PhosNet laboratory/ Aristotle University of Thessaloniki- Center for Research and Technology Hellas, as the lead researcher for EU ICT-RAMPLAS research project. Dr. Kanellos has published more than 30 scientific papers and 2 book chapters.

Nikos Pleros (M'01) received the Diploma and Ph.D. degrees in electrical and computer engineering from the National Technical University of Athens (NTUA), Athens, Greece, in 2000 and 2004, respectively. He was a Teaching and Research Associate with the Photonics Communications Research Laboratories, NTUA, from 2005 to 2007. Since 2007, he has been a Lecturer with the Department of Informatics, Aristotle University of Thessaloniki, Thessaloniki, Greece. His current research interests include all aspects of optical communication and photonic systems spanning from integrated photonic devices to optical networking concepts. Dr. Pleros received the IEEE/Lasers and Electro-Optics Society Graduate Student Fellowship in 2003. Dr. Pleros is a member of IEEE and the Optical Society of America.

Fabrice Raineri received the B.Sc. and M.Sc degrees in physics from Nice University, Nice, France, in 1999 and 2001, respectively, and the Ph.D. degree from Paris Sud University Orsay, France, in nonlinear optics and semiconductor nanostructures in 2004. From 2004 to 2005, he was a Postdoctoral Researcher at the Institut Ciencies Fotoniques (ICFO) (Barcelona, Spain) on optical parametric oscillators. Since 2005, he is an Associate Professor at Universite Paris Diderot and at CNRS Laboratoire de Photonique et de Nanostructures, Marcoussis, France. His current research interests include nanophotonics, nonlinear optics, and hybrid III–V on SOI structures.