جامعة الملك عبدالله للعلوم والتقنية King Abdullah University of Science and Technology

## Impact of Gate Dielectric in Carrier Mobility in Low Temperature Chalcogenide Thin Film Transistors for Flexible Electronics

| Item Type      | Article                                                                                                                                                                                      |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Authors        | Salas-Villasenor, A. L.; Mejia, I.; Hovarth, J.; Alshareef, Husam N.;<br>Cha, Dong Kyu; Ramirez-Bon, R.; Gnade, B. E.; Quevedo-Lopez,<br>M. A.                                               |

| Citation       | Impact of Gate Dielectric in Carrier Mobility in Low Temperature<br>Chalcogenide Thin Film Transistors for Flexible Electronics 2010,<br>13 (9):H313 Electrochemical and Solid-State Letters |

| Eprint version | Publisher's Version/PDF                                                                                                                                                                      |

| DOI            | 10.1149/1.3456551                                                                                                                                                                            |

| Publisher      | The Electrochemical Society                                                                                                                                                                  |

| Journal        | Electrochemical and Solid-State Letters                                                                                                                                                      |

| Rights         | Archived with thanks to Electrochemical and Solid-State Letters<br>© 2010 ECS - The Electrochemical Society                                                                                  |

| Download date  | 23/08/2022 06:33:55                                                                                                                                                                          |

| Link to Item   | http://hdl.handle.net/10754/555786                                                                                                                                                           |

## Impact of Gate Dielectric in Carrier Mobility in Low Temperature Chalcogenide Thin Film Transistors for Flexible Electronics

A. L. Salas-Villasenor,<sup>a</sup> I. Mejia,<sup>a</sup> J. Hovarth,<sup>a</sup> H. N. Alshareef,<sup>b</sup> D. K. Cha,<sup>b</sup> R. Ramirez-Bon,<sup>c</sup> B. E. Gnade,<sup>a</sup> and M. A. Quevedo-Lopez<sup>a,z</sup>

<sup>a</sup>Department of Materials Science and Engineering, University of Texas at Dallas, Richardson, Texas 75080, USA

<sup>b</sup>Department of Materials Science and Engineering, King Abdullah University of Science and Technology, Thuwal 23955-6900, Saudi Arabia

<sup>c</sup>Centro de Investigación y Estudios Avanzados del IPN, Unidad Querétaro, Querétaro, Qro. 76001, Mexico

Cadmium sulfide thin film transistors were demonstrated as the n-type device for use in flexible electronics. CdS thin films were deposited by chemical bath deposition (70°C) on either 100 nm HfO<sub>2</sub> or SiO<sub>2</sub> as the gate dielectrics. Common gate transistors with channel lengths of 40–100  $\mu$ m were fabricated with source and drain aluminum top contacts defined using a shadow mask process. No thermal annealing was performed throughout the device process. X-ray diffraction results clearly show the hexagonal crystalline phase of CdS. The electrical performance of HfO<sub>2</sub>/CdS-based thin film transistors shows a field effect mobility and threshold voltage of 25 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and 2 V, respectively. Improvement in carrier mobility is associated with better nucleation and growth of CdS films deposited on HfO<sub>2</sub>.

© 2010 The Electrochemical Society. [DOI: 10.1149/1.3456551] All rights reserved.

Manuscript submitted May 5, 2010; revised manuscript received June 1, 2010. Published June 29, 2010.

Amorphous silicon (a-Si:H) thin film transistors (TFTs) have become one of the most common devices employed in the large area/ flexible electronics industries because they are relatively inexpensive to produce over large areas as compared to single-crystal silicon.<sup>1</sup> While the a-Si:H TFT technology has emerged as the industry leader in applications such as active matrix liquid crystal display backplanes, its relatively low mobility ( $\sim 1 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ) and threshold voltage instability<sup>2,3</sup> limit its use in applications that require significant device performance. Therefore, the development of alternative TFT semiconductor materials is very relevant and is currently mostly driven by improved carrier mobility, device stability, and reduced processing costs.<sup>4</sup>

The synthesis of binary metal chalcogenides of group II–VI semiconductors has been a rapidly growing area of research due to their important nonlinear optical properties,<sup>5-8</sup> luminescent properties,<sup>9-12</sup> quantum size effect, <sup>13-15</sup> and other important physical and chemical properties.<sup>16,17</sup> Among the most studied chalcogenides is cadmium sulfide (CdS). CdS, with a bandgap of 2.4 eV (in bulk),<sup>18</sup> was studied as the semiconductor active layer during the early development of TFTs.<sup>19</sup> Recently, chemically deposited CdS active layers have shown acceptable performance in TFTs with field effect mobility values in the range of 0.5–1.5 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, comparable to those obtained with a TFT based in a-Si:H.<sup>20-24</sup> However, all of these articles included a postdeposition annealing process at temperatures higher than 200°C. The maximum processing temperature for flexible electronics must be lower than 200°C.

CdS thin films can be prepared by a variety of physical and chemical methods. Among those, chemical bath deposition (CBD) processes are attractive because they are simple and inexpensive techniques that can yield homogeneous, adherent, transparent, and highly stoichiometric CdS thin films.<sup>25,26</sup> Typically, in CBD, the CdS films are deposited from the reaction between a cadmium salt and thiourea in an alkaline solution.<sup>27-29</sup>

Here we report the properties of CdS synthesized by an ammonia-free CBD process employing sodium citrate as the complexing agent.<sup>30,31</sup> An atomic layer deposited HfO<sub>2</sub> gate dielectric improves the effective mobility of the resulting TFT devices to values as high as 25 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. Furthermore, the maximum processing temperature is maintained below 100°C, which is compatible with flexible substrates used in flexible electronic applications.<sup>32</sup>

Normally, in devices with SiO<sub>2</sub> as the gate dielectric, the mobility increases linearly with increasing charge per unit area on the semiconductor side of the insulator  $(Q_S)$  and the gate field (E) until it eventually saturates. Because  $Q_{\rm S}$  is a function of the concentration of accumulated carriers in the channel region (N) and the accumulation region is confined very close to the interface of the insulator with the organic semiconductor,<sup>33</sup> an increase in gate voltage ( $V_{\rm G}$ ) results in an increase in E and N. Dimitrakopoulos and Malenfant demonstrated that high mobilities in pentacene TFTs can be achieved at low operating voltages when relatively high dielectric constant gate insulator materials are used. The increased mobility was explained by using a multiple trapping and release model. This model explains that mobility in organic TFTs depends on N (accumulated carriers in the channel) rather than E (electric field). In other words, for the same  $V_{\rm G}$ , N depends on both the dielectric constant and the thickness of the gate insulator, while E depends only on the dielectric thickness. If SiO<sub>2</sub> is replaced with an insulator having similar thickness but a higher dielectric constant (such as HfO<sub>2</sub>, used here), then charge accumulation is facilitated and carrier concentrations similar to the SiO2 case can be attained at a much lower  $V_{\rm G}$  (and E) with improved mobilities.

We used a cadmium chloride/sodium citrate/thiourea system to grow the CdS active layers using the CBD method that we have reported before.<sup>30,31</sup> The CdS was deposited on different gate dielectric materials: p-Si/SiO<sub>2</sub>/CdS and p-Si/HfO<sub>2</sub>/CdS with Al gate, source, and drain contacts. The SiO<sub>2</sub> dielectric (100 nm) was grown at 1100°C using a single-wafer system. The HfO<sub>2</sub> (100 nm) films were deposited using atomic layer deposition (ALD) at 100°C. After the gate dielectric formation, the substrates were immersed in the chemical bath solution prepared by the sequential addition of 0.05 M CdCl<sub>2</sub> (cadmium chloride), 0.5 M Na<sub>3</sub>C<sub>6</sub>H<sub>5</sub>O<sub>7</sub> (sodium citrate), 0.5 M KOH (potassium hydroxide), and 0.5 M CS(NH<sub>2</sub>)<sub>2</sub> (thiourea) in distilled water. The beaker with the solution was then immersed in a thermal bath with the temperature set to 70°C. The substrates were placed vertically in the beaker. Stirring was not used during the deposition. The CdS thickness series to study film nucleation and growth was obtained by sequentially removing the CdS substrates from the CBD solution. Deposition times ranged from 0.5 to 25 min. After deposition, the CdS films were cleaned in an ultrasonic bath with methanol, rinsed with distilled water, and dried with N<sub>2</sub> gas. Next, 100 nm of Al was used as the source and drain metal contacts. The source and drain were defined using a shadow mask process.

The resulting CdS films were studied using many materials characterization techniques. The crystalline structure was analyzed in a

<sup>&</sup>lt;sup>z</sup> E-mail: mquevedo@utdallas.edu

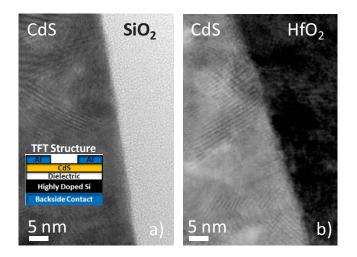

Figure 1. (Color online) TEM for CdS films grown at  $70^{\circ}$ C for 25 min on (a) SiO<sub>2</sub> and (b) HfO<sub>2</sub>. A schematic cross section of the TFT fabricated is also illustrated.

Rigaku Ultima III X-ray diffractometer. Transmission electron microscopy (TEM) was performed in a JEOL 2100 system. X-ray photoelectron spectroscopy (XPS) analyses were performed in an Omicron 5600 system, and the electrical characteristics of the TFTs were determined using current–voltage (I-V) measurements at room temperature in a 4200 Keithley semiconductor parameter analyzer.

The resulting CdS layers were homogeneous and continuous with an average grain size of  $\sim 30$  nm, as calculated by X-ray diffraction (XRD). This morphology suggests that the deposition process is through an ion-by-ion mechanism, as previously reported.

Figure 1 shows the TEM images for the CdS thin films grown on  $SiO_2$  and  $HfO_2$  at 70°C for 25 min (~60 nm thick). A higher surface roughness is observed for CdS deposited on  $HfO_2$  when compared with those deposited on  $SiO_2$ . However, and independent of the dielectric, crystalline features are observed in the CdS films indicating that the films are polycrystalline.

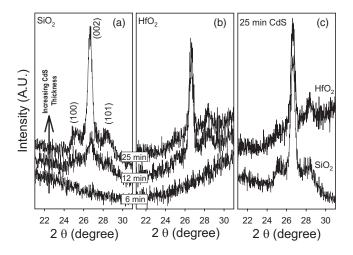

Figure 2 shows the XRD results for the CdS films grown on SiO<sub>2</sub> (Fig. 2a) and HfO<sub>2</sub> (Fig. 2b) deposited for 6, 12, and 25 min. The thickness of the CdS films grown for 12 min was  $\sim$ 35 nm, whereas the thickness of those deposited for 25 min was  $\sim$ 60 nm. The thickness for the CdS films deposited for times shorter than 6 min

Figure 2. XRD patterns for the samples deposited at different times on (a)  $SiO_2$  and (b)  $HfO_2$  dielectric layer and (c) CdS grown for 25 min on  $HfO_2$  or  $SiO_2$ .

could not be measured and no crystalline features were detected by XRD. The XRD pattern for the films deposited for 12 and 25 min shows clear diffraction peaks corresponding to the (100), (002), and (101) crystalline planes of the hexagonal crystalline phase of CdS.<sup>36</sup> Clearly, the resulting CdS films deposited after 12 min are polycrystalline with a hexagonal structure and with a preferred crystalline orientation along the (002) direction. The final microstructure of the CdS deposited on HfO<sub>2</sub> and SiO<sub>2</sub> is different. This difference in the microstructure starts at the early stages of CdS nucleation and growth and it remains constant throughout the entire CdS film thickness, as clearly seen in Fig. 2a and b.

Although both films show a preferential growth in the (002) direction, CdS deposited on  $HfO_2$  does not show a clear diffraction for the (100) orientation. The difference in the XRD patterns suggests that the CdS grown in  $HfO_2$  are mostly composed of (002) and (101) phases, whereas the CdS deposited on SiO<sub>2</sub> shows an additional orientation in the (100) direction. The difference in nucleation for CdS on SiO<sub>2</sub> and  $HfO_2$  is likely due to the presence of an excess of hydroxyl groups (OH<sup>-</sup>) resulting from the ALD process (as we will discuss in detail below). Thermal SiO<sub>2</sub> is likely to have a lower concentration of OH<sup>-</sup> on the surface, and therefore, less nucleation sites for CdS growth.

Figure 2c compares the XRD results for CdS grown for 25 min ( $\sim 60$  nm) on either HfO<sub>2</sub> or SiO<sub>2</sub>. Clearly, the CdS grown on SiO<sub>2</sub> is more polycrystalline than that grown in HfO<sub>2</sub>. This results in more grain boundaries at the interface between the dielectric and the semiconductor. This is likely to result in degraded carrier mobility for the CdS films deposited on SiO<sub>2</sub>.

To further investigate the impact of the dielectric in the nucleation of the CdS films, XPS was performed for the CdS films deposited for 0.5, 1, and 2 min on either SiO<sub>2</sub> or HfO<sub>2</sub>. Figure 3a and b shows the Cd 3d region for the CdS films deposited on HfO<sub>2</sub> and SiO<sub>2</sub>, respectively. For reference, the scan for the HfO<sub>2</sub> and SiO<sub>2</sub> films before any CdS deposition is also shown. In HfO<sub>2</sub> (Fig. 3a), the Cd 3d feature is observed in depositions of as short as 0.5 min, and after 2 min of reaction, distinct peaks of Cd bonded to S are clearly observed.<sup>37</sup> However, for the CdS films deposited on SiO<sub>2</sub>, no Cd features are observed for times shorter than 2 min (Fig. 3b). The presence of the Cd XPS features from the very early stages in CdS deposited on HfO<sub>2</sub> indicates that nucleation in this dielectric is faster than when CdS is grown on SiO<sub>2</sub>.

Figure 3c and d shows the S 1s region for the CdS films deposited on HfO<sub>2</sub> and SiO<sub>2</sub>, respectively. The peak observed at ~162 eV for the CdS films deposited for 2 min on HfO<sub>2</sub> corresponds to S bonded to Cd and the broad peak at ~169 eV corresponds to CdSO<sub>4</sub> (Fig. 3c).<sup>37,36</sup> No sulfur is detected for deposition times shorter than 2 min; therefore, in HfO<sub>2</sub>, 2 min of reaction is enough to grow CdS. Similarly, from CdS deposited on SiO<sub>2</sub>, no sulfur is observed for times shorter than 2 min (Fig. 3d). The small band at ~162 eV observed in films grown for 2 min indicates that CdS is just beginning to grow. These substantial differences in the nucleation of CdS on HfO<sub>2</sub> and SiO<sub>2</sub> impact the final microstructure of the resulting CdS films (Fig. 2). The CdSO<sub>4</sub> feature might be due to surface oxidation due to air exposure before the XPS analyses.

The O 1s region for CdS deposited on HfO<sub>2</sub> is shown in Fig. 3e. The peaks observed in the films grown for less than 2 min are consistent with a mixture of CdSO<sub>4</sub> (531.70 eV), Cd(OH)<sub>2</sub> (530.90 eV), and CdO (531.60 eV).<sup>36,37</sup> For reference, a CdS film deposited for 25 min is also shown. No clear difference between the CdS films deposited for 2 and 25 min on HfO<sub>2</sub> is observed, which indicates that the excess oxygen is likely due to surface oxidation resulting from air exposure of the films before the XPS analyses. It is difficult to determine if the CdS films grown for times shorter than 2 min on SiO<sub>2</sub> (Fig. 3f) have CdSO<sub>4</sub>, Cd(OH)<sub>2</sub>, or CdO because the XPS bands from these materials overlap with the Si–O–Si band at ~533 eV. The broadening and intensity reduction of the band as b)

Cd 3d a) Cd 3*d* HfO<sub>2</sub> SiO<sub>2</sub> Intensity (A.U.) Intensity (A.U. 2 min 2 mir mir 1 min 0.5 mir 0.5 mi no dep no dep 416 414 412 410 408 406 404 402 416 414 412 410 408 406 404 402 Binding Energy (eV) Binding Energy (eV) HfO<sub>2</sub> S 1s d) c) SiO<sub>2</sub> S 1s 2 min Intensity (A.U.) (A.U.) 1 min m 0.5 mi ntensity Ww no dep 1 mir 0.5 mii no dep mmmmmm 172 170 168 166 164 162 160 158 172 170 168 166 164 162 160 158 HfO<sub>2</sub> e) SiO<sub>2</sub> f) O 1s O 1s 25 min 25 min Intensity (A.U.) ntensity (A.U. 2 mi miı 0.5 mi 0.5 mir No der No dep 538 536 534 532 530 528 526 538 536 534 532 530 528 526 Binding Energy (eV) Binding Energy (eV)

Figure 3. XPS for CdS films grown on either HfO<sub>2</sub> or SiO<sub>2</sub>.

well as evidence of Cd (Fig. 3b) and S (Fig. 3d) seem to indicate the presence of Cd-S bonds for reactions with deposition times longer than 2 min.

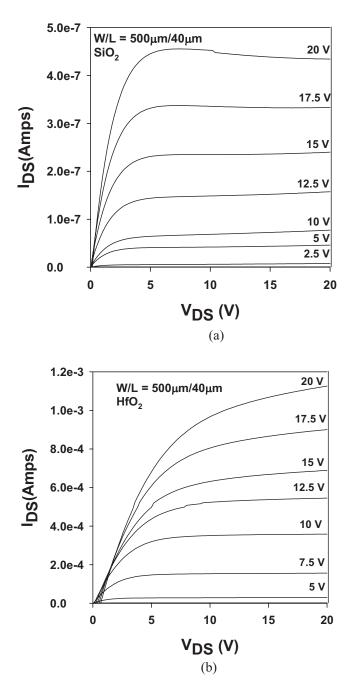

The electrical characteristics of TFTs with CdS films deposited for 25 min (60 nm) on  $SiO_2$  and  $HfO_2$  are shown in Fig. 4 and 5. Figure 4 shows the drain current  $(I_D)$  vs source–drain voltage  $(V_{DS})$ results, measured from 0 to 20 V for devices with (a) SiO<sub>2</sub> and (b) HfO<sub>2</sub> as the gate dielectric. An excellent transistor behavior is observed in devices deposited on either SiO<sub>2</sub> or HfO<sub>2</sub>. The decrease in  $I_{\rm D}$  with  $V_{\rm DS}$  at high  $V_{\rm G}$  observed for devices with SiO<sub>2</sub> as the dielectric material is likely due to a well-known effect in poly-Sibased TFTs and silicon on insulator devices where thermal effects caused by power dissipation in metal-oxide-semiconductor devices can alter their I-V characteristics and can even show a negative dynamic resistance in their saturation regions.<sup>38</sup> Our SiO<sub>2</sub> devices are fabricated on top of a thick insulator, which might limit power dissipation and result in increased temperature in the channel at high  $V_{\rm G}$ , which results in lower mobility and reduced  $I_{\rm D}$  at  $V_{\rm G}$ .  $I_{\rm G}$  in these devices is very low.

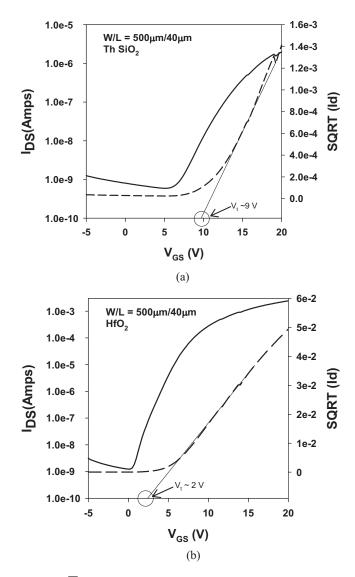

The  $I_{\rm D}$ - $V_{\rm G}$  (solid lines) and the  $\sqrt{I_{\rm D}}$ - $V_{\rm G}$  (dashed lines) for CdS films deposited for 25 min (60 nm) on SiO<sub>2</sub> and HfO<sub>2</sub> are shown in Fig. 5a and b, respectively. All measurements were performed at  $V_{\rm DS} = 20$  V. To determine the channel mobility ( $\mu$ ) and the threshold voltage  $(V_{\rm T})$  for the devices, the linear region of the curves were fitted to the equation<sup>3</sup>

Figure 4. Characteristic  $I_D$  vs  $V_{DS}$  plots for several values of  $V_G$  for the CdS-based TFTs deposited on (a) SiO<sub>2</sub> and (b) HfO<sub>2</sub>.

$$I_{\rm D}^{1/2} = \left(\frac{C_{\rm i} W \mu_{\rm sat}}{2L}\right)^{1/2} (V_{\rm G} - V_{\rm T})$$

[1]

where  $V_{\rm G}$  is the gate voltage, W is the channel width, L is the channel length, and  $C_i$  is the capacitance per unit area for the gate dielectric. The fitting is shown as dotted lines in Fig. 5. The threshold voltage, which corresponds to the intersections of the dotted lines with the  $V_{\rm G}$  axis, is ~9 V for devices with SiO<sub>2</sub> and ~2 V for devices with  $HfO_2$ . One of the reasons for the lower  $V_T$  observed for CdS deposited on HfO<sub>2</sub> is the higher dielectric constant of HfO<sub>2</sub>. More importantly, the electron mobility, extracted for devices with SiO<sub>2</sub> as the gate dielectric, is  $2.3 \times 10^{-2}$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, whereas for devices with HfO2 as the gate dielectric, the mobility is  $\sim\!25~\text{cm}^2~V^{-1}~\text{s}^{-1}$  or higher. The electron mobility of bulk CdS is 210 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1,19</sup> The main reason for the lower mobility in

**Figure 5.**  $\sqrt{I_D}$  vs  $V_G$  plots (right axis) for the CdS-based TFTs on different dielectrics (a) SiO<sub>2</sub> and (b) HfO<sub>2</sub>. The straight lines correspond to the best linear fits to Eq. 1. Semilogarithmic plots of  $I_D$  vs  $V_G$  (left axis) for the same devices.

TFTs is the polycrystalline nature of the CdS layers. The electrical response of the HfO2/CdS-based TFTs is considerably higher than that reported for SiO<sub>2</sub>/CdS-based TFTs ( $\mu_{sat}$  = 0.13–0.16 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and  $V_T$  = 8.8–25 V) <sup>24</sup> and the CdS deposited here on SiO<sub>2</sub> (0.023 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>). The main reason for the better mobility of the devices fabricated on HfO2 is likely the better interface between the dielectric and the semiconductor. This behavior is associated with the (OH<sup>-</sup>)-rich surface of the HfO<sub>2</sub> that results from the ALD process. This CBD-friendly surface promotes better nucleation and growth and better oriented CdS films. The fabrication process for the CdS-based TFTs reported here does not include thermal annealing, and the highest temperature involved in the processing of the HfO<sub>2</sub>/CdS-based TFTs is 100°C, which is quite compatible with the fabrication of electronic flexible devices.

In conclusion, we have studied the growth stages in the CBD process of CdS films on different dielectric layers and correlated film structure with device performance. CdS films as-grown on HfO<sub>2</sub> showed higher mobility ( $\sim 25 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ) and low threshold voltage ( $\sim 2$  V). HfO<sub>2</sub> seems to provide a better starting surface for CdS nucleation and growth. This is likely due to the presence of (OH)<sup>-</sup> on the surface of the HfO<sub>2</sub> as a result of the ALD process used to deposit the HfO2 films. Based on these results we conclude that ALD HfO<sub>2</sub> is a promising dielectric for chalcogenide-based TFT devices for flexible electronics.

## Acknowledgments

This work was partially supported by the Army Research Laboratory and CONACYT Mexico.

University of Texas at Dallas assisted in meeting the publication costs of this article.

## References

- 1. C. D. Dimitrakopoulos and P. R. L. Malenfant, Adv. Mater., 14, 99 (2002).

- A. Sazonov and A. Nathan, J. Vac. Sci. Technol. A, 18, 780 (2000). 2

- C.-S. Yang, L. L. Smith, C. B. Arthur, and G. N. Parsons, J. Vac. Sci. Technol. B, 3. 18, 683 (2000).

- R. E. I. Schropp, B. Stannowski, and J. K. Rath, J. Non-Cryst. Solids, 299-302, 1304 (2002)

- S. Bose and S. K. Saha, Chem. Mater., 15, 4464 (2003). 5

- L. E. Brus, Appl. Phys. A: Mater. Sci. Process., 53, 465 (1991). 6.

- Y. Wang and N. Herron, J. Phys. Chem., 95, 525 (1991).

- A. Henglein, Top. Curr. Chem., 143, 113 (1988).

- 9. R. B. Kale, S. D. Sartale, B. K. Chougule, and C. D. Lokhande, Semicond. Sci. Technol., 19, 980 (2004) N. N. Greenwood and E. A. Earnshaw, Chemistry of the Elements, Pergamon Press, 10.

- Oxford (1990).

- 11. A. Vadivel Murugan, R. S. Sonawane, B. B. Kale, S. K. Apte, and A. V. Kulkarni, Mater. Chem. Phys., **71**, 98 (2001). W. Hoheisel, V. L. Colvin, C. S. Johnson, and A. P. Alivisatos, J. Chem. Phys., 12.

- 101, 8455 (1994).

- C. B. Murray, C. R. Kagan, and M. G. Bawendi, Science, 270, 1335 (1995)

- R. Rossetti, R. Hull, J. M. Gibson, and L. E. Brus, J. Chem. Phys., 82, 552 (1985).

- 15. M. L. Steigerwald and L. E. Brus, Annu. Rev. Mater. Sci., 19, 471 (1989).

- 16. S. Mann, Nature (London), 332, 119 (1988).

- C. B. Murray, D. J. Morris, and M. G. Bawendi, J. Am. Chem. Soc., 115, 8706 17. (1993).

- J. I. Pankove, Optical Processes in Semiconductors, Dover, New York (1971). 18.

- W. E. Howard, in Thin Film Transistors, C. R. Kagan and P. Andry, Editors, Marcel 19. Dekker, New York (2003).

- F. Y. Gan and I. Shih, IEEE Trans. Electron Devices, 49, 15 (2002) 20.

- 21. C. Voss, S. Subramanian, and C.-H. Chang, J. Appl. Phys., 96, 5819 (2004).

- B. Mereu, G. Sarau, E. Pentia, V. Draghici, M. Lisca, T. Botila, and L. Pintilie, 22. Mater. Sci. Eng., B, 109, 260 (2004).

- Y.-J. Chang, C. L. Munsee, G. S. Herman, J. F. Wager, P. Mugdur, D.-H. Lee, and 23. C.-H. Chang, C.- E. Mullser, G. S. Helman, J. F. Wagel, T. Mugdui, D.-H. Eee, and

C.-H. Chang, Surf. Interface Anal., 37, 398 (2005).

J. H. Lee, J. W. Yoon, I. G. Kim, J. S. Oh, H. J. Nam, and D. Y. Jung, *Thin Solid*

- Films, 516, 6492 (2008).

- 25 R. Ramírez-Bon, M. A. Quevedo-López, R. A. Orozco-Terán, F. J. Espinoza-Beltrán, and M. Sotelo-Lerma, J. Phys. Chem. Solids, 59, 145 (1998).

- R. A. Orozco-Terán, M. Sotelo-Lerma, R. Ramirez-Bon, M. A. Quevedo-López, O. 26. Medoza-González, and O. Zelaya-Angel, Thin Solid Films, 343-344, 587 (1999).

- D. S. Boyle, A. Bayer, M. R. Heinrich, O. Robbe, and P. O. O'Brien, Thin Solid 27. Films, 361-362, 150 (2000).

- 28. D. Hariskos, M. Powalla, N. Chevaldonnet, D. Lincot, A. Schindler, and B. Dimmler, Thin Solid Films, 387, 179 (2001).

- H. Zhang, X. Ma, and D. Yang, Mater. Lett., 58, 5 (2004). M. B. Ortuño-López, J. J. Valenzuela-Jáuergui, M. Sotelo-Lerma, A. Mendoza-30.

- Galván, and R. Ramírez-Bon, Thin Solid Films, 429, 34 (2003). 31 M. B. Ortuño-López, M. Sotelo-Lerma, A. Mendoza-Galván, and R. Ramírez-Bon,

- Thin Solid Films, 457, 278 (2004). S. Gowrisanker, M. A. Quevedo-Lopez, H. N. Alshareef, B. Gnade S. Venugopal, 32.

- R. Krishna, K. Kaftanoglu, and D. Allee, Org. Electron., 10, 1217 (2009).

- 33 A. Dodabalapur, L. Torsi, and H. E. Katz, Science, 268, 270 (1995)

- 34. D. Lincot and R. Ortega-Borges, J. Electrochem. Soc., 139, 1880 (1992).

- M. G. Sandoval-Paz, M. Sotelo-Lerma, A. Mendoza-Galvan, and R. Ramírez-Bon, 35. Thin Solid Films, 515, 3356 (2007).

- K. L. Narayanan K. P. Vijayakumar K. G. M. Nair, and G. V. N. Rao, Bull. Mater. Sci., 20, 287 (1997).

- 37. D. A. Mazón-Montijo, M. Sotelo-Lerma, M. A. Quevedo-Lopez, M. El-Bouanani, H. N. Alshareef, F. J. Espinoza-Beltrán, and R. Ramírez-Bon, Appl. Surf. Sci., 254, 499 (2007).

- 38. D. Sharma, J. Gautier, and G. Merckel, IEEE J. Solid-State Circuits, 13, 378 (1978).

- 39. J. Jang, in Thin Film Transistors, C. R. Kagan and P. Andry, Editors, Marcel Dekker, New York (2003).