Vol. 7, No. 4, August 2017, pp. 1899~1905

ISSN: 2088-8708, DOI: 10.11591/ijece.v7i4.pp1899-1905

# Impact of multiple channels on the Characteristics of Rectangular GAA MOSFET

# Mohammed Khaouani, Ahlam Guen-Bouazza

Unit of Research Materials and Renewable Energies, Department of Electronics, Faculty of Technology, University, Abou-Bakr Belkaid, Tlemcen, Algeria BP 330 Tlemcen

# Article Info

## Article history:

Received Oct 11, 2016 Revised Feb 21, 2017 Accepted Mar 4, 2017

# Keyword:

Channels

DIBL

Gate-all-around

MOSFETS

Multiple

SCEs

Silicon

Silvaco-TCAD

# **ABSTRACT**

Square gate all around MOSFETs are a very promising device structures allowing to continue scaling due to their superior control over the short channel effects. In this work a numerical study of a square structure with single channel is compared to a structure with 4 channels in order to highlight the impact of channels number on the device's DC parameters (drain current and threshold voltage). Our single channel rectangular GAA MOSFET showed reasonable ratio Ion/Ioff of 10<sup>4</sup>, while our four channels GAA MOSFET showed a value of 10<sup>3</sup>. In addition, a low value of drain induced barrier lowering (*DIBL*) of 60mV/V was obtained for our single channel GAA and a lower value of with 40mv/v has been obtained for our four channels one. Also, an extrinsic transconductance of 88ms/μm have been obtained for our four channels GAA compared to the single channel that is equal to 7ms/μm.

Copyright © 2017 Institute of Advanced Engineering and Science.

All rights reserved.

1899

#### Corresponding Author:

Khaouani mohammed

Unit of Research Materials and Renewable Energies

Department of Electronics,

Faculty of Technology

University, Abou-Bakr Belkaid, Tlemcen, Algeria BP 330 Tlemcen.

Email: mohammed.khaouani@mail.univ-tlemcen.dz

# 1. INTRODUCTION

Over the past decades, the Metal oxide Semiconductor (MOSFET) has repeatedly been scaled down in size. However, as the size reduction of planar bulk MOSFET continues, leakage increases, the control of short-channel effects becomes increasingly difficult in planar-bulk architecture [1]. Today different new architectures such as Multiple-gate MOSFETs are considered as a very good alternative replacing bulk MOSFET allowing keeping up with the continuous reduction in device dimensions imposed by Moore's law. The non planar transistors have been found to be more appropriate to the highly scaled transistors lengths. These devices provide better control over the channel thus reducing short channel and hot carriers effects [2]. Indeed, the use of several gates has revealed good electrostatic control of the channel with the opportunity of higher reduction in channel length compared to conventional MOSFETs .New architectures called MUGFETS that are Double-Gate, Triple-Gate, Junctionless FET, PI- Gate, Omega- Gate, Surrounding Gate "square Gate-All- Around MOSFETs and Cylindrical Gate-All- Around) are very promising devices for very short channel lengths [3], [4]. Short channel effects" SCEs" such as threshold voltage roll-off, off-state leakage current, drain Induced Barrier Lowering (DIBL) and subthresholde swing SSs are significantly reduced in multiple gate architectures [5-8]. Among these multiple gate structures, GAA structures offer superior control over the channel due to its surrounding gate structure, which in turn reduces SCEs effectively [8-10]. MUGFETs devices show a very promising possibilities, advantages over single MOSFETs, in relation to the control of SCEs and the achievement of very promising sub-threshold swing values, a high immunity to SCEs, its low drain induced barrier lowering, high gate controllability, higher current drivability, mobility enhancement and reduction of leakage currents [10].

These devices are considered as excellent candidates for future CMOS integration. Among all MUGFETs devices, GAA structures have gained considerable attention from device and circuit developers. Additionally to the effective suppression of SCEs, MUGFETs devices show exceptional current drive and have the merit that they are perfectly compatible with conventional CMOS processes. The rectangular GAA MOSFETs considered in our study, are a multi-gate structure, their architecture are based on a SOI triple gate structure. The vertical GAA structure has a higher yield [11]. It is considered as a potential candidate for future energy-efficient electronics [12]. In a vertical MOSFET device, the current is orthogonal to the surface of the wafer. In n-channel MOSFET devices, a stack of n+ p n+ silicon is made by epitaxial growth or implantation, then a gate is put around the structure. This architecture has proved to be a realistic approach to sub-100nm channel length devices [14]. Since the introduction of GAA MOSFET, much different architecture has been proposed, using high-k dielectrics [13,15] or ultra-thin silicon channel with possibility to using in channel III-V material ZnO or organic material like Pantacen for different application of MUGFETs devices [16], [17]. A 15nm Channel length in a vertical gate MOSFET has recently been demonstrated [18], [19]. Vertical MOSFETs show better performances than bulk planar devices. They are attractive structures that show better performances than bulk planar devices even if there is no leading design or fully optimized fabrication process for the moment. The GAA MOSFET, which is basically a 3-D structure, cannot be analyzed directly using the conventional way. It can be analyzed by Laplace's equation in rectangular coordinates by means of using a series expansion in Bessel functions [20].

In this work, a simulation of Bohm quantum potential (BQP) model was used to calculate a position dependent potential energy term using an auxiliary equation derived from the Bohn interpretation of quantum mechanics [21]. In this paper we set up a 3D device simulation framework using the SILVACO technology Computer Aided Design (TCAD). In our simulation quantum effects are considered. These have been achieved using the Bohm quantum potential (BQP) model.

#### 2. DEVICE DESCRIPTION

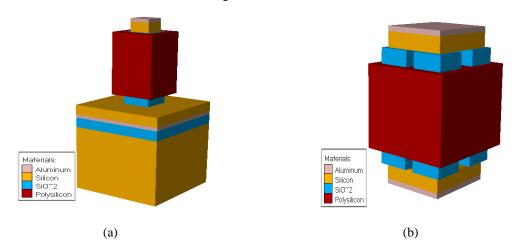

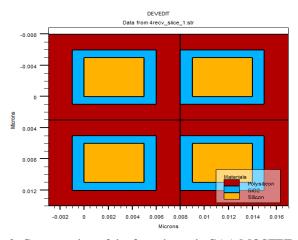

The simulation data presented in this work have been obtained by using SILVACO TCAD tool. The geometry of the two rectangular GAA MOSFETs studied are shown in Figure 1, the cross-section of our four channels GAA MOSFET studied is shown in Figure 2.

Figure 1. (a) One channel, (b) Four channels Rectangular GAA MOSFETs

As shown in Figure 1 the first device studied is one channel GAA MOSFET, the second one is a four channels GAA MOSFET. All the channels are identical and have the same geometrical parameters. We can see that the gate completely surrounds the square silicon channels where conduction takes place. The devices details of our two GAA are given in Table 1. SILVACO TCAD simulator is used with the adequate models in all our study.

Figure 2. Cross-section of the four channels GAA MOSFET studied

| Table 1 | 1. Parameters | value of | our two squa | are GAA devices |

|---------|---------------|----------|--------------|-----------------|

|---------|---------------|----------|--------------|-----------------|

| Values               |

|----------------------|

| 19 nm                |

| 22nm                 |

| 5 nm                 |

| 5 nm                 |

| 2 nm                 |

| 1E20/cm <sup>3</sup> |

| $1E17 / cm^3$        |

| 8nm                  |

| 50nm                 |

|                      |

The geometry of our rectangular cross section GAA device confines the electrons in the plane perpendicular to the transport axis. In this case, a 1D electron gas is considered electrons are confined perpendicularly to the transport axis. The quantum charge density can be expressed by [21], [22]:

$$\rho(y,z) = \frac{q}{\pi} \left( \frac{2mk_{\rm B}T}{\hbar^2} \right)^{\frac{1}{2}} \sum_{n} \Psi_{\rm n}^2(y,z) \Im_{-\frac{1}{2}} \left( \frac{E_{\rm F} - E_{\rm n}}{k_{\rm B}T} \right) \tag{1}$$

where q is the electron charge,  $E_F$  is the Fermi level,  $\psi_n$  is the wave function belonging to energy level En,  $\mathfrak{F}_{-\frac{1}{2}}$  is the complete Fermi-Dirac integral of order -1/2.

# 3. RESULTS AND ANALYSIS

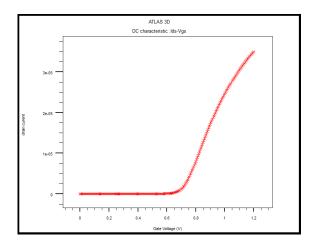

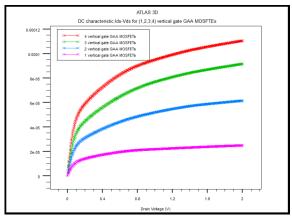

All our results were carried out at room temperature. Our Simulation results had been obtained using Atlas Silvaco Software. Typical transfer characteristics  $I_{ds}$ - $V_{gs}$  leads to determining different device parameters, like threshold voltage Vth, subthreshold slope SS or off-state leakage current  $I_{off}$ . All these extracted parameters allow revealing the performance of the devices in accordance to their scaling. Figure 3 and Figure 4 show the  $I_{DS}$  versus  $V_{GS}$  and  $I_{DS}$  versus  $V_{DS}$  characteristics at  $T=300^{\circ}$ K.

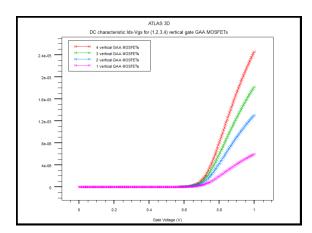

In order to increase our device current, wider transistors with higher on-currents are obtained using a multiple channel connected together. The current drive is proportional to channels number. Transfer and output characteristic for one, two, three and four channels are shown in Figure 5 and Figure 6.

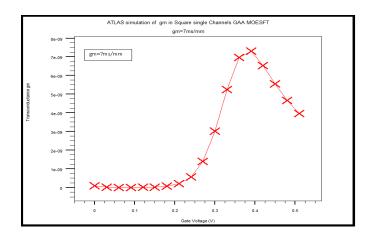

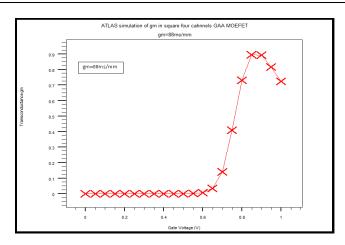

AS shown in Figure 6, the drain current obtained with four channels device is four times higher than the current obtained by one channel. We can conclude that n-channels connected together allow to obtain a current n- times higher than the current obtained for one channel device. Transconductance  $g_m$  is an important parameter for small-signal analysis of analog circuits. Generally, it is important to analyze the transconductance  $g_m$  and also transconductance efficiency  $(g_m/ID)$  as it provides useful design guidlines. The sensitivity of  $g_m$  and  $(g_m/ID)$  on process related parameters gives deeper insight of circuit performance. Figure 7 and Figure 8 show the transconductance versus gate voltage for our single channel and our four

channels devices. We can observe that peak tranconductance is occured four our single channel device at  $V_{GS}$ = 0.4 volts, whereas for our four channel device, this peak is occured at VGS= 0.85 volts.

ATLAS 3D

DC characteristic Ids-Vds for 4 vertical gate gate all around MOSFETs

Vgs=1 6r

Vgs=1 4r

0 0012

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

0 0000

Figure 3. Transfer characteristic of a four channel rectangular GAA

Figure 4. Output characteristics of our four channels rectangular GAA MOSFETs.

Figure 5. Transfer Characteristics of one, two, three and four channels rectangular GAA

Figure 6. Output Characteristics for (one channel, two channel, three channel and four channel vertical rectangular GAA MOSFETs

Figure 7. Transconductance  $g_m$  versus gate voltage for one channel rectangular GAA MOSFET

Figure 8.Transconductance g<sub>m</sub> versus gate voltage for four channels rectangular GAA MOSFET

The simulated curves exhibit a maximum of  $7ms/\mu m$  in single channels and  $88ms/\mu m$  in four channels GAA MOESFT at  $V_{DS}=1.0$  V. This peak appearing in the curve of the transconductance depends mainly on the gate bias  $V_{GS}$  and reflects the DC behavior of the simulated MOSFETs, which correspond to the channels modulated by different gate voltages. The DC characteristics obtained for a four channels devices are better, compared with a sample channel device that has obviously a slight inferior electrical properties earlier reported [23-24], the total parasitic resistance is usually dominated at low Ohmic contact resistance which is highly wanted, and can be attributed to the increase of carrier concentration or/and the increase of carrier mobility [25-27], We can note from our results that the  $g_m$  value is more important for our four channel GAA MOEFTS compared to the single channel one .

Table 2. Variation of the device electrical parameters as function of channels number

|   |                | One Channel | Two Channels | Three    | Four Channels |

|---|----------------|-------------|--------------|----------|---------------|

|   |                | GAA         | GAA          | Channels | GAA MOSFET    |

|   |                | MOSFET      | MOSFET       | GAA      |               |

|   |                |             |              | MOSFET   |               |

| - | Dibl<br>(mv/v) | 60          | 55           | 50       | 40            |

|   | Ion(A)         | 5.35E-07    | 1.24E-07     | 1.73E-07 | 2.28E-6       |

|   | Ioff(A)        | 2.13E-13    | 1.80E-12     | 1.94E-12 | 1.78E-11      |

|   | Ion/Ioff       | 2,5E6       | 0.68E5       | 0.89E5   | 1.20E5        |

| _ | SS (mV/dec)    | 62.5        | 73           | 73.7     | 72            |

One of the major challenges for the miniaturization of the MOS transistor is to ge t a high report Ion/Ioff. These nanometer MOSFET impose new technological challenges and reveal new phenomena that we cannot neglect, with Ion defined as the drain current when  $Vgs=V_{ds}=V_{dd}$  and  $I_{off}$  as the drain current when Vgs=0 and  $V_{ds}=V_{dd}$  [28- 29].The MOSFETs have a high DIBL which is generally greater than  $100mV\ /\ V$  for lengths less than 50 nm that we can show in Table 2. The reduction in channel lengths improves the electrostatic and thus reduces the DIBL (less than  $20mV\ /\ V$  for a gate length of 50 nm).

### 4. CONCLUSION

In this work, a 3D simulation of 22nm four channels rectangular Gate MOSFETs on Si substrates using Silvaco software was presented. Our device exhibited high current density with a value of 30mA/mm, and a peak of extrinsic transconductance equal to 88ms/mm at  $V_{DS}$ =1 V, a cut-off frequency equal to 300GHz, fmax equal to 800 GHz and DIBL=60mV/V. These results demonstrate the possibility of using this technology in different application. This result also allows us to see the impact of channels number on the electrical characteristics of the device.

#### REFERENCES

- [1] The International Technology Roadmap for Semiconductors (ITRS), 2012.

- [2] T. Poiroux, M. Vinet, O. Faynot, J. Wildeiz, J. Lolivier, T.Ernst, B.Previtali, S.Delonibus, "Multiple Gate Devices: Advantages and Challenges", *Microelectronic Engineering*, vol.80, pp. 378-385, June 2005.

- [3] S. Oh, D. Monroe and JM. Hergenrother, "Analytic Description of Short channel effects in Fully Depleted Double Gate and Cylindrical Surrounding Gate MOSFETs", *IEEE Transactions on Electron Devices*, vol. 21, no. 9, pp. 445-447, September 2000.

- [4] Munawar A Riyadi, Irawan D Sukawati, Teguh Prakoso, Darjat, "Influence of Gate Material and Process on Junctionless FET Subthreshold Performance", *International Journal of Electrical and Computer Engineering* (*IJECE*), vol. 6, no. 2, April 2016, pp. 895~900

- [5] Hak Kee Jung, Sima Dimitrijev, "The Impact of Tunneling on the Subthreshold Swing in Sub-20 nm Asymmetric Double Gate MOSFETs," *International Journal of Electrical and Computer Engineering (IJECE)*, vol. 6, no. 6, December 2016, pp. 2730~2734.

- [6] D. Jimenez, B. Iniguez, J. Sune and J. J. Saenz, "Analog Performance of the Nanoscale Double Gate MOSFET near the Ultimate Scaling Limits", *J. App. Physics.*, vol.96, no.9, pp. 5271-5276, November 2004.

- [7] D. Jiménez, J. J. Sáenz, B. Iñíguez, J. Suñé, L. F. Marsal, J. Pallarès, "Modeling of Nanoscale Gate-All-Around MOSFETs", *IEEE Electron Device Letters*, vol. 25, no. 5, May 2004.

- [8] J.-T. Park, J.-P. Colinge, "Multiple-gate SOI MOSFETs: Device Design Guidelines," *IEEE Trans. Electron Devices*, vol. 49, no. 12, pp. 2222–2229, December 2002.

- [9] J.-T. Park, J.-P. Colinge, "Multiple-gate SOI MOSFETs: Device Design Guidelines," *IEEE Trans. Electron Devices*, vol. 49, no. 12, pp. 2222–2229, December 2002.

- [10] S. D. Suk, S.-Y. Lee, S.-M. Kim, E.-J. Yoon, M.-S. Kim, M. Li, C. W. Oh, K. H. Yeo, S. H. Kim, D.-S. Shin, K.-H.Lee, H. S. Park, J. N. Han, C. J. Park, J.-B. Park, D.-W. Kim, D. Park, B.-I. Ryu, "High Performance 5 nm Radius twin Silicon nano-wire MOSFET (TSNWFET): Fabrication on bulk Si wafer, Characteristics, and Reliability," *IEDM Tech.* Dig., 2005, pp. 717720.

- [11] DavideSacchetto, ShenqiXie, Veronica Savu, Michael Zervas, Giovanni De Micheli, Jürgen Brugger, Yusuf Leblebici, "Vertically-stacked gate-all-around Polysilicon Nanowire FETs with Sub-lm Gates Patterned by Nanostencil Lithography", *Microelectronic Engineering*, 2012.

- [12] Ramanathan Gandhi, Zhixian Chen, Navab Singh, Senior Member, IEEE, Kaustav Banerjee, Senior Member, IEEE, Sungjoo Lee, "CMOS-Compatible Vertical-Silicon-Nanowire Gate-All-Around p-Type Tunneling FETs With ≤ 50-mV/decade Subthreshold Swing", *IEEE Electron Device Letters*, vol. 32, no. 11, Nov 2011.

- [13] J. M. Hergenrother, G. D. Wilk, T. Nigam, F. P. Klemens, D. Monroe, P. J. Silverman, T. W. Sorsch, B. Busch, M. L. Green, M. R. Baker, T. Boone, M. K. Bude, N. A. Ciampa, E. J. Ferry, A. T. Fiory, S. J. Hillenius, D. C. Jacobson, R. W. Johnson, P. Kalavade, R. Keller, C. A. King, A. Kornblit, H. W. Krautter, J. T.-C. Lee, W. M. Mansfield, J. F. Miner, M. D. Morris, S.-H. Oh, J. M. Rosamilia, B. J. Sapjeta, K. Short, K. Steiner, D. A. Muller, P. M. Voyles, J. L. Grazul, E. Shero, M. E. Givens, C. Pomarede, M. Mazanec, and C. Werkhoven, "50 nm vertical replacement-gate (VRG) nMOSFETs with ALD HfO2 and Al2O3 gate dielectrics", *Technical Digest of IEDM*, pp. 3.1.1-3.1.4, Washington DC, 2001.

- [14] E. Josse, T. Skotnicki, M. Jurczak, M. Paoli, B. Tormen, D. Dutartre, P. Ribot, A.Villaret and E. Sondergard, 'High performance 40 nm vertical MOSFET within a conventional CMOS process flow', *Proceedings of VLSI Symposium on Technology*, pp. 55-56, Kyoto JP, 2001.

- [15] Kavindra Kandpal, Navneet Gupta, "Zinc Oxide Thin Film Transistors Advances Challenges and Future Trends", Bulletin of Electrical Engineering and Informatics, vol. 5, no. 2, June 2016, pp. 205~212.

- [16] Fadliondi, Muhammad Kunta Biddinika, Shun-ichiro Ohmi, "The Humidity Dependence of Pentacene Organic Metal-Oxide-Semiconductor Field-Effect Transistor," *TELKOMNIKA*, vol. 15, no. 2, June 2017, pp. 578~583.

- [17] M. Masahara, T. Matsukawa, K. Ishii, L. Yongxun, H. Tanoue, K. Sakamoto, T. Sekigawa, H. Yamauchi, S. Kanemaru, E. Suzuki, "15-nm-thick Si channel wall vertical double-gate MOSFET", *Technical Digest of IEDM*, pp. 949-951, San Francisco CA, 2002.

- [18] P. Razavi, G. Fagas, I. Ferain, N. Akhavan, R. Yu, J. Colinge, "Performance Investigation of Junctionless Multigate short -channel Transistors", in Ultimate Integration on Silicon (ULIS), 201112th International Conference on, P. 1-3, IEEE, 2011.WFET): Fabrication on bulk Si wafer, characteristics, and reliability, IEDM Tech. Dig., 2005, pp. 717720.

- [19] D. Jimenez, B. Iniguez, J. Sune and J. J. Saenz, "Analog Performance of the Nanoscale Double Gate MOSFET near the Ultimate Scaling Limits", *J. App. Physics.*, vol. 96, no. 9, pp. 5271-5276, November 2004.

- [20] H. A. El Hamid, B. Iñiguez, J. Roig, "Analytical Model of the Threshold Voltage and Subthreshold swing of undoped Cylindrical gate-allaround-based MOSFETs," *IEEE Trans. Electron Devices*, vol. 54, no. 3, pp. 572–579, Mar. 2007.

- [21] J. S. Xue, J. C. Zhang, Y. W. Hou, H. Zhou, J. F. Zhang, Y. Hao, "Fabrication and Characterization of InAlN/GaN-based double-channel high Electron Mobility Transistors for Electronic Applications", J. Appl. Phys. 111, pp. 114513, 2012.

- [22] A. Trellakis, A. T. Galick, A. Paceli, U. Ravaioli, "Iteration Scheme for the Solution of the two Dimensional Schrdinger-Poisson Equations in Quantum Structures", *Journal Applied Physics*, vol 81, no. 12, pp. 7880-7884, 1997.

- [23] F.J.Garc\_a Ruiz, A.Godoy, F.G\_amiz, C.Sampedro, L.Donetti, *IEEE Transactionson Electron Devices*, 54: 3369-3377, 2007.

- [24] B. Tian, C. Chen, J. Zhang, et al., "Structure and Electrical Characteristics of AlGaN/GaN MISHFET with Al2O3 thin film as both Surface Passivation and gate Dielectric", *SemicondSciTechnol*, 2011, 26: 085023.

- [25] T. Poiroux, M. Vinet, O. Faynot, J. Wildeiz, J. Lolivier, T.Ernst, B.Previtali, S.Delonibus, "Multiple Gate Devices :Advantages and Challenges", *Microelectronic Engineering*, vol.80, pp. 378-385, June 2005.

- [26] S. Oh, D. Monroe, JM. Hergenrother, "Analytic Description of Short channel effects in Fully Depleted Double Gate and Cylindrical Surrounding Gate MOSFETs", *IEEE Transactions on Electron Devices*, vol. 21, no. 9, pp. 445-447, September 2000.

- [27] D.Chanemougame, "Conception et fabrication de nouvelles architectures MOS étude Du transport dans les canaux de conduction ultra minces obtenus avec la technologie SON' thèse de doctorat", L'Institut national des sciences appliquées de Lyon, Décembre, 2005.

- [28] J. S. Martin, "Étude par simulation Monte- Carlo d'architectures de MOSFET ultracourts à grille multiple sur SOI", Thèse de Doctorat, *Université Paris XI Orsay*, France, 2005