# Implementation of a Wireless ECG Acquisition SoC for IEEE 802.15.4 (ZigBee) Applications

Liang-Hung Wang, Member, IEEE, Tsung-Yen Chen, Kuang-Hao Lin, Member, IEEE, Qiang Fang, Member, IEEE, and Shuenn-Yuh Lee, Member, IEEE

Abstract—This paper presents a wireless biosignal acquisition system-on-a-chip (WBSA-SoC) specialized for electrocardiogram (ECG) monitoring. The proposed system consists of three subsystems, namely, 1) the ECG acquisition node, 2) the protocol for standard IEEE 802.15.4 ZigBee system, and 3) the RF transmitter circuits. The ZigBee protocol is adopted for wireless communication to achieve high integration, applicability, and portability. A fully integrated CMOS RF front end containing a quadrature voltage-controlled oscillator and a 2.4-GHz low-IF (i.e., zero-IF) transmitter is employed to transmit ECG signals through wireless communication. The low-power WBSA-SoC is implemented by the TSMC 0.18- $\mu$ m standard CMOS process. An ARM-based displayer with FPGA demodulation and an RF receiver with analog-to-digital mixed-mode circuits are constructed as verification platform to demonstrate the wireless ECG acquisition system. Measurement results on the human body show that the proposed SoC can effectively acquire ECG signals.

Index Terms—ARM-based platform, RF transceiver, SoC design, wireless ECG detection, ZigBee baseband spreading technique.

#### I. Introduction

R APID economic and industrial development increase intensity in daily life which results. such as nervousness, anxiety, and melancholy [1]. These emotions, along with rapid lifestyle changes, result in the development of chronic cardiovascular diseases [2], which are one of the leading causes of major adult illnesses after infectious diseases [3].

Several products that aim to diagnose cardiovascular diseases have been developed in the market. For instance, BioSenseTeK promoted the EP-2000 [4], a PC-based 12-lead ECG acquisition device. North-Vision has also launched the Prince 180B [5], and

Manuscript received September 3, 2013; revised December 16, 2013 and February 14, 2014; accepted March 3, 2014. Date of publication March 11, 2014; date of current version December 30, 2014. This work was supported in part by the Chip Implementation Center (CIC) and the National Science Council (NSC) of Taiwan under Grants NSC101-3113-P-006-025, NSC102-2220-E-006-020, and NSC102-2221-E-006-289-MY3, respectively.

- L. H. Wang and S. Y. Lee are with the Electrical Engineering Department, National Cheng Kung University, Tainan, 70101, Taiwan (e-mail: eetommy@mail2000.com.tw; ieesyl@mail.ncku.edu.tw).

- T. Y. Chen is with the Electrical Engineering Department, National Chung Cheng University, Chia-Yi 62102, Taiwan (e-mail: 98yancy@cbic.ee.ncku.

- K.-H. Lin is with the Electrical Engineering Department, National Formosa University, Yunlin 632, Taiwan (e-mail: khlin@nfu.edu.tw).

- Q. Fang is with the Electrical and Computer Engineering, RMIT University, Melbourne, Australia (e-mail: john.fang@rmit.edu.au).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org

Digital Object Identifier 10.1109/JBHI.2014.2311232

IMEC has demonstrated an integrated ECG monitoring system with RF and digital signal processing capability [6]. All the above products are targeted on medical-grade ECG signal acquisition and processing capability. In addition, many studies have used the Bluetooth technology to build the ECG signal transmission network infrastructure.

System-on-a-chip (SoC) is a mainstream device because of its smaller device size, lower power consumption, and lower cost features, in which entire circuits, including digital mixedmode (MM) signals and RF components, are integrated into a single piece of silicon [7]. The SoC developed for the body sensor network (BSN) intends to bring healthcare closer from the hospital to the patients, allowing biosignal monitoring to be conducted daily than limiting it within the clinical environment. In recent years, some wireless technologies are adopted for BSN application, such as the low-power radio frequency identification (RFID) technology [8]. These networks are also used for wireless personal area networks for the IEEE 802.15.4 standard (i.e., ZigBee applications) [9], [10]. BSN is predicted as the next homecare platform because of its significant potential as a low-cost high-patient-safety medical device [11].

Yang et al. [12] proposes the prototype of a biopatch with integrated low-power SoC. The SoC features the programmable gain and bandwidth for ECG detection, containing a three-stage front-end circuit, an 8-bit successive-approximation-register analog-to-digital converter (SAR-ADC), and a digital core. The SoC is integrated into a biopatch prototype without wireless transmission. Khayatzadeh et al. [13] presents a fully integrated wireless ECG SoC applied in a wireless body sensor network. The SoC includes a two-channel ECG front-end with an 8-bit SAR-ADC, a simple microcontroller and a SRAM, and a medical implantation communication service band RF-transceiver with binary frequency-shift keying and on-off keying (OOK) modulation for uplink and downlink transmissions, respectively. Yan et al. [14] proposes a low power highly sensitive ECG monitoring SoC where it is designed and implemented into a poultice-like plaster sensor for wearable cardiac monitoring. The SoC includes, four reconfigurable electrode front-ends, a differential sinusoidal current generator for balanced current injection, a digital module with finite state machine controller and SRAM data storage, and a cm-range 13.56-MHz fabric inductor coupling OOK remote communication. The SoCs implemented by both Khayatzadeh and Yan are customized as an application-specific integrated circuit (ASIC) with simple FSK and OOK wireless transmission. However, this paper presents a standard-based wireless solution (ZigBee) which has low-power consumption, low cost, high-node density, simple protocol, and long-distance communication [9]. Moreover, the spreading

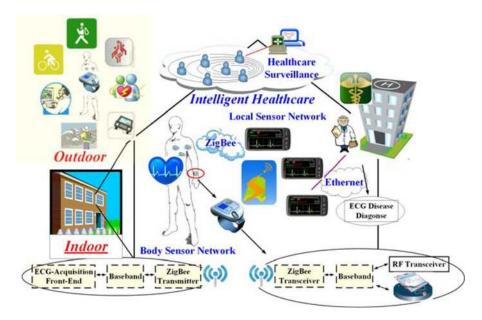

Fig. 1. Interactive intelligent healthcare and monitoring system.

technique with offset quadrature phase shift keying (O-QPSK) is adopted to decrease the noise interference.

The main contributions of the presented research are the detailed descriptions for the integrated circuit design and the measured results have revealed the achievement, different from our previous works [15] that employ an ECG acquisition module (without on-chip) and RF integrated circuits (ICs). This paper presents the first SoC with the IEEE 802.15.4 standard for wireless ECG acquisition, and aims to develop a wireless biosignal acquisition system-on-a-chip (WBSA-SoC), with on-chip ECG acquisition circuits, a baseband processor, a mixed-mode interface, and an RF transmitter, as well as an ARM-based receiver platform, to demonstrate the wireless ECG acquisition system. It makes a wearable device, but not a protocol evaluation board, to be possible in the future. The ARM-based receiver is intended for telemedical healthcare monitoring, in which, 1) the WBSA-SoC consists of an RF front-end circuit, a ZigBee transmitter baseband, and an analog front-end (AFE) circuit; and 2) the ARM-based receiver platform is constructed from an RF receiver, MM circuits, and a demodulator implemented in the FPGA with an ARM-based displayer. The rest of the paper is organized as follows. Section II presents the system architecture in personal health monitoring. Section III describes the circuit implementation of the wireless ECG acquisition system. Section IV presents the measurement results of system integration and the discussion. Section V concludes the study.

# II. SYSTEM ARCHITECTURE IN PERSONAL HEALTH MONITORING

An interactive intelligent healthcare and monitoring system (IIHMS) [8] (see Fig. 1) is proposed to enhance the portability of home telecare system. The IIHMS includes a BSN and a local sensor network (LSN). The BSN is the medium of communication between the acquisition auxiliaries and the wearable device

Fig. 2. Data flowchart of ECG detection for intelligent healthcare monitoring.

(e.g., watch). The auxiliary with electrical leads and WBSA-SoC are responsible for ECG signal acquisition. The LSN is the intermediate medium between the wearable device and the portable facility (e.g., mobile phone and personal digital assistant) for simple data analysis.

Fig. 2 shows the data flow of ECG signal detection for the intelligent healthcare monitor. The ECG signal is acquired by

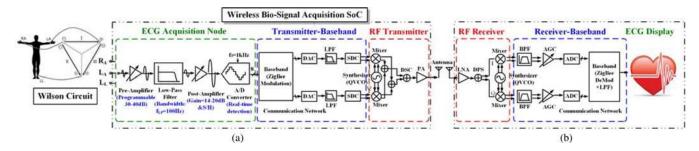

Fig. 3. (a) Block diagram of the proposed WBSA-SoC, and the (b) wireless receiver for ECG monitoring.

the WBSA-SoC. The SNR of the ECG data is improved via the ZigBee spreading technique after signal digitization. The ECG data are both demodulated and verified. If the data are correct, the ECG waveform will be displayed through the wearable device. The data are also encrypted to ensure highest confidentiality before transmittal to the portable facility. The LSN supplies the surveillance service, including data analysis and healthcare monitoring, via the ECG server and health center, respectively. Illness diagnosis is also an important service by the doctor node in the LSN.

# III. CIRCUITS IMPLEMENTATION OF WBSA-SOC AND RECEIVER PLATFORM

In this paper, the ECG acquisition circuits, a transmitter-baseband processor, and an RF front-end transmitter are used to coordinate with the low-power high-integration WBSA-SoC. The WBSA-SoC is responsible for acquiring feeble ECG signals perceived from the electrode leads [16]. The system block diagram is shown in Fig. 3(a). A real-time ECG data receiver is integrated on the board to receive and display the physical signals controlled by the ZigBee firmware. These physical signals include those from RF receiver circuits, the analog-to-digital MM interface, the demodulator implemented by FPGA, and the ARM-based displayer [see Fig. 3(b)]. The detailed circuits are described in the subsequent sections.

#### A. ECG Acquisition Node

The ECG signals obtained are translated by Wilson resistors. Aside from the Wilson resistors, the AFE circuits integrate several components, including a programmable gain preamplifier (PGA), a low-pass filter (LPF), a postamplifier (PostAmp), and an analog-to-digital converter (ADC) [7]. The detailed circuit implementations are as follows:

- 1) Programmable Gain Preamplifier: The structure of the differential difference amplifier (DDA) [17] is used for the first stage of the preamplifier (PreAmp). The proposed closed-loop PreAmp comprises a DDA amplifier and a PGA to determine the functionality of the variable gain. The output gain of the PGA circuits is adjusted through the ratios of capacitance  $C_i$  and  $C_f$  [7], which are placed on the dc feedback path. The gain can be programmed between 30 to 40 dB.

- 2) Fourth-Order Butterworth LPF: The large magnitude of the cardiogram R and T waves can be adopted to detect cardiac diseases [18]. Therefore, an LPF with fourth-order But-

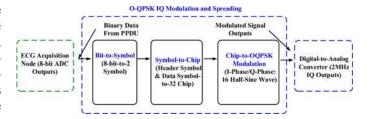

Fig. 4. Block diagram of the modulation functions.

terworth topology behind the PreAmp is provided to decrease the out-of-band high-frequency noise. The ladder structure [7], including resistors and inductors, can be substituted with operational transconductance amplifiers in the form of a gyrator by component replacement [19].

- 3) Second-Stage PostAmp: Given the gain attenuation of the LPF and the gain-amplifying insufficiency of the PreAmp, the second-stage PostAmp is used for the dynamic-range requirement of ADC behind the PostAmp [7].

- 4) 8-bit Successive Approximation ADC: Using the high-speed ADC to digitize the ECG signal in physiology examination is unnecessary because the bandwidth of the biosignal is below 250 Hz [16]. An 8-bit successive approximation (SA)-ADC with 1-kHz sampling frequency is used to digitize the ECG signal [7]. The digital-to-analog converter (DAC) structure with a binary searching algorithm not only dominates the accuracy of the digitization but also influences the operation speed of the SA-ADC.

#### B. Transmitter-Baseband Processor

The IEEE 802.15.4 specification provides the worldwide standard, operated in an unlicensed 2.4-GHz ISM band. The O-QPSK modulation with chip rate and data rate of 2 MHz and 250 kbps, respectively, is used to determine the transmitter-baseband protocol of the proposed WBSA-SoC. The MM circuits are the interface between the ZigBee digital processor and the RF front-end circuits, including a DAC, an LPF, and a single-end to differential converter (SDC) to convert the in-phase (I-phase) and quadrature-phase (Q-phase) signals into quadrature signals.

1) ZigBee Modulation and Spreading Technique: The ZigBee physical layers (PHYs) in the 2.45-GHz band utilize 16-ary quasi-orthogonal modulation. Four data bits are selected from one of the 16 nearly orthogonal pseudorandom noise (PN) sequences [9]. Fig. 4 shows that the corresponding modulation

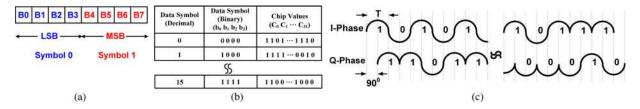

Fig. 5. (a) Bit-to-symbol mapping; (b) table of symbol-to-chip mapping; (c) samples of I-phase and Q-phase chip sequences with pulse shaping.

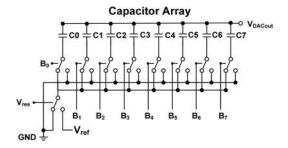

Fig. 6. Schematic of an 8-bit capacitor array DAC.

and spreading techniques of the PHYs are bit-to-symbol, symbol-to-chip, and chip-to-O-QPSK carrier.

The digitized data converted from the SA-ADC of the WBSA-SoC are parallel 8-ary binary codes, which are mapped into two data symbols, such as the 4-bit least significant bit  $(B_0, B_1, B_2, B_3)$  symbol and the 4-bit most significant bit  $(B_4, B_5, B_6, B_7)$  symbol. The symbol segments are compliant with the PHY protocol data unit (PPDU) encoding specification. Fig. 5(a) shows the PPDU data symbols. Each octet data is processed beginning at the preamble bit and ending at the last PHY service data unit bit.

Each data symbol is spread into 32-chip PN sequences by using the mapping table according to the ZigBee protocol [9]. The simple mapping table is illustrated in Fig. 5(b). The chip sequences are modulated onto the carrier to employ the O-QPSK with half-sine pulse shaping. Moreover, the I-phase and Q-phase modulation carriers are constructed from the even-indexed and odd-indexed 32-chip PN sequences, respectively. Fig. 5(c) shows the pulse shaping of the I-phase and Q-phase. The Q-phase is delayed by 90° from the I-phase. The formula for half-sine pulse shaping is derived by using

$$p(t) = \begin{pmatrix} \sin\left(\pi \frac{t}{T}\right), & 0 \le t \le T\\ 0, & \text{otherwise} \end{pmatrix}$$

(1)

where T is the period of each half-sine pulse shaping.

2) MM Circuits: MM circuits are responsible for translating digitized data into analog signals so that the modulated data can be transmitted via wireless transmission.

Capacitor-Based DAC: The DAC converts an abstract finite-precision time series data (i.e., fixed-point binary number) into a continually varying physical quantity (e.g., a voltage). The capacitor-based DAC (see Fig. 6) uses an op-amp-free capacitor array to implement a low-power DAC circuit. The output voltage

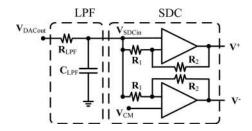

Fig. 7. Schematic of an LPF and an SDC.

with a binary-weighted capacitor array is derived by using

$$V_{\text{out}} = V_{\text{ref}} \frac{C_i + \sum_{j=i+1}^8 B_j C_j}{C_{\text{total}}}$$

(2)

where  $V_{\rm ref}$  and  $V_{\rm res}$  are the DAC output swing and the dc offset voltage, respectively;  $C_{\rm total}$  is the total capacitance of the DAC; the parameter i ranges from 0 to 7, corresponding to the 8-bit DAC.

The unit capacitor  $C_0$  is designed to be as small as possible to minimize power consumption. However, this capacitor will be traded off with the mismatch in layout caused by process variation and the switch thermal noise in the switched-capacitor circuits. A metal–insulator–metal capacitor of 100 fF with a common-centroid matching skill has been used to tradeoff between power consumption and noise contribution. The other capacitors,  $C_1$  to  $C_7$ , are multiples of  $C_0$  and are arranged in parallel for better placement, thus avoiding matching errors.

*LPF and SDC:* Given that the output of the capacitor-based DAC resembles a staircase, an LPF is required to smoothen the waveform. An SDC is also used to provide gain and differential output for the mixer requirement. The detailed circuits are shown in Fig. 7.

### C. RF Transceiver

An RF transmitter, including a fully differential up-conversion mixer, a two-stage power amplifier, and a quadrature voltage-controlled oscillator (QVCO), is implemented and integrated in WBSA-SoC for the ZigBee system. A low-power zero-IF RF receiver, including a current-reused low-noise amplifier (LNA) and a folded-cascode down-conversion mixer, is also utilized to receive ECG signals by wireless communication according to the IEEE 802.15.4 standard. The details of the circuits are described subsequently.

1) RF Transmitter: The RF transmitter [15], which is used to convert the baseband signals to RF carrier for wireless transmission, is located behind the MM circuits of the WBSA-SoC. The quadrature baseband signals are converted into differential RF

signals by using the proposed up-conversion mixer. Circuit linearity results in interference in the adjacent channel; therefore, the technique of the multitanh circuit is employed to improve linearity. The common-source amplifier with two-stage cascade structures is utilized in the power amplifier to improve conversion gain and to enhance the isolation between the output and input stages. The differential pair with an active current mirror is used as an active RF-balun to transform the differential output of the up-mixer into the single-ended input of the power amplifier.

The QVCO with subharmonic and injection-locked (SHIL) techniques is applied for I/Q channel digital communication to generate quadrature outputs (0°, 90°, 180°, and 270°). The NMOS and PMOS cross-coupled pair transistors with current-reuse technique are used in the proposed SHIL-QVCO [20] to save half of the dc current and to enhance the conversion gain under the push–pull operation. NMOS frequency-doubled differential pairs provide double resonant frequency injection into the NMOS and PMOS cross-coupled pairs to lock the quadrature phase. Instead of using the traditional transformer-coupling [21], the proposed SHIL-QVCO can be used to save chip area.

2) RF Receiver: The architecture of direct conversion (i.e., zero-IF) is widely used in RF receivers because it does not require off-chip components to eliminate an image signal. The proposed current-reused folded RF receiver consists of a single-ended LNA, a current-reused differential power splitter (DPS), and the folded structure quadrature mixer [15]. The DPS not only provides conversion gain but also acts as an SDC between the LNA and the quadrature mixer.

With regard to power gain, the gain efficiency of the proposed LNA can be increased by biasing the transistors in the subthreshold region. In this paper, a DPS circuit [15] stacked on the single-ended LNA for current reuse is directly implemented without extra power consumption. According to the Friis equation [22], the thermal noise of a mixer can be sufficiently suppressed by the LNA and DPS with high conversion gain. Moreover, the flicker noise can be reduced simultaneously because of its large transistor size in the subthreshold region.

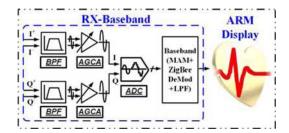

### D. Receiver Baseband and ARM-Based Displayer

The receiver baseband is divided into two parts 1) the analog-to-digital MM board, which is constructed with bandpass filter (BPF) circuits, an automatic gain-controlled amplifier (AGCA), and a 10-bit ADC; and 2) the O-QPSK digital demodulation implemented in FPGA and ARM-based displayer for demonstrating the ECG waveform. The system block diagram of the receiver baseband is shown in Fig. 8, and the details of the circuit integration are described subsequently.

1) Analog-to-Digital MM Board: BPF is employed as the first stage of the MM circuits to reject out-of-band noise, which is implemented by a second-order high-pass filter with bandwidth of 30 kHz combined with a first-order LPF with bandwidth of 280 kHz. The BPF is used not only to amplify the tiny quadrature baseband signal but also to convert the differential

Fig. 8. Block diagram of RX-baseband circuits.

input to the single-ended output. An AGCA is used behind the BPF to satisfy the dynamic voltage of an ADC. The IA model, INA217, which has low dc supply voltage and wide operation bandwidth, is suitable to function as the required AGCA.

The ADC selected in the MM board should have low dc supply voltage, low power consumption, and high bit resolution. The AD9201 with a dual channel and a 10-bit resolution is used to provide the quadrature I/Q channels for digital communication. The rising and falling edges of the clock in ADC are applied to convert the I-phase and Q-phase signals to the digital codes simultaneously.

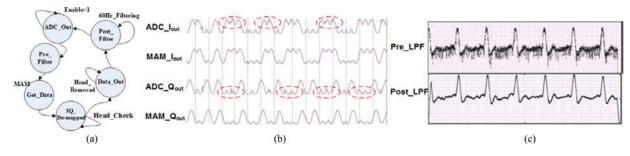

2) O-QPSK Digital Demodulation: Both dual 10-bit I/Q channel digitization codes are demodulated in FPGA. Fig. 9(a) shows the procedures of the digital demodulation. The digitized data with noise interference are precisely converted from the ADC circuits and stored in the registers embedded in the FPGA. The data prefiltered before the I/Q chips are demapped. A conventional moving average method (MAM) is also used to modify the waveform distribution and to enhance data identification. Fig. 9(b) shows the analog waveform at the output of the ModelSim simulator with AD9201 (i.e., ADC\_I<sub>out</sub> and ADC\_Q<sub>out</sub>). High noise interference is injected into the I/Q half-sine pulse shaping [see Fig. 9(b)]. However, according to the filtering and MAM technique, the I/Q waveform can be exactly recovered (i.e., MAM\_I<sub>out</sub> of MAM\_Q<sub>out</sub>) and demapped as I/Q chip values, as shown in Fig. 5(c).

The configuration of the I/Q chip values includes a leading header and the ECG data. The MM board with a LabView simulator is used to preverify the demodulation in the FPGA. Through the LabView simulator, the demodulation data without header data can demonstrate the ECG waveform [see Fig. 9(c)]. Given the 60-Hz instrument noise interference, a 256-tap finite impulse response LPF is adopted to filter the 60-Hz noise. The ECG signals at the Pre\_LPF and Post\_LPF outputs in Fig. 9(c) describe the ECG waveform with and without 60-Hz noise interference, respectively. The ECG signal can be further processed by digital signal processing in software [23] or hardware [24] to realize the anomaly detection, feature extraction, or classification.

## IV. EXPERIMENTAL RESULTS AND DISCUSSION

The proposed low-power high-integration WBSA-SoC, including the ECG acquisition node, a transmitter-baseband digital I/Q modulator, and an RF front-end transmitter, is

Fig. 9. (a) Procedure of IQ demodulation, (b) data out of ADC\_IQ and MAM\_IQ, and (c) ECG output of Pre\_LPF and Post\_LPF.

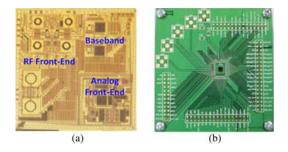

Fig. 10. (a) Chip microphotograph and (b) daughter board of WBSA-SoC.

Fig. 11. Measurement results of AFE circuits on an actual human body.

implemented in the TSMC 0.18- $\mu$ m standard CMOS process, moreover, the ASIC is the first full function SoC applied in wireless ECG detection in the word. The die area of the WBSA-SoC is 9 mm<sup>2</sup>, as shown in Fig. 10(a). The WBSA-SoC hollowed wire bond onto the PCB with gilding is used to replace the traditional ceramic package in ECG examination. The daughter board is shown in Fig. 10(b).

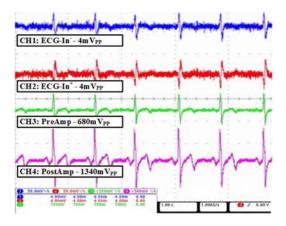

Fig. 11 shows the measurement results obtained by the AFE circuits during human-body ECG detection. The results are measured from each output node of the following AFE circuits: 1) the measured ECG waveform (see Fig. 11: ECG\_In^+/^-), which is the amplitude of the R-Wave and S-Wave interval (R–S interval, approximated to 4 mV $_{\rm R-S}$ ); 2) the output of the PGA and PostAmp. Fig. 11 shows the PreAmp and PostAmp, whose amplitudes of the R–S interval are approximately 680 and 1340 mV $_{\rm R-S}$ , respectively. The corresponding conversion gains are 44.6 and 50.5 dB, respectively.

Fig. 12. (a) I/Q modulation waveform recovered by logic analyzer and MATLAB simulators; the (b)  $90^{\circ}$ -phase difference between I-phase and Q-phase.

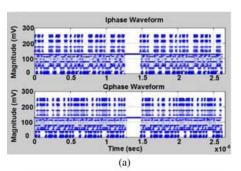

The Agilent 16901A logic analyzer is used to measure the dual I/Q channel modulation data converted from the ADC of WBSA-SoC. Moreover, the MATLAB simulator is used to recover the digitized data as analog signals. Fig. 12(a) shows the half-sine pulse shaping of the I/Q-phase dual channels. The phase difference between the dual channels (I-phase leading Q-phase 90°) is fitted in the ZigBee specification [8]. Fig. 12(b) illustrates the O-QPSK digital modulation. According to the measured results, the current consumption of analog front-end and digital I/Q channels are 0.74 and 0.29 mA, respectively, under the supply voltage of 1.8 V.

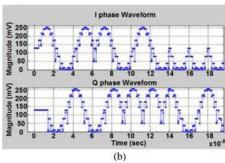

The DAC is applied to translate the O-QPSK modulation codes into analog signals. Fig. 13(a) shows the I/Q-phase modulation waveforms converted from the DAC circuits of WBSA-SoC. Fig. 13(b) shows the measured differential modulated waveform of the I-phase (I<sup>+</sup> and I<sup>-</sup>). Furthermore, the four quadrature signals of the I/Q channels (I<sup>+</sup>, I<sup>-</sup>, Q<sup>+</sup>, and Q<sup>-</sup>) are injected into the up-conversion mixer and mixed with the local oscillation frequency provided by the proposed QVCO.

Fig. 13. (a) Outputs of AFE circuits and DAC; (b) the I-phase differential waveform of DAC outputs.

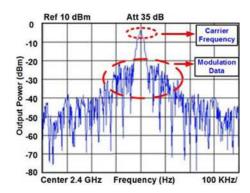

Fig. 14. Transmitter output power measured with a power spectrum analyzer.

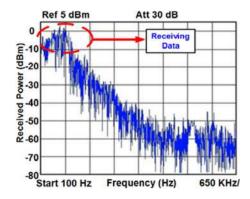

The transmission power of the RF transmitter of WBSA-SoC is measured by using a power spectrum analyzer, as illustrated in Fig. 14, in which the carrier frequency and data bandwidth are 2.4 GHz and 200 kHz, respectively. The current consumption of MM circuits and RF-transmitter are 0.69 and 19.38 mA, respectively, under the supply voltage of 1.2 V. Therefore, the total current consumption of WBSA-SoC neglecting regulator circuits is 21.1 mA. Fitted with two 605 mAh PR44 zinc-air batteries, the WBSA-SoC can be operated for over 2 days. Fig. 15 describes the received power spectrum with I/O channel modulation data from the down-conversion mixer of the RF receiver under 15 cm distance in the air. The data curve decreases slowly and significantly until the frequency band becomes larger than 2.6 MHz. The highest amount of data is obtained theoretically in the range 150 to 750 kHz, where the scale of the x-axis of the power spectrum analyzer is 650 kHz.

Fig. 15. Received signal power measured by using a power spectrum analyzer.

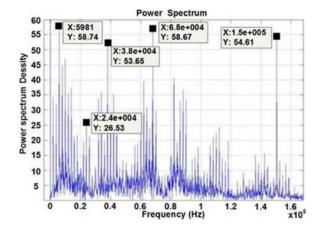

Fig. 16. Spectrum of the received data processed with a MATLAB simulator.

Fig. 17. Received data for pre-BPF and post-BPF.

To observe the data distribution, the MATLAB simulator with fast Fourier transform algorithm is applied to translate the received data from the time domain to the frequency domain. Fig. 16 shows that the bandwidth of the modulation data is less than 250 kHz, and the data distributed beside the 250 kHz are harmonic signals and high frequency interference.

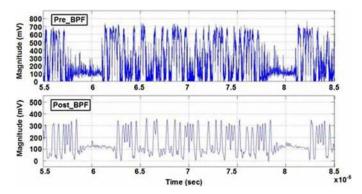

The BPF behind the RF down-conversion mixer is utilized not only to filter high-frequency noise but also to block the dc feedback punched through the RF receiver. Fig. 17 shows the modulation data with or without high-frequency interference (Pre\_BPF/Post-BPF). This figure reveals that the signal is clear with the BPF in place.

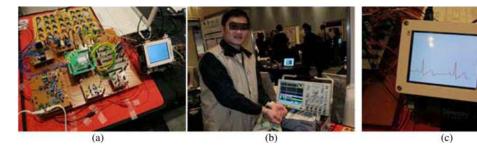

Fig. 18. (a) Experiment environment setup; (b) measurement result by an actual human body; (c) ECG biosignal display in the ARM-based displayer.

ECG detection is implemented in the WBSA-SoC daughter board, which is mounted on the fully integrated motherboard [see Fig. 18(a)]. The human-body ECG acquisition signal is translated from the Wilson resistors with electric patches stuck on the right wrist, left wrist, and left ankle. The oscilloscope is used to preshow the ECG signal in each output of the AFE circuits, including the automatic gain-controlled PreAmp and PostAmp. The human ECG detection is illustrated in Fig. 18(b). Once the ECG signal is acquired and digitized, the data are modulated and transmitted by the proposed WBSA-SoC. If the radiation carrier is received from the ARM-based receiver platform, the signals are processed by the MM circuits with amplification and digitization, the FPGA with demodulation, and the ARM-based display. Fig. 18(c) shows the ECG waveform presented by the ARM-based displayer.

The ECG experiment is validated by applying several types of daughter boards for auxiliary system integration. In this setup, 1) a bias board instead of a power supply provides all the required dc voltage of the system, and the bias circuits can be designed and integrated into the SoC in the future; 2) an off-chip clock generator provides the baseband and ADC operation frequency; 3) the level shifter and digital buffer are integrated into the motherboard to isolate the high voltage into the WBSA-SoC and to enhance the driving capability between ADC and digital modulation, respectively.

The ECG data demonstration with wireless transmission has poor reliability between the RF transmitter and receiver circuits because the noise and interference are significant during data transmission in the air. For future investigations, two approaches can be adopted to enhance the reliability of the WBSA-SoC: 1) modify the RF circuits with respect to noise isolation and increase the gain efficiency for high noise rejection; 2) use the multilayer PCB with noise shielding to improve wireless transmission.

# V. CONCLUSION

This paper presents an IIHMS, including a BSN and a local sensor network. The WBSA-SoC for BSN application is adopted to acquire actual human-body ECG signals via the IEEE 802.15.4 ZigBee network communication. The high-integration WBSA-SoC, including an ECG acquisition node, a transmitter-baseband processor with ZigBee protocol, an MM interface, and an RF transmitter, is implemented in the TSMC 0.18- $\mu$ m standard CMOS process. In addition, an ARM-based receiver platform, which includes an RF receiver, an analog-to-digital MM board, an O-QPSK digital demodulation implemented in

FPGA, and an ARM-based display, is adopted to demonstrate the wireless ECG communication. According to the actual human ECG measurement results, the ECG signals can be acquired and transmitted by using the proposed WBSA-SoC. Improving the data transmission of RF front-end circuits will enhance the noise resistance in wireless communication and increase the system performance.

#### ACKNOWLEDGMENT

The authors would like to thank the Chip Implementation Center, Taiwan, for its technical support and the Communication and Biologic Integrated Circuit Laboratory members for their assistance.

#### REFERENCES

- [1] E. C. Gullette, J. A. Blumenthal, M. Babyak, W. Jiang, R. A. Waugh, D. J. Frid, C. M. O'Connor, J. J. Morris, and D. S. Krantz, "Effects of mental stress on myocardial ischemia during daily life," *Amer. Med. As*soc., vol. 277, pp. 1521–1526, 1997.

- [2] A. Huang, C. Chen, K. Bian, X. Duan, M. Chen, H. Gao, C. Meng, Q. Zheng, Y. Zhang, B. Jiao, and L. Xie, "WE-CARE: an intelligent mobile telecardiology system to enable mHealth applications," *IEEE J. Biomed. Health Inf.*, vol. 18, no. 2, pp. 693–702, Mar. 2014.

- [3] Government Information Office, Taiwan. (2008). *The Republic of China Yearbook* [Online]. Available: http://www.gio.gov.tw/taiwan-website/5-gp/yearbook

- [4] BioSenseTek, (2003). [Online]. Available: http://www.biosensetek.com/

- [5] North-vision, (2004). [Online]. Available: http://www.north-vision.com/north-vision.htm

- [6] IMEC Scientific Report. (2010). Integrated wearable systems [Online]. Available: http://www.imec.be/ScientificReport/SR2010/ 2010/1159154.html

- [7] L. H. Wang, T. Y. Chen, S. Y. Lee, T. H. Yang, S. Y. Huang, J. H. Wu, K. H. Lin, and Q. Fang, "A wireless ECG acquisition SoC for body sensor network," in *Proc. IEEE Biomed. Circuits Syst. Conf.*, Nov. 2012, pp. 156– 159.

- [8] S. Y. Lee, L. H. Wang, and Q. Fang, "A low power RFID integrated circuits for intelligent healthcare systems," *IEEE Trans. Inf. Technol. Biomed.*, vol. 14, no. 6, pp. 1387–1396, Nov. 2010.

- [9] IEEE Standard Part 15.4: Wireless Medium Access Control (MAC) and Physical Layer (PHY) Specification for Wireless Personal Area Networks (WPANs), IEEE Sstandard 802.15.4–2003, 2003.

- [10] ZigBee Alliance, (2006). [Online]. Available: http://www.ZigBee.org

- [11] S. L. Chen, H. Y. Lee, C. A. Chen, H. Y. Huang, and C. H. Lou, "Wireless body sensor network with adaptive low-power design for biometrics and healthcare applications," *IEEE Trans. Syst. J.*, vol. 3, no. 4, pp. 398–409, Dec. 2009.

- [12] G. Yang, L. Xie, M. Mantysalo, J. Chen, H. Tenhunen, and L. R. Zheng, "Bio-patch design and implementation based on a low-power systemon-chip and paper-based inkjet printing technology," *IEEE Trans. Inf. Technol. Biomed.*, vol. 16, no. 6, pp. 1043–1050, Nov. 2012.

- [13] M. Khayatzadeh, X. Zhang, J. Tan, W. S. Liew, and Y. Lian, "A 0.7-V 17.4-µW 3-lead wireless ECG SoC," *IEEE Trans. Biomed. Circuits Syst.*, vol. 7, no. 5, pp. 583–592, Oct. 2013.

- [14] L. Yan, J. Bae, S. Lee, T. Roh, K. Song, and H. J. Yoo, "A 3.9 mW 25electrode reconfigured sensor for wearable cardiac monitoring system," *IEEE J. Solid-State Circuits*, vol. 46, no. 1, pp. 353–364, Jan. 2011.

- [15] T. H. Tsai, J. H. Hong, L. H. Wang, and S. Y. Lee, "Low-power analog integrated circuits for wireless ECG acquisition systems," *IEEE Trans. Inf. Technol. Biomed.*, vol. 16, no. 5, pp. 907–917, Sep. 2012.

- [16] J. G. Webster, Medical Instrumentation: Application and Design. New York, NY, USA: Wiley, 1995.

- [17] S. Y. Lee, C. J. Cheng, and M. C. Liang, "A low-power bidirectional telemetry device with a near-field charging feature for a cardiac microstimulator," *IEEE Trans. Biomed. Circuits Syst.*, vol. 5, no. 4, pp. 357–367, Aug. 2011.

- [18] J. D. Bronzino, The Biomedical Engineering Handbook, 2nd ed. Boca Raton, FL, USA: CRC, 2000.

- [19] S. Y. Lee and C. J. Cheng, "System design and modeling of a OTA-C filter for portable ECG detection," *IEEE Trans. Biomed. Circuits Syst.*, vol. 3, no. 1, pp. 53–64, Feb. 2008.

- [20] S. Y. Lee, L. H. Wang, and Y. H. Lin, "A CMOS quadrature VCO with subharmonic and injection-locked techniques," *IEEE Trans. Circuits Syst.-II: Brief Paper*, vol. 57, no. 11, pp. 843–847, Nov. 2010.

- [21] S. L. J. Gierkink, S. Levantino, R. C. Frye, C. Samori, and V. Boccuzzi, "A low-phase-noise 5-GHz CMOS quadrature VCO using superharmonic coupling," *IEEE J. Solid-State Circuits*, vol. 38, no. 7, pp. 1148–1154, Jul. 2003.

- [22] H. T. Friis, "Noise figure of radio receivers," Proc. IRE, vol. 32, pp. 419–422, Jul. 1944.

- [23] Z. Li, W. Xu, A. Huang, and M. Sarrafzadeh, "Dimensionality reduction for anomaly detection in electrocardiography: A manifold approach," in *Proc. Ninth Int. Conf. Wearable Implantable Body Sensor Netw.*, 2012, pp. 161–165.

- [24] X. Liu, Y. Zheng, M. W. Phyu, B. Zhao, and X. Yuan, "Multiple functional ECG signal is processing for wearable applications of long-term cardiac monitoring," *IEEE Trans. Biomed. Eng.*, vol. 58, no. 2, pp. 380–389, Feb. 2011.

**Kuang-Hao Lin** (M'11) received the B.S. and M.S. degrees in electronics engineering from Southern Taiwan University of Technology, Tainan, Taiwan, in 2001 and 2003, respectively, and the Ph.D. degree in electrical engineering from National Chung Hsing University, Taichung, Taiwan, in 2009.

In 2014, he joined the faculty of the Department of Electrical Engineering, National Formosa University, Yunlin County, Taiwan, where he is currently an Assistant Professor. He served as the SOC Technology Center of Industrial Technology Research In-

stitute from 2008 to 2009, and the Department of Electronic Engineering of National Chin-Yi University of Technology from 2009 to 2014. He has published more than 50 technical journal and conference papers. His research interests include digital signal processing, digital communications, baseband circuits design, and VLSI architectures design.

Qiang Fang (M'98) received the B.S. degree in applied physics from Tsinghua University, Beijing, China, in 1991 and the Ph.D. degree in biomedical engineering from Monash University, Melbourne, Australia, in 2000, respectively.

He joined RMIT University, Australia, in 2000 and is currently a Senior Lecturer in the School of Electrical and Computer Engineering, RMIT. His major research interests include intelligent and miniaturized medical instrumentation, wearable and implantable body sensor network and pervasive computing tech-

nologies applicable to healthcare delivery.

Liang-Hung Wang (M'13) was born in Tainan, Taiwan, in 1976. He received the B.S. and M.S. degrees in electrical engineering from the I-Shou University, Kaohsiung, Taiwan, in 2000 and 2003, respectively, and the Ph.D. degree from the Institute of Electrical Engineering, National Chung Cheng University (NCCU), Chia-Yi, Taiwan, in 2013.

He joined Fuzhou University, China in 2014 and is currently a lecturer in the Department of Microelectronic, College of Physics and Information Engineering. Since 2013, he has served as the educational

affairs of IEEE Solid-State Circuits Society Tainan Chapter. His present research activities involve the wireless biomedical circuits and systems integration including low-power low-voltage bio-signal acquisition system, digital modulation/demodulation and coding/decoding, RF transmitter and receiver, and RFID system applications.

Dr. Wang is a member of Circuits and Systems (CAS) Society, and Solid-State Circuits Society (SSCS) of IEEE.

Tsung-Yen Chen (S'09) was born in Kaohsiung, Taiwan, in 1983. He received the B.S. degree from the Chung Yuan Christian University, Taoyuan, Taiwan, in 2006, and the M.S. degree from the National Chi Nan University, Nantou, Taiwan, in 2009. He is currently working toward the Ph.D. degree at the Institute of Electrical Engineering, National Chung Cheng University, Chia-Yi, Taiwan.

His research interests include the low-power and low-voltage active radio-frequency (RF) front-end integrated circuits for biomedical application, and base-

band system for wireless communications.

Shuenn-Yuh Lee (M'98) was born in Taichung, Taiwan, in 1966. He received the B.S. degree from the National Taiwan Ocean University, Keelung, Taiwan, in 1988, and the M.S. and Ph.D. degrees from the National Cheng Kung University, Tainan, Taiwan, in 1994 and 1999, respectively.

He was an Associate Professor from 2006 and a Professor from 2011, respectively, at the Department of Electrical Engineering, National Chung Cheng University, Chia-Yi, Taiwan. He is currently a Professor at the Department of Electrical Engineering,

National Cheng Kung University, Tainan, Taiwan. He served as the Chairman of Heterogeneous Integration Consortium (HIC) under the VLSI Educational Program sponsored by Ministry of Education, Taiwan, from 2009 to 2011. He served as the Technical Program Chair (TPC) of the 2011 International Symposium on Bioelectronics and Bioinformatics (ISBB) and the 2013 IEEE International Conference on Orange Technologies (ICOT), and the Publication Chair for the 2012 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS). From 2013, he serves as the Chairman of IEEE Solid-State Circuits Society Tainan Chapter. His cuuurrent research activities involve the design of analog and mixed-signal integrated circuits including filter, high-speed ADC/DAC, and sigma-delta ADC/DAC, biomedical circuits and systems, low-power and low-voltage analog circuits, and RF front-end integrated circuits for wireless communications.

Dr. Lee now is a Member of Circuits and Systems (CAS) Society, Solid-State Circuits Society, and Medicine and Biology Society of IEEE.