## Santa Clara University Scholar Commons

**Electrical Engineering**

School of Engineering

1-27-1992

## Improved Crystalline Quality of $Si_{1-x}Ge_x$ Formed by Low-temperature Germanium Ion Implantation

Ken-Ichi Shoji

Akira Fukami

Takahiro Nagano

Takashi Tokuyama

Cary Y. Yang Santa Clara University, cyang@scu.edu

Follow this and additional works at: https://scholarcommons.scu.edu/elec Part of the <u>Electrical and Computer Engineering Commons</u>

## **Recommended** Citation

K. Shoji, A. Fukami, T. Nagano, T. Tokuyama, and C.Y. Yang, "Improved Crystalline Quality of Si<sub>1-x</sub>Ge<sub>x</sub> Formed by Low-temperature Germanium Ion Implantation," Applied Physics Letters 60, 451-453 (1992). https://doi.org/10.1063/1.106631

Copyright © 1992 American Institute of Physics Publishing. Reprinted with permission.

This Article is brought to you for free and open access by the School of Engineering at Scholar Commons. It has been accepted for inclusion in Electrical Engineering by an authorized administrator of Scholar Commons. For more information, please contact rscroggin@scu.edu.

## Improved crystalline quality of $Si_{1-x}Ge_x$ formed by low-temperature germanium ion implantation

Ken-ichi Shoji, Akira Fukami, and Takahiro Nagano Hitachi Research Laboratory, Hitachi, Ltd., 4026 Kuji, Hitachi-shi, Ibaraki 319-12, Japan

Takashi Tokuyama Institute of Applied Physics, University of Tsukuba, Tsukuba-shi, Ibaraki 305, Japan

Cary Y. Yang Microelectronics Laboratory, Santa Clara University, Santa Clara, California 95053

(Received 12 September 1991; accepted for publication 7 November 1991)

Improvement of crystalline quality in  $Si_{1-x}Ge_x$  formed by germanium ion implantation has been found. End-of-range defects were drastically reduced in number by lowering the substrate temperature during implantation with doses on the order of  $10^{16}$  cm<sup>-2</sup>. This improvement was confirmed by electrical characterization of *p*-*n* junctions formed in the SiGe layer as well as by transmission electron microscopy.

Formation of SiGe/Si heterostructures has been investigated by various researchers using techniques such as molecular beam epitaxy and ultrahigh vacuum chemical vapor deposition.<sup>1-6</sup> Recently, largely as a result of interests in developing silicon-compatible, high-performance hetero-bipolar technology, SiGe/Si heterostructures have been fabricated by high-dose Ge+ implantation.7-11 Lowdose Ge+ implantation is a well-established technique to form shallow p-n junctions in preamorphized Si substrates,<sup>12</sup> and is inherently compatible with standard silicon integrated circuit fabrication. However, high-dose Ge+ implantation introduces residual defects, which significantly degrade the crystalline quality.<sup>11</sup> The extent to which these defects affect the device performance is of interest to both materials scientists and device technologists. There are two kinds of defects in the recrystallized SiGe layer formed by Ge+ implantation and subsequent thermal annealing. One consists of misfit dislocations near the surface, while the other consists of dislocations due to residual damage at the interface between the recrystallized SiGe layer and Si substrate. The latter is known as "endof-range (EOR) defects." Reduction of EOR defect density has been achieved by lowering the substrate temperature during ion implantation.<sup>13-15</sup> In this letter, we present experimental results on  $\mathrm{Ge}^+$  implantation with doses on the order of  $10^{16}$  cm<sup>-2</sup> and substrate temperatures as low as -100 °C. Our results show improvements in the SiGe crystallinity and the p-n junctions characteristics.

Cross-sectional transmission electron microscopy (XTEM) was used to estimate the SiGe layer crystallinity. Germanium ions were implanted into *p*-type Si(100) through a thermally grown 10-nm oxide at an acceleration energy of 160 keV with a dose of  $5 \times 10^{16}$  cm<sup>-2</sup>. The peak germanium concentration was  $6 \times 10^{21}$  cm<sup>-3</sup>, which corresponds to a germanium content of 12 at. %. The Si substrate temperatures during ion implantation were set at -100 and 27 °C with liquid nitrogen and water as coolants, respectively. The beam current density was kept below 0.44  $\mu$ A/cm<sup>2</sup> during the implantation to eliminate the possibility of crystal regrowth due to beam heating. A tilt

angle of 7° was used for implantation. Implanted samples were then annealed in  $N_2$  at 700 °C for 8 h.

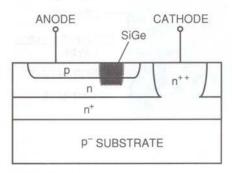

To evaluate the SiGe crystalline quality, a planar p-nstructure was fabricated using a standard bipolar process for collector junction formation. This structure is shown schematically in Fig. 1. Antimony was diffused into a ptype Si(100) substrate to form the  $n^+$  region using a twostep process with predeposition followed by drive-in. An undoped Si epitaxial layer was then grown, followed by phosphorus ion implantation to form the *n* region. A  $SiO_2$ overlayer was deposited, and diffusion windows were opened. Arsenic ions were implanted and a furnace anneal at 950 °C for 30 min was carried out to form the  $n^{++}$ region for metal contact. To form the p region, boron ions were implanted followed by a furnace anneal at 900 °C for 10 min. A SiO<sub>2</sub> overlayer was added again, and the Ge<sup>+</sup> implantation window was opened. Germanium ions were implanted through a thermally grown 10-nm oxide. Conditions for Ge<sup>+</sup> implantations were the same as those for the samples for XTEM observation. Then, a two-step anneal (700 °C for 8 h and 900 °C for 10 min) was carried out.

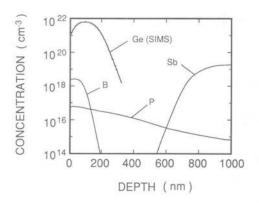

Figure 2 shows the concentration profile of germanium obtained from secondary ion mass spectroscopy (SIMS) and those of the dopants (antimony, phosphorus, and boron) obtained from process simulation. Comparing the SIMS data, the germanium profile of the -100 °C im-

FIG. 1. Schematic of diode geometry to evaluate SiGe crystalline quality.

FIG. 2. Concentration profile of Ge obtained from SIMS and those of B, P, and Sb obtained from simulation. The Ge profile is from a sample annealed at 700  $^{\circ}$ C for 8 h, followed by 900  $^{\circ}$ C for 10 min.

planted sample is found to be identical to the 27 °C implanted one. The junction depth is 150 nm, and the boron and phosphorus concentrations at the junction are about  $4 \times 10^{16}$  cm<sup>-3</sup>. The thickness of the *n* layer is 450 nm, with an average doping concentration of around  $10^{16}$  cm<sup>-3</sup>. The germanium content at the *p*-*n* junction is approximately 12 at. %, and the germanium distribution extends to the center of the *n* layer.

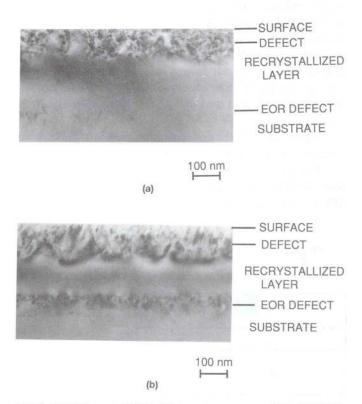

Figures 3(a) and 3(b) show XTEM photographs for the 700 °C annealed samples with implantations at -100and 27 °C, respectively. Two types of defects are observed. One is located near the surface and the other at the EOR. In either case, the surface defect region is about 100 nm deep. However, the surface defects in the -100 °C implanted sample do not extend as far as those in the 27 °C implanted sample. The EOR defects in the -100 and

FIG. 3. XTEM images of SiGe/Si heterostructures annealed at 700 °C for 8 h (a) -100 °C Ge<sup>+</sup> implantation, (b) 27 °C Ge<sup>+</sup> implantation.

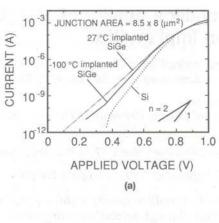

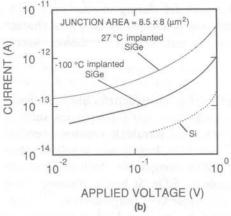

FIG. 4. Comparisons of current-voltage characteristics for diodes formed with -100 and 27  $^{\circ}\mathrm{C}$  Ge $^+$  implantations, and without Ge $^+$  implantation (a) forward bias, (b) reverse bias.

27 °C implanted samples are centered at about 310 and 280 nm from the surface, respectively, while the density as well as the extent of EOR defects in the low-temperature implanted sample are substantially less. From the profile shown in Fig. 2, the germanium concentration at the EOR for the -100 °C implanted sample is  $5 \times 10^{18}$  cm<sup>-3</sup>, whereas that for the 27 °C implanted one is  $10^{19}$  cm<sup>-3</sup>. Since the residual damage resulting from Ge<sup>+</sup> bombardment increases with local germanium concentration, this difference in concentration at EOR is consistent with the observed difference in defect density.

Figure 4 summarizes the results of the room-temperature, current-voltage measurements for three p-n junction diodes. For forward biases between 0.4 and 0.7 V [Fig. 4(a)], the Si control diode exhibits ideal characteristics as expected. The larger concentrations of recombination centers in the SiGe diodes lead to larger currents and smaller slopes than the Si control diode. This increase in recombination centers is due primarily to the EOR defects within the depletion region of the *p*-*n* junction. However, the current and ideality factor for the - 100 °C implanted diode are smaller than those for the 27 °C implanted one. The ideality factor of the former is 1.3, while that of the latter is 1.5. This confirms that reduction of EOR defects is achieved by lowering the substrate temperature during germanium ion implantation. Figure 4(b) compares reverse current-voltage characteristics for the three diodes up to a bias of 1 V. The breakdown voltages of the control, the

27 °C implanted, and the - 100 °C implanted diodes are 6.2, 5.9, and 6.5 V, respectively. Assuming a linearly graded junction model for each diode, these values are consistent with the doping concentrations shown in Fig. 2. The reverse current of the 27 °C implanted diode is about one order of magnitude larger than that of the Si control diode, while the reverse current of the -100 °C implanted diode is about half of the 27 °C implanted one. This reduction in generation current for the low-temperature implanted diode must be accompanied by an improvement in crystalline quality in the SiGe layer and near the SiGe Si substrate interface, as demonstrated by the XTEM observations shown in Fig. 3. Compared with the Si control device, the larger reverse current for the - 100 °C implanted diode may also be partially attributed to a narrower band gap in SiGe.

In summary, the density of EOR defects in the SiGe/Si heterostructure formed by Ge<sup>+</sup> implantation with doses on the order of  $10^{16}$  cm<sup>-2</sup> followed by thermal annealing is reduced by lowering the substrate temperature during ion implantation to -100 °C. This is verified by forward and reverse current–voltage characteristics of *p*-*n* junctions as well as by XTEM.

The authors would like to thank Dr. N. Momma for his encouragement throughout this work. Thanks are also due to S. Kawakami, K. Sukegawa, and the technical staff of Hitachi Research Laboratory for their contributions in the device fabrication.

- <sup>1</sup>J. W. Matthews and A. E. Blakeslee, J. Cryst. Growth 27, 118 (1974)

- <sup>2</sup>J. W. Matthews, J. Vac. Sci. Technol. 12, 126 (1975).

- <sup>3</sup>J. H. van der Merme, J. Appl. Phys. 34, 123 (1963).

- <sup>4</sup>B. S. Meyerson, Appl. Phys. Lett. 48, 797 (1986).

- <sup>5</sup>B. S. Meyerson, F. K. LeGoues, T. N. Nguyen, and D. L. Harame, Appl. Phys. Lett. **50**, 113 (1987).

- <sup>6</sup>B. S. Meyerson, K. J. Uram, and F. K. LeGoues, Appl. Phys. Lett. 53, 2555 (1988).

- <sup>7</sup>O. W. Holland, C. W. White, and D. Fathy, Appl. Phys. Lett. **51**, 520 (1987).

- <sup>8</sup>D. Fathy, O. W. Holland, and C. W. White, Appl. Phys. Lett. **51**, 1337 (1987).

- <sup>9</sup>K. Ohta, J. Sakano, and S. Furukawa, Extended Abstracts of 21st Conference on Solid State Devices and Materials, Tokyo, August, 1989 (unpublished), p. 555.

- <sup>10</sup>A. R. Srivasta, S. Sharan, O. W. Holland, and J. Narayan, J. Appl. Phys. 65, 4028 (1989).

- <sup>11</sup> A. Fukami, K. Shoji, T. Nagano, and C. Y. Yang, Appl. Phys. Lett. 57, 2345 (1990).

- <sup>12</sup> K. Kuriyama, S. Aoki, M. Satoh, and M. Nakano, Phys. Res. B 39, 397 (1989).

- <sup>13</sup>K. S. Jones and D. Venables, J. Appl. Phys. 69, 2931 (1991).

- <sup>14</sup>S. Prussin and K. S. Jones, J. Electrochem. Soc. 137, 1912 (1990).

- <sup>15</sup>T. Suzuki, H. Yamaguchi, S. Ohzono, and N. Natsuaki, Extended Abstracts of 22nd Conference on Solid State Devices and Materials, Sendai, August, 1990 (unpublished), p. 1163.