Open access · Journal Article · DOI:10.1109/TPEL.2011.2169993

# Improved Natural Balancing With Modified Phase-Shifted PWM for Single-Leg Five-Level Flying-Capacitor Converters — Source link 🗹

Steven Thielemans, Alex Ruderman, Boris Reznikov, Jan Melkebeek

Institutions: Ghent University

Published on: 01 Apr 2012 - IEEE Transactions on Power Electronics (IEEE)

Topics: Pulse-width modulation, Converters and Capacitor

Related papers:

- Modified Phase-Shifted PWM Control for Flying Capacitor Multilevel Converters

- Recent Advances and Industrial Applications of Multilevel Converters

- Natural Balancing of Flying Capacitor Voltages in Multicell Inverter Under PD Carrier-Based PWM

- Natural Capacitor Voltage Balancing for a Flying Capacitor Converter Induction Motor Drive

- Enhanced Voltage Balancing of a Flying Capacitor Multilevel Converter Using Phase Disposition (PD) Modulation

# Improved Natural Balancing with Modified Phase Shifted PWM for Single-Leg Five-Level Flying-Capacitor Converters

Steven Thielemans, *Member, IEEE, Alex Ruderman, Member, IEEE, Boris Reznikov and Jan Melkebeek, Senior Member, IEEE.*

Abstract-Flying capacitor converters (FCCs), as most multilevel converter topologies, require a balancing mechanism of the capacitor voltages. FCCs have the valuable property of natural voltage balancing when a special modulation technique is used. The classic methods, like Phase-Shifted Pulse Width Modulation (PS-PWM), result in very slow balancing for some duty ratio ranges. Previous work showed that for a single-leg five-level FCC one time constant is infinite for a zero desired output voltage. In this paper, a modified PS-PWM scheme for a single-leg fivelevel FCC is presented which results in faster balancing over the total duty ratio range. The modified PS-PWM scheme is studied, resulting in an averaged voltage balancing model. This model is verified using simulations and experiments. The modified PS-PWM scheme solves the slow balancing problems of the normal PS-PWM method for odd-level FCCs, while maintaining the passive control property, and it provides a self-precharge capability.

*Index Terms*—pulse width modulation, multilevel converters, capacitor voltage balancing, power converters

#### I. INTRODUCTION

Multilevel converters have several advantages over twolevel converters. A higher voltage handling is possible due to a series connection of switch components. The topologies also allow intermediate voltage levels to be applied, which results in a better approximation of the desired output voltage with lower harmonic distortion, [1]. Flying capacitor converters (FCCs) have several advantages over other multilevel topologies like neutral-point-clamped (NPC) and cascaded converters, [1], [2].

Most multilevel topologies require some kind of balancing of capacitor voltages to be able to construct the required output voltage levels. FCCs have the advantage that many redundant states are possible for the same output voltage. This creates possibilities to balance the capacitor voltages directly on a small term, like a PWM period. Other topologies, like NPC,

This work was supported by FWO projects G.0011.08 and G.0665.06 and by the Interuniversity Attraction Pole under Project (IUAP) P6/21. A. Ruderman and B. Reznikov gratefully acknowledge Elmo Motion Control and General Satellite Corporation management respectively for on-going support to advanced applied power electronics research support.

S. Thielemans and J. Melkebeek are with the Department of Electrical Energy, Systems and Automation of Ghent University, Belgium (e-mail: Steven.Thielemans@UGent.be; Jan.Melkebeek@UGent.be). A. Ruderman is with Elmo Motion Control Ltd., Petach-Tikva 49103, Israel (e-mail: arud-erman@elmomc.com). B. Reznikov is with General Satellite Corp., Russia (e-mail: ReznikovB@spb.gs.ru).

need a total fundamental period to balance the capacitors due to the lack of redundant switch states.

Two major types of balancing mechanisms for FCCs exist. The first mechanism is active balancing. Here, measurements are required to define the unbalance state and algorithms are able to find the appropriate switch state which creates the required output voltage and at the same time balance the capacitors, [3]-[6]. Besides the measurements and additional control effort, also the uneven switching loss distribution over the switches is a disadvantage. The second mechanism is particular for FCCs, as they have a natural balancing property. Using a special pulse width modulation (PWM), phase shifted PWM (PS-PWM), or a derivative of PS-PWM, a natural balancing of the capacitor voltages is obtained. Without any measurements or special control algorithms the capacitor voltages balance to the required values. This natural balancing mechanism was analyzed before in many papers, [7]-[13], mostly using frequency domain analysis.

Recent time domain analysis of the dynamics of the PS-PWM natural balancing, [14], [15], result in time constant equations which reveal large time constants, meaning poor voltage balancing dynamics, for some duty ratio (D) regions. It turns out that PS-PWM doesn't use the redundant switch states optimally in some duty ratio regions. The small stability margin of the voltage balancing, caused by the poor dynamics, results in an increased sensitivity to non-idealities (semiconductor switch voltage drops, deadtime, delays, etc.). In a practical setup, divergence of the capacitor voltage due to the non-idealities can occur for small duty ratios, as observed in [4]. To make FCCs with natural voltage balancing suitable for practical applications, the challenge is to design switching patterns (and corresponding modulation strategies) that assure convergence and fast natural voltage balancing dynamics. As an additional requirement the benefits of PS-PWM, the optimal voltage quality, the minimal switching losses and the uniform loss distribution over the switches, have to be sustained.

In this paper, a new PWM scheme, which results in better balancing properties than the normal PS-PWM, will be proposed and analyzed. A five-level FCC will be used, as this is the converter with the lowest level-count and suffering infinite time constants when applying PS-PWM. Simulations and experiments will verify the theoretical results from the time-domain analysis.

Manuscript received May 19, 2011; revised July 19, 2011. Accepted for publication September 10, 2011

# II. FIVE-LEVEL SINGLE-LEG FCC TOPOLOGY AND SWITCH STATES

# A. Five-level single-leg FCC topology

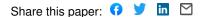

The topology of a five-level single-leg FCC is depicted in figure 1. The converter has four pairs of complementary controlled switches,  $(S_1, \overline{S_1})$ ,  $(S_2, \overline{S_2})$ ,  $(S_3, \overline{S_3})$  and  $(S_4, \overline{S_4})$ . These switches make it possible to connect the flying capacitors in series with the load. The load is represented here as an RL series connection, to simulate a simple inductive load. The flying capacitors,  $C_1$ ,  $C_2$  and  $C_3$  should be charged to their nominal voltages,  $V_{\rm DC}/4$ ,  $V_{\rm DC}/2$  and  $3V_{\rm DC}/4$  resp., to be able to construct the desired output voltages. To ensure the voltage stress over the switches is limited and the output voltage quality is acceptable, the capacitor voltages need to remain in the vicinity of the nominal voltages.

Figure 1: Topology of a single-leg five-level FCC.

The switch states can be represented by four digits corresponding with the switch pairs. A normal digit means the upper switch of the switch pair is closed, while an overlined digit means the bottom switch is closed. An overview of the possible switch states and their resulting output voltage  $V_{an}$ is given in table I.

#### B. Switch states and their circuit topologies

Applying a certain switch state results in a temporary circuit topology. The capacitors connected in series with the load in these circuits define, together with the DC-bus voltage, the voltage over the load. At the same time the voltages of these capacitors are altered by the load current which flows through these capacitors for a certain time.

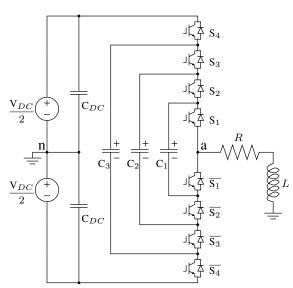

The six circuit topologies of a five-level FCC which result in a zero voltage over the load are depicted in figure 2. Switch states 1 ( $\overline{12}34$ ) and 2 ( $12\overline{34}$ ) can be considered as the inverse of each other, just as switch states 3 and 4 and switch states 5 and 6. The same current direction in these inverse circuits has an opposite effect on the capacitor voltages.

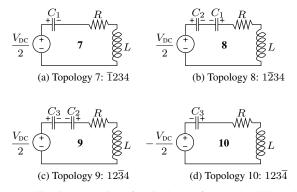

The four circuit topologies of a five-level FCC resulting in a load voltage of  $V_{\rm DC}/4$  are depicted in figure 3. The inverse

Table I: Switch states and the corresponding output voltages of a five-level single-leg FCC (when  $V_{C1} = V_{\rm DC}/4$ ,  $V_{C2} = V_{\rm DC}/2$  and  $V_{C3} = 3V_{\rm DC}/4$ )

| #  | switch state                 | $V_{an}$        |

|----|------------------------------|-----------------|

| 1  | $\overline{12}34$            | 0               |

| 2  | $12\overline{34}$            | 0               |

| 3  | $1\overline{23}4$            | 0               |

| 4  | $\overline{1}23\overline{4}$ | 0               |

| 5  | $\overline{1}2\overline{3}4$ | 0               |

| 6  | $1\overline{2}3\overline{4}$ | 0               |

| 7  | $\overline{1}234$            | $V_{\rm DC}/4$  |

| 8  | $1\overline{2}34$            | $V_{\rm DC}/4$  |

| 9  | $12\overline{3}4$            | $V_{\rm DC}/4$  |

| 10 | $123\overline{4}$            | $V_{\rm DC}/4$  |

| 11 | $1\overline{234}$            | $-V_{\rm DC}/4$ |

| 12 | $\overline{1}2\overline{34}$ | $-V_{\rm DC}/4$ |

| 13 | $\overline{12}3\overline{4}$ | $-V_{\rm DC}/4$ |

| 14 | $\overline{123}4$            | $-V_{\rm DC}/4$ |

| 15 | 1234                         | $V_{\rm DC}/2$  |

| 16 | $\overline{1234}$            | $-V_{\rm DC}/2$ |

Figure 2: Circuit topologies of a single-leg five-level FCC resulting in zero load voltage.

of these switch states results in a load voltage of  $-V_{\rm DC}/4$ and corresponds with switch states 11–14. The two remaining possible switch states, 15 and 16, which result in an output voltage of  $V_{\rm DC}/2$  and  $-V_{\rm DC}/2$  respectively, are created by closing all upper or all bottom switches (1234 and 1234). As no flying capacitors are connected in switch states 15 and 16, their voltages are not altered and they don't have any influence on the load voltage.

#### III. NATURAL BALANCING WITH PS-PWM

The most convenient way to control the capacitor voltages of an FCC is by using a modulation strategy which results in natural balancing. This passive control method doesn't need measurements and the control effort is low. To achieve natural balancing, all the switch pairs in a phase leg must

Figure 3: Circuit topologies of a single-leg five-level FCC resulting in a load voltage of  $V_{\rm DC}/4$ .

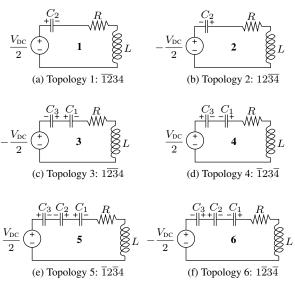

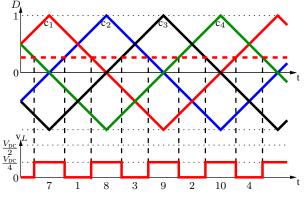

be controlled using the same duty cycle. Commonly this is implemented using the Phase Shifted PWM (PS-PWM), depicted in figure 4 for a five-level converter. Each switch pair has its own triangular carrier. The carriers are phase shifted over  $2\pi/(N-1)$  for an *N*-level converter. The normalized voltage command *D* (from -1 to 1), with  $V_{DC}/2$  as reference, is used to compare the carriers with. This results in the switch state for each switch pair. When *D* is above the carrier, the upper switch is closed and when below the carrier, the bottom switch is closed. The order of the carriers (here c<sub>1</sub>, c<sub>2</sub>, c<sub>3</sub>, c<sub>4</sub>, lead order) can be reversed to the lag order (c<sub>4</sub>, c<sub>3</sub>, c<sub>2</sub>, c<sub>1</sub>), without influencing the balancing time constants, [16].

PS-PWM for five-level single-leg FCCs was heavily analyzed before, mostly in the frequency domain, [7]-[9], [11]. Time domain analysis, [14]-[16], clarified that the voltage balancing is driven by the losses caused by current harmonics generated by the unbalance of the capacitors. All loss mechanisms influence the dynamics of the voltage balancing. In this study only the ohmic loss mechanism in the load is considered, but every additional loss mechanism speeds up the balancing dynamics, [17]. The time domain analysis of the voltage balancing of the flying capacitors results in closed form solutions of the time constants of the balancing dynamics. The obtained equations show the dependence on the system parameters (including load parameters) and D.

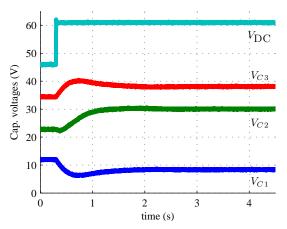

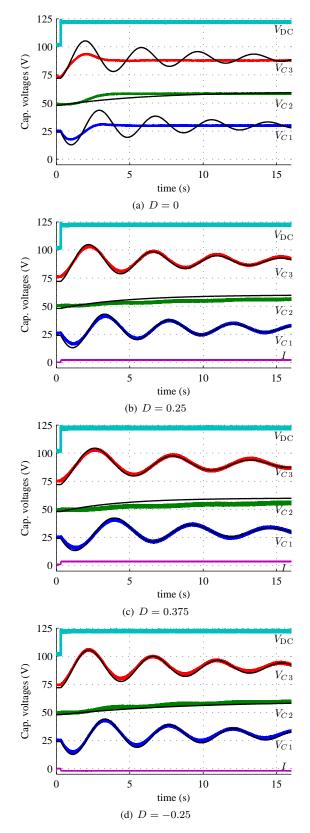

From the obtained time constant equations, it is possible to characterize some problematic aspects of natural balancing. The largest (and most significant) time constant, the aperiodic time constant, tends to infinity for some ranges of D. For a five-level converter for example, this is not only the case for ranges where the flying capacitors are not used (D close to 1 and -1), but also for D close to zero. As an example, the balancing after a DC-bus voltage step for PS-PWM with D = 0 is depicted in figure 5, using the experimental setup. As predicted by the theory, while capacitor  $C_2$  balances immediately, the voltages of capacitors  $C_1$  and  $C_3$  don't balance to their nominal values as the common-mode time constant of both capacitors is infinite.

When the balancing time constants increase (or approach infinity), the stability margin of the system becomes very small. In simulation, this still results in (slow) balancing. In practice, the slow balancing is unable to overcome the unbalancing influences of parasitic effects, nonlinearities and non-idealities

Figure 4: Carriers of PS-PWM for a five-level FCC.

Figure 5: Balancing with PS-PWM for a five-level FCC at D = 0 (experimental measurement).

(power switch voltage drops, deadtimes, finite rise and fall times, ...). To overcome these effects, the balancing has to be fast enough.

The switch state sequence for D = 0 is 1 - 3 - 2 - 4 (see figure 4). In [16] it is shown that the cause of this infinite time constant for D = 0 is found in the circuit topologies 1, 2, 3 and 4. It's clear from these topologies, see figure 2, that capacitors  $C_1$  and  $C_3$  are, for D = 0, always used as a pair and are always connected in an anti-series way. If capacitors  $C_1$ and  $C_3$  both have the same voltage deviation, it's impossible to balance it out, as this unbalance has no influence on the output voltage.

Besides this practical explanation, this can also be confirmed by theoretical reasoning. The balancing dynamics can be mathematically simplified by assuming  $V_{DC} = 0$ , ideal switches (no diodes) and charged flying capacitors. For a voltage balancing with non-infinite time constant, the charged capacitors have to balance to 0 V. This zero-solution should be the single steady state solution of the homogeneous system of linear equations, created by topologies in the sequence 1, 2, 3 and 4. The rank of this system (the number of independent equations in the base of the system) is only 2. As there are three variables, the three flying capacitor voltages, the system is underdetermined and there is more than one solution. The rank of the system of linear equations created by adding topologies 5 and 6 to the original system is three, equal to the number of variables. When all 0 V generating topologies are used in the sequence, there is only one unique solution, which is the zero solution and thus a completely balanced system.

## IV. NATURAL BALANCING WITH MODIFIED PHASE SHIFTED PWM

After a thorough analysis of the balancing aspects of a five-level single-leg FCC, it was found that all switch states resulting in zero output voltage are necessary to guarantee a fast balancing. Other aspects which should be met are:

- switch to the nearest levels to obtain the optimal voltage quality,

- consecutive switch states should differ only in the state of one switch (limit the switching losses),

- uniform distribution of the switching losses over the switch pairs.

• inverse states should be applied during equal time period These elements will be implemented in a new modulation scheme with improved natural balancing dynamics.

# A. Modified phase shifted PWM strategy

As concluded from the previous section, the order of equations requires all six switch states to be used for D = 0. It seems impossible to create a sequence of six states using these six switch states with a uniform distribution of the switching losses, although this requirement can be met when using eight states in a sequence. An appropriate sequence can be constructed starting from the following scheme:

$$z-*-\overline{z}-*-z-*-\overline{z}-*.$$

In this sequence scheme  $(z,\overline{z})$  is the base pair which can be one of the zero voltage generating complementary switch pairs (1,2), (3,4) or (5,6). Once one base pair is chosen, the other zero voltage generating switch states have to be spread over the four \*'s. The exact placement of these states influences the balancing dynamics. There are 24 (= 4!) ways to place these switch states for every chosen base pair. With three possible base pairs, this results in 72 possible sequences.

A good sequence is for example (for D = 0, with (3,4) as base pair): 3 - 1 - 4 - 2 - 3 - 5 - 4 - 6. The switch state sequences for  $D \neq 0$ , which include states creating the other intermediate voltages ( $V_{\rm DC}/4$  and  $-V_{\rm DC}/4$ ), must be chosen to have only one switching for every switch state transition. The sequence for 0 < D < 0.5, corresponding with the previously presented zero-sequence, is: 3 - 8 - 1 - 7 - 4 - 10 - 2 - 9 - 3 -9 - 5 - 7 - 4 - 10 - 6 - 8. For -0.5 < D < 0 the sequence is 3 - 14 - 1 - 13 - 4 - 12 - 2 - 11 - 3 - 14 - 5 - 12 - 4 - 13 - 6 - 11.

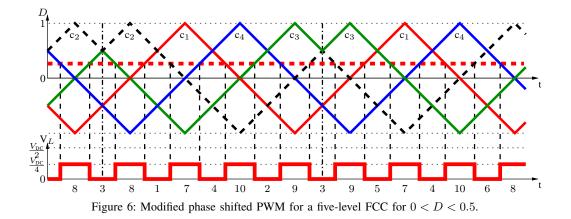

The proposed switch state sequence can be obtained using carriers. The carrier representation of the proposed sequence example is depicted in figure 6 for 0 < D < 0.5. The carrier waveforms are constructed by alternating two carrier signals after half of the PWM period. It should be noted that the PWM period is now, unlike the PS-PWM case in figure 4, double that of the normal triangular carrier signal. In this example the carriers  $c_2$  and  $c_3$  alternate places at every dash-dot line, this is

when they meet each other on the positive D side. In the first part (states 3-8-1-7-4-10-2-9) carrier  $c_2$  is leading carrier  $c_3$ , at the second switch state 3 the carriers switch places and from there on (states 3-9-5-7-4-10-6-8) carrier  $c_3$  leads carrier  $c_2$ .

#### B. Related sequences

As stated before, the proposed method of creating the modified PS-PWM sequences results in 72 possible sequences. These sequences are not all unrelated, in fact, most of them are related. This means some sequences can be created by a transformation of another sequence. These related switch state sequences can not only be constructed from each other, but also their balancing dynamics are related. Using these properties, the number of sequences which have to be investigated to find the optimum sequence can be significantly reduced.

There are three ways to relate the sequences with each other. All three of these ways cause the number of sequences to be divided by two. In the end only three sequences for every base pair remain unrelated. The three ways to relate the sequences are now discussed.

a) Reversing the sequences: The sequences which have the reversed order result in the same dynamic parameters (the same time constants and oscillation frequencies). The only difference is a sign change of the sinusoidal term in the solution, similar to PS-PWM, [16]. Example: 3-1-4-2-3-5-4-6and 6-4-5-3-2-4-1-3;

b) Swap first and last part: Swapping the first four and last four states: 3-1-4-2-3-5-4-6 results in the same sequence as 3-5-4-6-3-1-4-2;

c) Mirror equivalent sequences: As can be derived from the carrier representation of figure 6, the sequence for D > 0is significantly different from the one for D < 0. This means the balancing dynamics are also different for the two cases, and not symmetrical around D = 0, which is the case for PS-PWM. When the carriers of figure 6 are mirrored over the time-axis, the resulting sequence can be found by taking for every switch state the inverse of the original switch state. For the zero switch states this means replacing state 1 by 2, 3 by 4, 5 by 6 and the other way around. The balancing dynamics of the resulting sequence is mirror equivalent with the original. The dynamics for D > 0 of the new sequence are equal to the dynamics for D < 0 of the original sequence. For the example of 3-1-4-2-3-5-4-6, the mirror equivalent sequence is 4-2-3-1-4-6-3-5. In figure 6, the faster balancing for D > 0 is caused by the identical adjacent switch states when approaching D = 0.5. This creates a higher current ripple and stronger damping due to the PWM copper loss.

These three ways to relate the switch state sequences reduce the total number of possible switch state sequences to three per base pair, making a total of nine sequences. These sequences each have their own balancing dynamics. These dynamics can be analyzed to find an optimal sequence with the fastest balancing.

#### C. Self-precharge

The precharging of an FCC is an important factor. In [18] it is shown that using a ramp-controlled DC-bus voltage, while

maintaining a zero average load voltage (D = 0) and a fast as: enough balancing, it is possible to apply self-precharge. This self-precharge is only applicable when the load is known, so the DC-bus voltage ramp can be adapted to the largest time constant of the balancing dynamics. For five-level single-leg FCC however, the normal PS-PWM is not appropriate as the time constant is infinite at the desired output voltage (D = 0). The modified PS-PWM scheme allows fast balancing at D =

The model which will be developed for the capacitor voltage balancing depends on the fact that  $v_{C1} < v_{C2} < v_{C3}$ . If this is not the case, the clamping diodes of the switches are activated, introducing nonlinearities in the system. In the self-precharge process, the capacitor voltages all start from zero volts, meaning that due to the balancing dynamics the clamping diodes will interact with the balancing. It can be shown however that the effect of the clamping diodes reduces the balancing duration, [18]. In section VI an experimental example of self-precharge will be presented.

0.

# V. BALANCE DYNAMICS ANALYSIS AND SIMULATION

The voltage balancing dynamics of a five-level single-leg FCC using PS-PWM was previously carried out in the time domain in [16]. The method for analyzing the balancing dynamics uses an averaged state-space model which is obtained by applying some assumptions. These assumptions are large enough capacitor values (to be able to neglect capacitor voltage changes during a PWM period) and an inductive load, which means load time constant L/R is significantly larger than the PWM period. Practically this means the current ripple is low and and can be considered as piecewise linear. The analysis of this averaged state-space model, where high order terms are neglected, results in a general solution with time constants and oscillation frequencies, [14]. This method is directly applicable to the proposed sequences of the modified phase shifted PWM. For the analysis, the deviations of the capacitor voltages from their nominal (balanced) values are used. These are defined

$$v_{d1} = v_{C1} - \frac{V_{\rm DC}}{4};$$

$$v_{d2} = v_{C2} - \frac{V_{\rm DC}}{2};$$

$$v_{d3} = v_{C3} - \frac{3V_{\rm DC}}{4};$$

(1)

where  $v_{C1}$ ,  $v_{C2}$  and  $v_{C3}$  are the voltages of the flying capacitors  $C_1$ ,  $C_2$  and  $C_3$ , respectively. The flying capacitors are supposed to be equal in the following analysis.

All the potential candidate sequences were analyzed and only the two most promising were selected to be presented here based on balancing speed. For all sequences the time constant equations were obtained. The maximum time constant over the total D-range was used as criterion for the selection, taking in mind that the time constants increase to infinity for D going to 1 or -1.

# A. Analysis of two promising sequences

The first promising sequence is the one already introduced and has a zero voltage generating sequence of 3-1-4-2-3-5-4-6. The general solution for this sequence is:

$$v_{d1}(t) = \exp\left(-\frac{t}{T_P}\right) \left[v_{d1}(0)\cos\omega t + v_{d3}(0)\sin\omega t\right];$$

$$v_{d2}(t) = \exp\left(-\frac{t}{T_A}\right) v_{d2}(0);$$

$$v_{d3}(t) = \exp\left(-\frac{t}{T_P}\right) \left[v_{d3}(0)\cos\omega t - v_{d1}(0)\sin\omega t\right];$$

(2)

with  $v_{C1}(0)$ ,  $v_{C2}(0)$  and  $v_{C3}(0)$  the initial capacitor voltages. It can be noted that voltage  $v_{d2}$  has no oscillating term. The time constants and the oscillation frequencies for this sequence for the whole range of D are tabulated in table II, with constant  $K_T$ :

$$K_T = \frac{192L^2C}{RT_{\rm PWM}^2} \tag{3}$$

The second example of a zero voltage generating sequence which results in fast balancing is: 5 - 1 - 6 - 3 - 5 - 4 - 6 - 2. Also for this sequence it is possible to find a carrier representation as figure 6 but

Table II: Parameters of the balancing dynamics for sequence 3 - 1 - 4 - 2 - 3 - 5 - 4 - 6

| D                 | -1 < D < -0.5                                      | -0.5 < D < 0                                  | 0 < D < 0.5                                   | 0.5 < D < 1                                   |

|-------------------|----------------------------------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------|

| T.                | 1                                                  | 1                                             | 1                                             | 1                                             |

| $\frac{T_A}{K_T}$ | $\frac{1}{(1+D)^2(1-2D)}$                          | $\frac{4}{5+6D}$                              | $\frac{4}{5+6D}$                              | $\frac{1}{(7+2D)(1-D)^2}$                     |

| $T_P$             | 16                                                 | 16                                            | 16                                            | 16                                            |

| $\overline{K_T}$  | $\overline{\left(1+D\right)^2\left(13-32D\right)}$ | $\overline{15+6D-27D^2-16D^3}$                | $\overline{15+6D-27D^2+16D^3}$                | $\overline{(37+32D)(1-D)^2}$                  |

| Ω                 | $\frac{\left(1+D\right)^2 T_{\rm PWM}}{16LC}$      | $\frac{\left(1-2D^2\right)T_{\rm PWM}}{32LC}$ | $\frac{\left(1-2D^2\right)T_{\rm PWM}}{32LC}$ | $\frac{\left(1-D\right)^2 T_{\rm PWM}}{16LC}$ |

now carriers  $c_2$  and  $c_4$  are alternating places. The general solution for this sequence is:

$$v_{d1}(t) = \exp\left(-\frac{t}{T_P}\right) \\ \cdot \left[\frac{v_{d1}(0) - v_{d2}(0)}{2}\cos\omega t - \frac{v_{d3}(0)}{2}\sin\omega t\right] \\ + \exp\left(-\frac{t}{T_A}\right)\frac{v_{d1}(0) + v_{d2}(0)}{2};$$

$$v_{d2}(t) = \exp\left(-\frac{t}{T_P}\right) \\ \cdot \left[\frac{v_{d2}(0) - v_{d1}(0)}{2}\cos\omega t + \frac{v_{d3}(0)}{2}\sin\omega t\right] \\ + \exp\left(-\frac{t}{T_A}\right)\frac{v_{d1}(0) + v_{d2}(0)}{2};$$

(4)

$$v_{d3}(t) = \exp\left(-\frac{t}{T_P}\right)$$

$$\cdot \left[v_{d3}(0)\cos\omega t + \frac{v_{d1}(0) - v_{d2}(0)}{2}\sin\omega t\right];$$

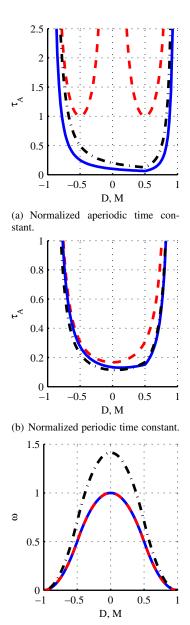

It can be noted that voltage  $v_{d3}$  has no over-damped (aperiodic) term. The parameters of both presented modified PS-PWM sequences and of the regular PS-PWM are depicted in figure 7 as a function of D. In figures 7(a) and 7(b) the normalized time constants  $\tau_A$  and  $\tau_P$  are depicted, with as reference the minimum aperiodic time constant of PS-PWM. Figure 7(c) shows the normalized oscillation frequency. The most significant difference between the PS-PWM and the modified PS-PWM sequences is noticeable in the aperiodic time constant. The infinite time constant for D = 0 has disappeared and the aperiodic balancing is faster over the full D-range. The aperiodic time constant of the first example (sequence 1) is half of the one of the second example (sequence 2). The periodic time constants (figure 7(b)) of the modified PS-PWM sequences are slightly asymmetric and smaller than the periodic time constant of the normal PS-PWM. In general the periodic time constant is smaller than the aperiodic time constant. The oscillation frequencies, figure 7(c), are equal for the PS-PWM and the first example of the modified PS-PWM. The oscillation frequency of the second example is larger (factor  $\sqrt{2}$ ). These oscillation frequencies are of smaller interest in this study. They are a parameter of the stepresponse, but have no real influence on the stability or the speed of the balancing.

A sequence of the improved PS-PWM is not equally beneficial over the total *D*-range, especially because of the asymmetry. This can be overcome by using, in the example of sequence 1, for D < 0 the mirror equivalent sequence, while keeping the original sequence 1 for D > 0. This results in symmetric behaviour. A detailed analysis of this possibility of out of the scope of this paper.

The DC parameters of table II can be used to obtain AC parameters. Substituting  $D = M \sin(\omega t)$  (*M* the modulation index and  $\omega$  the fundamental frequency) in the equations and averaging over a fundamental period results in the AC parameters, as presented in [16].

## B. Simulations

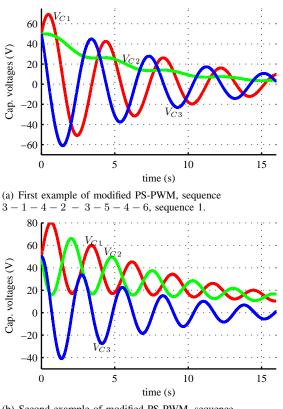

To visualize the balancing terms in equations (2) and (4), the results of switched simulations are presented in figure 8. The system parameters, used in this simulation, are the same as those of the practical setup and will be discussed later. The capacitors are equally charged to a voltage of 50 V. With a zero DC-bus voltage, the capacitors start to balance to 0 V. This is only possible with ideal switches, without clamping diodes. The behavior in figure 8(a) for sequence 1 corresponds with its equations (2) except for a small oscillating term in the capacitor voltage  $v_{C2}$ , which is not included in equations (2). This small periodic term is not included in the model because it's caused by higher order terms and by the non-zero R/Lload parameter. The lower this value is, the smaller is the oscillating term in voltage  $v_{C2}$ . The simulation using sequence 2, see figure 8(b), corresponds perfectly with equations (4).

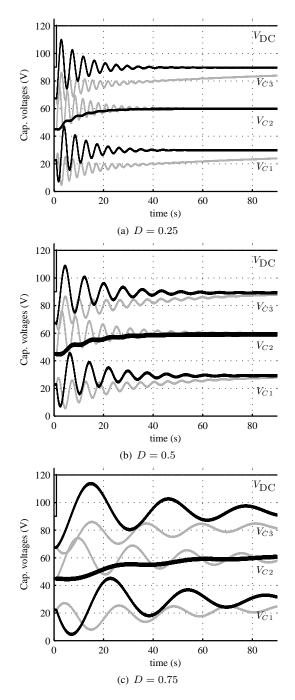

In figure 9 simulation results are presented of a step response in the capacitor voltages for a step in  $V_{\rm DC}$  from 90 V to 120 V for the classic PS-PWM (gray lines) together with the modified PS-PWM (sequence 1, black lines). For small D, capacitors  $C_1$  and  $C_3$  take a long time to balance for the classic PS-PWM. After the oscillations damped out, the overdamped part of the solutions takes a long time due to the large aperiodic time constant. The absence of an important over-damped part in the solution for the modified PS-PWM of those capacitors lets the voltages oscillate around the steady state solution and the oscillations are damped in a short time. Using the modified PS-PWM, capacitor  $C_2$  only has an overdamped part as expected. For high D, balancing is slower for both methods, but even there the modified PS-PWM is a significant improvement.

(c) Normalized oscillation frequency.

Figure 7: Voltage balancing dynamics parameters for PS-PWM (dashed line) and the two proposed examples of the modified phase shifted PWM, sequence 1 (full line) and sequence 2 (dash-dot line).

# VI. EXPERIMENTAL VERIFICATION

## A. Experimental setup

The experimental setup is a five-level flying capacitor converter constructed from in-house, half-bridge power electronic building blocks (PEBB). The system parameters of the setup are the same as those used in the simulation study and are given in Table III. The converter is controlled with an Xilinx VirtexII-Pro FPGA (XUPV2P-30), clocked at 100 MHz.

An ironless choke is used as load, connected between the output and the mid-point of the voltage supply, see figure 1. A simple series connection of a resistance R and an inductance L is used as a model for the load. Because of the absence of an iron core, the parameters do not depend very much on the frequency. The inductance, as well as the resistance, are only

(b) Second example of modified PS-PWM, sequence 5-1-6-3-5-4-6-2, sequence 2.

Figure 8: Simulation of voltage balancing with initially charged capacitors, D = 0 and zero DC-bus voltage (ideal switches).

Table III: System parameters

| Converter parameters |                     |   | Load parameters |  |

|----------------------|---------------------|---|-----------------|--|

| $C_1, C_2, C_3$      | $= 880 \mu\text{F}$ | L | = 30  mH        |  |

| $T_{\rm PWM}$        | = 1/750  ms         | R | $= 11 \Omega$   |  |

slightly influenced by the frequency and taken constant. The load parameters are found using an LCR-meter.

#### B. Experimental results

Measurements of the balancing after a step in the DC-bus voltage are depicted in figure 10. These measurements are carried out using sequence 3 - 1 - 4 - 2 - 3 - 5 - 4 - 6 (sequence 1 in figure 7). In each subfigure, the graphs represent, from top to bottom: the DC-bus voltage  $V_{\rm DC}$ , followed by the capacitor voltages  $v_{C3}$ ,  $v_{C2}$  and  $v_{C1}$ . The black lines in the graphs are calculated using the model, equations (2).

The oscillation frequency of the balancing corresponds well with the theoretical values. Except for D = 0, the damping of the oscillation in the experiments is only slightly faster than in theory. This is caused by the losses in the converter, whereas in the model only load losses are included. As stated before, these additional losses speed up the voltage balancing. The small oscillating term in voltage  $v_{C2}$ , as found in the simulations of figure 8, is also noticeable in the measurements.

In the measurements, the voltage balancing damping is significantly higher around D = 0 than that of the model.

Figure 9: Simulation of voltage balancing after a step in  $V_{\rm DC}$  from 90 V to 120 V, gray: classic PS-PWM; black: modified PS-PWM.

The reason for this was studied using simulations and measurements and is explained here. When D is small enough, the current ripple amplitude is larger than the average load current. This results in a sign change of the load current during a voltage pulse. The actual voltage pulse depends on the applied switch state and the capacitor voltages. Let's assume as an example a positive voltage pulse. This pulse will start with a negative current. The forward voltage drop over the four IGBTs or diodes in the current path are each about 0.7V, resulting in an extra voltage rise of 2.8V for negative current. When the current changes to a positive sign, the voltage over the IGBTs or diodes results in an extra voltage drop of 2.8V (after a short transient). In total an extra voltage variation of 5.6V is created by the voltage drops over the IGBTs because of the current sign change. This extra voltage variation results in extra losses, which makes the balancing faster. The influence of this effect depends on the relative voltage variation to the total voltage. For a higher DC-bus voltage, the relative voltage variation due to the voltage drops decreases and the balancing is less influenced by the forward voltage drops of the switch components. This effect can be reproduced in simulation (using non-ideal switches and diodes), but it is out of the scope of this paper to be presented in detail here. The effect of the extra introduced losses is an even faster balancing around D = 0 than expected from our model. This means the model is on the safe side and results in a maximum time constant.

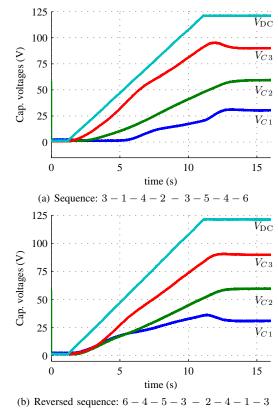

The fast balancing of the modified PS-PWM at D = 0 is an important improvement over the normal PS-PWM. This property can be used for self-precharge, when the DC-bus voltage rise is controlled. When using D = 0 during the selfprecharge process, a zero average current flows through the load. Figure 11 shows a self-precharge example. During selfprecharge, the most important factor is the voltage stress over the switches. The voltage stresses over the different switch pairs is equal to the voltage difference between the consecutive flying capacitors. This means the distance between the lines in figure 11 should not exceed the voltage rating of the switches.

An example of self-precharge is depicted in figure where the previously discussed 11(a), sequence (3-1-4-2-3-5-4-6) is used. Due to the nonlinearities introduced by the clamping diodes, the capacitor voltage  $v_{C1}$  stay at zero volts for some time because according to the linear model the voltage first goes negative. By using the reversed sequence (6 - 4 - 5 - 3 - 2 - 4 - 1 - 3), figure 11(b), the capacitor voltages rise immediately, but stay the same for some time due to the clamping diodes. This effect change is caused by the changing sign of the sine terms in equations (2) when the switch state sequence is reversed. The reversed sequence results in slightly faster balancing and lower voltage stress. By slowing down the DC-bus voltage rise even more, the maximum voltage stress over the switches during self-precharge can be further reduced.

#### VII. CONCLUSIONS

Natural balancing of FCCs can be achieved by using the normal PS-PWM scheme. It was observed that the balancing is not guaranteed at certain regions of the duty ratio. For five-level single-leg converters there is no balancing for D = 0. A new PWM scheme should enhance the voltage balancing, while maintaining the optimal voltage quality of nearest voltage level switching and an equal distribution of the switching losses over the switches.

The presented modified PS-PWM scheme results in faster balancing dynamics, with balancing over the total range of D, unlike the normal PS-PWM scheme. The modified PS-PWM scheme creates 72 possible sequences, which are all related to 9 original sequences, with their own balancing dynamics.

Figure 10: Experiment of voltage balancing after step in  $V_{\rm DC}$  from 45V to 60V at t = 0.3 s for modified PS-PWM sequence, compared with the derived model (black lines).

Figure 11: Self-precharge example with a controlled DC-bus voltage rise.

A carrier representation of the modified PS-PWM scheme is presented. The balancing dynamics of the two most promising sequences were analyzed.

The models for the two promising sequences were developed using an averaged state-space model approach. The balancing time constants are small, even for D = 0, but are asymmetric around D = 0. The experimental results show improved balancing dynamics compared with the normal PS-PWM and they also confirmed the accuracy of the obtained model parameters. A good characterization of the load is necessary to obtain correct theoretical values. The modified PS-PWM scheme allows self-precharge for a five-level converter as for D = 0 the time constants are not infinite.

#### REFERENCES

- J.-S. Lai and F. Z. Peng, "Multilevel converters-a new breed of power converters," *IEEE Trans. Industry Applications*, vol. 32, no. 3, pp. 509 -517, may/jun 1996.

- [2] A. Shukla, A. Ghosh, and A. Joshi, "Hysteresis modulation of multilevel inverters," *IEEE Trans. Power Electronics*, vol. 26, no. 5, pp. 1396 – 1409, may 2011.

- [3] F. Defay, A. M. Llor, and M. Fadel, "Direct Control Strategy for a Four-Level Three-Phase Flying-Capacitor Inverter," *IEEE Trans. Industrial Electronics*, vol. 57, no. 7, pp. 2240–2248, 2010.

- [4] C. Feng, J. Liang, and V. G. Agelidis, "Modified phase-shifted PWM control for flying capacitor multilevel converters," *IEEE Trans. Power Electronics*, vol. 22, no. 1, pp. 178–185, 2007.

- [5] X. Yuang, H. Stemmler, and I. Barbi, "Self-balancing of the clampingcapacitor-voltages in the multilevel capacitor-clamping-inverter under sub-harmonic pwm modulation," *IEEE Trans. Power Electronics*, vol. 16, no. 2, pp. 256–263, Mar. 2001.

- [6] M. Khazraei, H. Sepahvand, K. Corzine, and M. Ferdowsi, "A generalized capacitor voltage balancing scheme for flying capacitor multilevel converters," in *Applied Power Electronics Conference and Exposition* (APEC), 2010 Twenty-Fifth Annual IEEE, feb. 2010, pp. 58–62.

- [7] B. P. McGrath and D. G. Holmes, "Analytical modelling of voltage balance dynamics for a flying capacitor multilevel converter," *IEEE Trans. Power Electronics*, vol. 23, no. 2, pp. 543–550, 2008.

- [8] —, "Natural capacitor voltage balancing for a flying capacitor converter induction motor drive," *IEEE Trans. Power Electronics*, vol. 24, no. 6, pp. 1554–1561, june 2009.

- [9] —, "Enhanced voltage balancing of a flying capacitor multilevel converter using phase disposition (pd) modulation," *IEEE Trans. Power Electronics*, vol. PP, no. 99, pp. 3108–3115, 2010.

- [10] R. H. Wilkinson, T. A. Meynard, and H. du Toit Mouton, "Natural balance of multicell converters: The two-cell case," *IEEE Trans. Power Electronics*, vol. 21, no. 6, pp. 1649–1657, 2006.

- [11] ——, "Natural balance of multicell converters: The general case," *IEEE Trans. Power Electronics*, vol. 21, no. 6, pp. 1658–1666, 2006.

- [12] A. K. Sadigh, S. H. Hosseini, M. Sabahi, and G. Gharehpetian, "Double flying capacitor multicell converter based on modified phase-shifted pulsewidth modulation," *IEEE Trans. Power Electronics*, vol. 25, no. 6, pp. 1517–1526, june 2010.

- [13] F. Khan, L. Tolbert, and W. Webb, "Start-up and dynamic modeling of the multilevel modular capacitor-clamped converter," *IEEE Trans. Power Electronics*, vol. 25, no. 2, pp. 519 –531, feb. 2010.

- [14] A. Ruderman, B. Reznikov, and M. Margaliot, "Simple analysis of a flying capacitor converter voltage balance dynamics for dc modulation," in *Power Electronics and Motion Control Conference*, 2008. EPE-PEMC 2008. 13th, sept. 2008, pp. 260 –267.

- [15] S. Thielemans, A. Ruderman, B. Reznikov, and J. Melkebeek, "Simple time domain analysis of a 4-level H-bridge flying capacitor converter voltage balancing," in *Proc. IEEE Int. Conf. on Industrial Technology* (*ICIT*). IEEE, 2010, pp. 818–823.

- [16] A. Ruderman and B. Reznikov, "Five-level single-leg flying capacitor converter voltage balance dynamics analysis," in *Industrial Electronics*, 2009. IECON '09. 35th Annual Conference of IEEE, nov. 2009, pp. 486 –491.

- [17] A. Ruderman, B. Reznikov, and S. Thielemans, "Single-leg flying capacitor converter voltage balancing dynamics analysis accounting for pwm iron loss," in *Power Electronics and ECCE Asia (ICPE ECCE)*, 2011 IEEE 8th International Conference on, june 2011, pp. 977–982.

- [18] S. Thielemans, A. Ruderman, B. Reznikov, and J. Melkebeek, "Selfprecharge for single-leg odd-level multilevel converter," in *Power Electronics, Machines and Drives (PEMD 2010), 5th IET International Conference on*, april 2010, pp. 1–6.

Alex Ruderman (M'07) was born in Leningrad, USSR, in 1957. He received his M.Sc. degree with Honors from Leningrad Electrical Engineering Institute (1980) and Ph.D. degree from Leningrad Polytechnic Institute (1987) (both in electromechanical engineering). In 1995-2003, Alex worked for Intel Corporation Microprocessor Development Center (Haifa, Israel) as a research scientist investigating into microprocessors thermal stabilization, fast static timing calculations, power delivery and power minimization. Since 2006, Alex is a chief scientist

for ELMO Motion Control Ltd. His research interests include multilevel power converter topologies and voltage modulation strategies, motor periodic disturbances compensation by drive control and more. Alex serves as a regular reviewer for power electronics / motion control conferences, for IEEE Transactions on Industrial Electronics and Power Electronics and other journals. He is a member of IEEE Power Electronics Technical Committee (PETC).

**Boris Reznikov** was born in Leningrad, USSR, in 1951. He received the M.Sc. degree in control engineering from Leningrad Electrical Engineering Institute (1974). His professional experience includes a study of dielectric properties of bounded water and its molecular behavior, numerical control systems for different machine tools, communication systems etc. Boris is currently a software leader for General Satellite Corporation, St. Petersburg, Russia. His research interests cover application of analytical mathematical methods in power electronics multi-

level and matrix converters voltage quality asymptotic time domain evaluation, flying capacitor converter natural voltage balancing dynamics time domain analysis using small parameter techniques and more.

Jan Melkebeek (SM'82) was born in Ghent, Belgium, in 1952. He received the Ingenieur degree in electrical and mechanical engineering, the Doctor in Applied Sciences Degree, and the Doctor Habilitus degree from the Ghent University, Ghent, Belgium, in 1975, 1980, and 1986, respectively. He is director of the Electrical Energy Laboratory (EELAB) and Head of the Department of Electrical Power Engineering, Systems and Automation (EESA) of Ghent University. His teaching activities and research interests include electrical machines, power electronics,

variable-frequency drives, magnetic materials, and also control systems theory applied to electrical drives. Prof. Melkebeek is a member of the Koninklijke Vlaamse Ingenieursvereniging (K.VIV), the Koninklijke Belgische Vereniging van Elektrotechnici (KBVE-SRBE), the Belgian Federation for Automatic Control (BIRA-IBRA), and a Fellow of the Institution of Engineering and Technology (IET, formerly IEE), U.K. He served as the President of the IEEE Benelux IAS-PELS joint chapter from 2002 to 2003 and is a longtime member of the IEEE-IAS Electrical Machines Committee, the IEEE-IAS Electic Drives Committee, and the IEEE-PES Machine Theory Subcommittee.

Steven Thielemans (M'07) was born in Ghent, Belgium, in 1983. He received the M.Sc. degree in electromechanical engineering from Ghent University, Ghent, Belgium, in 2006. Since than, he is with the Electrical Energy Laboratory, Department of Electrical Engineering, Systems and Automation, Ghent University. His research interests include power electronics, multilevel converters, advanced control strategies (e.g. model predictive control) and energy storage systems (ultra-cap and lithium cells).