# Improving Processor Performance by Dynamically PreProcessing the Instruction Stream

by

#### **James David Dundas**

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 1998

#### **Doctoral Committee:**

Professor Trevor Mudge, Chairman

Professor Richard Brown

**Professor Ronald Lomax**

Professor Karem Sakallah

#### **ABSTRACT**

# Improving Processor Performance by Dynamically Pre-**Processing the Instruction Stream**

by

#### **James David Dundas**

Chairman: Trevor Mudge

The exponentially increasing gap between processors and off-chip memory, as measured in processor cycles, is rapidly turning memory latency into a major processor performance bottleneck. Traditional solutions, such as employing multiple levels of caches, are expensive and do not work well with some applications. We evaluate a technique, called runahead pre-processing, that can significantly improve processor performance.

The basic idea behind runahead is to use the processor pipeline to pre-process instructions during cache miss cycles, instead of stalling. The pre-processed instructions are used to generate highly accurate instruction and data stream prefetches, while all of the pre-processed instruction results are discarded after the cache miss has been serviced: this allows us to achieve a form of very aggressive speculation with a simple in-order pipeline. The principal hardware cost is a means of checkpointing the sequential state of the register file and memory hierarchy while instructions are pre-processed. As we discard all pre-processed instruction results, the checkpointing can be accomplished with a modest amount of hardware.

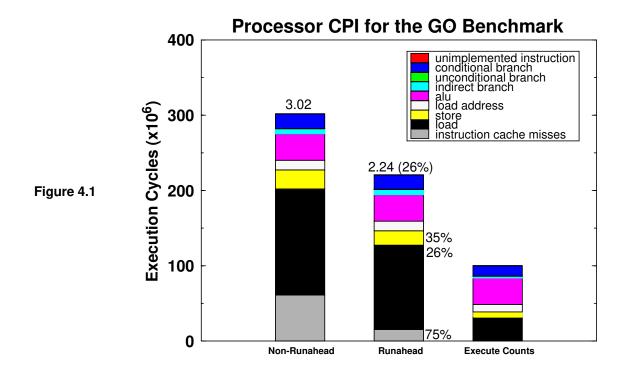

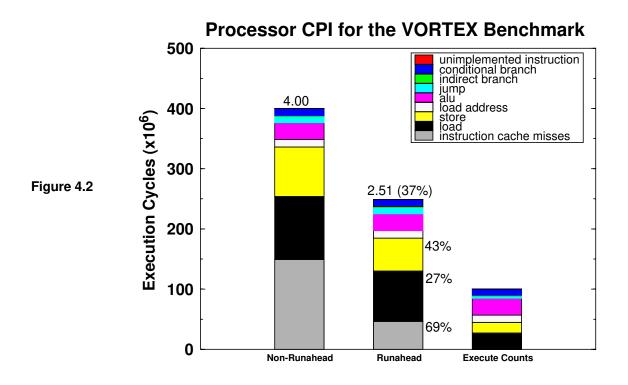

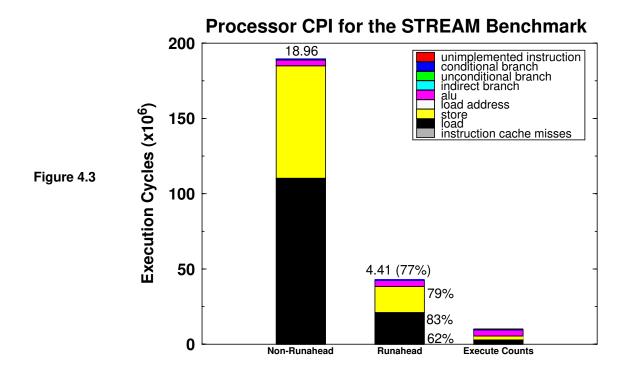

The instruction and data stream prefetches generated during runahead episodes led to a significant performance improvement for all of the benchmarks we examined. We found that runahead typically led to about a 30% reduction in CPI for the four Spec95 integer benchmarks that we simulated, while runahead was able to reduce CPI by 77% for the STREAM benchmark. This is for a five stage pipeline with two levels of split instruction and data caches: 8KB each of L1, and 1MB each of L2. A significant result is that when the latency to off-chip memory increases, or if the caching performance for a particular benchmark is poor, runahead is especially effective as the processor has more opportunities in which to pre-process instructions. Finally, runahead appears particularly well suited for use with high clock-rate in-order processors that employ relatively inexpensive memory hierarchies.

Confutatis maledictis flammis acribus addictus, voca me cum benedictus. Oro supplex et acclinis, cor contritum quasi cinis, gere curam mei finis. Lacrimosa dies illa, quae resurget ex favilla, judicandus homo reus.

Excerpted from *Requiem*— Wolfgang Amadeus Mozart

© James David Dundas All Rights Reserved 1998

# **DEDICATION**

To my family.

## **ACKNOWLEDGEMENTS**

I would like to thank Peter Bird, I-Cheng Chen, Brian Davis, Kris Flautner, Bruce Jacob, Viktor Kravets, Chih-Chieh Lee, Charles Lefurgy, Trevor Mudge, Dave Nagle, Yale Patt, Matt Postiff, Mike Riepe, Tim Stanley, Tim Strong, and David Van Campenhout for their many helpful suggestions over the years. I would also like to thank my thesis committee for providing me with advice and perspective on my research. Finally, I would like to thank my father for his many years of encouragement.

# **Table of Contents**

| Chapter 1 | Runahead                                                               | 1  |

|-----------|------------------------------------------------------------------------|----|

| 1.1       | Basic runahead theory                                                  | 2  |

| 1.2       | Some Runahead Examples                                                 | 4  |

| 1.3       | Dissertation Organization                                              | 7  |

| Chapter 2 | The Memory Latency Problem                                             | 9  |

| 2.1       | Caches                                                                 | 9  |

| 2.2       | Perform other useful work during cache miss cycles                     | 10 |

| 2.3       | Use the available memory bandwidth more effectively                    | 10 |

| 2.4       | Increase the bandwidth of the memory hierarchy                         | 11 |

| 2.5       | Statically schedule loads before stores                                | 12 |

| 2.6       | Executing loads early                                                  | 13 |

| 2.7       | Data Prefetching                                                       | 16 |

|           | 2.7.1 Hardware data prefetching                                        |    |

|           | 2.7.2 Software data prefetching                                        |    |

|           | 2.7.3 Hybrid hardware-software data prefetching                        |    |

| Chapter 3 | Runahead Simulation Methodology                                        | 25 |

| 3.1       | The basic idea behind the simulator                                    |    |

| 3.2       | How the workstation and simulator interact                             |    |

|           | 3.2.1 Simulation example                                               |    |

|           | 3.2.2 Modeling the instruction stream                                  |    |

|           | 3.2.3 Unimplemented instructions                                       |    |

| 3.3       | Pipeline Model                                                         |    |

| 3.4       | Processor model including the memory hierarchy                         |    |

| 5.4       | 3.4.1 L1 instruction cache                                             |    |

|           | 3.4.2 L2 instruction cache                                             |    |

|           | 3.4.3 L1 data cache                                                    |    |

|           | 3.4.4 L2 data cache                                                    | 40 |

|           | 3.4.5 Main Memory                                                      | 42 |

| 3.5       | What the simulator does not model                                      | 43 |

| 3.6       | Processor modifications to support runahead                            | 43 |

|           | 3.6.1 Hazard logic modifications                                       | 44 |

|           | 3.6.2 Runahead instruction source and destination valid bits           |    |

|           | 3.6.3 Entering runahead mode                                           |    |

|           | 3.6.4 Pipeline operation during runahead mode                          |    |

|           | 3.6.5 Resuming normal operation                                        |    |

|           | 3.6.6 Instruction cache miss initiated runahead                        |    |

|           | 3.6.7 Instruction cache misses during load and store miss initiated ru |    |

|           | 3.6.8 Branch prediction                                                |    |

|           | 3.6.10 Avoiding segmentation faults during runahead simulation         |    |

|           | 2.5.12 1.1 orang segmentation autility randical similarity             | 00 |

| 3.7       | Benchmarks                                                                                                                                                 |     |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|           | 3.7.1 System Issues                                                                                                                                        |     |

| Chapter 4 | Baseline Runahead Experiments                                                                                                                              | 61  |

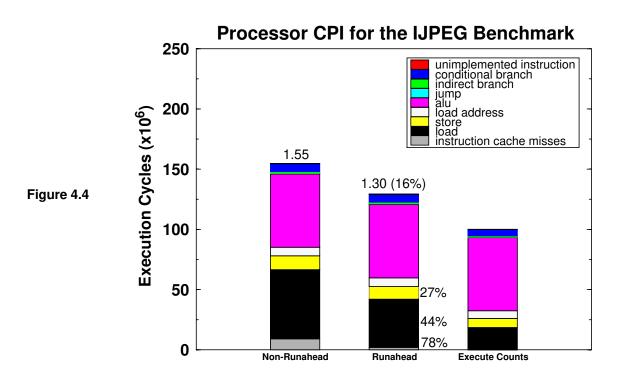

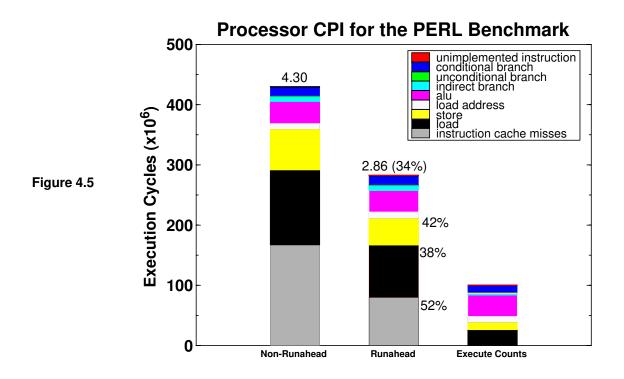

| 4.1       | CPI results                                                                                                                                                | 61  |

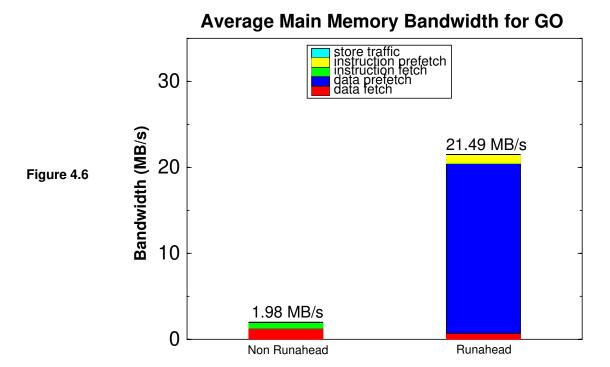

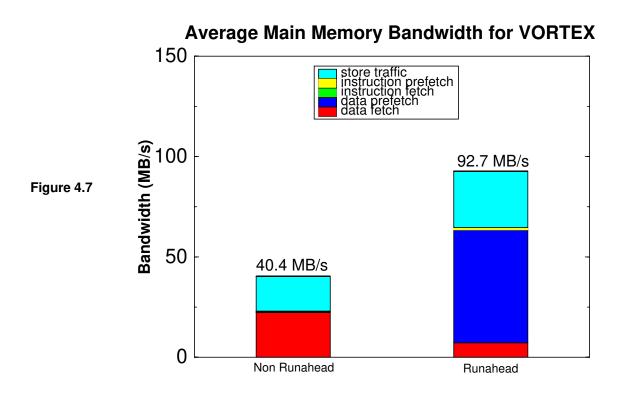

| 4.2       | Memory Bandwidth                                                                                                                                           | 67  |

|           | 4.2.1 Main memory bandwidth                                                                                                                                |     |

|           | 4.2.2 L2 data cache bandwidth                                                                                                                              |     |

|           | 4.2.3 L2 instruction cache bandwidth                                                                                                                       |     |

| 4.3       | Prefetching effectiveness over the course of runahead episodes                                                                                             |     |

|           | 4.3.1 Probability of remaining on the correct path during runahead                                                                                         |     |

|           | 4.3.2 Number of runahead episodes of each type                                                                                                             |     |

|           | <ul><li>4.3.3 Average number of prefetches generated per runahead episode</li><li>4.3.4 Prefetching utility over the course of runahead episodes</li></ul> |     |

| 4.4       | Measurements of miss-prefetch spatial locality                                                                                                             |     |

| 4.4       | 4.4.1 Data stream prefetch locality                                                                                                                        |     |

|           | 4.4.2 Instruction stream prefetch locality                                                                                                                 |     |

| 4.5       | What happens to potential data stream prefetches during runahead                                                                                           |     |

| 4.6       | Branch Prediction Effects                                                                                                                                  |     |

| 4.0       | 4.6.1 Branch misprediction rates                                                                                                                           |     |

|           | 4.6.2 Runahead Branch Register Utilization                                                                                                                 |     |

| 4.7       | Summary and Conclusions                                                                                                                                    |     |

| Chapter 5 | Runahead at the Instruction and Function level                                                                                                             | 141 |

| 5.1       | Processor Model                                                                                                                                            | 142 |

| 0.1       | 5.1.1 The distribution of prefetches on a per-function basis                                                                                               |     |

|           | 5.1.2 The distribution of prefetches on a per-instruction basis                                                                                            |     |

|           | 5.1.3 Where are the most useful loads and stores in the source code?                                                                                       |     |

| 5.2       | Register file effects                                                                                                                                      | 163 |

|           | 5.2.1 Data stream prefetch address computation                                                                                                             |     |

|           | 5.2.2 Branch condition computation                                                                                                                         |     |

|           | 5.2.3 Indirect branch target computation                                                                                                                   |     |

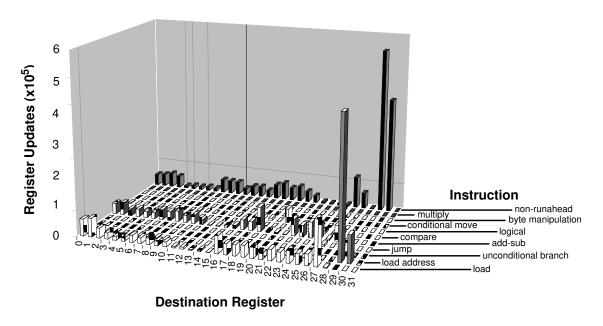

|           | 5.2.4 Data stream prefetch base address registers                                                                                                          |     |

| 5.3       | Summary and Conclusions                                                                                                                                    |     |

| Chapter 6 | Probing the Limits of the Baseline Technique                                                                                                               | 184 |

| 6.1       | Instruction cache misses during runahead                                                                                                                   |     |

| 6.2       | Increasing the length of the average runahead episode                                                                                                      |     |

| 6.3       | Wrong path effects during runahead                                                                                                                         |     |

| 6.4       | Runahead Models                                                                                                                                            | 186 |

| 6.5       | Simulation Results                                                                                                                                         |     |

|           | 6.5.1 CPI                                                                                                                                                  |     |

|           | 6.5.2 Prefetching utility over the course of runahead episodes                                                                                             |     |

|           | 6.5.3 Probability of remaining on the correct path during runahead                                                                                         |     |

|           | 6.5.4 Number of runahead episodes                                                                                                                          |     |

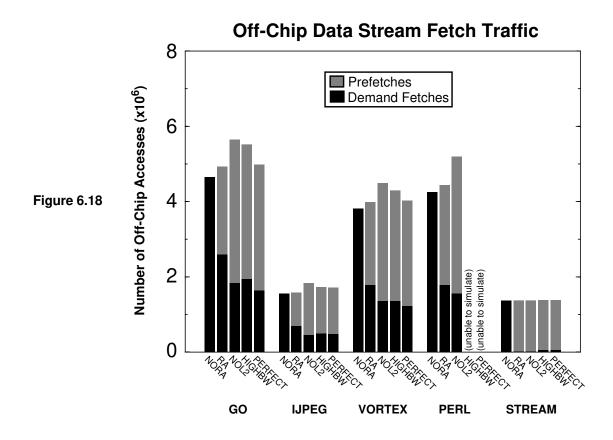

|           | 6.5.5 Average number of prefetches generated per runahead episode 6.5.6 Off-chip fetch and prefetch traffic                                                |     |

| 6.6       | Summary and Conclusions                                                                                                                                    |     |

| 0.0       | Daniniary and Conclusions                                                                                                                                  | ∠∪/ |

| Chapter 7  | Simplifying the Runahead Processor                       | 209 |

|------------|----------------------------------------------------------|-----|

| 7.1        | Eliminating the register file save and restore operation | 209 |

| 7.2        | Eliminating the BRF altogether                           | 212 |

| 7.3        | Simulation Results                                       | 213 |

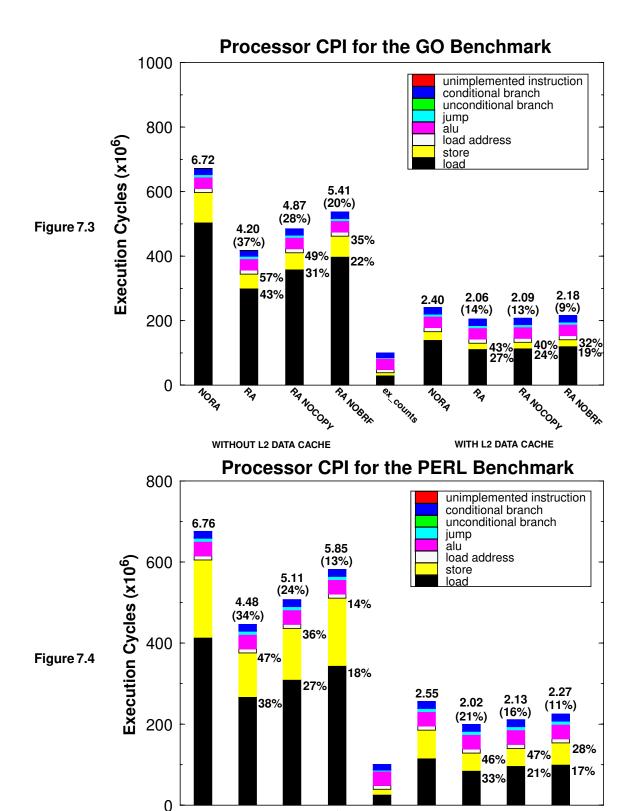

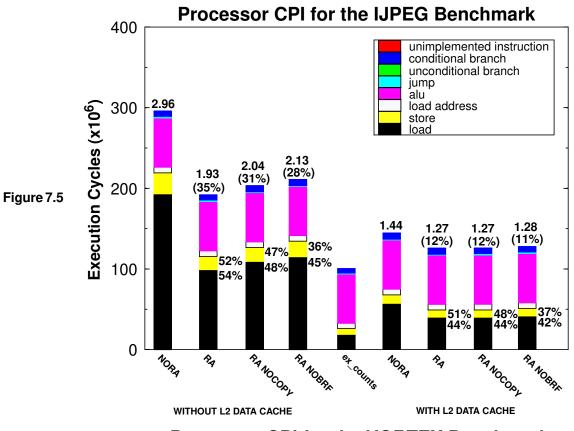

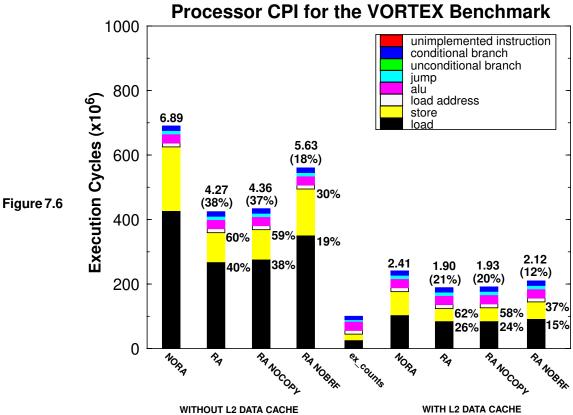

|            | 7.3.1 CPI                                                | 214 |

|            | 7.3.2 Stale Registers                                    | 224 |

| 7.4        | Eliminating the L1 data cache runahead valid bits        | 229 |

|            | 7.4.1 CPI                                                |     |

| 7.5        | Summary and Conclusions                                  | 233 |

| Chapter 8  | Summary and Conclusions                                  | 235 |

| Chapter 9  | Future Work                                              | 239 |

| 9.1        | Pre-process more than one instruction per cycle          | 239 |

| 9.2        | Runahead Co-processors                                   | 240 |

| 9.3        | Compiler Interaction                                     | 241 |

| References | •                                                        | 228 |

# LIST OF FIGURES

| Figure 1.1  | Basic runahead example                              | 4  |

|-------------|-----------------------------------------------------|----|

| Figure 1.2  | Stores during runahead                              | 6  |

| Figure 1.3  | Dependent branches during runahead                  | 7  |

| Figure 3.1  | Uninstrumented benchmark                            |    |

| Figure 3.2  | Instrumented benchmark                              | 28 |

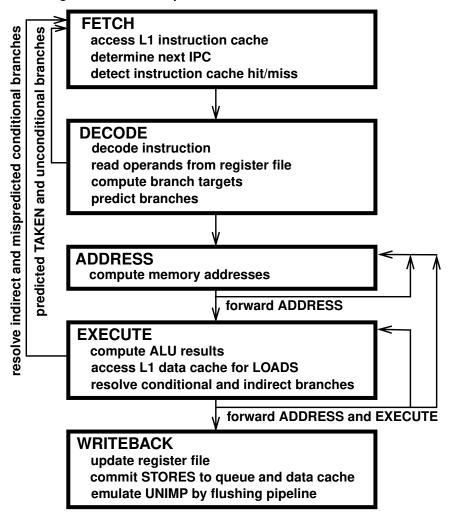

| Figure 3.3  | Block Diagram of the AGI Pipeline                   | 33 |

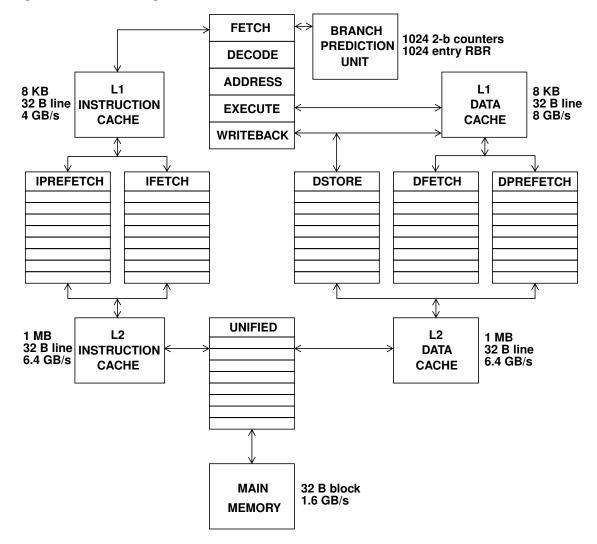

| Figure 3.4  | Block Diagram of the Baseline Processor Model       |    |

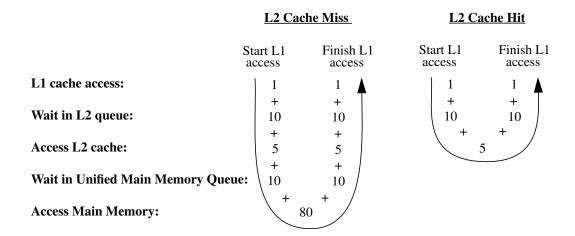

| Figure 3.5  | Minimum L2 cache access timing                      | 38 |

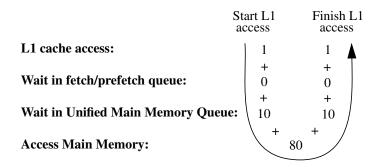

| Figure 3.6  | Minimum L1 data cache miss timing for processors    |    |

|             | without L2 data cache                               | 42 |

| Figure 3.7  | Pseudo code description of Runahead Branch Register |    |

|             | Behavior                                            | 52 |

| Figure 3.8  | Runahead Branch Register Example                    | 53 |

| Figure 4.1  | Processor CPI for the GO Benchmark                  | 65 |

| Figure 4.2  | Processor CPI for the VORTEX Benchmark              | 65 |

| Figure 4.3  | Processor CPI for the STREAM Benchmark              | 66 |

| Figure 4.4  | Processor CPI for the IJPEG Benchmark               | 66 |

| Figure 4.5  | Processor CPI for the PERL Benchmark                | 67 |

| Figure 4.6  | Average Main Memory Bandwidth for GO                | 70 |

| Figure 4.7  | Average Main Memory Bandwidth for VORTEX            | 70 |

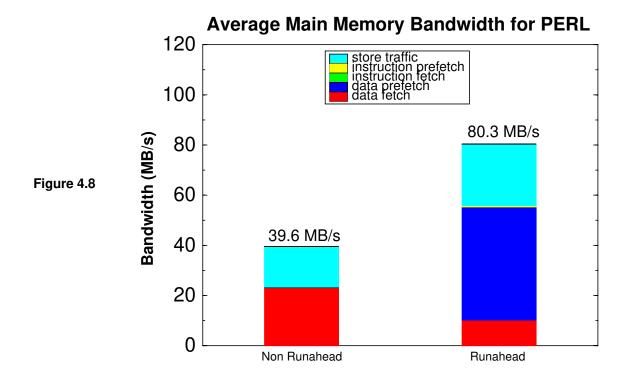

| Figure 4.8  | Average Main Memory Bandwidth for PERL              |    |

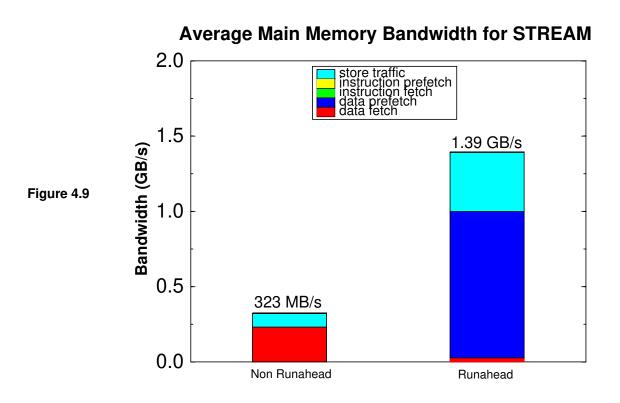

| Figure 4.9  | Average Main Memory Bandwidth for STREAM            | 71 |

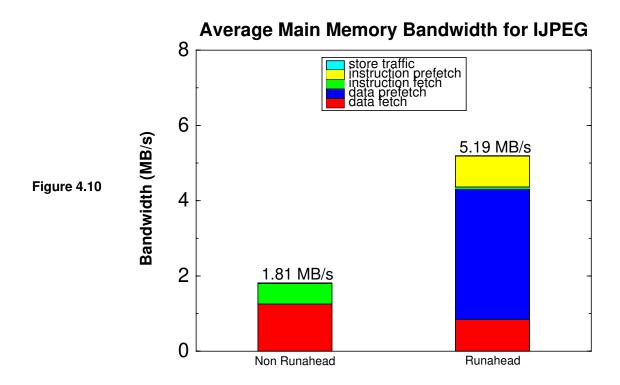

| Figure 4.10 | Average Main Memory Bandwidth for IJPEG             | 72 |

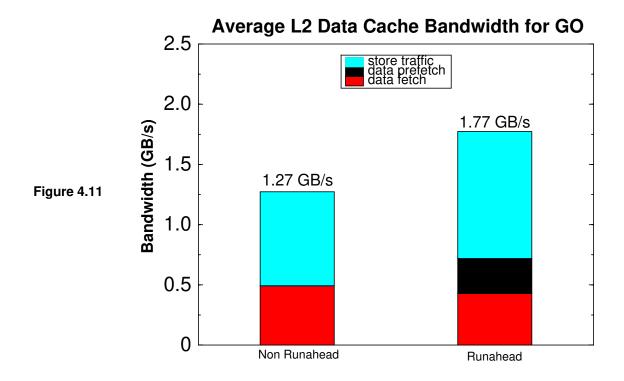

| Figure 4.11 | Average L2 Data Cache Bandwidth for GO              | 75 |

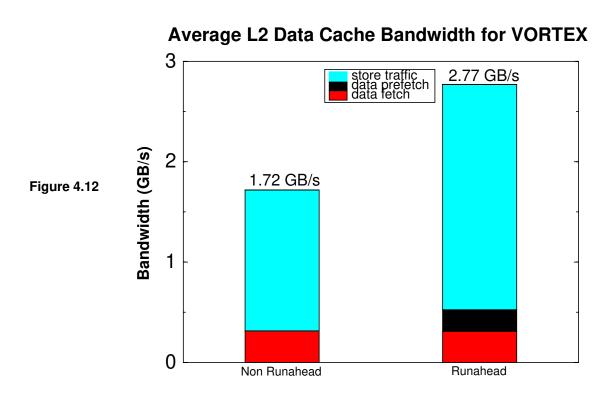

| Figure 4.12 | Average L2 Data Cache Bandwidth for VORTEX          | 75 |

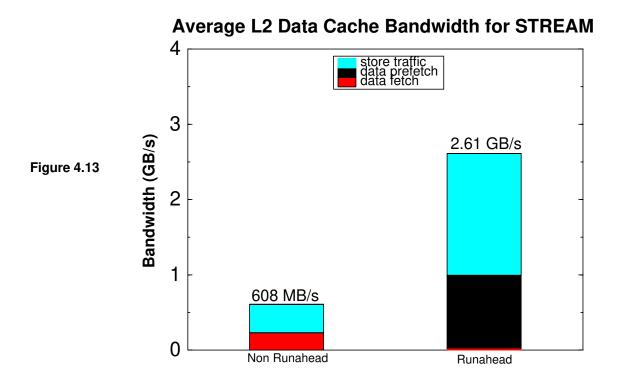

| Figure 4.13 | Average L2 Data Cache Bandwidth for STREAM          |    |

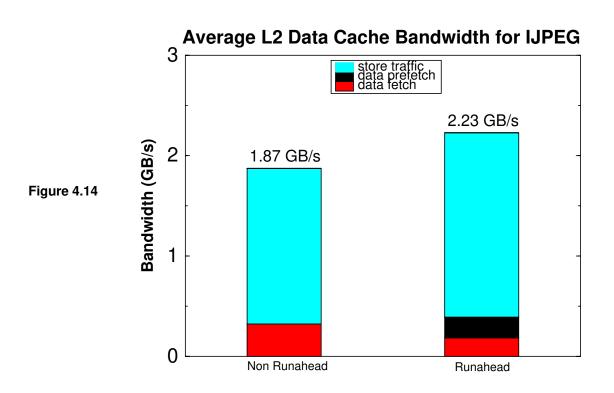

| Figure 4.14 | Average L2 Data Cache Bandwidth for IJPEG           | 76 |

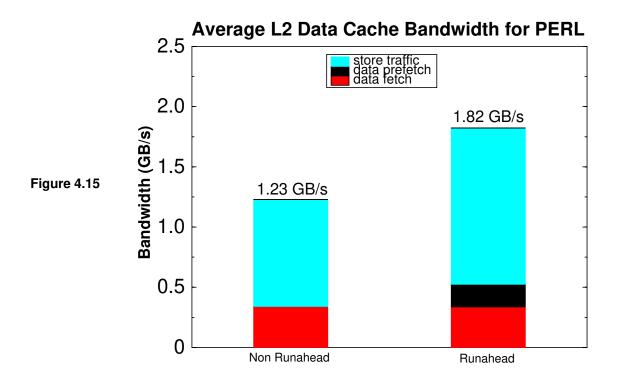

| Figure 4.15 | Average L2 Data Cache Bandwidth for PERL            | 77 |

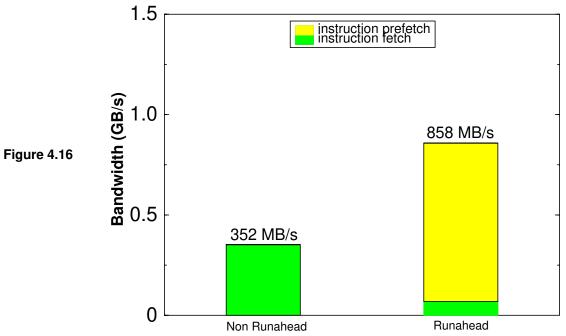

| Figure 4.16 | Average L2 Instruction Cache Bandwidth for GO       | 79 |

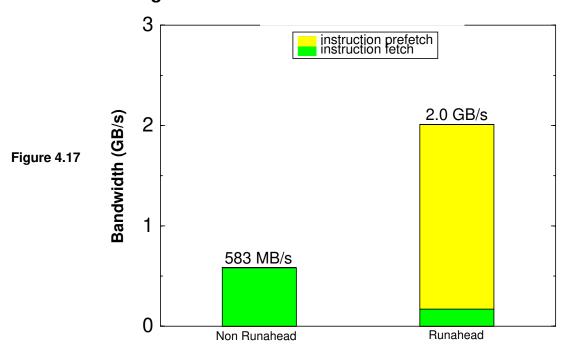

| Figure 4.17 | Average L2 Instruction Cache Bandwidth for VORTEX   | 79 |

| Figure 4.18 | Average L2 Instruction Cache Bandwidth for STREAM   |    |

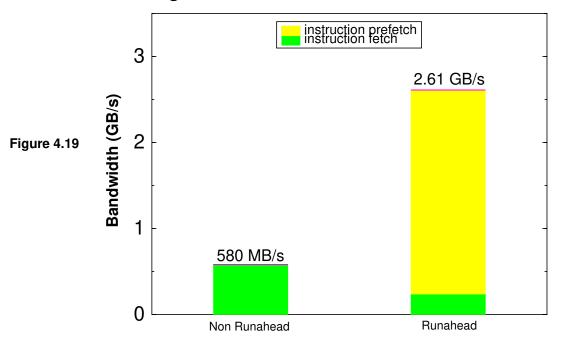

| Figure 4.19 | Average L2 Instruction Cache Bandwidth for PERL     | 80 |

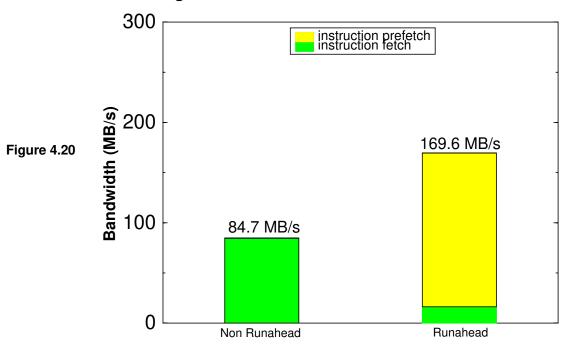

| Figure 4.20 | Average L2 Instruction Cache Bandwidth for IJPEG    | 81 |

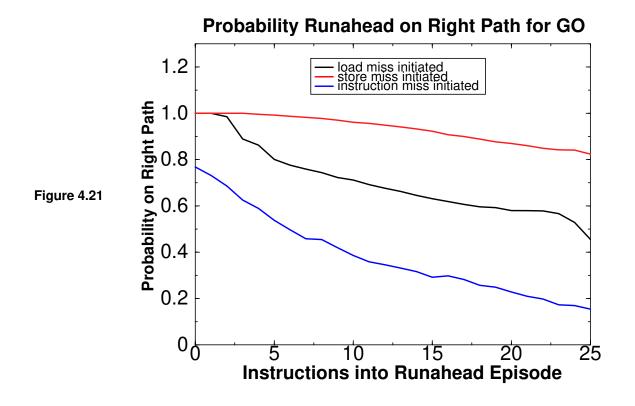

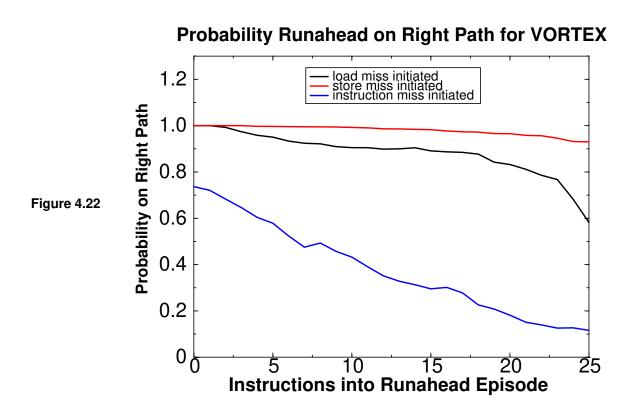

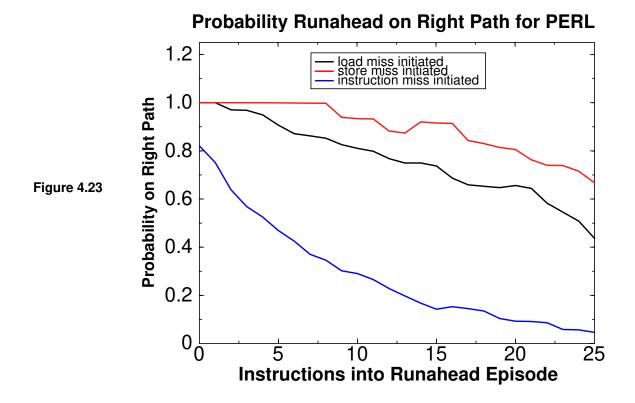

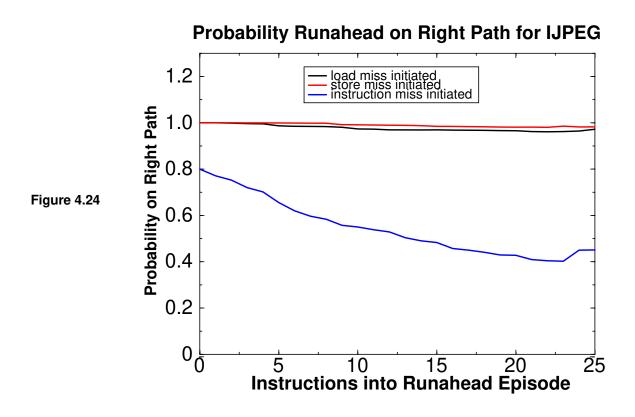

| Figure 4.21 | Probability Runahead on Right Path for GO                  | 85 |

|-------------|------------------------------------------------------------|----|

| Figure 4.22 | Probability Runahead on Right Path for VORTEX              |    |

| Figure 4.23 | Probability Runahead on Right Path for PERL                | 86 |

| Figure 4.24 | Probability Runahead on Right Path for IJPEG               | 86 |

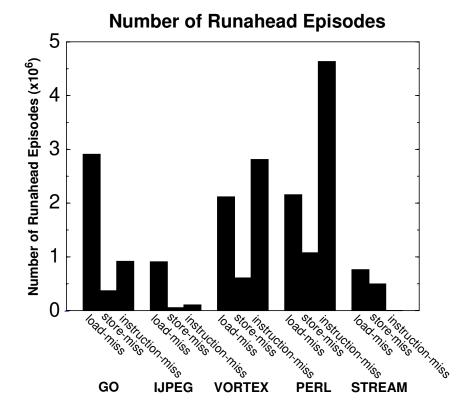

| Figure 4.25 | Number of Runahead Episodes                                | 88 |

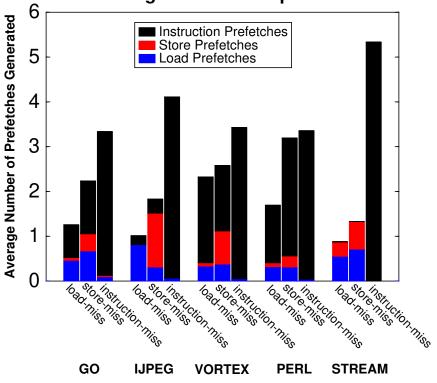

| Figure 4.26 | Number of Prefetches Generated during the Average          |    |

|             | Runahead Episode                                           | 88 |

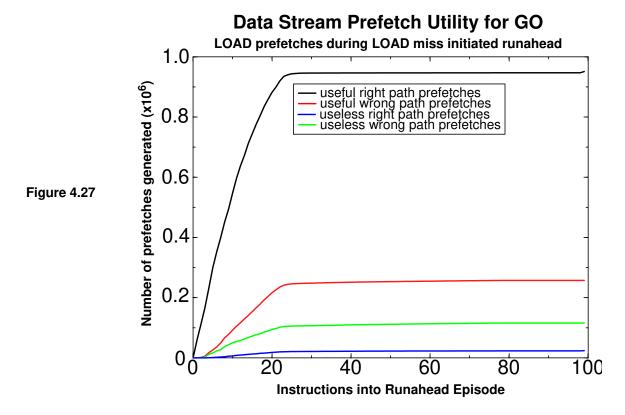

| Figure 4.27 | Data Stream Prefetch Utility for GO                        |    |

|             | LOAD prefetches during LOAD miss initiated runahead        | 92 |

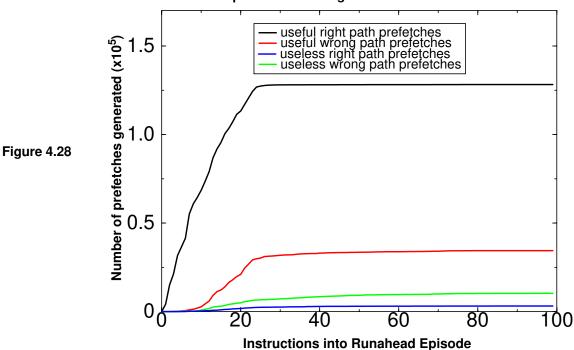

| Figure 4.28 | Data Stream Prefetch Utility for GO                        |    |

|             | STORE prefetches during LOAD miss initiated runahead       | 93 |

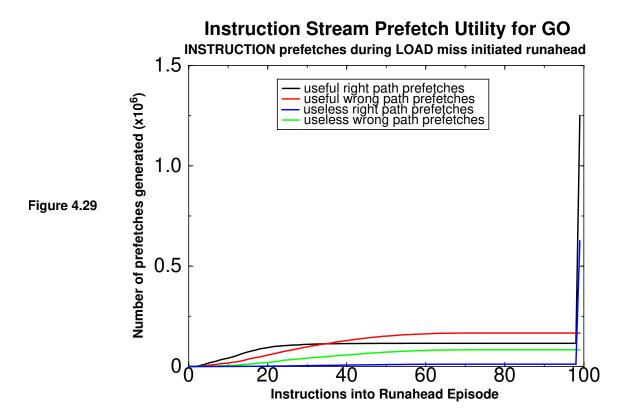

| Figure 4.29 | Instruction Stream Prefetch Utility for GO                 |    |

|             | INSTRUCTION prefetches during LOAD miss initiated runahead | 93 |

| Figure 4.30 | Data Stream Prefetch Utility for VORTEX                    |    |

|             | LOAD prefetches during LOAD miss initiated runahead        | 94 |

| Figure 4.31 | Data Stream Prefetch Utility for VORTEX                    |    |

|             | STORE prefetches during LOAD miss initiated runahead       | 94 |

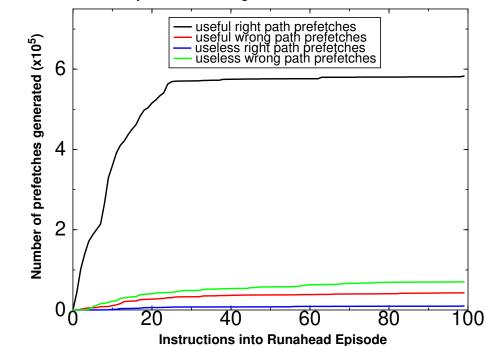

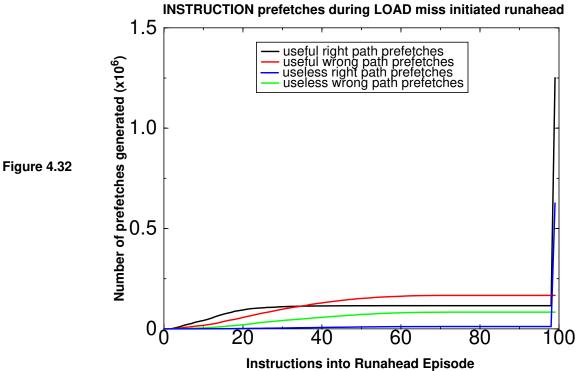

| Figure 4.32 | Instruction Stream Prefetch Utility for VORTEX             |    |

|             | INSTRUCTION prefetches during LOAD miss initiated runahead | 95 |

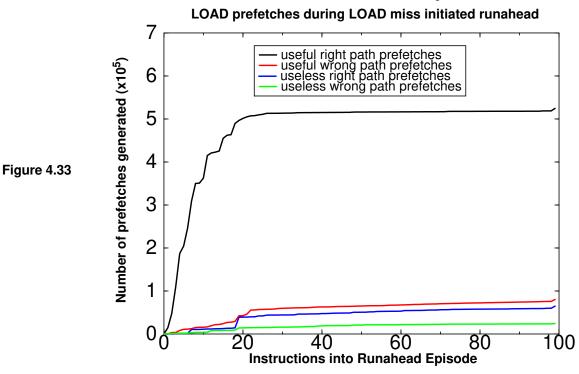

| Figure 4.33 | Data Stream Prefetch Utility for PERL                      |    |

|             | LOAD prefetches during LOAD miss initiated runahead        | 95 |

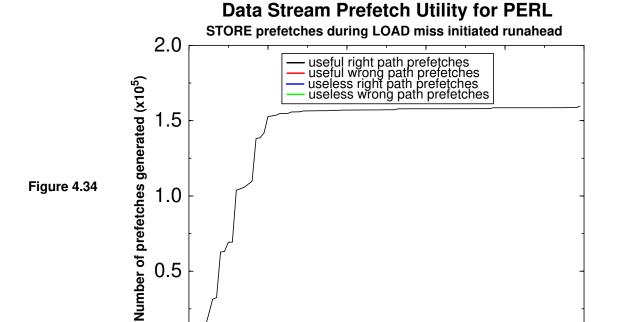

| Figure 4.34 | Data Stream Prefetch Utility for PERL                      |    |

|             | STORE prefetches during LOAD miss initiated runahead       | 96 |

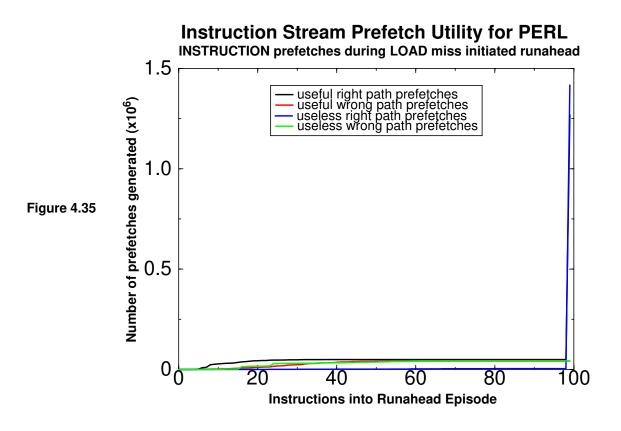

| Figure 4.35 | Instruction Stream Prefetch Utility for PERL               |    |

|             | INSTRUCTION prefetches during LOAD miss initiated runahead | 96 |

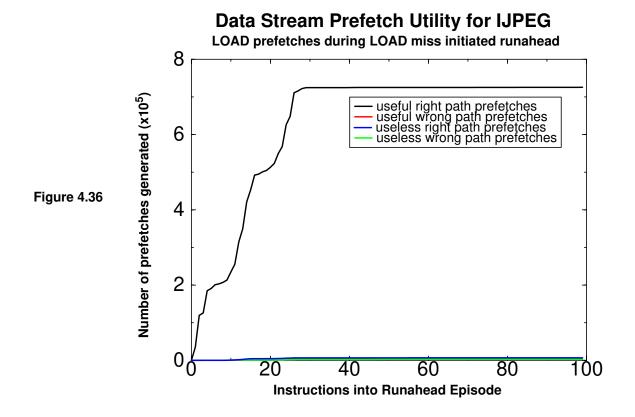

| Figure 4.36 | Data Stream Prefetch Utility for IJPEG                     |    |

|             | LOAD prefetches during LOAD miss initiated runahead        | 97 |

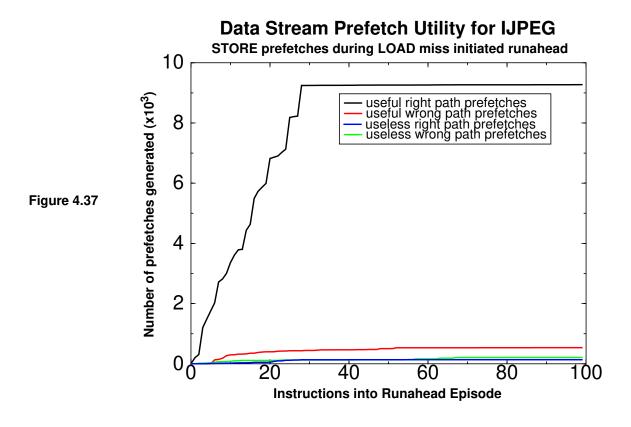

| Figure 4.37 | Data Stream Prefetch Utility for IJPEG                     |    |

|             | STORE prefetches during LOAD miss initiated runahead       | 97 |

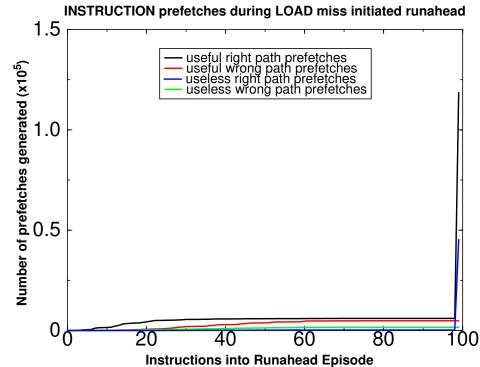

| Figure 4.38 | Instruction Stream Prefetch Utility for IJPEG              |    |

|             | INSTRUCTION prefetches during LOAD miss initiated runahead | 98 |

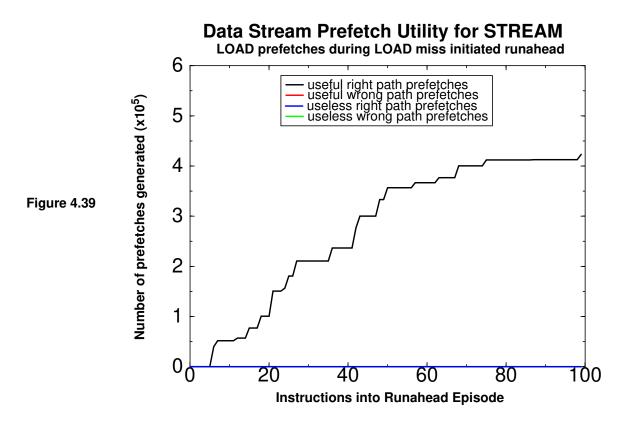

| Figure 4.39 | Data Stream Prefetch Utility for STREAM                    |    |

|             | LOAD prefetches during LOAD miss initiated runahead        | 98 |

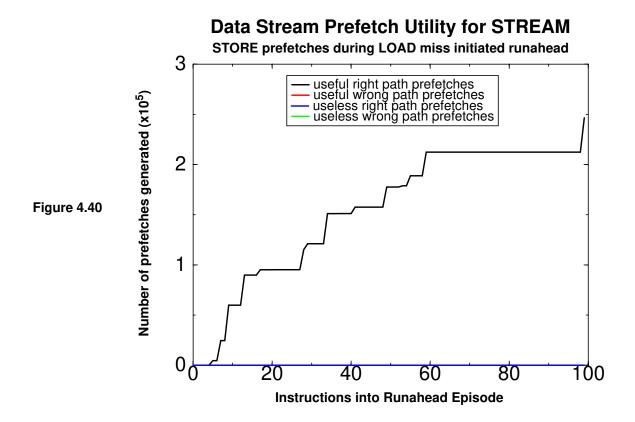

| Figure 4.40 | Data Stream Prefetch Utility for STREAM                    |    |

|             | STORE prefetches during LOAD miss initiated runahead       | 99 |

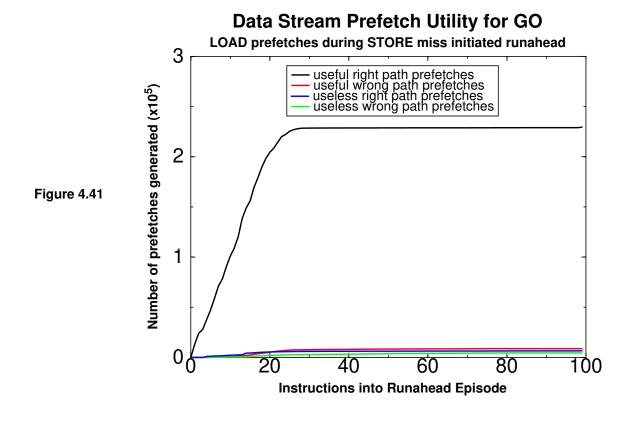

| Figure 4.41 | Data Stream Prefetch Utility for GO                            |

|-------------|----------------------------------------------------------------|

|             | LOAD prefetches during STORE miss initiated runahead101        |

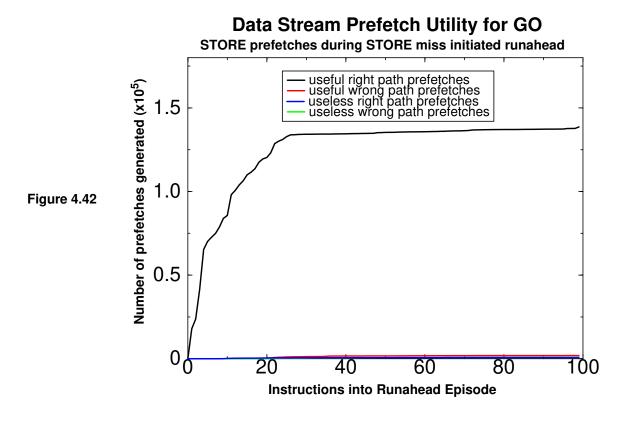

| Figure 4.42 | Data Stream Prefetch Utility for GO                            |

|             | STORE prefetches during STORE miss initiated runahead101       |

| Figure 4.43 | Instruction Stream Prefetch Utility for GO                     |

|             | INSTRUCTION prefetches during STORE miss initiated runahead102 |

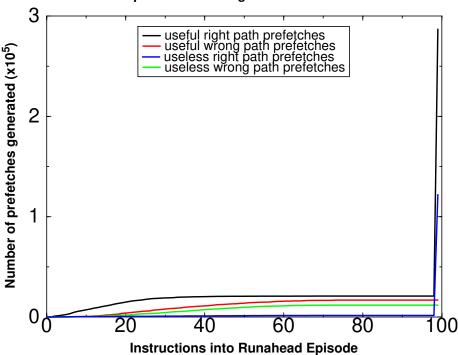

| Figure 4.44 | Data Stream Prefetch Utility for VORTEX                        |

|             | LOAD prefetches during STORE miss initiated runahead102        |

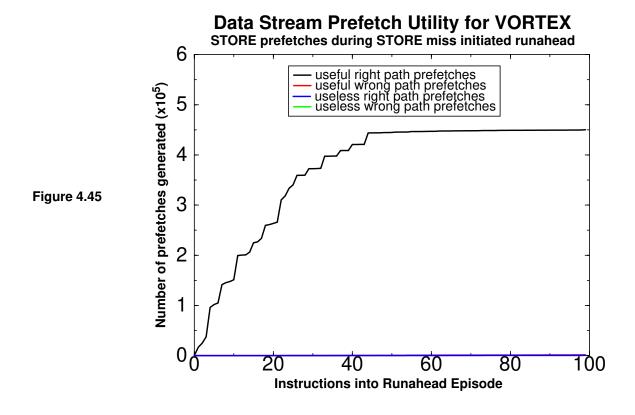

| Figure 4.45 | Data Stream Prefetch Utility for VORTEX                        |

|             | STORE prefetches during STORE miss initiated runahead103       |

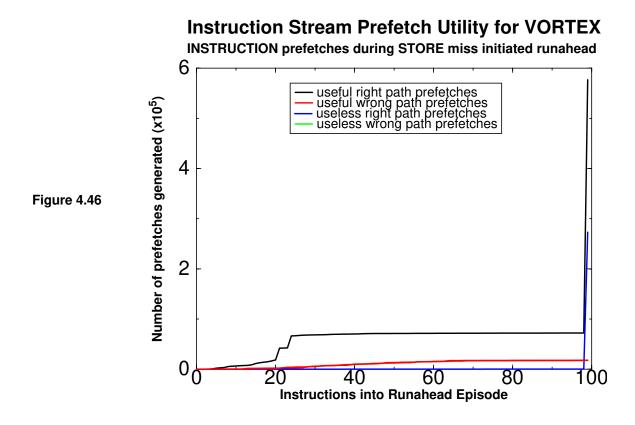

| Figure 4.46 | Instruction Stream Prefetch Utility for VORTEX                 |

|             | INSTRUCTION prefetches during STORE miss initiated runahead103 |

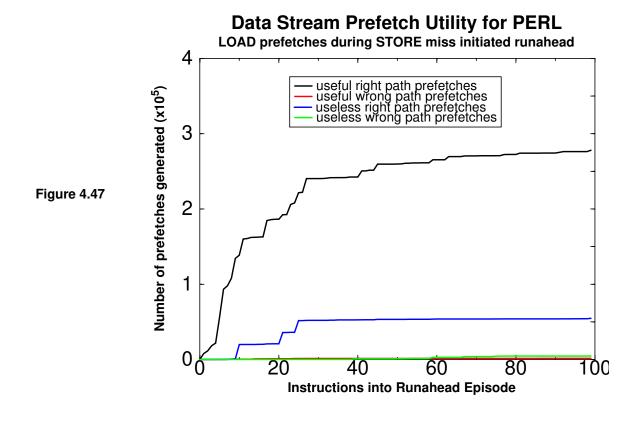

| Figure 4.47 | Data Stream Prefetch Utility for PERL                          |

|             | LOAD prefetches during STORE miss initiated runahead104        |

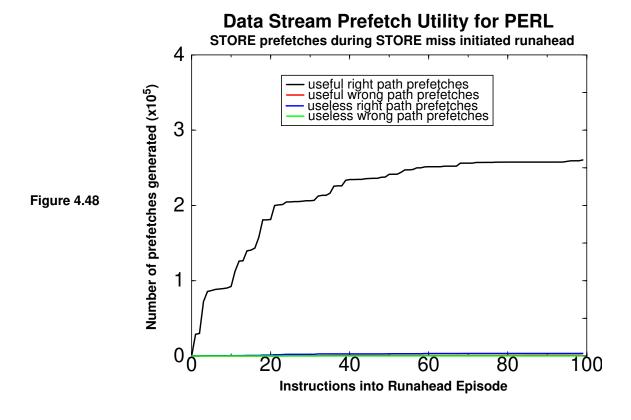

| Figure 4.48 | Data Stream Prefetch Utility for PERL                          |

|             | STORE prefetches during STORE miss initiated runahead104       |

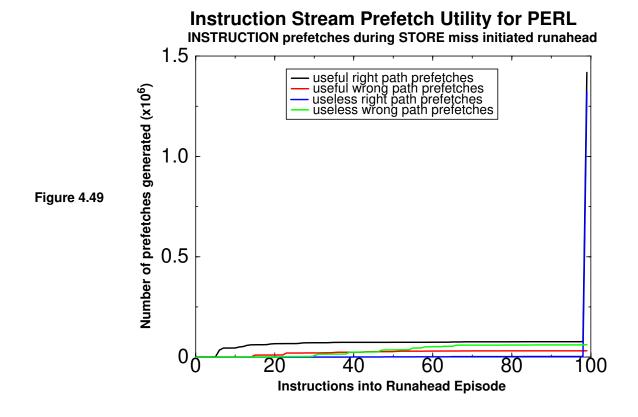

| Figure 4.49 | Instruction Stream Prefetch Utility for PERL                   |

|             | INSTRUCTION prefetches during STORE miss initiated runahead105 |

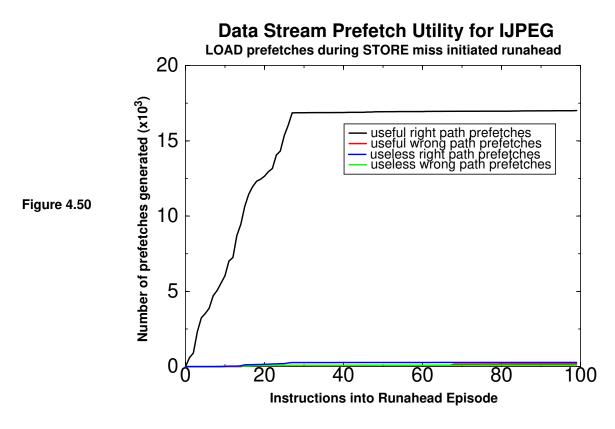

| Figure 4.50 | Data Stream Prefetch Utility for IJPEG                         |

|             | LOAD prefetches during STORE miss initiated runahead105        |

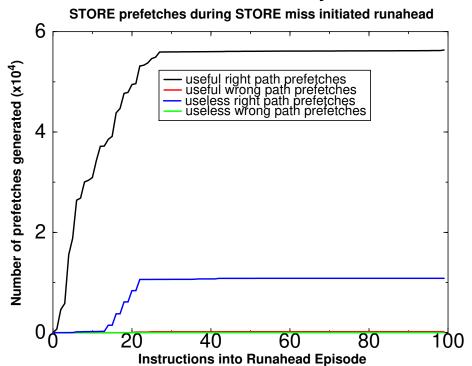

| Figure 4.51 | Data Stream Prefetch Utility for IJPEG                         |

|             | STORE prefetches during STORE miss initiated runahead106       |

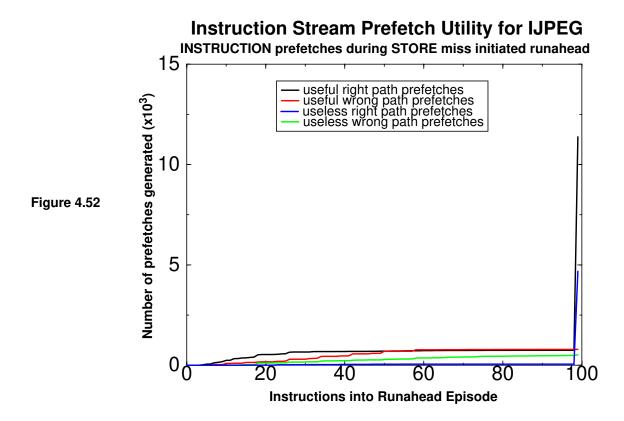

| Figure 4.52 | Instruction Stream Prefetch Utility for IJPEG                  |

|             | INSTRUCTION prefetches during STORE miss initiated runahead106 |

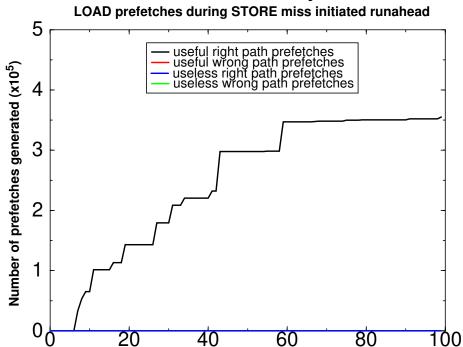

| Figure 4.53 | Data Stream Prefetch Utility for STREAM                        |

|             | LOAD prefetches during STORE miss initiated runahead107        |

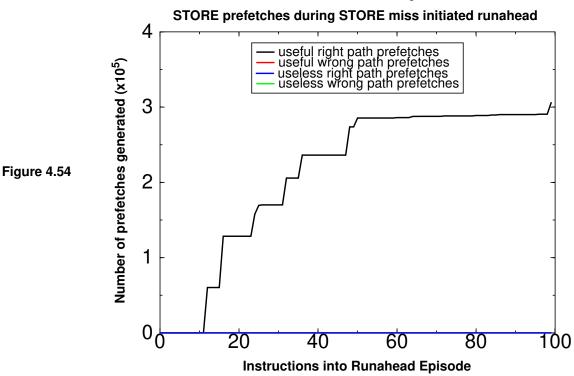

| Figure 4.54 | Data Stream Prefetch Utility for STREAM                        |

|             | STORE prefetches during STORE miss initiated runahead107       |

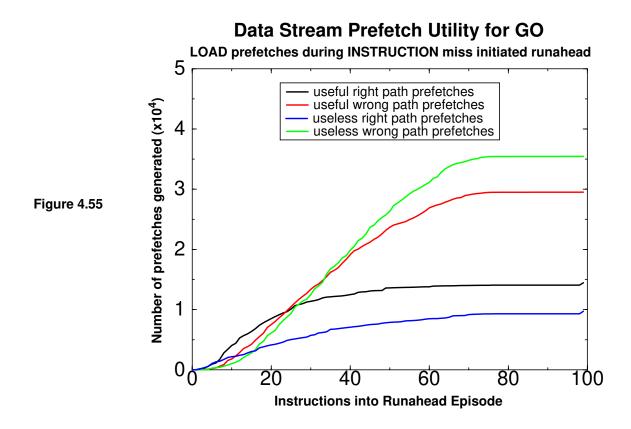

| Figure 4.55 | Data Stream Prefetch Utility for GO                            |

|             | LOAD prefetches during INSTRUCTION miss initiated runahead110  |

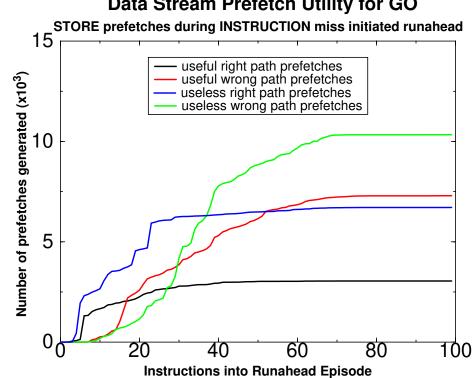

| Figure 4.56 | Data Stream Prefetch Utility for GO                            |

|             | STORE prefetches during INSTRUCTION miss initiated runahead111 |

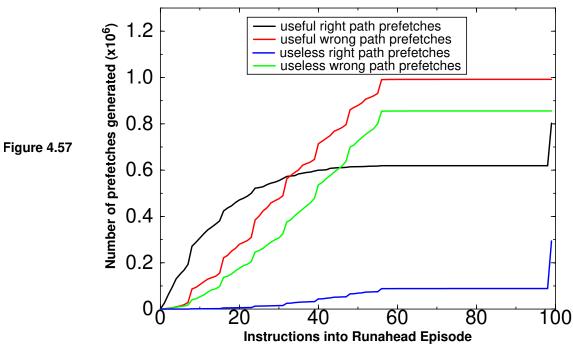

| Figure 4.57 | Instruction Stream Prefetch Utility for GO                     |

|             | INSTRUCTION prefetches during INSTRUCTION miss initiated       |

|             | runahead 111                                                   |

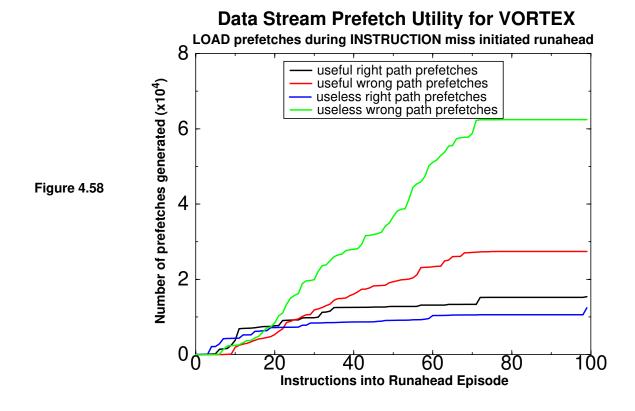

| Figure 4.58 | Data Stream Prefetch Utility for VORTEX                     |     |

|-------------|-------------------------------------------------------------|-----|

|             | LOAD prefetches during INSTRUCTION miss initiated runahead  | 112 |

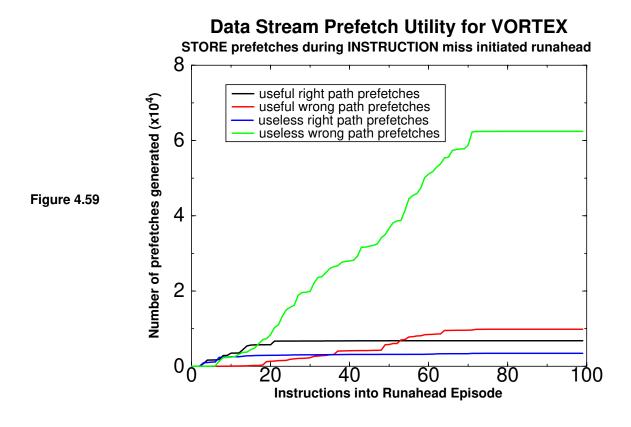

| Figure 4.59 | Data Stream Prefetch Utility for VORTEX                     |     |

|             | STORE prefetches during INSTRUCTION miss initiated runahead | 112 |

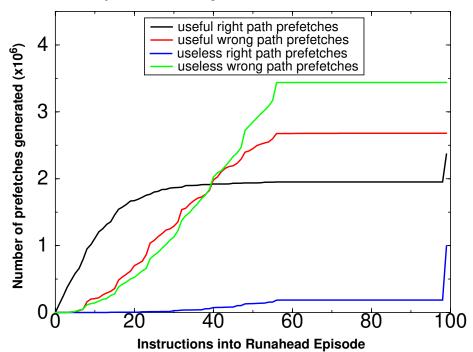

| Figure 4.60 | Instruction Stream Prefetch Utility for VORTEX              |     |

|             | INSTRUCTION prefetches during INSTRUCTION miss initiated    |     |

|             | runahead                                                    | 113 |

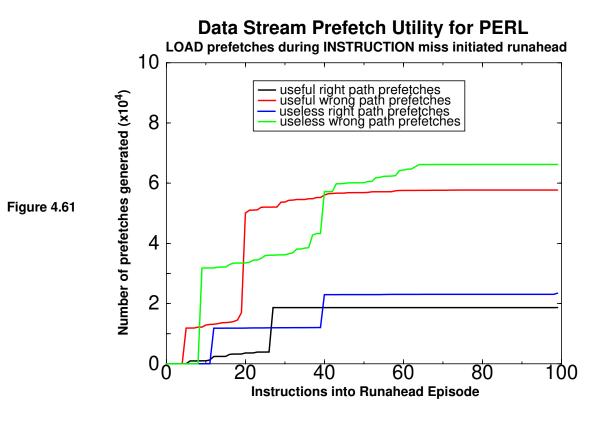

| Figure 4.61 | Data Stream Prefetch Utility for PERL                       |     |

|             | LOAD prefetches during INSTRUCTION miss initiated runahead  | 113 |

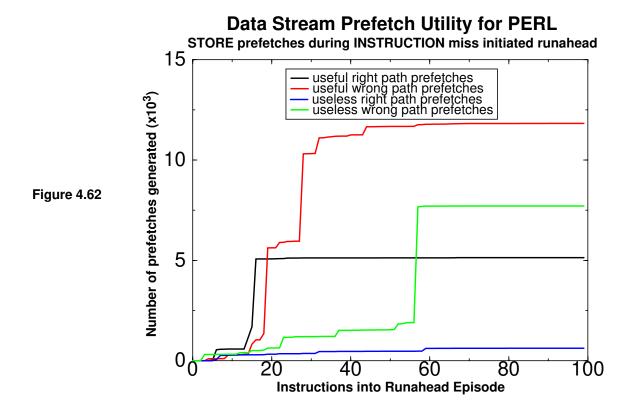

| Figure 4.62 | Data Stream Prefetch Utility for PERL                       |     |

|             | STORE prefetches during INSTRUCTION miss initiated runahead | 114 |

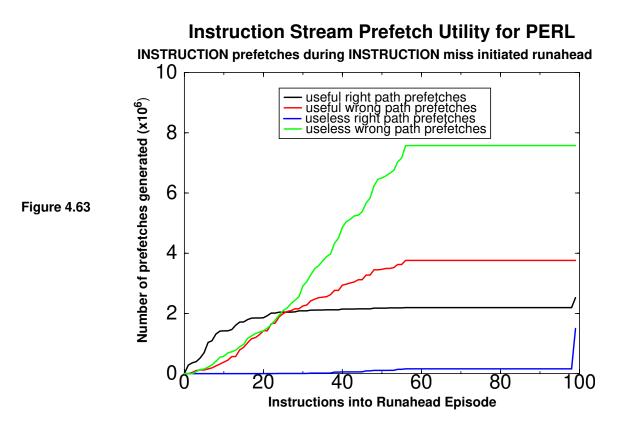

| Figure 4.63 | Instruction Stream Prefetch Utility for PERL                |     |

|             | INSTRUCTION prefetches during INSTRUCTION miss initiated    |     |

|             | runahead                                                    | 114 |

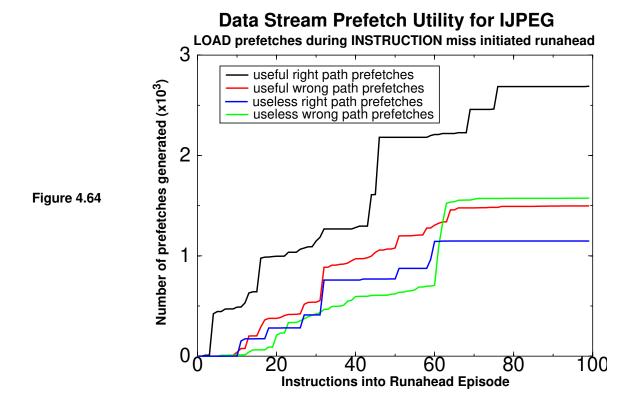

| Figure 4.64 | Data Stream Prefetch Utility for IJPEG                      |     |

|             | LOAD prefetches during INSTRUCTION miss initiated runahead  | 115 |

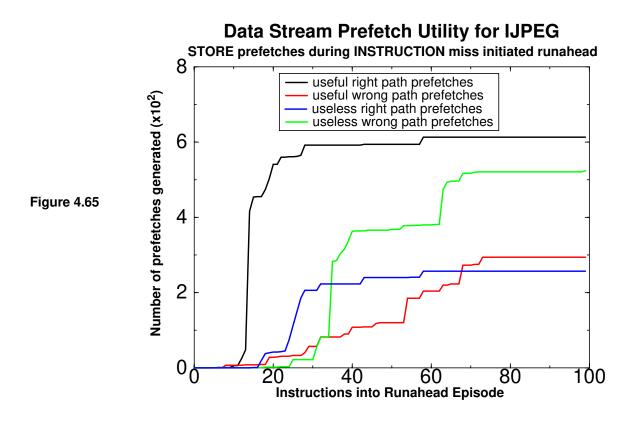

| Figure 4.65 | Data Stream Prefetch Utility for IJPEG                      |     |

|             | STORE prefetches during INSTRUCTION miss initiated runahead | 115 |

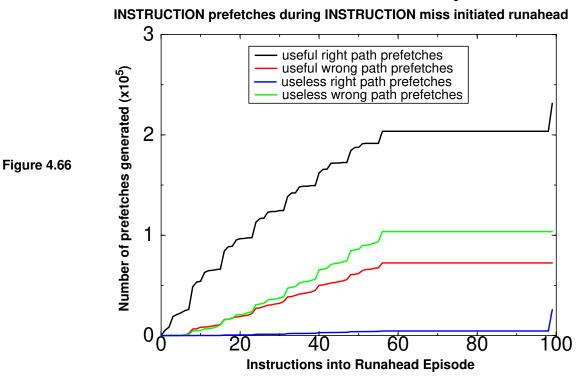

| Figure 4.66 | Instruction Stream Prefetch Utility for IJPEG               |     |

|             | INSTRUCTION prefetches during INSTRUCTION miss initiated    |     |

|             | runahead                                                    | 116 |

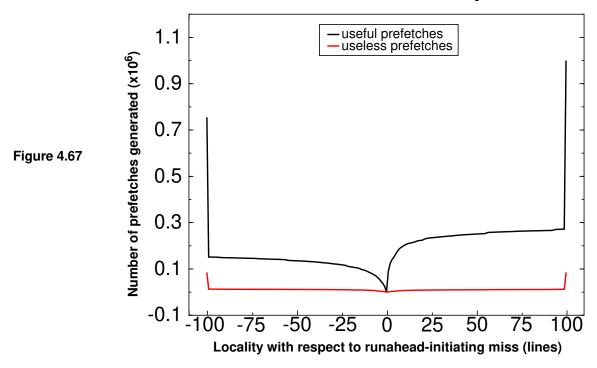

| Figure 4.67 | Data Stream Prefetch Locality for GO                        |     |

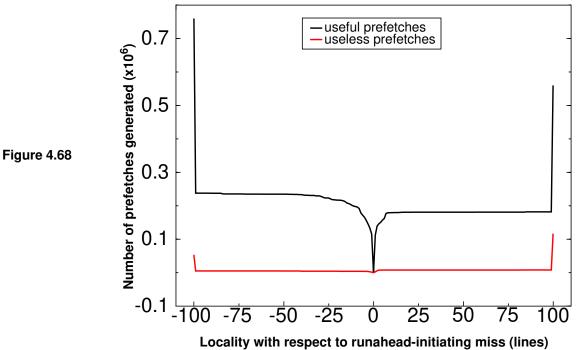

| Figure 4.68 | Data Stream Prefetch Locality for PERL                      | 119 |

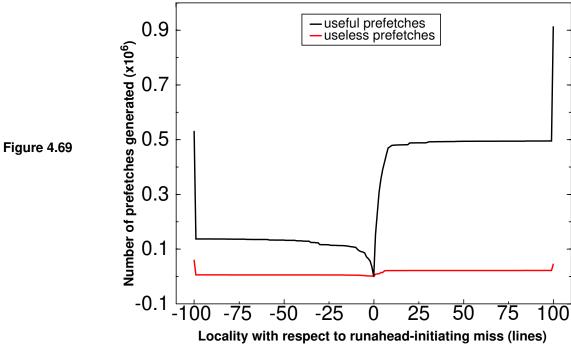

| Figure 4.69 | Data Stream Prefetch Locality for VORTEX                    | 120 |

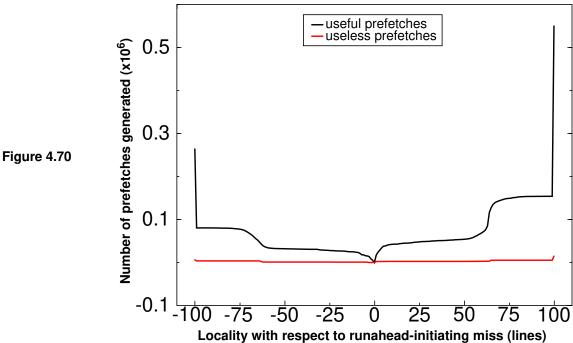

| Figure 4.70 | Data Stream Prefetch Locality for IJPEG                     | 120 |

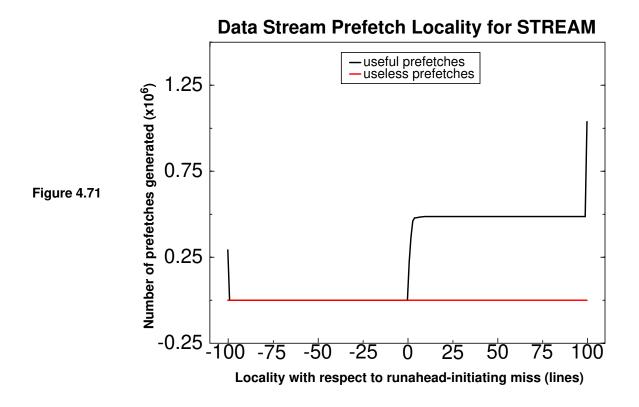

| Figure 4.71 | Data Stream Prefetch Locality for STREAM                    | 121 |

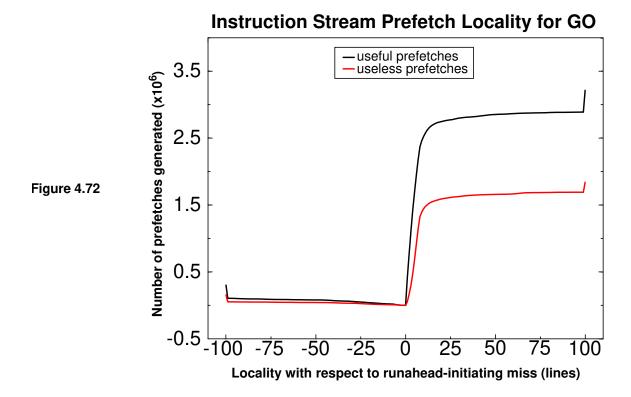

| Figure 4.72 | Instruction Stream Prefetch Locality for GO                 | 123 |

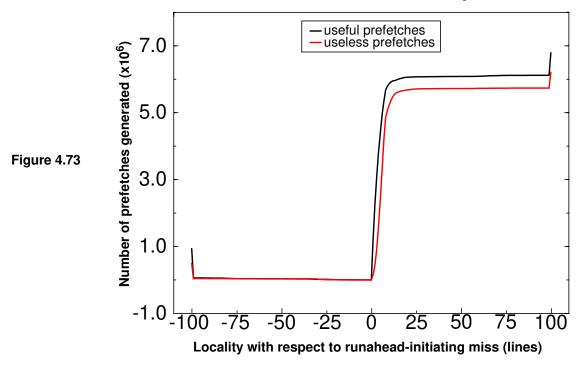

| Figure 4.73 | Instruction Stream Prefetch Locality for VORTEX             | 123 |

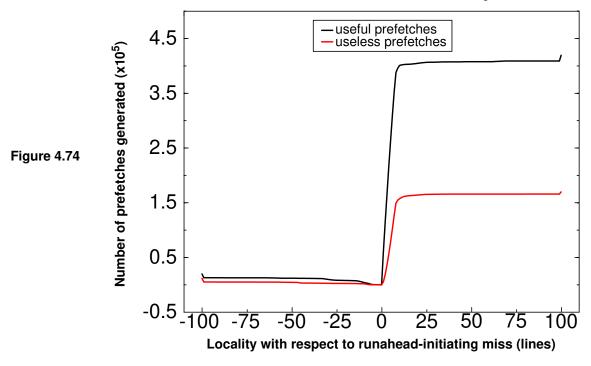

| Figure 4.74 | Instruction Stream Prefetch Locality for IJPEG              | 124 |

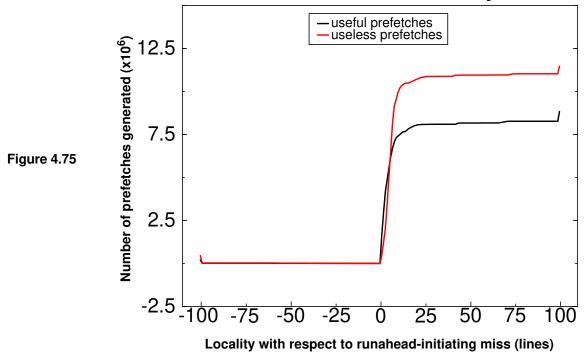

| Figure 4.75 | Instruction Stream Prefetch Locality for PERL               | 124 |

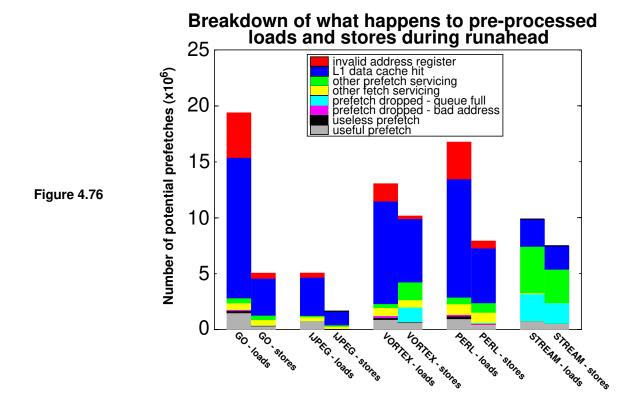

| Figure 4.76 | Breakdown of what happens to pre-processed loads and stores |     |

|             | during runahead                                             | 127 |

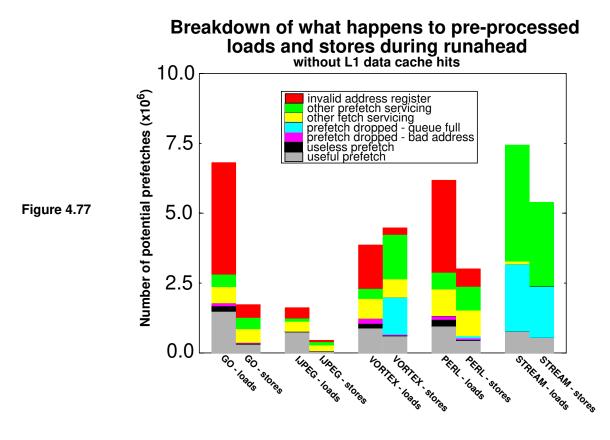

| Figure 4.77 | Breakdown of what happens to pre-processed loads and stores |     |

|             | during runahead: without L1 data cache hits                 | 127 |

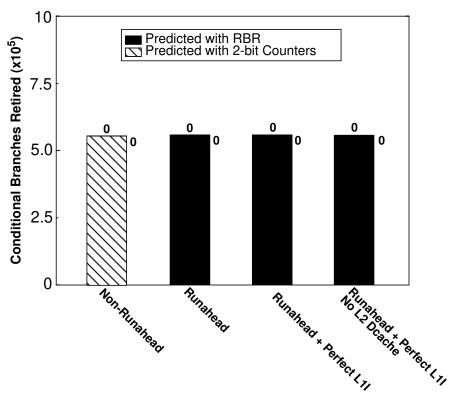

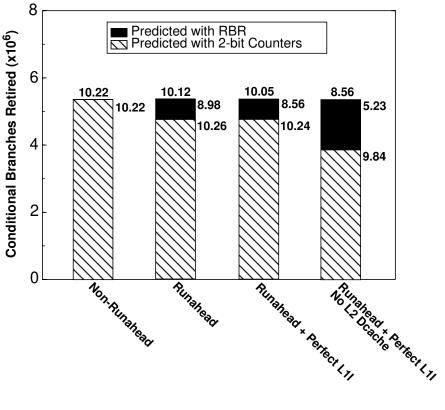

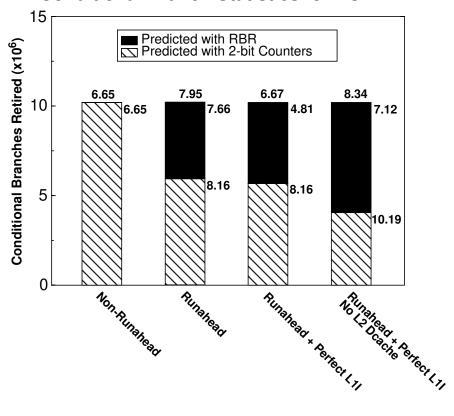

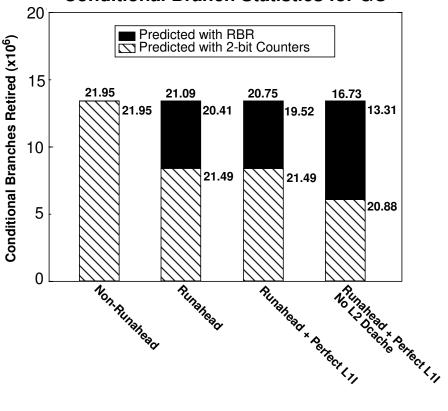

| Figure 4.78 | Conditional Branch Statistics for STREAM                    | 135 |

| Figure 4.79 | Conditional Branch Statistics for IJPEG                     | 135 |

| Figure 4.80 | Conditional Branch Statistics for VORTEX                        | 136 |

|-------------|-----------------------------------------------------------------|-----|

| Figure 4.81 | Conditional Branch Statistics for GO                            | 136 |

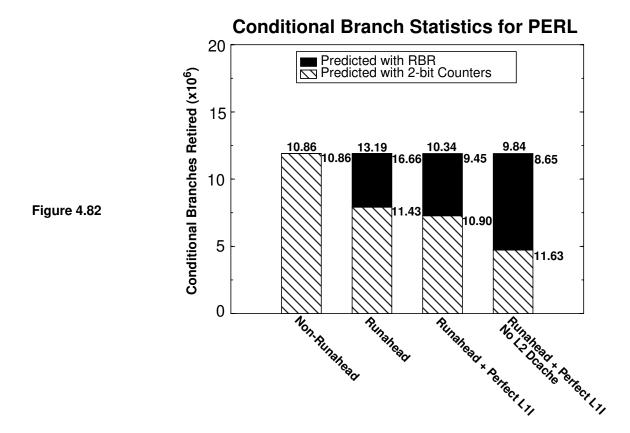

| Figure 4.82 | Conditional Branch Statistics for PERL                          | 137 |

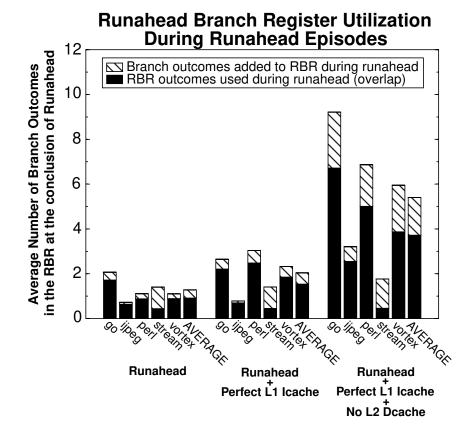

| Figure 4.83 | Runahead Branch Register Utilization During Runahead Episodes   | 139 |

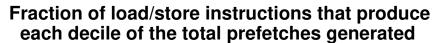

| Figure 5.1  | Fraction of load/store instructions that produce each decile of |     |

|             | the total prefetches generated                                  | 148 |

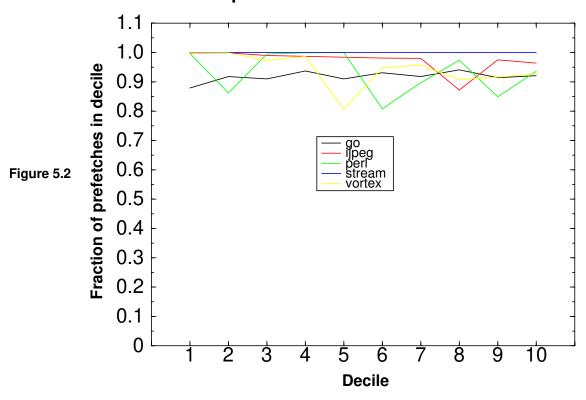

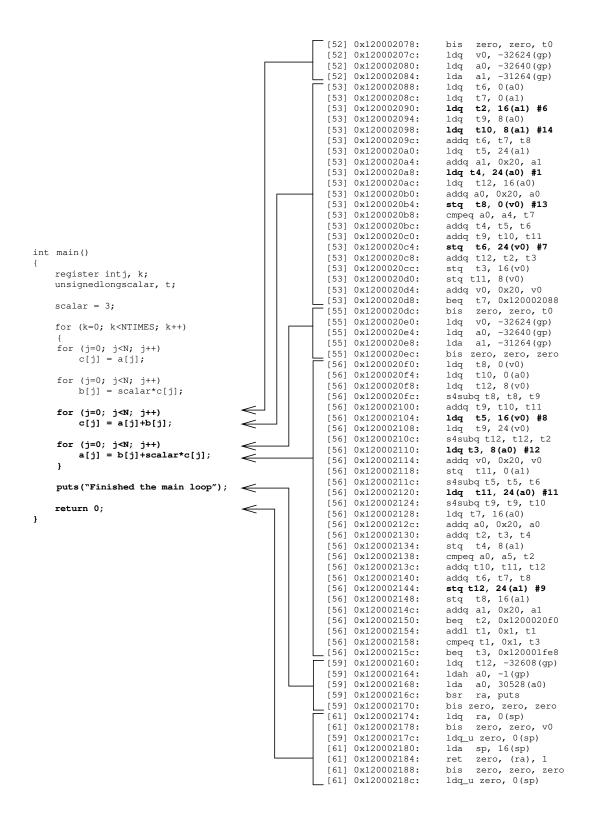

| Figure 5.2  | Fraction of prefetches in each decile that are useful           | 150 |

| Figure 5.3  | addlist() function from the GO benchmark                        | 151 |

| Figure 5.4  | undercut() function from the GO benchmark                       | 152 |

| Figure 5.5  | dellist() function from the GO benchmark                        | 153 |

| Figure 5.6  | blockuc() function from the GO benchmark                        | 154 |

| Figure 5.7  | cpylist() function from the GO benchmark                        | 155 |

| Figure 5.8  | mrglist() function from the GO benchmark                        | 156 |

| Figure 5.9  | findshapes() function from the GO benchmark                     | 157 |

| Figure 5.10 | rgb_ycc_convert() function from the IJPEG benchmark             | 158 |

| Figure 5.11 | Chunk_ChkGetChunk() function from the VORTEX benchmark          | 159 |

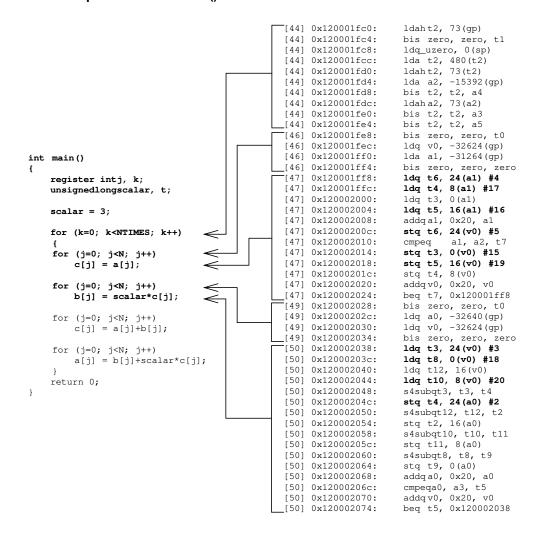

| Figure 5.12 | First portion of the main() function from the STREAM benchmark  | 161 |

| Figure 5.13 | Second portion of the main() function from the STREAM benchmark | 162 |

| Figure 5.14 | Prefetch address computation example                            | 165 |

| Figure 5.15 | Source of Data Stream Prefetch Addresses for GO                 | 168 |

| Figure 5.16 | Source of Data Stream Prefetch Addresses for VORTEX             | 168 |

| Figure 5.17 | Source of Data Stream Prefetch Addresses for PERL               | 169 |

| Figure 5.18 | Source of Data Stream Prefetch Addresses for IJPEG              | 169 |

| Figure 5.19 | Source of Data Stream Prefetch Addresses for STREAM             | 170 |

| Figure 5.20 | Source of Branch Conditions for GO                              | 171 |

| Figure 5.21 | Source of Branch Conditions for VORTEX                          | 172 |

| Figure 5.22 | Source of Branch Conditions for PERL                            | 172 |

| Figure 5.23 | Source of Branch Conditions for IJPEG                           | 173 |

| Figure 5.24 | Source of Branch Conditions for STREAM                          | 173 |

| Figure 5.25 | Source of Indirect Branch Targets for GO                        | 174 |

| Figure 5.26 | Source of Indirect Branch Targets for PERL                      | 175 |

| Figure 5.27 | Source of Indirect Branch Targets for VORTEX                    | 175 |

| Figure 5.28 | Source of Indirect Branch Targets for IJPEG                     | 176 |

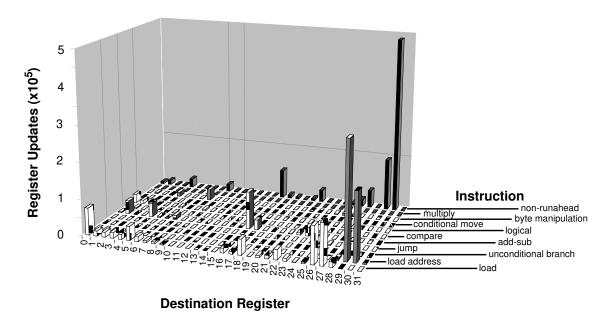

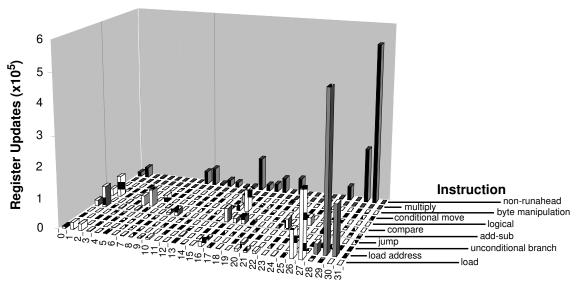

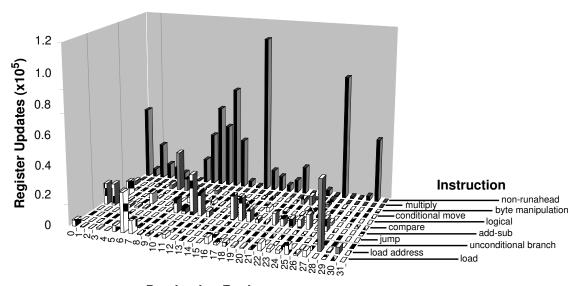

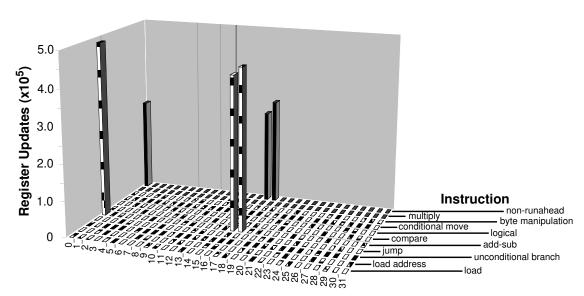

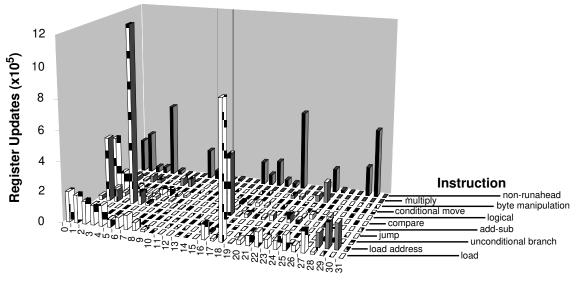

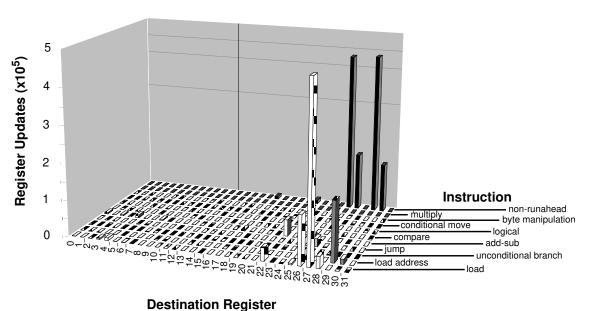

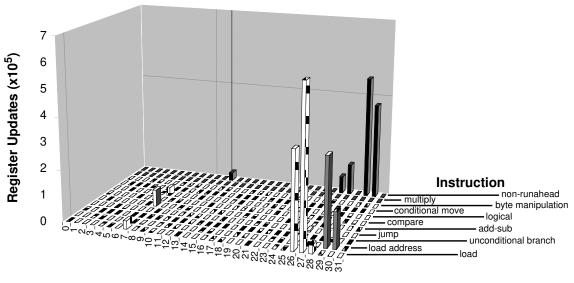

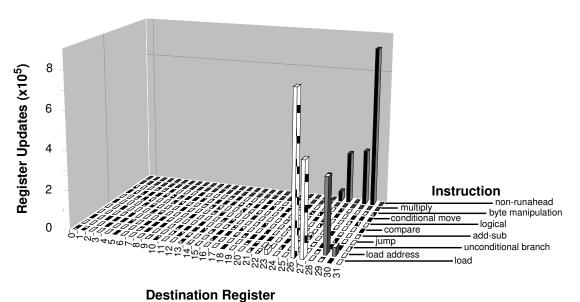

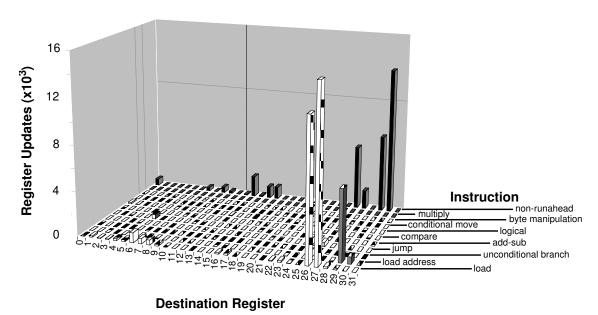

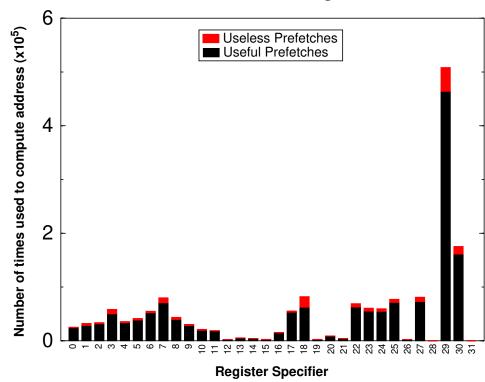

| Figure 5.29 | Load Prefetch Address Registers for GO                          | 178 |

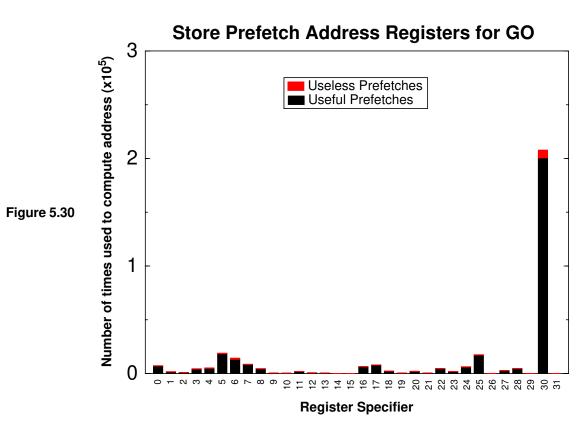

| Figure 5.30 | Store Prefetch Address Registers for GO                         | 178 |

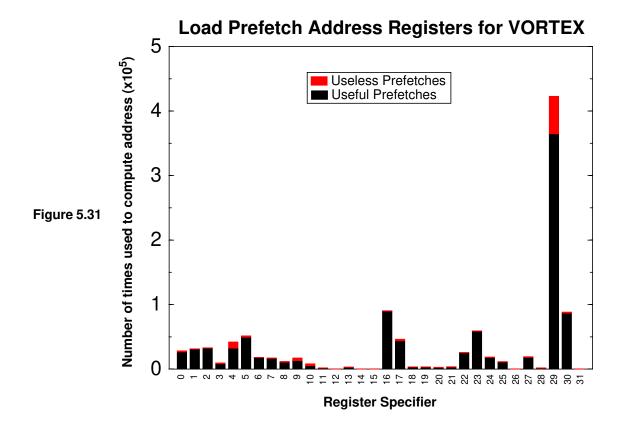

| Figure 5.31 | Load Prefetch Address Registers for VORTEX                      | 179 |

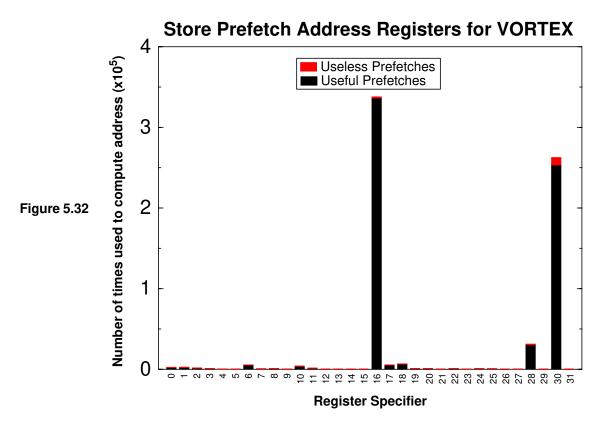

| Figure 5.32 | Store Prefetch Address Registers for VORTEX                                     | 179 |

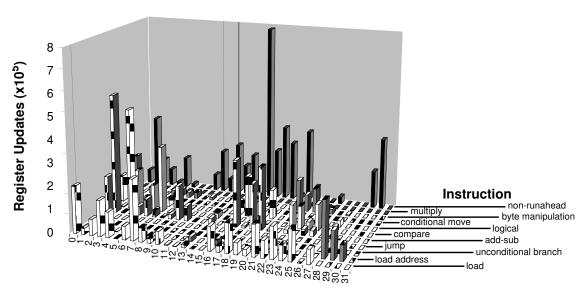

|-------------|---------------------------------------------------------------------------------|-----|

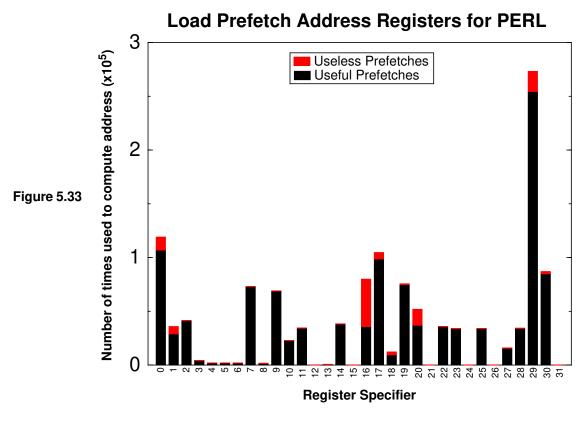

| Figure 5.33 | Load Prefetch Address Registers for PERL                                        | 180 |

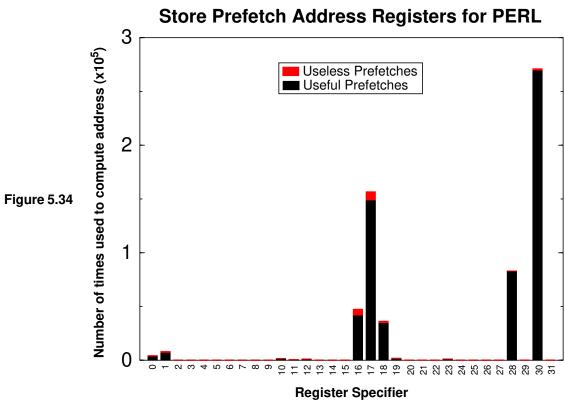

| Figure 5.34 | Store Prefetch Address Registers for PERL                                       | 180 |

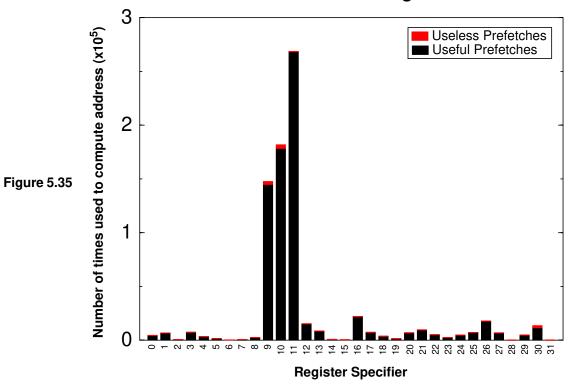

| Figure 5.35 | Load Prefetch Address Registers for IJPEG                                       | 181 |

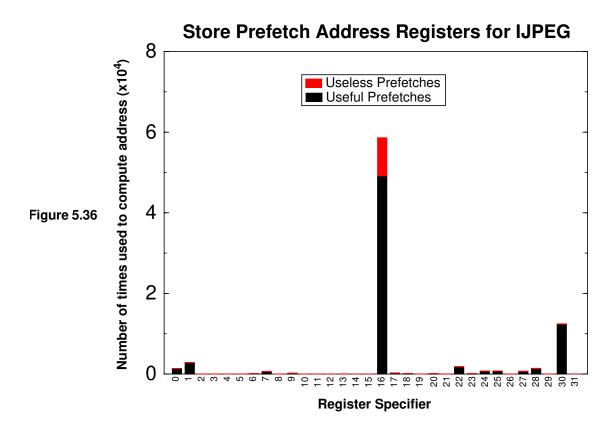

| Figure 5.36 | Store Prefetch Address Registers for IJPEG                                      | 181 |

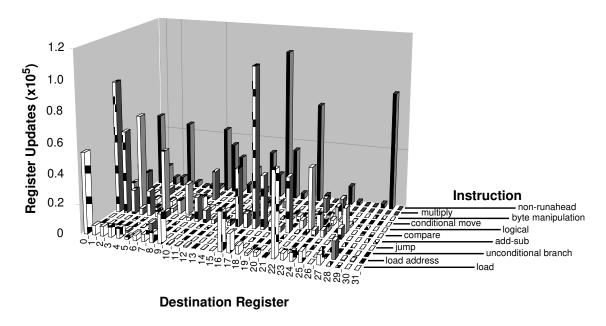

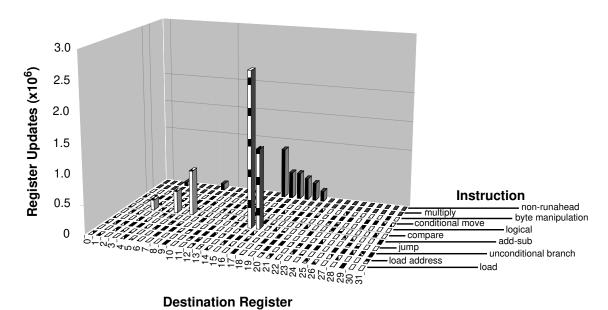

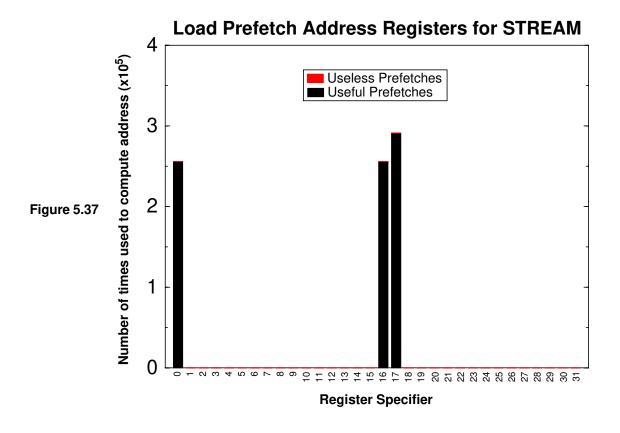

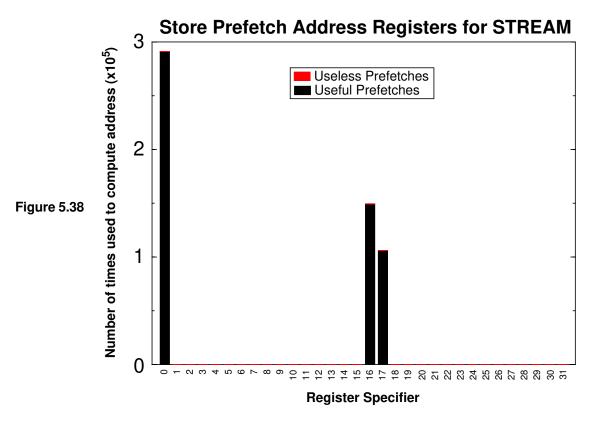

| Figure 5.37 | Load Prefetch Address Registers for STREAM                                      | 182 |

| Figure 5.38 | Store Prefetch Address Registers for STREAM                                     |     |

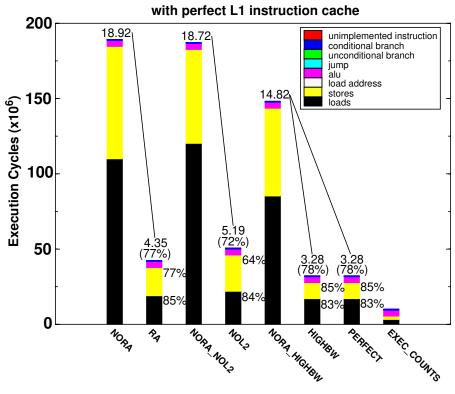

| Figure 6.1  | Processor CPI for the STREAM Benchmark                                          |     |

|             | with perfect L1 instruction cache                                               | 191 |

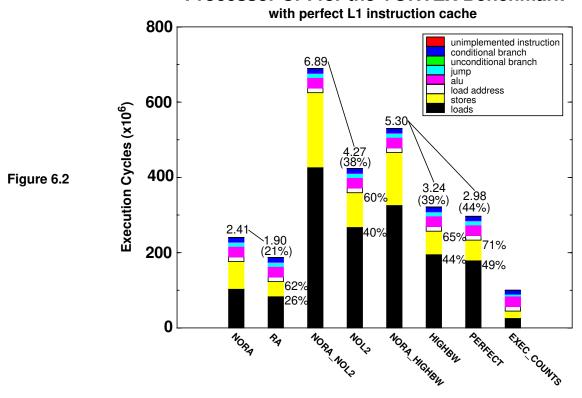

| Figure 6.2  | Processor CPI for the VORTEX Benchmark                                          |     |

|             | with perfect L1 instruction cache                                               | 191 |

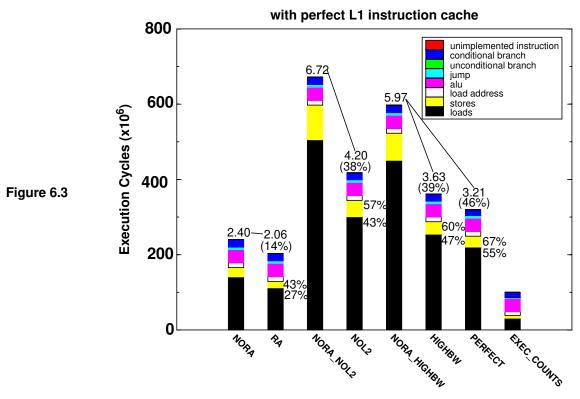

| Figure 6.3  | Processor CPI for the GO Benchmark                                              |     |

|             | with perfect L1 instruction cache                                               | 192 |

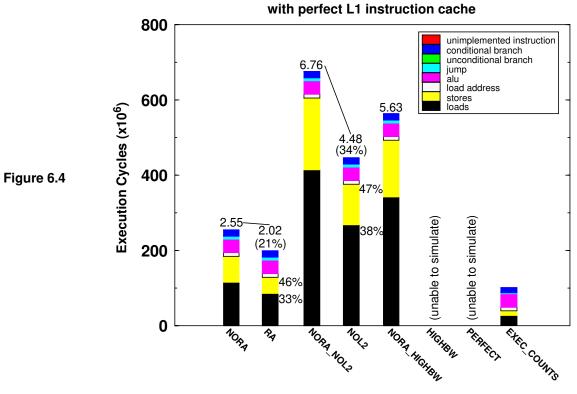

| Figure 6.4  | Processor CPI for the PERL Benchmark                                            |     |

|             | with perfect L1 instruction cache                                               | 192 |

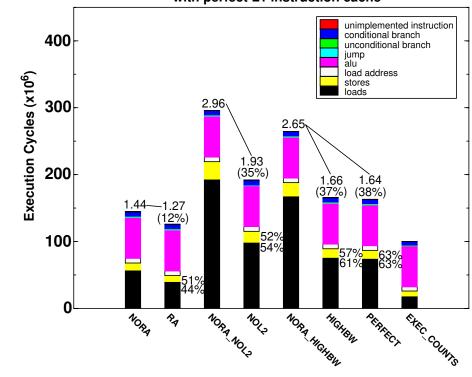

| Figure 6.5  | Processor CPI for the IJPEG Benchmark                                           |     |

|             | with perfect L1 instruction cache                                               | 193 |

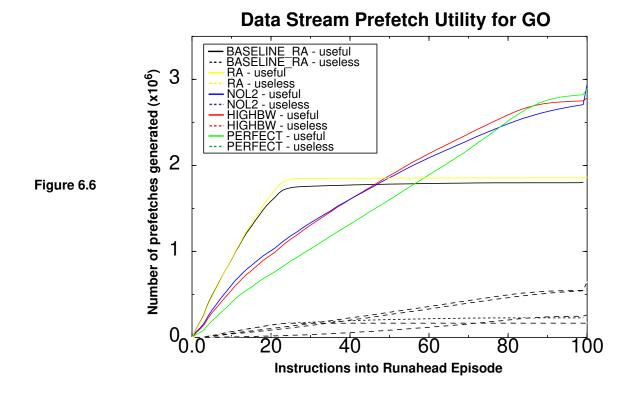

| Figure 6.6  | Data Stream Prefetch Utility for GO                                             | 196 |

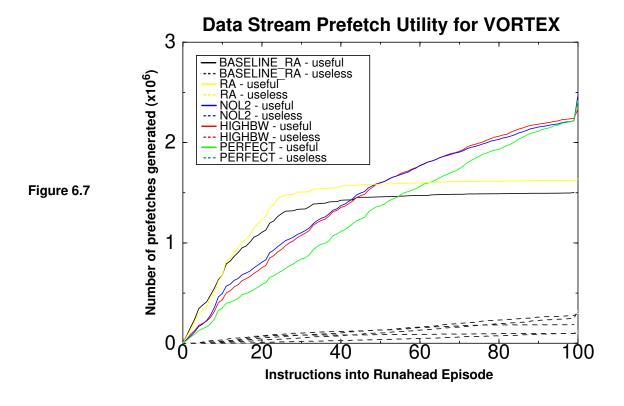

| Figure 6.7  | Data Stream Prefetch Utility for VORTEX                                         | 196 |

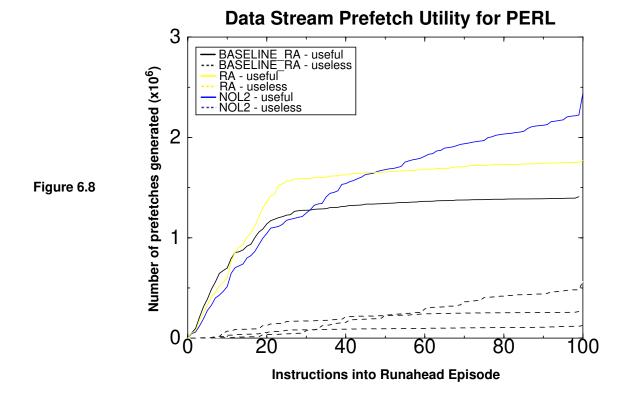

| Figure 6.8  | Data Stream Prefetch Utility for PERL                                           | 197 |

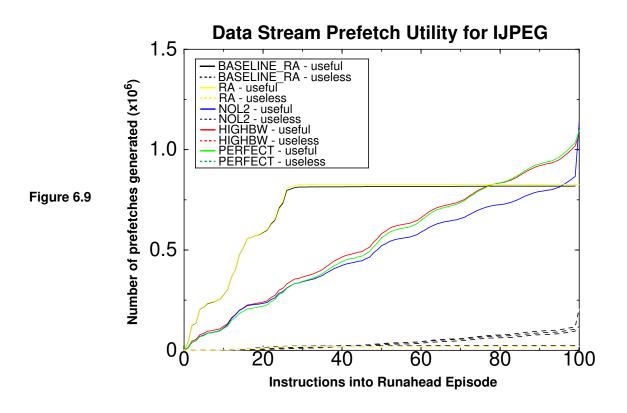

| Figure 6.9  | Data Stream Prefetch Utility for IJPEG                                          | 197 |

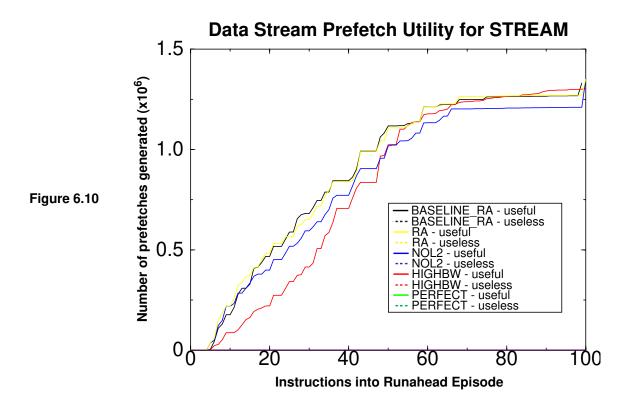

| Figure 6.10 | Data Stream Prefetch Utility for STREAM                                         | 198 |

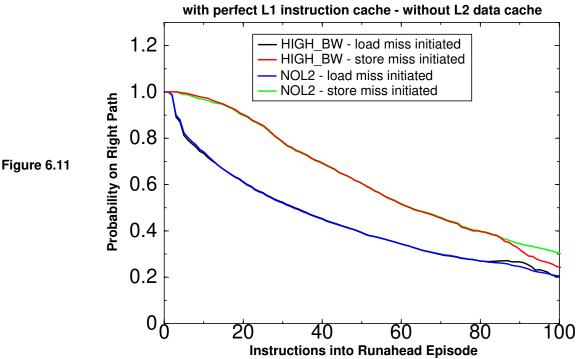

| Figure 6.11 | Probability Runahead on Right Path for GO                                       |     |

|             | with perfect L1 instruction cache - without L2 data cache                       | 200 |

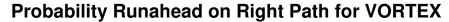

| Figure 6.12 | Probability Runahead on Right Path for VORTEX                                   |     |

|             | with perfect L1 instruction cache - without L2 data cache                       | 200 |

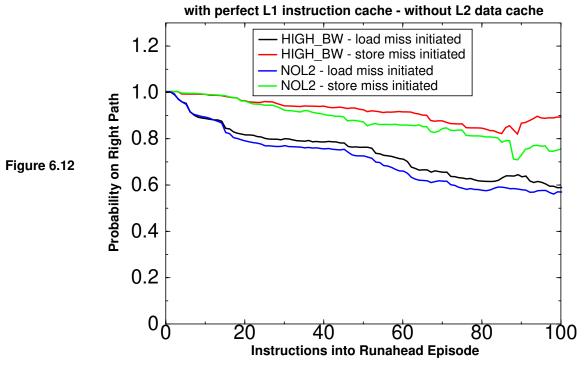

| Figure 6.13 | Probability Runahead on Right Path for PERL                                     |     |

|             | with perfect L1 instruction cache - without L2 data cache                       | 201 |

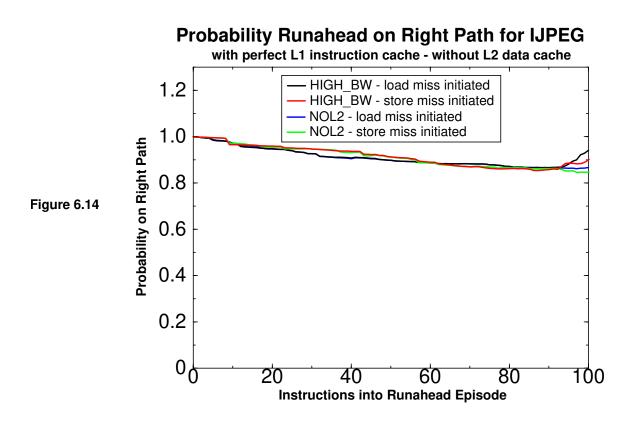

| Figure 6.14 | Probability Runahead on Right Path for IJPEG                                    |     |

|             | with perfect L1 instruction cache - without L2 data cache                       | 201 |

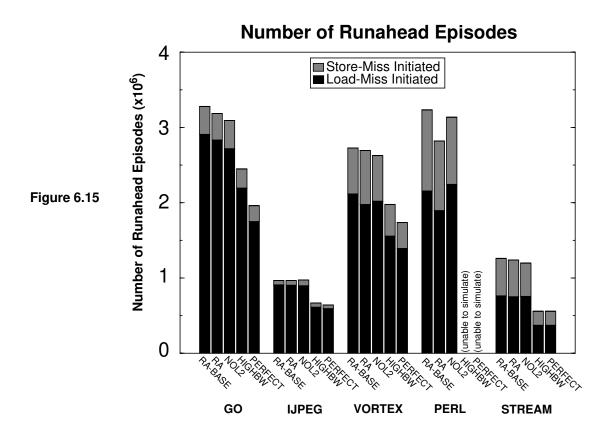

| Figure 6.15 | Number of Runahead Episodes                                                     | 203 |

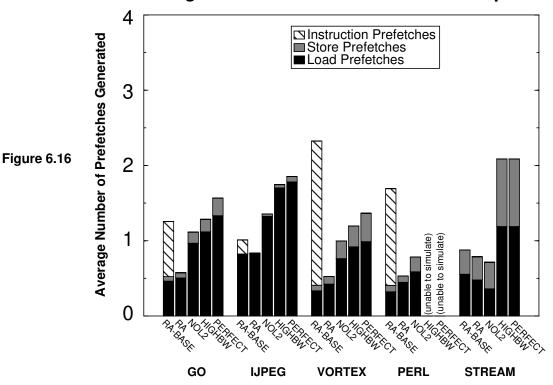

| Figure 6.16 | Number of Prefetches Generated during the Average Load-Miss Ir Runahead Episode |     |

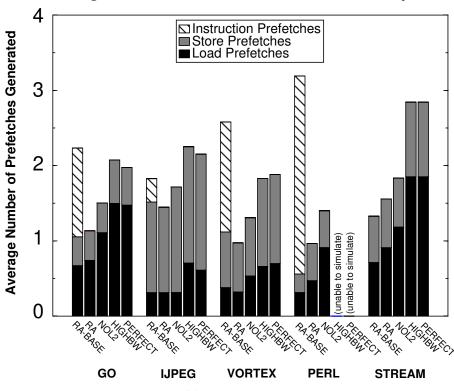

| Figure 6.17 | Number of Prefetches Generated during the Average Store-Miss In                 |     |

| 115010 0.17 | Runahead Episode                                                                |     |

| Figure 6.18 | Off-Chip Data Stream Fetch Traffic                                              |     |

| Figure 7.1  | Operation of the RA_NOCOPY register file implementation | 211 |

|-------------|---------------------------------------------------------|-----|

| Figure 7.2  | Operation of the RA_NOBRF register file implementation  | 213 |

| Figure 7.3  | Processor CPI for the GO Benchmark                      |     |

|             | simplified register file models                         | 219 |

| Figure 7.4  | Processor CPI for the PERL Benchmark                    |     |

|             | simplified register file models                         | 219 |

| Figure 7.5  | Processor CPI for the IJPEG Benchmark                   |     |

|             | simplified register file models                         | 220 |

| Figure 7.6  | Processor CPI for the VORTEX Benchmark                  |     |

|             | simplified register file models                         | 220 |

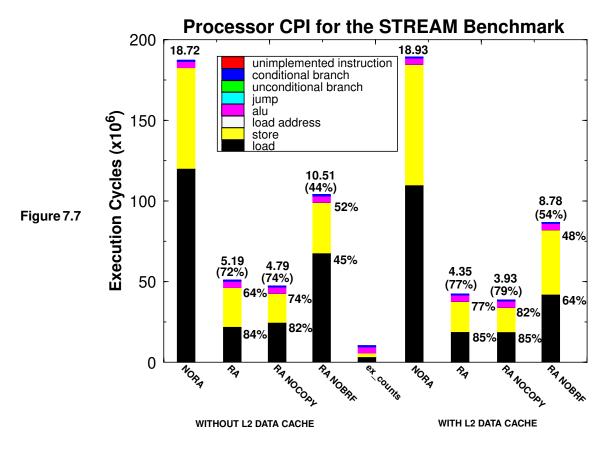

| Figure 7.7  | Processor CPI for the STREAM Benchmark                  |     |

|             | simplified register file models                         | 221 |

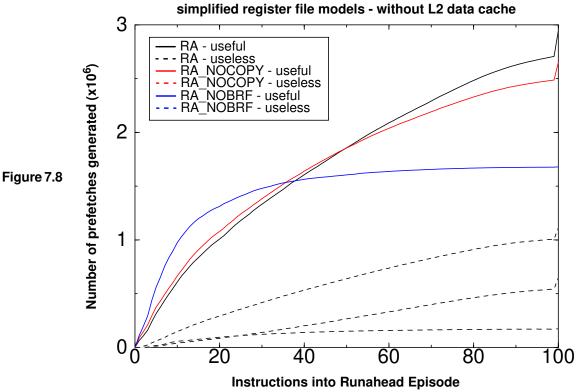

| Figure 7.8  | Data Stream Prefetch Utility for GO                     |     |

|             | simplified register file models - without L2 data cache | 221 |

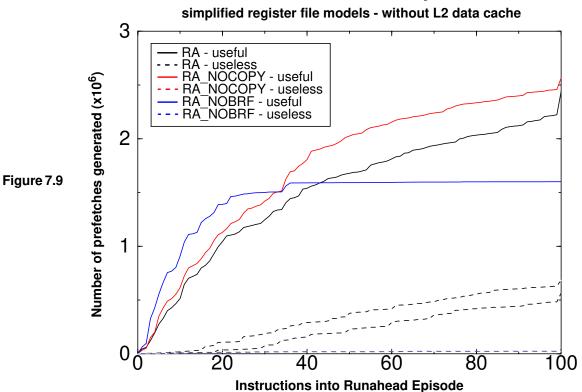

| Figure 7.9  | Data Stream Prefetch Utility for PERL                   |     |

|             | simplified register file models - without L2 data cache | 222 |

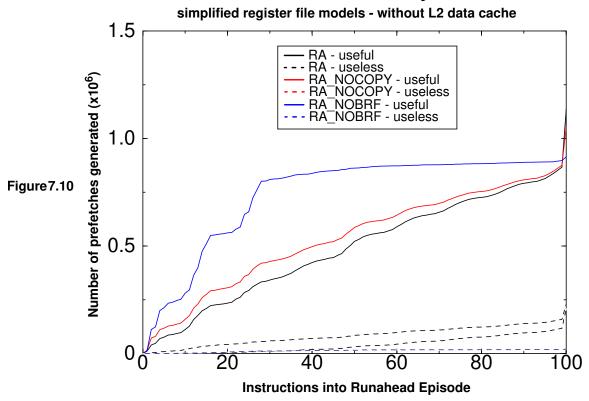

| Figure 7.10 | Data Stream Prefetch Utility for IJPEG                  |     |

|             | simplified register file models - without L2 data cache | 222 |

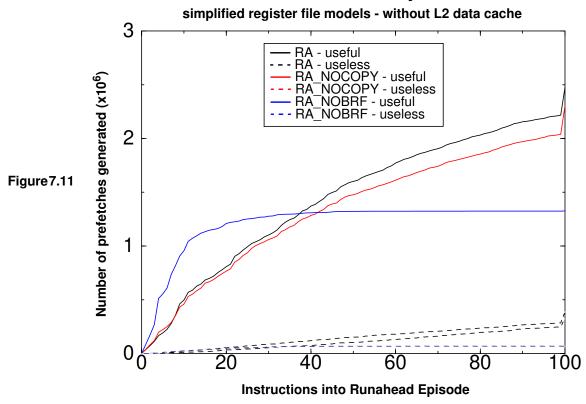

| Figure 7.11 | Data Stream Prefetch Utility for VORTEX                 |     |

|             | simplified register file models - without L2 data cache | 223 |

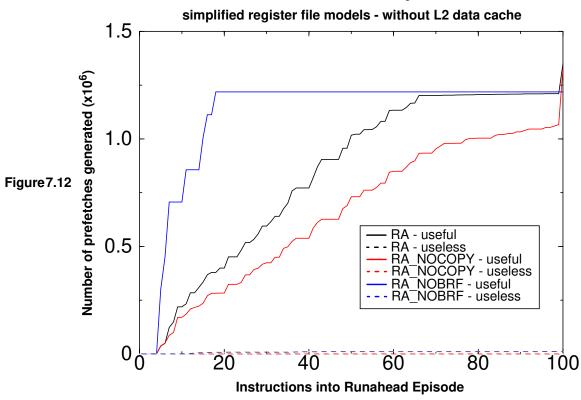

| Figure 7.12 | Data Stream Prefetch Utility for STREAM                 |     |

|             | simplified register file models - without L2 data cache | 223 |

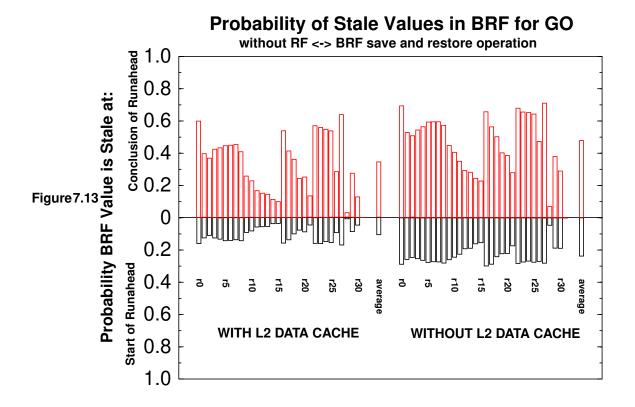

| Figure 7.13 | Probability of Stale Values in BRF for GO               |     |

|             | without RF<-> BRF save and restore operation            | 226 |

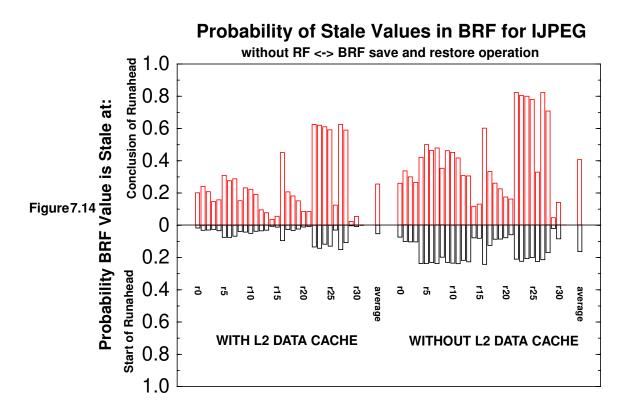

| Figure 7.14 | Probability of Stale Values in BRF for IJPEG            |     |

|             | without RF<-> BRF save and restore operation            | 226 |

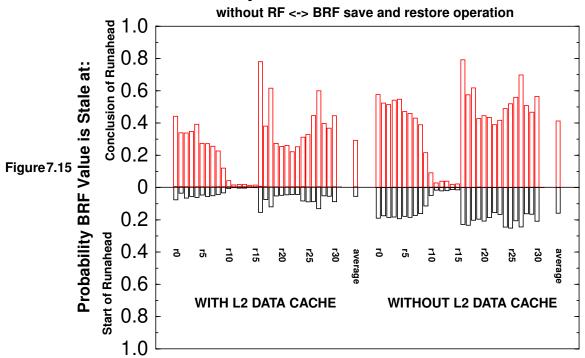

| Figure 7.15 | Probability of Stale Values in BRF for VORTEX           |     |

|             | without RF<-> BRF save and restore operation            | 227 |

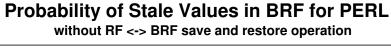

| Figure 7.16 | Probability of Stale Values in BRF for PERL             |     |

|             | without RF<-> BRF save and restore operation            | 227 |

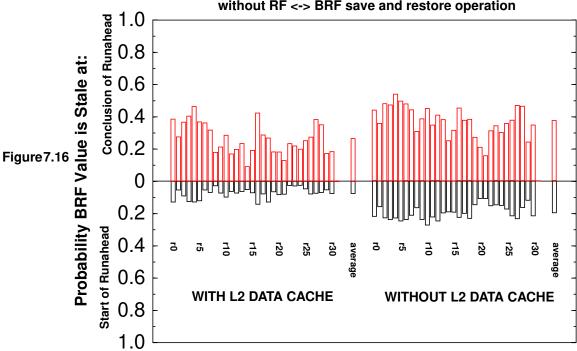

| Figure 7.17 | Probability of Stale Values in BRF for STREAM           |     |

|             | without RF<-> BRF save and restore operation            | 228 |

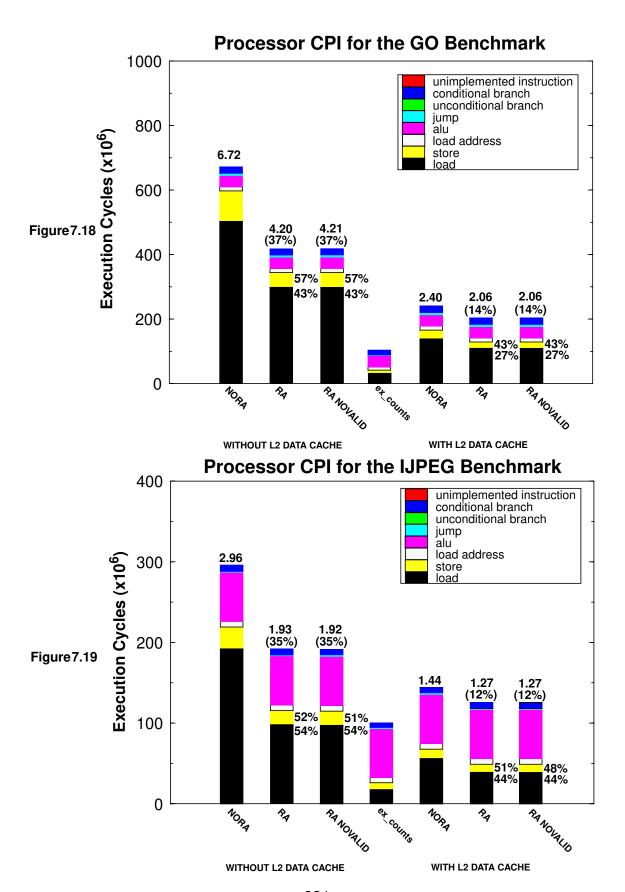

| Figure 7.18 | Processor CPI for the GO Benchmark                      |     |

|             | without L1 data cache runahead valid bits               | 231 |

| Figure 7.19 | Processor CPI for the IJPEG Benchmark     |     |

|-------------|-------------------------------------------|-----|

|             | without L1 data cache runahead valid bits | 231 |

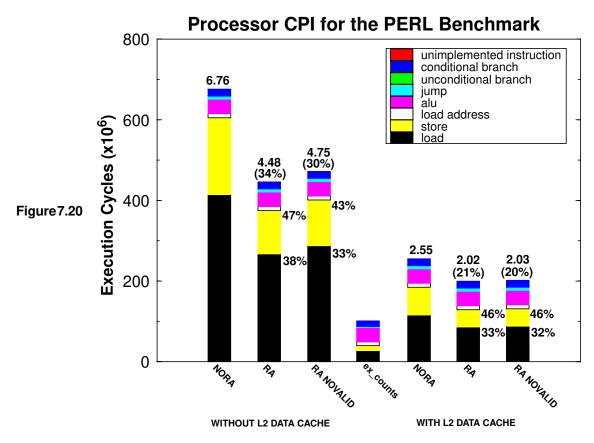

| Figure 7.20 | Processor CPI for the PERL Benchmark      |     |

|             | without L1 data cache runahead valid bits | 232 |

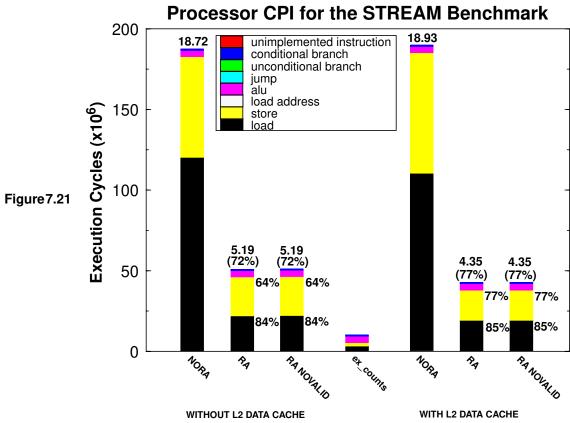

| Figure 7.21 | Processor CPI for the STREAM Benchmark    |     |

|             | without L1 data cache runahead valid bits | 232 |

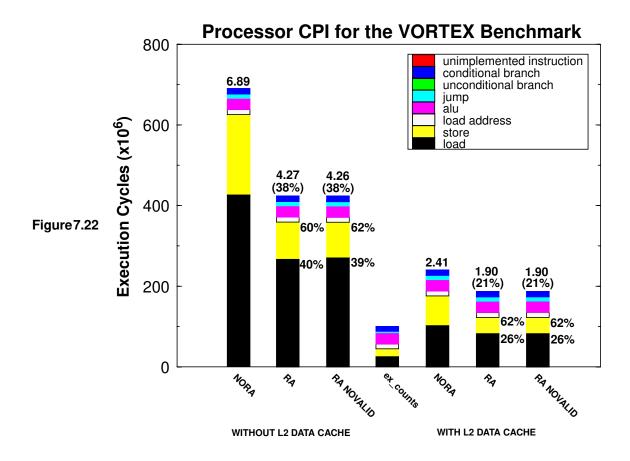

| Figure 7.22 | Processor CPI for the VORTEX Benchmark    |     |

|             | without L1 data cache runahead valid bits | 233 |

# LIST OF TABLES

| Table 3.1 | Benchmark Arguments                                       | 60  |

|-----------|-----------------------------------------------------------|-----|

| Table 5.1 | Prefetches Generated by Most Prolific Functions in GO     | 143 |

| Table 5.2 | Prefetches Generated by Most Prolific Functions in IJPEG  | 144 |

| Table 5.3 | Prefetches Generated by Most Prolific Functions in PERL   | 145 |

| Table 5.4 | Prefetches Generated by Most Prolific Functions in VORTEX | 146 |

| Table 5.5 | DEC OSF/1 Alpha Register Usage                            | 166 |

## Chapter 1

#### Runahead

The severe device count constraint forced upon the design space of a Gallium Arsenide processor led us to consider a number of unorthodox architectural ideas. One of these was runahead pre-processing. The basic idea is to allow a simple, yet very fast, processor pipeline to pre-process instructions during cache miss cycles, instead of stalling.

The pre-processed instructions are used to generate highly accurate instruction and data stream prefetches by detecting cache misses before they would otherwise occur, while all of the pre-processed instruction results are eventually discarded. This allows us to achieve a form of very aggressive speculation with a simple in-order pipeline. The principal hardware cost is a means of checkpointing the sequential state of the register file and memory hierarchy while instructions are pre-processed. Since we discard all results that are computed during runahead episodes after the cache miss has been serviced, the checkpointing can be accomplished with a modest amount of hardware.

By waiting until cache misses occur before generating prefetches, runahead adds a highly responsive feedback component to the memory hierarchy: the greater the cache miss penalty, the more opportunities there are for prefetching, which tend to reduce the frequency of future cache misses. Conversely, if an application enters a phase where its hit rate is high, few prefetches are generated.

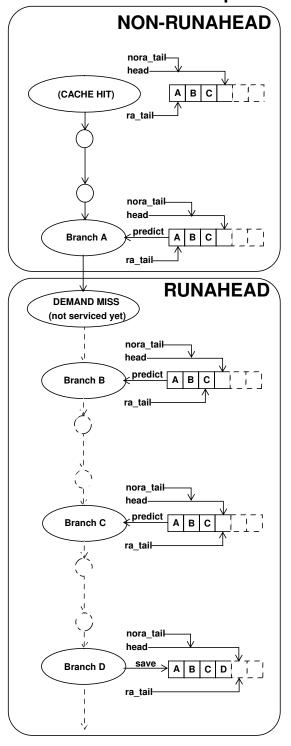

#### 1.1 Basic runahead theory

When a runahead processor detects an L1 instruction or data cache miss it records the instruction address of the faulting access and enters runahead mode. A demand fetch request for the missing instruction or data cache line is generated if necessary. The processor also checkpoints the register file, RF, by copying its contents to a backup register file, or BRF. The processor then pre-processes subsequent instructions while the cache miss is serviced. The goal is to generate prefetches for instructions and data that will be needed in the near future. If a pre-processed load or store generates a cache miss the processor can generate a prefetch for the missing line. Similarly, instruction fetch misses in the instruction cache during runahead become instruction stream prefetches. Because the value returned from a cache miss cannot be known ahead of time, it is possible for pre-processed instructions to be dependent upon invalid data. Rather than terminating runahead we allow registers and data cache values to have an explicit "invalid" state during runahead. Denoting this value, INV, requires an extra bit associated with each register in the RF as well as with each word in the L1 data cache (if byte or half-word addressing is allowed, additional bits are required). Pre-processing of most instructions consists of the usual steps of fetch, decode, and execute, with some changes to deal with INV data. Also stores are treated slightly differently. The actions associated with pre-processing can be summarized as follows:

- 1. **register-to-register** instructions mark their destination register INV if any of their source registers are marked INV. (They can also replace an INV value in their destination register if all sources are VALID).

- 2. **load** instructions mark their destination register INV if any of three cases arises:

- i. if the base register used to form the effective address is marked INV, or

- ii. a cache miss occurs, or

- iii. the target word in the cache is marked INV as a result of a preceding store during the same runahead episode (see next case).

- (They can also replace an INV value in their destination register if none of the preceding three cases apply).

- 3. **store** instructions do not write data into the cache or main memory. They do, however, mark the referenced cache item INV, if the base register used in address calculation is VALID and the target line is in the cache.

- 4. **conditional branch** instructions are resolved normally if their branch condition is VALID. If it is marked INV, the outcome is determined by whatever branch prediction strategy the processor employs, and the processor continues to pre-process instructions down the predicted path.

- 5. **indirect branch** instructions (the target of the branch is obtained from a register) in which the register is marked INV stall the processor pipeline until normal operation resumes.

- 6. **instruction cache misses** during runahead generate instruction stream prefetches.

The above actions were formulated from straightforward considerations of read-after-write dependencies, however they do not always accurately anticipate what occurs during actual execution. Action 3 does not account for the case when stores cause a cache miss or cannot compute their target addresses because their base register is marked INV. Such stores cannot mark their target word INV. It thus follows that subsequent loads have a small possibility of introducing apparently VALID data into the RF, which should have been INV. Action 4 does not account for the case when an unresolvable conditional branch is mispredicted. Finally, action 5 does not account for the case when an instruction cache miss causes the processor to not pre-process one or more taken branch or ALU instructions, which can insert uncertainty into the RF and PC state during runahead.

To summarize, the above runahead pre-processing actions result in values in the RF that cannot be trusted with certainty: there is a small possibility that a VALID register should be marked INV and vice versa. As the values in the RF during runahead are only used to generate prefetches, they do not affect the sequential state of the machine. Actions taken by the processor during runahead episodes cannot affect program correctness.

After the cache miss that initiated runahead mode is serviced, the processor resumes execution at the PC of the faulting instruction, and the RF is restored from its backup, the BRF. The runahead valid bits in the RF and the L1 data cache are then set to the VALID state. The L1 data cache runahead valid bits for a given line are also set to the VALID state whenever a new line of data is allocated in the cache.

#### 1.2 Some Runahead Examples

An example sequence of code is shown in Figure 1.1. Note that the sub-block runahead valid bits in the L1 data cache are not shown for this example, and that only the first eight general purpose registers are considered. The runahead valid bits for these registers are collectively referred to as the Invalid Register Vector (IRV). A register is marked INV if its corresponding bit in the IRV is a 0.

Figure 1.1 Basic runahead example

| Comment          | Instruction    | IRV State                  |

|------------------|----------------|----------------------------|

|                  |                | rrrrrrr<br>0 1 2 3 4 5 6 7 |

| dcache miss      | load r1, 0(r2) | 1 0 1 1 1 1 1 1            |

| INV result       | add r1, r2, r3 | 1 0 1 0 1 1 1 1            |

| bad address      | load r4, 4(r3) | 1 0 1 0 0 1 1 1            |

| correct result   | sub r6, r2, r5 | 1 0 1 0 0 1 1 1            |

| prefetch if miss | load r5, 0(r5) | 1 0 1 0 0 ? 1 1            |

The first instruction in the sequence is a load that misses in the L1 data cache, causing the processor to enter runahead. The bit in the IRV corresponding to the destination register of the load (r1) is marked INV (with a zero) in the IRV. The second instruction sources an INV register (r1). Its destination register (r3) is subsequently marked INV. The third instruction is another load. This load cannot properly form its target address, since it sources an INV register (r3). As a result this load cannot generate a runahead prefetch, and has to mark

its destination register (r4) as INV. The fourth instruction can source VALID registers (r6 and r2), which it uses to compute a new value for (r5), which remains VALID. The final instruction in the sequence is another load. This load can compute a VALID address using r5. If the load hits in the L1 data cache, then it marks its destination register (r5) as VALID after reading the data from the cache. If the load misses in the cache, then it marks its destination register (r5) as INV, and generates a prefetch for its target line.

This process continues until the memory hierarchy is able to service the L1 data cache miss corresponding to the first instruction. When this occurs, the processor leaves runahead mode and restarts execution at the instruction that initiated runahead (the first instruction in Figure 1.1). Before the processor can leave runahead mode it has to reset all of the IRV and L1 data cache sub-block valid bits to the VALID state, and perform the 1:1 copy from the BRF registers to their counterparts in the RF.

Once the processor has left runahead mode it restarts execution at the PC of the first instruction shown in Figure 1.1. Since the miss corresponding to the load has already been serviced, it is guaranteed to hit in the L1 data cache. The following add instruction is then able to execute normally. The third instruction may generate a L1 data cache miss. If it does not, then it can execute in the normal fashion. If it does generate a cache miss, then the processor re-enters runahead starting at the second load instruction. Assuming that the second load did not generate a L1 data cache miss, then the fourth instruction (the subtract) can execute normally. Finally, if the last instruction in the example generated a prefetch during the previous runahead episode, and that prefetch has been serviced, then the load will not generate an L1 data cache miss. If the prefetch has not been serviced, then the processor will re-enter runahead mode.

Another runahead example is shown in Figure 1.2.

Figure 1.2 Stores during runahead

| Comment         | Instruction     | IRV State                                              |  |  |

|-----------------|-----------------|--------------------------------------------------------|--|--|

|                 |                 | $     \begin{array}{ccccccccccccccccccccccccccccccccc$ |  |  |

| dcache miss     | load r1, 0(r2)  | 1 0 1 1 1 1 1 1                                        |  |  |

| INV dcache word | store r2, 0(r1) | 1011111                                                |  |  |

| is r4 valid?    | load r4, 4(r3)  | 1011?111                                               |  |  |

Note that the first instruction in the sequence is the same as that in the previous example. It has generated a runahead-initiating L1 data cache miss, and marked its destination register INV as in the previous example. The second instruction is a store that needs to use an INV register (r1) to calculate its target address. Since it cannot determine its target address, it cannot mark its target word in the L1 data cache as INV, even if it is in the cache. As a result, the subsequent load instruction cannot know for certain if the word it attempts to read from the L1 data cache is INV or not, as it could be read-after-write dependent upon the store instruction (in which case the data in the cache is stale). As these dependencies should be relatively rare, the processor should always assume that any word in the L1 data cache that it reads that is not marked as INV, is actually VALID. However, if a dependence does exist, a load can unknowingly add an "undetectable" INV value to the register file.

A third runahead example is shown in Figure 1.3. This example illustrates the effect of branches during runahead.

Figure 1.3 Dependent branches during runahead

| Comment           | Instruction    | IRV State                                                     |  |  |

|-------------------|----------------|---------------------------------------------------------------|--|--|

|                   |                | rrrrrrr<br>0 1 2 3 4 5 6 7                                    |  |  |

| dcache miss       | load r1, 0(r2) | 1 0 1 1 1 1 1 1                                               |  |  |

| dependent branch  | blt r1, loop   | 1 0 1 1 1 1 1 1                                               |  |  |

| prefetch if miss? | load r4, 4(r3) | $\begin{bmatrix} 1 & 0 & 1 & 1 & 2 & 1 & 1 & 1 \end{bmatrix}$ |  |  |

The first instruction initiates runahead as before. Note that the conditional branch is dependent upon the INV register generated by the load miss (r1). A runahead processor implementing a conservative runahead scheme would simply halt pre-processing at the INV-dependent branch in order to avoid polluting the L1 data cache. A runahead processor implementing a more aggressive runahead scheme would continue to pre-process instructions past the branch, using its branch prediction unit to predict the likely path of future execution. In preliminary tests with our current simulator we found that the aggressive scheme always provided superior performance. For this reason all of the runahead simulation results that we present are for processors models that use the aggressive scheme.

#### 1.3 Dissertation Organization

The dissertation is organized as follows. Chapter 2 discusses previous research work. Chapter 3 describes the methodology. Chapter 4 presents experimental results for a baseline runahead processor model. Chapter 5 presents an analysis of the effectiveness of runahead at both the function and instruction level, as well as a study of register and instruction usage. Chapter 6 describes simulation results for more advanced runahead processor models, in which the effects of instruction cache misses, memory hierarchy bandwidth, and wrongpath effects are eliminated. Chapter 7 describes simulation results for reduced-cost

runahead processor models. Chapter 8 presents a summary of our work. Chapter 9 concludes with a discussion of future work.

## Chapter 2

### **The Memory Latency Problem**

Processor clock rates have been increasing at about 40% per year, accounting for much of the 59% per year increase in performance [1]. During this time, the access time of commodity DRAM has been decreasing at only 7% per year [2], resulting in an exponentially increasing cycle time gap between processors and main-memory. Unless clever architectural tricks are employed, Amdahl's Law [2] tells us that memory latency effects will eventually dominate the execution time of applications. There are many different established methods of attacking the problem of memory latency.

#### 2.1 Caches

The classic method of reducing the impact of memory latency is to employ one or more levels of high-speed cache memory [3]. Caches work by exploiting locality of reference, meaning that if a data item is referenced once, then that item, or one near it in the address space, is likely to be referenced in the future. Locality of reference is exploited by holding, or caching, recently referenced data items in a small, fast, memory located close to the processor. While a data item is in the cache, subsequent accesses to it have a much lower latency than a main memory access. Caches work well for applications whose address streams exhibit locality, however many important applications do not. Nevertheless, caches

still form the backbone of high-performance memory systems, and can be made very effective when combined with other latency reduction and toleration techniques.

#### 2.2 Perform other useful work during cache miss cycles

One way to add a measure of memory latency tolerance is to allow a processor to continue to perform useful work while a cache miss is serviced. This can be done in a variety of ways. Non-blocking L1 data caches [4] allow a processor to continue to access the cache while a miss is serviced. Processors that allow the out-of-order completion of instructions [2] can continue to execute instructions while a data cache miss is serviced. This allows a processor to tolerate cache miss latency by attempting to keep the execution units busy while a cache miss is serviced. A conceptually similar approach is taken by coarse-grained multi-threaded processors, which can switch between independent threads of execution when a cache miss is detected [5].

#### 2.3 Use the available memory bandwidth more effectively

Another way to reduce latency is to control the store traffic to the lower levels of the memory hierarchy. Reducing store traffic allows the lower levels of the memory hierarchy to concentrate on servicing demand misses, which must be fulfilled quickly in order to maintain a high rate of execution, unlike store traffic, which is only needed to ensure consistency throughout the memory hierarchy.

The easiest way to reduce store traffic is to use a write-back, as opposed to a write-through data cache [3]. While write-back caches make sense for the lower levels of the memory hierarchy where accesses are less frequent, using a write-back L1 cache can complicate processor design [6].

If the priority of store traffic can be made lower than that of miss fill requests, then the average latency of miss fill requests can be lowered by allowing them to proceed ahead of earlier stores. This requires both a relaxed memory consistency model [2], as well as a means of checking to ensure that miss fill request and store addresses do not conflict. One way of lowering the priority of store traffic is to place them into a buffer, where they can be deferred until the off-chip memory is not busy servicing miss fill requests. The easiest way to do this is to place stores into a FIFO queue called a write buffer [2]. Loads that pass stores in the buffer must compare their target address to the target addresses of the stores in the buffer. The performance of write buffers can be increased by coalescing stores in the buffer that map to the same block of memory. This further reduces the amount of store traffic by combining requests that map to the same line into a single access to the next level of the memory hierarchy. An even more advanced way of controlling store traffic is to employ a write cache [7]. A write cache is essentially a coalescing write buffer with an LRU line replacement policy, as opposed to a FIFO replacement policy, turning the buffer into a cache. This allows the write cache to coalesce even more stores, resulting in an even greater reduction in store traffic.

#### 2.4 Increase the bandwidth of the memory hierarchy

A low latency memory hierarchy is not enough to ensure adequate performance on many applications [8]. Memory bandwidth is also very important. Bandwidth can be increased in many different ways. Cache and main memory bandwidth can be increased by employing wider cache lines or memory buses, pipelining accesses, and interleaving cache and memory banks. Main memory bandwidth can be increased even more by employing

exotic DRAM types, such as RAMBUS, as opposed to traditional commodity-type DRAMs [9].

#### 2.5 Statically schedule loads before stores

One way to reduce the effects of memory latency is to statically schedule code such that loads are moved as far as possible before any subsequent dependent instructions. This will allow an aggressive processor to start loads earlier than usual, increasing the likelihood that some or all of any cache miss latency will be hidden by the time any load-dependent instructions are ready for issue. This approach is limited by the ability of the compiler to statically detect dependencies between load and store instructions, among other things. Although some dependence analysis can be done statically, in the general case it is difficult to move loads before stores due to the problem of memory dependences between them. These potential hazards can only be detected after address calculations have been performed, which themselves, require hazard detection. The solution to this problem is referred to as memory disambiguation [10].

Although pure hardware memory disambiguation techniques, such as the store-buffer, can allow loads to pass stores dynamically, additional performance can be obtained by improving the static code schedule beyond that obtainable with standard compiler optimizations. One way of doing this is to employ hybrid hardware-software memory disambiguation, a recent example of which is [10], which introduced the memory conflict buffer (MCB). The MCB is a hardware device used to detect dependencies between rescheduled load instructions and any subsequent store instructions. This allows the traditional load instructions to be split into two parts: a preload instruction that can be scheduled by the compiler before any prior ambiguous stores, and a check instruction located at the position

of the original (non-rescheduled) load instruction. The preload instruction executes before the ambiguous stores, and records its target address and destination register in an MCB entry. Any stores that execute after the preload, but before the check instruction, access the MCB. If a store target address matches that of any MCB entries, then one or more load-store conflicts exist, and the target registers of the corresponding preload instructions are marked invalid in the MCB. If and when the corresponding check instructions are executed, they access the MCB to see if their corresponding preload conflicted with a store. If a conflict exists, the check instruction causes the processor to branch to a preload-specific fixup routine that fixes the error. This is done by re-executing the load instruction, as well as any load-dependent instructions that were rescheduled by the compiler.

#### 2.6 Executing loads early

The conventional five-stage pipeline [11] uses an adder in the ALU to compute loadstore target addresses. This improves performance by reducing the branch misprediction penalty, since the ALU execute stage is the first stage that instructions enter once they are issued. Unfortunately, this comes at the price of a load hazard.

A hardware load-use interlock is control hardware that is added to a pipeline that detects data dependencies, or load hazards, between load destination registers and subsequent dependent instructions [2]. The interlock hardware can stall the pipeline until any data dependencies can be resolved. This results in increased design complexity, however this allows the compiler to ignore the pipeline implementation, if correct operation is all that is needed. An alternative is to require that the compiler to either insert independent instructions, or NOPs, into the slots after a load that can result in a data hazard [11]. This approach

makes the compiler's job harder, as well as that of any future processor designers that may wish to radically change the microarchitecture of a subsequent implementation.

The work in [12] first proposed eliminating the load-use interlock (LUI) in the traditional five-stage pipeline by performing load/store address calculation in a stage before the ALU execute stage. This allows loads to execute in the same stage as ALU operations, which when combined with result forwarding, allows load-data dependent ALU instructions to be issued immediately after a load. This replaces the load-use interlock with an address-generation interlock, which occurs less often in typical applications. For this reason this pipeline organization is often referred to as the address generation interlock (AGI) organization. Unfortunately it delays branch resolution by an additional cycle, resulting in an increased branch misprediction penalty. In [11] this trade-off was evaluated, and concluded that a five stage AGI pipeline had to have a branch misprediction rate no greater than 20% in order to beat the performance of the traditional LUI pipeline. This pipeline organization has been employed in Intel i486, Pentium, Cyrix M1, and R8000 processors [11]. Note that while the AGI organization was initially proposed in [12], they concluded that the extra adder that it required was expensive enough to make the LUI organization more attractive at the time.

Another way to perform loads early in a pipeline is to detect them early, and attempt to access the data cache ahead of time by predicting the load target address. This idea was first explained in [13] where the concept of the load target buffer (LTB) was introduced. The LTB is a table indexed by the processor PC. Each entry of the LTB contains fields that hold the previous target address of a load instruction, the difference between the target addresses of the last two executions of the load (the stride), and some status bits. The LTB is accessed

in parallel with the instruction cache in the fetch stage of a pipeline. If the PC hits in the LTB, then the pipeline is fetching a load instruction. If on a hit, and the status bits indicate that the target address and stride should be trusted based upon the prior history of the load, then a speculative load from the address previous\_address + stride is immediately issued to the data cache, when possible. If the speculative load hits in the data cache, and the predicted address is correct, then the load latency is hidden. In [13] it was concluded that the latency to the L1 data cache must be at least five cycles to justify the use of a moderate sized LTB.

In [14] a method is presented to reduce load latency by performing effective address calculation in parallel with data cache access within the cache access stage. They employed a simple carry-free addition circuit that can compute the cache set index portion of the effective address with a single level of logic. Assuming that no carries are generated within, or propagated to, the set index portion of the address, the set index can usually be computed by simply ORing the set index portion of the address operands together. This very fast computation of the set index allows them to perform set index calculation in series with data cache access. The tag portion of the effective address can be computed in parallel with the cache lookup, as well as the actual effective address of the load. This allows them to perform many loads one cycle earlier than would otherwise be the case. If the carry-free addition was incorrect, or if the data cache port is busy, the load is performed in the customary MEM stage of the pipeline.

The authors in [15] went on to combine the idea of the LTB [13] with their earlier work on Fast Address Calculation [14] to reduce load latency even further. They proposed the Base Register and Index Cache (BRIC), a cache of general purpose register values that is

accessed in the fetch stage in parallel with the instruction cache. Each entry in the BRIC contains a register pair consisting of the base and index (if used) register values corresponding to a load instruction. These register values are used in conjunction with the load offset (if any) and some predecode information from the instruction cache to allow load instructions to obtain their address operands by the beginning of the decode stage of the pipeline. The pipeline can then use Fast Address Calculation (FAC) [14] to potentially access the data cache during the decode stage of the pipeline. If this succeeds, then two cycles of load latency are hidden. If the BRIC misses, the register values read during the decode stage can be used to perform the cache access during the execute stage of the pipeline using FAC. This will still hide one cycle of load latency. If the FAC fails, then the data cache is accessed in the usual fashion during the MEM stage of the pipeline.

#### 2.7 Data Prefetching

Data prefetching can reduce average memory latency by bringing data close to the processor before it is needed. The problem of course is selecting which data to prefetch. If data is prefetched into the L1 cache, then useless prefetches will replace other lines. As these other lines were probably fetched as a result of actual misses as opposed to prefetches, replacing these lines with useless prefetches can degrade performance. This is referred to as cache pollution [3]. If data is prefetched into a buffer where it waits for a demand miss before it is moved into the cache, pollution effects can be reduced, although useless prefetches can still reduce performance by increasing memory traffic. Prefetching into a buffer also introduces coherency problems, as the buffer contents must be checked every time that a store is committed.

The most elementary form of data prefetching is provided by having cache lines larger than the largest addressable data item. This brings additional data items into the cache, where they may be used before they are displaced from the cache. Other forms of data prefetching can generally be divided into hardware and software approaches.

# 2.7.1 Hardware data prefetching

Hardware data prefetching techniques allow the processor to generate prefetch requests without the intervention or knowledge of the compiler. This is more versatile, as it allows prefetching to be employed on legacy code, and across platforms.

The earliest form of hardware prefetching, sequential prefetching [3], generates prefetches for one or more lines located immediately after a referenced line in the address space. When this is done on every access, it is referred to as always-prefetch. Generating sequential prefetches only when a reference to the current line misses is referred to as prefetch-on-miss. It is also possible to perform tagged-prefetch, a variation of always-prefetch, in which sequential prefetches are generated whenever a previously prefetched line is accessed. One of the problems with sequential prefetching is that prefetched lines that are not referenced in the near future can displace useful lines from the cache, resulting in cache pollution. Sequential prefetch can also generate a great deal of additional traffic, which can swamp the connection to memory.

A conceptually similar approach, the data stream buffer, was proposed in [16]. The data stream buffer generates fetch requests for sequential lines after a missing line. These lines are fetched into the FIFO stream buffer, where they can be subsequently placed into the cache if the processor requests them. Since the stream buffer does not place prefetched lines into the cache until they are requested, cache pollution is kept to a minimum. Note that both

the stream buffer and sequential prefetching are conceptually similar to having very large cache lines, however using a stream buffer requires that the cache and buffer be kept coherent at all times. One of the problems with both the stream buffer and sequential prefetching is that prefetches are only generated for lines located after a missing line in the address space. Another problem with using the stream buffer for data stream prefetching is that multiple stream buffers are usually required for adequate performance, multiplying the coherency problem.

In [17] a more advanced sequential prefetching scheme for shared memory multiprocessors was proposed and evaluated. They compared the simple sequential prefetching technique [3], with an adaptive technique of their own design. Their adaptive sequential prefetching technique can dynamically adjust the number of sequential lines that are prefetched after a miss during program execution. This approach can even turn off prefetching if the program is in a region where prefetching is detrimental to performance, and subsequently re-enable prefetching if it detects that it would have benefited from prefetching.

More advanced hardware data prefetching methods attempt to generate prefetches for non-sequential lines. These approaches are particularly suited for processors executing scientific code, which typically access very large sparse matrices. The stride prefetch cache [18] can generate prefetches by using stride information obtained from vector memory operations to generate the prefetch addresses. Unfortunately this only works for vector machines, although one could use the PowerPC load/store with update instructions in a similar fashion under certain circumstances.

Conventional processors can generate strided prefetches by caching information about the history of memory operations. This was first done by [19] with their Reference Prediction Table (RPT). The RPT is a table that contains information about loads and stores executed in the recent past. The table is accessed by a Lookahead Program Counter (LA-PC) which is simply a register that runs ahead of the conventional program counter, using a branch target buffer to (hopefully) stay on the proper path of execution. If at any time the LA-PC "hits" in the RPT, then the LA-PC points to a likely future execution of a load or store instruction. Each entry of the RPT contains the previous target address of the load or store, the difference between the target addresses of the last two executions of the instruction (the stride), and some state information. If the state information for the entry indicates that the reference information can be trusted, then a potential prefetch with the target address previous\_address + stride is generated if the target address misses in the cache, and there is no outstanding fetch to that address in progress.

In [20] the Stride Prediction Table (SPT) was proposed. It is conceptually very similar to those developed by [19] and [21]. The primary difference between the SPT and the RPT [19] is that the SPT is indexed by the PC, while the RPT is indexed by the lookahead PC (LA-PC), which can move ahead of the PC. This means that the RPT can generate prefetches earlier than the SPT. The approach taken by [21] is similar to the SPT.

The authors of [19] continued their work with the RPT, and proposed three variants in [22]. The basic scheme uses the PC to index into the RPT, similar to that described in [20]. The lookahead scheme is basically the same as that described earlier in [19], except that an additional iteration count field is added to the RPT that allows the LA-PC to continue to generate prefetches when it has moved multiple loop iterations ahead of the PC. The correlated scheme attempts to correlate prefetches with changes in loop level, unlike the previous table approaches.

The authors of [23] recognized that the reference prediction table (RPT) described in [22] could not keep up with the issue rate of superscalar processors, as it could only scan one instruction at a time. Their basic idea is the same, except that they use a modified branch target buffer (BTB) called a program progress graph (PPG). Instead of outputting the predicted taken target address, the PPG outputs a pointer to the next branch on the predicted path of execution in the PPG. In other words, the PPG provides a way to a way to jump between basic blocks in a rapid fashion. The output of the PPG is applied to their superscalar reference prediction table (SRPT). When the output of the PPG is applied to the SRPT, any cached stride information about any loads or stores in the predicted future basic block of instructions drop out of the SRPT automatically in parallel, and are then used to generate hardware prefetches in the same manner as that described by [22].

## 2.7.2 Software data prefetching

Software prefetching was first proposed in passing in [3], and expanded upon without evaluation in [24]. The general idea is to add a instruction or instructions to the ISA that can compute a target address using the same addressing modes as the load and store instructions already present in the ISA. These instructions can be used to probe the L1 data cache for the presence of a given block of data. If the desired block is not in the cache, then a prefetch for the missing block is generated. These prefetches are generally non-binding, i.e. they are dropped if they would cause an exception, and they prefetch into the cache, not the register set. In other words, non-binding prefetches cannot cause incorrect program execution. Software prefetching is generally only effective for scientific applications that stride linearly through large matrices in a predictable manner.

In [25] a simple heuristic was proposed to decide where to insert the prefetch instructions. If an innermost loop induction variable is used to generate a load or store address, then the loop step is added to the induction variable and a prefetch instruction for that target address expression is inserted into the code by the compiler. This prefetch instruction can then generate prefetches for data one loop iteration before it is needed. This simple method inserts too many prefetch instructions, resulting in wasted execution slots. In an attempt to solve this problem a heuristic that predicts which accesses are likely to cause cache misses was proposed. The overflow iteration is defined as the maximum number of loop iterations whose data accesses can fit into the cache. Any data dependence that is carried by a loop for more iterations than the overflow iteration is likely to cause a miss. Prefetches are only generated for these accesses. This simple heuristic made software prefetching practical, at least for scientific applications that stride through large matrices in a regular fashion.

Additional software prefetching work was performed by [26]. They developed the concept of the prefetch distance, or the number of loop iterations a data item should be prefetched before its first use. The prefetch distance is based upon system memory latency and the estimated execution time of one loop iteration, and allows them to generate prefetches several iterations before the data will be needed, increasing the likelihood that prefetched data will be available by the time the first use of the data occurs. As the prefetch distance can be fairly large, prefetched data is sent to a buffer where it waits until needed by the cache. This avoids displacing useful data from the cache, however this comes at the cost of keeping data in the buffer and cache coherent.