### This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

# In-band phase noise reduction techniques for phase-locked loops in advanced CMOS technologies

Liang, Zhipeng

2018

Liang, Z. (2018). In-band phase noise reduction techniques for phase-locked loops in advanced CMOS technologies. Doctoral thesis, Nanyang Technological University, Singapore.

## https://hdl.handle.net/10356/89075

https://doi.org/10.32657/10220/46111

Downloaded on 28 Aug 2022 00:02:39 SGT

# In-Band Phase Noise Reduction Techniques for Phase-Locked Loops in Advanced CMOS Technologies

**Liang Zhipeng**

### School of Electrical and Electronic Engineering

A dissertation submitted to the Nanyang Technological University in partial fulfillment of the requirement for the degree of Doctor of Philosophy

2018

### Acknowledgements

During my study as a Ph.D. candidate in NTU, I have learnt a lot in many aspects. This is a result of the support and help from my family and many people.

Firstly and most importantly, I would like to thank my supervisor, Prof. Boon Chirn Chye. His full support provided me the opportunity to study in NTU on this interesting research topic. Prof. Boon's meticulousness and foresight in RFIC designs inspired me a lot during these years, and encouraged me in this research. I am also grateful to Dr. Yi Xiang, who is also very meticulous and knowledgeable. We have worked together in several projects, from which I have learnt not only design and measurement techniques but also his earnest attitude towards engineering. As my senior, project leader, and friend, Dr. Yi also established a good example about how to co-operate with other researchers. I would like to thank Dr. Feng Guangyin, who is also outstanding and informative in research. I would also like to thank Dr. Meng Fanyi for his guidance in research methods. In addition, I am grateful to my teachers in Sun Yat-sen University for their cultivation during my undergraduate study and for inspiring me to think from a physical point of view.

Some of my colleagues also helped with this research, and I would like to extend my gratitude to them. Dr. Lou Liheng and Dr. Wang Yisheng have taught me about digital flow for mixed-signal designs. Dr. Lin Jiafu helped me on the server management. Sunny Sharma provided me good suggestion on TDC measurement. Mr. Devrishi Khanna has discussed a lot with me about PLLs. I would also like to thank Ms. Lim-Tan Gek Eng and Mr. David Robert Neubronner for providing excellent technical supports in VIRTUS, the IC design research center in NTU.

I cannot forget my friends in VIRTUS, including Guo Kaizhe, Yang Yongkui, Yang Chuanshi, Wu Lei, Liu Bei, Yang Kaituo, Wang Xiaoying, Lu Lu, Yao Enyi, and Li Chenyang. Discussions with them on different research areas and techniques have broadened my knowledge. They made my study in NTU a wonderful period of my life.

The last paragraph is for my family. My beloved wife, Yang Qing, has worked in many ways to support my study. Her spiritual support heartened me during the tough time of my research. With her companionship, my stay in Singapore is not only an exciting exploration in research but also a journey full of memories. I would also like to thank my parents, grandparents, and my sister for their lasting concern and encouragement.

## Abbreviations

| AC-SS | Alias-Cancelling Subsampling            |

|-------|-----------------------------------------|

| ADC   | Analog-to-Digital Converter             |

| AFC   | Automatic Frequency Controller          |

| BJT   | Bipolar Junction Transistor             |

| CML   | Current-Mode Logic                      |

| CMOS  | Complementary Metal–Oxide–Semiconductor |

| DCO   | Digitally Controlled Oscillator         |

| DSM   | Delta-Sigma Modulator                   |

| DSP   | Digital Signal Processing               |

| DTC   | Digital-to-Time Converter               |

| ENOB  | Effective Number of Bits                |

| FET   | Field-Effect Transistor                 |

| FFT   | Fast Fourier transform                  |

| FLL   | Frequency-Locked Loop                   |

| FoM   | Figure of Merit                         |

| GaAs  | Gallium Arsenide                        |

| GMSK  | Gaussian Minimum Shift Keying           |

| GRO   | Gated Ring Oscillator                   |

| IC    | Integrated Circuit                      |

| ILFD  | Injection-Locked Frequency Divider      |

| IoT   | Internet of Things                       |

|-------|------------------------------------------|

| IP    | Intellectual Property                    |

| IRO   | Inverted Ring Oscillator                 |

| LDO   | Low-Dropout                              |

| LO    | Local Oscillator                         |

| LPF   | Low-Pass Filter                          |

| LSB   | Least Significant Bit                    |

| MPW   | Multi-Project Wafer                      |

| MUX   | Multiplexer                              |

| NRE   | Non-Recurring Engineering                |

| РСВ   | Printed Circuit Board                    |

| PDK   | Process Design Kit                       |

| PLL   | Phase-Locked Loop                        |

| PNRR  | Phase Noise Rejection Ratio              |

| PSD   | Power Spectral Density                   |

| PSK   | Phase-Shift Keying                       |

| PSRR  | Power Supply Rejection Ratio             |

| PS-SS | Phase-Switching Subsampling              |

| PVT   | Process, supply Voltage, and Temperature |

| QAM   | Quadrature Amplitude Modulation          |

| R&D   | Research and Development                 |

| RBW   | Resolution Bandwidth                     |

- RDL Redistribution Layer

- REF Reference

- RF Radio Frequency

- RFIC Radio Frequency Integrated Circuit

- RS-SS Rerefence-Shifting Subsampling

- SiGe Silicon-Germanium

- SiP System in Package

- SNR Signal-to-Noise Ratio

- SoC System on a Chip

- SPI Serial Peripheral Interface

- SRO Switched Ring Oscillator

- SSCP Subsampling Charge Pump

- SSPD Subsampling Phase Detector

- SSPLL Subsampling Phase-Locked Loop

- SWT Sweep Time

- TDC Time-to-Digital Converter

- TSV Through-Silicon Via

- VCO Voltage-Controlled Oscillator

## Summary

Phase-locked loops (PLLs) have been successfully used as frequency synthesizers for decades in complementary metal-oxide-semiconductor (CMOS) transceivers for wireless communications. However, modern developments in communications require PLLs with wider loop bandwidth and lower in-band phase noise. High in-band phase noise leads to serious consequences in communications, such as degraded signal-to-noise ratio (SNR) and constellation diagram, resulting in low communication quality. Therefore, low PLL in-band phase noise is crucial to the overall transceiver performance, especially in future high-speed high-quality wireless communications. Unfortunately, frequency synthesizers based on conventional PLL structures are facing challenges because their in-band phase noise is often limited by the phase detectors and charge pumps. Noises from these components are amplified due to the structure of the conventional PLLs. Furthermore, PLL often needs to achieve short settling time for some communication standards, and has to provide multi-phase output in some transceiver architectures. Inspired by these requirements, this thesis aims to enhance PLL in-band phase noise performance while meeting other important requirements of future wireless communications in the multi-GHz band.

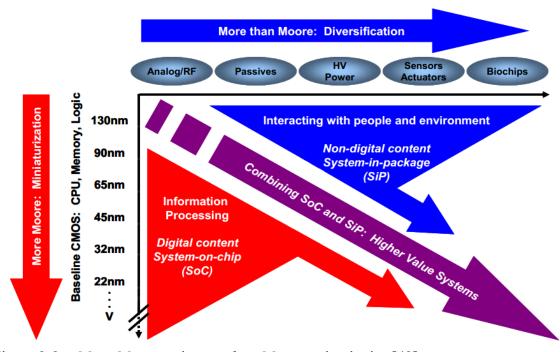

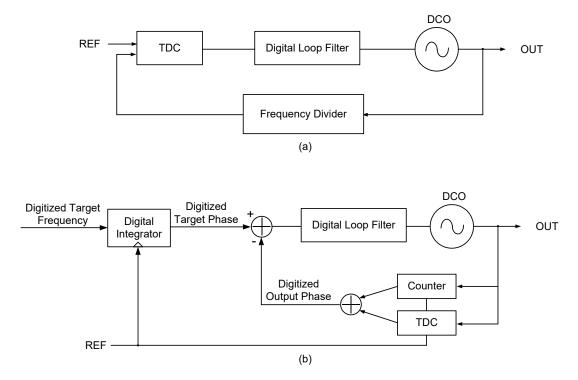

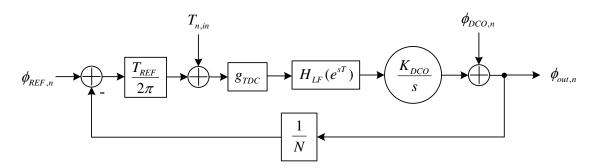

As the background of this research, conceptual PLL fundamentals related to phase noise will be briefly discussed. According to these fundamentals, the in-band phase noise is usually limited by the phase detector and charge pump in analog PLLs, and by the time-to-digital converter (TDC) in digital PLLs. Therefore, the objective of this research is specifically to reduce the adverse impact from these components. When choosing an analog or a digital PLL structure, characteristics of the adopted fabrication technology have to be considered. As the CMOS technology development is facing physical and economic limitations, two promising future CMOS technologies have been predicted, i.e., the *more-than-Moore* technology and the *more-Moore* technology. In regard to PLL implementation, the *more-than-Moore* technology permits the use of CMOS with larger feature size so that high-performance analog PLLs can be designed with mature methods, while the *more-Moore* technology keeps using the finer processes in which digital PLLs may be more suitable due to their promising performance with technology scaling. Both PLL types will be important in future advanced CMOS technologies. Therefore, this research investigates in-band phase noise reduction techniques for both analog and digital PLLs.

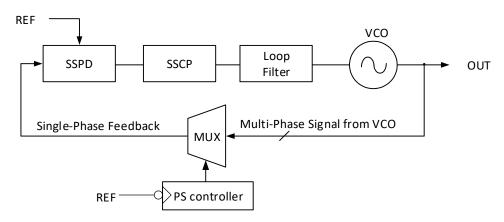

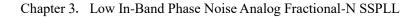

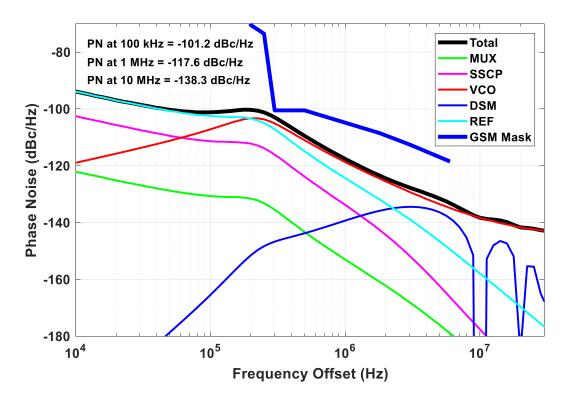

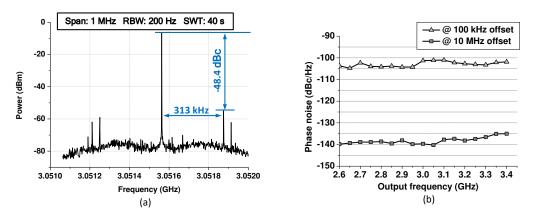

Firstly, in-band phase noise reduction technique for analog PLLs is investigated. With mature design and verification methods, analog PLLs have evolved and achieved low power consumption in the past years. However, conventional analog PLLs suffer from the high in-band noise from the phase detector and charge pump because noises from these components are amplified. To reduce such adverse impact, one of the most attractive structures is the fractional-N subsampling phase-locked loop (SSPLL) that can remove this amplification. It has enabled promising in-band performance and fine tuning steps for wireless systems. However, prior arts of fractional-N SSPLLs need long time for calibrations (~20 ms), which is much longer than PLL settling time (normally less than 200 µs). So these prior arts are not suitable for wireless communications requiring short settling time, such as Bluetooth. To extend the SSPLL applications, we explore the fractional-N SSPLL with a calibration-free manner and propose a phase-switching subsampling (PS-SS) technique. Fabricated in a 65 nm CMOS technology, a 2.6-3.4 GHz fractional-N 8-phase SSPLL prototype using the proposed technique totally eliminates the need for calibration and achieves a low in-band phase noise of -100.3 dBc/Hz at 100 kHz offset. Under calibration-less measurement condition, this prototype achieves the best jitter performance and figure of merit (FoM) among fractional-N SSPLLs. By using the proposed PS-SS technique, a low in-band phase noise in future analog PLLs can be expected without the need for long calibration time.

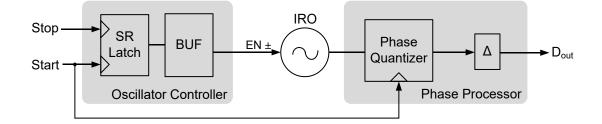

Secondly, in-band phase noise reduction technique for digital PLLs is investigated. For CMOS processes with small feature size, digital PLL has been proposed as a promising substitution of analog PLL due to many aspects. In these processes, in contrast to relying on the degraded transistor analog characteristics, digital PLLs take advantages of the improved digital characteristics and time resolution. Therefore, performance of digital PLLs can be improved with technology scaling. In addition, digital PLLs can also benefit from the automated digital design tools with shorter design cycle. However, in-band noise performance of digital PLLs is generally limited by the TDC noise. Among various TDC types, TDCs based on controlled oscillators have been reported to achieve low noise, hence low PLL in-band noise. Nevertheless, there is still a lot of headroom in such TDCs towards even lower noise. Besides, the operations of these TDCs draw different supply current at different time, leading to disturbance to power supply and to other circuitries when applied in a digital PLL. This can also affect the phase noise of the digital PLL. In this thesis, we investigate the controlled oscillator-based TDC family and propose an inverted ring oscillator (IRO) technique to further reduce TDC noise. A noise model is also proposed for noise prediction and design optimization for the controlled oscillator-based TDC family. An IRO-TDC prototype achieves an integrated noise of 196 fs<sub>rms</sub> in a 3 MHz bandwidth at 200 MS/s rate, showing lower in-band noise compared with state-of-the-art works. Moreover, a unique coherent phase noise cancellation (up to 36.4 dB cancellation ratio measured) and a constant TDC power dissipation were demonstrated, which can reduce the digital PLL in-band noise caused by coherent noises.

In summary, this thesis proposes techniques and methods to improve PLL in-band phase noise in advanced CMOS technologies. The proposed techniques, models, and methods can be extended to more complicated designs in future researches and products.

## **Table of Contents**

| A | cknow    | ledgem   | ents                                            | i    |

|---|----------|----------|-------------------------------------------------|------|

| A | bbrevi   | ations . |                                                 | iii  |

| S | ummar    | y        |                                                 | vi   |

| Т | able of  | Conter   | nts                                             | ix   |

| L | ist of F | 'igures. |                                                 | xii  |

| L | ist of T | ables    |                                                 | xvii |

| 1 | Intro    | duction  | 1                                               | 1    |

|   | 1.1      | CM       | IOS PLLs in RFIC                                | 1    |

|   | 1.2      | CM       | IOS PLLs Challenges in Future Communications    | 2    |

|   | 1.3      | Ma       | jor Contributions of the Thesis                 | 5    |

|   | 1.4      | Org      | ganization of the Thesis                        | 8    |

| 2 | Backg    | ground   | on CMOS PLLs                                    | 10   |

|   | 2.1      | PL       | L Fundamentals                                  | 10   |

|   |          | 2.1.1    | Conceptual Architecture                         | 10   |

|   |          | 2.1.2    | Noise Contributors                              | 12   |

|   | 2.2      | CM       | IOS Technology Development                      | 16   |

|   |          | 2.2.1    | Moore's Law and Limitations                     | 16   |

|   |          | 2.2.2    | Predicted Advanced CMOS Technologies            | 20   |

|   | 2.3      | PL       | L Schemes in Advanced CMOS Technologies         | 23   |

|   |          | 2.3.1    | Analog PLL                                      | 24   |

|   |          | 2.3.2    | Digital PLL                                     | 25   |

|   | 2.4      | Su       | mmary                                           | 27   |

| 3 | Low l    | (n-Ban   | d Phase Noise Analog Fractional- <i>N</i> SSPLL |      |

|   | 3.1      | Lit      | erature Review of Divider PLLs and SSPLLs       |      |

|   |          | 3.1.1    | Integer-N Divider PLL                           |      |

|   |          | 3.1.2    | Fractional-N Divider PLL                        |      |

|   |          | 3.1.3    | Integer-N SSPLL                                 |      |

|   |                                                           | 3.1.4                                                                           | Fractional-N SSPLL                                                                                                                                                                                                                                                                                                       |                |

|---|-----------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|   | 3.2                                                       | Pro                                                                             | pposed PS-SS Technique                                                                                                                                                                                                                                                                                                   |                |

|   |                                                           | 3.2.1                                                                           | Constant-Step Phase Switching                                                                                                                                                                                                                                                                                            |                |

|   |                                                           | 3.2.2                                                                           | DSM-Assisted Phase Switching                                                                                                                                                                                                                                                                                             | 41             |

|   | 3.3                                                       | Pro                                                                             | pposed Phase Model                                                                                                                                                                                                                                                                                                       | 44             |

|   |                                                           | 3.3.1                                                                           | Phase Switching Noise                                                                                                                                                                                                                                                                                                    | 44             |

|   |                                                           | 3.3.2                                                                           | Phase Mismatch                                                                                                                                                                                                                                                                                                           | 45             |

|   | 3.4                                                       | Fra                                                                             | ctional-N Low-Noise PS-SSPLL Implementation                                                                                                                                                                                                                                                                              | 48             |

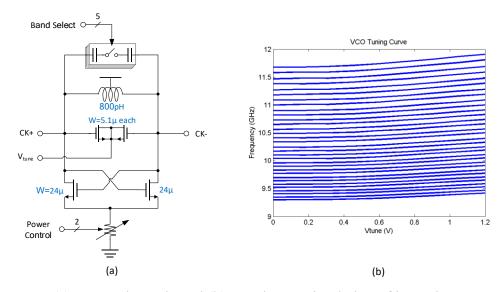

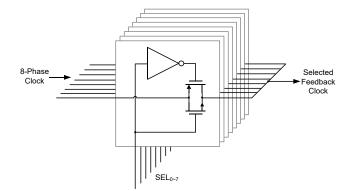

|   |                                                           | 3.4.1                                                                           | VCO and 8-Phase Feedback Signal                                                                                                                                                                                                                                                                                          | 49             |

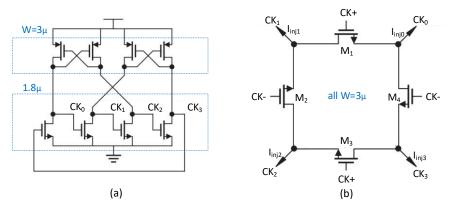

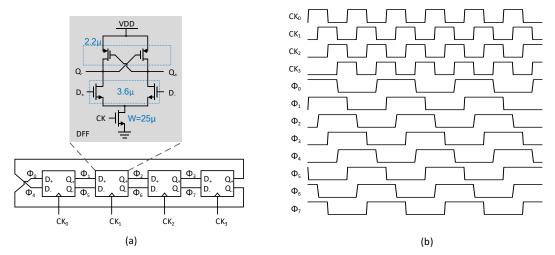

|   |                                                           | 3.4.2                                                                           | Multiplexer and Sampler                                                                                                                                                                                                                                                                                                  |                |

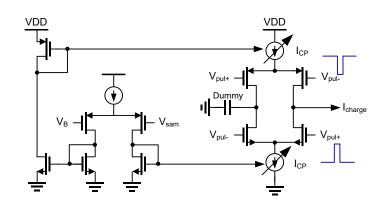

|   |                                                           | 3.4.3                                                                           | SSCP                                                                                                                                                                                                                                                                                                                     | 54             |

|   |                                                           | 3.4.4                                                                           | Loop Filter                                                                                                                                                                                                                                                                                                              | 55             |

|   |                                                           | 3.4.5                                                                           | Simulation Result                                                                                                                                                                                                                                                                                                        | 55             |

|   | 3.5                                                       | Ex                                                                              | perimental Results                                                                                                                                                                                                                                                                                                       | 57             |

|   | 3.6                                                       | Su                                                                              | mmary                                                                                                                                                                                                                                                                                                                    | 64             |

|   |                                                           |                                                                                 |                                                                                                                                                                                                                                                                                                                          |                |

| 4 | IRO-7                                                     | ГDC fo                                                                          | or Low In-Band Phase Noise Digital PLLs                                                                                                                                                                                                                                                                                  | 66             |

| 4 | <b>IRO-</b> 7                                             |                                                                                 | or Low In-Band Phase Noise Digital PLLs                                                                                                                                                                                                                                                                                  |                |

| 4 |                                                           | TD                                                                              |                                                                                                                                                                                                                                                                                                                          | 66             |

| 4 | 4.1                                                       | TD<br>Lit                                                                       | C Specifications in Digital PLL Designs                                                                                                                                                                                                                                                                                  | 66             |

| 4 | 4.1<br>4.2                                                | TD<br>Lit<br>Pro                                                                | C Specifications in Digital PLL Designs                                                                                                                                                                                                                                                                                  | 66<br>68<br>72 |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>             | TD<br>Lit<br>Pro                                                                | OC Specifications in Digital PLL Designs<br>erature Review of TDCs<br>oposed IRO for TDCs                                                                                                                                                                                                                                |                |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>             | TD<br>Lit<br>Pro<br>Pro                                                         | OC Specifications in Digital PLL Designs<br>erature Review of TDCs<br>oposed IRO for TDCs<br>oposed Noise Model for Controlled Oscillator-based TDCs                                                                                                                                                                     |                |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>             | TD<br>Lit<br>Pro<br>4.4.1                                                       | OC Specifications in Digital PLL Designs<br>erature Review of TDCs<br>oposed IRO for TDCs<br>oposed Noise Model for Controlled Oscillator-based TDCs<br>Quantization Error                                                                                                                                               |                |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>             | TD<br>Lit<br>Pro<br>4.4.1<br>4.4.2                                              | OC Specifications in Digital PLL Designs<br>erature Review of TDCs<br>oposed IRO for TDCs<br>oposed Noise Model for Controlled Oscillator-based TDCs<br>Quantization Error<br>Stage Delay Mismatch                                                                                                                       |                |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>             | TD<br>Lit<br>Pro<br>4.4.1<br>4.4.2<br>4.4.3                                     | DC Specifications in Digital PLL Designs<br>erature Review of TDCs<br>oposed IRO for TDCs<br>oposed Noise Model for Controlled Oscillator-based TDCs<br>Quantization Error<br>Stage Delay Mismatch<br>Skew Error                                                                                                         |                |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>             | TD<br>Lit<br>Pro<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4                            | DC Specifications in Digital PLL Designs<br>erature Review of TDCs<br>oposed IRO for TDCs<br>oposed Noise Model for Controlled Oscillator-based TDCs<br>Quantization Error<br>Stage Delay Mismatch<br>Skew Error<br>Dead-Zone Behaviors                                                                                  |                |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>             | TD<br>Lit<br>Pro<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.3<br>4.4.4<br>4.4.5<br>4.4.6 | DC Specifications in Digital PLL Designs<br>erature Review of TDCs<br>oposed IRO for TDCs<br>oposed Noise Model for Controlled Oscillator-based TDCs<br>Quantization Error<br>Stage Delay Mismatch<br>Skew Error<br>Dead-Zone Behaviors<br>Oscillator Phase Noise                                                        |                |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li><li>4.4</li></ul> | TD<br>Lit<br>Pro<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.3<br>4.4.4<br>4.4.5<br>4.4.6 | DC Specifications in Digital PLL Designs<br>erature Review of TDCs<br>oposed IRO for TDCs<br>oposed Noise Model for Controlled Oscillator-based TDCs<br>Quantization Error<br>Stage Delay Mismatch<br>Skew Error<br>Dead-Zone Behaviors<br>Oscillator Phase Noise<br>IRO Phase Noise Cancellation                        |                |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li><li>4.4</li></ul> | TD<br>Lit<br>Pro<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4<br>4.4.5<br>4.4.6<br>IRO   | C Specifications in Digital PLL Designs<br>erature Review of TDCs<br>oposed IRO for TDCs<br>oposed Noise Model for Controlled Oscillator-based TDCs<br>Quantization Error<br>Stage Delay Mismatch<br>Skew Error<br>Dead-Zone Behaviors<br>Oscillator Phase Noise<br>IRO Phase Noise Cancellation<br>D-TDC Implementation |                |

| Bi | bliogr | aphy    |                                    | 125 |

|----|--------|---------|------------------------------------|-----|

| Aı | uthor' | s Publi | cations                            | 123 |

|    | 5.2    | Re      | commendations for Future Research  | 119 |

|    | 5.1    | Co      | nclusions                          | 118 |

| 5  | Conc   | lusions | and Recommendations                | 118 |

|    |        | 4.7.2   | Possible Drawbacks and Mitigations | 117 |

|    |        | 4.7.1   | Achievements                       | 116 |

|    | 4.7    | Su      | mmary                              | 115 |

|    |        | 4.6.3   | Phase Noise Cancellation Test      | 112 |

|    |        | 4.6.2   | Noise Performance Test             | 109 |

|    |        | 4.6.1   | Dead-Zone Test                     | 107 |

# **List of Figures**

| Figure 1-1  | A general architecture of a wireless transceiver1                     |

|-------------|-----------------------------------------------------------------------|

| Figure 1-2  | (a) An RF transceiver from Qualcomm [11], and (b) a 802.11            |

|             | WLAN RF front-end [12]2                                               |

| Figure 1-3  | Phase noise impact on (a) receiver and (b) transmitter [13]3          |

| Figure 1-4  | Constellation diagram with (a) no phase noise and (b) large phase     |

|             | noise                                                                 |

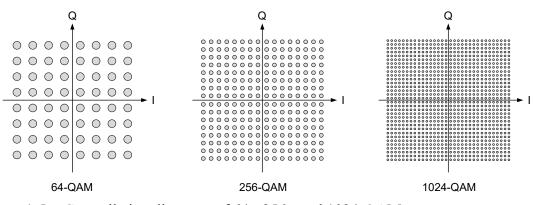

| Figure 1-5  | Constellation diagrams of 64-, 256-, and 1024-QAM4                    |

| Figure 2-1  | Conceptual diagram of a feedback control loop10                       |

| Figure 2-2  | Comparison between concepts of (a) phase noise and (b) voltage        |

|             | noise                                                                 |

| Figure 2-3  | Noise model of a general PLL                                          |

| Figure 2-4  | An example of noise source contributions to the PLL output phase      |

|             | noise14                                                               |

| Figure 2-5  | Microprocessor transistor counts in 1971-2011 [40]17                  |

| Figure 2-6  | Costs of an IC product [41]19                                         |

| Figure 2-7  | (a) Approximate mask set cost [41]. (b) Product total cost in old and |

|             | new technologies                                                      |

| Figure 2-8  | More-Moore and more-than-Moore technologies [42]20                    |

| Figure 2-9  | Exemplary SiP technologies combining several dies in one package,     |

|             | including (a) TSV, (b) InFO, and (c) dual-die flip-chip packaging21   |

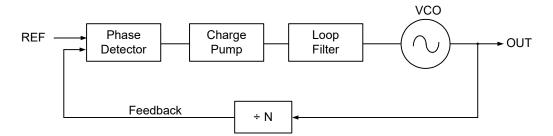

| Figure 2-10 | Structure of a general analog PLL24                                   |

| Figure 2-11 | Structures of digital PLLs (a) with frequency divider and (b) without |

|             | frequency divider25                                                   |

| Figure 3-1  | Basic structure of an analog divider PLL                              |

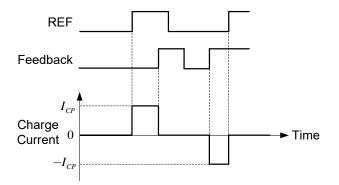

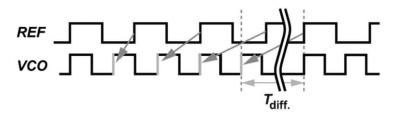

| Figure 3-2  | Input-output timing diagram of phase detector and charge pump29       |

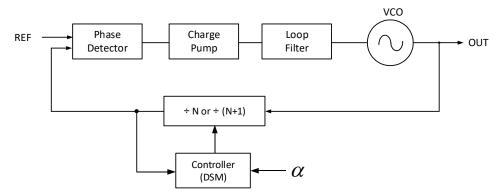

| Figure 3-3  | Conventional fractional- <i>N</i> divider PLL structure               |

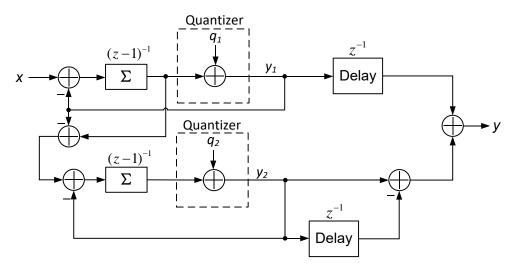

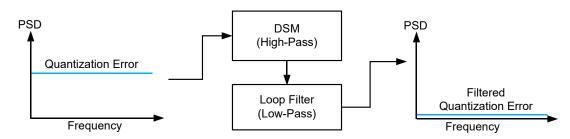

| Figure 3-4  | MASH 1-1 DSM structure                                                |

| Figure 3-5  | Conceptual signal path showing the impact of DSM and loop filter      |      |

|-------------|-----------------------------------------------------------------------|------|

|             | on quantization error                                                 | 33   |

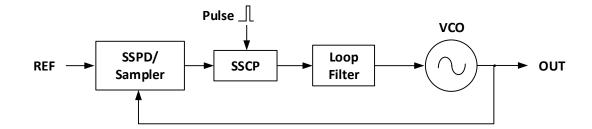

| Figure 3-6  | Structure of a conventional SSPLL                                     | 33   |

| Figure 3-7  | Phase model of a conventional SSPLL [53].                             | 34   |

| Figure 3-8  | Phases fail to align with a fractional frequency ratio [55]           | 35   |

| Figure 3-9  | Achitecture of a fractional-N reference-shifting SSPLL.               | 36   |

| Figure 3-10 | Architecture of a fractional- <i>N</i> alias-canceling SSPLL [58]     | 37   |

| Figure 3-11 | Operation of alias canceling                                          | 37   |

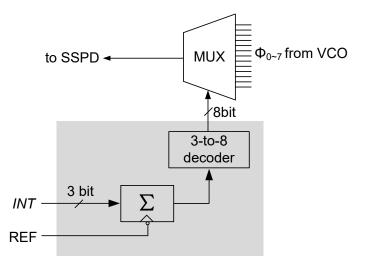

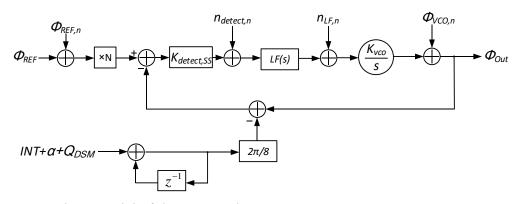

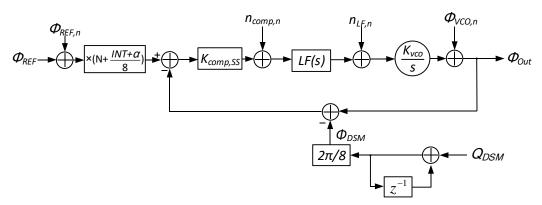

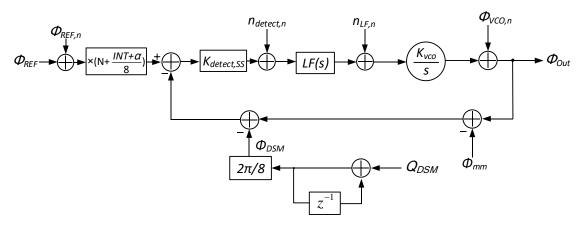

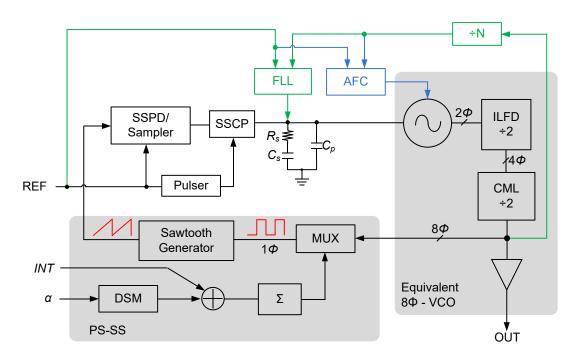

| Figure 3-12 | Architecture of a PS-SSPLL.                                           | 39   |

| Figure 3-13 | Structure of constant-step phase switching                            | 39   |

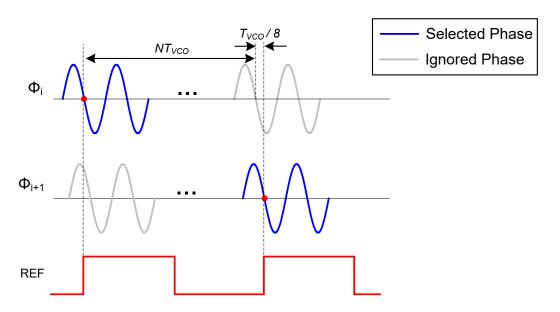

| Figure 3-14 | Timging diagram of constant-step phase switching $(INT = 1)$          | 40   |

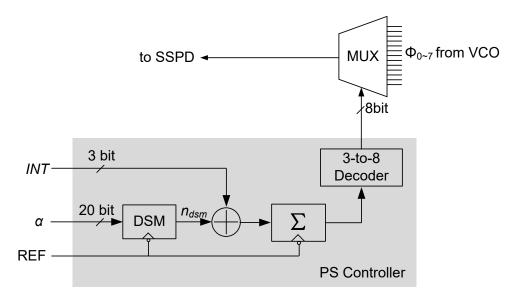

| Figure 3-15 | Structure of DSM-assisted phase switching.                            | 41   |

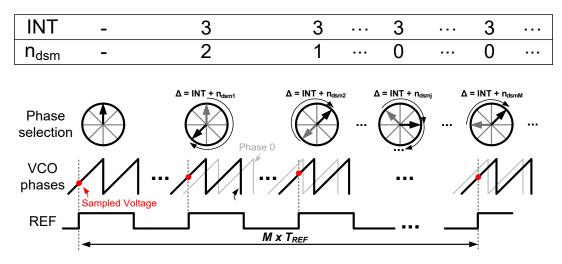

| Figure 3-16 | Timing diagram of DSM-assisted phase switching.                       | 42   |

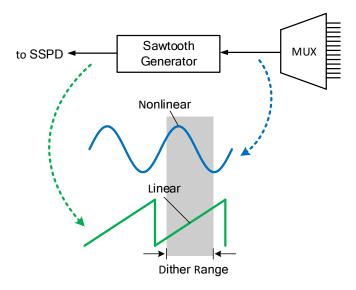

| Figure 3-17 | Feedback signal can be transformed into a sawtooth wave with a        |      |

|             | larger linear range for DSM dithering.                                | 43   |

| Figure 3-18 | Phase model of the proposed PS-SSPLL.                                 | 44   |

| Figure 3-19 | Reconstructed phase model of the proposed PS-SSPLL.                   | 44   |

| Figure 3-20 | Phase model with multi-phase mismatch added.                          | 46   |

| Figure 3-21 | Schematic of the PS-SSPLL prototype.                                  | 48   |

| Figure 3-22 | (a) VCO schematic and (b) post-layout simulation of its tuning curve. |      |

|             |                                                                       | 49   |

| Figure 3-23 | Schematic of the adopted ILFD [59].                                   | 50   |

| Figure 3-24 | (a) Schematic and (b) timing diagram of the adopted 4-input           |      |

|             | 8-output CML divider.                                                 | 51   |

| Figure 3-25 | Post-layout simulation showing worst case phase nosie of the          |      |

|             | 8-phase clock.                                                        | 52   |

| Figure 3-26 | Schematic of the multiplexer.                                         | 52   |

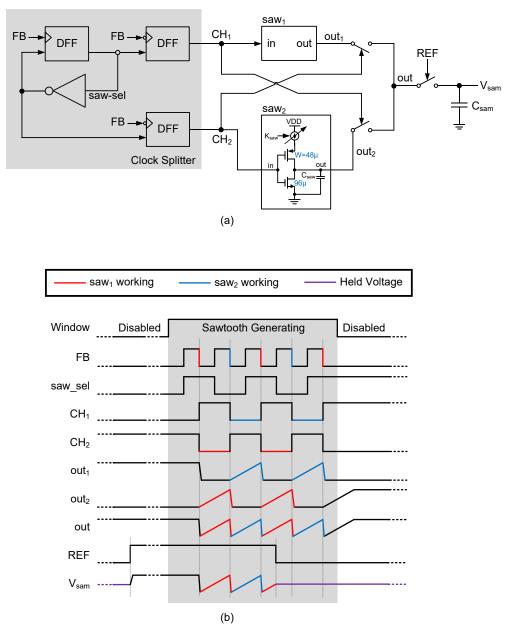

| Figure 3-27 | (a) Schematic and (b) timing diagram of the waveform generator and    |      |

|             | sampler                                                               | 53   |

| Figure 3-28 | Schematic of the SSCP [60]                                            | 55   |

|             |                                                                       | xiii |

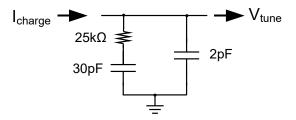

| Figure 3-29        | Schematic of the loop filter                                                 |

|--------------------|------------------------------------------------------------------------------|

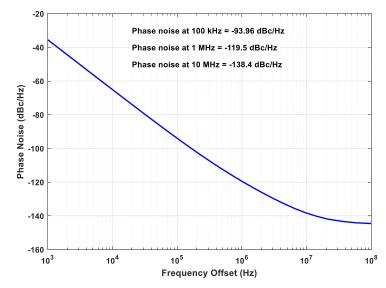

| Figure 3-30        | Simulation result of the SSPLL output phase noise                            |

| Figure 3-31        | Simulation of the SSPLL locking                                              |

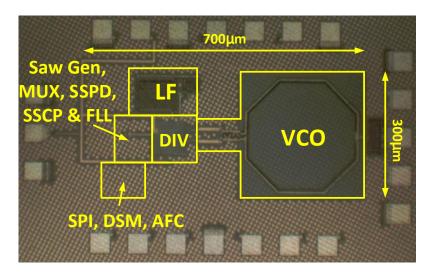

| Figure 3-32        | Die photograph of the fabricated PS-SSPLL prototype58                        |

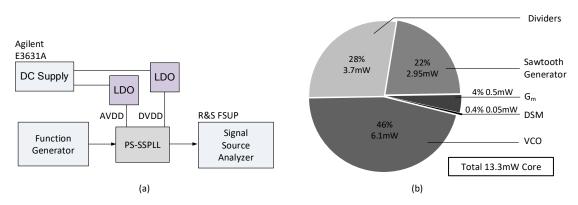

| Figure 3-33        | (a) Testbench of this work. (b) Power consumption of each block58            |

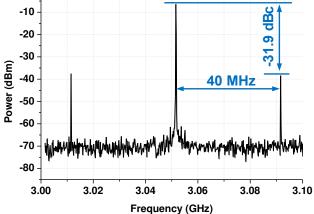

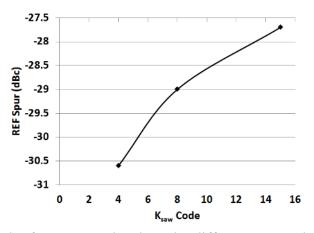

| Figure 3-34        | Measured reference spurs at fractional- <i>N</i> output59                    |

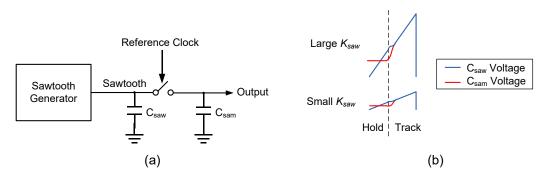

| Figure 3-35        | (a) Connection between the sawtooth generator and the sampling               |

|                    | capacitor, and (b) a conceptual timing diagram of charge sharing             |

|                    | under different sawtooth slopes60                                            |

| Figure 3-36        | Measured reference spur levels under different sawtooth slope                |

|                    | configurations60                                                             |

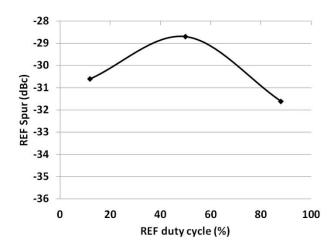

| Figure 3-37        | Measured reference spur levels under different reference clock duty          |

|                    | cycles                                                                       |

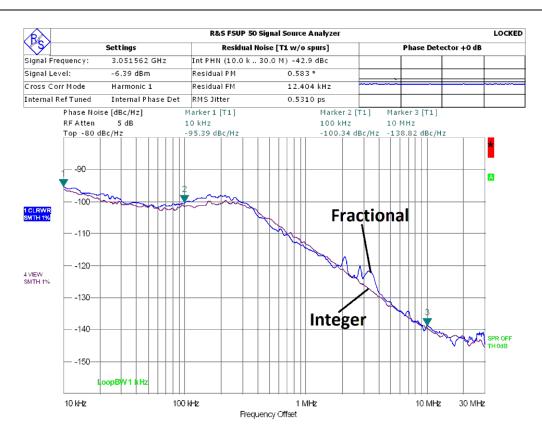

| Figure 3-38        | Measured phase noise of integer- <i>N</i> and fractional- <i>N</i> outputs62 |

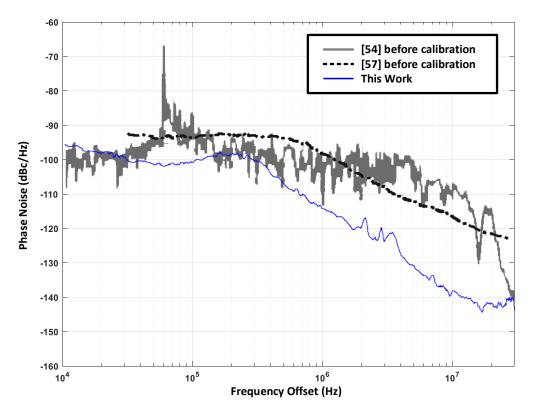

| Figure 3-39        | Phase noise comparison with prior arts62                                     |

| Figure 3-40        | (a) Measured fractional spurs and (b) measured in-band and                   |

|                    | out-of-band noises across the PLL output range                               |

| Figure 4-1         | Noise model of a digital PLL with frequency divider67                        |

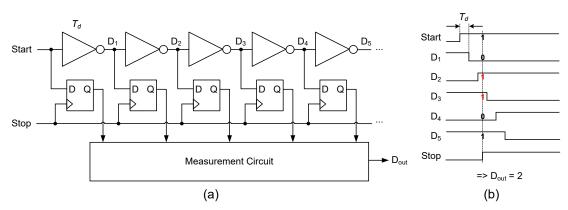

| Figure 4-2         | (a) Schematic and (b) timing diagram of a Flash TDC68                        |

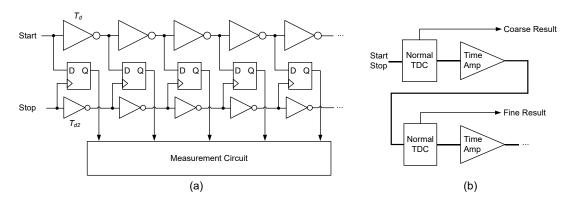

| Figure 4-3         | (a) Vernier TDC and (b) pipeline TDC for improved resolution                 |

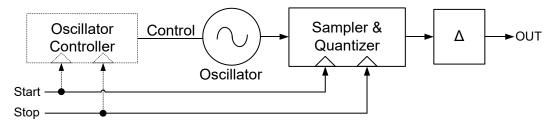

| Figure 4-4         | A general structure of an oscillator-based TDC69                             |

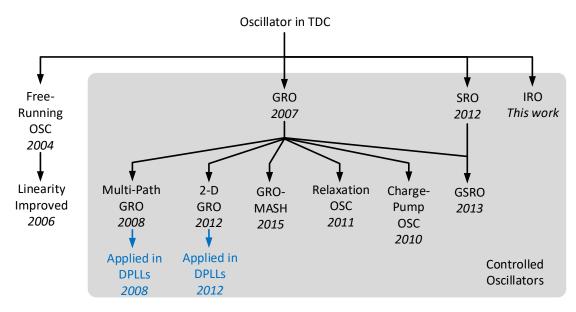

| Figure 4-5         | Development of the oscillator-based TDC family70                             |

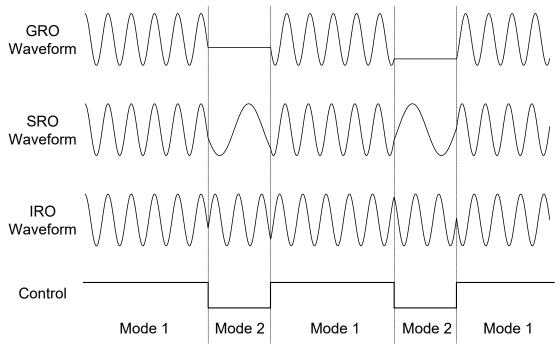

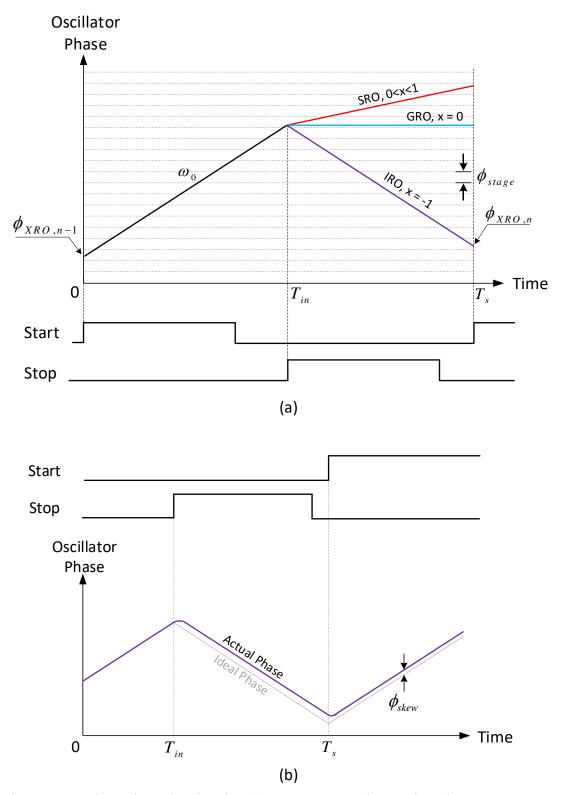

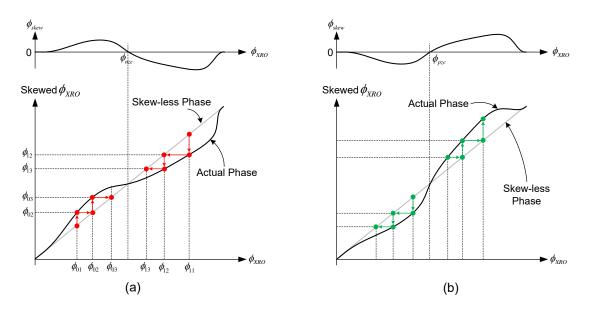

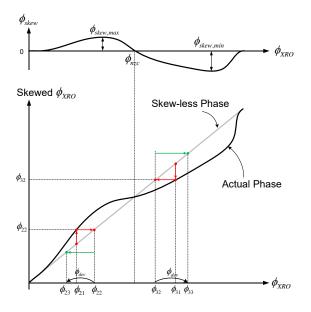

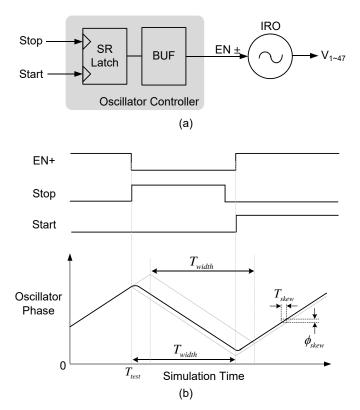

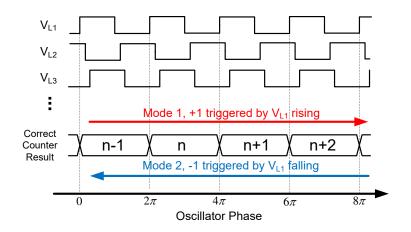

| Figure 4-6         | Timing diagram of GRO, SRO, and IRO voltage73                                |

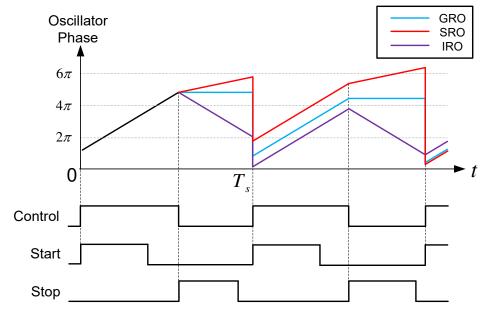

| Figure 4-7         | Phase-time plot of GRO, SRO and IRO74                                        |

| Figure 4-8         | Phase-time plot showing (a) GRO, SRO and IRO phase increments                |

|                    | during one measurement cycle and (b) IRO phase skew75                        |

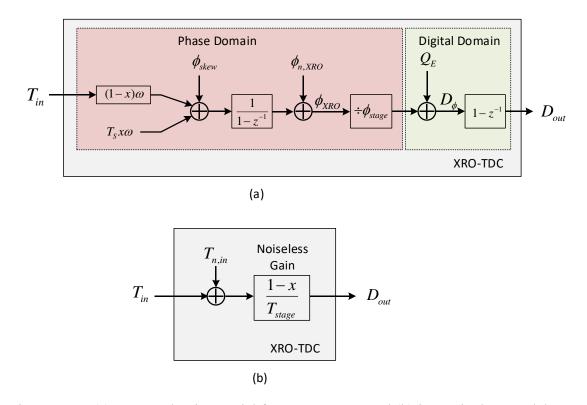

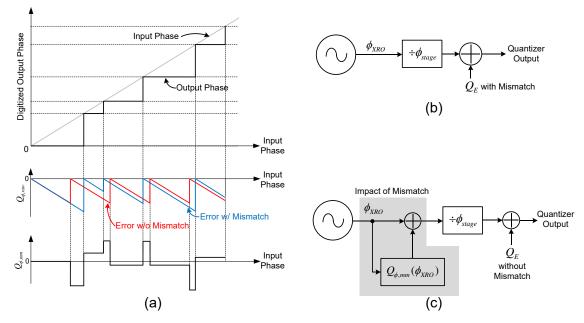

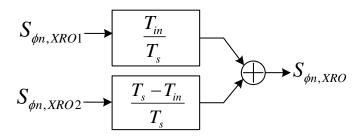

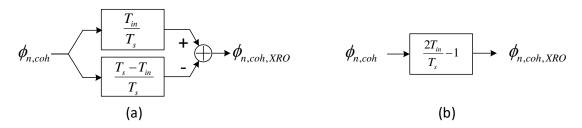

| Figure 4-9         | (a) Proposed noise model for XRO-TDCs, and (b) its equivalent                |

|                    | model showing the input-referred noise77                                     |

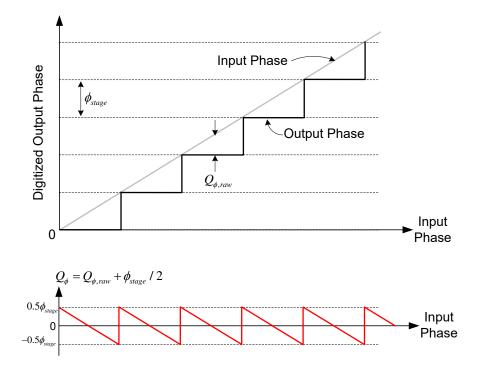

| Figure 4-10        | Phase quantization transfer characteristic                                   |

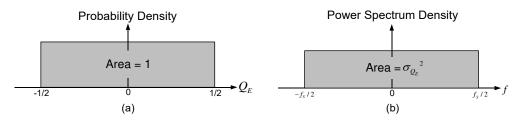

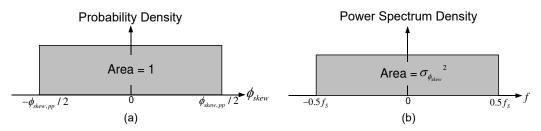

| Figure 4-11<br>xiv | (a) Probability density and (b) PSD of quantization error80                  |

| Figure 4-12 | (a) Phase quantization transfer characteristic with delay mismatch.   |

|-------------|-----------------------------------------------------------------------|

|             | (b) Quantization model with mismatch. (c) An equivalent model that    |

|             | extracts the impact of mismatch82                                     |

| Figure 4-13 | (a) Probability density and (b) PSD of phase skew83                   |

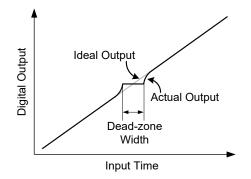

| Figure 4-14 | Conceptual DC transfer characteristic showing a dead-zone             |

| Figure 4-15 | Effect of phase skew to an oscillator                                 |

| Figure 4-16 | Phase changes with $2K\pi$ phase increment near (a) a negative        |

|             | zero-crossing point and (b) a positive zero-crossing point85          |

| Figure 4-17 | Phase changes near $\phi nzc$ with $2K\pi + \phi dev$ phase increment |

| Figure 4-18 | Relation between phase increment and dead-zone                        |

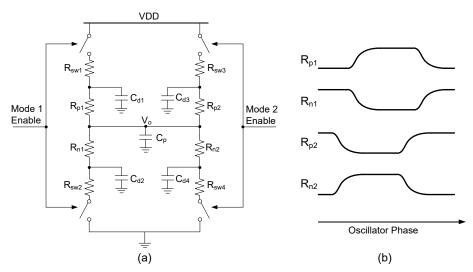

| Figure 4-19 | Phase noise model of dual-mode XRO                                    |

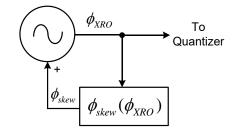

| Figure 4-20 | IRO coherent noise model under quasi-stationary $\phi n, coh$ 90      |

| Figure 4-21 | Structure of the proposed IRO-TDC                                     |

| Figure 4-22 | (a) Simulation testbench for the IRO phase skew and (b) an            |

|             | exemplarity timing diagram                                            |

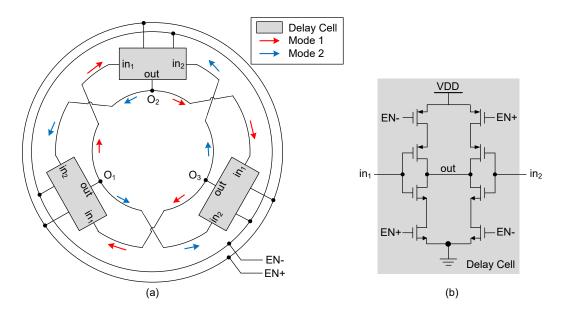

| Figure 4-23 | Schematic of (a) a simple IRO and (b) each of its delay cells94       |

| Figure 4-24 | (a) An equivalent schematic of a single delay cell and (b) changes of |

|             | transistor resistances                                                |

| Figure 4-25 | (a) Total IRO phase skew contributed from each transition stage. (b)  |

|             | Phase skew mitigated through averaging by extended transitions96      |

| Figure 4-26 | (a) Topology and (b) schematic of the multi-path IRO97                |

| Figure 4-27 | Simulated supply currents of GRO and IRO (including oscillator        |

|             | controllers) with same transistor sizes                               |

| Figure 4-28 | (a) Schematic of fractional quantization and (b) state identification |

|             | truth table101                                                        |

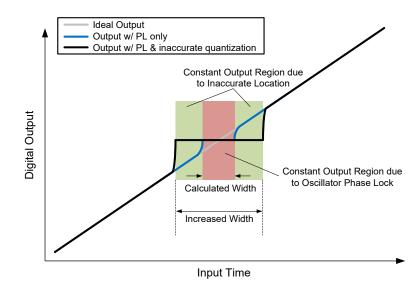

| Figure 4-29 | Dead-zone due to phase lock (PL) and inaccurate quantization101       |

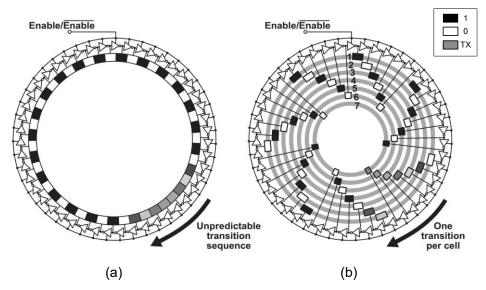

| Figure 4-30 | (a) A transition locator with location error, and (b) a regrouped     |

|             | locator that can reduce this error [70]102                            |

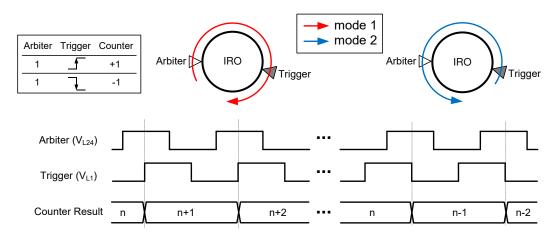

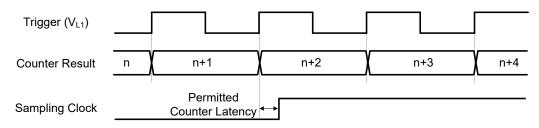

| Figure 4-31 | Timing diagram of a correct wrap counting103                          |

| Figure 4-32 | Wrap counter truth table and timing diagram of $\pm 1$ counting104 xv |

| Figure 4-33 | Timing challenge in asynchronous count-and-read operation104              |

|-------------|---------------------------------------------------------------------------|

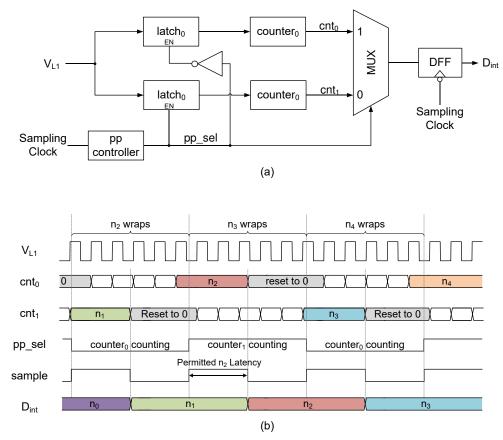

| Figure 4-34 | (a) Structure and (b) timing diagram of the ping-pong counter104          |

| Figure 4-35 | (a) Microphotograph and (b) power consumption of the IRO-TDC              |

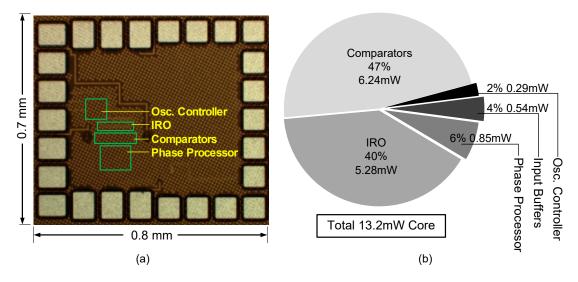

|             | prototype106                                                              |

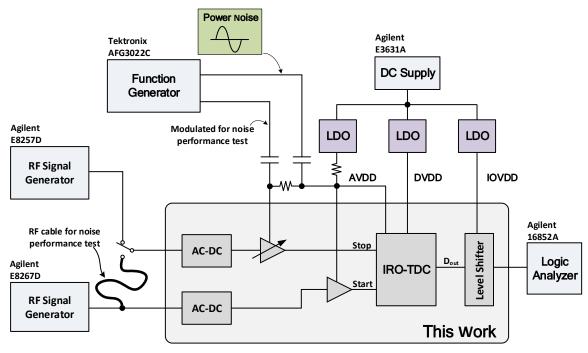

| Figure 4-36 | Testbench for IRO-TDC106                                                  |

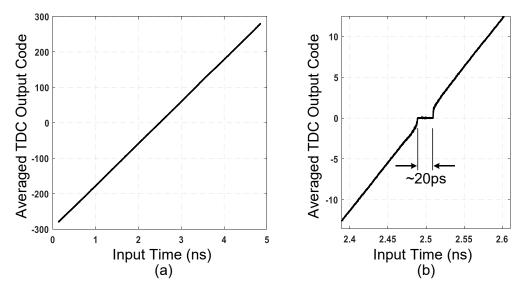

| Figure 4-37 | Static test results showing (a) DC transfer characteristic and (b) the    |

|             | widest dead-zone near TDC output code = 0107                              |

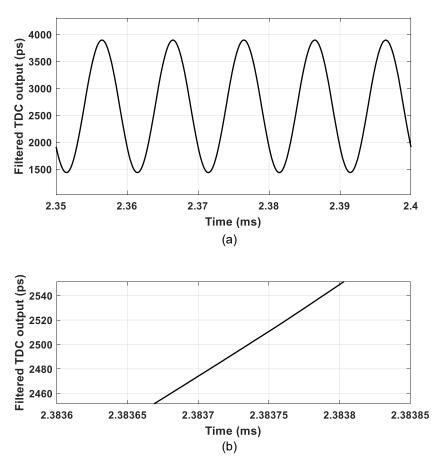

| Figure 4-38 | A 3 MHz-filtered time domain IRO-TDC output for a 100 kHz, 2.5            |

|             | $ns_{pp}$ input signal with $\sim$ 2.67 ns offset, showing (a) the output |

|             | waveform and (b) a zoom-in view near the widest dead-zone108              |

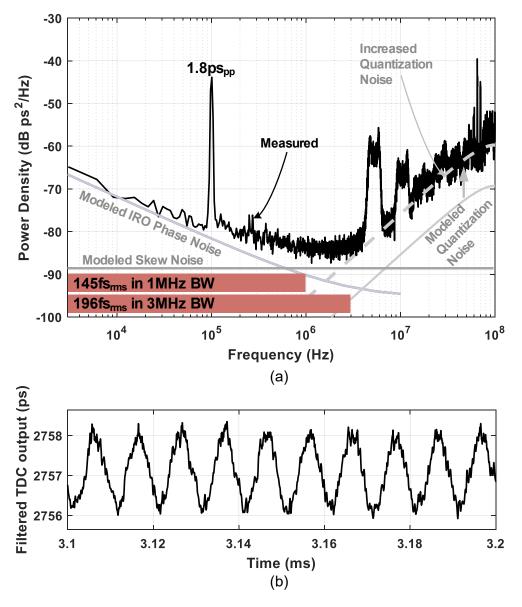

| Figure 4-39 | Measured IRO-TDC output for a 100 kHz 1.8 pspp input signal with          |

|             | $\sim$ 2.76 ns offset, showing (a) a double-sided PSD and (b) time        |

|             | domain output after a 3 MHz digital LPF110                                |

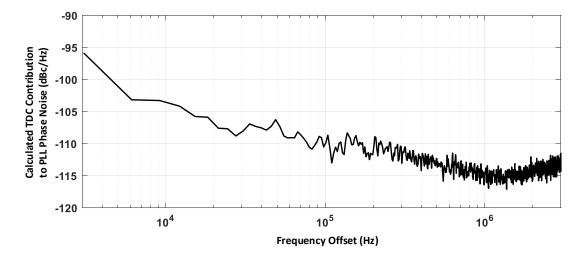

| Figure 4-40 | Calculated TDC contribution to a 3 GHz PLL output phase noise             |

|             | (without considering PLL bandwidth)111                                    |

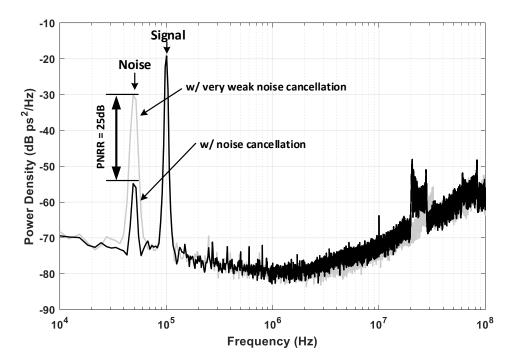

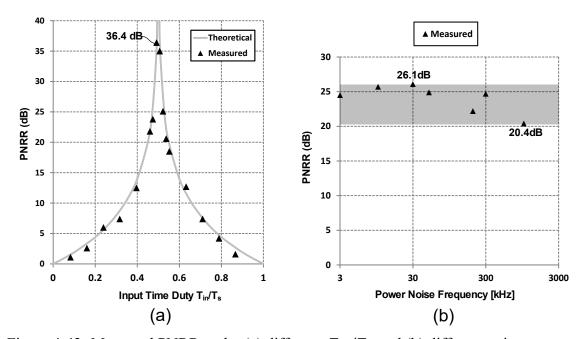

| Figure 4-41 | PNRR obtained from PSD comparison between outputs with strong             |

|             | and very weak noise cancellation                                          |

| Figure 4-42 | Measured PNRR under (a) different <i>Tin/Ts</i> and (b) different noise   |

|             | frequencies113                                                            |

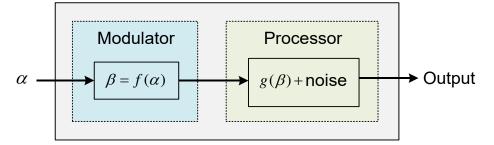

| Figure 5-1  | Concept of data processing with modulation120                             |

## **List of Tables**

| Table 2-1 | Closed-Loop Transfer Functions from each Noise Source to PLL         |

|-----------|----------------------------------------------------------------------|

|           | Output14                                                             |

| Table 2-2 | Different Technologies Preferred by Various Functional Circuits21    |

| Table 2-3 | Characteristics Comparison between Analog and Digital PLLs in        |

|           | Processes with Moderate and Small Feature Sizes27                    |

| Table 3-1 | Comparison among Fractional-N Divider PLLs and SSPLLs43              |

| Table 3-2 | Closed-Loop Transfer Functions from each Noise Source to PS-SSPLL    |

|           | Output47                                                             |

| Table 3-3 | Specifications of the PS-SSPLL Prototype48                           |

| Table 3-4 | Summary of Parameters Related to Loop Bandwidth56                    |

| Table 3-5 | Comparison with Other State-of-the-Art Fractional-N SSPLLs63         |

| Table 4-1 | Closed-Loop Transfer Functions from TDC and DCO Noises to Digital    |

|           | PLL Output67                                                         |

| Table 4-2 | A Conceptual Comparison among GRO, SRO, and IRO73                    |

| Table 4-3 | Characteristics Comparison among GRO, SRO, and IRO-TDCs92            |

| Table 4-4 | Post-Layout Simulation and Calculation Results of the Simple IRO     |

|           | Implementation with 200 MHz Sampling Rate96                          |

| Table 4-5 | Post-Layout Simulation and Calculation Results of the Multi-Path IRO |

|           | Implementation with 200 MHz Sampling Rate98                          |

| Table 4-6 | Simulated and Calculated Results of IRO-TDC In-Band Noise111         |

| Table 4-7 | Comparison with Other Start-of-the-Art Noise-Shaping TDCs115         |

| Table 5-1 | Mathematical Operations in Time-to-Phase Conversions in GRO, SRO,    |

|           | and IRO122                                                           |

## **1** Introduction

#### 1.1 CMOS PLLs in RFIC

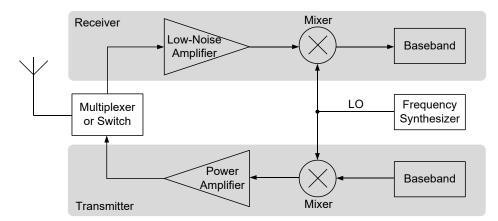

In most radio frequency integrated circuit (RFIC) for wireless communications, frequency synthesizers are used to generate local oscillator (LO) signals for other blocks. As shown in Figure 1-1, a common wireless transceiver comprises three main modules, including the receiver, the transmitter, and the frequency synthesizer. A PLL technique is usually adopted as the core of the frequency synthesizer to regulate the LO signals. The LO signals determine the frequency at which the transceiver communicates with other devices. Therefore, the PLLs have critical importance to the communication quality.

Figure 1-1 A general architecture of a wireless transceiver.

In traditional IC technologies, the RF front-end circuits were implemented using processes such as bipolar junction transistors (BJTs), gallium arsenide (GaAs), silicon-germanium (SiGe), while the digital signal processing (DSP) circuits and analog circuits were implemented in complementary metal–oxide–semiconductor (CMOS) technologies. It was the time when designers faced many challenges when fabricating RF circuits on CMOS process. However, many of these challenges have been resolved, such as high-quality on-chip inductors [1]-[4], wide-band CMOS oscillators [5]-[7], CMOS low-noise amplifiers [8]-[10], etc. Moreover, due to the surge of consumer electronics such

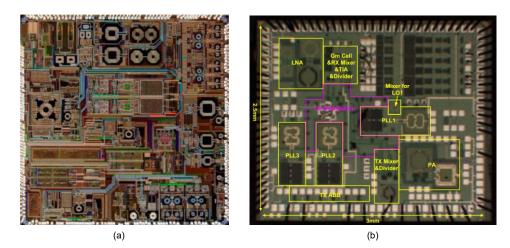

as smartphones and entertainment electronics, wireless applications evolve towards low power, small dimensions, higher yield, and higher level of integration owing to its low cost. Driven by these incentives, efforts have been made to combine RF modules and baseband circuits in a single CMOS chip. Figure 1-2 shows two RFIC arts. Figure 1-2(a) is a micrograph of an RF transceiver chip from Qualcomm, equipping frequency synthesizers for GSM, WCDMA, and GPS with about 1/4 of its total area and power consumption [11]. Figure 1-2(b) shows a prototype of one of the author's projects for IEEE 802.11 WLAN application. This prototype includes three PLL frequency synthesizers and a buffer network for LO clock delivery [12]. In fact, CMOS PLL frequency synthesizers are commonly considered as the most complicated blocks in an RFIC, and usually determine the design cycle of a RFIC product [13].

Figure 1-2 (a) An RF transceiver from Qualcomm [11], and (b) a 802.11 WLAN RF front-end [12].

#### **1.2 CMOS PLLs Challenges in Future Communications**

In general, for PLLs adopted in RF frequency synthesizers, designers have to consider at least three specifications. Firstly, the frequency has to be tuned accurately with small steps, so that the transceiver can communicate precisely at the target frequency. Secondly, the LO signals should be clean in spectrum with low phase noise. Thirdly, the synthesizer should settle and generate the LO signals within a specified time. For example, in GSM applications, the frequency has to settle within 200  $\mu$ s.

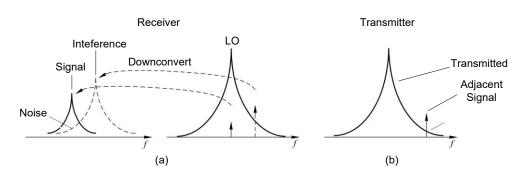

Figure 1-3 Phase noise impact on (a) receiver and (b) transmitter [13].

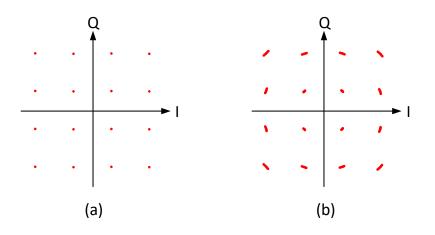

Figure 1-4 Constellation diagram with (a) no phase noise and (b) large phase noise.

A poor phase noise performance can lead to many serious consequences to wireless communication. Figure 1-3 illustrates these impacts. For receivers, an LO with poor phase noise makes the mixer convert not only the wanted RF signal but also some adjacent interferences down to baseband, degrading the SNR of the signal, as shown in Figure 1-3(a). In transmitters, a poor LO phase noise is emitted by the power amplifier and contaminates other channels nearby, as shown in Figure 1-3(b). Some modern wireless standards utilize phase information to transmit data, such as Gaussian minimum shift keying (GMSK) and phase-shift keying (PSK) in phase modulated GSM/EDGE. The in-band phase noise can introduce rotation and degradation to the constellation diagram, as shown in Figure 1-4.

Figure 1-5 Constellation diagrams of 64-, 256-, and 1024-QAM.

As wireless communication standards are becoming more complicated, the specifications for frequency synthesizers are also more stringent than that in the older generations.

One important challenge in future is that the modulation scheme is becoming more complicated and requiring better phase noise performance from the PLLs. For example, in 802.11n standard, the most complicated modulation is 64-quadrature amplitude modulation (-QAM). The later 802.11ac requires a more sophisticated 256-QAM, and the latest 802.11ax even requires a 1024-QAM modulation for higher data rate. In terms of the constellation diagram, this leads to a more congest pattern, as shown in Figure 1-5. As phase noise cause rotation to the constellation diagram and degrades the communication quality, the PLL phase noise performance becomes increasingly important in future [14]-[17].

Another challenge is that a wide bandwidth is preferred and sometimes required. As PLL is essentially a control loop, it has an own loop bandwidth which determines the major characteristics. A wide PLL bandwidth is desirable as it results in [18]-[23]:

- Improved data modulation bandwidth for higher data throughput

- Larger suppression of oscillator phase noise, which helps to reduce power consumption (will be explained in Chapter 2)

- Faster settling time to meet specified requirement

- Reduced oscillator pulling to enhance robustness

Due to the increased loop bandwidth and lower phase noise, the in-band phase noise performance is becoming increasingly important in future.

To summarize, the challenge for the PLLs in future is the reduction of the phase noise, especially the in-band phase noise, without scarifying other important features such as fast settling time.

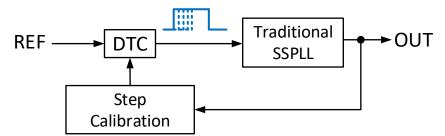

However, conventional analog PLL structures fail to satisfy this requirement because the noise of their phase detector and charge pump is amplified and dominates the in-band phase noise. Fractional-*N* SSPLL has been proposed to eliminate this amplification and has achieved low in-band phase noise. However, these SSPLLs require time-consuming calibrations. In order to apply these SSPLLs into communications requiring short settling time, such calibration time has to be reduced or totally eliminated.

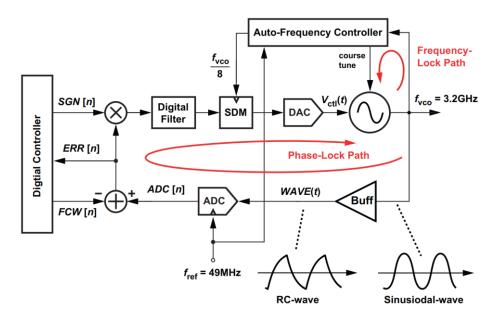

On the other hand, a digital PLL architecture has been reported to take advantages of the future CMOS processes with finer feature size. Phase detector and charge pump do not exist in such architecture. In-band phase noise of these digital PLLs is dominated by the noise from their TDCs. Designers have made great effort to reduce the TDC noise using different TDC structures. One of the promising approaches is utilizing noise shaping by employing controlled oscillator-based TDCs due to their low in-band noise. Yet, the in-band noise of these TDCs is dominated by the internal oscillator phase noise. And there is no prior technique to further reduce such noise. In addition, prior arts of these TDCs draw varying supply current, introducing disturbance to the power supply and hence to other circuitries in a digital PLL, leading to other phase noises.

In order to overcome these challenges, the goal of this thesis is to investigate and propose techniques to reduce in-band phase noise of both analog and digital PLLs.

#### **1.3 Major Contributions of the Thesis**

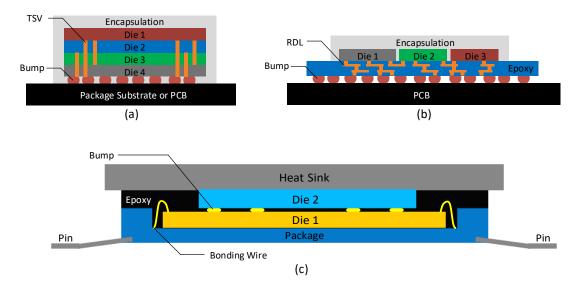

As the background of this research, we review the current limitations of *Moore's Law* and two promising advanced CMOS technologies, including a function-oriented *more-than-Moore* technology (i.e., system in package (SiP) technology) and a

cost-oriented *more-Moore* technology (i.e., system on a chip (SoC) technology). In regard to PLL implementation, the SiP technology permits the use of CMOS with larger feature size in which analog PLLs can be designed and verified with mature methods, while the SoC technology keeps following *Moore's Law* and tries to use finer processes in which digital PLLs may be more suitable due to their promising performance that can be improved by technology scaling. Therefore, this thesis tries to achieve in-band noise reduction in both PLL types. Accordingly, contributions in this research can be divided into two parts.

The first part focuses on analog PLL in-band phase noise. In-band phase noise of a conventional analog PLL is usually limited by the noise amplification of phase detector and charge pump. Fractional-*N* SSPLLs can be used to reduce this noise amplification. However, prior arts of such PLLs require time-consuming calibrations. Contributions in this part are listed below.

- Prior arts in low-noise fractional-*N* SSPLL have been investigated. Their needs for the time-consuming calibrations are explained.

- A novel PS-SS technique that can eliminate the need for calibrations is introduced. This PS-SS technique utilizes the phase information from the voltage-controlled oscillator (VCO) output rather than a calibrated digital-to-time converter (DTC). Hence, the phase is inherently related to the VCO phase without any calibration.

- A phase model for PS-SSPLL analysis is proposed. This phase model can be used for output phase noise prediction and design optimization not only in this research, but also in future designs with similar operation.

- A prototype fractional-*N* PS-SSPLL is designed, fabricated, and measured to verify the proposed PS-SS technique. An 8-phase output at 2.6-3.4 GHz is available in this structure. The prototype achieves an in-band phase noise of -100.3 dBc/Hz and an FoM of -234.3 dB. Under a calibration-less condition, this

prototype achieves the best jitter performance and FoM among the fractional-*N* SSPLLs.

Conclusions and design suggestions for similar future designs are provided. The core idea of PS-SS technique is to obtain phase shifting steps from the VCO phase rather than a calibrated circuit. This idea can drive other implementations of calibration-free designs.

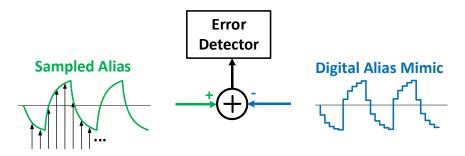

The second part focuses on digital PLL in-band phase noise, which is usually limited by the TDC noise. Prior arts have been achieved low TDC in-band noise through noise shaping by using controlled oscillators, but there is still headroom towards lower in-band noise. Therefore, in this part, the major focus is to further reduce the TDC in-band noise. Contributions in this part are listed below.

- A noise model is proposed to analyze the noise characteristics of the controlled oscillator-based TDC family. In this model, operation of these TDCs is generalized as transformation from time domain to phase domain and digital domain. By analyzing the noises in these transformations, the TDC noise can be predicted in order to help with design and optimization. This model can also conduce to future TDC designs with more complicated controlled oscillators.

- A novel IRO technique that can reduce the TDC in-band noise is introduced. This IRO can invert its oscillation direction with unchanged frequency. By doing this, a potentially larger gain can be expected, and the noise performance can be improved. In addition, due to the constant oscillator frequency, the supply current is kept constant, leading to a reduced disturbance to the power supply and other circuitries when applied in a digital PLL.

- A prototype IRO-TDC is designed, fabricated, and measured to verify the proposed IRO technique. With a sampling rate of 200 MS/s and a wide signal bandwidth of 3 MHz, the IRO-TDC prototype achieves a low in-band noise of 196 fs<sub>rms</sub>, outperforming state-of-the-art works. To our knowledge, this is the first

demonstration of utilizing oscillation inversion to reduce the impact of oscillator phase noise and achieve coherent noise cancellation.

- A unique coherent oscillator phase noise cancellation in the proposed IRO is predicted by the noise model and verified through measurement results. A cancellation ratio of up to 36.4 dB is achieved in measurement. This unique noise cancellation protects the TDC from the coherent noise sources such as power supply noise and substrate noise.

- Conclusions and design suggestions for similar future designs are provided. The proposed IRO utilizes oscillation inversion to achieve noise reduction, coherent noise cancellation, and low disturbance to power supply at the same time. As an extension, the proposed idea suggests future converters to utilize polarity of a parameter, rather than its amplitude, to achieve similar properties.

Together, these contributions demonstrate helpful techniques that can enhance the noise performance of the analog and digital CMOS PLLs in future advanced CMOS technologies.

#### **1.4** Organization of the Thesis

The rest of this thesis is organized as follows.

Chapter 2 provides the background of this research. To begin with, PLL principle and noise characteristics are briefly introduced to identify the contributors of in-band phase noise. Detailed analysis of in-band noise depends on the actual PLL implementation in different CMOS technologies. Therefore, the development of CMOS technologies is also reviewed. This chapter summarizes the implementation considerations of PLLs in different applications and technologies, and serves as a guidance of this research. Our conclusion in this chapter is that advanced CMOS technologies will follow both an SiP technology where analog PLLs may be preferable, and an SoC technology where digital PLLs may be more suitable. The following chapters deal with these two PLL types accordingly.

Chapter 3 focuses on in-band noise reduction for analog PLLs. Literature review of divider PLLs and SSPLLs is provided as the basis of our exploration. The reasons and drawbacks of the time-consuming calibration issue are discussed. The proposed PS-SS technique and PS-SSPLL implementation are described in detail, with measurement results provided. At the end of this chapter, we point out some potential drawbacks in this prototype and provide possible solutions.

For a digital PLL, the in-band phase noise is usually limited by the TDC. Therefore, the main focus of Chapter 4 is on low-noise TDCs, which can be applied to reduce in-band phase noise of digital PLLs. Among various TDC types, the controlled oscillator-based TDCs provide attractive noise-shaping characteristics and achieve low in-band noise. Literature review about this TDC family is provided. The proposed IRO and noise model are described in detail. Noise characteristics of gated ring oscillator- (GRO-), switched ring oscillator- (SRO-), and IRO-TDCs are also compared. The unique IRO noise cancellation is predicted using the noise model. Measurement results and calculation results from the model are provided and compared. At the end, we conclude this IRO-TDC work, point out drawbacks of the prototype, and give some possible solutions.

Chapter 5 draws the conclusion of this research and provides recommendations for future work. Core ideas of the proposed techniques are reworded in a physical point of view for future researches. Other possible implementations of the proposed techniques are also mentioned.

## 2 Background on CMOS PLLs

#### 2.1 PLL Fundamentals

In this chapter, in order to provide the reader a conceptual understanding of PLLs, we will introduce some PLL fundamentals without diving into circuit details. In the later PLL analysis, some fundamentals in this chapter will be extended accordingly.

As suggested by its name, the purpose of a PLL is to adjust an output phase according to an input phase with a given input-output relation. Such a required function dates back to 1930s when researchers were building a direct-conversion receiver, in which the receiver LO was tuned to the desired input frequency and multiplied with the input signal in order to obtain the original modulation information. Since the LO frequency would drift, a feedback control mechanism is needed to correct the LO frequency in order to maintain the phase and frequency of the desired LO signal. The technique was described in [24]-[25] by Henri de Bellescize in 1932.

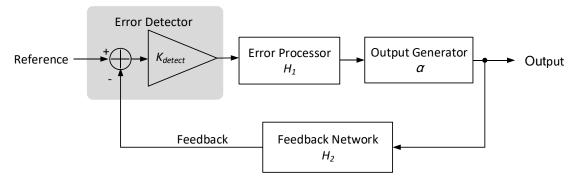

Figure 2-1 Conceptual diagram of a feedback control loop.

#### 2.1.1 Conceptual Architecture

A PLL is essentially a negative feedback loop with high feedforward gain and accurate feedback factor. Figure 2-1 shows the conceptual diagram of a feedback control loop. Such a conceptual diagram can apply to other kinds of control loop circuits such as closed-loop DC-DC converters, low-dropout (LDO) regulators, closed-loop amplifiers, etc. Functions of different blocks are described next.

A controllable output generator is to produce the wanted output signals across a targeted range. In PLL, a controlled oscillator is used to generate the output clock, i.e., the output phase.

An input is applied to the loop as the reference for the output signal. For LDO and DC-DC converters, the parameter to be controlled is the output voltage. A bandgap reference circuit is normally integrated in the IC to provide a constant reference voltage, because the BJTs in IC technologies can provide a voltage with sufficiently small deviation across a wide range of process, supply voltage, and temperature (PVT) variations. Similar to a reference voltage, a reference phase (or a reference clock) can also be generated in the IC itself. However, such an integrated clock in IC has poor frequency stability due to material limitations. This poor frequency stability is unacceptable for most RF transceivers. As a matter of fact, for a common PLL for RF transceivers, the reference clock is generally from an external clock source with much more stable frequencies, such as a crystal oscillator.

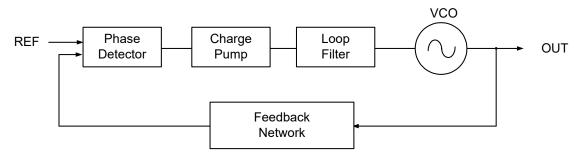

In order to maintain a certain relation between the output and input parameters, a feedback network, an error detector and an error processor are used. In this thesis, we term a set of components an "error detector" if their function is to detector the difference between the reference and the feedback signal and to generate a signal representing this difference. For conventional analog PLLs, the error detector comprises a phase detector and a charge pump. For digital PLLs (which will be introduced later), the error detector is usually a TDC. The error detector usually has its own gain, which is denoted as  $K_{detect}$ . Generally, a high feedforward gain ( $K_{detect}H_1\alpha \gg 1$ ) and an accurate feedback gain ( $H_2$ ) are adopted, and the open-loop gain is usually high ( $K_{detect}H_1\alpha H_2 \gg 1$ ). The output signal of the error detector represents the error between the input reference and the feedback information. An error processor takes this signal and generate a control signal to regulate the output generator. This error processor is usually a low-pass filter, and thus called a "loop filter" in PLL researches. The closed-loop gain of this control loop can be expressed as

$$A_{cl} = \frac{K_{detect}H_1\alpha}{1 + K_{detect}H_1\alpha H_2} \approx \frac{1}{H_2}.$$

(2-1)

If the feedforward gain is changed by  $\Delta(K_{detect}H_1\alpha)$ , the variation of the loop gain is

$$\frac{\Delta A_{cl}}{A_{cl}}\Big|_{H_2} = \frac{1}{1 + K_{detect}H_1\alpha H_2} \cdot \frac{\Delta (K_{detect}H_1\alpha)}{K_{detect}H_1\alpha} \approx 0.$$

(2-2)

This implies that for normal PLLs ( $K_{detect}H_1\alpha H_2 \gg 1$ ), the loop gain is not sensitive to the feedforward gain. Similarly, if the feedback gain is changed by  $\Delta H_2$ , loop gain variation is

$$\frac{\Delta A_{cl}}{A_{cl}}\Big|_{K_{detect}H_{1}\alpha} = \frac{-K_{detect}H_{1}\alpha H_{2}}{1+K_{detect}H_{1}\alpha H_{2}} \cdot \frac{\Delta H_{2}}{H_{2}} \approx -\frac{\Delta H_{2}}{H_{2}}.$$

(2-3)

In contrast, this implies that the PLLs are sensitive to the feedback gain. Thus, an accurate and linear feedback gain has to be guaranteed. In fact, the feedback network determines the input-output relation of the target parameter.

The above discussion reveals that the feedforward path requires a high gain and the feedback network requires sufficient accuracy and linearity.

Note that this PLL concept is not limited to circuit implementations. All the above blocks may be embodied in software (software PLL), neurons (neuronal PLL), natural phenomena, and even human activities.

#### 2.1.2 Noise Contributors

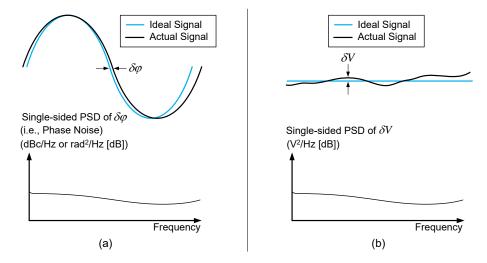

Using the conceptual structure, we can obtain a simplified analysis of the PLL noise performance. As a PLL is used to provide phase information, when considering the noise from the PLL, a concept of phase noise is usually adopted since the amplitude noise seldom affects the transceiver performance. The phase noise is defined by the deviation from the ideal phase to the actual phase, as shown in Figure 2-2. A common expression of phase noise is the single-sided power spectral density (PSD) of the stochastic instantaneous phase error,  $\delta \varphi$ . The unit of this PSD is *dBc/Hz*, where character *c* refers to *carrier frequency*. The unit *dBc/Hz* is the logarithmic of *rad<sup>2</sup>/Hz*. The expression of phase noise can be better understood through an analogy with the single-sided PSD of a voltage noise, where the unit is  $V^2/Hz$ . The instantaneous phase error,  $\delta \varphi$ , can also be converted into a time domain jitter in some analysis.

Figure 2-2 Comparison between concepts of (a) phase noise and (b) voltage noise.

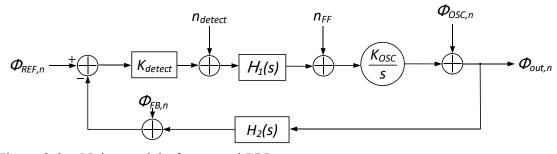

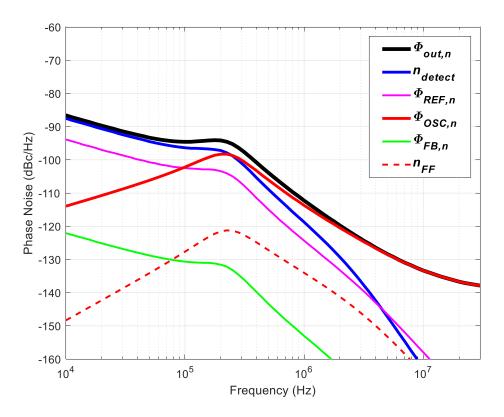

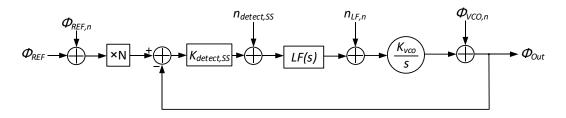

Each sub-circuit in a PLL, as well as the input reference signal, generates its own noise. These noises may be transformed into phase domain by the PLL, and thus contributes to the output phase noise. Figure 2-3 shows a noise model of a general PLL. Parameters  $\Phi_{REF,n}$ ,  $\Phi_{FB,n}$ ,  $n_{detect}$ ,  $n_{FF}$ , and  $\Phi_{OSC,n}$  represent the input reference phase noise, feedback phase noise, error detector noise, error processor noise, and oscillator phase noise, respectively.  $K_{OSC}$  is the control gain of the oscillator. The closed-loop transfer function for each noise source is listed in Table 2-1. As can be seen later in Chapter 3, low in-band phase noise can be guaranteed in the feedback network. Therefore, it has a negligible contribution to the PLL in-band phase noise.

Figure 2-3 Noise model of a general PLL.

| Noise Source     | Transfer Function*                                                                                   | Transfer Function Type |

|------------------|------------------------------------------------------------------------------------------------------|------------------------|

| Reference Phase  | $\frac{\Phi_{out,n}}{\Phi_{REF,n}}(s) = \frac{1}{H_2(s)} \cdot \frac{G(s)}{1 + G(s)}$                | Low Pass               |

| Feedback Phase   | $\frac{\Phi_{out,n}}{\Phi_{FB,n}}(s) = \frac{-1}{H_2(s)} \cdot \frac{G(s)}{1 + G(s)}$                | Low Pass               |

| Error Detector   | $\frac{\Phi_{out,n}}{n_{detect}}(s) = \frac{1}{K_{detect} \cdot H_2(s)} \cdot \frac{G(s)}{1 + G(s)}$ | Low Pass               |

| Error Processor  | $\frac{\Phi_{out,n}}{n_{FF}}(s) = \frac{K_{OSC}}{s} \cdot \frac{1}{1 + G(s)}$                        | Band Pass              |

| Oscillator Phase | $\frac{\Phi_{out,n}}{\Phi_{OSC,n}}(s) = \frac{1}{1+G(s)}$                                            | High Pass              |

Table 2-1

Closed-Loop Transfer Functions from each Noise Source to PLL Output

\* Open-loop transfer function  $G(s) = K_{detect} \cdot H_1(s) \cdot H_2(s) \cdot K_{OSC}/s$ .

Figure 2-4 An example of noise source contributions to the PLL output phase noise.

As an example, Figure 2-4 plots the phase noise contribution of each in a typical PLL. From the figure and Table 2-1, the PLL in-band phase noise may be dominated by the input reference noise or comparator noise since they follow low-pass transfer function, whereas the out-of-band phase noise is probably dominated by the oscillator due to its high-pass transfer function.

The high-pass transfer function of the oscillator phase noise implies a suppression of the oscillator phase noise within the PLL bandwidth. This reveals that within the loop bandwidth, the negative feedback mechanism can correct the oscillator output phase according to the input reference phase; while at the frequencies outside the loop bandwidth, the oscillator noise is changing so fast that the loop fails to correct it. This reveals that, with a wider loop bandwidth, more oscillator phase noise can be suppressed, so that a noisy oscillator with lower power consumption can be adopted. Therefore, a wide-bandwidth PLL is preferred in terms of the oscillator noise and power dissipation.

Another consideration for wide bandwidth is the loop transient. With a wider bandwidth, the PLL can lock from one target frequency to another faster, in order to fulfill the requirement of the corresponding standard. Moreover, for some applications the PLL is used not only to provide the LO, but also to modulate the LO signal. Under such a scheme, the modulation input is controlling the target output frequency. Such a modulation follows the same low-pass transfer function. Obviously, a wider loop bandwidth permits a wider modulation bandwidth, hence a wider data bandwidth. However, the phase model in Figure 2-3 is an approximation with the precondition that the loop bandwidth is much smaller than the reference frequency. Consequently, for most PLLs, the loop bandwidth is an order of magnitude lower than the reference frequency.

As PLL bandwidth increases, the integrated in-band phase noise becomes more important to the PLL overall noise. If the reference clock is provided by an external crystal oscillator, its phase noise is usually very low. Therefore, the error detector noise is usually the major contributor to the in-band noise. From a general point of view, the proposed techniques in this thesis aim to reduce noise from the error detectors.

#### 2.2 CMOS Technology Development

Actual implementation of a PLL depends on the process technology. Transistors in various processes have different characteristics, such as leakage and noise performance. Therefore, there is not a single scheme or integration level that is optimized for all IC technologies. In fact, the proposal of PLL technique (Bellescize, 1932) and applications of PLL in television receivers (late 1930s) date back to even well before the invention of the first IC (Jack Kilby, 1958).

Early monolithic PLL ICs (e.g., [37]-[39]) integrated the phase detector and oscillator in a single chip, but without reference clock, loop filter (as the error processor) or feedback network. Users were thus able to configure the loop filter and the frequency division ratio externally. However, bulky passive components for the loop filter made the whole design very large, and interconnections between the IC and the printed circuit board (PCB) also degraded the PLL performance. Current fully integrated PLLs in modern RFICs leave only the reference clock source outside the chip (e.g., [11]-[12]). Crystal oscillators are still commonly used as the reference clock source for modern wireless transceiver PLLs.

The PLLs we will discuss in this thesis are limited to designs fabricated in CMOS technologies. In order to provide a ground for our research and to help future explorations, next, we will review the CMOS technology development that is related to PLL implementation.

#### 2.2.1 Moore's Law and Limitations

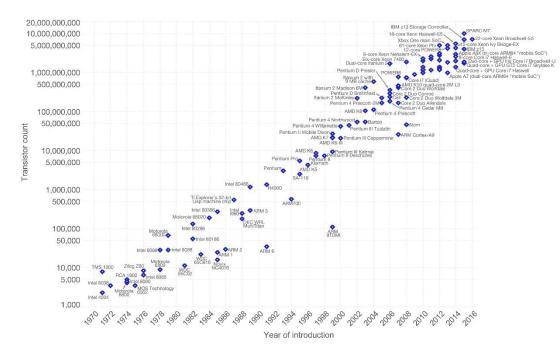

The history of IC technology can be represented by one famous observation, the *Moore's Law*, which is named after Gordon Moore. It projected that the number of transistor components per IC area would double after every two years. The chip performance was predicted to improve with the similar pace. The reason of *Moore's Law* is that the semiconductor industry needs an appropriate growth pace to maximize the overall profit. Companies would spend certain amount of their profit to upgrade their technologies, in order to increase their future profit. Figure 2-5 shows this evolution during the past several decades.

Figure 2-5 Microprocessor transistor counts in 1971-2011 [40].

Along with the size scaling, the IC performance enhanced during the last decades. Due to size shrinking, power consumption was reduced and speed was increased. Chips with higher-performance can be fabricated with same power specification.

Two driving forces for *Moore's Law* include fabrication technology development and economic considerations. At larger feature sizes, scaling seems promising and easy. Lithography masks used to fabricate ICs could be produced with smaller and smaller resolutions. Companies were willing to invest for new technologies in order to improve performance, to reduce cost and to maximize profits. However, physical laws and the size of atoms are not scalable. These facts set a huge barrier against the CMOS feature size scaling. As the feature size approaches the boundary of macrophysics and quantum physics, research and development (R&D) of advanced process technologies is becoming tremendously challenging and expensive.

#### **Physical Limitations**

The major physical limitations are quantum effects and lithography accuracy. When the feature size is reduced to 10 nm, quantum effects need to be considered, making the transistor characteristics difficult to control. For example, the quantum tunneling effect

results in serious transistor leakage and degrades the transistor performance dramatically. For mobile applications, this means a high power consumption and short battery life even in a standby mode. Such leakage also degrades the analog/RF circuit performance. Another limitation is the lithography accuracy, which is mainly determined by the wavelength of the light for lithography. In order to obtain smaller resolution, it requires light with extremely small wavelength and the corresponding photoresist. Lack of these tools calls for more researches in the fabrication research.

# **Economic Limitations**

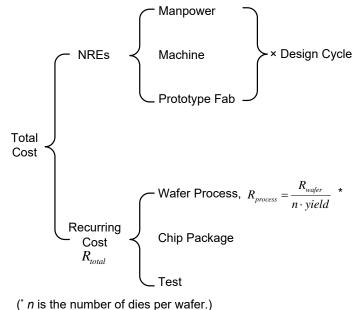

In order to understand the economics of an IC chip, it is important for the IC designer and company to be able to anticipate the cost and time required. For a particular IC product, the total cost includes the following elements:

- Non-recurring engineering (NRE) costs, including cost for manpower (designers, supporting staffs, etc.), tools (computers, software, process design kits (PDKs), intellectual properties (IPs), etc.), and most importantly the prototype fabrication. In addition, NREs tend to increase with longer design cycle.

- Recurring cost, *R*<sub>total</sub>, which is spent on each product and thus increases with the number of product. This includes the wafer process cost, packaging cost, and test cost.

The total cost of a product can be expressed as

$$C_{total} = NREs + R_{total} \times N, \qquad (2-4)$$

where N denotes the total number of the product. Figure 2-6 illustrates the major costs for the product.  $R_{process}$  refers to the wafer process cost for each die. It depends on the cost per wafer (i.e.,  $R_{wafer}$ ), number of dies per wafer (i.e., n), and yield.

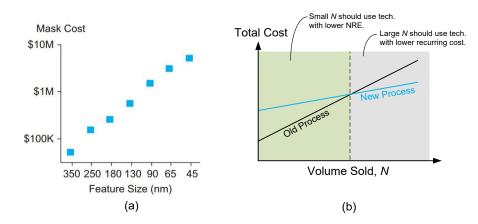

Scaling of feature size mainly helps reduce process cost of each die and increase profit. As the transistors and the whole IC can be produced in a smaller size, the wafer process cost for each chip,  $R_{process}$ , shrunk continuously because they need less materials and area. On the other hand, for processes with smaller feature size, the design tools (such as PDKs and IPs) and prototype fabrication are more expensive. Hence, NREs increase with smaller feature size.

Figure 2-6 Costs of an IC product [41].

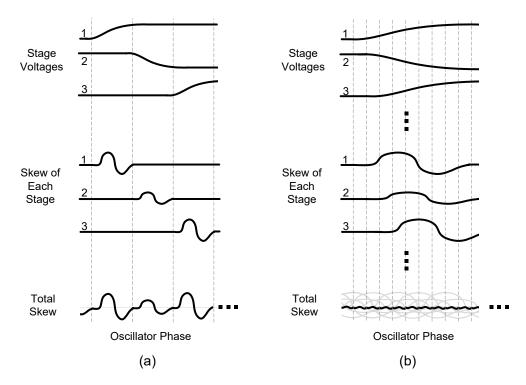

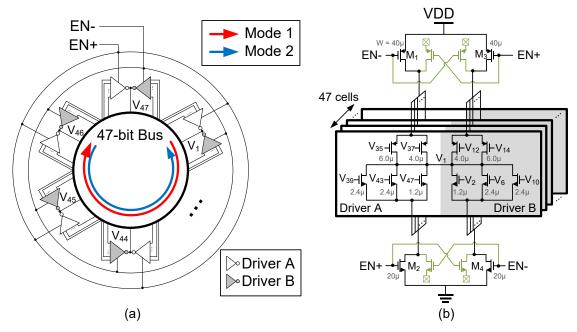

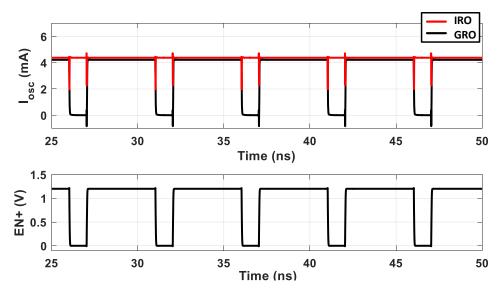

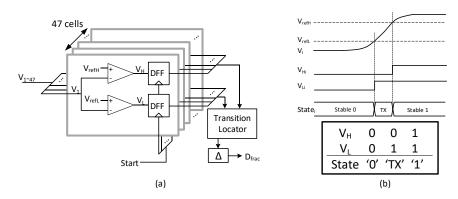

Figure 2-7 (a) Approximate mask set cost [41]. (b) Product total cost in old and new technologies.