Louisiana State University

LSU Digital Commons

LSU Doctoral Dissertations

**Graduate School**

2016

# Increasing Off-Chip Bandwidth and Mitigating Dark Silicon via Switchable Pins

Shaoming Chen Louisiana State University and Agricultural and Mechanical College

Follow this and additional works at: https://digitalcommons.lsu.edu/gradschool\_dissertations

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Chen, Shaoming, "Increasing Off-Chip Bandwidth and Mitigating Dark Silicon via Switchable Pins" (2016). *LSU Doctoral Dissertations*. 3337. https://digitalcommons.lsu.edu/gradschool\_dissertations/3337

This Dissertation is brought to you for free and open access by the Graduate School at LSU Digital Commons. It has been accepted for inclusion in LSU Doctoral Dissertations by an authorized graduate school editor of LSU Digital Commons. For more information, please contactgradetd@lsu.edu.

## INCREASING OFF-CHIP BANDWIDTH AND MITIGATING DARK SILICON VIA SWITCHABLE PINS

A Dissertation

Submitted to the Graduate Faculty of the Louisiana State University and Agricultural and Mechanical College in partial fulfillment of the requirements for the degree of Doctor of Philosophy

in

School of Electrical Engineering and Computer Science

by

Shaoming Chen B.E., Huazhong University of Science and Technology, Wuhan, China 2008 M.E., Huazhong University of Science and Technology, Wuhan, China 2011 August 2016

#### ACKNOWLEDGEMENTS

I would like to dedicate the dissertation to my parents and my friends for their continuous support and encouragement throughout my entire life.

This dissertation is completed with the valuable help and support from a lot of people including my advisor, Dr. Lu Peng. He thoughtfully guided me to pick up the emerging topic and offered valuable advises for my study. Dr. Ashok Srivastava gave appreciated help of circuit design and encouraged me to response bitter feedbacks from reviewers. Dr. Bin Li from Department of Experimental Statistics provided insightful statistical methods to help me to analyze experimental data. Dr. David Koppelman and Dr. Rudy Hirschheim as my committee members take their valuable time to supervise my dissertation and attend my defense. I sincerely appreciate the professors' supports as the foundation of the work. I also would like to thanks my co-workers in my lab. Dr. Zhang provided insight thoughts that helped me to develop the dissertation. Yue devoted enormous effort on circuit design especially on power delivery network. Zhou elaborated the circuit design and helped me to improve the circuit design. Sam proofread the work and gave me wonderful feedbacks.

I am thankful to the Department of Electrical and Computer Engineering for providing assistantship throughout my study.

Finally, I would like thank all the friends I met at LSU for making my life here wonderful and memorable.

| ACKNOWLEDGEMENTS                                                            | ii |

|-----------------------------------------------------------------------------|----|

| LIST OF TABLES                                                              | v  |

| LIST OF FIGURES                                                             | vi |

| ABSTRACT                                                                    | X  |

| CHAPTER 1. INTRODUCTION                                                     | 1  |

| 1.1. MOTIVATIONS                                                            | 1  |

| 1.2. DISSERTATION ORGANIZATION                                              | 6  |

| CHAPTER 2. INCREASING OFF-CHIP BANDWIDTH IN MULTI-CORE                      |    |

| PROCESSORS WITH SWITCHABLE PINS                                             | 9  |

| 2.1. DESIGN OVERVIEW                                                        | 9  |

| 2.1.1 Pin Switch                                                            | 9  |

| 2.1.2 Off-Chip Bus Connection                                               | 12 |

| 2.1.3 Memory Controller                                                     |    |

| 2.1.4 Area Overhead                                                         |    |

| 2.1.5 Address Mapping                                                       |    |

| 2.1.6 Signal Integrity                                                      |    |

| 2.1.7 Power Delivery Simulation                                             |    |

| 2.1.8 Runtime Switch Conditions                                             |    |

| 2.1.9 Switching Overhead                                                    |    |

| 2.2. EXPERIMENTAL SETUP                                                     |    |

| 2.2.1 Performance and Energy Efficiency Metrics                             |    |

| 2.2.2 Workloads                                                             |    |

| 2.3. RESULTS                                                                |    |

| 2.3.1 Memory-Intensive Workloads                                            |    |

| 2.3.2 Wide-bus mode                                                         |    |

| 2.3.2 Wide-bus mode                                                         |    |

| 2.3.4 Compute-Intensive Workloads                                           |    |

| 2.3.4 Compute-intensive workloads                                           |    |

| CHAPTER 3. MITIGATING DARK SILICON VIA SWITCHABLE PINS                      | 40 |

| 3.1. BACKGROUND                                                             |    |

| 3.2. OVERVIEW DESIGN                                                        |    |

|                                                                             |    |

| <ul><li>3.2.1 Pin Allocation</li><li>3.2.2 Power Delivery Network</li></ul> |    |

| 3.2.2 Power Denvery Network                                                 |    |

|                                                                             |    |

| 3.2.4 Signal Transmission                                                   |    |

| 3.2.5 Thermal Issues                                                        |    |

| 3.2.6 Dynamic Pin Switching based on Program Phases                         |    |

| 3.2.7 Prediction Model                                                      | JI |

## **TABLE OF CONTENTS**

| 3.3. EXPERIMENTAL SETUP                                               | 53   |

|-----------------------------------------------------------------------|------|

| 3.4. RESULT ANALYSIS                                                  | . 56 |

| 3.4.1 Rules Explanation                                               | 56   |

| 3.4.2 Dim Silicon Result                                              | 57   |

| 3.5. RELATED WORK                                                     | . 60 |

|                                                                       |      |

| CHAPTER 4. BOOSTING OFF-CHIP BANDWIDTH WITH PCM VIA                   |      |

| SWITCHABLE PINS                                                       |      |

| 4.1. BACKGROUND                                                       |      |

| 4.2. EXPERIMENTAL SETUP                                               | . 63 |

| 4.3. RESULTS                                                          |      |

| 4.3.1 Memory-Intensive Multi-threaded Workloads                       |      |

| 4.3.2 Memory-Intensive Multi-programmed Workloads using PCM           |      |

| 4.3.3 Memory-Intensive Multi-threaded Workloads using PCM             |      |

| 4.3.4 Mixed Multi-program Workloads on the memory subsystem using PCM |      |

| 4.4. CONCLUSION                                                       | . 68 |

|                                                                       |      |

| CHAPTER 5. INCREASING INTER-SOCKET BANDWIDTH VIA SWITCHABL            |      |

| PINS                                                                  |      |

| 5.1. RELATED WORK                                                     |      |

| 5.2. DESIGN OVERVIEW                                                  |      |

| 5.2.1 Off-chip connection                                             |      |

| 5.2.2 Memory controllers                                              |      |

| 5.2.3 QPI stack                                                       |      |

| 5.2.4 Switch agents                                                   |      |

| 5.2.5 Switch condition                                                |      |

| 5.2.6 Area Overhead & Propagation Delay                               |      |

| 5.2.7 Runtime overhead                                                |      |

| 5.2.8 Signal integrity                                                |      |

| 5.3. EXPERIMENTAL SETUP                                               |      |

| 5.4. RESULT                                                           |      |

| 5.4.1 Performance of the static switching                             |      |

| 5.4.2 Performance of the dynamical switching                          |      |

| 5.4.3 Energy efficiency                                               |      |

| 5.4.4 Enhancement from a stride prefetcher                            |      |

| 5.4.5 The bandwidth of the DRAM cache                                 |      |

| 5.4.6 The size of DRAM cache                                          |      |

| 5.4.7 The frequency of QPI buses                                      |      |

| 5.5. CONCLUSION                                                       |      |

| 5.6. SUMMARY                                                          | . 98 |

|                                                                       |      |

| REFERENCES                                                            | 100  |

|                                                                       | 107  |

| VITA                                                                  | 107  |

## LIST OF TABLES

| Table 2-1. Pin allocation of an Intel Processor i5-4670                                                                                                       | 3 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Table 2-2. Power network model parameters    1                                                                                                                | 9 |

| Table 2-3. Processor power and frequency parameters for different number of buses 2                                                                           | 1 |

| Table 2-4. The Configuration of the simulated system                                                                                                          | 5 |

| Table 2-4. The selected memory-intensive and compute-intensive workloads                                                                                      | 7 |

| Table 3-1. Pin allocation of the Intel Xeon Processor E5-2450L       4                                                                                        | 4 |

| Table 3-2. Processor configurations under different cooling techniques       4                                                                                | 6 |

| Table 3-3. Parameters of the performance and power models                                                                                                     | 4 |

| Table 3-4. Simulated multi-program workloads    5                                                                                                             | 5 |

| Table 4-1. Benchmark memory statistics                                                                                                                        | 3 |

| Table 5-1. The configuration of the simulated system                                                                                                          | 5 |

| Table 5-2. The selected workloads    8                                                                                                                        | 6 |

| Table 5-3. The intervals in the multi-link mode and in the single-link mode as well as the times of switching to the multi-link mode and the single-link mode |   |

## LIST OF FIGURES

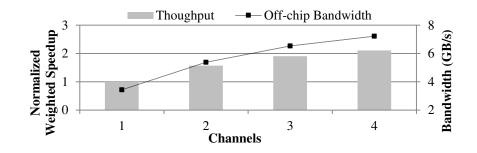

| Figure 1-1. Normalized weighted speedup and off-chip bandwidth of 4 lbm co-running on a processor with 1,2,3,4 memory channels                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

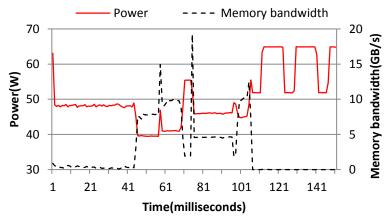

| Figure 1-2. Power and memory bandwidth (8 copies of DEALII from SPEC2006)                                                                                                    |

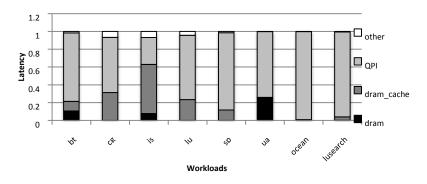

| Figure 1-3. The latency breakdown of un-core requests in the simulated system with two sockets                                                                               |

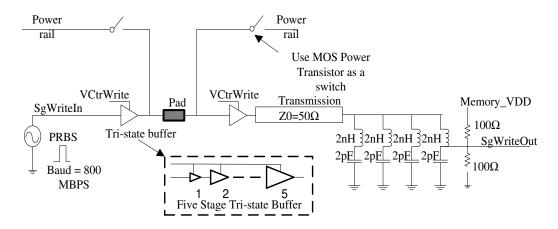

| Figure 2-1. The circuit of pin switch 10                                                                                                                                     |

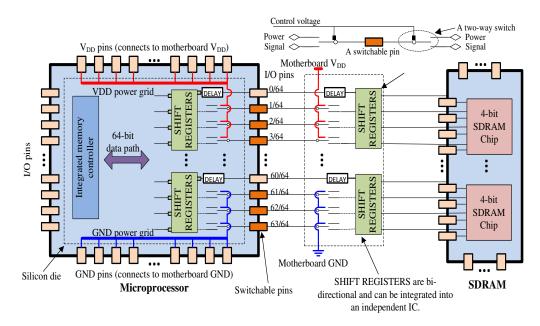

| Figure 2-2. The overview of the hardware design of off-chip bus connection for switching between the Multi-bus mode and the Single-bus mode                                  |

| Figure 2-3. The Overview of the hardware design of memory controller for switching between the Multi-bus mode and the Single-bus mode                                        |

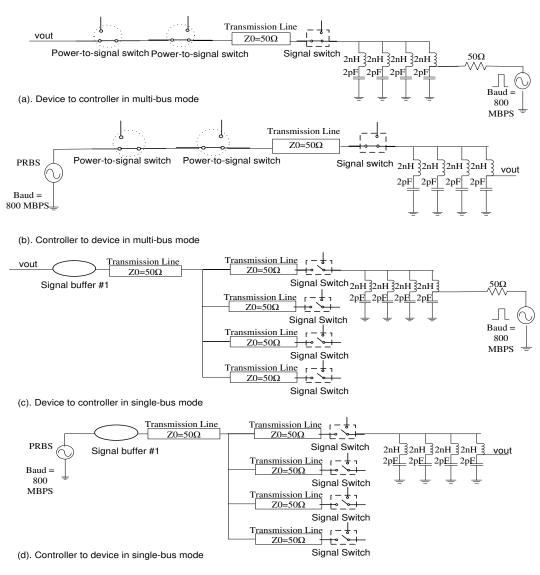

| Figure 2-4. Spice models for signal integrity simulation 17                                                                                                                  |

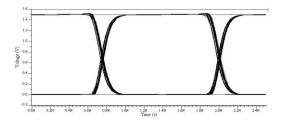

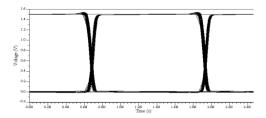

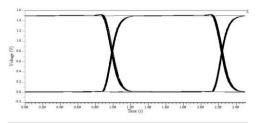

| Figure 2-5. The eye diagrams                                                                                                                                                 |

| Figure 2-6. RLC power delivery model                                                                                                                                         |

| Figure 2-7. The normalized off-chip latencies and on-chip latencies of workloads against the total execution time                                                            |

| Figure 2-8. The normalized weighted speedup of memory-intensive workloads with 2, 3, and 4 buses against the each baseline                                                   |

| Figure 2-9. The average normalized weighted speedup of memory workloads in geometric mean with multi-bus mode. Each normalize to the same configuration with single bus mode |

| Figure 2-10. The normalized weighted speedup of memory intensive workloads boosted by Static Switching and Dynamic Switching with 3 buses against the baseline               |

| Figure 2-11. The increased bandwidth due to pin switching. The normalized bandwidth of baseline, static pin switching, and dynamic pin switching                             |

| Figure 2-12. The improved throughput of Dynamic Switching boosted by a stride prefetchers (degree = 1, 2, 4) for memory-Intensive workloads                                  |

| Figure 2-13. The off-chip bandwidth of Dynamic Switching improved by a stride prefetcher (degree = 1, 2, 4) for memory-Intensive workloads                                   |

| Figure 2-14. The performance of memory intensive workloads for the baseline (core frequency of 4GHz and a memory bus of 64 bits) and two configurations of wide bus          |

| mode (core frequency of 3.6GHz and a memory bus of 128 bits; core frequency of 2.8GHz and a memory bus of 256 bits)                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-15. The off-chip bandwidth of memory intensive workloads for the baseline (core frequency of 4GHz and a memory bus of 64 bits) and two configurations of wide bus mode (core frequency of 3.6GHz and a memory bus of 128 bits, core frequency of 2.8GHz and a memory bus of 256 bits) |

| Figure 2-16. The normalized EPI of Dynamic Switching for memory intensive workloads with 3 buses, and the EPI from DVFS (running on 2.4GHz with the single bus)                                                                                                                                |

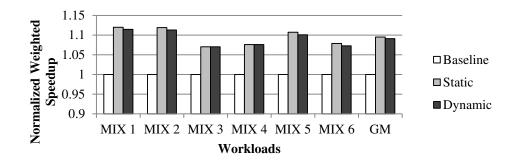

| Figure 2-17. The normalized weighted speedup of mixed workloads boosted by Static Switching and Dynamic Switching                                                                                                                                                                              |

| Figure 2-18. The improved throughput of Dynamic Switching boosted by a stride prefetchers (degree = 1, 2, 4) for mixed workloads                                                                                                                                                               |

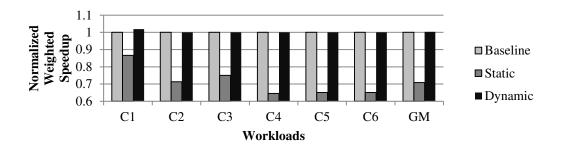

| Figure 2-19. The normalized weighted speedup of Compute-Intensive workloads with Static Switching and Dynamic Switching                                                                                                                                                                        |

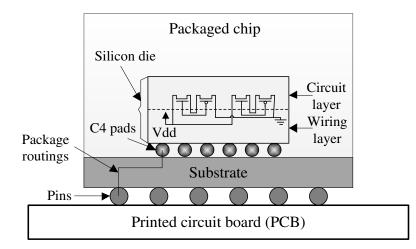

| Figure 3-1. Structure of a packaged chip (8 copies of DEALII from SPEC2006)                                                                                                                                                                                                                    |

| Figure 3-2. Design overview on the proposed scheme                                                                                                                                                                                                                                             |

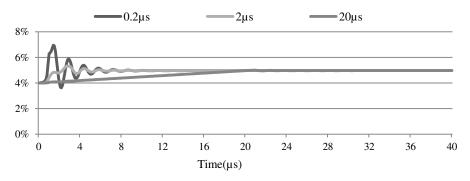

| Figure 3-3. Dynamic simulation                                                                                                                                                                                                                                                                 |

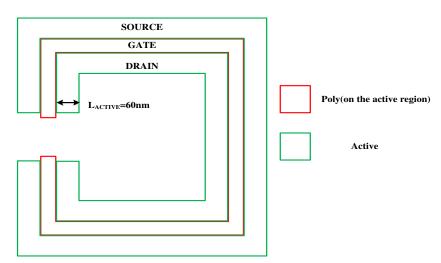

| Figure 3-4. Layout of wrapped around large transistor                                                                                                                                                                                                                                          |

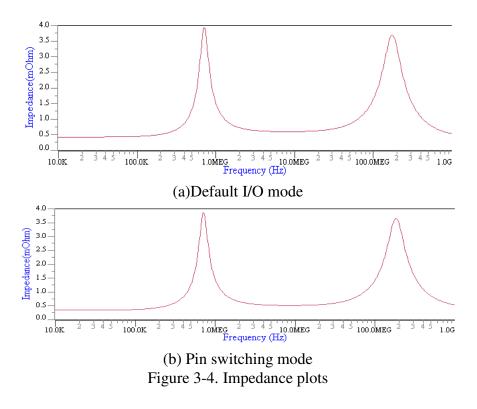

| Figure 3-5. Impedance plots                                                                                                                                                                                                                                                                    |

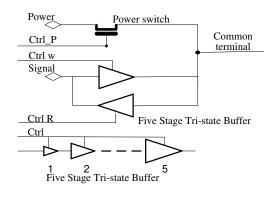

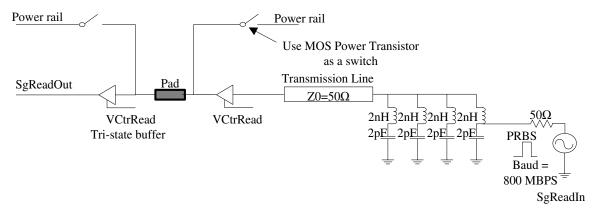

| Figure 3-6. Circuits when a switchable pin is used for signal transmission                                                                                                                                                                                                                     |

| Figure 3-7. Received eye diagram                                                                                                                                                                                                                                                               |

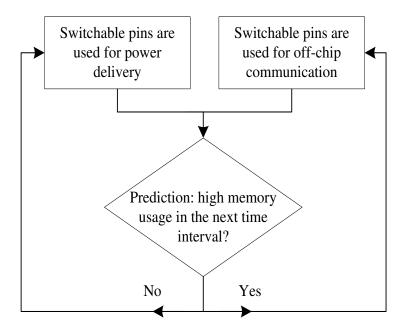

| Figure 3-8. Workflow of dynamic switching                                                                                                                                                                                                                                                      |

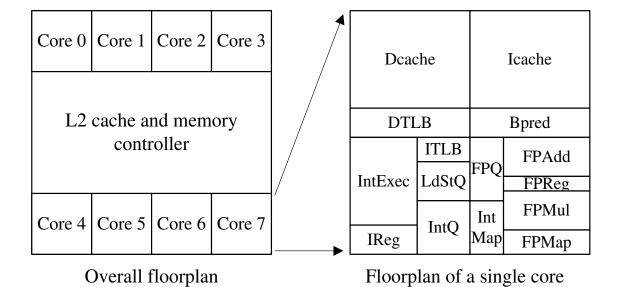

| Figure 3-9. Floorplan of the chip multiprocessor                                                                                                                                                                                                                                               |

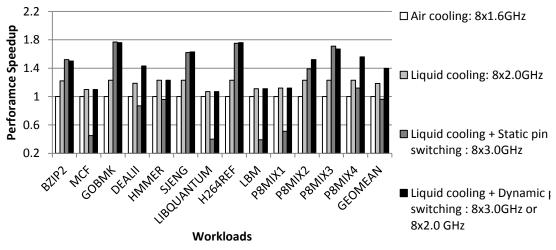

| Figure 3-10. Performance speedup when the processor is in dim silicon mode                                                                                                                                                                                                                     |

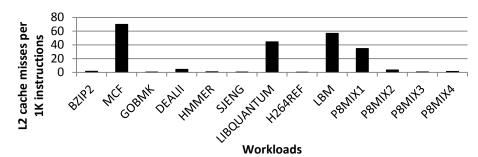

| Figure 3-11. Number of L2 cache misses per 1K instructions on a processor configured to 8×2.0GHz (liquid coiling)                                                                                                                                                                              |

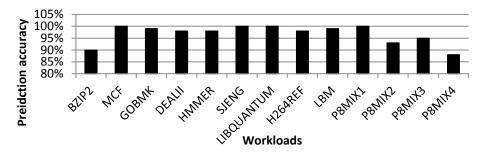

| Figure 3-12. Prediction accuracy on a processor in dim silicon mode                                                                                                                                                                                                                            |

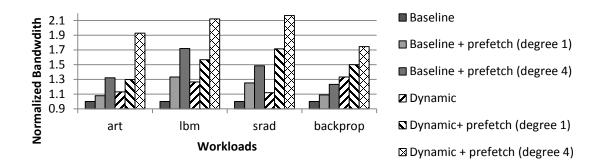

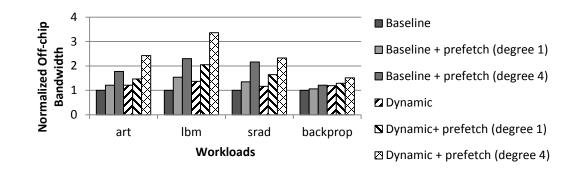

| Figure 4-1. Performance evaluation of multi-threaded workloads with Dynamic Switching and prefetching (degree = 1, 4)                                                                                                                                                                          |

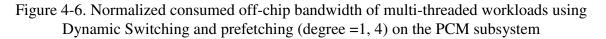

| Figure 4-2. Normalized consumption of off-chip bandwidth of multi-threaded workloads using Dynamic Switching and prefetching (degree = 1, 4)                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

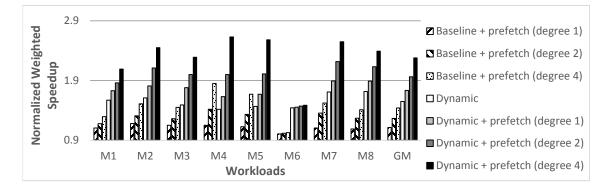

| Figure 4-3. Improved throughput of Dynamic Switching boosted by stride prefetchers (degree = 1, 2, 4) for memory-Intensive workloads using PCM                             |

| Figure 4-4. Normalized off-chip bandwidth of Dynamic Switching boosted by stride prefetchers (degree = 1, 2, 4) for memory-Intensive workloads using PCM                   |

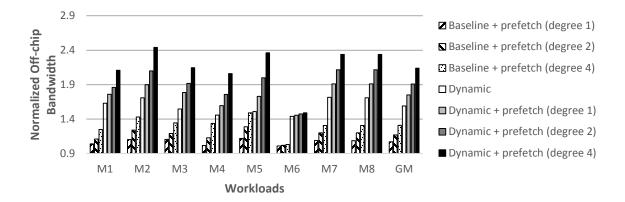

| Figure 4-5. Performance evaluation of multi-threaded workloads using Dynamic Switching and prefetching (degree=1, 4) on the PCM subsystem                                  |

| Figure 4-6. Normalized consumed off-chip bandwidth of multi-threaded workloads using Dynamic Switching and prefetching (degree =1, 4) on the PCM subsystem                 |

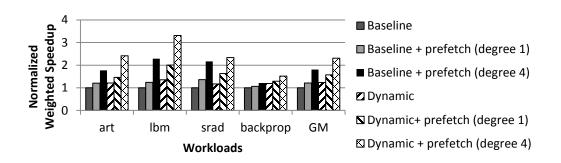

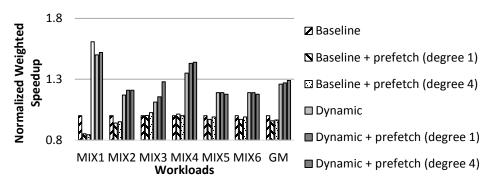

| Figure 4-7. The improved throughput of Dynamic Switching boosted by stride prefetchers (degree = 1, 4) for mixed workloads with PCM                                        |

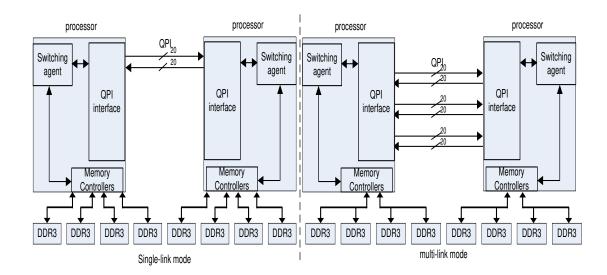

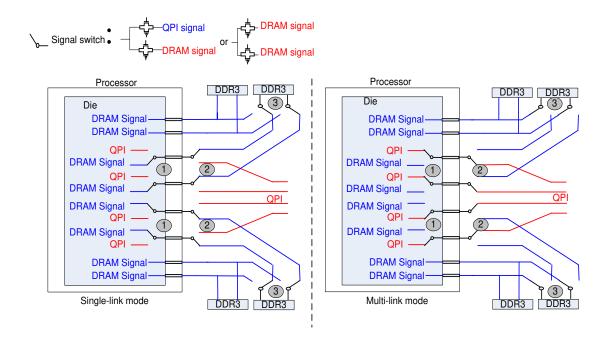

| Figure 5-1. The simulated system running in the single-link mode and the multi-link mode                                                                                   |

| Figure 5-2. The off-chip bus connection in the single-link mode and the multi-link mode                                                                                    |

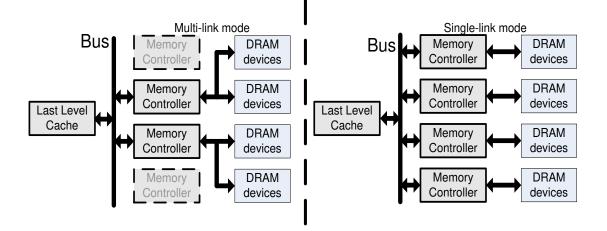

| Figure 5-3. The memory controller running in the single-link mode and the multi-link mode                                                                                  |

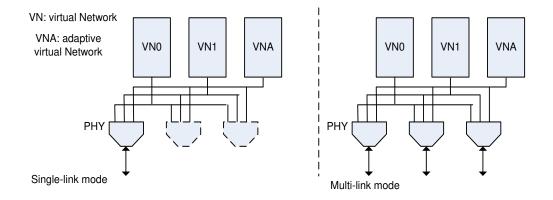

| Figure 5-4. The physical layers of QPI running in the single-link mode and the multi-link mode77                                                                           |

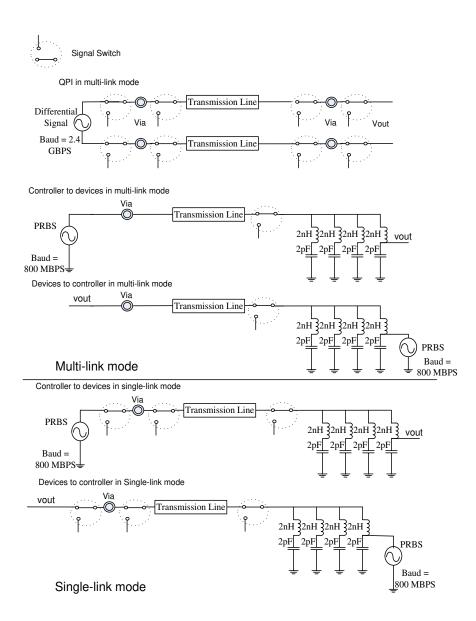

| Figure 5-5. The Spice models for QPI buses and memory buses in single-link mode and the multi-link mode                                                                    |

| Figure 5-6. Eye diagrams                                                                                                                                                   |

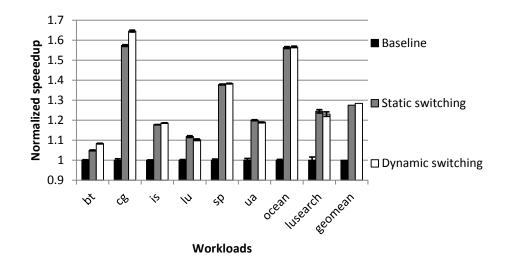

| Figure 5-7. The normalized speedup of the static switching and the dynamic switching compared with the baseline                                                            |

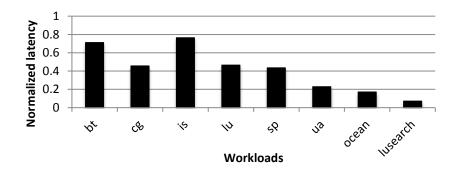

| Figure 5-8. The latency of un-core requests for the static switching normalized against that of the baseline                                                               |

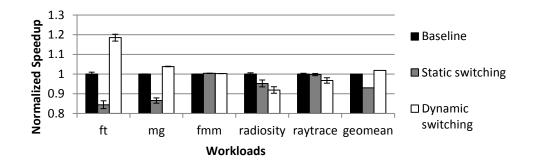

| Figure 5-9. The normalized speedup of the static switching and the dynamic switching compared with baseline for the workloads with moderate or low inter-socket traffic 90 |

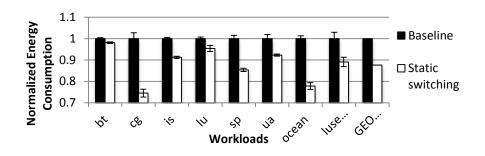

| Figure 5-10. The energy consumption in the static switching normalized against the baseline                                                                                |

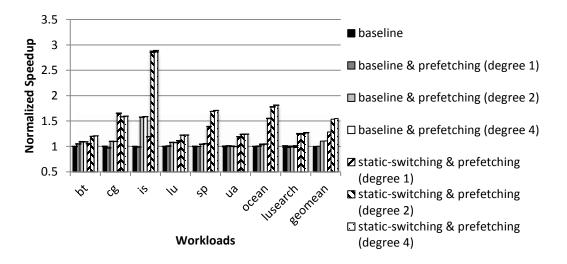

| Figure 5-11. The normalized speedup of the static switching with a prefetcher (degree 1, 2, 4) compared with baseline and the prefetcher                                   |

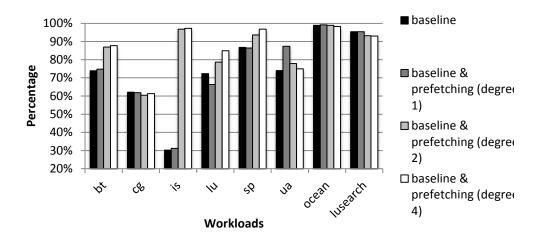

| Figure 5-12. The ratio between the un-core latencies of QPI and the total un-core latencies with the baseline and a prefetcher (degree 1, 2, 4)          | 92 |

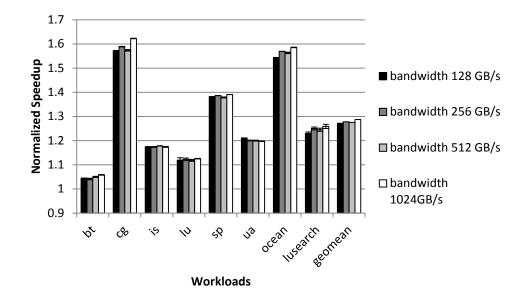

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

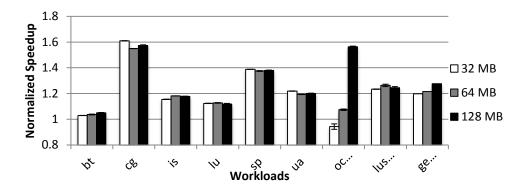

| Figure 5-13. The normalized speedup of the static switching with the different bandwidths of DRAM cache                                                  | 93 |

| Figure 5-14. The normalized speedup of the static switching with the different sizes of DRAM cache                                                       |    |

| Figure 5-15. The normalized latencies of un-core requests in the static switching with different sizes of DRAM cache                                     |    |

| Figure 5-16. The normalized speedup of the static switching with the different frequencies of QPI                                                        | 95 |

| Figure 5-17. The ratio between the un-core latencies of QPI and the total un-core latencies with the baseline and the different frequencies of OPI buses | 96 |

#### ABSTRACT

Off-chip memory bandwidth has been considered as one of the major limiting factors to processor performance, especially for multi-cores and many-cores. Conventional processor design allocates a large portion of off-chip pins to deliver power, leaving a small number of pins for processor signal communication. We observed that the processor requires much less power than that can be supplied during memory intensive stages in some cases. In this work, we propose a dynamic pin switch technique to alleviate the bandwidth limitation issue. The technique is introduced to dynamically exploit the surplus pins for power delivery in the memory intensive phases and uses them to provide extra bandwidth for the program executions, thus significantly boosting the performance. We also explore its performance benefit in the era of Phase-change memory (PCM) and prove that the technique can be applied beyond DRAM-based memory systems.

On the other hand, the end of Dennard Scaling has led to a large amount of inactive or significantly under-clocked transistors on modern chip multi-processors in order to comply with the power budget and prevent the processors from overheating. This so-called "dark silicon" is one of the most critical constraints that will hinder the scaling with Moore's Law in the future. While advanced cooling techniques, such as liquid cooling, can effectively decrease the chip temperature and alleviate the power constraints; the peak performance, determined by the maximum number of transistors which are allowed to switch simultaneously, is still confined by the amount of power pins on the chip package. In this paper, we propose a novel mechanism to power up the dark silicon by dynamically switching a portion of I/O pins to power pins when off-chip

communications are less frequent. By enabling extra cores or increasing processor frequency, the proposed strategy can significantly boost performance compared with traditional designs.

Using the switchable pins can increase inter-socket bandwidth as one of performance bottlenecks. Multi-socket computer systems are popular in workstations and servers. However, they suffer from the relatively low bandwidth of inter-socket communication especially for massive parallel workloads that generates many inter-socket requests for synchronizations and remote memory accesses. The inter-socket traffic poses a huge pressure on the underlying networks fully connecting all processors with the limited bandwidth that is confined by pin resources. Given the constraint, we propose to dynamically increase the inter-socket bandwidth, trading off with lower off-chip memory bandwidth when the systems have heavy inter-socket communication but few off-chip memory accesses. The design increases the physical bandwidth of inter-socket communication via switching the function of pins from off-chip memory accesses to inter-socket communication.

### **CHAPTER 1. INTRODUCTION**

#### **1.1. MOTIVATIONS**

As memory-intensive applications such as web servers, database software, and tools for data analysis prevail, the focus of computer architects shifts from Instruction Level Parallelism (ILP) to Memory Level Parallelism (MLP). The term "Memory Wall" was coined to describe the disparity between the rate of core performance improvement and the relatively stagnant rate of off-chip memory bandwidth increase. Additional cores, when integrated on the same die, and supplemental applications serve to widen this gap, since each individual core may generate substantial memory requests that need to be queued and served by the memory subsystem. Obviously, the capability of the off-chip memory system largely determines the per-core or even the overall performance of the entire system. In scenarios where the off-chip memory is insufficiently fast to handle all memory transactions in a timely manner, the system performance is highly likely to be bottlenecked by the slow memory accesses. An intuitive solution to this problem is to increase the off-chip memory bandwidth by enabling more memory channels. Figure 1-1 illustrates the variation of normalized throughput with the number of memory channels increased from 1 to 4 when 4 lbm programs are running on an X86 platform. As can be seen from the figure, enabling more memory channels significantly increases the off-chip bandwidth, which in turn translates to an impressive boost of the system performance. Furthermore, compared to compute-intensive stages, processors consume much less power during memory-intensive phases when cores wait for data to be fetched from main memory.

Figure 1-1. Normalized weighted speedup and off-chip bandwidth of 4 lbm co-running on a processor with 1,2,3,4 memory channels

Motivated by this observation, we propose an innovative technique to mitigate the shortage of off-chip bandwidth during the memory-intensive phases of program executions, in order to enhance the overall performance. Our scheme is built on top of a novel switchable pin design and accurate identifications of memory-intensive phases. Pins can be dynamically altered for power delivery or signal transmission via accessory circuits. These circuits enable pins to deliver quality power or signal with relatively low area overhead. On the other hand, we identify the memory-intensive phases by observing the key performance metrics at runtime. Extra off-chip bandwidth is demanding in phases with high memory intensity. Therefore, by switching the pins and providing additional bandwidth for off-chip memory transactions, the performance of memory-intensive stages can be boosted, thus impressively accelerating the overall execution.

On the other hand, "dark silicon" can be mitigated via the switchable pins. In the current industry, there are two commonly accepted reasons for power constraints that cause dark silicon: thermal constraints and power delivery [41]. The slow improvement of per-transistor switch energy along with the fast growing transistor density has led to a considerable rise in the power consumption per unit area (i.e., power density). Provided that inexpensive cooling techniques such as air cooling are still the mainstream solution

to heat dissipation for desktop and mobile platforms, such increasing of the power density tends to generate substantial heat that outstrips the chip's heat spreading capability. In this situation, the maximum power consumption of the chip cannot go beyond a threshold in order to maintain a safe working temperature for the entire processor. This power limit is usually referred to as the thermal design power (TDP). Some high-end processors with a higher TDP use backplate liquid cooling [33] to avoid thermal issues.

The underlying power delivery system, on the other hand, constrains the amount or the frequency of simultaneously active transistors as it determines the maximum power that is able to be provided to the chip irrespective of the thermal concern. To alleviate this constraint, we consider increasing the power envelope with minimum circuit change to the existing computer systems, in order to enable more transistors or raise the operating frequency in the power-hungry phases during program execution. Figure 1-2 plots a snapshot of the execution of 8 copies of DEALII from SPEC2006 on an 8-core processor, visualizing a representative scenario that motivates our work. The off-chip memory traffic and processor power consumption both vary in different execution phases. More interestingly, the two traces generally show an opposite trend during the execution; when the memory traffic is relatively light, the total power consumption is quite considerable

Figure 1-2. Power and memory bandwidth (8 copies of DEALII from SPEC2006)

(e.g., time interval 106 – 151ms). On the other hand, a duration of memory-intensive execution will correspond to a low-power period. The underlying reason for this phenomenon is that frequent misses in the last-level cache and the resultant off-chip memory accesses will largely slow down the overall execution rate, leading to a decrease in the processor's power consumption.

This intuitive observation implies an important opportunity for performance improvement and dark silicon mitigation by appropriately balancing the power delivery and off-chip traffic. To exploit this potential benefit, we propose a novel mechanism to dynamically switch a portion of I/O pins for extra power delivery when off-chip memory accesses are infrequent, thus powering up the dark silicon for performance boost. During a phase when off-chip activities are relatively high, we switch back the pins for signal transmission.

Pin Switching provides a great opportunity for increasing the off-chip bandwidth of CPUs using Phase-change memory (PCM). As DRAM is experiencing difficulties with memory technology scaling, architects are intensively studying potential alternative memory technologies such as PCM. Although PCM exhibits different features from DRAM, Pin Switching is expected to also improve the performance of PCM subsystems. This work investigates the potential benefit of Pin Switching in the era of PCM.

Pin Switching also provides an opportunity for increasing the inter-socket bandwidth as one of performance bottlenecks. Multi-socket systems are widely used to boost the throughput of massive parallel workloads that generate intensive local traffic, between processors and off-chip memory devices such as DRAM, and remote traffic for inter-socket communication. The limited local bandwidth of main memory bounds the performance of parallel workloads, since it serializes the parallel memory requests and offsets the benefit of memory level parallelism, especially considering the everincreasing data size of workloads and number of cores per die. This problem is addressed by many architects by boosting the system throughput via advanced algorithms for offchip memory requests [11], increasing the physical memory bandwidth at the cost of lower core frequency [6], or reducing traffic via using a stacked DRAM, which has higher bandwidth than off-chip memory devices and a larger size than a SRAM-based cache [18]. These solutions relieve the performance bottleneck, while remote inter-socket bandwidth emerges as a new performance bottleneck for workloads with intensive inter-socket communication.

Remote bandwidth bounds the performance of workloads that frequently fetch data from the cache of other processors or remotely from main memory. Inadequate remote bandwidth serializes memory requests and limits the benefits of memory level parallelism. The bottleneck of inter-socket communications such as QuickPath Interconnect (QPI) [20] was hidden, as remote main memory access is constrained by offchip bandwidth, but is now revealed by the volume of requests directly to the DRAM

Figure 1-3. The latency breakdown of un-core requests in the simulated system with two sockets

cache that do not use off chip bandwidth. The QPI bandwidth becomes a greater concern than off chip bandwidth when data is more likely to be fetched from stacked DRAM, which has superior bandwidth compared to the remote bandwidth. This bottleneck is shown in Figure 1-3 that breaks down the latencies of un-core requests.

qSwitch, which dynamically allocates off-chip bandwidth between local and remote accesses, is proposed to relieve the bottleneck constraining remote accesses. The total number of pins bound the bandwidth as a scarce resource [24] that power delivery networks and I/O compete for. Additionally, increasing the total number of signal pins is prohibitive since routing traces beneath processors is becoming very difficult. qSwitch dynamically shifts a portion of local off-chip bandwidth for accessing main memory into remote inter-socket communication bandwidth when low local access activities are observed without increasing the total number of signal pins. qSwitch improves the performance of workloads suffering from limited inter-socket bandwidth, based on a vertical design from the circuit to architecture level.

#### **1.2. DISSERTATION ORGANIZATION**

The dissertation first presents a pin switch technique to increase off-chip bandwidth based on switchable pins. It demonstrates applying the switchable pins to mitigate dark silicon by boosting core frequency. Additionally, it explores the benefit of the pin switch technique in the era of PCM with multi-threaded workloads. Based on the underlying idea of the pin switch technique, it proposes another pin switch technique to increase inter-socket bandwidth. In general, the main contributions of this work are summarized as follows:

- We propose a switchable pin design which can convert a power pin to a signal ٠ pin or the other way around for increasing off-chip bandwidth. Detailed examinations at both the circuit and architectural level are conducted to validate the feasibility of the proposed design. We examine the performance improvement of the design in various memory configurations. A sensitivity study is conducted to compare the benefit of our design with a different number of channels, buses, banks and ranks. We design Dynamic Switching to alleviate the negative side-effects of pin switching by actively identifying memory-intensive phases and only switching when the condition is satisfied. Without prior knowledge of program characteristics, this policy switches the system to prioritize memory bandwidth or core performance according to the identified phase. Our experiments show that significant performance improvement can be achieved for memory-intensive workloads while maintaining the same performance for compute-intensive workloads as the system without Pin Switching.

- We give a circuit implementation for mitigating dark silicon, using minor changes to existing processor and motherboard circuitry. We further design a rigorous statistical model that correlates the historical execution behaviors and off-chip access intensities in upcoming intervals. The established model can be employed by the operating system or equivalent supervisor to guide pin switching at runtime. We conduct a series of simulations to evaluate the performance, energy efficiency, and thermal impact of the proposed design on a chip multi-processor (CMP) in the dim silicon [81].

- We integrate a PCM model into our simulations to evaluate the benefits of Pin Switching in the era of PCM. Pin Switching significantly improves the performance of the PCM memory subsystem in our evaluation. We also show that multi-threaded workloads can benefit from Pin switching as long as they share the performance bottleneck of off-chip bandwidth.

- We identify that the latency of inter-socket communication as the major bottleneck for massive parallel workloads that intensively share data across sockets. We propose qSwitch for improving the performance of the workloads on a multi-socket system in which switching agents turn on/off memory channels, QPI buses, and off-chip bus connections. We evaluate the performance of qSwitch with the selected multi-thread workloads. We also investigate the runtime overhead and signal integrity for qSwitch.

The remainder of the dissertation is organized as follows. We present the design which increase off-chip bandwidth via switchable pins in chapter 2, and the design which mitigate dark silicon in chapter 3. We propose boosting off-chip bandwidth with PCM and improve the performance of multi-threaded programs in chapter 4. Finally, we propose increasing inter-socket bandwidth via switchable pins in chapter 5.

### CHAPTER 2. INCREASING OFF-CHIP BANDWIDTH IN MULTI-CORE PROCESSORS WITH SWITCHABLE PINS

#### 2.1. DESIGN OVERVIEW

Our design aims to boost computer system performance especially for memoryintensive programs. In conventional designs, the performances of these workloads are degraded by a shortage of memory buses which limits off-chip bandwidth. We provide increased memory bandwidth, thereby reducing the average latency of off-chip memory access, at the expense of a lower core frequency. Rather than retaining a fixed number of buses connected to the DRAM (typically one bus per channel), our design dynamically switches buses between signal and power pins (VDD or GND) to reduce the latency for these workloads. This is referred to as multi-bus mode henceforth, as opposed to singlebus mode similar to conventional processor operation. Switchable pins facilitate changing between these two modes as discussed below. This paper focuses on how to fully exploit the benefits of substituting power pins for I/O pins during memory-intensive programs without interfering with compute-intensive programs.

#### 2.1.1 Pin Switch

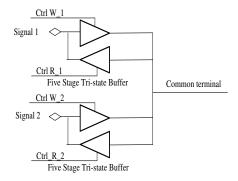

Figure 2-1 depicts the schematic of two switches and a signal buffer which serve as the basic units for exchanging power pins for signal pins. The signal-to-power switch shown in

Figure 2-1 (a) is key to alternate a regular pin between the two modes. As illustrated in this figure, we utilize a dedicated power switch [59] which sits on the power delivery path to minimize the corresponding IR drop and power consumption with its

(a) The circuit of a signal-to-power switch

(b) The circuit of a signal switch

(c) The circuit of a signal buffer

Figure 2-1. The circuit of pin switch

ultra-low switch-on resistance, measuring as low as  $1.8m\Omega$ . While in the single-bus mode, the power switch is turned on while two 5 stage tri-state buffers on the signal line are off. Otherwise, the power switch is turned off to block noisy interference from the power line, and the tri-state buffers are turned on in one direction according to whether data is read from the memory or written by the memory controller. To compensate for the parasitic capacitances of the power switch, we place the 5 stage tri-state buffers in signal lines to amplify I/O signals. Between each stage, the buffer size is increased by four times to amplify the signal with small delay. In total, the 5 stage tri-state buffer incurs a 0.9ns delay. On the other hand, the die area of the aforementioned power switch is commensurate to that of 3,000 traditional transistors [59]. The number of signal pins for a DRAM bus could slightly vary depending on different processors (e.g. with or without ECC). We pick up 125 power switches per bus which consists of 64 data pins and 61 address and command pins from the pin allocation of an i5-4670 Intel Processor [7]. The total die area consumes 375,000 (3,000 \* 125) traditional transistors. Considering a billion-transistor chip, the area overhead for the 3 buses which will be used in our work is less than 0.12% of the total chip area.

The signal switch shown in Figure 2-1 (b) is employed to guarantee that data in the DRAM can be accessed in two modes. The signal switch uses two pairs of 5 stage tristate buffers to enable memory devices that can be accessed via two buses. The buffers identical to that in the signal-to-power switch can resist noise from a channel when the other channel is selected. On the other hand, the signal buffers shown in Figure 2-1 (c) also have strong peak-drive current and sink capabilities. They are utilized to amplify the signal in order to offset the effect of the parasitic capacitance.

Processors possess specific pin allocations depending on the package, power consumption, and hardware interface (the number of memory channels). For our experiment, we use the pin allocation of an i5-4670 Intel Processor [7] shown in Table 2-1. While this processor includes 4 cores and 2 memory channels, 54.6% of the pins are used for power delivery. Out of the 628 power pins, 125 of these can be replaced with switchable pins for a single bus. To maintain the same ratio of VDD to GND pins, we

allocate 30 of the 125 switchable pins as VDD pins and the remaining 95 as GND pins. In our experiment we will allocate at most three additional buses via pin switching because adding more leads to a considerable drop in performance.

#### 2.1.2 Off-Chip Bus Connection

Designing a memory interface which could take the advantage of the switchable pins to dynamically increase off-chip bandwidth is non-trivial. In this section, we propose an off-chip bus connection and instructions to configure the switchable pins for power delivery or for signal transmission.

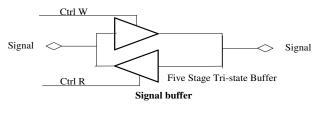

The two modes of the off-chip bus connection could be described as the multi-bus mode and the single-bus mode, as shown in Figure 2-2. In multi-bus mode, several buses (assuming N) are connected to private DRAM interfaces via the individual buses. On the other hand, single-bus mode can only access DRAM by a single bus. Two signal-to-power switches and a signal switch for each signal wire of N-1 buses are needed. These signal-to-power switches configure the switchable pins for signal transmission where the signal switches connect the bus to DRAM devices in the multi-bus mode, otherwise the switchable pin is configured for power delivery where the DRAM devices are connected to the shared bus.

In order to implement the mechanism, we control the signal-to-power switch detailed in Figure 2-1 (a) and the signal switch detailed in Figure 2-1 (b) to route signal and power in the two modes. The signal to the DRAM interface could be divided into two groups: command signals and data signals. The command signals running in one direction could be routed via the two switches which only need one direction buffer

instead of a pair. On the other hand, the data signals (DQ) are bi-directional and the switches shown in Figure 2-2 could receive and send signals in both directions.

For the placements of the switches on the printed circuit board (PCB), one signalto-power switch for each signal line should be placed close to the processor package in

Figure 2-2. The overview of the hardware design of off-chip bus connection for switching between the Multi-bus mode and the Single-bus mode

| $V_{DD}$ | GND | DDR3 | Others | Total |

|----------|-----|------|--------|-------|

| 153      | 475 | 250  | 272    | 1150  |

Table 2-1. Pin allocation of an Intel Processor i5-4670

order to shorten the signal wire which has to bear high current for power delivery. To avoid signal reflections caused by an impedance mismatch, we keep the width of the signal wires and conduct an experiment to test the feasibility of high current via these signal wires. Based on a specification from the PCB manufacturer [9] and the DDR3 PCB layout guidelines [8], our simulation with COMSOL shows the MTTF of the 6mil signal wire could be more than 2.5 x 105 hours with a 1A current. On the other hand, the signal switch should be placed near the corresponding DRAM device to reduce signal reflections.

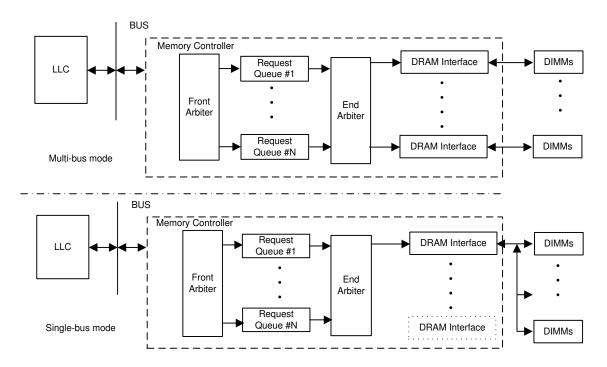

#### 2.1.3 Memory Controller

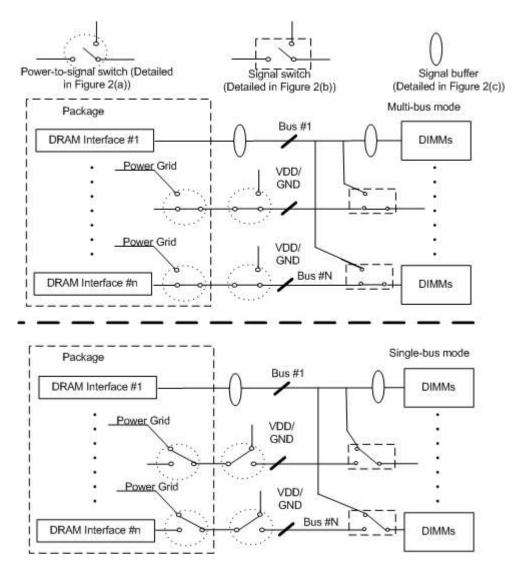

The data availability of the memory controller is our primary concern. All the available memory buses in the multi-bus mode must be fully utilized to achieve maximum bandwidth while still allowing all the data in single-bus mode to be accessed. Due to the complicated synchronization of memory requests between memory controllers, the switch between the two bus modes is only implemented inside the memory controller. Within a memory controller, a memory interface is designed for each bus to fully exploit the benefit of the multi-bus mode without the interference of traffic from other buses compared to the design of multiple buses sharing a single memory interface.

The memory controller in our design includes dedicated request queues which buffer the incoming requests to the buses shown in Figure 2-3. Queues individually receive the requests from the front arbiter which employs its address mapping policy when dispatching requests. Once the requests are residing in the queues, they are fetched by the back arbiter. While in multi-bus mode, the requests are fed into their corresponding buses via the corresponding DRAM interfaces. Because memory interfaces can operate independently and in parallel, the memory bandwidth can be amplified by a factor of the number of memory buses. In the single-bus mode, the memory controller works similar to a conventional processor and communicates with the attached DIMMs as appended ranks.

#### 2.1.4 Area Overhead

The circuit overhead of our design consists of the front arbiter, the end arbiter, and extra DRAM interfaces. As a result of both arbiters, the cost of dispatching requests without buffering them should be negligible. Furthermore, the cost of the additional DRAM interface is inexpensive. The estimated net area of a typical DRAM interface from Opencore [1] is 5,134  $\mu$ m2 in 45 nm technology. This estimation is conducted by the Encounter RTL Compiler [5] with the NanGate Open Cell Library [6]. No more than

Figure 2-3. The Overview of the hardware design of memory controller for switching between the Multi-bus mode and the Single-bus mode

three additional buses in total are used in our experiment thus creating a maximum hardware overhead less than 0.00015 cm2 which is significantly less than the typical 1 cm2 die area.

#### 2.1.5 Address Mapping

Data accesses interleave at the page level via different buses exploiting the benefit of memory-level parallelism while maintaining a high row buffer hit ratio. Interleaving at the block level considerably decreases the row buffer hit ratio resulting in longer off-chip latency per request and extended queue delay. To reduce row-buffer conflicts, we employ XOR banking indexing which could effectively reduce bank conflicts resulting from resource-contention-induced traffic and write-backs. This permutation distributes the blocks stored in the last level cache into different banks as opposed to possibly including tags of physical addresses containing the same bank index.

#### 2.1.6 Signal Integrity

Signal integrity is analyzed to demonstrate feasibility in the single-bus and the multi-bus modes. We simulate SPICE models of our accessory circuit as well as PCB transmission lines, bond wire inductance, and driver capacitance associated with the device package in the AMS packages of Mentor Graphic as shown in Figure 2-4. The parameters are derived from previous works [58][62]. Signal integrity challenges are alleviated since the DDR3 command signal is unidirectional and its speed is no more than that of the data signals [58]. In this study, we only analyze the effect of our accessory circuit on the data signals which could be viewed as the worst case for all the signals.

In Figure 2-5 (a-d), the eye patterns of writing data (controller to device) and reading data (device to controller) in the two modes are derived from the corresponding SPICE models in Figure 2-4 (a-d) respectively. They have clear eyes since the signal-to-power switch alleviates the effect of the parasitic capacitance of the power switches. Furthermore, the signal switches as well as signal buffers alleviate the signal reflections caused by discontinuities. Thus, the results indicate our accessory circuit could maintain the signal quality in the two modes.

Figure 2-4. Spice models for signal integrity simulation

(a) DQ Read in multi-bus mode (Device to Controller)

(b) DQ Write in multi-bus mode (Controller to Device)

(c) DQ Read in single-bus mode (Device to Controller)

(d) DQ write in single bus mode (Controller to Device)

Figure 2-5. The eye diagrams

### 2.1.7 Power Delivery Simulation

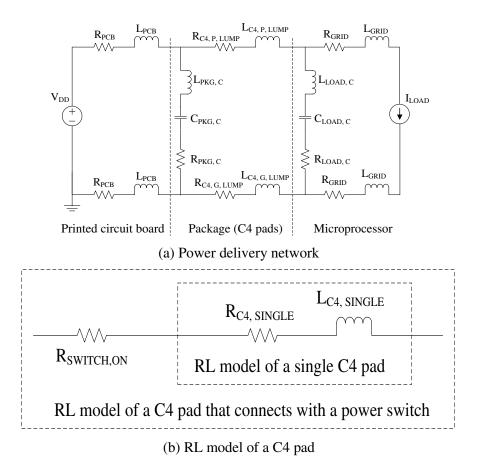

In this section, we assess the repercussions experienced by the power delivery network (PDN) when the switchable pins are shifted from single-bus mode to multi-bus mode. The PDN is depicted in Figure 2-6 (a). The power delivery path is modeled with RL components (i.e. resistors and inductors) connected in series across the PCB, the

package, and the silicon die. Decoupling capacitors are introduced between each individual PDN to control any voltage fluctuations. The on-chip power grids and processor circuits on the silicon die are modeled separately as RL components with an ideal current source.

Figure 2-6 (b) illustrates the RL model of the Controlled Collapse Chip Connection (C4) pads [31] in which the resistance of the on-state power switches is taken into consideration. Table 2-2 lists the parameter values obtained from prior work [45].

PDN simulations are performed in PSPICE to evaluate the impact of Pin Switching. Due to resistance along the power delivery path, an IR drop exists between the supply voltage and load voltage as current flows through the PDN. We assume a normalized IR drop should be upper-bounded by 5% as prior work dictates [52][56]. This implies that the maximum currents are 125A, 104A, 80A, and 56A for the baseline and then for Pin Switching mechanisms with one, two, and four borrowed buses respectively. In other words, the three Pin Switching diagrams switch 125, 250, and 375 power pins to signal pins providing 16.8%, 36.0%, and 55.2% less current with 19.9%, 39.8% and 59.7% less power pins respectively. The percentage of current decrease is less than that of

| Table 2-2. I ower network moder parameters |                         |                         |        |  |  |

|--------------------------------------------|-------------------------|-------------------------|--------|--|--|

| Resistance                                 | Value                   | Inductance              | Value  |  |  |

| R <sub>PCB</sub>                           | $0.015 \text{ m}\Omega$ | L <sub>PCB</sub>        | 0.1 nH |  |  |

| Rpkg, c                                    | 0.2 mΩ                  | L <sub>PKG,C</sub>      | 1 pH   |  |  |

| RLOAD,C                                    | 0.4 mΩ                  | Lload,c                 | 1 fH   |  |  |

| R <sub>GRID</sub>                          | 0.01 mΩ                 | L <sub>GRID</sub>       | 0.8 fH |  |  |

| R <sub>C4</sub> , single                   | 40 mΩ                   | L <sub>C4, SINGLE</sub> | 72 pH  |  |  |

| Rswitch,on                                 | 1.8 mΩ                  |                         |        |  |  |

| Capacitance                                |                         |                         |        |  |  |

| C <sub>PKG,C</sub>                         | 250 µF                  | C <sub>LOAD,C</sub>     | 500 nF |  |  |

Table 2-2. Power network model parameters

Figure 2-6. RLC power delivery model

proportional power pin quantity decrease because the IR drop depends on the resistance in the PCB and power grids.

We assume the processor employs a dynamic voltage and frequency scaling (DVFS) mechanism supporting 4 voltage and frequency operating points. The frequency can be scaled down from 4.0GHz to 1.2GHz. Correspondingly, the voltage will be decreased from 1.0V to 0.64V. According to McPAT [56], the baseline design can work at a frequency of 4.0GHz given the power delivery information. However, the processor frequency must be decreased individually to 3.2GHz, 2.4GHz, and 1.2GHz when the power pins for one, two, and three sets of memory channel pins are borrowed as I/O pins respectively. The results shown in Table 2-3 are used in the following evaluation.

| BUS             | 1   | 2    | 3    | 4    |

|-----------------|-----|------|------|------|

| Current (A)     | 125 | 104  | 80   | 56   |

| Voltage (V)     | 1   | 0.88 | 0.76 | 0.64 |

| Power (W)       | 125 | 92   | 61   | 36   |

| Frequency (GHz) | 4   | 3.2  | 2.4  | 1.2  |

Table 2-3. Processor power and frequency parameters for different number of buses

#### 2.1.8 Runtime Switch Conditions

Designing a predictor to choose the most beneficial mode for the next interval is non-trivial for multi-program workloads. Simply switching based on the amount of consumed off-chip bandwidth is not sophisticated enough to improve the overall performance of a system in which only some of the programs that suffer from long offchip access latency are likely to benefit from multi-bus mode. To identify intervals that will benefit from Pin Switching it is necessary to estimate both the performance change of each program and the overall benefit of switching for the following interval based on the current performance before a switching occurs. We introduce a metric called the switching benefit  $B_{ii}(T_c)$  to help identify the most beneficial mode for each 1 millisecond interval, where B<sub>ii</sub>(T<sub>c</sub>) represents the estimated reward for running the interval following time  $T_c$  in mode j instead of mode i. Based on the history of the switching benefit, we predict  $\tilde{B}_{ii}(T_c)$  as the switching benefit for the following interval using  $\tilde{B}_{ii}(T_c) =$  $\sum_{k=1}^N B_{ij}(T_c-k*T_{interval})$  , where  $B_{ij}(T_c-k*T_{interval})$  represents the switching benefits detailed in equation (1) and can be measured from the N intervals ago and N is the length of the history to consider which were carefully chosen to be 2 for our experiment. If the predicted switching benefit is negative, the system will stay in mode i, otherwise, it will switch to mode j.

The switching benefit is calculated using the following equation:

$$B_{ij}(T_c) = \sum_{k=1}^{p} (WS_{j,k}(T_c) - WS_{i,k}(T_c))$$

2-1

Where  $WS_{i,k}(T_c)$  and  $WS_{j,k}(T_c)$  stand for the estimated weighted speedups for program k at time  $T_c$  in mode i and mode j respectively, while p represents the number of simultaneously executing programs which is equal to 4 in our experiment. The weighted speedup of each program in mode i during the interval can be estimated based on the information derived from hardware counters and off-line profiling, since the system is running in mode i during the current interval. The weighted speedup is calculated as follows:

$$WS_{i,k}(T_c) = T_{alone,i,k}(T_c)/T_{shared,i,k}(T_c)$$

2-2

$$T_{alone,i,k}(T_c) = Committed Inst_{alone,k}(T_c)/(average IPS_{alone,k})$$

2-3

where  $T_{alone,i,k}(T_c)$  stands for the execution time of the same instructions running without interference from co-runners and  $T_{shared,i,k}(T_c)$  denotes the execution time of a fraction of program k running with others during the current interval which is equal to the length of an interval (1 millisecond). Furthermore, Committed Inst<sub>alone,i,k</sub>(T<sub>c</sub>) stands for the number of committed instructions during the interval following T<sub>c</sub> of program k, directly derived from a hardware counter since it should be identical to the number when program k shares the main memory system with others. Average IPS obtained from off-line profiling denotes the average number of executed Instructions Per Second (IPS) when program k running alone. These values are used to approximate  $T_{alone,i,k}(T_c)$  based on the assumption that the IPS of each program is relatively steady when it runs alone, since an accurate estimation of  $T_{alone,i,k}(T_c)$  is challenging [65]. The estimation of the weighted speedup of each program in currently unused mode j is more difficult compared to that in current mode i, since we can only estimate the performance of mode j according to the information collected in mode i. The weighted speedup is calculated as follows:

$$WS_{j,k}(T_c) = T_{alone,j,k}(T_c)/T_{shared,j,k}(T_c)$$

2-4

$$T_{\text{shared},j,k}(T_{\text{c}}) = T_{\text{on-core},j,k}(T_{\text{c}}) + T_{\text{off-core},j,k}(T_{\text{c}})$$

2-5

Where  $T_{alone,j,k}(T_c)$  is identical to  $T_{alone,i,k}(T_c)$  and  $T_{shared,j,k}(T_c)$  represents the execution time of program k running with others in mode j. It can be divided into two parts based on whether the execution times vary with core frequency:  $T_{on-core,j,k}(T_c)$  denotes the portion of the execution time spent inside the core which is inversely proportional to core frequency, while  $T_{off-core,j,k}(T_c)$  expresses the portion of execution time incurred by activity outside the core. We estimate  $T_{on-core,j,k}(T_c)$  based on the corresponding time  $T_{on-core,i,k}(T_c)$  in mode i using:

$$T_{on-core,j,k}(T_c) = T_{on-core,i,k}(T_c) * \frac{freq_{i,k}}{/freq_{j,k}}$$

2-6

Where  $\text{freq}_{i,k}$  and  $\text{freq}_{j,k}$  are the frequencies in mode i and mode j respectively. We estimate  $T_{\text{on-core},i,k}(T_c)$  with the same breakdown using

$$T_{on-core,i,k}(T_c) = T_{interval} - T_{off-core,i,k}(T_c)$$

2-7

$$T_{off-core,i,k}(T_c) = T_{LLC,i,k}(T_c) + T_{DRAM,i,k}(T_c)$$

2-8

where  $T_{LLC,i,k}(T_c)$  is the execution time incurred in the shared last level cache (LLC) in mode i, which is estimated using the number of the accesses to LLC, and  $T_{DRAM,i,k}(T_c)$ denotes the execution time incurred by activity in the DRAM controller in mode i.  $T_{DRAM,i,k}(T_c)$  is the cumulative time spent when there is at least one in-flight read requests in the DRAM controller, since it can avoid the overestimation due to the overlap of multiple in-flight read requests for single thread [68].

On the other hand,  $T_{off-core,j,k}(T_c)$  is mainly affected by the number of buses between different modes since the queue delay inside the DRAM controller is typically decreased as more off-chip buses are added. We calculate the time using:

$$T_{off-core,j,k}(T_c) = T_{off-core,i,k}(T_c) + T_{queue \ delay,j,k}(T_c) - T_{queue \ delay,i,k}(T_c)$$

2-9

$$T_{\text{queue delay},j,k}(T_{\text{c}}) = T_{\text{queue delay},i,k}(T_{\text{c}}) * \frac{N_{\text{request},j,k}(T_{\text{c}})}{N_{\text{request},i,k}(T_{\text{c}})} 2-10$$

where  $T_{queue \ delay,i,k}(T_c)$  and  $T_{queue \ delay,j,k}(T_c)$  denote the execution time incurred inside the queue of the DRAM controller in modes i and j respectively, while  $N_{request,i,k}(T_c)$  and  $N_{request,j,k}(T_c)$  stand for the average number of waiting requests per incoming read requests which have to wait until they have been completed in modes i and j.  $T_{queue \ delay,i,k}(T_c)$  can be estimated by the time when there is at least one read request in the queue of DRAM controller.  $T_{queue \ delay,j,k}(T_c)$  can be estimated by sampling the number of waiting requests in different modes

#### 2.1.9 Switching Overhead

Any runtime overhead incurred by switching comes from the DVFS and IR drop fluctuations caused by the pin switch. The overhead for DVFS is 20µs [57] and the time for the IR drop to re-stabilize is also bounded by 20µs according to our power delivery simulation. Because both of these delays overlap each other, the estimated total overhead is 20µs and is taken into consideration. Therefore, the penalty is 40µs when a phase is incorrectly identified. However, the overall switching overhead is still negligible since the average length of the identified phases shown is much longer than the overhead in our workloads. Since most programs only switch a few times during execution, nearly all the program phase transitions have been identified by the predictor.

# **2.2. EXPERIMENTAL SETUP**

To evaluate the benefit of our design, we simulate the x86 system documented in Table 2-4 using the Gem5 simulator [24]. We modify the DRAM model integrated in Gem5 to accurately simulate the proposed method. Throughout the experiments, multibus mode will utilize all available buses with the corresponding core frequency shown in Table 2-3. The buses are partially unutilized with a high core frequency between multibus and single-bus modes. We employ off-chip DVFS to maintain the same frequency on all 4 cores at any given time.

# 2.2.1 Performance and Energy Efficiency Metrics

We use weighted speedup [79] lists as follows to represent the throughput of our system shown in the following equation.

| Tuble 2 1. The Configuration of the simulated system |                                               |  |  |  |

|------------------------------------------------------|-----------------------------------------------|--|--|--|

| Processor                                            | 4 X86 OoO cores with issue width 4            |  |  |  |

| L1 I cache                                           | Private 32KB, 8 way, 64B cache line, 2 cycles |  |  |  |

| L1 D cache                                           | Private 32KB, 8 way, 64B cache line, 2 cycles |  |  |  |

| L2 Cache                                             | Shared 8MB, 8 way, 64B cache line, 20 cycles  |  |  |  |

| Memory controller                                    | FR-FCFS scheduling, open row policy           |  |  |  |

| Channel                                              | 1                                             |  |  |  |

| Bus per channel                                      | 2 /3/4 (additional buses 1/2/3)               |  |  |  |

| Rank per bus                                         | 2                                             |  |  |  |

| Bank per rank                                        | 8                                             |  |  |  |

| Bank                                                 | 8*8 DDR3-1600 chips from Micron datasheet[62] |  |  |  |

Table 2-4. The Configuration of the simulated system

Weighted Speedup =

$$\sum_{i=0}^{N-1} \frac{\frac{1}{T_i^{Shared}}}{\frac{1}{T_i^{Alone}}}$$

2-11

where  $T_i^{Shared}$  and  $T_i^{Alone}$  denote the execution time of a single program running alone and the execution time running with other programs respectively. Because the IPC is distorted by the frequency change from the employed DVFS, the execution time is used in place of it. We utilize Energy per Instruction (EPI) for the evaluation of energy efficiency. This metric can be obtained from dividing consumed energy by the number total number of instructions committed.

#### 2.2.2 Workloads

Various multi-program workloads consisting of SPEC 2006 benchmarks [76] are used for our evaluation. As listed in Table 2-5, the benchmarks are categorized into two separate groups based on their relative memory intensities: memory-intensive programs and compute-intensive programs. Each workload consists of four programs from one of these groups to represent a memory-intensive workload or compute-intensive workload accordingly. Memory-intensive workloads are used to demonstrate the benefit of multibus mode while the compute-intensive workloads demonstrate that there are negligible side-effects.

We select a simulated region of 200 million instructions for each benchmark based on their memory characteristics collected from Pin [10]. The simulation for a mixed workload does not end until the slowest program finishes its 200 million instructions. Faster programs continue running after committing the first 200 million instructions. Execution time of each program is collected after the program finishes its instructions.

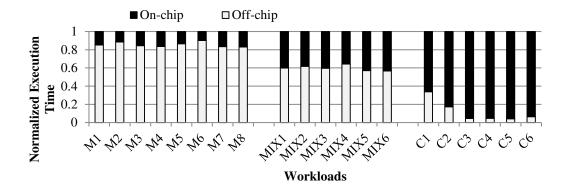

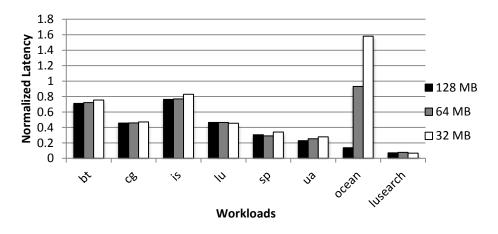

# 2.3. RESULTS

The execution latency of a program is composed of the on-chip and off-chip latency. The percentage of latency in the total execution time reveals which factor tends to be more influential to the overall performance of a workload. In Figure 2-7 we demonstrate the off- chip latency for memory-intensive workloads and on-chip latency for the compute-intensive workloads, since they are the main contributors to the execution latency of the two categories of workloads, respectively. Specifically, more than 80% of the latency of memory-intensive workloads comes from off-chip latency,

| workload                   |         | iory intensive | and compute-m |            |

|----------------------------|---------|----------------|---------------|------------|

| WOIKIOau                   | Men     | nory-intensive | programs      |            |

| M1                         |         | milc           | * *           | lihauantum |

|                            | lbm     |                | soplex        | libquantum |

| M2                         | lbm     | milc           | leslie3d      | libquantum |

| M3                         | lbm     | milc           | soplex        | leslie3d   |

| M4                         | lbm     | soplex         | libquantum    | leslie3d   |

| M5                         | milc    | soplex         | libquantum    | leslie3d   |

| M6                         | mcf     | mcf            | mcf           | mcf        |

| M7                         | mcf     | mcf            | astar         | astar      |

| M8                         | astar   | astar          | astar         | astar      |

| Mixed programs             |         |                |               |            |

| MIX1                       | lbm     | milc           | bzip2         | bzip2      |

| MIX2                       | lbm     | milc           | omnetpp       | omnetpp    |

| MIX3                       | lbm     | soplex         | omnetpp       | omnetpp    |

| MIX4                       | milc    | soplex         | omnetpp       | omnetpp    |

| MIX5                       | lbm     | milc           | omnetpp       | bzip2      |

| MIX6                       | milc    | soplex         | omnetpp       | bzip2      |

| Compute-intensive programs |         |                |               |            |

| C1                         | bzip2   | bzip2          | bzip2         | bzip2      |

| C2                         | hmmer   | hmmer          | hmmer         | hmmer      |

| C3                         | gromacs | bzip2          | omnetpp       | h264ref    |

| C4                         | gromacs | bzip2          | sjeng         | h264ref    |

| C5                         | gromacs | omnetpp        | sjeng         | h264ref    |

| C6                         | bzip2   | omnetpp        | sjeng         | h264ref    |

Table 2-5. The selected memory-intensive and compute-intensive workloads

while more than 60% of the latency of compute-intensive workloads is from on-chip latency. This implies that the memory-intensive workloads could be sped up by our Pin Switching, while the others are unlikely.

## 2.3.1 Memory-Intensive Workloads

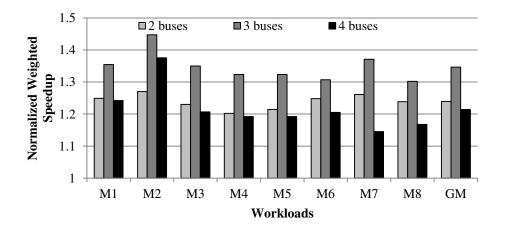

Figure 2-8 shows the performance improvements of memory-intensive workloads enhanced by 2, 3, and 4 buses. The weighted speedup of each case is normalized against its own baseline. The baseline is the simulated system fixed in the single-bus mode with

Figure 2-7. The normalized off-chip latencies and on-chip latencies of workloads against the total execution time

Figure 2-8. The normalized weighted speedup of memory-intensive workloads with 2, 3, and 4 buses against the each baseline

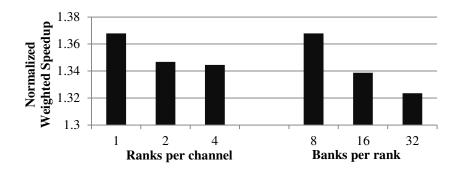

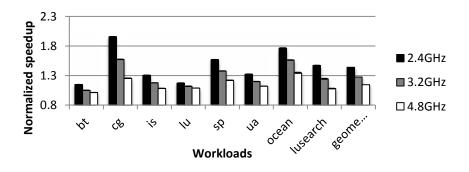

the corresponding number of buses and DRAM devices when the processor runs at 4.0GHz. Remarkably, the improvements experienced with 3 buses consistently surpass 2 and 4 buses in all workloads. These results stem from the balance between core performance and off-chip bandwidth that the 3 buses experience to maximize the throughput of the simulated system. Based on our specific hardware configuration and selected workloads, the multi-bus mode with 3 buses is the optimal choice and therefore referred to as the default configuration for the discussion of Static and Dynamic Switching that will be presented in later sections. Figure 2-9 illustrates the performance improvement for multi-bus mode tested using various DRAM configurations. The weighted speedup for each configuration is normalized against the same configuration in single-bus mode. As can be seen from the figure, all banks and ranks have weighted speedups greater than 32%. As the number of ranks per channel or the number of banks per rank increases, improvement is slightly diminished due to the resulting lower row buffer hit ratio causing shorter bank access latency.

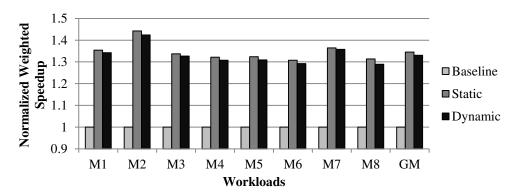

Figure 2-10 presents the benefits of Static Switching and Dynamic Switching with 3 buses versus the baseline of a simulated system that does not use the pin switch mechanism on memory-intensive workloads. Both schemes are able to speed up the execution of all workloads by more than 1.3 times, while an approximately 42% performance improvement is observed for M2. The geometric means of Static Switching and Dynamic Switching are respectively 1.34 and 1.33 due to more than 99% of the running time being identified as typical memory-intensive phases by Dynamic Switching.

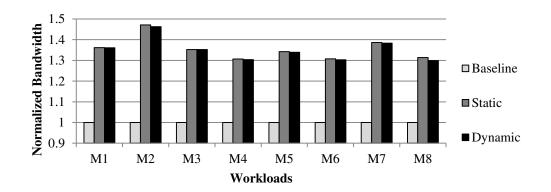

The benefit of the multi-bus mode is mainly attributed to the increase of consumed bandwidth as shown in Figure 2-11. The increase is similar to this of the

Figure 2-9. The average normalized weighted speedup of memory workloads in geometric mean with multi-bus mode. Each normalize to the same configuration with single bus mode

Figure 2-10. The normalized weighted speedup of memory intensive workloads boosted by Static Switching and Dynamic Switching with 3 buses against the baseline

weighted speedup in Figure 2-9. For example, M2 and M7 gain 47% and 39% off-chip bandwidth when switching from the single-bus mode to the multi-bus mode for static switching, while their performances are improved by 44% and 36% respectively. This similarity results from the fact that their execution latencies are largely dominated by off-chip latency. On the other hand, Dynamic Switching achieves a slightly smaller increase in bandwidth, which results in its performance being close to that of Static switching.

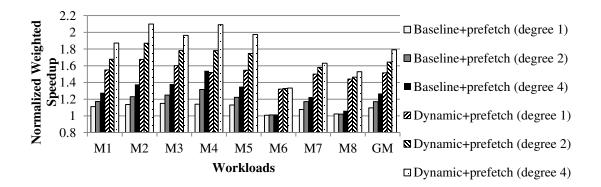

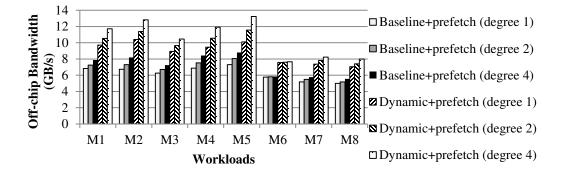

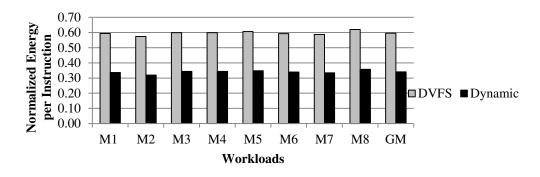

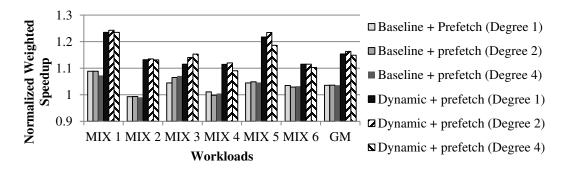

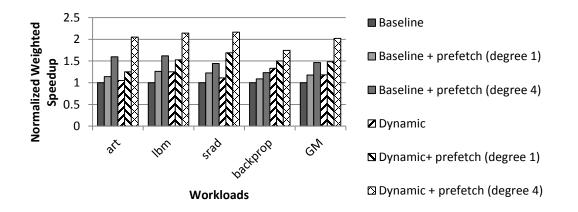

The throughput improvement of Dynamic Switching could be strengthened by using prefetchers which can utilize extra bandwidth brought by additional buses in our design. In our experiment, we use a stride prefetcher in the last level cache to demonstrate the benefit. More sophisticated prefetchers could be employed to further improve the system performance. The stride prefetcher used here has a prefetching degree of 1, 2, or 4, which denotes the number of prefetches issued on every memory reference. As illustrated in Figure 2-12, the geometric mean of the performance improvements of Dynamic Switching for all memory-intensive workloads with a prefetching degree of 1, 2, and 4 are 1.51, 1.64, and 1.79 respectively, compared with those of the baseline which are 1.10, 1.17, and 1.27. The gap of the improvements between Dynamic Switching and the baseline increases as the prefetch degree increases, which imply an aggressive stride prefetch could benefit more from Dynamic Switching.

Figure 2-11. The increased bandwidth due to pin switching. The normalized bandwidth of baseline, static pin switching, and dynamic pin switching

Figure 2-12. The improved throughput of Dynamic Switching boosted by a stride prefetchers (degree = 1, 2, 4) for memory-Intensive workloads

This observation could be demonstrated in all workloads except M6 which only gains a slight performance improvement from increasing the prefetch degree, since the stride prefetcher has a low coverage on mcf [42]. This performance improvement could be verified by the higher consumed off-chip bandwidth of Dynamic Switching shown in Figure 2-13. It implies that Dynamic Switching could boost the performance of the prefetch by providing more off-chip bandwidth.

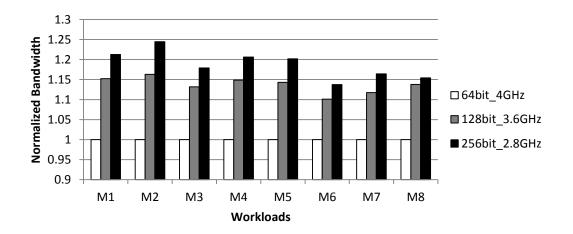

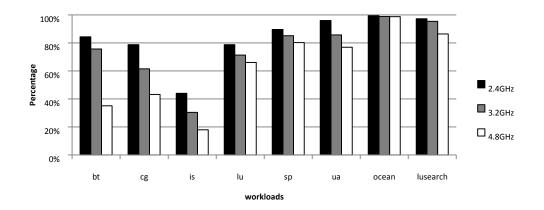

The energy efficiency of the system could be also improved by Dynamic Switching. Figure 2-16 details the energy efficiency improvement of the simulated system. In theory, the energy savings come from two sources: (1) low voltage and frequency scaling; and (2) the execution reduction time stemming from multiple buses brought by pin switching. We quantify the first part by setting the core frequency of the simulated system to 2.4 GHz (relating to the frequency of our multi-bus mode scheme) with the corresponding voltage for single bus. The results depicted as gray bars in Figure 2-16 demonstrate 40% improvement in the geometric mean of the EPI for all the workloads over the baseline. Note that the overall execution time of this setting is only

Figure 2-13. The off-chip bandwidth of Dynamic Switching improved by a stride prefetcher (degree = 1, 2, 4) for memory-Intensive workloads

slightly longer than that of the baseline system because all workloads are memoryintensive. Furthermore, the multi-bus mode offers an average of 66% improvement in the geometric mean of the EPI for all the workloads over the baseline resulting from execution time reduction.

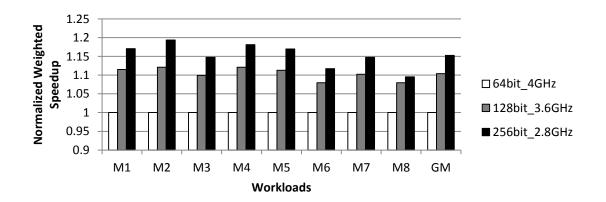

## 2.3.2 Wide-bus mode