## Turkish Journal of Electrical Engineering and Computer Sciences

Volume 30 | Number 3

Article 2

1-1-2022

# Independent closed loop control of di/dt and dv/dt for high power IGBTs

OSMAN TANRIVERDİ

DENİZ YILDIRIM

Follow this and additional works at: https://journals.tubitak.gov.tr/elektrik

Part of the Computer Engineering Commons, Computer Sciences Commons, and the Electrical and Computer Engineering Commons

#### **Recommended Citation**

TANRIVERDİ, OSMAN and YILDIRIM, DENİZ (2022) "Independent closed loop control of di/dt and dv/dt for high power IGBTs," *Turkish Journal of Electrical Engineering and Computer Sciences*: Vol. 30: No. 3, Article 2. https://doi.org/10.55730/1300-0632.3793 Available at: https://journals.tubitak.gov.tr/elektrik/vol30/iss3/2

This Article is brought to you for free and open access by TÜBİTAK Academic Journals. It has been accepted for inclusion in Turkish Journal of Electrical Engineering and Computer Sciences by an authorized editor of TÜBİTAK Academic Journals. For more information, please contact academic.publications@tubitak.gov.tr.

Turkish Journal of Electrical Engineering & Computer Sciences

http://journals.tubitak.gov.tr/elektrik/

Research Article

### Independent closed loop control of di/dt and dv/dt for high power IGBTs

Osman TANRIVERDİ<sup>1,2,\*</sup>, Deniz YILDIRIM<sup>3</sup>

<sup>1</sup>Department of Traction Systems, TÜBİTAK Rail Transport Technologies Institute, Kocaeli, Turkey <sup>2</sup>Electrical Engineering Program, Graduate School of Science Engineering and Technology, Istanbul Technical University, İstanbul, Turkey <sup>3</sup>Department of Electrical Engineering, Faculty of Electrical and Electronics, Istanbul Technical University,

İstanbul, Turkey

| <b>Received:</b> 06.03.2021 | • | Accepted/Published Online: 06.12.2021 | • | <b>Final Version:</b> 21.03.2022 |

|-----------------------------|---|---------------------------------------|---|----------------------------------|

|                             |   |                                       |   |                                  |

Abstract: As the insulated gate bipolar transistor (IGBT) modules have their own specific characteristic switching forms, their turn-on and turn-off times are changed according to practical applications. For the conventional gate drives, gate resistors are used to adjust the turn-on and turn-off times which change switching losses that have a significant amount in total losses. Collector current rate of change,  $di_C/dt$  and collector-emitter rate of change,  $dv_{CE}/dt$  are dependent on each other and they affect operating parameters in high power converters. Relations between current and voltages during the switching transitions are given and effects of the changes in electrical parameters for the operation of IGBT are described. Thereafter, closed-loop gate drive with analog control that performs independent control of  $di_C/dt$  and  $dv_{CE}/dt$  of a new generation IGBT module platform for high power applications is proposed. Unlike conventional gate drives, proposed closed-loop drive makes constant  $di_C/dt$  possible while  $dv_{CE}/dt$  is decreased to increase the efficiency of the power conversion system. This leads to decrease of the switching losses without changing the electromagnetic interference (EMI), IGBT voltage, and current stresses which are related with the rate of change of collector current. Simulations are performed in a double pulse test circuit in which new package next high power density dual (nHPD<sup>2</sup>) family MBM450FS33F Hitachi dual IGBT with 3300V 450A ratings is modelled.

Key words: Closed-loop gate drive, insulated-gate bipolar transistors (IGBTs), switching losses, turn-on and turn-off energy

#### 1. Introduction

Insulated gate bipolar transistors (IGBTs) are widely used in a variety of areas. Especially in high power converters, high voltage and high currents make switching behaviour of IGBTs important to be worked in the safe operating area (SOA). Gate drivers are employed to drive the IGBT with the desired gate current and also for safety switching. Conventional gate drives (CGDs) control switching transients  $di_C/dt$  and  $dv_{CE}/dt$  of IGBTs by manual selection of several gate resistors. Gate resistance also results in the variation of switching delay time that affects the control performance of power converters. CGDs control overshoot of the collector voltage and IGBT short circuit by active clamping and desaturation monitoring methods to protect IGBTs and the other components in a power electronics system [1–4].  $di_C/dt$  changes related with  $dv_{CE}/dt$  according to gate current which affects the switching losses, electromagnetic interference (EMI) issue and peak electrical

<sup>\*</sup>Correspondence: Correspondence: osman.tanriverdi@tubitak.gov.tr

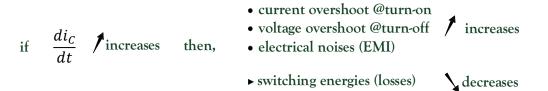

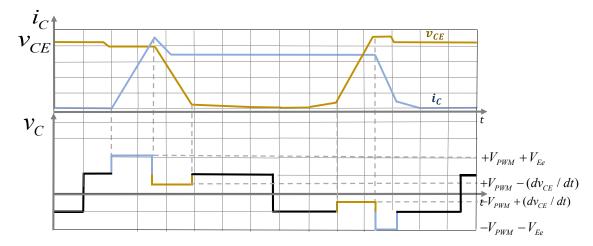

characteristics as shown in Figure 1. EMI problems are directly related with the value of  $di_C/dt$  which requires control of the current rate of change [5].

Figure 1.  $di_C/dt$  effects over electrical characteristics.

Ideal IGBT drive's capability is to turn the IGBT at specified levels of  $di_C/dt$  and  $dv_{CE}/dt$  regardless of load current, dc-link voltage, or junction temperature and to keep it within the SOA by means of controllable current and voltage peaks. In addition, the gate driver should be designed to withstand IGBT terminal voltage against high common-mode (CM)  $dv_{CE}/dt$  transients.

The rate of change of collector current  $(di_C/dt)$  is described in (1) for turn-on and turn-off, respectively [6];

$$\frac{di_C}{dt} = \frac{V_{GG} - (V_T - \frac{I_L}{2g_m})}{\frac{R_g C_{ies}}{g_m} + L_s}, \quad \text{at turn-on}

\frac{di_C}{dt} = \frac{V_T - V_{GG} + \frac{I_L}{2g_m}}{\frac{R_g C_{ies}}{g_m} + L_s}, \quad \text{at turn-off}$$

(1)

where  $V_{GG}$  is gate voltage,  $I_L$  is load current,  $g_m$  is IGBT transconductance,  $R_g$  is external gate resistance,  $C_{ies}$  is IGBT input parasitic capacitance,  $V_T$  is IGBT threshold voltage,  $L_s$  is the stray inductance between the IGBT chip emitter and the Kelvin emitter terminal of the IGBT. As seen in (1), gate resistance  $R_g$ is not dominant to change  $di_C/dt$  against transconductance of IGBT for CGDs. High delay time also occurs with CGD when gate resistor value is increased [6].

The rate of change of collector-emitter voltage depends actually on Miller capacitance and IGBT gate current which is defined as

$$\frac{dv_{CE}}{dt} = -\frac{V_{GC}}{dt} = -\frac{i_G}{C_{GC}} \tag{2}$$

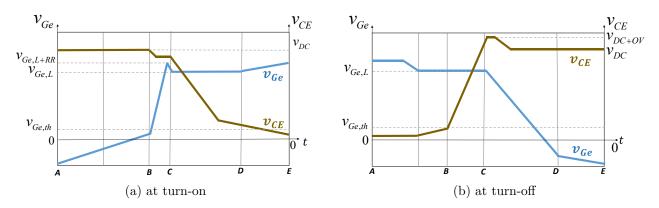

Figure 2 shows the relations of gate voltage and collector-emitter voltage at turn-on and at turn-off switching intervals. Each interval are divided into characteristic sections which are detailed in Table 1.  $dv_{CE}/dt$ always changes when the gate voltage is constant. This switching interval is called Miller Plateau. During the Miller Plateau, the gate voltage ( $v_{GE}$ ) and so the gate current ( $i_g$ ) is constant [7, 8]. This is shown with phase B-C at turn-on in Figure 2(a) and phase C-D at turn-off in Figure 2(b). According to (2),  $dv_{CE}/dt$  depends on Miller capacitance ( $C_{GC}$ ) and gate current ( $i_g$ ) where Miller capacitance is related to IGBT module in which the characteristic value cannot be changed. Therefore, the only control parameter that can change the  $dv_{CE}/dt$ can be gate current for CGDs.

Besides (1), the rate of collector current change is calculated as a function of gate current and the input capacitance as given in (3),

$$\frac{di_C}{dt} = g_m \frac{dv_{GE}}{dt} = g_m \frac{i_G}{C_{ies}} \simeq g_m \frac{i_G}{C_{GE}}$$

(3)

Figure 2. Collector-emitter and gate voltage waveforms for one switching cycle.

| Intervals | Turn-on                                                 | Turn-off                                        |  |

|-----------|---------------------------------------------------------|-------------------------------------------------|--|

| (A-B)     | Input capacitance $C_{GE}$ is charged.                  | Input capacitance $C_{GE}$ is discharged.       |  |

| (B-C)     | Gate voltage passes through the $v_{(GE,th)}$ .         | Constant gate voltage area (Miller Plateau).    |  |

|           | IGBT starts to conduct. $v_{CE}$ starts to decrease.    | $v_{CE}$ increases and reaches DC link voltage. |  |

| (C-D)     | Constant gate voltage area (Miller Plateau).            | $v_{CE}$ overshoots and sits on v+.             |  |

|           | $v_{CE}$ decreases its final minimum value immediately. | $v_{GE}$ passes through the $v_{GE,th}$ .       |  |

|           |                                                         | IGBT stops conducting.                          |  |

| (D-E)     | Gate voltage reaches its final positive value.          | Gate voltage reaches its final minimum value.   |  |

Table 1. IGBT turn-on and turn-off processes.

According to (3), the rate of collector current change depends on transconductance of the IGBT, gate current, and the gate-emitter capacitance where  $g_m$  and  $C_{GE}$  cannot be changed at the driver side. Gate current is again the only control parameter that changes the  $di_C/dt$ .

As a result, in CGDs,  $di_C/dt$  and  $dv_{CE}/dt$  can only be changed by gate resistor. Both  $di_C/dt$  and  $dv_{CE}/dt$  cannot be changed separately and setting one of them will result in the other one being fixed at a certain value. In order to control the rate of changes independently, they have to be adjusted individually, which cannot be performed in CGDs. An IGBT module with an antiparallel power diode is actually designed to achieve bidirectional current flow. The dynamic behaviours of the power diode are significantly impacting the transient switching of IGBT. Analysing the dynamic characteristics of power diodes shows that the peak reverse recovery current,  $I_{RR}$  given in (4), is proportional to the reverse recovery current rate of change,  $di_R/dt$ , which is the same as the collector current rate of change also at the commutation of antiparallel diode and the IGBT at turn-on [9].

$$I_{RR} \simeq 2.810^{-6} B V_{BD} \sqrt{I_F di_R/dt} \tag{4}$$

where  $I_F$  is diode forward current,  $BV_{BD}$  is diode breakdown voltage. The voltage overshoot,  $v_{OV}$ , is also proportional to the rate of change of the IGBT collector current during the turn-off and expressed as in (5)

$$v_{OV} = L_s \frac{di_C}{dt} \tag{5}$$

where  $L_s$  is the stray inductance of complete circuit.

The overshoot of the collector-emitter voltage occurs at turn-off and current overshoot occurs at turn-on, but all of these stresses that affect the SOA of the IGBT, and EMI issues of the system are related to collector current rate of change,  $di_C/dt$ . Decreasing gate resistor to reduce energy losses results in increase of  $di_C/dt$ and  $dv_{CE}/dt$  together and this leads to increase of overshoots of the IGBT, which is an undesirable situation for the power converters. Overshoots are decreased with increase of gate resistor, but this causes higher energy dissipation which affects the thermal state and the life of the IGBT module. The tradeoffs between EMI issue and switching losses are investigated in many studies such as in [10].

Many studies have been carried out on IGBT gate drive. There are active and closed-loop gate drive methods that change the switching transients by changing gate resistors [11, 12], change gate current parallel with pulse waveform according to feedbacks of collector current and collector-emitter voltage [13–26] and change gate voltage according to different switching periods [27, 28]. Closed-loop gate drive methods that directly change the pulse width modulation (PWM) voltage and thus control the gate current are given in [5, 6, 29– 45]. Digital control methods are given in [29–37]. Analog-to-digital controller (ADC) and digital-to-analog controller (DAC) converters are used for feedbacks and the digital control algorithm are achieved in a field programmable gate array (FPGA). These methods have drawbacks of delay in ADC and DAC that affect the switching delay times. Much more effective methods use analog control for the feedback algorithm. With the high bandwith operational amplifiers (OPAMPs), the control loop achieved high accuracy and minimum delays for the switching. These methods are proposed with  $di_C/dt$  control only [5, 6, 38],  $dv_{CE}/dt$  control only [39–43], and both  $di_C/dt$  and  $dv_{CE}/dt$  control [44, 45].

In order to overcome the disadvantages of the CGDs, the proposed gate drive method is developed. Since voltage and current transitions take place in different time intervals,  $di_C/dt$  and  $dv_{CE}/dt$  rates of high power IGBT module can be controlled independently in a closed-loop system. A new type half-bridge 3300V, 450A Hitachi IGBT module (MBM450FS33F) is used to apply the switching algorithm proposed in this paper, which provides some challenge and improved performance against other closed-loop gate drive studies. MBM450FS33F module is a new chip design IGBT which is physically new platform for high power IGBT module category. They have advantages of 75% reduction of inductance, 20% increase in power density and scalable design to increase the current capability of high power converters. The proposed IGBT gate drive control method achieves drive parameters over other closed-loop methods as outlined below:

- 1. High DC bus voltage: Closed-loop analog gate control designs given in the literature switch IGBTs under maximum 1000VDC bus voltage. The proposed control method is studied when DC bus voltage is 1830VDC which is much more critical especially at turn-off. The new method implements effective control with faster turn-off  $dv_{CE}/dt$  value.

- 2. Module scalable design: MBM450S33F IGBT module is designed according to parallel operation to increase the power capacity. The proposed gate drive method controls  $di_C/dt$  and this helps to achieve transient equal current sharing (TECS) in paralleling operation.

- 3. Low inductance sensing: MBM450FS33F IGBT module offers low inductance internal design to reduce oscillations in converter systems. Sensing the voltage slope with high oscillations at the transition time interval over low inductance is a challenge for the active gate drivers. The proposed gate drive senses  $di_C/dt$  accurately using parasitic inductance,  $L_{Ee}$ , between the main emitter and Kelvin emitter of the IGBT module.

#### 2. Proposed closed-loop gate drive

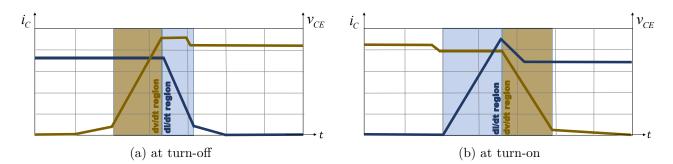

Ideally, it is clear in Figure 3 that collector-emitter voltage change is zero in the region of collector current change, and collector current change is zero in the region of collector-emitter voltage change, which means that the changes of  $v_{CE}$  and  $i_C$  do not occur at the same switching transition times.

Figure 3. Collector-emitter voltage and collector current behaviours at one switching cycle.

Due to the diode reverse recovery current at turn-on, the collector current, which has a peak in the turn-on state, drops to the normal level while the negative current change coincides with the collector voltage change. Although this situation initially causes change in  $dv_{CE}/dt$ , its effect during the turn-on will be very small.

Because switching speeds are independent of each other during the turn-on and turn-off intervals, single controller can easily be used for simultaneous control of  $dv_{CE}/dt$  and  $di_C/dt$ . This allows separate current and voltage control loops with one controller, which makes the control system simple.

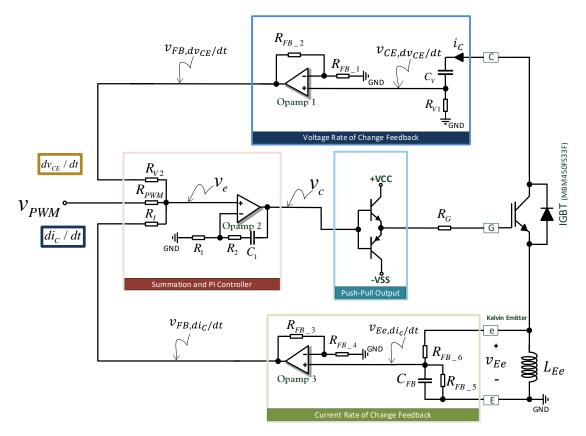

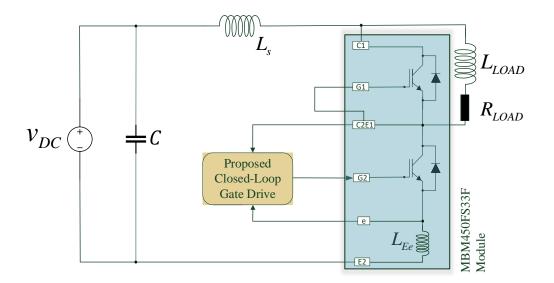

The proposed closed-loop gate drive circuit model that includes  $di_C/dt$  and  $dv_{CE}/dt$  feedbacks are given in Figure 4, where collector-emitter voltage and Kelvin emitter voltage are used as inputs for the analog controller. The feedback proportional to  $dv_{CE}/dt$  is obtained directly from capacitor  $C_V$  and resistor  $R_{F1}$  which is a phase-lead compensation structure that is used to measure the collector-emitter voltage slope  $(dv_{CE}/dt)$ . Derivative voltage, calculated as in (6), then feeds the input of Opamp 1.

$$v_{CE,dv_{CE}/dt} = R_{F1} \cdot C_V \cdot dv_{CE}/dt \tag{6}$$

Feedback proportional to  $di_C/dt$  feeds input of the Opamp 3 which is obtained from the stray inductance  $L_{Ee}$ . Output feedback voltage ( $v_{Ee,di_C/dt}$ ) is filtered and scaled with R-C-R integrator circuit and calculated as in (7) when  $R_{FB_6} << R_{FB_5}$ .  $C_{FB}$  is selected to filter the MHz level voltage oscillations over the  $L_{Ee}$ .

$$v_{Ee} = -L_{Ee} di_C / dt,$$

$$(v_{Ee} - v_{Ee,di_C / dt}) / R_{FB_6} = C_{FB} \cdot dv_{Ee,di_C / dt} / dt$$

(7)

$k_v$  and  $k_i$ , given in (8), are two feedback gains that are used to adjust  $di_C/dt$  and  $dv_{CE}/dt$ . These gains remain constant throughout the entire switching cycle according to desired  $di_C/dt$  and  $dv_{CE}/dt$  values. Two different control loops are active in successive times over a single PI controller. Although both control loops have separate gains, they operate on the common control reference PWM voltage. Feedback voltages are added to  $v_{PWM}$  reference PWM voltage and  $v_C$  control voltage occurs after the PI block. PWM control signal ( $v_{PWM}$ ) remains at the desired constant value at the positive cycle during the transition period of positive  $di_C/dt$  and

Figure 4. Proposed closed-loop control circuit diagram.

negative  $dv_{CE}/dt$ ; and during the transition period of negative  $di_C/dt$  and positive  $dv_{CE}/dt$ ,  $v_{PWM}$  stays at the required constant value at the negative cycle.  $v_{FB,di_C/dt}$  is feedback voltage of  $di_C/dt$ ,  $v_{FB,dv_{CE}/dt}$  is feedback voltage of  $dv_{CE}/dt$  as given in (9).

$$k_v = 1 + \frac{R_{FB_2}}{R_{FB_1}}$$

and  $k_i = 1 + \frac{R_{FB_3}}{R_{FB_4}}$  (8)

$$v_{FB,dv_{CE}/dt} = k_v \cdot v_{CE,dv_{CE}/dt},$$

$$v_{FB,di_C/dt} = k_i \cdot v_{Fe,di_C/dt}$$

(9)

A control error voltage  $(v_e)$  is generated by current and voltage feedbacks that are added to the reference PWM voltage  $(v_{PWM})$  in the closed loop as seen in Figure 5. Because the change intervals of the  $v_{CE}$  and  $i_C$  are different from each other, their feedback sample voltages occur in succession. They do not affect their control loop and this feature leads to separate change of  $di_C/dt$  and  $dv_{CE}/dt$  on their own active intervals.

Error voltage is applied to the PI controller to generate the control voltage  $(v_c)$ . PI controller can be built by fast operational amplifier where (ideal) gains can be written as in (10). After the PI unit, push-pull drive is used to provide the needed current to drive IGBT module.

$$K_p = 1 + R_2/R_1, \quad K_I = 1 + R_1/C_1$$

(10)

Figure 5. Complete cycle of switching with feedback voltages of  $di_C/dt$  and  $dv_{CE}/dt$ .

#### 3. Simulations

Double pulse test power circuit and gate drive control circuit is modelled in ANSYS Simplorer. New package 3300V 450A dual IGBT modules have been recently designed by manufacturers. These modules are easy to be used in parallel in power converters with the advantages of high power density and easy scalable features. The dynamic behaviour model of MBM450FS33F IGBT module is generated to use in analysis.  $v_{GE}$ - $i_C$ ,  $v_{CE}$ - $i_C$ ,  $v_{F}$ - $i_F$ ,  $Z_{thjc}$ -t waveforms are used directly from the module datasheet. Parameters which are used to model the IGBT module are listed as in Table 2.

| Symbol      | Definition                     | Value                |

|-------------|--------------------------------|----------------------|

| $C_{in}$    | Input capacitance              | 24nF                 |

| $C_r$       | Feedback (miller) capacitance  | 1nF                  |

| $R_G$       | Internal gate resistance       | $6.2 \ \Omega$       |

| $L_{G_Ext}$ | External gate stray inductance | 2nH                  |

| $L_{tot}$   | Total lead stray inductance    | 9nH                  |

| $R_{tot}$   | Total lead resistance          | $18 \text{ m}\Omega$ |

Table 2. Input parameters for IGBT model.

The circuit as in Figure 6 is simulated and different situations are investigated in this part. Pulse width is chosen as 10  $\mu$ s. DC-link voltage  $v_{DC}$  is 1800 VDC. System line inductance  $L_s$  is 60 nH. The load inductance  $L_{LOAD}$  is 1200  $\mu$ H and its resistance  $R_{LOAD}$  is 2 m $\Omega$ . Collector current level goes up to 450 A at turn-on interval. As the MBM450FS33f dual IGBT module is selected, its inductance  $L_{Ee}$  between kelvin emitter and power emitter is calculated as 3 nH which is used for feedback inductance for  $di_C/dt$ . This emitter inductance value is extracted from the IGBT short circuit test waveforms of the manufacturer.

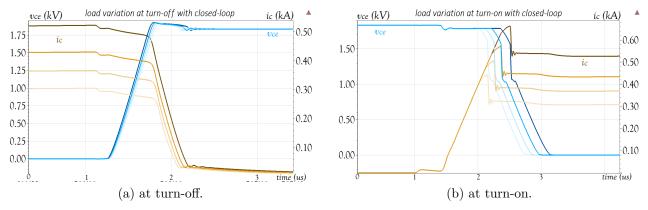

#### 3.1. Load variations in proposed gate control

Collector current changes with different load values. Normally, for the conventional gate drivers, increasing the system load leads collector current to rise that results with the increase of  $di_C/dt$ .  $T_{on}$  turn-on time

Figure 6. Double pulse test circuit with feedbacks.

increases with the collector current while  $T_{off}$  turn-off time decreases with the collector current as depicted in the datasheet of the MBM450FS33F IGBT module.

For the proposed  $di_C/dt$  and  $dv_{CE}/dt$  closed-loop control, it can be seen from Figures 7a and 7b that load variations do not affect the rates of change of current and voltage. Their rates of change become stable at turn-off and turn-on switching cycles, which means that the load current does not change the electrical stresses during the switching instant.

Figure 7. Simulation results of  $v_{CE}$  and  $i_C$  waveforms for load variation at turn-off and turn-on.

#### 3.2. $di_C/dt$ and $dv_{CE}/dt$ independent control

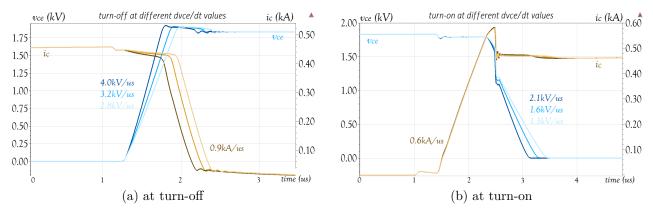

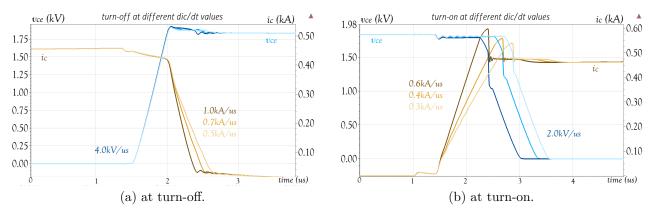

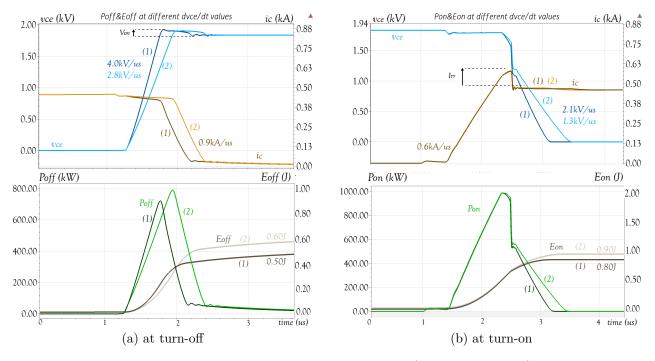

To explain the basic function of the proposed independent control, feedback gains are changed in simulations and all  $i_C$  and  $v_{CE}$  waveforms are curved together. Figures 8a and 8b shows the turn-off and turn-on switching transitions for a variation of  $dv_{CE}/dt$  when the  $di_C/dt$  is kept constant. By changing the feedback resistor of  $R_{FB_2}$  in the  $dv_{CE}/dt$  feedback loop, it is seen that only  $dv_{CE}/dt$  changes with  $4kV/\mu s$ ,  $3.2kV/\mu s$ , and  $2.8kV/\mu s$  at turn-off and  $2.1kV/\mu s$ ,  $1.6kV/\mu s$ , and  $1.3kV/\mu s$  at turn-on.  $di_C/dt$  stays constant with  $0.9kA/\mu s$ at turn-off and  $0.6kA/\mu s$  at turn-on simultaneously.

#### TANRIVERDİ and YILDIRIM/Turk J Elec Eng & Comp Sci

Figures 9a and 9b show the turn-on and turn-off switching transitions for a variation of  $di_C/dt$  when the  $dv_{CE}/dt$  is kept constant. By changing the feedback resistor of  $R_{FB_3}$  in the  $di_C/dt$  feedback loop, it is seen that only  $di_C/dt$  is changing with  $1kA/\mu s$ ,  $0.7kA/\mu s$ , and  $0.5kA/\mu s$  at turn-off and  $0.6kA/\mu s$ ,  $0.4kA/\mu s$ , and  $0.3kA/\mu s$  at turn-on.  $dv_{CE}/dt$  stays constant with  $4kV/\mu s$  at turn-off and  $2kV/\mu s$  at turn-on in all switching cycles. In conventional gate drives, peak of the collector-emitter voltage  $v_{CE}$  normally increases when the  $di_C/dt$  increases at turn-off, whereas the overshoot of  $v_{CE}$  is same in all  $di_C/dt$  values with the proposed closed-loop gate drive as seen in Figure 9a.

Figure 8. Simulation results of  $v_{CE}$  and  $i_C$  waveforms for (a) turn-off and (b) turn-on at different  $dv_{CE}/dt$  values when  $di_C/dt$  is constant.

Figure 9. Simulation results of  $v_{CE}$  and  $i_C$  waveforms for (a) turn-off and (b) turn-on at different  $di_C/dt$  values when  $dv_{CE}/dt$  is constant.

#### 3.3. Comperative study with CGDs

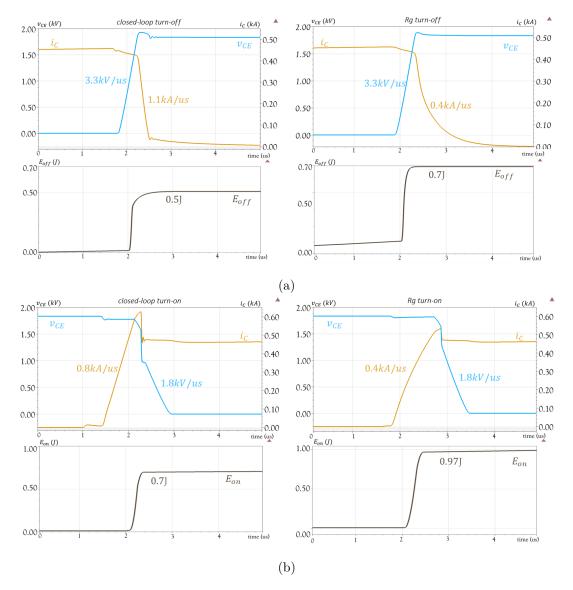

The following study is derived in order to show the benefits of the proposed control against open loop, i.e. resistive CGD. Comparison is done with the same 3.3kV, 450A IGBT half-bridge model (Hitachi MBM450FS33F) based on switching losses. Turn-off and turn-on waveforms of switching transients for  $i_C$  and  $v_{CE}$  are shown in Figures 10a and 10b, respectively. Left column shows the closed-loop control, rigth column shows the CGDs waveforms at turn-off and turn-on. Waveforms are derived to show the controllability of the current and voltage change speed in the current study.  $dv_{CE}/dt$  is set to  $1.8 \text{kV}/\mu$ s and gate resistors of the CGD are adjusted for the same  $dv_{CE}/dt$  value with the closed-loop drive for turn-on analysis. In CGD,  $di_C/dt$  is measured as 0.4kA/ $\mu$ s.  $dv_{CE}/dt$  is set to 3.3kV/ $\mu$ s and gate resistors of the CGD are adjusted for the same voltage slope as the closed-loop drive for turn-off analysis. In CGD,  $di_C/dt$  is measured as 0.4kA/ $\mu$ s. However, contrary to CGDs, due to the independent control of current,  $di_C/dt$  is set to be 0.8kA/ $\mu$ s at turn-on and 1.1kA/ $\mu$ s at turn-off for the proposed closed-loop control. In addition to illustrate the slope differences of  $di_C/dt$ , Figure 10 shows also the energies at turn-on and turn-off. The proposed gate drive enables decrease of switching energies significantly by its ability to set  $di_C/dt$  faster than CGDs. As a result, the comperative study shows that  $di_C/dt$  can be changed while  $dv_{CE}/dt$  is constant by using the closed-loop gate drive technique which is not possible with CGDs. Restrictions of SOA operation and EMI can be solved to decrease power losses of the IGBT module with independent control of voltage and current slope which is described in detail in the following section.

Figure 10. Simulation comparison of CGD and closed-loop voltage and current waveforms for (a) turn-off and (b) turn-on at different  $di_C/dt$  values when  $dv_{CE}/dt$  is constant.

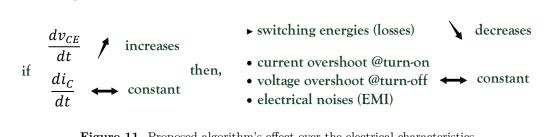

#### **3.4.** $dv_{CE}/dt$ control with constant $di_C/dt$

The critical issue for the proposed gate drive is the ability to change  $dv_{CE}/dt$  without changing  $di_C/dt$  by using feedback gain  $k_v$ . Therefore, energy losses of the IGBT module in the operation of high power energy conversion can be decreased without the increase of overshoots of the  $v_{CE}$  and  $i_C$  at turn-off and turn-on, respectively. Also, EMI issue is not affected. The relationship of the switching system parameters of the proposed gate control is seen in Figure 11.

Figure 11. Proposed algorithm's effect over the electrical characteristics.

In order to describe the effect of the proposed switching algorithm over the energy losses, mathematical expressions are given [46]. The voltage and current waveforms are considered to be linear to simplify the switching energy expressions. Discrete change areas of the voltage and current waveforms make energy expressions  $dv_{CE}/dt$  and  $di_C/dt$  related basically as given in (11).

Turn-on switching energies are expressed in three parts which are voltage slope related,  $E_{on,dv_{CE}/dt}$ , current slope related,  $E_{on,di_C/dt}$ , and reverse recovery related,  $E_{on,irr}$ . Turn-off switching energies are expressed in three parts which are voltage slope related,  $E_{off,dv_{CE}/dt}$ , current slope related,  $E_{off,di_C/dt}$ , and tail current related,  $E_{off,tail}$  for turn-off switching interval. It can be seen in (12) that by the proposed method, increase of the  $dv_{CE}/dt$  leads to decrease of the  $E_{on}$  and  $E_{off}$  in which  $di_C/dt$  is constant.

$$E_{on} = E_{on,dv_{CE}/dt} + E_{on,di_C/dt} + E_{on,irr}$$

$$E_{off} = E_{off,dv_{CE}/dt} + E_{off,di_C/dt} + E_{off,tail}$$

(11)

$$E_{on} = \underbrace{\frac{i_L \cdot v_{DC}}{2} \cdot \frac{v_{DC}}{|dv_{CE}/dt|} \cdot (1 - \sigma_s)^2}_{E_{on,dv_{CE}/dt}} + \underbrace{\frac{i_L \cdot v_{DC}}{2} \cdot \frac{i_L}{|di_C/dt|} - \frac{1}{2} \cdot L_s \cdot i_L^2}_{E_{on,di_C/dt}} + \underbrace{(i_L \cdot \sqrt{\frac{Q_{rr}}{|di_C/dt|}} + Q_{rr}) \cdot v_{DC} \cdot (1 - \sigma_s)^2}_{E_{on,irr}}$$

(12)

$$E_{off} = \underbrace{\frac{i_L \cdot v_{DC}}{2} \cdot \frac{v_{DC}}{\mid dv_{CE}/dt \mid} \cdot (1 + \sigma_s)^2}_{E_{off,dv_{CE}/dt}} + \underbrace{\frac{i_L \cdot v_{DC}}{2} \cdot \frac{i_L}{\mid di_C/dt \mid}}_{E_{off,di_C/dt}} + \underbrace{\frac{1}{2} \cdot L_s \cdot i_L^2}_{E_{off,di_C/dt}} + \underbrace{\frac{v_{DC} \cdot Q_t}{E_{off,tail}}}_{E_{off,di_C/dt}}$$

where  $v_{DC}$  is the DC-link voltage,  $Q_{rr}$  is the stored reverse recovery charge of the diode,  $\sigma_s$  is the ratio between voltage drop across  $L_s$  and voltage  $v_{DC}$  during the current slope, and  $Q_t$  is the stored charge extracted by the tail current.

Figures 12a and 12b show the main principle idea of the proposed hard switching method clearly.  $E_{on}$  and  $E_{off}$  change according to change in  $dv_{CE}/dt$  with the  $di_C/dt$  kept constant. It is clearly seen that, by the proposed control technique, without changing  $di_C/dt$ , switching energy losses can be adjusted. As  $di_C/dt$  is constant, collector-emitter voltage peak  $(v_{ov})$  and collector current peak  $(i_{rr})$  stay constant at turn-off and turn-on, respectively.

Figure 12. Simulation results of  $E_{off}$  and  $E_{on}$  at different  $dv_{CE}/dt$  values when  $di_C/dt$  is constant.

#### 4. Conclusion

A new type of closed-loop gate drive technique based on  $di_C/dt$  and  $dv_{CE}/dt$  feedback control is proposed in this paper. Different change time intervals of current and voltage allows  $dv_{CE}/dt$  and  $di_C/dt$  to be controlled with the same PWM reference gate voltage. Control of current and voltage slopes independently leads to reduction of the switching energy losses for a constant  $di_C/dt$  while changing  $dv_{CE}/dt$ . Constant  $di_C/dt$  limits the collector-emitter voltage ( $v_{CE}$ ) and collector current ( $i_C$ ) overshoots and conducted and radiated-mode noise levels in the power conversion system. Otherwise, in CGDs, there has to be a trade-off between losses and safety operation parameters like EMI, voltage and current overshoots.

The control method is implemented using the double pulse test circuit and model of a new type nHPD<sup>2</sup> series MBM450FS33F Hitachi high power IGBT is used for the simulations. Feedbacks and control side of the closed-loop gate drive are implemented using analogue circuits. The new closed-loop control method achieves very high speed switching at high voltage (>1800VDC) especially at turn-off transient in which voltage overshoot occurs. With the high-accuracy current slope control over very low internal inductance sensing, the proposed closed-loop control enables paralleling of MBM450FS33F IGBT modules that have scalable design to increase power in a converter system. CGDs employed in different IGBT modules with same gate resistors results in various levels of safe operating area issues. Unlike the conventional methods, the closed-loop gate drive allows hardware to be used with different models of IGBT modules without changing gate resistors.

#### TANRIVERDİ and YILDIRIM/Turk J Elec Eng & Comp Sci

Despite its advantages, the proposed gate drive control may have some limitations at the implementation. The system can be sensitive to electronic component tolerances because the proposed method is composed of analogue circuits. Proper selection of operational amplifiers should be done to avoid control limitations, such as voltage drift due to the temperature, slew rate and common mode rejection ratio. Since turn-on and turn-off transitions are in nanosecond levels, high analogue control bandwidth has to be used to achieve accurate  $dv_{CE}/dt$  and  $di_C/dt$  feedback signals. PCB layout design is critical to avoid electrical noises because of high current switching at high voltage.

As a future research, the proposed control method will be tested with different IGBT models and performance of the method will be analysed. In addition, transfer functions of the whole closed-loop system will be conducted to confirm the new control method. Some traction converter-based system disturbances such as IGBT thermal effect and instantaneous DC bus voltage fluctuations will be modelled to test the stability of the proposed control method.

#### References

- Chen G, Wang Y, Cai X, Igarashi S. Adaptive digital drive for high power and voltage IGBT in multi-MW wind power converter. In: Proceedings of The 7th International Power Electronics and Motion Control Conference; Harbin, China; 2012. doi: 10.1109/IPEMC.2012.6259033

- [2] Lai J, Hefner A, Maitra A, Goodman F. Characterization of a multilevel HV-IGBT module for distribution applications. IEEE Industry Applications Conference Forty-First IAS Annual Meeting 2006. doi: 10.1109/IAS.2006.256610

- [3] Lai J, Leslie L, Ferrell J, Nergaard T. Characterization of HV-IGBT for High-Power Inverter Applications. In: Fourtieth IAS Annual Meeting. Conference Record of the 2005 Industry Applications Conference; Kowloon, Hong Kong, China; 2005. doi: 10.1109/IAS.2005.1518335

- [4] Reigosa PD, Wu R, Iannuzzo F, Blaabjerg F. Evidence of Gate Voltage Oscillations during Short Circuit of Commercial 1.7 kV / 1 kA IGBT Power Modules. In: PCIM International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management; Nuremberg, Germany; 2015.

- [5] Fink K, Bernel S. Advanced Gate Drive Unit With Closed-Loop di / dt Control. IEEE Transactions on Power Electronics; 28 (5); 2013. pp 2587 - 2595. doi: 10.1109/TPEL.2012.2215885

- [6] Chen L, Peng FZ. Closed-Loop Gate Drive for High Power IGBTs. In: Twenty-Fourth Annual IEEE Applied Power Electronics Conference and Exposition; Washington, DC, USA; 2009. doi: 10.1109/APEC.2009.4802837

- [7] Oberdieck K, Schuch S, DeDoncker RW. Short circuit detection using the gate charge characteristic for Trench/Fieldstop-IGBTs.In: 18th European Conference on Power Electronics and Applications; Karlsruhe, Germany; 2016. doi: 10.1109/EPE.2016.7695402

- [8] Khanna VK. IGBT Theory and Design. New York, NY, USA: IEEE Press, 2003.

- [9] Muhammad HR. Power Electronics-Circuits, Devices, and Applications. 3rd edition, Upper Saddle River, NJ, Pearson Prentice Hall, 2004.

- [10] Kagerbauer JD, Jahns TM. Development of an Active dv/dt Control Algorithm for Reducing Inverter Conducted EMI with Minimal Impact on Switching Losses. In: IEEE Power Electronics Specialists Conference; Orlando, FL, USA; 2007. doi: 10.1109/PESC.2007.4342107

- [11] Schmitt G, Kennel R, Holtz J. Voltage gradient limitation of IGBTS by optimised gate-current profiles. In: IEEE Power Electronics Specialists Conference; Rhodes, Greece; 2008. doi: 10.1109/PESC.2008.4592512

- [12] Takizawa S, Igarashi, Kuroki K. A novel gate drive circuit for low-loss system using IGBT saturation voltage characteristics. 13th International Symposium on Power Semiconductor Devices and ICs; Osaka, Japan; 2001. doi: 10.1109/ISPSD.2001.934633

- [13] Cacciato M, Consoli A, Frascodore G, Testa A, Gianninni G et al. Driving optimization of IGBT devices for traction applications. European Conference on Power Electronics and Applications; Dresden, Germany; 2005. doi: 10.1109/EPE.2005.219641

- [14] Liu Z, Zhou D, Sun K, Huang L, Matsuse K et al. A novel driving and protection circuit for reverse blocking IGBT used in matrix converter. IEEE Industry Applications Conference; Seattle, WA, USA; 2004. doi: 10.1109/IAS.2004.1348730

- [15] Wang Z, Shi X, Tolbert LM, Wang F, Blalock BJ. A di/dt feedback-based active gate driver for smart switching and fast overcurrent protection of IGBT modules. IEEE Transactions on Power Electronics; 29 (7); 2014. pp 3720-3732. doi: 10.1109/TPEL.2013.2278794

- [16] Shu L, Zhang J, Peng F, Chen Z. Active Current Source IGBT Gate Drive With Closed-Loop di/dt and dv/dt Control. IEEE Transactions on Power Electronics; 32 (5); 2017. pp 3787-3796. doi: 10.1109/TPEL.2016.2587340

- [17] Schmitt G, Kennel R, Holtz J. Voltage gradient limitation of IGBTs by optimised gate-current profile. In: IEEE Power Electronics Specialists Conference; Rhodes, Greece; 2008. doi: 10.1109/PESC.2008.4592512

- [18] Rose M, Krupar J, Hauswald H. Adaptive dv/dt and di/dt control for isolated gate power devices.In: IEEE Energy Conversion Congress and Exposition; Atlanta, GA, USA; 2010. doi: 10.1109/ECCE.2010.5617892

- [19] Baraia I, Barrena JA, Abad G, Segade JMC, Iraola U. An Experimentally Verified Active Gate Control Method for the Series Connection of IGBT/Diodes. IEEE Transactions on Power Electronics; 27 (2); 2012. pp 1025 - 1038. doi: 10.1109/TPEL.2011.2161336

- [20] Wittig B, Fuchs FW. Analysis and Comparison of Turn-off Active Gate Control Methods for Low-Voltage Power MOSFETs With High Current Ratings. IEEE Transactions on Power Electronics; 27 (3); 2012. doi: 10.1109/TPEL.2011.2162531

- [21] Zhang F, Ren Y, Tian M, Yang X. A novel active gate drive for HV-IGBTs using feed-forward gate charge control strategy. In: IEEE Energy Conversion Congress and Exposition (ECCE); Montreal, QC, Canada; 2015. doi: 10.1109/ECCE.2015.7310641

- [22] Shu L, Zhang J, Shao S. Crosstalk Analysis and Suppression for a Closed-Loop Active IGBT Gate Driver. IEEE Journal of Emerging and Selected Topics in Power Electronics; 7 (3); 2019. doi: 10.1109/JESTPE.2018.2869678

- [23] Shu L, Zhang J, Peng F, Chen Z. A voltage controlled current source gate drive method for IGBT devices. In: IEEE Energy Conversion Congress and Exposition (ECCE); Pittsburgh, PA, USA; 2014. doi: 10.1109/ECCE.2014.6954158

- [24] Shu L, Zhang J, Peng F, Chen Z. Active Current Source IGBT Gate Drive With Closed-Loop di/dt and dv/dt Control. IEEE Transactions on Power Electronics; 32 (5); 2017. pp 3787-3796. doi: 10.1109/TPEL.2016.2587340

- [25] Du X, Chen Q, Li G, Hu C, Ye Q. Closed loop control method of turn-on di/dt and turn-off du/dt for insulated gate bipolar transistors. In: 12th IEEE Conference on Industrial Electronics and Applications (ICIEA); Siem Reap, Cambodia; 2017. doi: 10.1109/ICIEA.2017.8283099

- [26] Zhang F, Yang X, Ren Y, Feng L, Chen W et al. Advanced Active Gate Drive for Switching Performance Improvement and Overvoltage Protection of High-Power IGBTs. IEEE Transactions on Power Electronics; 33 (5); 2018. doi: 10.1109/TPEL.2017.2716370

- [27] Idir N, Bausiere R, Franchaud JJ. Active gate voltage control of turn-on di/dt and turn-off dv/dt in insulated gate transistors. IEEE Transactions on Power Electronics; 21 (4); 2006. doi: 10.1109/TPEL.2007.876895

- [28] Ling Y, Zhao Z, Zhu Y. A Self-Regulation Gate Driver for High-Power IGBTs. IEEE Transactions on Power Electronics; 36 (3); 2021. doi:10.1109/TPEL.2020.3015924

- [29] Kuhn H, Koneke T, Mertens A. Potential of Digital Gate Units in High Power Appliations. In: 13th EPE-PEMC Power Electronics and Motion Control Conference; Poznan, Poland; 2008. doi:10.1109/EPEPEMC.2008.4635473

- [30] Handt K, Köhler H, Hiller M, Sommer R. Fully Digitally Controlled Gate Drive Unit for High Power IGBTs. In: PCIM Europe Conference; Nuremberg, Germany; 2012.

- [31] Blank M, Glück T, Kugi A, Kreuter HP. Slew rate control strategies for smart power ICs based on iterative learning control. In: IEEE Applied Power Electronics Conference and Exposition - APEC; Fort Worth, TX, USA; 2014. doi: 10.1109/APEC.2014.6803710

- [32] Dang L, Kuhn H, Mertens A. Digital Adaptive Driving Strategies for High-Voltage IGBTs. IEEE Transactions on Industry Applications; 49 (4); 2013. doi: 10.1109/TIA.2013.2257638

- [33] Groeger J, Schindler A, Wicht B, Norling K. Optimized dv/dt, di/dt sensing for a digitally controlled slope shaping gate driver. In: IEEE Applied Power Electronics Conference and Exposition (APEC); Tampa, FL, USA; 2017. doi: 10.1109/APEC.2017.7931209

- [34] Chen G, Wang Y, Cai X, Igarashi S. Adaptive Digital Drive for High Power and Voltage IGBT in Multi-MW Wind Power Converter. In: IEEE 7th International Power Electronics and Motion Control Conference - ECCE Asia; Harbin, China; 2012. doi: 10.1109/IPEMC.2012.6259033

- [35] Groeger J, Wicht B, Norling K. Dynamic stability of a closed-loop gate driver enabling digitally controlled slope shaping. In: 13th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME); Giardini Naxos, Italy; 2017. doi: 10.1109/PRIME.2017.7974107

- [36] Liangdeng H, Yulin C, Sheng A. A new two feed-back control method integrated in digital gate driver for large power IGBT. In: IEEE Information Technology, Networking, Electronic and Automation Control Conference; Chongqing, China; 2016. doi: 10.1109/ITNEC.2016.7560546

- [37] Wang R, Liang L, Chen Y, Pan Y, Li J et al. Self-Adaptive Active Gate Driver for IGBT Switching Performance Optimization Based on Status Monitoring. IEEE Transactions on Power Electronics; 35 (6); 2020. doi:10.1109/TPEL.2019.2947268

- [38] Chen L, Ge B, Peng FZ. Modeling and analysis of closed-loop gate drive. In: Twenty-Fifth Annual IEEE Applied Power Electronics Conference and Exposition (APEC); Palm Springs, CA, USA; 2010. doi: 10.1109/APEC.2010.5433360

- [39] Wang Y, Palmer PR, Bryant AT, Finney SJ, Abu-Khaizaran MS et al. An Analysis of High-Power IGBT Switching Under Cascade Active Voltage Control. IEEE Transactions on Industry Applications; 45 (2); 2009. pp 861 - 870. doi: 10.1109/TIA.2009.2013595

- [40] Wang Y, Palmer PR, Lim TC, Finney SJ, Bryant AT. Real-time optimization of IGBT/diode cell switching under active voltage control. In: IEEE Industry Applications Conference Forty-First IAS Annual Meeting; Tampa, FL, USA; 2006. doi: 10.1109/IAS.2006.256857

- [41] Lim TC, Williams BW, Finney SJ, Palmer PR. Series-Connected IGBTs Using Active Voltage Control Technique. IEEE Transactions on Power Electronics; 28 (8); 2013. doi: 10.1109/TPEL.2012.2227812

- [42] Palmer PR, Yang X, He W. Dead-time minimisation using active voltage control gate drive for high-power IGBT converters. In: 38th Annual Conference on IEEE Industrial Electronics Society; Montreal, QC, Canada; 2012. doi: 10.1109/IECON.2012.6388624

- [43] Yang X, Yuan Y, zhang X, Palmer PR. Shaping High-Power IGBT Switching Transitions by Active Voltage Control for Reduced EMI Generation. IEEE Transactions on Industry Applications; 51 (2); 2015. doi: 10.1109/TIA.2014.2347578

- [44] Lobsiger Y, Kolar JM. Closed-Loop di/dt and dv/dt IGBT Gate Driver. IEEE Transactions on Power Electronics; 30 (6); 2015. doi: 10.1109/TPEL.2014.2332811

- [45] Lobsiger Y, Kolar JM. Stability and robustness analysis of d/dt-closed-loop IGBT gate drive. In: Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC); Long Beach, CA, USA; 2013.

- [46] Lobsiger Y. Closed-Loop IGBT Gate Drive and Current Balancing Concepts. PhD, ETH Zürich, Switzerland, 2014.