P Applied Physics Letters

## Inductively heated synthesized graphene with record transistor mobility on oxidized silicon substrates at room temperature

Li Tao, Jongho Lee, Huifeng Li, Richard D. Piner, Rodney S. Ruoff et al.

Citation: Appl. Phys. Lett. **103**, 183115 (2013); doi: 10.1063/1.4828501 View online: http://dx.doi.org/10.1063/1.4828501 View Table of Contents: http://apl.aip.org/resource/1/APPLAB/v103/i18 Published by the AIP Publishing LLC.

## Additional information on Appl. Phys. Lett.

Journal Homepage: http://apl.aip.org/ Journal Information: http://apl.aip.org/about/about\_the\_journal Top downloads: http://apl.aip.org/features/most\_downloaded Information for Authors: http://apl.aip.org/authors

metals • ceramics • polymers composites • compounds • glasses

Save 5% • Buy online 70,000 products • Fast shipping

## Inductively heated synthesized graphene with record transistor mobility on oxidized silicon substrates at room temperature

Li Tao,<sup>1</sup> Jongho Lee,<sup>1</sup> Huifeng Li,<sup>2</sup> Richard D. Piner,<sup>2</sup> Rodney S. Ruoff,<sup>2</sup> and Deji Akinwande<sup>1,a)</sup>

<sup>1</sup>Department of Electrical and Computer Engineering, Microelectornics Research Center, The University of Texas, Austin, Texas, 78758, USA

<sup>2</sup>Department of Mechanical Engineering, The University of Texas, Austin, Texas 78758, USA.

(Received 23 July 2013; accepted 17 October 2013; published online 1 November 2013)

We report chemical vapor-deposited (CVD) graphene field-effect transistors (GFETs) on conventional SiO<sub>2</sub>/Si substrate with high-performance comparable to GFETs on boron nitride under practical ambient conditions. The fabricated GFET statistics reveal maximum carrier mobility of ~17800 cm<sup>2</sup>/V-s. Intrinsic graphene features such as three-region output characteristics including soft current saturation have also been observed, in addition to over ten-fold gate modulation. Low-temperature studies indicate that impurity scattering is the limiting transport mechanism. Our results on graphene, synthesized by an inductively heated CVD system, suggest that the prospects of GFETs on oxidized silicon are comparable to those on ideal surfaces, e.g., *h*BN at room temperature. © 2013 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4828501]

Charge transport in graphene on technological important interfaces such as oxidized silicon is of great importance owing to the maturity and widespread use of this interface as a gate oxide for solid-state transistors.<sup>1,2</sup> Compared to higher-k interfaces such as Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub>, graphene field-effect transistors on SiO<sub>2</sub> have higher FET mobility as a result of its relatively higher surface optical phonon energies (59 and 155 meV).<sup>2,3</sup> However, compared to hexagonal boron nitride (hBN) dielectric which offers even higher optical phonon energies (102 and 195 meV) and a flatter surface,<sup>3,4</sup> graphene on SiO<sub>2</sub>/Si consistently shows inferior performance which becomes more pronounced at lower temperatures as impurity scattering obscures the expected improvement in mobility.<sup>2</sup> In addition, many important features of carrier transport in GFETs such as current saturation and strong electron-hole symmetry are rarely observed especially with CVD graphene transferred onto SiO<sub>2</sub>/Si and tested under ambient conditions (the operating condition for virtually all practical device applications). Despite the outstanding GFET performance achievable on exfoliated hBN, the challenge of synthesizing high-quality large-area films of controlled thickness has limited its current prospects.<sup>5</sup> For these reasons, recent research has been increasingly focused on the transport properties of graphene on polar and non-polar interfaces, and many surface effect techniques have been reported including the use of hydrophobic, organic, and fluoropolymer thin film interfaces to enhance carrier mobility and reduce impurity doping on standard substrates.<sup>6-9</sup>

In this article, we report on the state-of-the-art transistors using large-area CVD graphene on standard SiO<sub>2</sub>/Si under ambient conditions. The GFETs displayed mobilities as high as 17 800 cm<sup>2</sup>/V-s, strong electron-hole symmetry, current saturation, and gate modulation of current that is greater than an order of magnitude. We attribute these outstanding transistor properties primarily to improvements in graphene synthesis based on our recently developed inductively-heated chemical vapor deposition,<sup>10</sup> and improvement in graphene transfer and fabrication that is largely free of residue. The achieved results using synthetic graphene on oxide are comparable to the leading results reported for exfoliated graphene on exfoliated *h*BN dielectric. This suggests that high-performance GFETs with all the desirable graphene properties are achievable on SiO<sub>2</sub>/Si at room temperature without the need for interface engineering or 'ideal' dielectric materials.

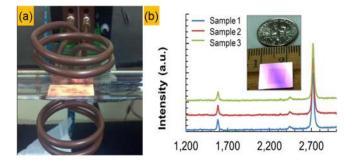

The graphene used in this study was synthesized via inductively heated chemical vapor deposition, a method we recently developed.<sup>10</sup> Inductive heating uses magnetic fields to remotely heat the surface of conductive films and is widely used in industry.<sup>10</sup> This inductively heated CVD setup (Fig. 1(a)) allows rapid heating and cooling rates (up to  $30 \,^{\circ}\text{C/s}$ ), and heating between room temperature and the growth temperature (1100°C) can be achieved within 3 min. A typical two-step annealing and growth consumes 20-30 min. Consequently, the total processing time takes 23-33 min, compared to 60–100 min for conventional thermal CVD.<sup>11,12</sup> In addition, the magnetic induction heating occurs mostly on the surface of the sample via eddy currents localized to within a skin depth. As a result, it is a much more energy-efficient furnace that heats up only the desired growth surface compared to traditional cold-wall resistive heating that heats up the entire substrate. The synthesized graphene was then transferred onto 285 nm thermal oxide on silicon using a popular process, adapted from the conventional poly(methyl methacrylate) (PMMA) method<sup>13</sup> with 12 rinse cycles to obtain highquality transfer.<sup>10</sup> Raman spectroscopy was employed to verify the quality of the monolayer graphene with the following characteristics (Fig.1(b)): (i) full width at half maximum (FWHM) of the 2D-peak is  $\sim 30 \text{ cm}^{-1}$ , (ii) the intensity ratio of the 2D/G is 3-4, and (iii) negligible D-peak.

Three-terminal back-gated GFETs were fabricated using a resist-free shadow mask process to define source and drain contacts. Device isolation was achieved by probe-tip

a)Electronic mail: deji@ece.utexas.edu

FIG. 1. (a) Image showing the center section of the inductively heated chemical vapor deposition system (operating frequency 240 kHz) for graphene synthesis; (b) representative Raman spectrum of synthesized graphene (inset is an optical image of transferred graphene onto  $SiO_2/Si$  substrate compared to a dime).

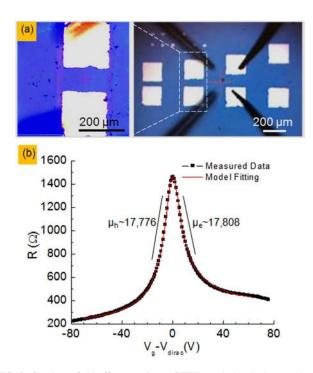

patterning. The GFET channel length varied in a doubling manner from 25 to 200  $\mu$ m with a fixed channel width of 200  $\mu$ m as shown in Fig. 2(a). A record mobility value of 17 800 was observed from these back-gated devices on SiO<sub>2</sub>/Si as seen in Fig. 2(b).

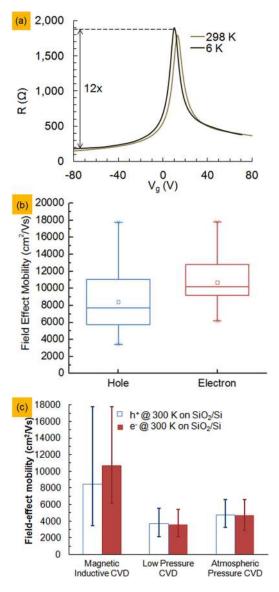

Electrostatic measurements under ambient and low temperature conditions shown in Fig. 3(a) represent the electrical performance of GFETs from our synthesized graphene. A typical transfer curve as seen in Fig. 3(a) reveals an  $I_{ON}/I_{OFF}$ (or  $R_{MAX}/R_{MIN}$ ) ratio over 12, which is one of the highest values reported so far for CVD graphene devices on SiO<sub>2</sub>/Si under ambient conditions. The  $I_{OFF}$  ( $R_{MAX}$ ) is defined here as the current (resistance) at the Dirac point, while the  $I_{ON}$ ( $R_{MIN}$ ) is the current (resistance) at gate voltages sufficiently far from the Dirac point where the device resistance asymptotically approaches the contact resistance.<sup>15,16</sup> The slight positive shift of the Dirac voltage is attributed to unintentional

FIG. 2. Graphene field-effect transistor (GFET) made by shadow mask: (a) optical image of GFET devices (channel length varied from 25 to 200  $\mu$ m). (b) Transfer curve (squares) measured at ambient condition in strong agreement with a diffusive model (line),<sup>14</sup> indicating outstanding mobility of ~17 800 cm<sup>2</sup>/V-s.

p-type charge doping of graphene either from the polymer residue on graphene from the wet-transfer process or moisture adsorption from the ambient.<sup>17–21</sup> Low-temperature studies of the carrier mobility down to 6K reveal little or no temperature dependence suggesting that impurity scattering is the dominant scattering mechanism.

Fig. 3(b) shows the statistics of the low-field carrier mobilities extracted from 22 different experimental devices using a widely accepted diffusive transport model.<sup>14</sup> The highest mobility obtained in our GFETs is  $\sim 17\,800 \text{ cm}^2/\text{V-s}$  and the statistical mobility data depict an average of 8400 and 10700 cm<sup>2</sup>/V-s for holes and electrons, respectively. These room-temperature values are significantly higher than

FIG. 3. Electrical characterization of fabricated graphene field effect transistors (GFET): (a) I<sub>d</sub> versus V<sub>g</sub> curve at 6 K and 298 K showing invariant mobility (~14 000 cm<sup>2</sup>/V-s using the same aforementioned fitting model) with respect to the temperature. (b) Box statistical value of extracted field effect mobility from 22 GFET devices measured at ambient condition (notches from top to bottom: maximum ×, 75%, mean value  $\Box$ , 25%, and minimum × values) with maximum field-effect mobility up to 17 800 cm<sup>2</sup>/V-s. (c) Comparison of field-effect mobility values from graphene transistors on SiO<sub>2</sub>/Si sharing the same configuration, admension, and transfer method: the inductive CVD graphene exhibited superior electrical performance than counterparts from conventional thermal chemical vapor deposition.

TABLE I. Comparison of the electrical properties of recently reported high mobility CVD and exfoliated graphene devices.

| Reference                  | Graphene source/dielectric      | Temperature for measurement | Field effect mobility (cm <sup>2</sup> /V-s) | Impurity concentration $(cm^{-2})$ |

|----------------------------|---------------------------------|-----------------------------|----------------------------------------------|------------------------------------|

| Cornell, 2011 (Ref. 23)    | CVD-Gra/SiO <sub>2</sub>        | 298 K                       | $7300 \pm 1100$                              | N/A                                |

| UTD 2012 (Ref. 22)         | CVD-Gra/SiO <sub>2</sub>        | 77 K                        | 7800-12700                                   | $5-6 \times 10^{11}$               |

|                            |                                 | 298 K                       | $5760 \pm 680$                               | $5.5-6.5 	imes 10^{11}$            |

| UT Austin 2010 (Ref. 24)   | CVD-Gra/SiO <sub>2</sub>        | 298 K                       | 800-16 000                                   | N/A                                |

| This work                  | CVD-Gra/SiO <sub>2</sub>        | 298 K                       | 6000-17 800                                  | $2-8 \times 10^{11}$               |

| Columbia U. 2010 (Ref. 26) | CVD-Gra/hBN                     | 298 K                       | 8579 or 10 713                               | $\sim 2 \times 10^{11}$            |

| SKKU, 2012 (Ref. 27)       | CVD-Gra/hBN                     | 298 K                       | 3000-6850                                    | $\sim 0.5 \times 10^{11}$          |

| UT Austin. 2010 (Ref. 30)  | Exfoliated Gra/SiO <sub>2</sub> | 298 K                       | $4000 \sim 11\ 000$                          | $5 - 15 \times 10^{11}$            |

the existing reported GFET mobilities from conventional CVD graphene on SiO<sub>2</sub> dielectric<sup>22-25</sup> and even comparable to GFETs on  $hBN^{26-28}$  dielectric as well as the best samples of exfoliated graphene on SiO<sub>2</sub>/Si<sup>29,30</sup> as summarized in Table I. Although high mobility values had been reported for conventional CVD graphene on SiO<sub>2</sub>/Si,<sup>24</sup> graphene synthesized in this work exhibits more stable performance with much higher average mobility value and lower variation range. We note that the maximum GFET mobility achieved in this work is within a factor of two of the surface phonon-limited theoretical value in the absence of charge or neutral impurity scattering ( $\sim 25900 \text{ cm}^2/\text{V-s}$ ),<sup>3</sup> indicating further progress is possible. Using the same device configuration and dimension, we conducted another comparison among different graphene synthesis methods to show that our developed synthesis route is the dominating factor for superior mobility of our GFETs. Fig. 3(c) shows the same batch of devices made using three different CVD methods, and the mobility of graphene synthesized via inductive heating is 2-3 times higher than counterparts from conventional low and atmospheric pressure CVD.

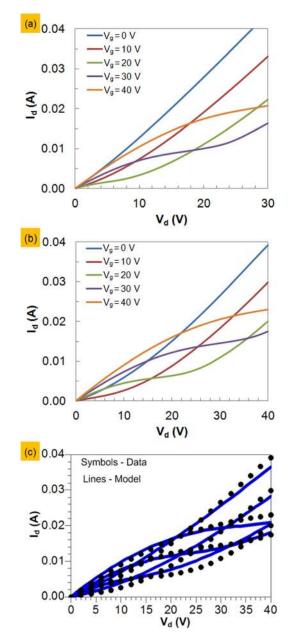

In addition to the high mobility and I<sub>ON</sub>/I<sub>OFF</sub>, the fabricated GFETs also demonstrated current saturation and the unique three-region response at room temperature. Although current saturation and the three-region response of graphene has been reported in 2008,<sup>31</sup> it had been limited to exfoliated graphene with top-gate configuration and measured at low temperature. Recent reports on this topic still employs top-gate,<sup>32</sup> or exfoliated graphene.<sup>33</sup> This is likely because back-gate structures with thick thermal oxide are considered a poor electrostatic media for observing these features.<sup>31</sup> However, our measurement in Fig. 4 shows that these features can be observed for the graphene studied here with thick gate oxides commonly used for basic post-transfer studies. Moreover, similar to the low temperature behavior (Fig. 4(a)), the  $I_d$ - $V_d$  output curve exhibits a complete three-region response with kink-effect<sup>31-33</sup> at ambient condition (purple and green curves in Fig. 4(b)). Physics based drift-diffusive transport modeling,<sup>34</sup> including fundamental effects such as field-dependent quantum capacitance, fixed velocity saturation, and fixed contact resistance show good agreement with the experimental output characteristics (Fig. 4(c)). The model parameters are based on values similar to those extracted from the transfer characteristics with (the best fit) saturation velocity of  $\sim 5 \times 10^7$  cm/s, which is close to the theoretical estimate for charge carriers in graphene on an oxidized Si substrate.<sup>3</sup> The high saturation velocity, which is about half of the Fermi velocity in graphene is further affirmation of the fast carrier properties of the high-quality graphene on SiO<sub>2</sub>/Si.

FIG. 4. Experimental  $I_d$  versus  $V_d$  with different gate bias showing saturation and the so-called second linear region (purple and brown curve) at (a) 6 K and (b) 298 K (room temperature); (c) drift-diffusive transport modeling exhibits a good agreement with experimental data in (b).

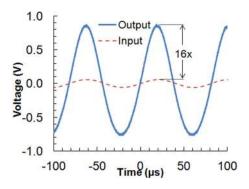

FIG. 5. Amplifier with  $16 \times$  voltage gain achieved with the fabricated graphene field effect transistors.

Given the high mobility, high  $I_{ON}/I_{OFF}$  ratio and demonstrated current saturation, our high-performance GFETs are well suited for analogue applications such as room temperature terahertz devices and detectors.<sup>35,36</sup> For instance, a common-source amplifier shown in Fig. 5 yields a 16 × voltage gain between output (at the drain) and input (at the gate). The hole branch of the GFET was employed showing the expected non-inverting amplifier response.<sup>35</sup> The input source was provided by a function generator (12.2 kHz) with an oscilloscope serving as the load with a load impedance of 1 MΩ.

In conclusion, we have demonstrated GFETs from inductively heated CVD graphene transferred onto SiO<sub>2</sub>/Si substrate with high carrier mobility comparable to those achieved on *h*BN under ambient conditions. Output characteristics indicate three-region response including soft current saturation, which is an intrinsic feature of GFETs. A GFET amplifier with voltage gain of about  $16 \times$  was also realized. Our results suggest that the prospects of experimental GFETs on oxidized silicon are comparable to those on ideal surfaces at room temperature.

This work was supported in part by the Nanoelectronic Research Initiative (NRI SWAN Center), the Office of Naval Research, and the NSF CAREER award (D.A).

- <sup>1</sup>S. C. Sun and J. D. Plummer, IEEE J. Solid-State Circuits **15**(4), 562 (1980).

- <sup>2</sup>J.-Hao. Chen, C. Jang, S. Xiao, M. Ishigami, and M. S. Fuhrer, Nat Nanotechnol. **3**(4), 206 (2008).

- <sup>3</sup>V. Perebeinos and P. Avouris, Phys. Rev. B 81(19), 195442 (2010).

- <sup>4</sup>C. R. Dean, A. F. Young, I. Meric, C. Lee, L. Wang, S. Sorgenfrei, K. Watanabe, T. Taniguchi, P. Kim, K. L. Shepard, and J. Hone, Nat Nanotechnol. 5(10), 722 (2010).

- <sup>5</sup>A. Ismach, H. Chou, D. A. Ferrer, Y. Wu, S. McDonnell, H. C. Floresca, A. Covacevich, C. Pope, R. Piner, M. J. Kim, R. M. Wallace, L. Colombo, and R. S. Ruoff, ACS Nano 6(7), 6378 (2012).

- <sup>6</sup>J. W. Suk, W. Hyoung Lee, J. Lee, H. Chou, R. D. Piner, Y. Hao, D. Akinwande, and R. S. Ruoff, Nano Lett. **13**(4), 1462 (2013).

- <sup>7</sup>T. J. Ha, J. Lee, D. Akinwande, and A. Dodabalapur, IEEE Electron Device Lett. **34**(4), 559 (2013).

- <sup>8</sup>T.-J. Ha, J. Lee, Sk. Fahad Chowdhury, D. Akinwande, P. J. Rossky, and A. Dodabalapur, ACS Appl. Mater. Interfaces **5**(1), 16 (2013).

- <sup>9</sup>M. Lafkioti, B. Krauss, T. Lohmann, U. Zschieschang, H. Klauk, K. V. Klitzing, and J. H. Smet, Nano Lett. **10**(4), 1149 (2010).

- <sup>10</sup>R. Piner, H. Li, X. Kong, L. Tao, I. N. Kholmanov, H. Ji, W. Hyoung Lee, J. Won Suk, J. Ye, Y. Hao, S. Chen, C. W. Magnuson, A. F. Ismach, D. Akinwande, and R. S. Ruoff, ACS Nano 7(9), 7495 (2013).

- <sup>11</sup>L. Tao, J. Lee, M. Holt, H. Chou, S. J. McDonnell, D. A. Ferrer, M. G. Babenco, R. M. Wallace, S. K. Banerjee, R. S. Ruoff, and D. Akinwande, J. Phys. Chem. C 116(45), 24068 (2012).

- <sup>12</sup>L. Tao, J. Lee, H. Chou, M. Holt, R. S. Ruoff, and D. Akinwande, ACS Nano 6(3), 2319 (2012).

- <sup>13</sup>X. Li, W. Cai, J. An, S. Kim, J. Nah, D. Yang, R. Piner, A. Velamakanni, I. Jung, E. Tutuc, S. K. Banerjee, L. Colombo, and R. S. Ruoff, Science **324**(5932), 1312 (2009).

- <sup>14</sup>S. Kim, J. Nah, I. Jo, D. Shahrjerdi, L. Colombo, Z. Yao, E. Tutuc, and S. K. Banerjee, Appl. Phys. Lett. **94**(6), 062107 (2009).

- <sup>15</sup>K. N. Parrish and D. Akinwande, Appl. Phys. Lett. **98**(18), 183505 (2011).

- <sup>16</sup>F. Xia, V. Perebeinos, Y.-ming Lin, Y. Wu, and P. Avouris, Nat Nano **6**(3), 179 (2011).

- <sup>17</sup>G. Giovannetti, P. A. Khomyakov, G. Brocks, V. M. Karpan, J. van den Brink, and P. J. Kelly, Phys. Rev. Lett. **101**(2), 026803 (2008).

- <sup>18</sup>R. Varns and P. Strange, J. Phys.: Condens. Matter 20(22), 225005 (2008).

<sup>19</sup>P. L. Levesque, S. S. Sabri, C. M. Aguirre, J. Guillemette, M. Siaj, P.

- Desjardins, T. Szkopek, and R. Martel, Nano Lett. 11(1), 132 (2011).

<sup>20</sup>K. M. McCreary, K. Pi, A. G. Swartz, W. Han, W. Bao, C. N. Lau, F. Guinea, M. I. Katsnelson, and R. K. Kawakami, Phys. Rev. B 81(11), 115453 (2010).

- <sup>21</sup>A. Pirkle, J. Chan, A. Venugopal, D. Hinojos, C. W. Magnuson, S. McDonnell, L. Colombo, E. M. Vogel, R. S. Ruoff, and R. M. Wallace, Appl. Phys. Lett. **99**(12), 122108 (2011).

- <sup>22</sup>J. Chan, A. Venugopal, A. Pirkle, S. McDonnell, D. Hinojos, C. W. Magnuson, R. S. Ruoff, L. Colombo, R. M. Wallace, and E. M. Vogel, ACS Nano 6(4), 3224 (2012).

- <sup>23</sup>P. Y. Huang, C. S. R. Vargas, A. M. van der Zande, W. S. Whitney, M. P. Levendorf, J. W. Kevek, S. Garg, J. S. Alden, C. J. Hustedt, Y. Zhu, J. Park, P. L. McEuen, and D. A. Muller, *Nature* **469**(7330), 389 (2011).

- <sup>24</sup>X. Li, C. W. Magnuson, A. Venugopal, J. An, J. Won Suk, B. Han, M. Borysiak, W. Cai, A. Velamakanni, Y. Zhu, L. Fu, E. M. Vogel, E. Voelkl, L. Colombo, and R. S. Ruoff, Nano Lett. **10**(11), 4328 (2010).

- <sup>25</sup>K. Nagashio, T. Yamashita, T. Nishimura, K. Kita, and A. Toriumi, J. Appl. Phys. **110**(2), 024513 (2011).

- <sup>26</sup>I. Meric, C. Dean, A. Young, J. Hone, P. Kim, and K. L. Shepard, "Graphene field-effect transistors based on boron nitride gate dielectrics," 2010 IEEE International Electron Devices Meeting (IEDM), 23.2.1.

- <sup>27</sup>K. H. Lee, H.-J. Shin, J. Lee, I.-Y. Lee, G.-H. Kim, J.-Y. Choi, and S.-W. Kim, Nano Lett. **12**(2), 714 (2012).

- <sup>28</sup>N. Petrone, C. R. Dean, I. Meric, A. M. van der Zande, P. Y. Huang, L. Wang, D. Muller, K. L. Shepard, and J. Hone, Nano Lett. **12**(6), 2751 (2012).

- <sup>20</sup>Y. W. Tan, Y. Zhang, K. Bolotin, Y. Zhao, S. Adam, E. H. Hwang, S. Das Sarma, H. L. Stormer, and P. Kim, Phys. Rev. Lett. **99**(24), 246803 (2007).

- <sup>30</sup>B. Fallahazad, S. Kim, L. Colombo, and E. Tutuc, Appl. Phys. Lett. **97**(12), 123105 (2010).

- <sup>31</sup>I. Meric, M. Y. Han, A. F. Young, B. Ozyilmaz, P. Kim, and K. L. Shepard, Nat. Nanotechnol 3(11), 654 (2008).

- <sup>32</sup>J. Bai, L. Liao, H. Zhou, R. Cheng, L. Liu, Y. Huang, and X. Duan, Nano Lett. **11**(6), 2555 (2011).

- <sup>33</sup>B. W. Scott and J. Leburton, "High-field carrier velocity and current saturation in graphene field-effect transistors," 2010 10th IEEE Conference on Nanotechnology, p. 655.

- <sup>34</sup>K. N. Parrish and D. Akinwande, Appl. Phys. Lett. **101**(5), 053501 (2012).

- <sup>35</sup>X. Yang, G. Liu, A. A. Balandin, and K. Mohanram, ACS Nano 4(10), 5532 (2010).

- <sup>36</sup>C. Pai-Yen, C. Argyropoulos, and A. Alu, IEEE Trans. Antennas Propag. 61(4), 1528 (2013).