## Instrumented chip dedicated to semiconductor temperature measurements in power electronic converters

Ibrahima Ka, Yvan Avenas, Laurent Dupont, Raha Vafaei, Benoît Thollin, Jean Christophe Crebier, Mickael Petit

### ▶ To cite this version:

Ibrahima Ka, Yvan Avenas, Laurent Dupont, Raha Vafaei, Benoît Thollin, et al.. Instrumented chip dedicated to semiconductor temperature measurements in power electronic converters. ECCE 2016 - IEEE Energy Conversion Congress and Exposition, Sep 2016, Milwaukee, United States. 11p, 10.1109/ECCE.2016.7855208. hal-01684165

## HAL Id: hal-01684165 https://hal.archives-ouvertes.fr/hal-01684165

Submitted on 15 Jan2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Instrumented Chip Dedicated to Semiconductor Temperature Measurements in Power Electronic Converters

Ibrahima KA<sup>1, 2</sup>, Yvan AVENAS<sup>1</sup>, Laurent DUPONT<sup>2</sup> <sup>1</sup> Univ. Grenoble Alpes, G2Elab, F-38000 Grenoble, France CNRS, G2Elab, F-38000 Grenoble, France. <sup>2</sup> SATIE, IFSTTAR, 25 allée des Marronniers, F-78000 Versailles, France.

#### Raha VAFAEI<sup>1</sup>, Benoît THOLLIN<sup>1</sup>, Jean-Christophe CREBIER<sup>1</sup>, Mickael PETIT<sup>3</sup> THE ENS Casher - CNAM - Université de Castre Parteire - CNAS - LIMP 8020, E 04220 Cast

<sup>3</sup> SATIE, ENS Cachan - CNAM - Université de Cergy Pontoise - CNRS UMR 8029, F-94230 Cachan, France.

*Abstract*— Temperature measurement of semiconductor components is essential, in particular to evaluate performances and to propose health monitoring of power modules. ThermoSensitive Electrical Parameters (TSEPs) are widely used to estimate a representative temperature of these components, mainly in non-operating conditions, different from the real environment of the latter (offline measurements). Nevertheless, some TSEPs may be adapted to online temperature measurements, in operating conditions of power converters. It is however difficult to evaluate the accuracy of those TSEPs. This paper presents an instrumented chip dedicated to estimate the temperature in power electronic modules under functional constraints. Thus, it offers a reliable and robust tool for temperature measurements in power electronic converters. Preliminary results presented in this paper concern the technological process of realization and demonstrate the good functioning of this instrumented chip under power dissipation and switching conditions.

Keywords— Temperature measurement; Thermo Sensitive Electrical Parameters; Temperature Sensor; monitoring; instrumented chip, power electronic converters.

#### I. INTRODUCTION

Power modules lifetime is strongly linked to multiphysic constraints and especially to thermal environment in which they are used, mostly through temperature fluctuations [1] [2]. According to a study published in 2011 [3], semiconductor components are among the most fragile elements in converters; 30% of breakdowns would be connected to these elements. This study also suggests that temperature would be the first cause of failures, causing about 55% of power components damages Thus, chip temperature evaluation is necessary to quantify thermal and electrical performances, to estimate damage levels and eventually to define a predictive approach of remaining lifetime of power electronic systems thanks to adapted diagnostic tools. Several acquisition techniques have been evaluated in order to measure the temperature within converters [4].

Nowadays, instrumented modules are proposed by manufacturers for chip temperature estimation through on-substrate integrated sensors, close to semiconductor active parts [5]. Thus, temperature estimation in operating conditions is done using thermal models. But, thermal modeling is relatively complex because of inaccurate estimation of power losses in components, electrothermal coupling effects and progressive degradation of thermal and electrical performances of power modules and dedicated cooling system. Consequently, estimated temperature from a model does not necessarily reflect the current electrothermal state of the system, particularly when one device is degraded [6].

Sensor integration inside the structure of semiconductor devices is also proposed to more accurately measure the temperature of the active parts [7]. However, this implementation induces an additional cost and increases the complexity of power modules. Besides, the integrated sensor makes local temperature measurements while the global distribution within the chip is strongly non-uniform [8]. In contrast, ThermoSensitive Electrical Parameters (TSEPs) mostly give a global value of the chip temperature, making their use attractive. It is worth to point out that temperature measurements with TSEPs are made without modifying the modules integrity, in contrast with other more intrusive methods, like fiber optic thermometry or infrared (IR) thermography.

TSEPs principle is based on correlation between defined electrical parameters of power semiconductor devices (Forward voltage drop, dynamics characteristics, etc.) and their temperature. It is thus possible to estimate the temperature of the active parts using calibration curves, generally adapted to each device. In the scientific literature, TSEPs are generally classified, according to

methodological approaches used for measurements, depending on whether it is adapted to operating conditions of converters (online measurements), or it requires to take place outside of these conditions (offline measurements). Thus, correlation between TSEPs and "real" temperature of semiconductor power devices is widely studied [9] [10] [11].

Nevertheless, as shown in [12], the results obtained with TSEPs stemming from static characteristics I(V) can be erroneous when the conditions of calibration of TSEPs are different from the real operating conditions of converter use. Besides, ageing of power modules may disturb measurements through TSEPs [13]. It is then important to evaluate the representativeness and the robustness of TSEPs in operating conditions of converters and for various levels of damage.

Up to now, the performances of online temperature measurements with TSEPs is demonstrated using IR thermography [14] [15] or electrothermal simulations [16]. IR thermography is intrusive, requiring modifications of power module packaging. Electrothermal models used in simulations involve trade-offs and are consequently not representative of investigated systems.

As an alternative, we propose to apply an original approach based on an adapted instrumented chip. Our investigation focuses on the validation of TSEPs in real operating conditions of power converters. This evaluation requires the design of specific tools, for instance by combining TSEPs and a thermal sensor. The guiding principle of our work is to use this integrated thermal sensor as validation means. In this paper, the process of realization of the instrumented power diode will be first explained. The experimental tests carried out for preliminary functional validation of the instrumented chip will then be presented.

#### II. TECHNOLOGICAL OPTIONS OF CONCEPTION

#### A. Approach and structure of instrumented chip

#### 1) Technological approach

The basic principle lies on the integration of a temperature sensor on top surface of a power diode [17] [18]. Temperature sensor uses the principle of variation of the electric resistivity of certain materials in respect to temperature. According to equation 1, resistivity of these materials varies in almost linear way with a constant Temperature Coefficient of Resistance (TCR)  $\alpha_{AI}$  [%/°C].  $\Delta R$  is sensor's resistance variation,  $R_0$  the sensor resistance at a reference temperature  $T_0$  and  $\Delta T$ , the temperature variation in respect to  $T_0$ . Resistance and temperature units are Ohms and Celsius respectively.

$$\frac{\Delta R}{R_0} = \alpha_{Al} \,\Delta T \quad [\%] \tag{1}$$

The material used to design the temperature sensor is chosen through the analysis of several criteria, in particular, sensibility which is intrinsically connected to TCR value, linearity, simplicity of technological implementation and manufacturing cost. In the light of this study, the aluminum presents interesting characteristics with a theoretical TCR of 0.43%/°C, a moderate cost, a good chemical stability and a compatibility with the technology of bondings for external connections of the sensor.

#### 2) Structure of instrumented chip

The temperature sensor was integrated on the top (Anode) of a standard off-the-shelf power diode (ABB fast recovery diode 5SLX 12M1711 1700V/200A, 13.56mmx13.56mm, 385µm thickness).

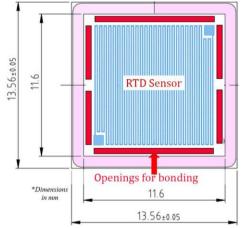

The sensor topology on the surface of the power diode (Figure 1) is defined in such a way that it will be able to measure averaged temperature of the instrumented chip. Openings on chip borders allow connecting bondings on power diode anode for external connections. It should be noted that this configuration is not efficient for the current distribution nevertheless it remains a good trade-off with regard to IR thermography measurements to be made easily in the experimental validation.

Fig. 1. Topology of RTD sensor integrated onto power diode

The voltage drop across the sensor is intrinsically linked to resistance variations and the current injected into the sensor. Theoretical value of the sensor resistance at 25°C is 400  $\Omega$  according to equation 2 with the parameters given in Tab 1. The minimum voltage drop across the sensor is then 400 mV with measurement current of 1mA, what offers sufficient measurement accuracy for temperature higher than 25°C in accordance with measurement tools.

$$R_{capteur} = \frac{\rho_{Al}*L}{e*h_{Al}} \tag{2}$$

Tab 1. Sensor parameters

| Aluminum resistivity $\rho_{Al}$ (@25°C) [19] | 2,8 10 <sup>-8</sup> Ω. m |

|-----------------------------------------------|---------------------------|

| Pattern thickness <i>e</i>                    | 70 μ <i>m</i>             |

| Aluminum thickness $h_{Al}$                   | 500 nm                    |

| Pattern mean length <i>L</i>                  | 0.5 m                     |

#### B. Realization process of instrumented chip

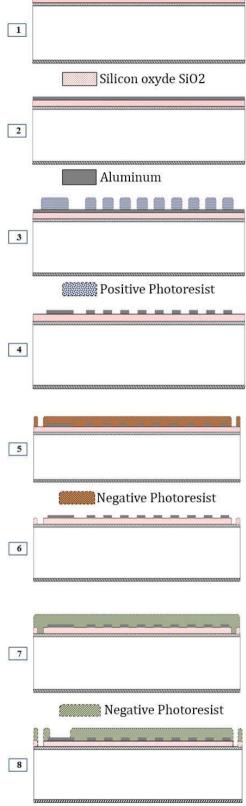

The instrumented chip is realized under environmentally controlled conditions in cleanroom (Plateforme Technologique Amont de Grenoble). The various steps of realization are illustrated on figure 3.

First of all, standard off-the-shelf power diodes are delivered without passivation (polyimide free) and are specially supplied before the final control tests usually performed by manufacturers. Thus, anode surface is protected from any degradation generally caused by microprobes. Chips are first chemically cleaned with a solution of acetone and isopropanol to avoid surface contaminations and to remove dust particles.

The step 1 consists of an insulating silicon oxide layer deposition (SiO<sub>2</sub> of  $2\mu$ m of thickness), realized by Plasma-Enhanced Chemical Vapor Deposition (PECVD). In addition to electrical insulation, the SiO<sub>2</sub> layer thickness is defined in order to lower thermal barrier between the chip and the temperature sensor and to provide mechanical holder with regard to the tests and bonding stress. Initially of 400nm, the SiO<sub>2</sub> layer was damaged by sensor calibration tests, what engendered a short circuit between the sensor pads and the power diode. Analytical calculations then allowed studying the impact of higher oxide layer thickness to  $2\mu$ m, which is a technological limit imposed by used PECVD equipment.

Then, a 500nm aluminum layer deposition is realized in the step 2 by vacuum evaporation on the top surface of the chip. Metal thickness is a determining parameter of resistance value and, consequently, the range of measurable voltage across the sensor, towards precision and accuracy of measuring devices. Metal thickness is also imposed by cleanroom process.

The sensor pattern is then drawn by UV lithography with positive photoresist AZ1512HS (step 3) and a chemical etching eliminate residual metal. Protection photoresist is removed by lift-off at step 4. In this state, the RTD sensor is completely defined and integrated on the power diode anode.

It is necessary to set up border openings to access to anode metallization for bondings. Reactive Ion Etching (RIE) allows eliminating thermal oxide on defined locations using negative photoresist nLof2070 reported by optical lithography (steps 5 and 6).

Finally, a second protection layer is realized with negative photoresist spin coated SU8, hardbaked to 180°C with adapted pattern defined by optical lithography. The lithography mask allows reaching the pads of the RTD sensor and the anode. This last photoresist layer aims to protect the RTD sensor from external degradations.

#### III. EXPERIMENTAL VALIDATION OF INSTRUMENTED CHIP

#### A. Calibrations of temperature sensor and power diode TSEP

#### 1) Calibration of temperature sensor with microprobes

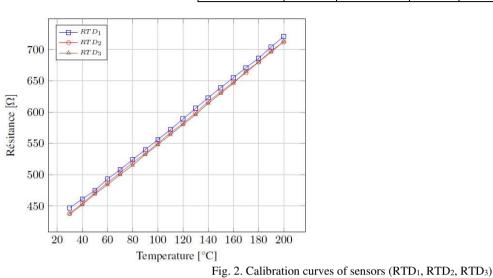

Sensors calibration with microprobes (Figure 2) is the first step to evaluate the RTD resistance. The measurement with a low measurement current (1mA) is done using four wires (Kelvin) method to avoid wire resistance contributions and, so, to estimate with more precision the sensor resistance as a function of chip temperature.

Fig. 2. RTD sensor calibration with microprobes

Fig. 3. Different steps of technological process

Current injection and voltage measurement are performed thanks to a sourcemeter unit (SMU) Keithley 2602B which offers a relative accuracy of 0.03% for a current source level of 1mA and 0.015% for a voltage measurement range of 1V. Chip temperature is controlled by a hotplate (Lab Mix 35) with control range within +/-5K. For preliminary tests, high measurement accuracy is not needed in order to validate good sensors integration.

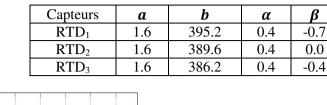

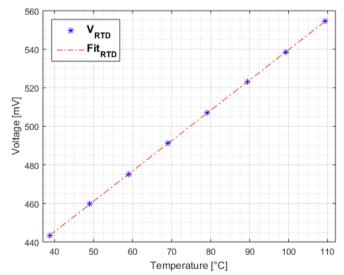

The sensor resistance evolution in respect to temperature is fitted by a linear equation with parameters a, b,  $\alpha$  and  $\beta$ :

$$\boldsymbol{R_{rtd}} = \boldsymbol{aT_{sensor}} + \boldsymbol{b} \quad [\Omega] \tag{3}$$

The TCR of the sensors is experimentally defined from the equation 4.

$$\frac{\Delta R}{R_0} = \alpha \,\Delta T + \beta \quad [\%] \tag{4}$$

Tab 2. RTD sensors parameters

#### 2) DBC substrat calibration

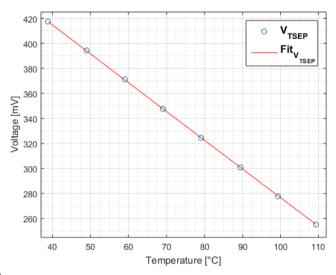

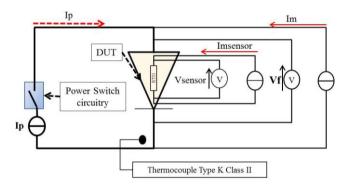

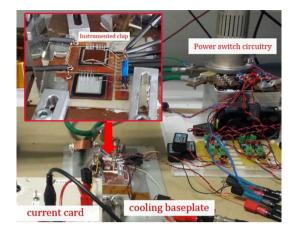

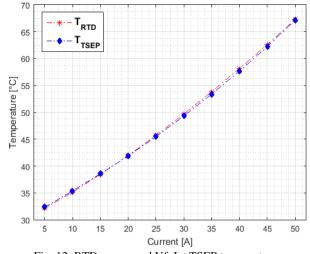

The instrumented chips are soldered on DBC substrates in a switching cell configuration (Figure 9). Calibration is performed on TSEP Vf\_Ict (forward voltage drop under low current) and on integrated RTD sensors

DBC substrate is disposed in a temperature controlled chamber so as to impose a homogeneous temperature on the device. Type K thermocouple is used to more closely monitor baseplate temperature. Measurement currents are injected by source meter unit SMU Keithley 2602B for RTD sensors (1mA) and by a current card dedicated to TSEP Vf\_Ict (50mA). As indicated above, "Kelvin" measurement method is used to avoid errors due to connections contribution into voltage drop across sensors. HBM GEN3i acquisition unit (2MEch/s-18bits) is used for recordings. The experimental configuration is presented in figure 7.

Calibration data are obtained through variations of RTD sensor resistance in respect to chip temperature: sensitivity  $S_{\text{RTD}} = 1.57 \text{ mV/}^{\circ}C$  and TCR  $\alpha_{\text{RTD}} = 0.35 \text{ \%/}^{\circ}C$ . TSEP Vf\_Ict calibration curve indicates a sensibility of  $-2.3 \text{ mV/}^{\circ}C$ .

Fig. 3. DBC sensor calibration curve

Fig. 4. Vf\_Ict TSEP calibration curve

#### B. Temperature measurements under constant power dissipation

#### 1) Measurement principle with Vf\_Ict TSEP

TSEP Vf\_Ict is used to indirectly estimate junction temperature of the power diode. A linear variation of forward voltage across PN junction drop is observed by low current injection with sensitivity about  $-2mV/^{\circ}C$  (Figure 6). It has been shown that estimated temperature with Vf\_Ict is close to average junction temperature of power diode [13].

In constant power dissipation conditions define by the test bench (Figure 7), a power current  $I_p$  is injected into the diode to reach thermal steady state. Power current is then replaced by measurement current  $I_m$  used in previous calibration (50mA). Cooling curve of the diode is recorded through forward voltage drop variations. Initial temperature Tj0 at the end of power current injection is then calculated using square root time based extrapolation on linear part of the cooling curve. Doing so, transient fluctuation effects which are prominent during some hundreds of  $\mu$ s are avoided.

Fig. 5. Schematic of test bench

#### 2) Power injection circuitry

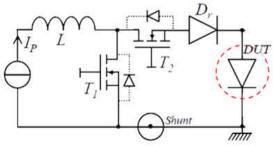

Experimental circuitry used for power current injection was developed as part of the work of Thollin and coll. [17]. In Figure 8, instrumented chip is the device under test (DUT). Switches T1 and T2 serve to control sequentially the direct power current injected into the DUT. Measuring non-inductive shunt (LEMSYS  $1m\Omega$ ) precisely sense power current with high bandwidth (2MHz).

Fig. 6. Power injection circuitry [17]

#### 3) Measurement procedure

DBC substrate on which instrumented power chip is soldered is mounted on a cooling system at constant controlled temperature (30°C) thanks to heating circulator Julabo MC-26. The baseplate temperature is monitored with type K thermocouple placed in center under the substrate. Test bench is presented in Figure 9.

Power current, up to 50 A, is injected in the diode during approximately one minute to reach thermal steady state. Switch T1 command order stops power injection and starts diode cooling curve and RTD sensor voltage recording by HBM acquisition unit for 1ms (with a data portion of 200µs recorded before power injection end).

#### Fig. 7. Experimental test bench

Power injection interruption generates a disturbance on measurement signals for up to 20µs. It is important to remove the data recorded on this time range where disturbance effects are important. Every measuring point is ten times repeated to ensure good repeatability and average values are calculated for every current level.

#### 4) Temperature sensor data treatment

Sensor data processing allows calculating RTD temperature just before power injection interruption. To avoid transient effects, calculation is made with samples recorded between 200µs and 20µs before power interruption. Average value on 360 samples is then used to calculate RTD sensor temperature according to calibration curve.

#### 5) Vf\_Ict TSEP data treatment

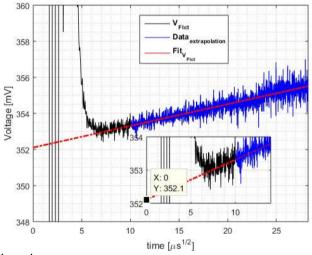

For every power lever, TSEP Vf\_Ict data processing gives initial temperature  $T_{j0}$  of diode at the end of the current injection (time=0s). Linear extrapolation equation in square root of time (Figure10) is used to estimate voltage Vf0 before recovering power diode temperature thanks to its calibration equation [20].

Fig.8. Data extrapolation of forward voltage drop

#### 6) IR thermography measurements

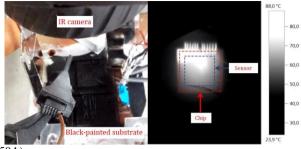

Additional measurement is made with an infrared camera (Testo 875-2i). The device under test is black-painted with hightemperature paint (Motip 0431) to improve chip surface emissivity up to an average value  $\varepsilon_{moy} = 0.95$ . DBC substrate is then hardbaked to 160°C during 60 minutes using a hotplate. IR camera calibration is performed on the same test bench between 30°C and 70°C having painted the substrate and without power current injection. Calibration temperature is limited to 70°C by heating circulator Julabo MC-26.

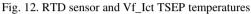

During heating phases, two averaged temperatures are calculated thanks to infrared camera (Figure 11). First, sensor temperature is estimated as an averaged temperature of central area  $T_{IR1}$  of the instrumented chip (sensor area, Figure 11), where the RTD sensor is located. Then, power diode active part temperature  $T_{IR2}$  is calculated as an averaged temperature of top metallization of the diode (chip area, Figure 11).

Fig. 9. Thermography measurement (Ip=50A)

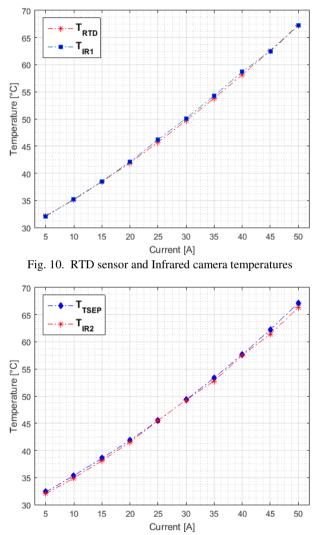

As depicted in Figures 12 and 13, the measurement results with the infrared camera strengthen those performed thanks to RTD sensor and TSEP Vf\_Ict in terms of temperature differences. Maximum temperature deviation is lower than 0.6°C throughout the range of injected power current.

Fig. 11. Vf\_Ict TSEP and infrared camera temperatures

#### 7) Experimental results comparaison

For power current higher than 15A, RTD sensor temperature is superior to temperature estimated by TSEP Vf\_Ict with a maximal difference of 0.5°C (Figure 14).

The RTD sensor covers 83% of the top metal layer surface of the power diode. Averaged temperature value, calculated with TSEP Vf\_Ict is lower, in particular because temperature is hotter in the center of the chip than on edges. Figure 14 illustrates temperature distribution for power current of 50A. We draw the temperature along a diagonal on the chip and we observe well that edges are appreciably colder, compared to RTD sensor area in the chip. Consequently, temperature averaged value of the sensor calculated on this area is higher than that given by TSEP Vf\_Ict (Figure 15).

Fig. 13. Temperature repartition on top surface of instrumented chip

Maximum standard deviations for every test point are of the order of 0.2°C, what shows a low difference around the average value of the temperature for every level of injected power current and thus good measurement repeatability.

#### C. Temperature measurements under switching conditions

In addition to validation under constant power dissipation which provided good results, it is necessary to evaluate the RTD sensor performance under switching conditions and thus to meet real operating condition requirements.

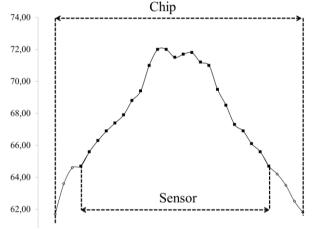

#### 1) Experimental test bench

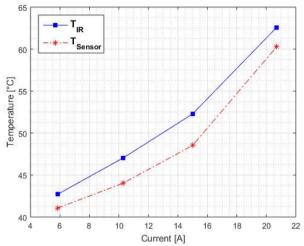

A second part of validating RTDs sensors is performed under switching conditions into buck converter configuration (Fig. 16). The temperature measured by RTD sensor is compared to mean temperature of sensor area given by IR camera, according to conditions described in III.A.6. RTD sensor temperature is estimated as an averaged temperature of central area  $T_{IR}$  of the instrumented chip (sensor area, Figure 11).

The buck converter is connected to a load supplied with mean current up to 20A. The switching frequency is set to 10 kHz with a duty cycle of 50%, a DC voltage of 100V (Vbus) and an electric charge composed of an inductor L of 820 $\mu$ H and a 10  $\Omega$  maximum resistor. The external thermal conditions are the same than those previously used in constant power dissipation validation. The DBC substrate is attached to a cooling system at constant controlled temperature (30°C) thanks to heating circulator Julabo MC-26.

Fig. 14. Buck converter test bench

#### 2) Temperature measurements

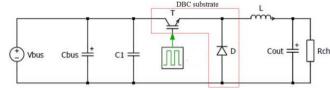

In this configuration, the temperature of the instrumented power diode is evaluated using the integrated RTD sensor and infrared camera. Sensor Data are recorded with HBM acquisition unit during 1ms in thermal stady state conditions, matching four switching periods. Four power current levels are successively used in order to evaluate the integrated sensor performances.

| Current [A] | T_IR [°C] | T_sensor [°C] | ∆T[°C] |

|-------------|-----------|---------------|--------|

| 5.9         | 42.7      | 41.1          | 1.6    |

| 10.3        | 47.1      | 44.0          | 3.0    |

| 15.0        | 52.3      | 48.5          | 3.8    |

| 20.7        | 62.6      | 60.3          | 2.3    |

Fig. 15. Temperature measurements under switching conditions

The results obtained in switching conditions indicate a difference between IR mean temperature and RTD sensor temperature lower than 4°C. As illustrated in figure 17, a relatively satisfactory correlation is observed between mean IR temperature and RTD sensor temperature. In switching configuration, integrated RTD sensor is thus able to measure chip temperature, albeit further investigation will be performed to investigate the effects of switching parameters variations, namely duty cycle, switching frequency and DC voltage.

#### IV. CONCLUSION

As a result of this study, researches focused on integration of a temperature sensor in a power diode allowed to validate technological realization process. Indeed, functional sensors were integrated on off-the-shelf chips thanks to a simple and economic microelectronic process.

Soldering the instrumented chip on a DBC substrate allowed then to compare RTD sensor data with those obtained with a robust ThermoSensitive Electrical Parameter (forward voltage drop of power diode under a low current Vf\_Ict) which is widely used in industry and research, and with infrared thermography measurement. In power dissipation configuration, temperature differences between RTD sensor temperature and that estimated by TSEP Vf\_Ict on one hand and between the RTD sensor temperature and that estimated by infrared camera on the other hand are lower than 0.5°C. The temperature difference between IR mean temperature and RTD sensor temperature is lower than 4°C under switching conditions.

#### V. PERSPECTIVES

In future work, experimental evaluation of good functioning of RTD temperature sensor will be completed by electrothermal simulation to estimate the integration impact on the instrumented chip behavior.

Finally, implementation of temperature measurement by RTD sensor integration in a power diode being a first validation step of this approach, the technological process so validated will enable integration of new sensor versions into IGBTs transistors. We can so realize power modules with all chips being instrumented, using it as an adapted tool to validate TSEPs in operating conditions.

#### ACKNOWLEDGMENT

Authors would like to thank ANR agency (MEMPHIS ANR-13-PRGE-0005-01 PROGELEC project) for financial support brought for these researches. These works were also partially supported by French network RENATECH for the realization of instrumented chips in the Plateforme Technologique Amont (PTA) de Grenoble.

Authors are grateful to Jean-Christophe Crebier, Raha Vafaei and Benoit Thollin for their assistance with chip design, Cyril Buttay, Vincent Bley and DeepConcept Company for their help in technological process and packaging, and Florian Dumas for mechanical realizations.

#### REFERENCES

- [1] E. Wolfgang, "Examples for failures in power electronics systems, "presented at ECPE Tutorial 'Rel. Power Electron. Syst.', Nuremberg, Germany, Apr. 2007.

- [2] Automotive Electronic Systems Reliability Standards, "Handbook for robustness validation of automotive electrical/electronic modules", SAE International, J1211\_201211, Jun.2012.

Tab 3.Mean temperatures under switching conditions

- [3] S. Yang, A. Bryant, P. Mawby, S. Member, D. Xiang, L. Ran, S. Member, P. Tavner, and S. Member, "An Industry-Based Survey of Reliability in Power Electronic Converters", IEEE Transactions on industry applications, vol. 47, no. 3, pp. 1441–1451, 2011.

- [4] Y. Avenas, L. Dupont, N. Baker, H. Zara and F. Barruel, "Condition Monitoring: A Decade of Proposed Techniques," in *IEEE Industrial Electronics Magazine*, vol. 9, no. 4, pp. 22-36, Dec. 2015.

- [5] M. K. Kim and S. W. Yoon, "Novel built-in sensor for in-situ monitoring of temperature and thermal stress in power modules," 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, 2015, pp. 4513-4519.

- [6] D.C. Katsis, J.D. Van Wyk, "Void-induced thermal impedance in power semiconductor modules: some transient temperature effects", IEEE Trans. Ind. Appl., vol.39, no.5, pp. 1239-1246, Sept/Oct 2003.

- [7] E-R. Motto, J-F. Donlon, "IGBT module with user accessible on-chip current and temperature sensors", 2012 27th Annual IEEE Applied Power Electronics Conference and Exposition (APEC), pp. 1-6.

- [8] R. Schmidt, U. Scheuermann, "Using the chip as a temperature sensor The influence of steep lateral temperature gradients on the Vce(T)-measurement", 13th Europ. Conf. on Power Electronics and App., 2009.

- Y. Avenas, L. Dupont, and Z. Khatir, "Temperature Measurement of Power Semiconductor Devices by Thermo-Sensitive Electrical Parameters—A Review," *IEEE Trans. Power Electron.*, vol. 27, no. 6, pp. 3081–3092, 2012.

- [10] N. Baker, M. Liserre, L. Dupont, Y. Avenas, "Improved Reliability of Power Modules: A Review of Online Junction Temperature Measurement Methods", IEEE Industrial Electronics Magazine, vol.8, no.3, pp.17-27, 2014.

- [11] N. Baker, M. Liserre, L. Dupont and Y. Avenas, "Junction temperature measurements via thermo-sensitive electrical parameters and their application to condition monitoring and active thermal control of power converters", Industrial Electronics Society, IECON 2013 - 39th Annual Conference of the IEEE, Vienna, 2013, pp. 942-948.

- [12] X. Perpiñà, J.F. Serviere, J. Saiz, D. Barlini, M. Mermet-Guyennet, J. Millán, "Temperature measurement on series resistance and devices in power packs based on on-state voltage drop monitoring at high current", Microelectron. Reliabil., vol 46, pp. 1834-1839, 2006.

- [13] L. Dupont and Y. Avenas, "Preliminary Evaluation of Thermo-Sensitive Electrical Parameters Based on the Forward Voltage for Online Chip Temperature Measurements of IGBT Devices," in IEEE Transactions on Industry Applications, vol. 51, no. 6, pp. 4688-4698, Nov.-Dec. 2015.

- [14] N. Baker, F. Iannuzzo, S. Munk-nielsen, L. Dupont, and S. Umr, "Experimental Evaluation of IGBT Junction Temperature Measurement via a Modified-V CE ( ΔVCE \_ ΔVGE ) Method with Series Resistance Removal," pp. 7–12, 2016.

- [15] M. Denk and M. Bakran, "Junction Temperature Measurement during Inverter Operation using a T J -IGBT-Driver," no. May, pp. 19–21, 2015.

- [16] B. Tian, W. Qiao, Z. Wang, T. Gachovska, and J. L. Hudgins, "Monitoring IGBT's Health Condition via Junction Temperature Variations," pp. 2550– 2555, 2014.

- [17] B. Thollin, L. Dupont, Z. Khatir, Y. Avenas, J. C. Crebier and P. O. Jeannin, "Partial thermal impedance measurement for die interconnection characterization by a microsecond "pulsed heating curve technique"," Power Electronics and Applications (EPE), 2013 15th European Conference on, Lille, 2013, pp. 1-10.

- [18] X. Jorda, X. Perpina, M. Vellvehi, F. Madrid, D. Flores, et al.."Low- cost and versatile thermal test chip for power assemblies assessment and thermometric calibration purposes". Applied Thermal Engineering, Elsevier, 2011, 31 (10), pp.1664.

- [19] Cutnell, John & Johnson, Kenneth. Physics 3rd Edition. New York: John Wiley & Sons Inc., 1995.

- [20] D. L. Blackburn and F. F. Oettinger, "Transient Thermal Response Measurements of Power Transistors," in IEEE Transactions on Industrial Electronics and Control Instrumentation, vol. IECI-22, no. 2, pp. 134-141, May 1975.