## Integrated shadow mask method for patterning small molecule organic semiconductors

Stijn De Vusser,<sup>a)</sup> Soeren Steudel,<sup>a)</sup> Kris Myny, Jan Genoe, and Paul Heremans<sup>a)</sup> *IMEC-MCP/PME, Kapeldreef 75, B-3001 Leuven, Belgium*

(Received 4 November 2005; accepted 12 February 2006; published online 7 March 2006)

We have developed a simple and efficient method for patterning small molecule semiconductors for applications in the field of organic electronics. In our approach, a profile is created using a single layer of photoresist, defining the regions where the organic semiconductor is to be deposited. Subsequent deposition of a small molecule semiconductor results in a discontinuity of the semiconductor film at the photoresist edge. The resulting transistor characteristics have an off current that is systematically below 1 pA. We demonstrate both *p*-type and *n*-type organic thin-film transistors using this method, using pentacene and copper hexadecafluorophthalocyanine ( $F_{16}CuPc$ ), respectively. © 2006 American Institute of Physics. [DOI: 10.1063/1.2182008]

Organic electronics is a field that has attracted the attention of both industrial and academic research groups. The performance of both polymeric and small molecule organic thin-film transistors (OTFTs) has improved considerably in the last few years. Several research groups have reported on pentacene OTFTs with field-effect mobilities  $\mu$  higher than 1 cm<sup>2</sup>/V s, bringing the performance of these devices at the same level as or even higher than that of amorphous silicon (*a*-Si:H) TFTs.<sup>1-4</sup>

Display applications are a particularly important driver for the continuing efforts in the field of organic electronics. Displays using OTFTs as the driving backplane have been realized, both on glass<sup>5</sup> and on flexible polymeric substrates.<sup>6,7</sup> In order to limit contrast degradation of the display, the off current of the driving transistor needs to be in the range of 10 pA or lower.<sup>8</sup> In other applications of organic electronics, like the fabrication of digital logic circuits, it is desired to be able to switch the OTFT completely off as well, for reasons of stability (reduction of cross talk) and power consumption.

Currents in the range of a few pA cannot be reached without patterning the organic semiconductor. For pentacene OTFTs, the off-current  $I_{off}$  of an unpatterned device is typically in the range of 1–10 nA. This clearly demonstrates the need for patterning the semiconductor. Patterning leads to the elimination of parasitic leakage paths, resulting in a significant decrease of  $I_{off}$ . At the same time, one should ensure that the patterning process does not lead to a degradation of the field-effect mobility  $\mu$  and the threshold voltage  $V_T$ , as these parameters (among others) determine the on current of the device.

One method to pattern the organic semiconductor is by photolithographically defining a photoresist profile after the organic semiconductor deposition. This has been realized with a water-soluble poly(vinyl alcohol)-based photoresist,<sup>9</sup> as well as with a regular solvent-based photoresist, using parylene as a coating between the organic semiconductor and the photoresist.<sup>10</sup> A subsequent dry etch step results in an effective patterning of the active areas of the OTFTs.

Another method, avoiding the etch step of the organic semiconductor, consists of evaporating the semiconductor through a shadow mask.<sup>11</sup> Aligning the shadow mask to the existing OTFT substrate, however, requires special equipment.

In order to overcome these problems, one could create a reentrant profile prior to the deposition of the semiconductor. This in fact forms a shadow mask that is integrated with the substrate. Upon vacuum deposition, the organic semiconductor breaks across the profile, resulting in isolated OTFT active areas. This method has been demonstrated using a double-layer photoresist profile,<sup>12</sup> as well as using a patterned multilayer of dense SiO<sub>2</sub>, porous SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub>.<sup>13</sup>

We have realized an integrated shadow mask by patterning one single layer of photoresist. Devices were processed on a highly doped Si wafer, acting as the substrate and the gate electrode. The gate dielectric was formed by thermally growing a layer of 100 nm SiO<sub>2</sub>. The source and drain electrodes consist of 20 nm of Au, patterned by photolithography and lift-off. Subsequently, a layer of the negative photoresist SU-8 25 (purchased from MicroChem Corp.) was spincoated. Processing of the SU-8 25 leads to a patterned layer of about 20  $\mu$ m thickness. Subsequent to the SU-8 processing, the substrate was thoroughly cleaned and treated with octadecyl trichlorosilane and dodecanethiol self-assembled monolayers. As a last step, a layer of 30 nm purified pentacene was deposited in ultrahigh vacuum ( $p=10^{-8}$  Torr). The deposition flux was 0.25 Å/s, and the substrate temperature was 65 °C.

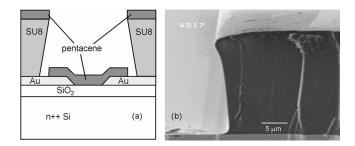

FIG. 1. (a) Schematic cross section of an OTFT with patterned pentacene layer; (b) scanning electron microscope image of a cross section of the integrated shadow mask.

<sup>&</sup>lt;sup>a)</sup>Also with: Electrical Engineering Department, Katholieke Universiteit Leuven, Leuven, Belgium; electronic mail: stijn.devusser@imec.be

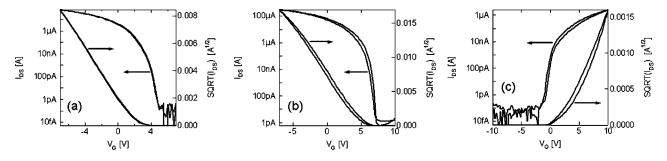

FIG. 2.  $I_D - V_G$  measurement of OTFTs patterned by an SU-8 25 profile: (a) pentacene OTFT processed on Si ( $V_{DS} = -7$  V; W/L = 400/5;  $\mu = 0.67$  cm<sup>2</sup>/V s;  $V_T = 2$  V; S = 0.22 V/dec;  $I_{on}/I_{off} = 8.10^8$ ); (b) pentacene OTFT processed on glass ( $V_{DS} = -7$  V; W/L = 5000/10;  $\mu = 0.22$  cm<sup>2</sup>/V s;  $V_T = 5$  V; S = 0.17 V/dec;  $I_{on}/I_{off} = 5.10^8$ ); (c) F<sub>16</sub>CuPc OTFT processed on Si ( $V_{DS} = 10$  V; W/L = 5000/10;  $\mu = 5.10^{-3}$  cm<sup>2</sup>/V s;  $V_T = 2.5$  V; S = 0.44 V/dec;  $I_{on}/I_{off} = 5.10^8$ ).

The cross section of the device is schematically shown in Fig. 1(a). As shown by the cross-section scanning electron microscope image in Fig. 1(b), it is clear that the walls of the photoresist are slightly reentrant, which is typical for negative photoresists.<sup>14</sup> The cleaning and surface treatment of the substrate have no influence on the profile. The photoresist profile effectively prohibits the formation of a continuous film during the semiconductor deposition. In other words, the SU-8 25 layer breaks the semiconductor layer, resulting in patterned active areas. This can be verified in Fig. 1(b), showing a layer of 30 nm of pentacene evaporated through the shadow mask. As can be seen, the edge of the pentacene active area on the substrate is clearly visible, demonstrating the effectiveness of this patterning method. The highest temperature used in the processing of SU-8 25 is 95 °C. The low thermal budget of this patterning method makes it compatible with production on flexible substrates.

We have measured OTFTs that were fabricated following the described method. After the deposition of pentacene, the samples were transported through air and measured in a N<sub>2</sub> atmosphere using an Agilent 4156C parameter analyzer. The transistor parameters were extracted from the transfer curve in the saturation regime. Typical values for the fieldeffect mobility  $\mu$  were in the range of 0.6 cm<sup>2</sup>/V s. The threshold voltage  $V_T$  was typically 2 V.  $I_{off}$  was systematically below 1 pA, being the noise level of our measurement setup. The on-off current ratio  $I_{on}/I_{off}$  was always higher than  $10^8$ . The average subthreshold slope was in the range of 0.2 V/dec. The hysteresis was negligibly small. Figure 2(a) shows a representative transfer curve of a pentacene OTFT in the saturation regime.

The patterning method was also applied to a pentacene OTFT processed on glass. Devices were processed on Corning EAGLE<sup>2000</sup> glass substrates. The gate consists of a layer of 20 nm of TiW, patterned by optical photolithography and lift-off; 100 nm of SiO<sub>2</sub> was sputtered to act as the gate dielectric. Vertical interconnects were defined by wet etching. Source and drain electrodes consist of 25 nm of Au. Subsequently, the integrated shadow mask and the pentacene layer were deposited as described above. After the SU-8 processing and the pentacene deposition, not a single processing step was taken. As can be verified in Fig. 2(b), the general performance of an OTFT processed on glass is comparable to a device processed on Si. In the context of this letter, it should be specifically noted that there is virtually no difference in  $I_{on}/I_{off}$  between the two devices. Like the OTFTs processed on Si, the devices processed on glass show a remarkably steep subthreshold slope S, being systematically in the range of 0.2 V/dec. It can be noticed that the off current of this device is not limited by the noise level of our setup. This is attributed to the fact that the gate current of an OTFT processed on glass is in the range of 1-10 pA, while that of an OTFT processed on Si is below 1 pA. Indeed, thermally grown SiO<sub>2</sub> is superior to the low-temperature sputtered SiO<sub>2</sub> we used. Nevertheless, an off current in the range of 1 pA is an excellent figure.

In order to demonstrate the general applicability of this patterning method, we have also fabricated *n*-type OTFTs. The *n*-type organic semiconductor copper hexadecafluorophthalocyanine  $(F_{16}CuPc)^{15}$  was deposited on a Si substrate that was prepared in the same way as for the case of pentacene, as described above. Patterned  $F_{16}CuPc$  OTFTs were measured in a N<sub>2</sub> glovebox, immediately after deposition. A typical transfer curve of an *n*-type OTFT is shown in Fig. 2(c). It can be seen that  $I_{off}$  is below 1 pA, showing that the *n*-type semiconductor  $F_{16}CuPc$  is patterned as effectively as the *p*-type semiconductor pentacene.

It should be mentioned that the patterning of an *n*-type organic semiconductor is difficult using a lithography and etching process, because of the rapid degradation of the semiconductor in the presence of air and moisture.<sup>16</sup> Hence, the patterning method proposed in this letter is a unique technology, as it allows for the patterning of small molecule *n*-type organic semiconductors with photolithographic resolution, while at the same time avoiding degradation.

In conclusion, we have demonstrated a simple method for patterning small molecule organic semiconductors. The method consists of patterning a thick and reentrant profile of a single negative photoresist (SU-8 25) prior to the semiconductor deposition. Upon deposition, it is not possible for the semiconductor to grow as a continuous layer on the photoresist walls. This effectively results in a patterned semiconductor film in the active areas of the OTFTs. The method provides a particularly simple way for patterning *n*-type small molecule organic semiconductors, since all possible sources of degradation are avoided. Finally, the thermal budget of the method is compatible with production techniques on flexible substrates.

This work is partially supported by the EU-funded Integrated Project POLYAPPLY (IST No. 507143) (http:// www.polyapply.org).

- <sup>2</sup>H. Klauk, M. Halik, U. Zschieschang, G. Schmid, W. Radlik, and W. Weber, J. Appl. Phys. **92**, 5259 (2002).

- <sup>3</sup>T. W. Kelley, L. D. Boardman, T. D. Dunbar, D. V. Muyres, M. J. Peller-

<sup>&</sup>lt;sup>1</sup>D. J. Gundlach, H. Klauk, C. D. Sheraw, C. C. Kuo, J. R. Huang, and T. N. Jackson, 1999 Tech. Dig. - Int. Electron Devices Meet. **1999**, 111 (1999).

- <sup>4</sup>T. W. Kelley, D. V. Muyres, P. F. Baude, T. P. Smith, and T. D. Jones, Mater. Res. Soc. Symp. Proc. **771**, L6.5.1 (2003).

- <sup>5</sup>H. E. A. Huitema, G. H. Gelinck, J. B. P. H. van der Putten, K. E. Kuijk, C. M. Hart, E. Cantatore, P. T. Herwig, A. J. J. M. van Breemen, and D. M. de Leeuw, Nature (London) **414**, 599 (2001).

- <sup>6</sup>C. D. Sheraw, L. Zhou, J. R. Huang, D. J. Gundlach, T. N. Jackson, M. G. Kane, I. G. Hill, M. S. Hammond, J. Campi, B. K. Greening, J. Francl, and J. West, Appl. Phys. Lett. **80**, 1088 (2002).

- <sup>7</sup>G. H. Gelinck, H. E. A. Huitema, E. van Veenendaal, E. Cantatore, L. Schrijnemakers, J. B. P. H. van der Putten, T. C. T. Geuns, M. Beenhakkers, J. B. Giesbers, B.-H. Huisman, E. J. Meijer, E. M. Benito, F. J. Touwslager, A. W. Marsman, B. J. E. Van Rens, and D. M. de Leeuw, Nat. Mater. **3**, 106 (2004).

- <sup>8</sup>H. E. A. Huitema, G. H. Gelinck, J. B. P. H. van der Putten, K. E. Kuijk, K. M. Hart, E. Cantatore, and D. M. de Leeuw, Adv. Mater. (Weinheim, Ger.) 14, 1201 (2002).

- <sup>9</sup>M. G. Kane, J. Campi, M. S. Hammond, F. P. Cuomo, B. Greening, C. D. Sheraw, J. A. Nichols, D. J. Gundlach, J. R. Huang, C. C. Kuo, L. Jia, H. Klauk, and T. N. Jackson, IEEE Electron Device Lett. **21**, 534 (2000).

- <sup>10</sup>I. Kymissis, C. D. Dimitrakopoulos, and S. Purushothaman, J. Vac. Sci. Technol. B **20**, 956 (2002).

- <sup>11</sup>P. F. Baude, D. A. Ender, M. A. Haase, T. W. Kelley, D. V. Muyres, and S. D. Theiss, Appl. Phys. Lett. **82**, 3964 (2003).

- <sup>12</sup>H. Klauk, D. J. Gundlach, M. Bonse, C. C. Kuo, and T. N. Jackson, Appl. Phys. Lett. **76**, 1692 (2000).

- <sup>13</sup>C. Py, D. Roth, I. Lévesque, J. Stapledon, and A. Donat-Bouillud, Synth. Met. **122**, 225 (2001).

- <sup>14</sup>J. M. Shaw, J. D. Gelorme, N. C. LaBianca, W. E. Conley, and S. J. Holmes, IBM J. Res. Dev. **41**, 81 (1997).

- <sup>15</sup>Z. Bao, A. J. Lovinger, and J. Brown, J. Am. Chem. Soc. **120**, 207 (1998).

<sup>16</sup>C. R. Newman, C. D. Frisbie, D. A. da Silva Filho, J.-L. Brédas, P. C. Ewbank, and K. R. Mann, Chem. Mater. **16**, 4436 (2004).

ite, and T. P. Smith, J. Phys. Chem. B 107, 5877 (2003).