Received January 18, 2019, accepted February 8, 2019, date of publication February 25, 2019, date of current version March 12, 2019.

Digital Object Identifier 10.1109/ACCESS.2019.2901441

# Interval Robust Controller to Minimize Oscillations Effects Caused by Constant Power Load in a DC Multi-Converter Buck-Buck System

KEVIN EDUARDO LUCAS MARCILLO<sup>®1,2</sup>, (Member, IEEE),

DOUGLAS ANTONIO PLAZA GUINGLA<sup>®1</sup>, (Member, IEEE), WALTER BARRA, Jr.<sup>2</sup>,

RENAN LANDAU PAIVA DE MEDEIROS<sup>3</sup>, ERICK MELO ROCHA<sup>2</sup>,

DAVID ALEJANDRO VACA BENAVIDES<sup>®1</sup>, (Member, IEEE),

AND FABRICIO GONZALEZ NOGUEIRA<sup>4</sup>

<sup>1</sup>Facultad de Ingeniería Eléctrica y Computación, Escuela Superior Politécnica del Litoral, Campus Gustavo Galindo, Guayaquil 09-01-5863, Ecuador

<sup>2</sup>Faculty of Electrical Engineering, Federal University of Pará, Campus do Guamá, Belém 66075-900, Brazil

Corresponding author: Kevin Eduardo Lucas Marcillo (keveluca@espol.edu.ec)

This work was supported in part by the Personnel Improvement Coordination of Superior Level-CAPES Grant, and in part by the Escuela Superior Politécnica del Litoral.

**ABSTRACT** Multi-converter electronic systems are becoming widely used in many industrial applications; therefore, the stability of the whole system is a big concern to the real-world power supplies applications. A multi-converter system comprised of cascaded converters has a basic configuration that consists of two or more converters in series connection, where the first is a source converter that maintains a regulated dc voltage on the intermediate bus while remaining are load converters that convert the intermediate bus voltage to the tightly regulated outputs for the next system stage or load. Instability in cascaded systems may occur due to the constant power load (CPL), which is a behavior of the tightly regulated converters. CPLs exhibit incremental negative resistance behavior causing a high risk of instability in interconnected converters. In addition, there are other problems apart from the CPL, e.g., non-linearities due to the inductive element and uncertainties due to the imprecision of a mathematical model of dc-dc converters. Aiming to effectively mitigate oscillations effects in the output of source converter loaded with a CPL, in this paper, an interval robust controller, by linear programming based on Kharitonov rectangle, is proposed to regulate the output of source converter. Several tests were developed by using an experimental plant and simulation models when the multi-converter buck-buck system is subjected to a variation of power reference. Both simulation and experimental results show the effectiveness of the proposed controller. Furthermore, the performance indices computed from the experimental data show that the proposed controller outperforms a classical control technique.

**INDEX TERMS** Constant power load (CPL), multi-converter buck-buck system, parametric uncertainties, robust control based on Kharitonov rectangle, mitigation oscillations in multi-converter buck-buck system.

#### I. INTRODUCTION

Nowadays, multi-converter electronic systems are increasingly used in industrial applications due to their simplicity in structure, high power efficiency, low cost and high reliability [1], [2]. Some modern industries, whose processes

The associate editor coordinating the review of this manuscript and approving it for publication was Ho Ching Iu.

demand high dynamic performance, have applied different types of converters for applications such as in variable speed DC motor drivers [3], renewable energy systems [4]–[6], transportation systems [7], [8], hybrid energy storage system [9], [10], communications systems [11]. In several of these applications, converters are controlled by switching through Pulse Width-Modulation (PWM) to transfer power from a power source to loads having a constant

<sup>&</sup>lt;sup>3</sup>Department of Electricity, Federal University of Amazonas, Manaus 69080-900, Brazil

<sup>&</sup>lt;sup>4</sup>Electrical Engineering Department, Federal University of Ceará, Fortaleza 60020-181, Brazil

power characteristic. Because of switching, the converters have some inherent nonlinear behaviors, e.g., high frequency of switching, increasing harmonics in the system, current and voltage distortion, and instabilities occur due this effects [12], [13]. Therefore, it is a challenging task to ensure the stability, transient performance and higher efficiency of such converters [13].

A multi-converter system comprised of cascaded converters has a basic configuration that consists of two converters in series connection, where the first is a source converter while the second one is a load converter. The source converter maintains a regulated DC voltage on the intermediate bus, and the load converter transforms the intermediate bus voltage to tightly regulated outputs for the next system stage or load. In a cascaded buck converter system a large variety of dynamic and static interactions are possible and these can lead to irregular behavior of a converter, a group of converters or the whole system.

When a converter tightly regulates its output, it behaves as a Constant Power Load (CPL), thereby, in cascaded systems, load converter acts as a CPL when it is tightly regulated, its dynamic response is faster than the dynamic response of the source converter and its switching operation frequency is faster than source converter [14]. If the source converter is faster than the load converter, then it will compensate for disturbances and will regulate its output before the feedback loop of the load converter reacts to disturbances. Therefore, the load converter will not act as a perfect CPL for the feeding converter [15]–[21].

Different from a resistive load, CPL is a nonlinear load with variable negative impedance characteristics, i.e., the input current increases/decreases with a decrease/increase in its terminal voltage [15]–[21]. Because of the negative impedance characteristics of CPL, the system may become unstable, which may lead the system into oscillation or failure, and stress or damage the system equipment when feeding a CPL [17]–[21]. For this issue, CPLs are receiving more attention of researchers to give solutions aiming to cancel or compensate the negative effects of CPL.

Traditionally, the stability analysis and controller design of cascaded DC-DC converters is carried out by using the impedance criterion applied to averaged and linearized models [19]–[22]. The load converter under a tight control is conventionally modeled CPL for stability analysis or for controller design [19]–[22].

In order to mitigate the destabilizing effect of CPL, several methods have been proposed [23], such as passive and active damping [24]–[26], Lyapunov redesign control [8], nonlinear feedback linearization [27]–[29], Sliding Mode Control (SMC) [30]–[32], fuzzy control [33], Model Predictive Control (MPC) [34], [35] and robust control [36], [37]. However, there are other problems apart from the CPL, e.g., uncertainties present in the system parameters, which may lead to performance degradation [38]. In literature can be found control strategies applied to DC-DC power converters that deal with parametric uncertainties [39]–[41].

In research on dynamic systems with parametric uncertainties, the techniques that deal with this problem have been studied extensively over the last 40 years [42], [43].

To the best of the authors' knowledge, it seems that most papers published so far focus on mitigating the destabilizing effect of CPL without considering the uncertainties present in the system parameters. Therefore, studies reporting robust parametric methodologies for DC-DC converters feeding a CPL to mitigate oscillations effects caused by CPL still scarce in literature. However, in [39], a novel multivariable robust parametric technique was used for minimizing coupling effect in single inductor multiple output DC-DC converter operating in continuous conduction mode. Moreover, in [40] and [41], the use of Robust Parametric Control (RPC) techniques is proposed to stabilize oscillations at the output of a buck converter caused by parametric uncertainties.

Recently, the study developed in [44] addressed the important problem of parametric uncertainties in DC-DC converters by using  $\mu$  analysis. However, their approach is focused only on a posterior analysis of system stability. The important subject of robust controller synthesis has been not addressed. In contrast, this paper is focused in the problem of robust controller synthesis, being thoroughly addressed from the onset, providing a practical and simple robust controller design algorithm with sufficient level of the detail in order to be easily implemented.

In this context, this paper proposes a robust controller based on RPC theory. The proposed controller is applied to source converter in order to mitigate oscillations effects due to CPL in multi-converter buck-buck (MCBB) system, aiming to reduce the control effort when the system is submitted to variation of power reference.

The main contributions of this work are briefly summarized in that following:

- By using the proposed robust technique, structured uncertainties of the type hyperbox, considering interval parametric type, are taking into account from the outset in the controller design process, incorporating available information about components (resistors, inductors, and capacitors) tolerances or defined by designer.

- The proposed robust technique leads to easy-toimplement controllers having fixed low-order structure, allowing the deployment of standard industry structures such as PID and Lead-Lag.

- Aiming to evaluate the performance of the proposed robust methodology under the instability problem caused by a CPL, the proposed robust methodology is compared with classical methodology carrying out several experimental and simulation tests. The performance index (ISE) is computed to analyze the control methodologies compared in this work. The results show the proposed methodology outperforms the other approach.

The remainder of this paper is organized as follows. Section II presents a brief review about the multi-converter buck-buck system; Section III presents a brief review about

parametric robust control background; Section IV proposes a mathematical model for multi-converter buck-buck system; Section V presents the proposed design methodology for interval robust controller; Section VI presents the experimental and simulation environment, describing the experiments to be performed in this paper; Section VII presents an assessment of the simulation results and experimental data. Finally, Section VIII presents the main conclusions.

#### II. SYSTEM DESCRIPTION AND PROBLEM FORMULATION

Multi-converter systems comprised of cascaded converters have a basic configuration that consists of two or more converters in series connection, where the first is a source converter that maintains a regulated DC voltage on the intermediate bus while remaining are load converters that transform the intermediate bus voltage to tightly regulated outputs for the next system stage or load.

In a cascaded buck converter a large variety of dynamic and static interactions are possible and these can lead to irregular behavior of a converter, a group of converters or the whole system.

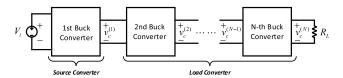

A typical cascaded system with N DC-DC buck converters is shown in Fig. 1, where N represents the quantitative of buck converters.

FIGURE 1. Buck Converters in series connection: Cascaded system with N-converters.

When a power converter tightly regulates its output, it behaves as a CPL [14]. CPLs have a negative incremental resistance, which tends to destabilize the system [19]–[21]. CPL approximation model describe the behavior at the input terminals of the load converter allows to capture its performance in a frequency range where its open-loop gain is high and an input voltage span where its controller is within its dynamic range.

#### A. BUCK CONVERTER WITH CONSTANT POWER LOAD

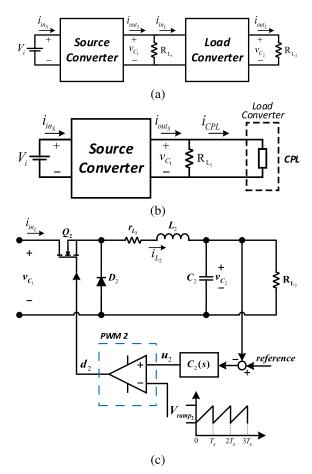

Cascaded buck converter system and its representation with CPL are shown in Figs. 2(a) and 2(b), respectively. It is assumed that the output of the load converter is tightly regulated as shown in Fig. 2(c).

CPLs introduce interesting nonlinear behavior to conventional buck-converter dynamics, but this behavior only exhibit above a certain voltage.

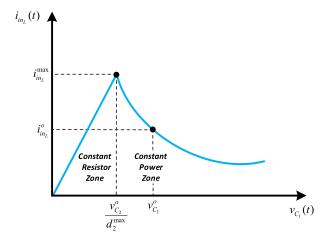

Fig. 3 shows the input "V-I" characteristics of load converter.

When the input voltage of the load converter,  $v_{c_1}$ , is lower than  $(v_{c_2}/d_2^{max})$ , the load converter behavior will be as the resistive load. Therefore, in this range of operation, load converter will be operates in a constant resistor zone (CRZ).

FIGURE 2. Multi-converter buck-buck system. (a) Cascaded system with two power stages. (b) Source converter loaded by a CPL. (c) Tightly regulated load converter.

FIGURE 3. Input "V-I" characteristics of the CPL.

On the other hand, when  $v_{c_1}$  is higher than  $(v_{c_2}/d_2^{max})$ , load converter behavior will be as a CPL, thus, load converter will be operate in a constant power zone (CPZ).

Where  $v_{c_1}^o$  is the input DC voltage of load converter;  $v_{c_2}^o$  is the tightly regulated output voltage of load converter;  $i_{inL}^o$  is the input operation current of load converter;  $i_{inL}^{max}$  is the maximum input current of load converter;  $d_2^{max}$  is the maximum

**IEEE** Access

operating duty cycle of load converter; and  $P_o$  is the operating power of CPL.

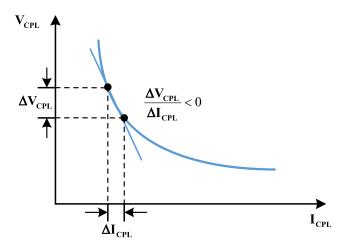

In order to maintain a constant power level, in a DC-DC converter when it acts as a CPL, input current increases when input voltage decreases, and vice versa, thus, the product of the input current and input voltage of the load converter, (i.e.,  $P_o = i_{in_L} v_{c_1}$ ) is a constant. The instantaneous value of the load impedance is positive (i.e.,  $v_{c_1}/i_{in_L} > 0$ ). However, the incremental impedance is always negative (i.e.,  $\Delta v_{c_1}/\Delta i_{in_L} < 0$ ) due to once appearing any disturbance, thus operating point will leave from previous point and never return. This negative incremental impedance has a negative impact on the power quality and stability of system. Fig. 4 shows the negative incremental impedance behavior of CPL.

FIGURE 4. The negative incremental impedance behavior of CPL.

#### B. STABILITY ANALYSIS OF STUDIED SYSTEM

The system, showed in Fig. 2(b), is used to show the instability of a DC-DC converter feeding a CPL. To obtain the large-signal behavior of the load converter, the CPL is represented by a dependent current source [14],  $i_{CPL} = P_o/v_{c_1}$ , so the instantaneous current drawn from source converter is given by

$$i_{out_s}(t) = i_{R_{L_1}}(t) + i_{CPL}(t)$$

$$i_{out_s}(t) = \frac{v_{c_1}(t)}{R_{L_1}} + \frac{P_o}{v_{c_1}(t)}$$

$$i_{out_s} = i_{L_1}$$

(1)

Depending on switching of the source converter, the largesignal model of the converter in continuous conduction mode can be obtained based on the following equations:

$$\begin{cases}

\frac{di_{L_1}}{dt} = -\frac{r_{L_1}}{L_1} i_{L_1} + \frac{1}{L_1} \left( V_i - v_{c_1} \right) \\

\frac{dv_{c_1}}{dt} = \frac{1}{C_1} i_{L_1} - \frac{1}{C_1} \left( \frac{v_{c_1}}{R_{L_1}} + \frac{P_o}{v_{c_1}} \right), \\

\end{cases} 0 < t < d_1 T_{s_1}$$

(2)

$$\begin{cases} \frac{di_{L_{1}}}{dt} = -\frac{r_{L_{1}}}{L_{1}}i_{L_{1}} + \frac{1}{L_{1}}\left(-v_{c_{1}}\right) \\ \frac{dv_{c_{1}}}{dt} = \frac{1}{C_{1}}i_{L_{1}} - \frac{1}{C_{1}}\left(\frac{v_{c_{1}}}{R_{L_{1}}} + \frac{P_{o}}{v_{c_{1}}}\right), \end{cases} d_{1}T_{s_{1}} < t < T_{s_{1}} \end{cases}$$

(3)

where  $d_1$  and  $T_{s_1}$  are the duty cycle and switching period of the source converter, respectively.  $L_1$ ,  $r_{L_1}$ ,  $C_1$  and  $R_{L_1}$  are the plant parameter of source converter.  $V_i$  is the input DC voltage of source converter.  $P_o$  is the output power of load converter that is constant.  $i_{out_s} = i_{L_1}$ .

Using the state-space averaging method [14], [20], the buck converter dynamics can be written as:

$$\begin{cases} \frac{di_{L_1}}{dt} = -\frac{r_{L_1}}{L_1} i_{L_1} + \frac{1}{L_1} \left( V_i d_1 - v_{c_1} \right) \\ \frac{dv_{c_1}}{dt} = \frac{1}{C_1} i_{L_1} - \frac{1}{C_1} \left( \frac{v_{c_1}}{R_{L_1}} + \frac{P_o}{v_{c_1}} \right) \end{cases}$$

(4)

Consider small perturbations in the state variables due to small disturbances in the input voltage and duty cycle

$$\begin{cases} V_{i} = \bar{V}_{i} + \tilde{V}_{i} \\ d_{1} = \bar{d}_{1} + \tilde{d}_{1} \\ v_{c_{1}} = V_{C_{1}} + \tilde{v}_{c_{1}} \\ i_{L_{1}} = I_{L_{1}} + \tilde{i}_{L_{1}} \end{cases}$$

(5)

where,  $\bar{V}_i$ ,  $\bar{d}_1$ ,  $V_{C_1}$  and  $I_{L_1}$  are the average values of  $V_i$ ,  $d_1$ ,  $v_{c_1}$  and  $i_{L_1}$ , respectively.

Substituting (5) in (4) and neglecting the internal resistance of the inductor to simplify the calculations, the buck converter model becomes

$$\begin{cases} \frac{d\tilde{i}_{L_1}}{dt} = \frac{1}{L_1} \left( \bar{V}_i \tilde{d}_1 + \bar{d}_1 V_i - \tilde{v}_{c_1} \right) \\ \frac{d\tilde{v}_{c_1}}{dt} = \frac{1}{C_1} \left( \tilde{i}_{L_1} - \frac{P_o \tilde{v}_{c_1}}{V_{c_1}^2} \right) \end{cases}$$

(6)

Note that the following approximation was made in (6),  $\bar{V}_i \gg \tilde{V}_i$  and  $V_{c_1} \gg \tilde{v}_{c_1}$ .

Therefore, the transfer function of the buck converter loaded with a CPL can be obtained from (6) as follows:

$$G(s) = \frac{\tilde{v}_{c_1}}{\tilde{V}_i} = \frac{\frac{\bar{d}_1}{L_1 C_1}}{s^2 - \left(\frac{P_o}{C_1 V_{c_1}^2}\right) s + \frac{1}{L_1 C_1}}$$

(7)

Due to CPL, the transfer function in (7) have poles in the right half-plane, thus, the buck converter, when it is loaded with a CPL, is unstable.

In (4), the nonlinear coefficient introduced by a CPL and the constraints on the state variables make the equation difficult to solve. Therefore, any unwanted dynamics introduced in (4) cannot be damped, so trajectories will tend to have cycling or unbounded behaviors [20], [21].

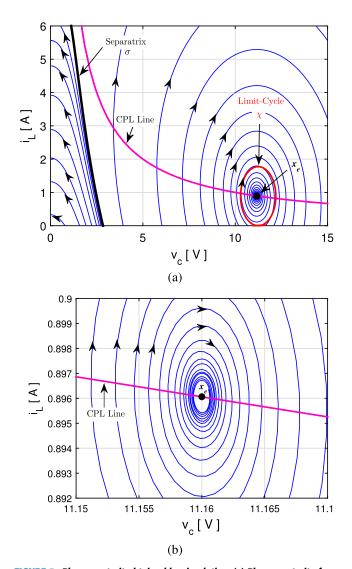

The simulation results in Fig. 5 confirm the intuitive behavior suggested by (4).

The system is analyzed by a phase-plane analysis, solving (plotting) the system differential equations giving

FIGURE 5. Phase-portrait obtained by simulating. (a) Phase-portrait of source converter loaded with a CPL. (b) Zoomed area near the operating condition.

an insight about how the system dynamics evolve with time [16], [20], [21].

The phase-portrait of source converter feeding a CPL (cf. Fig. 5) is simulated with the following parameters:  $V_i = 15 \ V$ ,  $L_1 = 2mH$ ,  $C_1 = 2000 \ mF$ ,  $P_o = 10 \ W$ , and  $d_1 = 0.744$ .

The phase-portrait (Fig. 5(a)) shows the state plane divided into two regions with distinct characteristics [16], [20]: one to the left of a separatrix  $\sigma$ , in which the bus voltage  $v_{c_1}$  collapses being an unstable region, and the other to the right of  $\sigma$ , in which  $v_{c_1}$  presents significant and undesirable oscillations because of the existence of a limit-cycle  $\chi$  [16], [20]. These oscillations are caused by energy imbalances, which occur during the transient period when LC input filter and output powers are not equal as it occurs in steady state. Therefore, without resistive components in the system, which can dissipate the energy imbalance, this energy will resonate among

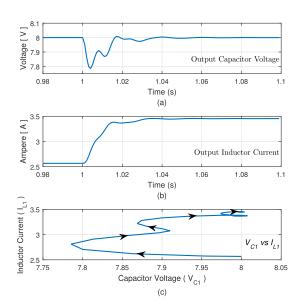

**FIGURE 6.** Closed-Loop system subjected to a variation of power CPL of 10 W. (a) Capacitor Voltage of Source Converter. (b) Inductor Current of Source Converter. (c) Phase-Plane of  $v_{c_1}$  vs  $i_{L_1}$  during the variation of power CPL.

the energy storage elements in the system. This oscillatory behavior is also observed when attempting regulation if the controller is not adequately designed [16].

Fig. 6 shows voltage and current oscillations when a buck converter is subjected (t = 1 s) to a variation of power CPL  $(\Delta P_o)$  of 10 W with  $V_i = 15 \text{ V}$ ,  $L_1 = 2mH$ ,  $C_1 = 2000 \text{ mF}$ ,  $P_o = 5 \text{ W}$ , regulated for an output voltage of 8 V with a PID controller with integral gain of 2.41, proportional gain of 0.011 and derivative gain of  $1.05e^{-5}$ . Load converter acts as a CPL due to the incremental negative resistance behavior during the variation of CPL power as shown in Fig. 6(c).

#### III. ROBUST PARAMETRIC CONTROL BACKGROUND

Mathematical models naturally present errors that are neglected, depending on the type of study. An important consideration in model-based control systems is to keep the system stable, subject to parametric variations. However, generally in the classic controller design, models that ignore uncertainties are used [45]. In this way, it is common to use a nominal transfer function for the controller design. Although the controller is developed based on a nominal transfer function, the real system must be stable for all kinds of transfer functions that represent the whole set of uncertainties.

Thereby, uncertainty of a system can be classified as unstructured (non-parametric uncertainty) and structured (parametric uncertainty) [38], [43].

#### A. ROBUST STABILITY

A system with interval parametric uncertainties is generally described by uncertain polynomials B(s, b) and A(s, a), restricted within pre-specified closed real intervals,

**IEEE** Access

as shown in (8) [38].

$$G(s, b, a) = \frac{B(s, b)}{A(s, a)} = \frac{\sum_{i=0}^{m} [b_i^-, b_i^+] s^i}{\sum_{i=0}^{n} [a_i^-, a_i^+] s^i}$$

(8)

Many robust stability tests under parametric uncertainty are based on analysis of uncertain characteristic polynomial assumed as an interval polynomial family [38], such as

$$P(s,p) = \sum_{i=0}^{n} [p_i^-, p_i^+] s^i$$

(9)

Polynomial P(s, p) is stable if and only if all its roots are contained on the Left Half-Plane (LHP) of the s-plane. Then, P(s, p) is robustly stable if and only if all its polynomials are stable for a set of operating point different from the nominal operating point within its minimum and maximum limits [46]. However, it is not necessary to check stability of an infinite number of polynomials to guarantee the robust stability. Robust stability can be checked through the analysis of four polynomials within P(s, a); these polynomials can be found by Kharitonov Theorem [38], [47].

#### B. KHARITONOV STABILITY THEOREM

The Kharitonov Theorem is a test used in robust control theory to evaluate the stability of a dynamic system whose parameters vary within a closed real interval as follows:

$$\delta(s) = \delta_0 + \delta_1 s + \delta_2 s^2 + \delta_3 s^3 + \dots + \delta_n s^n \tag{10}$$

where, the coefficient vector  $\bar{\delta} = [\delta_0, \delta_1, \delta_2, \delta_3, \cdots, \delta_n]$  ranges over a box:

$$\Delta = \left[\delta_0^-, \delta_0^+\right] \times \left[\delta_1^-, \delta_1^+\right] \times \dots \times \left[\delta_n^-, \delta_n^+\right] \tag{11}$$

where,  $\delta_n^-$  and  $\delta_n^+$  represent the lower and upper limit respectively. Therefore, the Kharitonov polynomials are defined as:

$$K_{1}(s) = \delta_{0}^{-} + \delta_{1}^{-} s + \delta_{2}^{+} s^{2} + \delta_{3}^{+} s^{3} + \delta_{4}^{-} s^{4} + \delta_{5}^{-} s^{5} + \delta_{6}^{+} s^{6} + \cdots$$

$$K_{2}(s) = \delta_{0}^{-} + \delta_{1}^{+} s + \delta_{2}^{+} s^{2} + \delta_{3}^{-} s^{3} + \delta_{4}^{-} s^{4} + \delta_{5}^{+} s^{5} + \delta_{6}^{+} s^{6} + \cdots$$

$$K_{3}(s) = \delta_{0}^{+} + \delta_{1}^{-} s + \delta_{2}^{-} s^{2} + \delta_{3}^{+} s^{3} + \delta_{4}^{+} s^{4} + \delta_{5}^{-} s^{5} + \delta_{6}^{-} s^{6} + \cdots$$

$$K_{4}(s) = \delta_{0}^{+} + \delta_{1}^{+} s + \delta_{2}^{-} s^{2} + \delta_{3}^{-} s^{3} + \delta_{4}^{+} s^{4} + \delta_{5}^{+} s^{5} + \delta_{6}^{-} s^{6} + \cdots$$

$$(12)$$

Theorem 1 (Robust Stability): The interval polynomial family delimited by  $\Delta$  is robustly stable if and only if its four Kharitonov polynomials are stable [38], [47], i.e., all roots of the interval polynomial are in the SPL of the complex plane [48].

## C. ROBUST CONTROLLER DESIGN BY INTERVAL POLE-PLACEMENT

To design the controller, a region of uncertainty is previously defined, considering that the uncertainty is contained in the parameter variation of the plant-model. The controller is designed according to Keel and Bhattacharyya [45], associated with a linear goal programming formulation, which will lead to a set of linear inequality constraints.

Consider G(s, p) a uncertain plant of order n and C(s, x) the controller of order r, defined in (13) and (14) respectively.

$$G(s,p) = \frac{n(s)}{d(s)} = \frac{b_1 s^{n-1} + \dots + b_{n-1} s + b_n}{s^n + a_1 s^{n-1} + \dots + a_{n-1} s + a_n}$$

(13)

$$C(s,x) = \frac{n_c(s)}{d_c(s)} = \frac{x_0 s^r + x_1 s^{r-1} + \dots + x_{r-1} s + x_r}{s^r + y_1 s^{r-1} + \dots + y_{r-1} s + y_r}$$

(14)

Let p be the vector of parameters that represent the plant and x the vector of real parameters representing the controller defined in (15) and (16) respectively. In addition,  $p^o$  represents the nominal value of plant parameters defined in a hyperbox region of uncertainties.

$$p := [b_1 \ b_2 \ \cdots \ b_{n-1} \ b_n \ a_1 \ a_2 \ \cdots \ a_{n-1} \ a_n] \quad (15)$$

$$p := [x_0 \ x_1 \ \cdots \ x_{r-1} \ x_r \ y_1 \ y_2 \ \cdots \ y_{r-1} \ y_r]$$

(16)

According to [45], the solution of the Diophantine equation (17) summarizes the pole-placement problem

$$d(s) = d(s)d_c(s) + n(s)n_c(s)$$

(17)

where, d(s) is the closed-loop characteristic polynomial. Therefore, the parameters of the closed-loop characteristic polynomial are represented as follows:

$$d_i = d_i(x, p) \tag{18}$$

Assuming that the desired dynamic of closed-loop system is represented by

$$\Delta_d(s) = s^i + \phi_1 s^{i-1} + \dots + \phi_{i-1} s + \phi_i$$

(19)

where,  $\phi_i$  represent the parameters of the closed-loop desired polynomial.

In order to tune the controller, the closed-loop polynomial parameters are compared with the desired closed-loop polynomial, which represent the desired dynamics of the system follow as

$$d_i(x, p^o) = \phi_i, \quad i = 1, 2, \dots, l$$

(20)

This problem can be written in its matrix format, presenting the following relationship [38], (21), as shown at the bottom of the next page.

When the system is subject to parametric uncertainties, the controller performance may deteriorate. Therefore, the controller must guarantee robust performance within an acceptable region of closed-loop parameters variation, so that the closed-loop poles are located in a certain region. Thereby, a desired region is defined as follows:

$$\Phi := \left\{ \phi_i^- \le \phi_i \le \phi_i^+ \right\} \tag{22}$$

Therefore, according to [46], replacing the parameters of (22) in (20), it is possible to formulate a linear inequalities set, which restricted the controller and desired polynomial coefficients in the predefined intervals, as shown in (23). Thus, the closed-loop system has its poles within the roots

space of interval-desired polynomial, ensuring the robust stability [49].

$$\phi_i^- \le d_i(x, p) \le \phi_i^+, \quad \forall i = 1, 2, \dots, l$$

(23)

The robust design problem is summarized in the choice of X (if possible) to satisfy the set of inequalities (23) for all  $p \in P$ . The aforementioned robust performance control design problem for the pre-established conditions can be rewritten as the following optimization problem:

$$X = \arg(\min f(X))$$

$$s.t. \begin{bmatrix} A(p) \\ -A(p) \end{bmatrix} X \le \begin{bmatrix} B(\phi^{+}) \\ -B(\phi^{-}) \end{bmatrix}$$

(24)

where, f(X) is a linear cost function that must be built and minimized according to the control goals. In this study, the cost function f(X) has been chosen to be the sum of the elements of vector of the controller parameter X, such as suggested by Keel and Bhattacharyya [45] and Bhattacharyya *et al.* [50].

## IV. MATHEMATICAL MODEL FOR MULTI-CONVERTER BUCK-BUCK SYSTEM

In order to represent the dynamical behavior of DC Multiconverter buck-buck System, a small signal approximation model is employed as an effective mathematical model.

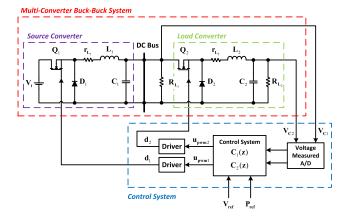

Fig. 7 represents the DC MCBB system with two decoupled outputs,  $V_{C_1}$  and  $V_{C_2}$ , such that  $V_{C_2} < V_{C_1}$ , and a topology employed to control the system. The main characteristic of this system is that it has two DC-DC buck converters connected in series where the output of the first one converter is the DC source of the second one.

Each converter can be considered an independent subsystem; therefore, the dynamics of the system can be simplified to the analysis of two independent converters. The dynamic behavior of buck converter, in Continuous Conduction Mode (CCM), can be found in [40] and [41].

The following equations involving the state variables of buck converters are written based on the analysis of their

FIGURE 7. Multi-Converter Buck-Buck System.

respective equivalent circuits.

$$\begin{cases}

L_1 \frac{di_{L_1}}{dt} = d_1 V_i - V_{C_1} - r_{L_1} i_{L_1} \\

C_1 \frac{dV_{C_1}}{dt} = i_{L_1} - \frac{V_{C_1}}{R_{L_1}} \\

L_2 \frac{di_{L_2}}{dt} = d_2 V_{C_1} - V_{C_2} - r_{L_2} i_{L_2} \\

C_2 \frac{dV_{C_2}}{dt} = i_{L_2} - \frac{V_{C_2}}{R_{L_2}}

\end{cases}$$

(25)

The duty cycle  $d_1$  regulates the output voltage  $(V_{C1})$  of source converter, i.e. the DC bus voltage, and the duty cycle  $d_2$  regulates the output power of load converter, i.e.,  $V_{C2}^2/R_{L2}$ . Thereby, the outputs of system are described below.

$$y_{1} = \begin{bmatrix} 0 \ V_{C_{1}} \end{bmatrix}$$

$$y_{2} = \begin{bmatrix} 0 \ \frac{V_{C_{2}}^{2}}{R_{L_{2}}} \end{bmatrix}$$

(26)

Assuming that the electronic switches and diodes are ideal, the linearized model that describes the dynamic behavior of

$$\begin{bmatrix}

[b_{1}] & 0 & \cdots & 0 & 0 & | & 1 & 0 & \cdots & 0 & 0 \\

[b_{2}] & [b_{1}] & \ddots & \vdots & 0 & | & [a_{1}] & 1 & \ddots & \vdots & 0 \\

\vdots & [b_{2}] & \ddots & 0 & \vdots & | & \vdots & [a_{1}] & \ddots & 0 & \vdots \\

[b_{m-1}] & \vdots & \ddots & [b_{1}] & 0 & | & [a_{n-1}] & \vdots & \ddots & 1 & 0 \\

[b_{m}] & [b_{m-1}] & \ddots & [b_{2}] & [b_{1}] & | & [a_{n}] & [a_{n-1}] & \ddots & [a_{1}] & 1 \\

0 & [b_{m}] & \ddots & \vdots & [b_{2}] & | & 0 & [a_{n}] & \ddots & \vdots & [a_{1}] \\

\vdots & 0 & \ddots & [b_{m-1}] & \vdots & | & \vdots & 0 & \ddots & [a_{n-1}] & \vdots \\

0 & \vdots & \ddots & [b_{m}] & [b_{m-1}] & | & 0 & \vdots & \ddots & [a_{n}] & [a_{n-1}] \\

0 & 0 & \cdots & 0 & [b_{m}] & | & 0 & 0 & \cdots & 0 & [a_{n}]

\end{bmatrix}$$

$$(21)$$

the converter is represented as follows:

$$\frac{V_{C_1}(s)}{V_i(s)} = \frac{\frac{d_1^o}{L_1 C_1}}{s^2 + \left(\frac{1}{R_{L_1} C_1} + \frac{r_{L_1}}{L_1}\right) s + \left(\frac{1}{L_1 C_1} + \frac{r_{L_1}}{R_{L_1} L_1 C_1}\right)} \tag{27}$$

$$\frac{V_{C_2}(s)}{V_{C_1}(s)} = \frac{2\left(\frac{d_2^o}{L_1C_1}\right)\left(\sqrt{\frac{P_o}{R_{L_2}}}\right)}{s^2 + \left(\frac{1}{R_{L_2}C_2} + \frac{r_{L_2}}{L_2}\right)s + \left(\frac{1}{L_2C_2} + \frac{r_{L_2}}{R_{L_2}L_2C_2}\right)}$$

(28)

where,  $d_1^o$  and  $d_2^o$  are operational point for duty cycle of outputs 1 and 2, respectively.  $P_o$  is the operating power of output 2.

The nominal values of the parameters, operational point and the meaning of each symbol in (27) and (28) are presented in Table 1.

**TABLE 1.** Values for the physical parameters of the DC multi-converter buck-buck board test system.

| Par.        | Uni.     | Var.<br>(%) | Nom.<br>Val. | Description                             |  |

|-------------|----------|-------------|--------------|-----------------------------------------|--|

| $V_i$       | V        | 15          | 15.0         | Source input voltage                    |  |

| $R_{L_1}$   | $\Omega$ | 50          | 4.0          | Loading at output 1                     |  |

| $R_{L_2}$   | $\Omega$ | _           | 4.0          | Loading at output 2                     |  |

| $C_1$       | $\mu F$  | 10          | 2000         | Capacitor at output 1                   |  |

| $C_2$       | $\mu F$  | _           | 2200         | Capacitor at output 2                   |  |

| $L_1$       | mH       | 10          | 2.0          | Inductor at source subsystem            |  |

| $L_2$       | mH       | _           | 2.0          | Inductor at CPL                         |  |

| $r_{L_1}$   | $\Omega$ | 15          | 0.05         | Internal resistance of $L_1$            |  |

| $r_{L_2}$   | $\Omega$ | _           | 0.05         | Internal resistance of $L_2$            |  |

| $d_1^o$     | %        | _           | 74.4         | Operating duty cycle of output 1        |  |

| $d_2^o$     | %        | _           | 63.2         | Operating duty cycle of output 2        |  |

| $V_{C_1}^o$ | V        | _           | 8.0          | Output voltage of source subsystem      |  |

| $P_{CPL}$   | p.u.     | _           | 0.3          | Output power of CPL                     |  |

| $f_{sw1}$   | kHz      | _           | 1.0          | Switching frequency of duty cycle $d_1$ |  |

| $f_{sw2}$   | kHz      | _           | 5.0          | Switching frequency of duty cycle $d_2$ |  |

| $P_{max}$   | W        | _           | 20.0         | Maximum power at CPL                    |  |

| $f_s$       | kHz      | _           | 1.0          | Sampling frequency                      |  |

|             |          |             |              |                                         |  |

#### V. ROBUST CONTROLLER DESIGN METHODOLOGY

This section presents a method to design a fixed order robust controller that provides robust stability and performance for a predetermined uncertain family of models with parameters bounded in a hyperbox region. This study only considers uncertainties in the parameters of source converter (see Table 1) because oscillations, caused by a CPL, occur in the LC filter of the converter. Therefore, only output 1 will be regulated by a robust controller. A classic controller, based on Classical Pole-Placement (CPP), will regulate output 2. The robust controller is designed according to presented by Bhattacharyya *et al.* [50]. In this paper, this method is denominated as "Control Based on Kharitonov's Rectangle (CKR". The proposed controller must ensure robust stability and performance for the entire region of parametric variation.

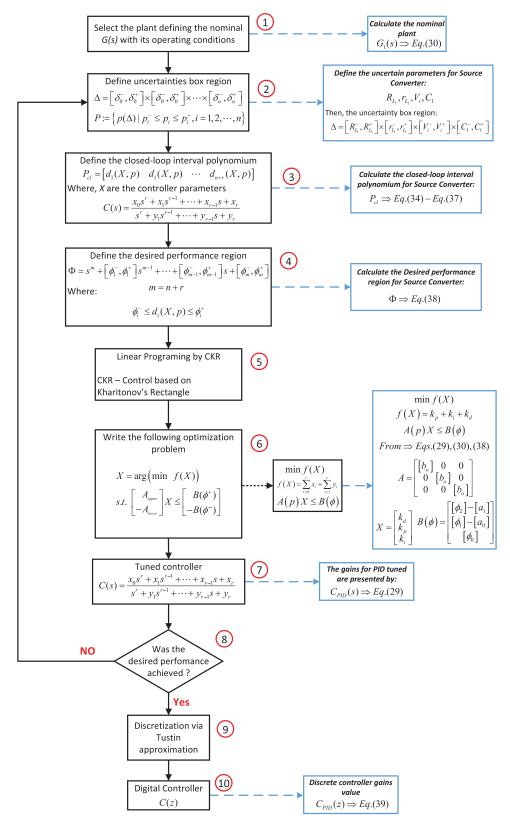

Fig. 8 illustrates a simplified flowchart of the methodology for designing the robust controller. The process starts in step 1, by defining the nominal plant (20) with its operating conditions; in step 2, the box region of uncertainties is built based on a previously specified uncertainty range delimited by the designer. Since box region of uncertainties influence on the delimitation of the convex region where the control gains will be determined, the correct selection of this box region is an important point to have success of the proposed methodology. The lower-and upper-bound of each parameter are provided in Table 1.

The characteristic closed-loop polynomial is obtained (Step 3) by using the controller parameter and the nominal model (20) selected in step 1, then by replacing the nominal and interval values, defined in step 2, the interval closed-loop polynomial is calculated.

The controller function depends on the chosen control structure. In this work, a controller with a PID structure is selected. The transfer function is given below.

$$C_{PID}(s) = \frac{U(s)}{E(s)} = \frac{k_d s^2 + k_p s + k_i}{s}$$

(29)

For simplification, transfer function presented in (20) can be represented as follows:

$$G_1(s) = \frac{V_{C1}(s)}{V_i(s)} = \frac{b_0}{s^2 + a_1 s + a_0}$$

(30)

where

$$a_1 = \left(\frac{1}{R_{L_1}C_1} + \frac{r_{L_1}}{L_1}\right) \tag{31}$$

$$a_0 = \left(\frac{1}{L_1 C_1} + \frac{r_{L_1}}{R_{L_1} L_1 C_1}\right) \tag{32}$$

$$b_0 = \frac{d_1^o}{L_1 C_1} \tag{33}$$

Finally, closed-loop interval polynomial is obtained by using the controller parameters (22) and plant parameters (23).

$$P_{cl}(s) = s^3 + \left[\varphi_2^-, \varphi_2^+\right] s^2 + \left[\varphi_1^-, \varphi_1^+\right] s + \left[\varphi_o^-, \varphi_o^+\right] \quad (34)$$

The nominal parameters of  $P_{cl}$  depend on the parameters of source converter (cf. Table 1), resulting in the following nominal parameters:

$$\varphi_0^o = b_0 k_i \tag{35}$$

$$\varphi_1^o = a_0 + b_0 k_p \tag{36}$$

$$\varphi_2^o = a_1 + b_0 k_d \tag{37}$$

The lower- and upper-limits for these parameters must be computed by replacing the nominal and interval presented in Table 1 by using interval analysis for (23)-(26). The region defined by the closed-loop interval polynomial of (27) must be inside the region determined by the desired performance polynomial (chosen in Step 4). Particularly, it was chosen for a maximum settling time of less than 0.15 sec and a damping factor greater than 0.9, defining the desired performance region (38). Note that an auxiliary pole must be added that does not affect the desired dynamics of system to satisfy (20).

$$\Phi = s^3 + [\phi_2] s^2 + [\phi_1] s + [\phi_o]$$

(38)

FIGURE 8. Flowchart of methodology for designing of robust controller.

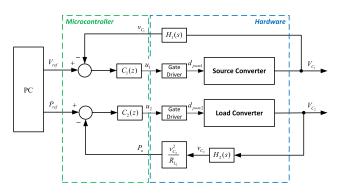

FIGURE 9. Block diagram of the developed hardware system and actuation of the system control signal.

The optimization problem is selected in step 5 and solved in step 6, where the cost function is defined as the sum of controller gains and the parameter vector X. The feasible solution  $X^*$  (obtained in step 6) is used to set the control structure (step 7).

The performance condition is verified in step 8 in case of achieving it, advance to step 9, if not, go back to step 2, where you must redefine the system's uncertainties.

In order to obtain a discrete equivalent controller the Tustin Method [51] was used (Step 9). A sampling period of 1ms was chosen in order to comply with a sampling frequency between 2 to 10 greater than the frequency band of the system.

$$C_{PID}(z) = \frac{h_0 z^2 + h_1 z + h_2}{z^2 - 1}$$

(39)

#### VI. DESCRIPTION OF TEST ENVIRONMENTS

## A. DESCRIPTION OF THE MULTI-CONVERTER BUCK-BUCK SYSTEM TEST BOARD

Fig. 9 presents a control-generalized block diagram applying to multi-converter buck-buck system using filters in the outputs of system to avoid that ripples of the outputs interfere in the performance of the designed controller. These filters,  $H_1(s)$  and  $H_2(s)$ , must be designed so that they do not affect the system dynamics. Two SISO controllers are used to regulate system outputs.

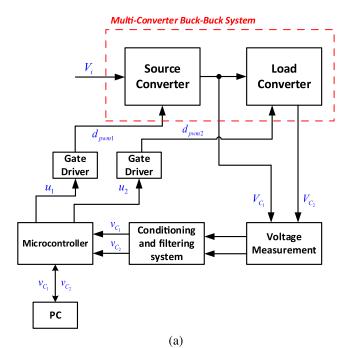

Fig. 10(a) presents a diagram of the subsystems used in the experimental tests and Fig. 10(b) shows the developed laboratory setup.

A DC Multi-Converter buck-buck (Fig. 10(b)) is developed for the experimental evaluation of the proposed control approach. The controller has been implemented by using a 32-bit ARM core microcontroller AT91SAM3X8E (Fig. 10(b)). The desired set point values are provided by a microcomputer system via USB communication.

#### **B. DESCRIPTION OF EXPERIMENTS**

The Integral Square Error (ISE) is used to evaluate the performance of the proposed control strategy.

In order to design the controllers, the following (nominal) requirements are chosen to regulate output 1: settling time less or equal than 0.1 s and damping factor greater or equal

FIGURE 10. (a) Block diagram of the Multi-converter buck-buck test system developed for our experiments. (b) DC Multi-Converter buck-buck experimental setup.

than 0.9. To regulate output 2, requirements are: settling time less or equal than 0.05 s and damping factor greater or equal than 0.9. Note that the dynamics of output 2 is faster than output 1, being this a necessary condition for the load converter acts as a CPL.

The experiments compare performance of controllers tuned by CKR and CPP methodologies using PID control structure.

Table 2 shows the controllers gains for the controllers designed to regulate outputs 1 and 2. Note that only for the output 1 is considered the robust control methodology.

The first experiment is performed to check the closed-loop performance for positive variation of power reference. The source converter is set to its initial operating condition, as mentioned in Table 1, until the steady state is achieved. Then, source converter starts feeding load converter. Thereafter the steady state is achieved, the multi-converter is subjected to 0.5 p.u. a positive variation of power reference.

| TABLE 2. Values | of | parameters | for the | designed | controllers. |

|-----------------|----|------------|---------|----------|--------------|

|-----------------|----|------------|---------|----------|--------------|

|          | Controller gains | CKR<br>Method  | CPP<br>Method   |

|----------|------------------|----------------|-----------------|

|          | $k_d$            | $1.0588e^{-5}$ | $1.2024e^{-5}$  |

| $C_1(z)$ | $k_p$            | 0.010814       | -0.009997       |

|          | $k_i$            | 2.6783         | 2.4169          |

|          | $k_d$            | _              | $2.49916e^{-5}$ |

| $C_2(z)$ | $k_p$            | _              | -0.025413       |

|          | $k_i$            | _              | 51.6969         |

The second experiment evaluates the closed-loop performance for negative variation of power reference. The system starts to operate in the same way as for the positive variation test until the system achieves its steady state. After that, the system operates at an operating point of 0.7 p.u. in order to obtain a 0.5 p.u. negative variation.

The third experiment evaluates the closed-loop performance for positive and negative variation of power reference. After the multi-converter system reaches its stable state, a positive variation of 0.5 p.u. is performed at the operating point of power reference. Then, a negative variation of 0.5 p.u. is performed to return to the initial condition.

These experiments aim to show that the proposed robust controller is able to compensate oscillations caused by a CPL at output 1 when the system is submitted to positive and negative variations in its power operating condition, maintaining the desired performance for the uncertainty region and consequently different operation points. All the experiments are performed in experimental environment using the developed DC MCBB system and simulation environment using MATLAB/Simulink.

#### VII. ASSESSMENT OF RESULTS

#### A. EVALUATION OF SYSTEM UNDER A POSITIVE VARIATION OF POWER REFERENCE

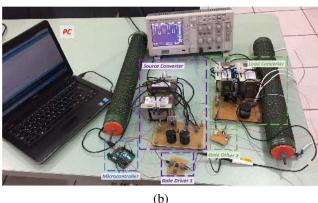

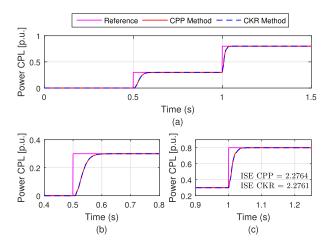

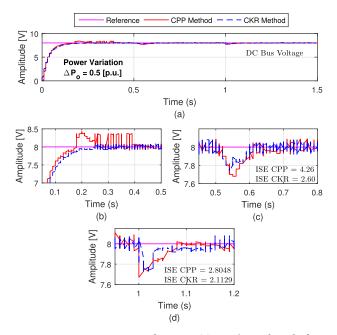

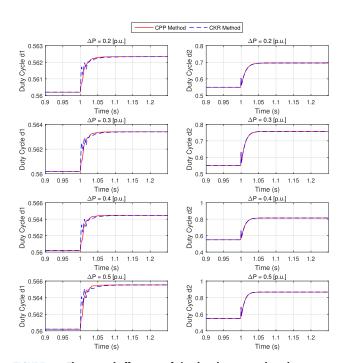

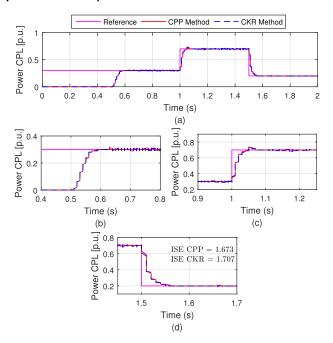

Figs. 11 and 12 show the simulated responses performed in the multi-converter model, using a PID control with a positive variation of power reference. Figs. 13 and 14 shows the experimental evaluation performed in the multi-converter buck-buck system.

The multi-converter buck-buck system stars with load converter disconnected until source converter achieves its steady state (see Table 1), then the load converter is connected ( $t=0.5~\rm s$ ) causing a load disturbance at the output of source converter. When the multi-converter buck-buck system is operating in its steady state (8V and 0.3 p.u.), the system is subjected to a positive variation of power reference ( $t=1.0~\rm s$ ) within amplitude range from 0.1 to 0.5 p.u..

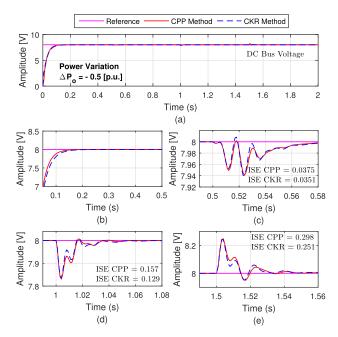

Figs. 11 and 13 show the simulated and experimental results, respectively, of source converter performance, when the system is subjected to a positive variation of 0.5 p.u. of

FIGURE 11. Source converter performance. (a) Simulated results for positive variations on the value of power reference of the Multi-converter buck-buck system using PID control structures. (b) Transient response. (c) Oscillations caused by the connection of load converter. (d) Oscillations caused by the variation of power reference of system.

FIGURE 12. Load converter performance. (a) Simulated results for positive variations on the value of power reference of the Multi-converter buck-buck system using PID control structures. (b) Transient response. (c) Variation of power reference of system.

its power reference (see Figs. 12(c) and 14(c)) using a PID control based on CPP and CKR approaches.

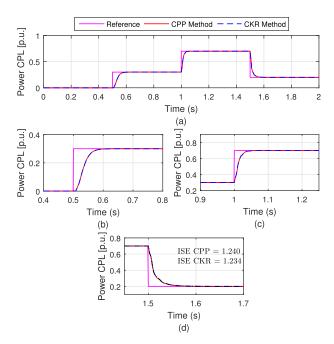

Fig. 12 and 14 show the simulated and experimental results, respectively, of load converter performance, using a PID control based on CPP approach, when the output of source converter is regulated by a PID control based on CPP and CKR approaches.

Note that all information about transient response, reference tracking and load perturbation are given in Figs. 11 to 14, obtaining a better performance of multi-converter buck-buck

FIGURE 13. Source converter performance. (a) Experimental results for positive variations on the value of power reference of the Multi-converter buck-buck system using PID control structures. (b) Transient response. (c) Oscillations caused by the connection of load converter. (d) Oscillations caused by the variation of power reference of system.

FIGURE 14. Load converter performance. (a) Experimental Results for positive variations on the value of power reference of the Multi-Converter buck-buck system using PID control structures. (b) Transient Response. (c) Variation of power reference of system.

system when the source converter is regulated by CKR approach.

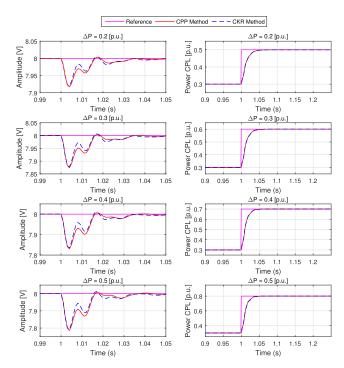

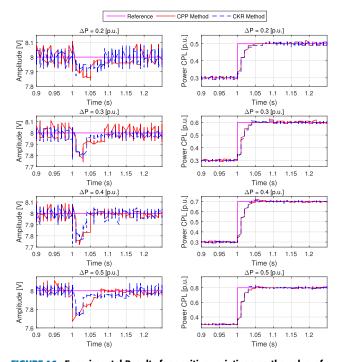

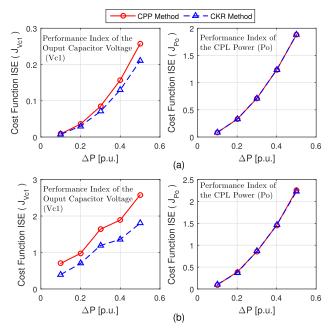

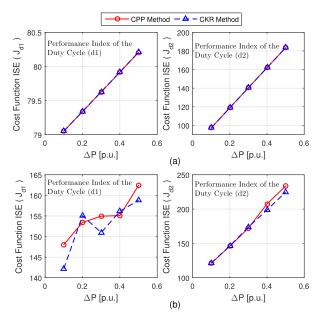

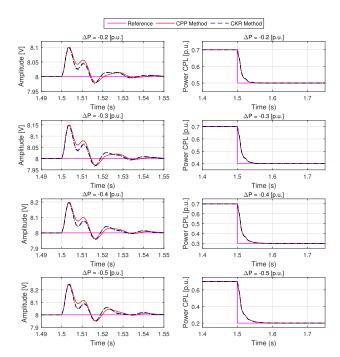

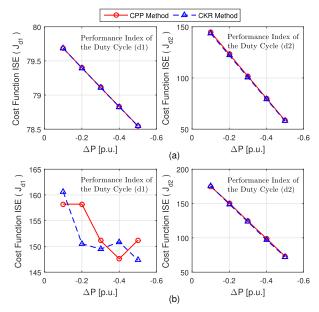

Figs. 15 and 16 show, respectively, the simulated and experimental evaluation performed in the multi-converter buck-buck system, using a PID control structures for different values of positive variation of power reference.

The simulated and experimental results demonstrate that both controllers of source converter can compensate oscillations at output 1 caused by positive variations in the power operating condition of system.

FIGURE 15. Simulated Results for positive variations on the value of power reference of the Multi-Converter buck-buck system using PID control structures.

FIGURE 16. Experimental Results for positive variations on the value of power reference of the Multi-Converter buck-buck system using PID control structures.

However, the interval robust (CKR Method) controller proposed in this paper provides a better performance in comparison with classical controller (CPP Method). Therefore, the impact of positive power variation is lower for the

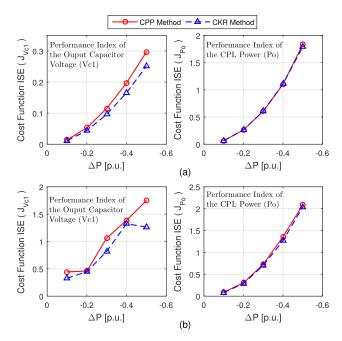

FIGURE 17. The cost function ISE of system outputs for positive variations of power reference. (a) Simulation assessment. (b) Experimental assessment

FIGURE 18. The control effort test of simulated system, when the system is subjected to positive variations on the value of power reference.

controller by CKR method as shown by the ISE performance indices in Figs. 17(a) and 17(b), ratifying the robustness of the proposed methodology.

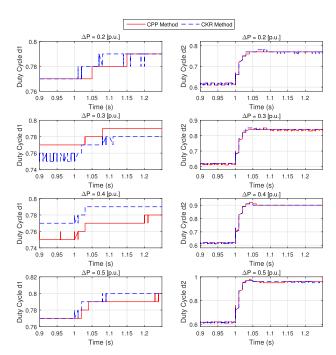

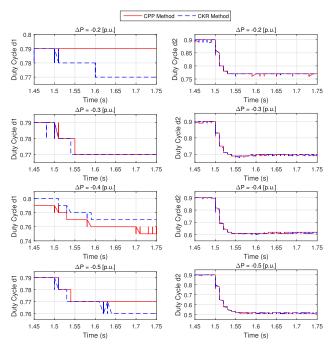

Figs. 18 and 19 show the control effort of controllers for simulated and experimental tests, respectively, using a PID control structures.

Note that the saturation of the control signal does not occur at any time.

FIGURE 19. The control effort test of experimental system, when the system is subjected to positive variations on the value of power reference.

FIGURE 20. The cost function ISE of effort control system for positive variations of power reference. (a) Simulation assessment. (b) Experimental assessment.

For the simulated case, the control effort obtained was almost similar for controllers of system as shown their ISE performance indices in Fig. 20(a). However, the performance presented by controllers in experimental tests was different as shown in Fig. 20(b).

The DC multi-converter buck-buck system obtained less degradation in the control system performance when the robust proposed controller controls the output 1 of

multi-converter buck-buck system. Fig. 20 shows the ISE index performance of control effort of signal.

Although the control strategy to regulate the load converter does not change, different performances can be observed (see Fig. 20(b)) due to the oscillation in the output voltage of source converter caused by the variation of power reference. Thereby, the controller of the voltage regulation stage that better compensates for the oscillations will cause less deterioration in the performance of the controller of the power control stage.

In the MCBB system, the load converter is considering a load for the source converter, thus, any change in the operating conditions of load converter affects as a load disturbance at the output of the source converter. Therefore, the greater the reference variation at output 2 (Power CPL), the greater the voltage oscillation at output 1 as shown in simulated (see Fig. 15) and experimental (see Fig. 16) assessment.

The simulated and experimental tests performed show that the robust proposed (CKR) approach outperforms the classical (CPP) approach for several values of power variations ( $P_o$ ). Therefore, the controller proposed provides a better performance with reduced oscillation amplitude at output 1 in comparison with the classical controller.

Fig 17 shows the comparison of ISE performance index for the multi-converter test system between robust and classical approaches. For most of the operating value of  $P_o$ , the ISE indices for CPP method shows higher values in comparison with CKR method.

## B. EVALUATION OF SYSTEM UNDER A NEGATIVE VARIATION OF POWER REFERENCE

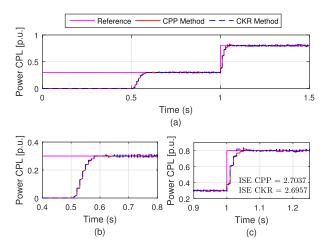

Figs. 21 and 22 show the simulated evaluation performed in the MCBB model, using a PID control with a negative variation of power reference. Figs. 23 and 24 shows the experimental evaluation performed in the multi-converter buckbuck system.

According to Figs. 21 to 24, the experiment begins in the same way that the experiment described in Section VII(A) until the MCBB system achieves its steady state (8V and 0.3 p.u.). Then, a variation in operating condition at output 2 ( $P_o$ ) occurs at t = 1 s, as explain in Section VI(B), so the system will operate with the following conditions:  $V_{C_1}{}^o = 8 \text{ V}$  and  $P_o = 0.7 \text{ p.u.}$ , after that, the system is subjected to a negative variation of power reference (t = 1.5 s) within an amplitude range from 0.1 to 0.5 p.u..

Fig. 21 shows the simulated results of source converter performance, when the system is subjected to a negative variation of 0.5 p.u. of its power reference (see Figs. 22(d) and 24(d)) using a PID control based on CPP and CKR approaches, while Fig. 23 shows the experimental results of the same test.

Fig. 22 shows the simulated results of load converter performance, using a PID control based on CPP approach, when the output of source converter is regulated by a PID control based on CPP and CKR approaches, while Fig. 24 shows the experimental results of the same test.

FIGURE 21. Source converter performance. (a) Simulated Results for negative variations on the value of power reference of the Multi-Converter buck-buck system using PID control structures. (b) Transient Response. (c) Oscillations caused by the connection of load converter. (d) Oscillations caused by a positive variation of power reference of system. (e) Oscillations caused by a negative variation of power reference of system.

FIGURE 22. Load converter performance. (a) Simulated Results for negative variations on the value of power reference of the Multi-Converter buck-buck system using PID control structures. (b) Transient Response. (c) Positive Variation of power reference of system. (d) Negative Variation of power reference of system.

Note that all information about transient response, reference tracking and load perturbation are given in Figs. 21 to 24, obtaining a better performance of multi-converter buck-buck

FIGURE 23. Source converter performance. (a) Experimental Results for negative variations on the value of power reference of the Multi-Converter buck-buck system using PID control structures. (b) Transient Response. (c) Oscillations caused by the connection of load converter. (d) Oscillations caused by a positive variation of power reference of system. (e) Oscillations caused by a negative variation of power reference of system.

FIGURE 24. Load converter performance. (a) Experimental Results for negative variations on the value of power reference of the Multi-Converter buck-buck system using PID control structures. (b) Transient Response. (c) Positive Variation of power reference of system. (d) Negative Variation of power reference of system.

system for negative variation of power reference when the source converter is regulated by CKR approach.

Figs. 25 and 26 show, respectively, the simulated and experimental evaluation performed in the multi-converter

FIGURE 25. Simulated Results for negative variations on the value of power reference of the Multi-Converter buck-buck system using PID control structures.

FIGURE 26. Experimental Results for negative variations on the value of power reference of the Multi-Converter buck-buck system using PID control structures.

buck-buck system, using a PID control structures for negative variations in operating condition at output 2 ( $P_o$ ).

The simulated and experimental results that both controllers have succeeded in correcting the load disturbance at output 1  $(V_{C_1})$  caused by negative variations in the power

FIGURE 27. The cost function ISE of system outputs for negative variations of power reference. (a) Simulation assessment. (b) Experimental assessment.

operating condition  $(P_o)$  of multi-converter buck-buck system. However, the proposed robust controller (CKR Method) more effectively compensates the oscillations in comparison with the classical controller (CPP Method). Therefore, the impact of negative variation of power reference  $(P_o)$  is lower for the CKR Method as shown in Figs. 27.

Figs. 27(a) and 27(b) show the comparison of ISE performance index of classical and robust controlles for simulated and experimental assessment, respectively. The ISE index evaluates the impact of negative variation of power reference ( $P_o$ ) on system performance. Therefore, the robust controller (CKR) shows the best performance under negative variation of power reference ( $P_o$ ) for simulated and experimental tests confirming the robustness of the proposed robust control methodology.

According to results while the greater the reference variation at output 2 (Power CPL), the greater the voltage oscillation at output 1 as shown in simulated (see Fig. 25) and experimental (see Fig. 26) assessment.

Figs. 28 and 29 show the control effort of controllers for simulated and experimental tests, respectively, under power reference ( $P_o$ ). Note that the saturation of the control signal does not occur at any time.

Note that for the simulated case, the obtained control effort was almost similar for controllers of system as shown their ISE performance indices in Fig. 30(a). However, the performance presented by controllers was different.

The multi-converter buck-buck system obtained less degradation in the control system performance when the robust proposed controller controls output 1.

Fig. 30(b) shows the ISE index performance of control effort signal.

**FIGURE 28.** The control effort test of simulated system, when the system is subjected to negative variations on the value of power reference.

FIGURE 29. The control effort test of experimental system, when the system is subjected to negative variations on the value of power reference.

### C. PERFORMANCE EVALUATION UNDER CPL POWER VARIATION

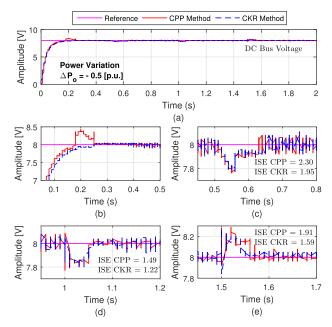

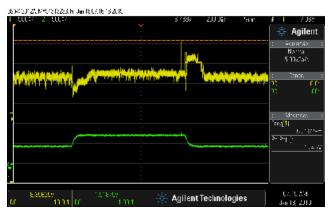

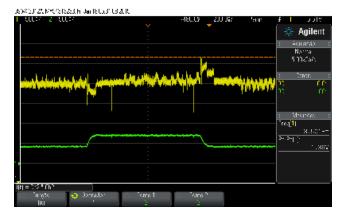

Fig. 31 shows the experimental evaluation performed in the MCBB system, using a PID control based on CPP approach. Fig. 32 shows the experimental evaluation performed in the MCBB system, using a PID control based on CKR approach.

According to Figs. 31 and 32, the experiment begins in the same way that the experiment described in Section VII(A) and VII(B) until the MCBB system achieves

FIGURE 30. The cost function ISE of effort control system for negative variations of power reference. (a) Simulation assessment.

(b) Experimental assessment.

FIGURE 31. MCBB system performance, using a PID control based on CPP approach.

FIGURE 32. MCBB system performance, using a PID control based on CKR approach.

its steady state (8V and 0.3 p.u.). Then, a variation in operating condition at output 2 ( $P_o$ ) occurs at t = 0.75 s, as explain in Section VI(B), so the system will operate with

the following conditions:  $V_{C_1}^{\ o} = 8 \ V$  and  $P_o = 0.8 \ p.u.$ , after that, the system is subjected to a negative variation of power reference ( $t = 1.25 \ s$ ) returning to the initial condition (8V and 0.3 p.u.).

Figs. 31 and 32 show the CPL power variation and the voltage oscillations in the feeder converter by using the classical control methodology and robust control methodology, respectively. It is worth note that the CKR approach outperforms the other approach due to the minimum voltage oscillation occurrence, in addition, the oscillation is quickly corrected in comparison with the CPP approach, furthermore the CKR methodology presents the smaller voltage ripple than the CPP approach. In order to ratify these results, the integral index of this oscillation for all approaches was calculated. the CKR approach presents 1.42 of the ISE value and the CPP approach presents 2.16 ISE value, therefore, it was ratified that the CKR approach outperform the CPP approach when there is variation of a CPL power variation in the system.

#### **VIII. CONCLUSION**

This paper proposes to use a robust parametric control technique for designing fixed order robust controller, in order to minimizing oscillations effects caused by constant power load in a DC Multi-converter buck-buck system guaranteeing robust stability and robust performance for an entire predefined uncertainty region.

The proposed technique has been exhaustively evaluated in both computational simulations as well as by means of experiments performed in a 20 W DC Multi-converter. The proposed robust controller (CKR Method) performance is compared with a classical controller based on pole-placement (CPP Method).

According to the results obtained via simulations and experiments, it is concluded that when the multi-converter buck-buck system is subjected to a certain variation of reference power  $(P_o)$ , the CKR method more effectively compensates the oscillations at output voltage of source converter  $(V_{C_1})$  improving the performance of the whole system as shown by the performance indicators obtained in this work.

Therefore, the results indicate that the proposed robust controller is justified and presents relevant improvements in the Multi-converter control, offering robust performance and stability.

#### **REFERENCES**

- Z. Qian, O. Abdel-Rahman, H. Al-Atrash, and I. Batarseh, "Modeling and control of three-port DC/DC converter interface for satellite applications," *IEEE Trans. Power Electron.*, vol. 25, no. 3, pp. 637–649, Mar. 2010.

- [2] C. Zhang, J. Wang, S. Li, B. Wu, and C. Qian, "Robust control for PWM-based DC–DC buck power converters with uncertainty via sampleddata output feedback," *IEEE Trans. Power Electron.*, vol. 30, no. 1, pp. 504–515, Jan. 2015.

- [3] A. Bhaumik, Y. Kumar, S. Srivastava, and M. Islam, "Performance studies of a separately excited DC motor speed control fed by a buck converter using optimized PIλDμ controller," in *Proc. Int. Conf. Circuit, Power Comput. Technol. (ICCPCT)*, Nagercoil, India, Mar. 2016, pp. 1–6.

- [4] M. Hassanalieragh, T. Soyata, A. Nadeau, and G. Sharma, "UR-SolarCap: An open source intelligent auto-wakeup solar energy harvesting system for supercapacitor-based energy buffering," *IEEE Access*, vol. 4, pp. 542–557, 2016.

- [5] Q. Xu, C. Zhang, C. Wen, and P. Wang, "A novel composite nonlinear controller for stabilization of constant power load in DC microgrid," *IEEE Trans. Smart Grid*, vol. 10, no. 1, pp. 752–761, Jan. 2019. doi: 10.1109/TSG.2017.2751755.

- [6] D. Kumar, F. Zare, and A. Ghosh, "DC microgrid technology: System architectures, AC grid interfaces, grounding schemes, power quality, communication networks, applications, and standardizations aspects," *IEEE Access*, vol. 5, pp. 12230–12256, 2017.

- [7] H.-C. Chang and C.-M. Liaw, "An integrated driving/charging switched reluctance motor drive using three-phase power module," *IEEE Trans. Ind. Electron.*, vol. 58, no. 5, pp. 1763–1775, May 2011.

- [8] M. I. Ghiasi, M. A. Golkar, and A. Hajizadeh, "Lyapunov based-distributed fuzzy-sliding mode control for building integrated-DC microgrid with plug-in electric vehicle," *IEEE Access*, vol. 5, pp. 7746–7752, 2017.

- [9] X. Xiong, C. K. Tse, and X. Ruan, "Bifurcation analysis of standalone photovoltaic-battery hybrid power system," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 60, no. 5, pp. 1354–1365, May 2013.

- [10] Q. Xu et al., "A decentralized dynamic power sharing strategy for hybrid energy storage system in autonomous DC microgrid," *IEEE Trans. Ind. Electron.*, vol. 64, no. 7, pp. 5930–5941, Jul. 2017.

- [11] X. Xiong, X. Ruan, H. Xi, and J. Ge, "Feed-forwarding the output voltage to improve efficiency for envelope-tracking power supply based on a switch-linear hybrid scheme," *IEEE Trans. Power Electron.*, vol. 26, no. 8, pp. 2106–2111, Aug. 2011.

- [12] N. Mohan, T. M. Undeland, and W. P. Robbins, Power Electronics: Converters, Applications, and Design. Hoboken, NJ, USA: Wiley, 2002.

- [13] M. Salimi and A. Zakipour, "Direct voltage regulation of DC-DC buck converter in a wide range of operation using adaptive input-output linearization," *IEEJ Trans. Elect. Electron. Eng.*, vol. 10, no. 1, pp. 85–91, Jan 2015

- [14] W. Du, J. Zhang, Y. Zhang, and Z. Qian, "Stability criterion for cascaded system with constant power load," *IEEE Trans. Power Electron.*, vol. 28, no. 4, pp. 1843–1851, Apr. 2013.

- [15] A. Emadi, B. Fahimi, and M. Ehsani, "On the concept of negative impedance instability in the more electric aircraft power systems with constant power loads," in *Proc. Intersoc. Energy Convers. Eng. Conf.*, Vancouver, BC, Canada, Aug. 1999, pp. 1–13.

- [16] A. Kwasinski and C. N. Onwuchekwa, "Dynamic behavior and stabilization of dc microgrids with instantaneous constant-power loads," *IEEE Trans. Power Electron.*, vol. 26, no. 3, pp. 822–834, Mar. 2011.

- [17] V. Grigore, J. Hatonen, J. Kyyra, and T. Suntio, "Dynamics of a buck converter with a constant power load," in *Proc. 29th Annu. IEEE Power Electron. Spec. Conf. (PESC)*, Fukuoka, Japan, May 1998, pp. 72–78.

- [18] R. D. Middlebrook, "Input filter considerations in design and application of switching regulators," in *Proc. Ind. Appl. Soc. Annu. Meeting*, vol. 1, 1976, pp. 366–382.

- [19] A. T. Elsayed, A. A. Mohamed, and O. A. Mohammed, "DC microgrids and distribution systems: An overview," *Electr. Power Syst. Res.*, vol. 119, pp. 407–417, Feb. 2015.

- [20] H. Mosskull, "Constant power load stabilization," Control Eng. Pract., vol. 72, pp. 114–124, Mar. 2018.

- [21] S. Singh, A. R. Gautam, and D. Fulwani, "Constant power loads and their effects in DC distributed power systems: A review," *Renew. Sustain. Energy Rev.*, vol. 72, pp. 407–421, May 2017.

- [22] C. N. Onwuchekwa and A. Kwasinski, "Analysis of boundary control for buck converters with instantaneous constant-power loads," *IEEE Trans. Power Electron.*, vol. 25, no. 8, pp. 2018–2032, Aug. 2010.

- [23] M. K. Al-Nussairi, R. Bayindir, S. Padmanaban, L. Mihet-Popa, and P. Siano, "Constant Power Loads (CPL) with Microgrids: Problem Definition, Stability Analysis and Compensation Techniques," *Energies*, vol. 10, no. 10, pp. 1656–1676, Oct. 2017.

- [24] M. Wu, D. D.-C. Lu, and C. K. Tse, "Direct and optimal linear active methods for stabilization of LC input filters and DC/DC converters under voltage mode control," *IEEE J. Emerg. Sel. Topics Circuits Syst.*, vol. 5, no. 3, pp. 402–412, Sep. 2015.

- [25] R. Gavagsaz-Ghoachani, L.-M. Saublet, J.-P. Martin, B. Nahid-Mobarakeh, and S. Pierfederici, "Stability analysis and active stabilization of DC power systems for electrified transportation systems, taking into account the load dynamics," *IEEE Trans. Transport. Electrific.*, vol. 3, no. 1, pp. 3–12, Mar. 2017.

- [26] X. Zhang, Q.-C. Zhong, and W.-L. Ming, "A virtual RLC damper to stabilize DC/DC converters having an LC input filter while improving the filter performance," *IEEE Trans. Power Electron.*, vol. 31, no. 12, pp. 8017–8023, Dec. 2016.

- [27] J. A. Solsona, S. G. Jorge, and C. A. Busada, "Nonlinear control of a buck converter which feeds a constant power load," *IEEE Trans. Power Electron.*, vol. 30, no. 12, pp. 7193–7201, Dec. 2015.

- [28] M. Cupelli, M. Moghimi, A. Riccobono, and A. Monti, "A comparison between synergetic control and feedback linearization for stabilizing mvdc microgrids with constant power load," in *Proc. IEEE PES Innov. Smart Grid Technol.*, Istanbul, Turkey, Oct. 2014, pp. 1–6.

- [29] J. You, M. Vilathgamuwa, and N. Ghasemi, "DC bus voltage stability improvement using disturbance observer feedforward control," *Control Eng. Pract.*, vol. 75, pp. 118–125, Jun. 2018.

- [30] Y. Zhao, W. Qiao, and D. Ha, "A sliding-mode duty-ratio controller for DC/DC buck converters with constant power loads," *IEEE Trans. Ind. Appl.*, vol. 50, no. 2, pp. 1448–1458, Mar./Apr. 2014.

- [31] S. Singh, V. Kumar, and D. Fulwani, "Mitigation of destabilising effect of CPLs in island DC micro-grid using non-linear control," *IET Power Electron.*, vol. 10, no. 3, pp. 387–397, Oct. 2017.

- [32] M. Zhang, Y. Li, F. Liu, L. Luo, Y. Cao, and M. Shahidehpour, "Voltage stability analysis and sliding-mode control method for rectifier in DC systems with constant power loads," *IEEE Trans. Emerg. Sel. Topics Power Electron.*, vol. 5, no. 4, pp. 1621–1630, Dec. 2017.

- [33] N. Vafamand, M. H. Khooban, T. Dragi ević, and F. Blaabjerg, "Networked fuzzy predictive control of power buffers for dynamic stabilization of DC microgrids," *IEEE Trans. Ind. Electron.*, vol. 66, no. 2, pp. 1356–1362, Feb. 2018.

- [34] T. Dragi ević, "Dynamic stabilization of DC microgrids with predictive control of point-of-load converters," *IEEE Trans. Power Electron.*, vol. 33, no. 12, pp. 10872–10884, Dec. 2018.

- [35] H. Mahmoudi, M. Aleenejad, and R. Ahmadi, "A new multiobjective modulated model predictive control method with adaptive objective prioritization," *IEEE Trans. Ind. Appl.*, vol. 53, no. 2, pp. 1188–1199, Mar./Apr. 2017.

- [36] H. Mosskull, "Performance and robustness evaluation of DC-link stabilization," Control Eng. Pract., vol. 44, pp. 104–116, Nov. 2015.

- [37] M.-A. Rodríguez-Licea, F.-J. Pérez-Pinal, J.-C. Nuñez-Perez, and C.-A. Herrera-Ramirez, "Nonlinear robust control for low voltage directcurrent residential microgrids with constant power loads," *Energies*, vol. 11, no. 5, pp. 1130–1149, May 2018.

- [38] B. R. Barmish and E. Jury, "New tools for robustness of linear systems," IEEE Trans. Autom. Control, vol. 39, no. 12, p. 2525, Dec. 1994.

- [39] R. L. P. de Medeiros, W. Barra, Jr., I. V. de Bessa, J. E. C. Filho, F. A. de Cavalho Ayres, Jr., and C. C. das Neves, "Robust decentralized controller for minimizing coupling effect in single inductor multiple output DC-DC converter operating in continuous conduction mode," *ISA Trans.*, vol. 73, pp. 112–129, Feb. 2018.

- [40] K. E. Lucas et al., "Robust control for DC-DC buck converter under parametric uncertainties," in Proc. 22nd Congresso Brasileiro de Automica (CBA), Brazil, USA, Sep. 2018, p. 18.

- [41] K. E. L. Marcillo, D. A. P. Guingla, E. M. Roch, W. Barra, D. A. V. Benavides, and R. L. P. de Medeiros, "Parameter optimization of an interval robust controller of a buck converter subject to parametric uncertainties," in *Proc. IEEE 3rd Ecuador Tech. Chapters Meeting* (ETCM), Cuenca, Ecuador, Oct. 2018, pp. 1–6.

- [42] S. P. Bhattacharyya, "Recent results in robust parametric stability and control," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, San Diego, CA, USA, May 1992, pp. 2707–2711.

- [43] S. P. Bhattacharyya, H. Chapellat, and L. H. Keel, Robust Control: The Parametric Approach. Upper Saddle River, NJ, USA: Prentice-Hall, 1995

- [44] S. Sumsurooah, M. Odavic, S. Bozhko, and D. Boroyevich, "Robust stability analysis of a DC/DC buck converter under multiple parametric uncertainties," *IEEE Trans. Power Electron.*, vol. 33, no. 6, pp. 5426–5441, Jun. 2018.

- [45] L. H. Keel and S. P. Bhattacharyya, "Robust stability and performance with fixed-order controllers," *Automatica*, vol. 35, no. 10, pp. 1717–1724, 1999.

- [46] L. H. Keel and S. P. Bhattacharyya, "A linear programming approach to controller design," in *Proc. 36th IEEE Conf. Decis. Control*, San Diego, CA, USA, vol. 3, Dec. 1997, pp. 2139–2148.

- [47] S. P. Bhattacharyya and L. H. Keel, "Robust control: The parametric approach," in *Proc. IFAC Symp. Adv. Control Edu.*, Tokyo, Japan, Aug. 1995, vol. 27, no. 9, pp. 49–52.

- [48] R. J. Minnichelli, J. J. Anagnost, and C. A. Desoer, "An elementary proof of Kharitonov's stability theorem with extensions," *IEEE Trans. Autom. Control*, vol. 34, no. 9, pp. 995–998, Sep. 1989.

- [49] A. D. S. Lordelo and P. A. V. Ferreira, "Interval analysis and design of robust pole assignment controllers," in *Proc. 41st IEEE Conf. Decis. Control*, Las Vegas, NV, USA, Dec. 2002, Dec. 2002, pp. 1461–1466.

- [50] S. P. Bhattacharyya, A. Datta, and L. H. Keel, *Linear Control Theory: Structure, Robustness, and Optimization*, vol. 1. Boca Raton, FL, USA: CRC Press, 2009.

- [51] K. J. Aström and B. Wittenmark, Computer-controlled Systems: Theory and Design. North Chelmsford, MA, USA: Courier Corporation, 2013.

**RENAN LANDAU PAIVA DE MEDEIROS** received the B.E., M.Sc., and Ph.D. degrees in electrical engineering from the Federal University of Pará, Brazil, in 2013, 2014, and 2018, respectively.

Since 2017, he has been a Full-Time Researcher with e-CONTROLS, a research group interested in any topics of the dynamic and control systems, with emphasis in electric power system control. He is currently an Associate Professor with the

Department of Electrical Engineering, Federal University of Amazonas. He has experience in electrical engineering, with emphasis on automation and control of industrial and electrical power systems, and multivariable robust control and application. His main areas of expertise and research interests include nonlinear control, multivariable robust control, and modeling and designing a robust control for electrical power systems.

**KEVIN EDUARDO LUCAS MARCILLO** received the bachelor's degree in electronic and telecommunications engineering from the Escuela Superior Politécnica del Litoral, Ecuador, in 2015, and the master's degree in electrical engineering from the Federal University of Pará (UFPA), Brazil, in 2018

He is currently a Researcher with the Power Systems Control Laboratory (LACSPOT), UFPA. He has experience in electrical engineering, with

emphasis on electronics, data acquisition system, control and automation of electrical and industrial processes, power electronics, hydraulic system, and control systems applied in power generation. His main research topic includes modeling and robust control of industrial and electronic power systems.

**ERICK MELO ROCHA** received the bachelor's and M.Sc. degrees in electrical engineering from the Federal University of Paré (UFPA), Brazil, in 2010 and 2012, respectively, where he is currently pursuing the Ph.D. degree in electrical engineering.

He is currently a Lecturer with the Department of Electrical Engineering, UFPA. He has experience in electrical engineering, with emphasis on industrial automation and control systems. His

research topics include detection and fault diagnosis, and robust control techniques.

## **DOUGLAS ANTONIO PLAZA GUINGLA** received the bachelor's degree in electrical engineering from the Escuela Superior Politécnica del

neering from the Escuela Superior Politécnica del Litoral (ESPOL), Guayaquil, Ecuador, in 2003, the master's degree in industrial control from the Universidad de Ibagué, Ibagué, Colombia, in 2008, and the Ph.D. Diploma degree in electromechanical engineering from Ghent University, Ghent, Belgium, in 2013.

From 2007 to 2012, he was a Full-Time Researcher with the Laboratory of Hydrology and Water Management, Ghent University. He has been an Associate Professor with the Electrical and Computer Engineering Faculty, ESPOL, since 2013. He is currently the Chair of the Master Program in Automation and Control with ESPOL. His areas of expertise and research interests include Kalman filtering and smoothing, sequential Monte Carlo methods, hydrologic modeling, hydrologic data assimilation, model predictive control, and nonlinear control. He is the Chair of the IEEE Control Systems and Industrial Electronics Societies, Ecuador Section.

**DAVID ALEJANDRO VACA BENAVIDES** received the bachelor's degree in electronic and telecommunications engineering from the Escuela Superior Politécnica del Litoral (ESPOL), Guayaquil, Ecuador, in 2014, and the M.Sc. degree in electrical engineering from the University of Applied Sciences of Southern Switzerland,

He has been a Lecturer with the Faculty of Electrical and Computer Engineering, ESPOL,

since 2016. He has experience in electrical engineering, with emphasis on biomedical instrumentation, signal processing, and data acquisition. His research topics include medical data processing on embedded systems and mixed-signal electronic design for medical applications.

Manno, Switzerland, in 2016.

**WALTER BARRA, Jr.** received the B.E., M.Sc., and Ph.D. degrees in electrical engineering from the Federal University of Pará (UFPA), Brazil, in 1991, 1997, and 2001, respectively.

He is currently an Associate Professor with the Department of Electrical Engineering, UFPA. He has experience in electrical engineering, with emphasis on automation and control of industrial and electrical power systems. His main research topic includes modeling and robust control of industrial and electric power systems.

**FABRICIO GONZALEZ NOGUEIRA** received the B.E., M.Sc., and Ph.D. degrees in electrical engineering from the Federal University of Pará, Brazil, in 2007, 2008, and 2012, respectively.

He is currently an Adjunct Professor with the Faculty of Electrical Engineering, Federal University of Ceará, Brazil. He has experience in electrical engineering, with emphasis on control of electrical power systems. His main research topics include system identification and robust control with application in electric power systems.

. .