# Southampton

### University of Southampton Research Repository ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

#### UNIVERSITY OF SOUTHAMPTON

Faculty of Engineering, Science and Mathematics School of Electronics and Computer Science

### Investigation into Voltage and Process Variation-Aware Manufacturing Test

by

Bo Urban Ingelsson

A thesis submitted for the degree of Doctor of Philosophy

July 2009

#### UNIVERSITY OF SOUTHAMPTON <u>ABSTRACT</u>

#### FACULTY OF ENGINEERING, SCIENCE AND MATHEMATICS SCHOOL OF ELECTRONICS AND COMPUTER SCIENCE

#### Doctor of Philosophy

#### Investigation into Voltage and Process Variation-Aware Manufacturing Test by Bo Urban Ingelsson

Increasing integration and complexity in IC design provides challenges for manufacturing testing. This thesis studies how process and supply voltage variation influence defect behaviour to determine the impact on manufacturing test cost and quality. The focus is on logic testing of static CMOS designs with respect to two important defect types in deep submicron CMOS: resistive bridges and full opens.

The first part of the thesis addresses testing for resistive bridge defects in designs with multiple supply voltage settings. To enable analysis, a fault simulator is developed using a supply voltage-aware model for bridge defect behaviour. The analysis shows that for high defect coverage it is necessary to perform test for more than one supply voltage setting, due to supply voltage-dependent behaviour. A low-cost and effective test method is presented consisting of multi-voltage test generation that achieves high defect coverage and test set size reduction without compromise to defect coverage. Experiments on synthesised benchmarks with realistic bridge locations validate the proposed method.

The second part focuses on the behaviour of full open defects under supply voltage variation. The aim is to determine the appropriate value of supply voltage to use when testing. Two models are considered for the behaviour of full open defects with and without gate tunnelling leakage influence. Analysis of the supply voltage-dependent behaviour of full open defects is performed to determine if it is required to test using more than one supply voltage to detect all full open defects. Experiments on synthesised benchmarks using an extended version of the fault simulator tool mentioned above, measure the quantitative impact of supply voltage variation on defect coverage.

The final part studies the impact of process variation on the behaviour of bridge defects. Detailed analysis using synthesised ISCAS benchmarks and realistic bridge model shows that process variation leads to additional faults. If process variation is not considered in test generation, the test will fail to detect some of these faults, which leads to test escapes. A novel metric to quantify the impact of process variation on test quality is employed in the development of a new test generation tool, which achieves high bridge defect coverage. The method achieves a user-specified test quality with test sets which are smaller than test sets generated without consideration of process variation.

### Contents

| A | Acknowledgementsix |         |                                                                    |           |

|---|--------------------|---------|--------------------------------------------------------------------|-----------|

| 1 | Intr               | oducti  | on                                                                 | 1         |

|   | 1.1                | Dynan   | nic Voltage and Frequency Scaling                                  | 2         |

|   | 1.2                |         | Voltage Design                                                     | 5         |

|   | 1.3                | Proces  | s Variation                                                        | 6         |

|   | 1.4                | Manuf   | acturing Testing of Integrated Circuits                            | 8         |

|   |                    | 1.4.1   | Defect Coverage by Fault Detection                                 | 9         |

|   |                    | 1.4.2   | Fault Modelling                                                    | 10        |

|   |                    | 1.4.3   | Fault Simulation                                                   | 11        |

|   |                    | 1.4.4   | Test Generation                                                    | 11        |

|   |                    | 1.4.5   | Scan Testing                                                       | 13        |

|   |                    | 1.4.6   | Test Cost                                                          | 14        |

|   |                    | 1.4.7   | Logic Testing, Delay Fault Testing and Current-Based Testing       | 14        |

|   |                    | 1.4.8   | Testing for Bridge Defects                                         | 16        |

|   |                    | 1.4.9   | Testing for Open Defects                                           | 18        |

|   |                    | 1.4.10  | Testing Low-Power ICs                                              | 19        |

|   | 1.5                | Thesis  | Outline and Scope                                                  | 21        |

|   | 1.6                | List of | Publications from this Ph.D. Project                               | 22        |

| 2 | Lite               | erature | Review and Motivation                                              | <b>24</b> |

|   | 2.1                | Bridgi  | ng Faults                                                          | 24        |

|   |                    | 2.1.1   | Stuck-at-Related Models                                            | 24        |

|   |                    | 2.1.2   | Models that Abstract From the Bridge Resistance                    | 25        |

|   |                    | 2.1.3   | Models that Consider the Bridge Resistance                         | 26        |

|   |                    | 2.1.4   | Test Generation and Fault Simulation for Resistive Bridging Faults | 29        |

|   | 2.2                | Full O  | pen Faults                                                         | 30        |

|   |                    | 2.2.1   | Full Open Defect Location                                          | 30        |

|   |                    | 2.2.2   | Gate Tunnelling Leakage Model                                      | 30        |

|   |                    | 2.2.3   | Capacitive Coupling Model                                          | 33        |

|   |                    | 2.2.4   | Test Generation and Fault Simulation of Full Open Defects          | 34        |

|   | 2.3                |         | Voltage-Dependent Defects and Test Methods                         | 35        |

|   |                    | 2.3.1   | Supply Voltage-Aware Test Methods for Bridge Defects               | 37        |

|   |                    | 2.3.2   | Supply Voltage-Aware Test Methods for Full Open Defects            | 38        |

|   | 2.4                |         | s Variation-Aware Test Methods                                     | 39        |

|   |                    | 2.4.1   | Delay Fault Testing under Process Variation                        | 39        |

|   |                    | 2.4.2   | Current-Based Testing under Process Variation                      | 40        |

|   |     | 2.4.3   | Logic Testing under Process Variation                            | . 40  |

|---|-----|---------|------------------------------------------------------------------|-------|

|   | 2.5 | Motiv   | ration                                                           | . 41  |

| 3 | Tes | ting fo | or Resistive Bridges under Supply Voltage Variation              | 43    |

|   | 3.1 | Analy   | rsis and Statement of Problem                                    | . 44  |

|   |     | 3.1.1   | Modelling of Resistive Bridging Faults                           | . 46  |

|   |     | 3.1.2   | Circuit Behaviour in the Presence of Resistive Bridging Faults . | . 47  |

|   |     | 3.1.3   | Multi-Voltage-Aware Defect Coverage Metric                       | . 50  |

|   |     | 3.1.4   | Test Generation                                                  | . 51  |

|   |     | 3.1.5   | Motivation of Testing Using Multiple Supply Voltages             | . 51  |

|   | 3.2 | Softw   | are Tool Suite                                                   | . 58  |

|   |     | 3.2.1   | Bridge Location List Generation                                  |       |

|   |     | 3.2.2   | Gate Library Characterisation                                    |       |

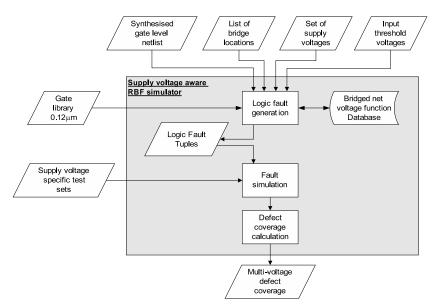

|   |     | 3.2.3   | Supply Voltage-Aware Resistive Bridging Fault Simulation         |       |

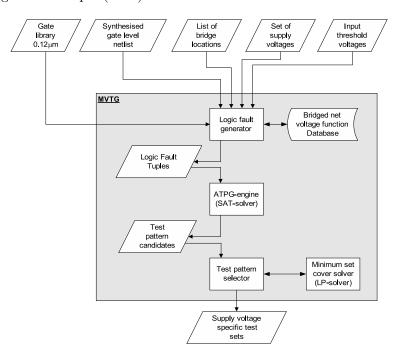

|   |     | 3.2.4   | Multi-Voltage Test Generation                                    |       |

|   |     | 3.2.5   | Test Set Post-Processing                                         |       |

|   | 3.3 | · ·     | rimental Results                                                 |       |

|   |     | 3.3.1   | Considering a Bridge Resistance Occurrence Distribution          |       |

|   |     | 3.3.2   | Multi-Voltage Test Generation Results                            |       |

|   |     | 3.3.3   | Test Set Size Reduction                                          |       |

|   |     | 3.3.4   | Integrated Flow with TetraMAX                                    |       |

|   |     | 3.3.5   | Summary                                                          |       |

|   | 3.4 | Concl   | uding Remarks                                                    | . 77  |

| 4 | Tes | _       | or Full Open Defects under Supply Voltage Variation              | 78    |

|   | 4.1 | Analy   | rsis and Statement of Problem                                    |       |

|   |     | 4.1.1   | Logic Behaviour                                                  |       |

|   |     | 4.1.2   | Test Methods for Full Open Defects                               |       |

|   |     | 4.1.3   | Supply Voltage-Dependent Detectability                           |       |

|   | 4.2 |         | Opens Influenced by Capacitive Coupling                          |       |

|   |     | 4.2.1   | Model for the Final Victim Net Voltage                           |       |

|   |     | 4.2.2   | Simulation of Full Open Defect Under Supply Voltage Variation    |       |

|   |     | 4.2.3   | Coupling Capacitance-Aware Analysis of Full Open Behaviour .     |       |

|   | 4.3 |         | Dens Influenced by Gate Tunnelling Leakage                       |       |

|   |     | 4.3.1   | Simulation of Full Open Defect Under Supply Voltage Variation    |       |

|   |     | 4.3.2   | Gate Tunnelling Leakage-Aware Analysis of Full Open Behaviour    |       |

|   |     | 4.3.3   | Model for the Final Victim Net Voltage                           |       |

|   | 4.4 |         | rsis Methodology                                                 |       |

|   |     | 4.4.1   | Prototype Tool Flow                                              |       |

|   |     | 4.4.2   | Fault Site Simulation                                            |       |

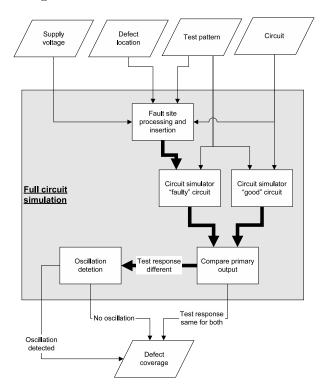

|   |     | 4.4.3   | Fault Simulation                                                 |       |

|   | 4.5 | -       | rimental Results                                                 |       |

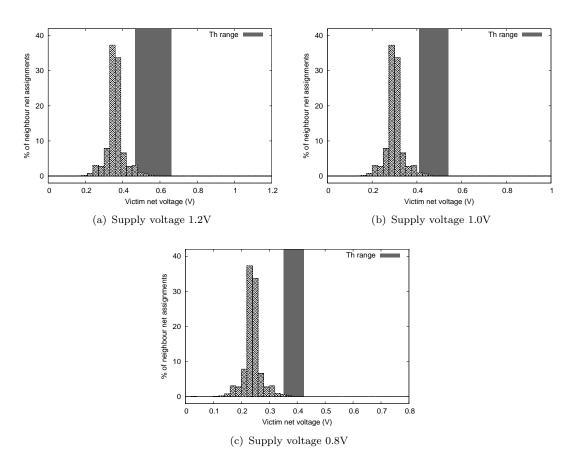

|   |     | 4.5.1   | The Distribution of Victim Net Voltage                           |       |

|   |     |         | 4.5.1.1 Leakage Unaware Model                                    |       |

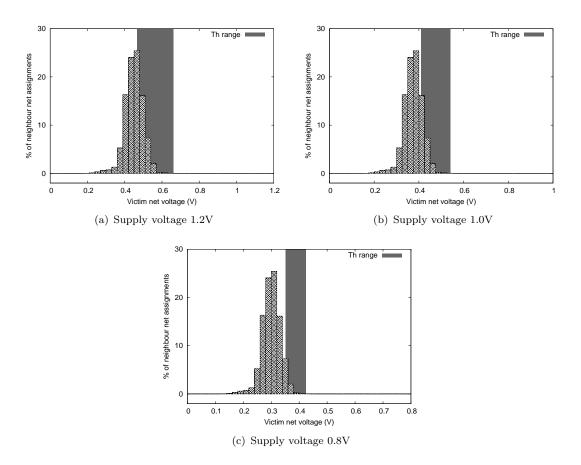

|   |     |         | 4.5.1.2 Leakage Aware Model                                      |       |

|   |     | 4.5.2   | The Quantity of Defects with Supply Voltage-Dependent Behaviou   |       |

|   |     | 4.5.3   | Supply Voltage-Dependent Detectability                           | . 113 |

|    |                 | 4.5.4                        | Summary                                                                                         | . 114 |

|----|-----------------|------------------------------|-------------------------------------------------------------------------------------------------|-------|

|    | 4.6             | Conclu                       | lding Remarks                                                                                   | . 115 |

| 5  | Pro             | $\mathbf{cess} \ \mathbf{V}$ | ariation-Aware Testing for Resistive Bridge Defects                                             | 117   |

|    | 5.1             | Backg                        | round and Prior Work                                                                            | . 119 |

|    | 5.2             | Motiva                       | ation $\ldots$ | . 121 |

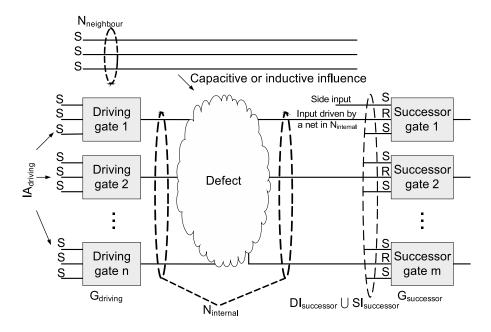

|    |                 | 5.2.1                        | Bridging Fault Analysis in the Presence of Process Variation                                    | . 123 |

|    |                 | 5.2.2                        | Test Escapes                                                                                    | . 126 |

|    | 5.3             | Test R                       | Robustness                                                                                      | . 128 |

|    |                 | 5.3.1                        | Test Robustness Calculation                                                                     | . 128 |

|    |                 | 5.3.2                        | Preparation of Test Robustness Calculation                                                      | . 131 |

|    |                 | 5.3.3                        | Considerations for Accuracy in the Test Robustness Metric                                       | . 133 |

|    |                 | 5.3.4                        | Estimating the Resistance Range for a Logic Fault Under Process                                 |       |

|    |                 |                              | Variation                                                                                       |       |

|    | 5.4             |                              | ss Variation Aware Test Generation                                                              |       |

|    | 5.5             | Experi                       | imental Results                                                                                 |       |

|    |                 | 5.5.1                        | Analysis: Test Robustness Reflects Test Quality                                                 |       |

|    |                 | 5.5.2                        | Analysis: Process Variation Impact on Test Quality                                              |       |

|    |                 | 5.5.3                        | Test Quality Improvement from Variation-Aware Test Generation                                   |       |

|    | 5.6             | Conclu                       | Iding Remarks                                                                                   | . 148 |

| 6  | Con             |                              | ns and Future Work                                                                              | 150   |

|    | 6.1             | Contri                       | butions in this Thesis                                                                          | . 150 |

|    | 6.2             | Future                       | Work                                                                                            | . 153 |

| A  | Fau             | lt Site                      | Schematic                                                                                       | 155   |

| в  | SAT             | <b>F-Base</b>                | d ATPG                                                                                          | 158   |

| Bi | Bibliography 16 |                              |                                                                                                 | 161   |

# List of Figures

| 1.1  | Task schedules with (bottom) and without (top) DVFS                                            | . 3  |

|------|------------------------------------------------------------------------------------------------|------|

| 1.2  | Supply voltage and clock frequency settings for three DVFS designs                             | . 4  |

| 1.3  | Example of multi-voltage design principle                                                      | . 6  |

| 1.4  | Test application procedure for scan-based testing                                              | . 13 |

| 1.5  | Bridge defect types                                                                            | . 17 |

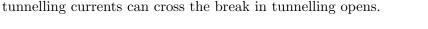

| 1.6  | Open defect                                                                                    | . 19 |

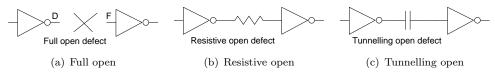

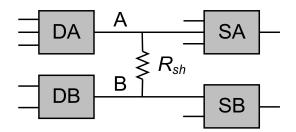

| 2.1  | Circuit where nets A and B are bridged                                                         | . 25 |

| 2.2  | Example resistive bridge                                                                       | . 27 |

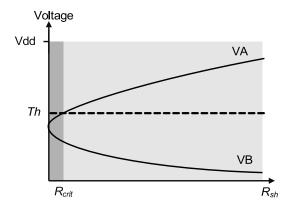

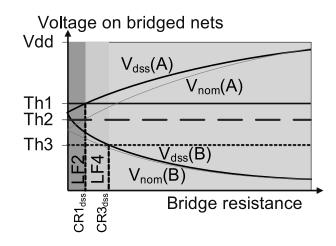

| 2.3  | The voltage on the bridged nets as it depends on the bridge resistance .                       | . 27 |

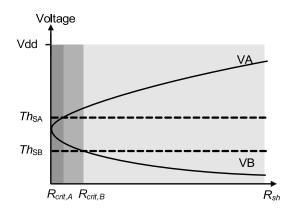

| 2.4  | The resistance ranges corresponding to the logic threshold voltages $Th_{SA}$<br>and $Th_{SB}$ | . 28 |

| 2.5  | A net with several possible full open locations                                                |      |

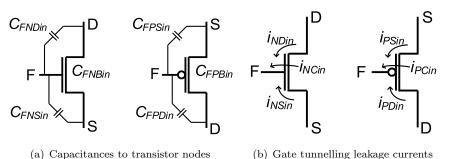

| 2.6  | Gate tunnelling leakage current components                                                     |      |

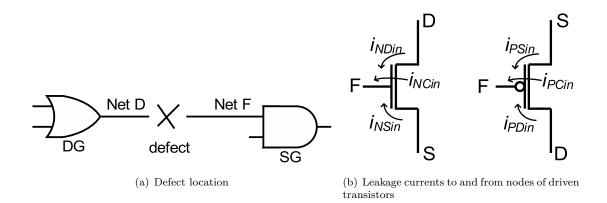

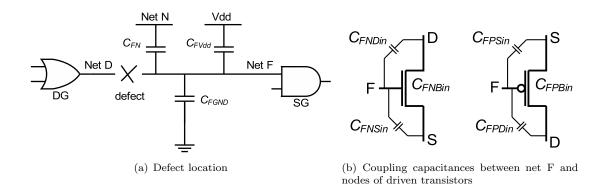

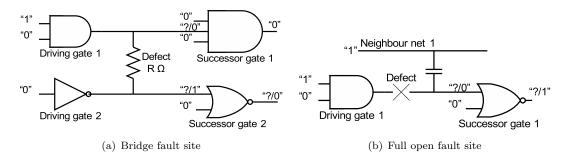

| 2.7  | A full open defect which is influenced by gate tunnelling leakage                              |      |

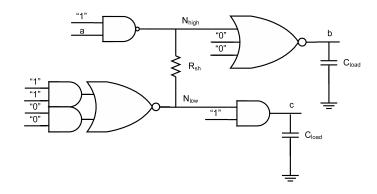

| 2.8  | A full open defect influenced by capacitive coupling                                           |      |

| 2.0  |                                                                                                |      |

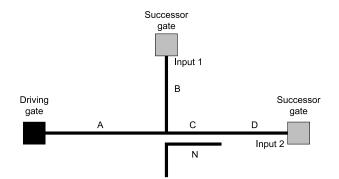

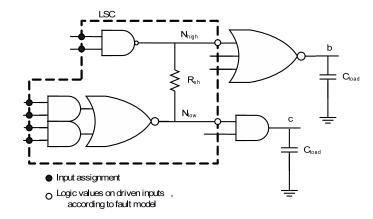

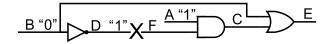

| 3.1  | Example fault site with bridging defect                                                        | . 45 |

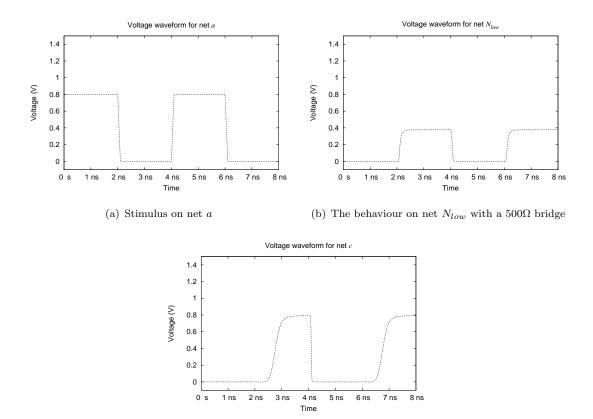

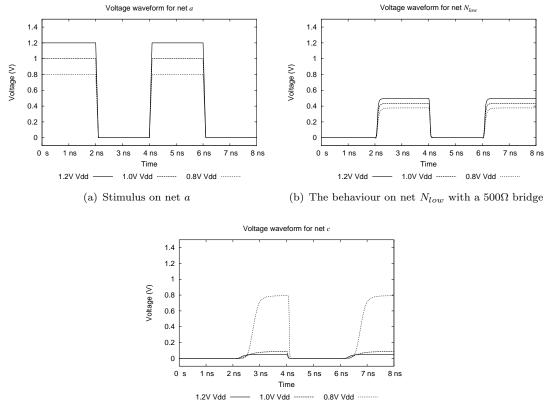

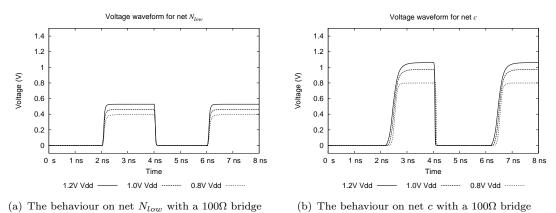

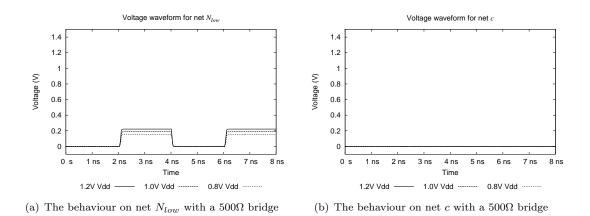

| 3.2  | Waveforms for simulation on the fault site in Figure 3.1                                       | . 46 |

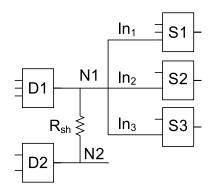

| 3.3  | Bridge defect example                                                                          | . 47 |

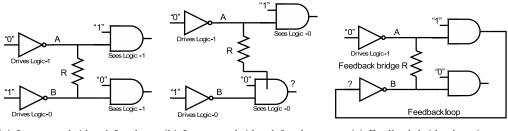

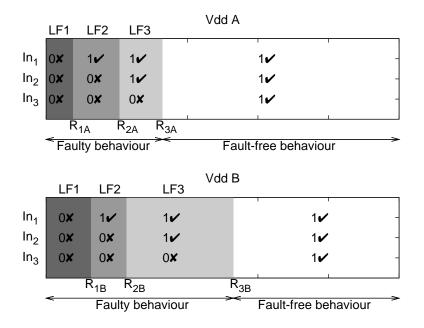

| 3.4  | Bridging fault behaviour                                                                       | . 48 |

| 3.5  | Logic State Configuration example                                                              | . 49 |

| 3.6  | Waveforms for simulation on the fault site in Figure 3.1 for supply voltage                    |      |

|      | settings 0.8V, 1.0V and 1.2V and a 500 $\Omega$ bridge                                         | . 52 |

| 3.7  | Waveforms for simulation on the fault site in Figure 3.1 for supply voltage                    |      |

|      | settings 0.8V, 1.0V and 1.2V and a 500 $\Omega$ bridge                                         | . 53 |

| 3.8  | Waveforms for simulation on the fault site in Figure 3.1 for supply voltage                    |      |

|      | settings 0.8V, 1.0V and 1.2V and a 500 $\Omega$ bridge and the altered input                   | •    |

|      | assignment $\{1, 1, 1, 1\}$ to the gate that drives $N_{low}$                                  |      |

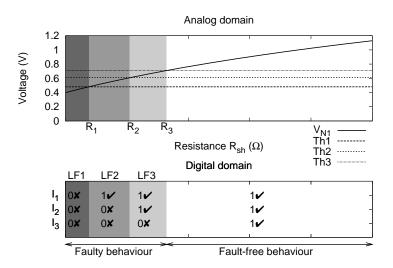

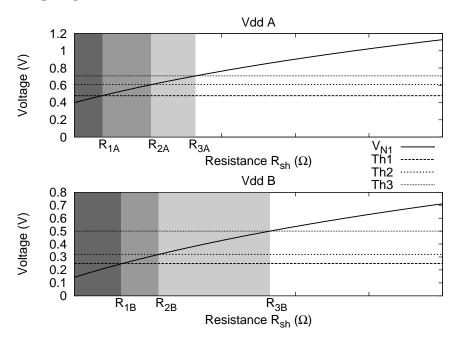

| 3.9  | Effect of supply voltage on bridging fault behaviour: Analog domain                            |      |

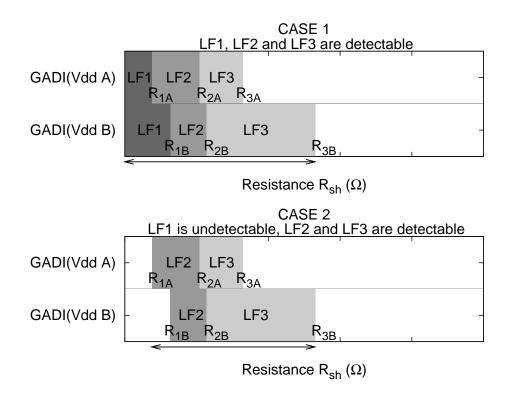

|      | Effect of supply voltage on bridging fault behaviour: Digital domain                           | . 54 |

| 3.11 | Effect of supply voltage on bridging fault behaviour: Observable bridging                      |      |

| 0.10 | resistance ranges                                                                              | . 55 |

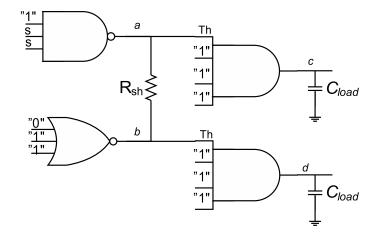

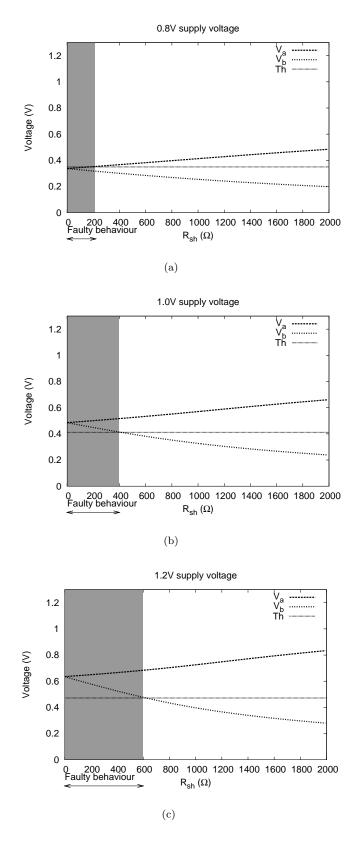

| 3.12 | Example bridge defect that is best detected using the highest supply volt-<br>age setting      | . 56 |

| 3.13 | The voltage on net $a$ and net $b$ in Figure 3.12 as it depends on the bridge                  | - •  |

|      | resistance and the supply voltage                                                              | . 57 |

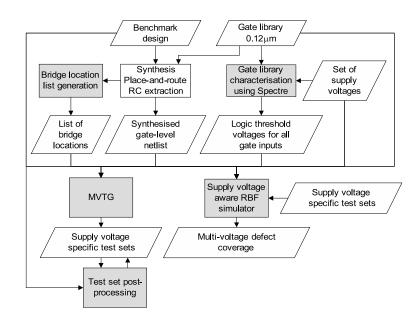

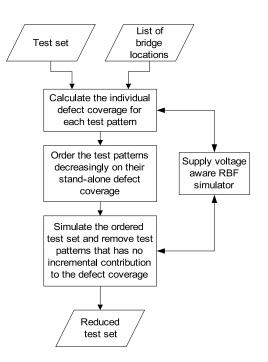

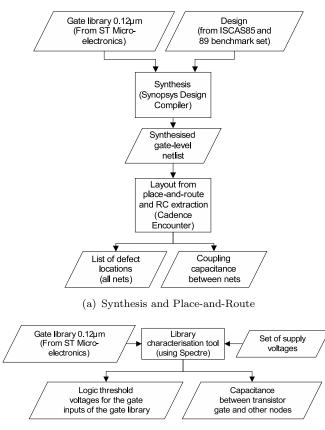

| 3.14 | SMuVoRBAT tool flow                                                                            |      |

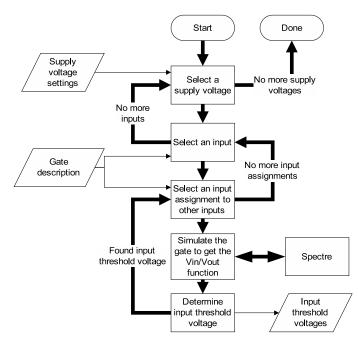

|      | Gate library characterisation flow                                                             |      |

|      |                                                                                                |      |

| 3.16                                      | Detailed flow for the fault simulator SVARFS                                         | . 63  |

|-------------------------------------------|--------------------------------------------------------------------------------------|-------|

| 3.17                                      | Fault simulation algorithm used in SVARFS                                            | . 64  |

| 3.18                                      | FindLogicValue method                                                                | . 65  |

| 3.19                                      | Detailed flow for the Multi-Voltage Test Generation method                           | . 66  |

| 3.20                                      | LP problem formulation used to select the minimum set of test patterns               |       |

|                                           | to cover the full range of detectable bridge resistance                              | . 67  |

| 3.21                                      | The Multi-Voltage Test Generation method (MVTG)                                      | . 69  |

| 3.22                                      | Test set post-processing flow for test set size reduction                            | . 70  |

| 3.23                                      | The distribution of resistance values that cannot be detected at 0.8V supply voltage | . 71  |

| 4 1                                       |                                                                                      | 20    |

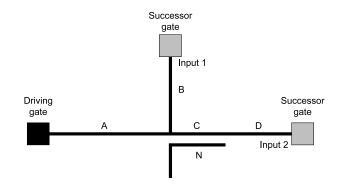

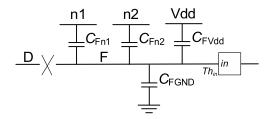

| 4.1                                       | A full open defect                                                                   |       |

| 4.2                                       | Influence from input $in \in IN$ on the victim net F                                 |       |

| 4.3                                       | Net segmentation representing possible defect locations                              |       |

| 4.4                                       | Defect that can only be detected through stuck-at-0 test                             |       |

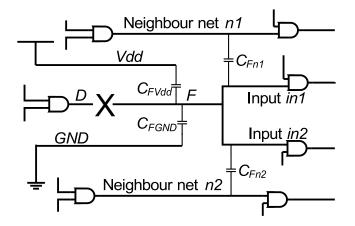

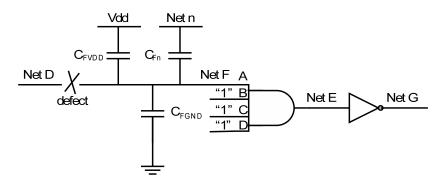

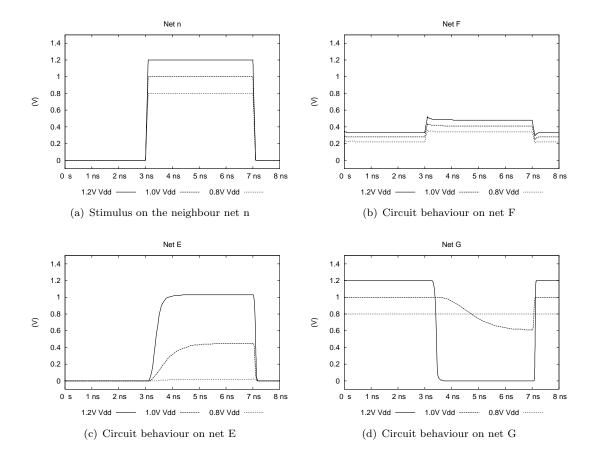

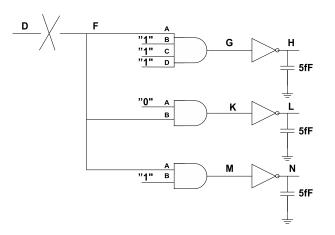

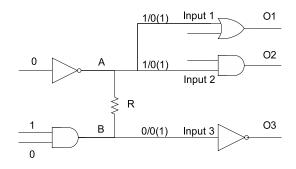

| $\begin{array}{c} 4.5 \\ 4.6 \end{array}$ | Simulated fault site with full open defect on interconnect                           |       |

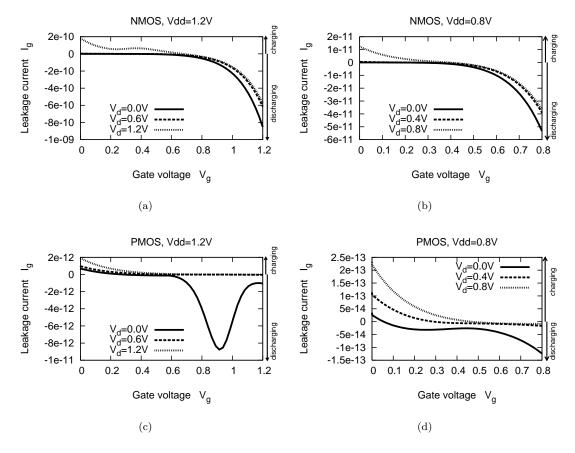

| 4.0<br>4.7                                | Single supply voltage example of full open defect                                    |       |

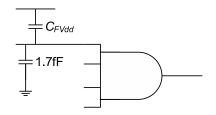

| 4.7<br>4.8                                | Setup for studying the capacitance between the gate input and nodes of               | . 90  |

| 4.0                                       | driven transistors                                                                   | . 92  |

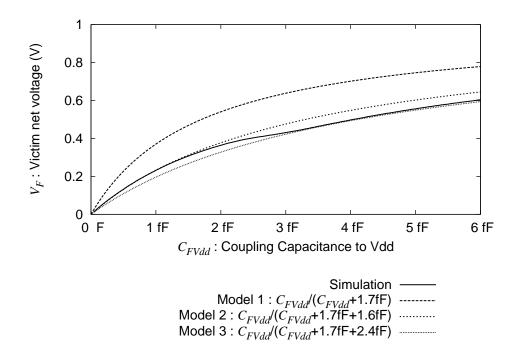

| 4.9                                       | Victim net voltage versus coupling capacitance to supply voltage                     |       |

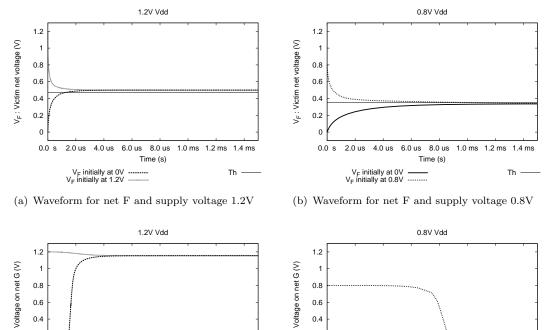

| 4.10                                      |                                                                                      |       |

| 4.11                                      | Waveforms for simulation of the circuit in Figure 4.10                               |       |

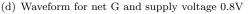

|                                           | Gate tunnelling leakage current for 1.2V and 0.8V supply voltage                     |       |

|                                           | Example: modelling the victim net voltage in the presence of gate tun-               |       |

|                                           | nelling leakage                                                                      | . 102 |

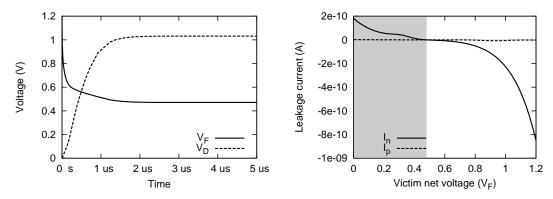

| 4.14                                      | Tool flow to study the detectability of full open defects                            | . 103 |

| 4.15                                      | Flows used to prepare data for analysis of full open defects                         | . 104 |

| 4.16                                      | Fault simulation flow                                                                | . 106 |

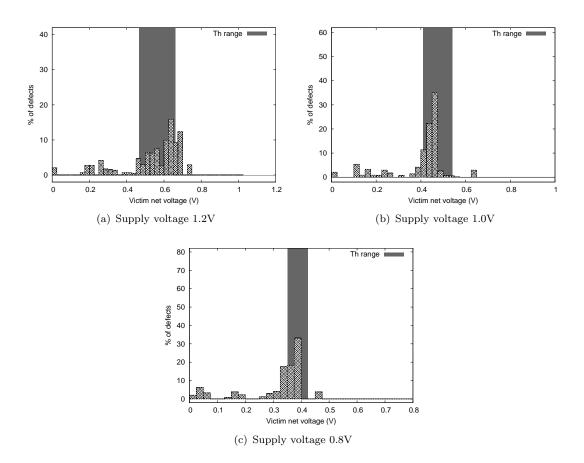

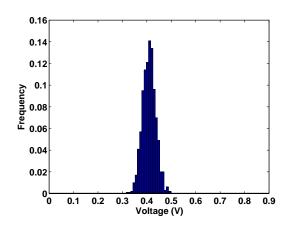

| 4.17                                      | Distribution of victim net voltages, design C1355                                    | . 108 |

| 4.18                                      | Distribution of victim net voltages, design S641                                     | . 109 |

| 4.19                                      | Distribution of victim net voltages using the leakage aware model, design            |       |

|                                           | C1355                                                                                | . 110 |

| 5.1                                       | Example bridge location                                                              | 121   |

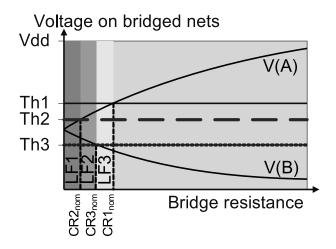

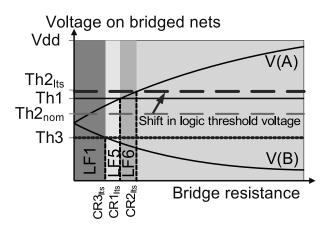

| 5.2                                       | Nominal parameter behaviour of example bridge                                        |       |

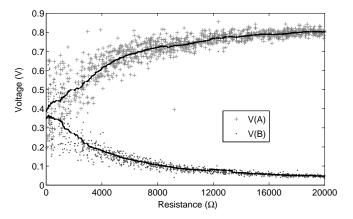

| 5.3                                       | V(A) and $V(B)$ for parameter samples and defect resistances from a                  | . 122 |

| 0.0                                       | Monte-Carlo simulation                                                               | . 124 |

| 5.4                                       | Shift in the drive strength balance of driving gates                                 |       |

| 5.5                                       | Process variation induced values of the logic threshold voltage for the              |       |

|                                           | example gate input                                                                   | . 126 |

| 5.6                                       | Shift in logic threshold voltage Th2                                                 |       |

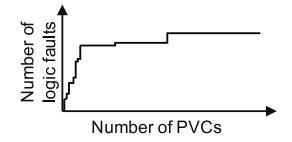

| 5.7                                       | Logic behaviours for the three configurations of parameter values                    |       |

| 5.8                                       | Typical scenario when identifying variation induced faults by simulating             |       |

|                                           | PVCs                                                                                 | . 133 |

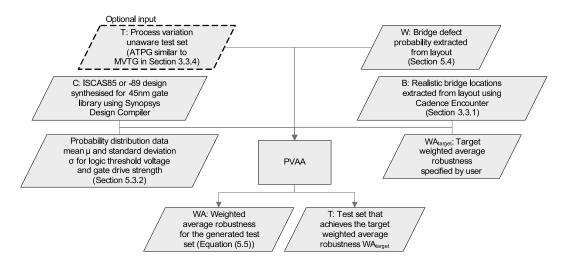

| 5.9                                       | PVAA top level flow                                                                  | . 135 |

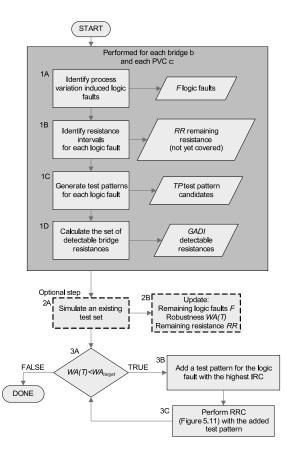

| 5.10                                      | The flow of the process variation-aware test generation method (PVAA)                | . 137 |

| 5.11                                      | Algorithm RRC - Robustness ReCalculation                                             | . 138 |

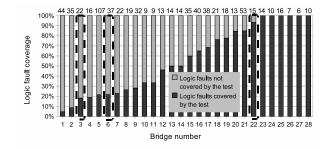

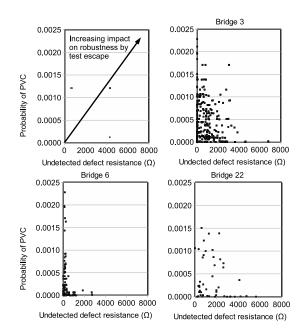

| 5.12 | Detected and undetected logic faults on benchmark circuit S838 140                     |

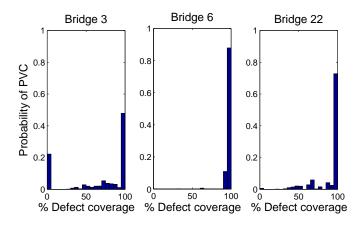

|------|----------------------------------------------------------------------------------------|

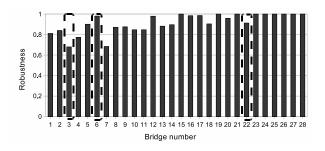

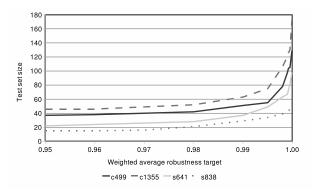

| 5.13 | Robustness for the bridges of benchmark circuit S838                                   |

| 5.14 | Test escapes of bridge 3, 6 and 22 of benchmark S838 $\ldots \ldots \ldots \ldots 141$ |

| 5.15 | Probability of defect coverage for bridge 3, 6 and 22 of design S838 141               |

| 5.16 | The number of test patterns required to achieve a given weighted average               |

|      | robustness                                                                             |

| Λ 1  | Fault site components                                                                  |

|      |                                                                                        |

| A.2  | Example fault sites                                                                    |

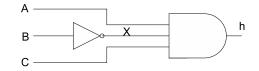

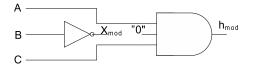

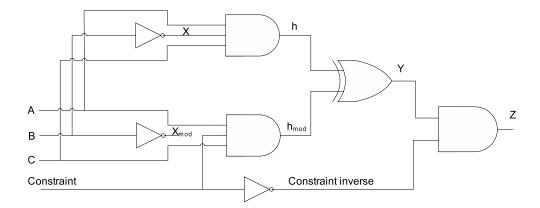

| B.1  | A circuit that implements the Boolean formula in Equation B.1 158                      |

|      |                                                                                        |

| Б.2  | The circuit in Equation B.1 modified by fault $F$                                      |

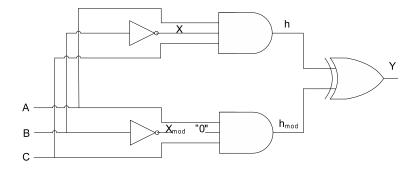

| B.3  | A circuit for the Satisfiability problem of fault $F$ in Figure B.1 159                |

| B.4  | A circuit that forces a Logic-0 on the input that is influenced by fault $F$ . 160     |

|      |                                                                                        |

### List of Tables

| 2.1 | Test types and test supply voltages that are effective for the reviewed defect types    |

|-----|-----------------------------------------------------------------------------------------|

| 3.1 | Logic threshold voltage ranges for three supply voltages                                |

| 3.2 | Results of Multi-Voltage Test Generation                                                |

| 3.3 | Defect coverage for the supply voltage-specific test sets from MVTG 74                  |

| 3.4 | Reduced test-set sizes using the post-processing step on the test sets from             |

|     | Table 3.2         75                                                                    |

| 3.5 | Results of using TetraMAX and MVTG as a combined test generation flow 76                |

| 4.1 | Values used to generate Table 4.2                                                       |

| 4.2 | Victim net voltage for various neighbour net assignments 90                             |

| 4.3 | The victim net voltages for given neighbour net assignments and supply voltage settings |

| 4.4 | The logic threshold voltage $Th_{in}$ for three supply voltage settings 91              |

| 4.5 | Defects with supply voltage-dependent neighbour assignments 111                         |

| 4.6 | Vdd dependency factor for supply voltage-dependent defects (leakage un-                 |

|     | aware model)                                                                            |

| 4.7 | Defect coverage for pseudo-random test patterns                                         |

| 5.1 | Example robustness calculation                                                          |

| 5.2 | Varied process parameters                                                               |

| 5.3 | Test robustness for benchmark circuits and corresponding process variation-             |

|     | unaware tests                                                                           |

| 5.4 | Results for the original test set augmented with test patterns generated                |

|     | by PVAA                                                                                 |

| 5.5 | Results achieved by the process variation-aware test generation method . 146            |

# DECLARATION OF AUTHORSHIP

I, Bo Urban Ingelsson, declare that the thesis entitled *Investigation into Voltage and Process Variation-Aware Manufacturing Test* and the work presented in the thesis are both my own, and have been generated by me as the result of my own original research. I confirm that:

- this work was done wholly or mainly while in candidature for a research degree at this University;

- where any part of the thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- where I have consulted the published work of others, this is always clearly attributed;

- where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

- where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- parts of this work have been published as listed in Section 1.6

Signed:

Date:

#### Acknowledgements

Throughout this Ph.D. project, I have benefited from the support and guidance of my supervisor Prof. Bashir M. Al-Hashimi, to whom I am deeply thankful. I am grateful for the funding and research facilities provided by the School of Electronics and Computer Science of the University of Southampton.

A big "thank you" to every-one who has been helpful to me in preparation of the conference and journal papers, especially my co-authors Dr. Paul Rosinger, Saqib Khursheed, Dr. Peter Harrod and Prof. Sudhakar Reddy.

This Ph.D. project has benefited from discussions with several very helpful people, and I want to thank them. Thank you Prof. Sandip Kundu, Dr. Harry Oldham, Dr. Piet Engelke, Dr. Ilia Polian, Prof. Krishnendu Chakrabarty, Prof. David Flynn, Paul Hughes, Matthew Collins, Ross Torkington, Jonathan Barker, Rishad A. Shafik, Dr. Noohul Basher Zain Ali, Dr. Biswajit Mishra, Dr. Matthew Swabey, Dr. Ashish Darbari, Karthik Baddam, Mustafa Imran Ali and Dr. Simon Ogg.

I am thankful to Prof. Erik Larsson, Erik Jan Marinissen and Dr. Sandeep Goel for introducing me to test research and for encouraging me to pursue this Ph.D.

Finally, I would like to thank my parents, Bo and Ann-Sofie Ingelsson, and my siblings Emma Ingelsson Alkbring, Ida and Lisa Ingelsson for their love, support and understanding over the past three years. S.D.G.

### Chapter 1

### Introduction

Since the technology for manufacturing integrated circuits (ICs) was invented, the level of integration has continued to increase [1], leading to increased functionality, increased performance and ever smaller transistors. This development has lead to challenges in manufacturing testing of ICs. The research community has addressed many of these challenges, but among the ones that remain to be addressed is the problem of testing ICs in the presence of different types of variation. Two types of variation are addressed in this thesis with regard to their influence on manufacturing testing: process and supply voltage variation.

To see why these types of variation should be studied, consider that recent designs have transistors with a length of 45nm or below. The manufacturing of such small transistors is prone to process variation, a fact that until recently has been ignored in development on manufacturing test methods. Similarly, supply voltage variation, as is employed in several modern low-power designs, has not been considered in terms of its impact on manufacturing test. State-of-the-art test methods tend to use abstract models of how defects occur and behave to simplify test generation and several techniques rely on the ability of such tests to detect also defects that are not explicitly modelled. While these abstract models do not consider process variation and supply voltage variation it is important to study the influence of such variation on manufacturing test.

This thesis studies the impact of supply voltage variation and process variation on manufacturing testing with particular regard to logic testing of static CMOS circuits. Two important defect types are investigated, namely resistive bridge defects and full open defects, with the aim of developing test methods to cope with any negative influence of the considered variation on test cost and test quality.

The chapter at hand provides background on relevant concepts used in the thesis. In particular, the chapter includes background on how the supply voltage is varied in low power IC design (Section 1.1 and Section 1.2) and background on process variation

(Section 1.3). Furthermore, there is a review of many concepts in manufacturing testing that are used in the thesis (Section 1.4). Subsequently, the outline of the thesis is given along with a list of publications that have resulted from the presented research.

#### 1.1 Dynamic Voltage and Frequency Scaling

The complexity of integrated circuits in battery-driven applications has been steadily increasing. The usability of such applications depends on the battery life time [2] and there are two ways of increasing the battery life time. Either improve the battery or reduce the power consumption of the device. Development of new battery technology has been lagging behind [3]. Therefore, the trend is to reduce the power consumption of integrated circuits by low power circuit design. Two main low-power design techniques, namely Multi-Voltage design and Dynamic Voltage and Frequency Scaling (DVFS), adjust the supply voltage to limit power consumption. This thesis studies the impact of such supply voltage variation on the behaviour of bridge and open defects (Chapter 3 and Chapter 4) and investigate how tests can be generated to detect defects under supply voltage variation. Therefore, this section and the next discuss DVFS and multi-voltage design respectively.

DVFS is a technique used in low-power IC design, which uses a range of operational supply voltages to implement power modes. DVFS utilises the fact that the power that is due to switching of logic states in a digital CMOS circuit is proportional to the square of the supply voltage. This relation is shown in Equation 1.1 where  $P_{Dyn}$  is the dynamic power consumption due to switching activity, f is the clock frequency and Vdd is the supply voltage.

$$P_{Dyn} \propto f \cdot V dd^2 \tag{1.1}$$

This shows that using a lower supply voltage leads to less dynamic power consumption. However, a lower supply voltage also leads to slower operation of logic gates and therefore lower performance. To see how the dynamic power consumption  $P_{Dyn}$  relates to the total power consumption  $P_{Tot}$ , consider Equation 1.2. The total power consumption  $P_{Tot}$  is the sum of the dynamic power consumption  $P_{dyn}$  and the static power consumption from leakage  $P_{Stat}$ . This means that techniques such as DVFS save on dynamic power consumption but there is also the static power consumption to consider.

$$P_{Tot} = P_{Dyn} + P_{Stat} \tag{1.2}$$

DVFS is an Adaptive Power Management technique (APM) [4], which means that power management is integrated on-chip. Other APM implementations include decoupling

of clock and supply voltage for circuitry that are not utilised and by doing so power consumption is reduced. Decoupling the clock from a circuit is called clock gating and is used to reduce dynamic power consumption. The other method, decoupling of supply voltage, is called power gating and is used to reduce leakage power consumption. DVFS reduces the dynamic power consumption by scaling down the operational clock frequency and the circuit supply voltage (Vdd) [5]. The scaling performed in DVFS is dynamic with regard to the workload of the system, so that power can be saved using low-performance mode when the IC is used but under-utilised and to provide high-performance in highpower mode when the IC is heavily used [5,2]. Typically, a DVFS design has a set of discrete supply voltage and clock frequency settings to implement power modes.

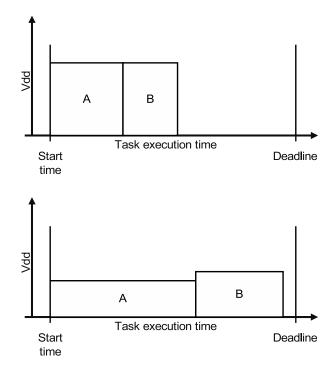

FIGURE 1.1: Task schedules with (bottom) and without (top) DVFS

Figure 1.1 shows an example of a scenario in which DVFS can save power. Two tasks, A and B, are to be performed in sequence and finish before a deadline. The deadline is a point in time when the output data of the tasks are required. The top graph shows both tasks operating at the same voltage and clock frequency, as is the case in a design that operates using a single high-performance supply voltage setting. There is idle time between the finish time of the second task (B) and the deadline. This means that the two tasks can be performed slower and still meet the deadline. In a DVFS design, this slack time is traded for lower clock frequency, as shown by the bottom graph of Figure 1.1 where the tasks take longer time. With a lowered clock frequency, it is possible to lower the supply voltage accordingly, as shown in Figure 1.1 where the height of the rectangles that represent the tasks have been adjusted to reflect different supply voltage settings for the two tasks. Lowering the supply voltage increases the transition delay of logic gates, therefore lowering the supply voltage is only possible when the clock frequency is

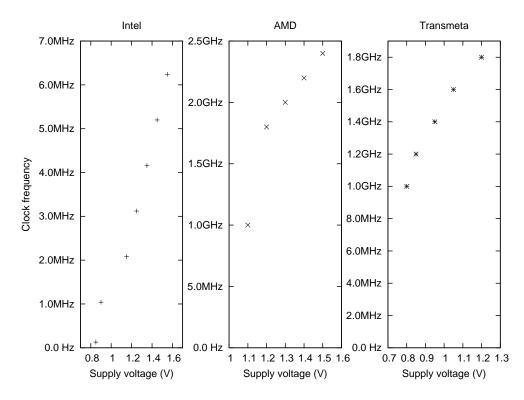

FIGURE 1.2: Supply voltage and clock frequency settings for three DVFS designs

low enough to accommodate the increased transition delay.

Examples of designs with DVFS implemented include ARM processors with IEM (Intelligent Energy Management) [6], XScale Intel processors [7], AMD Athlon 64 processors [8], and LongRun2 Transmeta processors [9]. Figure 1.2 shows three examples with the recommended supply voltage and clock frequency settings.

The switching of power modes in designs with DVFS can be controlled either by a predetermined application-specific power schedule [5], by a system that attempts to predict future process requirements [10] or by a system that is scheduling tasks depending on the battery current profile [2]. In order to implement DVFS capability in a design, extra hardware is included, such as a power management controller [6], level-shifters [11] and for the capability of continuous voltage scaling, particular pipeline latches [12]. Further savings in terms of power consumption can be gained by scaling the body bias voltage in conjunction with the supply voltage [13]. This is a technique that limits the static power consumption (leakage).

When discussing systems with multiple supply voltage settings, it is useful to have one particular setting for reference, the nominal supply voltage. In this thesis, the nominal supply voltage refers to the supply voltage that is recommended for a particular gate library. Often a gate library that is designed for a particular VLSI technology, has been characterised for a particular supply voltage. For example, the two gate libraries that are used for experimentation in this thesis, one for  $0.12\mu$ m technology [14] and the other

for 45nm technology [15], are associated with the nominal supply voltages 1.2V and 0.9V respectively. The nominal supply voltages are often set for a high performance, which also means relatively high power consumption. To save power, DVFS will typically introduce additional supply voltage settings below the nominal supply voltage.

#### 1.2 Multi-Voltage Design

Multi-voltage design is another low-power design technique that adjusts the supply voltage. Multi-voltage design partitions the internal logic of the chip into multiple voltage regions, each with its own supply voltage and corresponding supply voltage rail infrastructure [16]. It is based on the observation that in a modern design, different blocks of circuitry have different performance objectives and constraints. A processor, for instance, determines the system performance and needs to run as fast as the semiconductor technology will allow. In this case, a relatively high supply voltage is required. On the other hand, circuitry that conducts inter-system communication using a given protocol may run at a fixed, relatively low frequency dictated more by the protocol than the technology [16]. The low frequency allows the considered circuitry to operate on a relatively low supply voltage. By operating blocks that are not critical to system performance using a lower supply voltage, power consumption can be reduced in accordance to Equation 1.1.

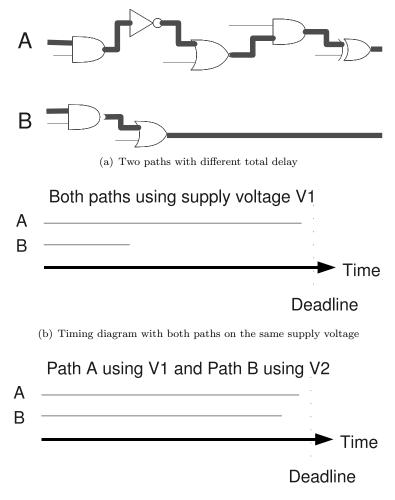

Multi-voltage design can also reduce power consumption within blocks if the path delay distribution allows [17]. In a typical design with a required clock frequency, all paths will have a total delay less than the clock period. Multi-voltage design exploits the observation that some of the paths will have a significantly lower total delay, which means that the circuitry on such paths can be operated at a lower supply voltage without impact on the overall performance. The basic idea in this type of multi-voltage design is to identify the non-critical paths and to power the gates in those paths with a lower voltage, which leads to reduction of power consumption. The example in Figure 1.3(a)shows two paths, A and B. There are fewer logic gates on path B than on path A and path B will reach the final state before path A. Therefore, path B is a candidate for being operated with lower voltage. Both paths, A and B, have the same timing constraint which is set by the clock period, as illustrated by Figure 1.3(b) where both paths are using the same supply voltage V1. As mentioned above, path B is a candidate for being operated with a lower voltage V2 (V2<V1). Figure 1.3(c) shows that with supply voltage V2, path B has a total delay that is better adjusted to the clock period. By using the lower supply voltage V2 on path B, less dynamic power is consumed on path B.

To implement a design with multiple voltage regions, as in the case of multi-voltage, level shifters are necessary to interface between different blocks. Signals crossing from

(c) Timing diagram with different supply voltage settings for the two paths

FIGURE 1.3: Example of multi-voltage design principle

one voltage region to another have to be interfaced through level shifters which shift the signals to the appropriate logic levels [16].

#### **1.3** Process Variation

Besides supply voltage variation, this thesis is concerned with process variation and how it influences defect behaviour, which has implications for manufacturing test. This thesis studies the impact of process variation in the context of resistive bridging faults, which is an important defect type in deep submicron designs (see below). In the study, test methods are developed to achieve high test quality in the presence of such variation (Chapter 5). The following provides background information about process variation.

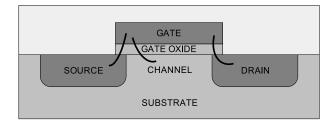

Recently, IC technology has reached such levels of integration, which involves miniaturisation, that the length of transistors are only tens of nanometres. Designs with transistors that have features which are shorter than  $0.5\mu$ m are referred to as Deep SubMicron designs (DSM) [18]. In DSM, the gate oxide (or dielectric) of the transistors can be very thin, down to ten atom layers [19]. Even small variations in the parameters of such small transistors has impact on the performance of the manufactured circuit. As the dimensions scale down to allow more integration on-chip, it is getting increasingly difficult to control all the IC parameters to the values that are specified in the design of the circuit [20]. These IC parameters include, among others, the concentration of doping atoms in the N-well and P-well substrates [21], the thickness of the gate oxide/dielectric TOX [22] and the length L of a given transistor [23]. It is often found that the actual values of some IC parameters vary across a wafer (the silicon substrate on which several ICs of the same design are manufactured next to each other in the same process), and also within each die, so that manufactured ICs from the same manufacture are slightly different [24]. This is called process variation. Process variation is considered either across different dies or within each die [22, 24] depending on the distance between circuitry that has correlated IC parameters. Within-die variation has no correlation with parameter values in other dies. The magnitude of variation on different parameters has been studied in [22]. Most of the IC parameter variations are tolerable and the chips will function normally, due to a sufficient noise margin, but variation may impact performance in terms of maximum clock frequency or power consumption [20]. However, these process variations become larger relative to the intended values of the IC parameters as the dimensions of transistors are scaled down in the pursuit of higher integration, higher performance and lower power consumption. Therefore, process variation is a challenge particularly for designs implemented in DSM technology [20].

It should be noted that some of the causes of process variation are unpredictable and unavoidable. To review some of these variations in terms of their mechanisms and characteristics, consider random dopant fluctuations, sub-wavelength lithography effects and line edge roughness [24]. The concept of random dopant fluctuations express that there are so few doping atoms in the substrate of a transistor, that the location and distribution of these atoms influence the value of the transistor threshold voltage VT [21], which is the gate-to-source voltage that makes the transistor start to conduct. The study in [21] noted that the atomistic effect of the location of doping atoms leads to a bellshaped probability distribution for the transistor threshold voltage VT. Because of the very local aspects of the distribution of doping atoms, random dopant fluctuations will affect adjacent transistors differently, i.e. there is no correlation in the variation. Up to 10% variation in the VT value has been observed [20, 25, 26]. The transistor length L is impacted both by sub-wavelength photo-lithography effects and line edge roughness [23, 24]. Photo-lithography is the process used in IC manufacturing to draw structures onto the wafer using light shining through masks, that contain the designed pattern, onto light-sensitive material, which will then be etched away depending on if it was illuminated or not. In pursuit of the ability to manufacture even smaller transistors, the resolution of the photo-lithography has traditionally been improved by moving deeper into ultraviolet spectrum of light. However, the wavelength of the optical source used for lithography has

not improved for nearly a decade. To manufacture ever smaller transistor that measure shorter than the wavelength of the light source, sub-wavelength lithography has been developed. Sub-wavelength lithography is associated with diffraction effects. Despite efforts of offsetting these effects, they still lead to variation in the manufacturing process, so that dies are affected depending on their relative position on the wafer to the light source. These effects have been observed in the forbidden pitch phenomenon [27]. The other effect that impacts the transistor length L is line edge roughness which reflects the difficulty of making the sides of the transistor channel completely smooth. This affects primarily the edge on the vertical side of wires because many nets are designed to be higher than they are wide, as a compromise between high integration (many transistors on a small area) and electrical resistance (which depends on the cut area of the net). The effect of line edge roughness is only correlated within a distance of less than 90nm [28] which means that it is unlikely that two adjacent transistors will be affected in the same way by line edge roughness. The study in [23] observed that the magnitude of line edge roughness variation is in the order of 5nm, and this magnitude remains independent of the scale of the manufactured transistors. There is a lack of published material on the mechanisms and correlations of TOX variation, but it is understandable that something that is so thin, around ten atom-layers [19], is difficult to manufacture. Due to the very thin gate oxides in DSM designs, the discussions in this thesis regard the effect of TOX variation to be uncorrelated between adjacent transistors. This is based on the observation that it is unlikely for variations in terms of an atom-layer more or less, to be correlated. It should be noted that TOX affects the value of VT and the gate capacitance. Furthermore, a very thin gate oxide will lead to gate tunnelling leakage, with leakage currents from the source, channel and drain nodes of the transistor flowing to and from the gate node [29]. Gate tunnelling leakage is further discussed in Chapter 4.

Design methods to cope with process variation include [12,30,31,32]. In [12], the authors suggest to add an extra latch to flip-flops to detect timing failures. When timing failures are detected, the circuit would use this information to adjust the supply voltage and clock frequency. Gate sizing is proposed in [31] to ensure confidence in the speed of a circuit under process variation. Another approach to cope with process variation is to use adaptive body bias and supply voltage scaling to adjust for delay and leakage caused by process variation [30].

#### **1.4 Manufacturing Testing of Integrated Circuits**

This thesis studies the impact of variation, in terms of supply voltage and process variation, on manufacturing testing. This section provides an introduction to manufacturing testing and the relevant concepts that are used later in the thesis.

The manufacturing process of integrated circuits is highly complex. Due to the com-

plexity of the manufacturing process, defects will be present and not all die on a wafer will operate correctly. Foreign particles and imperfections in the silicon wafer or the processing steps may result in bridged connections or missing features [33]. Such fabrication defects result from an imperfect manufacturing process [34]. Manufacturing tests are used after the IC is manufactured to verify that every gate and register in the IC are operational and have not been compromised by manufacturing defects. It is the aim of manufacturing testing to determine which die are good and should be used in end systems. There are certain types of defects that often occur in modern ICs. These include bridges, unintended connections between two or more circuit nodes, and opens, breaks between circuit nodes that were intended to be connected. More defect types are listed in Section 2.3. The main focus of this thesis is on bridge defects and open defects.

As circuit design become more densely integrated and therefore more complicated, more efforts in terms of testing are needed in order to maintain a high test quality. The invention of the integrated circuit (IC) in 1958 made it possible to integrate several logic functions onto the same piece of silicon. The integrated circuit meant that the basic components of a circuit could no longer be tested independently before the circuit was constructed, because all components are manufactured in the same process as the circuit itself. From the above it can be seen that integration leads to a requirement to test a large circuit rather than many small circuits.

Testing an IC involves applying stimulus to the inputs of the IC and observing the test response at the outputs. For digital circuits, which are the focus of this thesis, the stimulus consists of a vector of Logic-1's and Logic-0's such that each element of the vector corresponds to an IC input. The input assignment vector, together with the corresponding vector of expected test response for the IC outputs, is called a test pattern. A set of test patterns is called a test set.

The following sections give an overview of a range of concepts in manufacturing testing, including how defects are modelled using fault models (Section 1.4.2) which aid the evaluation (Section 1.4.3) and generation (Section 1.4.4) of test patterns. Furthermore, hardware added to a design to aid testing (Section 1.4.5) is discussed along with test cost (Section 1.4.6) and different types of tests and test methods (Section 1.4.7).

#### 1.4.1 Defect Coverage by Fault Detection

Manufacturing defects result from an imperfect manufacturing process [34]. Typical defects include bridges (unintended connections between two or more circuit nodes) and opens (breaks between circuit nodes that were intended to be connected) [33]. The defects that are of interest to manufacturing testing are those that cause malfunctions. Defects can change the logic behaviour, increase delay (i.e. reduce circuit performance) or increase the power consumption of the circuit. In this thesis the focus is on the defects

that change the logic behaviour. A defect is covered by a test if the test detects the faulty logic behaviour which is caused by the defect. Faulty logic behaviour is detected by a test pattern if the test response seen at the output of the circuit that contains the defect is different from test response of a fault-free circuit. The test pattern to detect a defect can be designed if the faulty behaviour for the defect is known. Therefore, the behaviour of defects is described in fault models.

#### 1.4.2 Fault Modelling

To design tests that identify defective ICs, fault models are developed and employed to predict how faults occur and their impact on circuits. A fault model is a formal description of how a defect alters the behaviour of a design. Using the fault models, test patterns can be designed to detect the impact of the defect, i.e. the faulty behaviour, by controlling nets so that the defect is activated and the faulty behaviour occurs while observing the behaviour on other nets. In this context, it is useful to define what is meant by controlling and observing. A net is controllable if an assignment to the IC inputs exists such that the net is set to the desired logic value. A net is observable if an assignment to the IC inputs exists such that a propagation path from the net to a primary output is created, so that the logic value on at least one primary output depends on the logic value on the net-under-observation. It should be noted that a test pattern needs to both control and observe nets in order to detect faults, which can lead to contradictions in terms of the assignment to IC inputs. If no test pattern exists which detects a logic fault, that logic fault is called undetectable.

A fault model typically specifies the faulty behaviour that can occur and where such behaviour can occur. That means that the fault model identifies the possible fault locations and therefore also the number of possible faults in a given circuit. For example, open defects can occur on any net. Therefore all nets are possible fault locations. When the possible fault locations are known, it is possible to evaluate the quality of a given test through a fault model-specific metric called fault coverage. The typical definition of fault coverage is the ratio of the number of faults detected to the total number of considered faults, usually given as a percentage. Full fault coverage, 100%, means that all possible fault locations that are specified by the fault model are tested.

The Stuck-At model is an example of a fault model [35, 36, 34]. With this model, a net can have two faulty behaviours, either stuck-at-0 or stuck-at-1. Therefore, each net is a possible fault location. To achieve full fault coverage according to the Stuck-At fault model, the test should detect both behaviours on each net. To detect a stuck-at-0 on net n, the test must control net n to Logic-1 and simultaneously observe net n. Detailed fault models will be further discussed regarding bridging faults and opens in Section 1.4.8 and Section 1.4.9 respectively. There are many types of possible defects in modern ICs and some of them are reviewed in Section 2.3. Different defect types impact ICs to produce different faulty behaviours. To detect many defects and to simplify test generation, many fault models are abstract, as in the case of the stuck-at model. This means that tests generated with such fault models cover defects with modelled behaviour but fail to cover defects that cause unmodelled behaviour. Because of the many types of possible defects and the abstract nature of fault models, some defects will not be covered by, for example, a test with full stuck-at fault coverage. Defects that the test fails to cover are called test escapes [37, 38, 39, 40]. To reduce test escape, different approaches exist, including the employment of a combination of more detailed fault models, application of a large (near exhaustive) test set, and N-detection. N-detection testing applies a number N of different test patterns to each net-under-test or gate-under-test, to increase the probability of detecting the faulty behaviour of unmodelled defects [41, 42, 43].

#### 1.4.3 Fault Simulation

The fault coverage of a test set T is measured by means of fault simulation. Each test pattern  $V \in T$  is simulated for each considered fault f to determine if f is detected by V. The number of detected logic faults is then compared with the total number of considered faults as described in Section 1.4.2. The fault simulation procedure simulates two circuits, D and Df, using the stimulus of test pattern V. Here, D is the intended design and Df is the same design modified by the fault f. The simulation of the two circuits produces two test responses D(V) and Df(V). If there is a discrepancy in the test responses so that  $D(V) \neq Df(V)$ , the fault f is detected by the test pattern V. A detailed discussion on how fault simulation can be performed in a software tool is given in Section 3.2.3, where such a tool is used for resistive bridging faults. The fault simulation software is adapted for use on full open defects in Section 4.4.3 and for considering process variation in Section 5.3.3.

#### 1.4.4 Test Generation

So far in this chapter, the discussion has introduced the concepts of test patterns, how test patterns are applied, how they detect faults and how they can be evaluated using fault simulation. Next, consider how test patterns are generated.

Test generation is the process of generating test patterns that when applied detect faulty circuit behaviour caused by defects [34]. Test generation is a hard problem considering that the numbers of test patterns should be kept low while achieving high fault coverage. Another aspect to the test generation problem is that some gates of a design are only accessible through other gates and a fair amount of computation is required to determine how such gates can be controlled and observed. In fact, the problem of proving that a

fault is undetectable, or providing a test pattern for it, is an NP-complete problem. This means that for worst-case problems the computation time is exponential in the number of inputs to the design. For large designs it can take a prohibitively long time to perform test generation for all faults and the test generator may have to give up on some faults. There are efficient algorithms for automatic test pattern generation (ATPG) [34]. These algorithms often focus on particular fault models such as the stuck-at fault model.

In this thesis, the concept of an ATPG-engine is used to refer to an algorithm that together with a fault model forms an ATPG tool. The main task for such an algorithm is to determine the assignments to the primary inputs of the circuit, that sensitises a path that contains the targeted defect location. The path is used to propagate the faulty signal from the defect location to a primary output. A path is called sensitised if it is composed of lines that for a test t change value in the presence of a fault f. Such lines are sensitised to the fault f by the test t [34]. An example of an ATPG-engine for combinatorial designs is the D-algorithm, which uses a particular algebra called D-notation for the generation of test patterns [34]. The computation time of the D-algorithm is exponential in the number of circuit nodes. Therefore, several algorithms improve on on the basic D-algorithm. Two such improved ATPG algorithms include PODEM and FAN [34]. These algorithms employ observations about the circuit structure to reduce the number of test generation problems that lead to exponential computation time and to make the computation time dependent on the number of primary inputs rather than on the number of circuit nodes. Another type of ATPG-engine, which is used in this thesis, is based on the Boolean Satisfiability problem, which is the problem of determining if there exists an assignment to the variables of a Boolean formula that makes the formula evaluate to **true**. There are solvers available, such as [44], that solve the Boolean Satisfiability problem by finding such an assignment to the variables. An ATPG-engine can be built using such a solver, by generating the Boolean formula that is equivalent of comparing the outputs of two circuits D and Df, where D corresponds to the fault-free circuit and Df corresponds to the same circuit modified by a fault f. The Boolean function should be defined so that it results in **true** if D and Df produce different results for the same input assignment. The input assignment generated by the solver is the stimulus vector of a test pattern for the considered fault. The solver in [44] is complete in the sense that it will find a test pattern if one exists. Therefore, if the solver fails to find a test pattern, the problem is unsatisfiable and the considered fault is undetectable. For more details on how to implement an ATPG-engine using this type of solver, see Appendix B. This type of ATPG-engine is used for resistive bridging faults in Section 3.2.4 and Section 5.5. Fault simulation plays an important role in test generation. Many test generation methods use a fault simulator to evaluate a proposed test. Based on the evaluation, additional test patterns are generated until the fault simulation shows that satisfactory fault coverage is obtained.

#### 1.4.5 Scan Testing

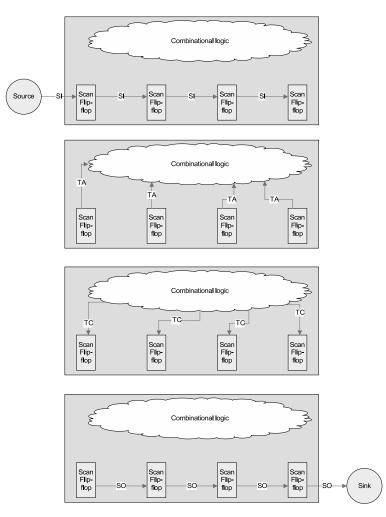

The testing that is considered in this thesis employs structural information about the considered design to reason about the location of faults and how faults should be detected. To provide controllability and observability structural tests employ additional hardware that connect the flip-flops (registers) of sequential circuits using multiplexers, making the collection of flip-flops that are connected in this way into shift registers called scan-chains [34]. The flip-flops operate as scan-chains during test scan mode and operate as normal flip-flops otherwise. This modifies the test application procedure so that the stimuli are not applied just at the input pins of the IC but also at the outputs of the flip-flops. Similarly, test responses are not captured just at the output pins of the IC but also at the inputs of the flip-flops. The test application procedure using scan-chains is called scan-based testing and is illustrated in Figure 1.4.

FIGURE 1.4: Test application procedure for scan-based testing

Figure 1.4 shows the procedure for testing using scan chains. The scan chain is used to shift the stimuli from a source, through the IC input pins into the circuit (as marked with SI, scan-in, in the top of Figure 1.4). The scan-in operation is followed by a clock

cycle of test application when the stimuli are applied at the output of the flip-flops (as marked with TA, test application, in the second part of Figure 1.4). During this clock cycle, the stimuli exercise the combinatorial circuitry between the flip-flops and produce test responses. The test responses are captured at the input of the flip-flops (as marked with TC, test response capture, in the third part of Figure 1.4) at the end of the clock cycle. Subsequently, the test response data is shifted out of the circuit by the scan chain to the IC output pins. From there the test response is transported to a sink (as marked with SO, scan-out, in the bottom of Figure 1.4). In this context, a source is where stimuli come from and a sink is where test responses go to be evaluated. The source and the sink can be implemented by automatic test equipment (ATE) or through extra hardware on-chip, called Built-in-Self-Test (BIST). An ATE has fast memories used for shifting test data to and from tested circuits and interfaces with tested circuits using probes and test ports. The BIST solution typically consists of memories and shift-registers that are designed to produce pseudo-random test stimuli sequences. Both ATE and BIST can serve as source for test stimulus and sink for test responses.

With regard to the design of scan-chains, there is a standard called IEEE 1149.1 [45] which specifies the interface used to communicate test data and circuitry to assist in testing integrated circuits in the context of chips assembled on printed circuit boards.

The concept of adding circuitry to a design to enable test to be conducted, as in the case of the scan-chains and BIST mentioned above, is called design-for-test (DfT).

#### 1.4.6 Test Cost

As was mentioned above, the number of test patterns should not be too high, and the test quality should be high. Both these factors can be expressed in terms of test cost, which includes the test application time (a function of the number of test patterns), and the cost of return of defective products (a function of the ability of the test patterns to find defects). Further terms in the test cost are the cost of chip area for DfT, extra circuit delay due to DfT, the cost of designing DfT and test patterns, and the cost of renting or buying automatic test equipment (ATE). In high volume manufacturing testing, any slight reduction of the test time of an IC can lead to substantial savings.

#### 1.4.7 Logic Testing, Delay Fault Testing and Current-Based Testing

Manufacturing testing of ICs can be divided into logic testing, delay fault testing and current-based testing. Logic testing is the type of testing considered in this thesis, but some of the relevant related research discussed in Chapter 2 addresses delay fault testing and current-based testing so all three types are reviewed in this section.

• Logic testing targets defects that cause time-independent logic malfunction. Operating scan-chains is the normal way of applying logic tests and tests generated

according to the stuck-at fault model belong to this category.

- Delay fault testing targets defects that cause additional circuit delay so that the circuit does not meet its performance requirements (e.g. a specified clock period). The delay is the time it takes for the circuit to go from one state to another. A change of input data, for example the application of a test pattern, will cause a change on output data but not momentarily. The transition is associated with a delay. The purpose of delay fault testing is to detect defects that causes the transition delay to surpass the required clock period for the desired performance. Delay fault testing requires two test vectors, one that initialises the circuit and one that causes a transition in logic state. The time for the transition to pass through the circuit is compared to the clock period by capturing the logic value at the outputs into the scan flip-flops after a time corresponding to the clock period has passed. Due to the fact that the scan-chains form simple shift registers, there are two techniques available for applying delay fault testing. The first technique is called launch-on-capture [46], which means that the second test pattern is the result of applying the first test pattern for one clock cycle. The clock cycle of the first test pattern ends with the capture of the second test pattern in the flip-flops. The next clock cycle applies the second test pattern, effectively causing a transition of logic state. The test response is captured at the end of this clock cycle. The second technique for application of delay fault test patterns is called launch-onshift [47], which means that the second test pattern is the result of shifting the first test pattern one step in the scan-chain. Similar to the first technique, a clock cycle is applied with the first test pattern, which ends with a shift of the scanchain which applies the second test pattern for the next clock cycle. At the end of this clock cycle, the test responses are captured in the scan-chain flip-flops. Both techniques (launch-on-capture and launch-on-shift) are associated with constraints regarding what test patterns that can be applied and consequently limited in terms of the circuitry and the defects that can be tested.

- Current-based testing, targets defects that cause the supply current profile of the tested circuit to change. For example, IDDQ testing [48, 49, 50, 51] measures the current when the circuit is in a stable state (i.e. no activity, quiescent mode). The two key observations behind this test technique is that (1) CMOS circuits ideally do not conduct any current while in a stable state and (2) many defect types produce such a current that can be measured to detect the presence of such defects. However, physical CMOS circuits experience small leakage currents during the stable state and for designs with very small transistors (as in the case in deep submicron designs), very thin gate oxides/dielectrics (approaching 10 atom layers) and low supply voltage (<1V) lead to an increase of these leakage currents [38]. This makes IDDQ testing less effective in detecting defects. Methods

like Delta-IDDQ testing still make current-based testing possible in many DSM designs. Some design methods have been suggested for making IDDQ testing more effective for DSM designs, but these methods typically result either in increased area or reduced performance [49]. Applying test patterns for IDDQ measurements is typically slower than voltage-based testing (logic testing and delay fault testing) because the circuit needs time to settle to a stable state (no activity) before the current measurement can take place. Another example of current based testing is the energy consumption ratio test (ECR) [52, 53]. It measures two dynamic currents and compares them. If one of the currents is elevated due to a defect, that will be reflected in the ratio between the two currents. This ratio is compared with that of other tested ICs from the same design to evaluate the test result. If the ECR value for an IC is significantly different from that of the other ICs, the IC is called an outlier and is regarded as defective. Tests that rely on comparison with other tested ICs, as in the case of ECR, cannot be evaluated until the test has been performed on many other ICs, which delays the pass-or-fail decision for all the ICs compared to voltage-based testing, where the pass-or-fail decision can be taken as soon as a fault is detected. The ECR test method has been shown to tolerate process variations, which would otherwise limit the usability of current-based tests [52].

#### 1.4.8 Testing for Bridge Defects