Received 5 October 2019; accepted 10 October 2019. Date of publication 15 October 2019; date of current version 6 December 2019.

The review of this article was arranged by Editor C. S. Tan.

Digital Object Identifier 10.1109/JEDS.2019.2947564

# Investigation of Self-Heating Effect on DC and RF Performances in AlGaN/GaN HEMTs on CVD-Diamond

K. RANJAN<sup>1,2</sup>, S. ARULKUMARAN<sup>2</sup>, G. I. NG<sup>®</sup> <sup>1</sup>, AND A. SANDUPATLA<sup>1</sup>

1 School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore 639798 2 Temasek Laboratories@NTU, Nanyang Technological University, Singapore 637553

CORRESPONDING AUTHOR: K. RANJAN (e-mail: kumudran001@e.ntu.edu.sg)

**ABSTRACT** Abstract-We have investigated the self-heating effect on DC and RF performances of identically fabricated AlGaN/GaN HEMTs on CVD-Diamond (GaN/Dia) and Si (GaN/Si) substrates. Self-heating induced device performances were extracted at different values drain bias voltage ( $V_D$ ) and dissipated DC power density ( $P_D$ ) in continuous wave (CW) operating condition. The effect of self-heating was observed much lesser in GaN/Dia HEMTs than GaN/Si HEMTs in terms of  $I_D$ ,  $I_G$ ,  $g_m$ ,  $f_T$  and  $f_{max}$  reduction. Increased channel temperature caused by joule heating at high  $P_D$  reduces the 2-DEG carrier mobility in the channel of the device. This behaviour was also confirmed by TCAD simulation which showed  $\sim$ 3.9-times lower rising rate of maximum channel temperature and lowers thermal resistance ( $R_{th}$ ) in GaN/Dia HEMTs than GaN/Si HEMTs. Small signal measurements and equivalent circuit parameter extraction were done to analyze the variation in performance of the devices. Our investigation reveals that the GaN/Dia HEMT is a promising candidate for high power density CW operation without significant reduction in electrical performance in a large drain bias range.

INDEX TERMS AlGaN/GaN, HEMT, CVD-diamond, self-heating, DC, RF and TCAD.

### I. INTRODUCTION

AlGaN/GaN high-electron-mobility transistors (HEMTs) are promising candidates for high power continuous wave (CW) operations in compact solid-state power amplifier (SSPA) modules which are ideal for civil avionics, communications, industrial, scientific, and medical applications. GaN HEMTs have the desirable intrinsic capacity of handling large current and power densities due to its unique material properties such as large band gap, high electron velocity and critical breakdown field [1]. However, thermal management, size reduction and long term reliable operation for GaN-based devices are some of the major challenges, especially when the device is operating at high drain bias voltage (e.g., V<sub>D</sub> 28-48 V). High drain bias voltage causes a higher longitudinal electric field at the gate edge of the gate-drain region near the AlGaN/GaN interface. Under such condition, a large electric field exists at the gate edge near the 2-dimensional electron gas (2-DEG) of AlGaN/GaN

interface [2]. The scattering of 2-DEG electrons with the generated phonons leads to large joule heating (self-heating) and increasing the lattice temperature locally (called hot spot) [3], [4]. Self-heating effect becomes more prominent when device size further reduces, mainly by lowering gatedrain spacing ( $L_{\rm gd}$ ), the gate to gate pitch ( $L_{\rm gg}$ ). Here, substrate plays an important medium for transporting the joule heat away from the hot spot region of the device. However, poor heat emission from conventional substrates (e.g., Si, Sapphire) further accelerates self-heating, which causes additional phonon scattering in the channel and degrades the 2-DEG effective carrier mobility ( $\mu_{\rm eff}$ ). This eventually leads to degraded DC and RF performance with an increase in  $V_{\rm D}$ .

To avoid self-heating effect, a superior thermal conductive material such as Diamond (10-20 W/cm-K) [5], has been employed as a substrate to dissipate the generated heat from the active region of the device. Researchers have also

reported AlGaN/GaN HEMTs on Diamond with dissipated DC power density  $(P_D = V_D \times I_D)$  of 22 W/mm (CW) [6], and 24 W/mm in pulse condition as well as 3.6-times higher RF power capability over GaN/SiC HEMTs [7]. These results show the strong manifestation of exploiting best transport properties of GaN HEMT by using Diamond as a substrate. However, the bias conditions effect on self-heating and transport properties in AlGaN/GaN HEMTson-Diamond have not been reported so far. Such work is inevitable for developing the electrical and thermal model of device as well as understanding the operating limit of GaN HEMTs for next-generation high power DC and RF application. In this work, we systematically investigated the self-heating effect on DC and RF performance with increasing the drain bias voltage and quantitatively analysed the results under increasing dissipated DC power density  $(P_{\rm D} = V_{\rm D} \times I_{\rm D})$ . Results were also compared and analysed with identical GaN HEMTs fabricated on Si (111) (low thermal conductive substrate,  $\sim 1.5$  W/cm.K). For a fair comparison of electrical performances, GaN HEMT on-Si was selected with similar 2-DEG property and identical device dimensions in this study. However, buffer thickness is higher in GaN/Si HEMT than GaN/Dia HEMT. Effect of this difference in channel temperature was also simulated.

#### II. DEVICE FABRICATION

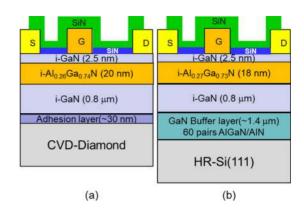

Figure 1 shows the schematic cross-sectional diagram of (a) GaN/Dia HEMT and (b) GaN/Si HEMTs. GaN/Dia (GaN/Si) HEMT exhibited an average room temperature 2-DEG mobility ( $\mu$ ) of 1502 (1450) cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>. sheet carrier density  $(n_s)$  (of  $0.97 \times 10^{13} (1.0 \times 10^{13})$  cm<sup>-2</sup> and an average sheet resistance of 422 (430) ohm/sq. with a variation of  $\pm 3\%$  over the full 4-inch wafer. The product of  $\mu$  and  $n_s$  ( $\mu \times n_s$ ) is almost the same for GaN/Si  $(1.450 \times 10^{16} \text{ V}^{-1}.\text{s}^{-1})$  and GaN/Dia  $(1.457 \times 10^{16} \text{ V}^{-1}.\text{s}^{-1})$ . The device fabrication started with the mesa isolation using BCl<sub>3</sub>/Cl<sub>2</sub> plasma. The ohmic contact was formed by depositing conventional Ti/Al/Ni/Au metal stacks followed by rapid thermal annealing at 825 °C for 30s in an N2 atmosphere. Next, the Ni/Au (150/300 nm) gate metalization was formed using conventional lithography and e-beam evaporation followed by a lift-off process. Further, thick Ti/Au (50/1000 nm) metalization was done to withstand high power density during operation. The devices were then passivated with 120-nm-thick SiN using plasma-enhanced chemical vapor deposition (PECVD). In this study, we have used the device dimensions of  $L_{\rm sg}/W_{\rm g}/L_{\rm gd} = 2/(2 \times 100)/2/3 \mu \rm m$  for both GaN/Si and GaN/Dia HEMTs. The DC and RF characterization were done on the device, in similar measurements condition, using Agilent B1505A semiconductor parameter analyzer and Keysight N5244A PNA-X network analyzer, respectively.

## III. RESULTS AND DISCUSSIONS

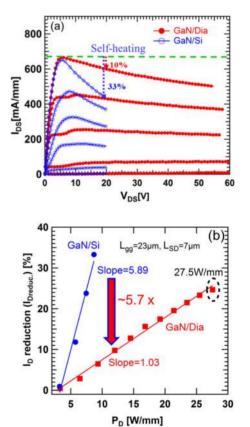

Figure 2 (a) shows the DC  $I_{\rm D}$ - $V_{\rm D}$  and of GaN/Dia and GaN/Si HEMTs with  $L_{\rm g}/W_{\rm g}=2/(2\times100)~\mu{\rm m}$ .

FIGURE 1. Cross-sectional schematic diagram of AlGaN/GaN HEMTs on (a) CVD-Diamond substrate (b) Si (111) substrate.

FIGURE 2. (a)  $I_{DS}$ - $V_{DS}$ , (b)  $I_{D}$  reduction ( $I_{Dreduc}$ .) versus DC  $P_{D}$  of GaN/Dia and GaN/Si HEMTs. Device dimensions:  $L_{sg}/W_{g}/L_{g}/L_{gd} = 2/(2 \times 100)/2/3$  with  $L_{gg} = 23$  um.

GaN/Dia HEMTs were measured up to  $V_{\rm D}=60~{\rm V}$  whereas GaN/Si HEMTs were measured up to  $V_{\rm D}=20~{\rm V}$  at  $V_{\rm G}=+1~{\rm V}$  to avoid on-state device breakdown. The GaN/Si and GaN/Dia HEMTs exhibited maximum drain current density ( $I_{\rm Dmax}$ ) of 652 and 662 mA/mm respectively. As we can see in Figure 2(a), GaN/Si suffered a significant reduction of  $I_{\rm D}$  beyond the maximum current density ( $I_{\rm Dmax}$ ) as compared to GaN/Dia. The  $I_{\rm D}$  reduction rate at  $V_{\rm g}=+1V$  was obtained as 15 mA/mm.V and 3.3 mA/mm.V for GaN/Si and GaN/Dia respectively.

VOLUME 7, 2019 1265

FIGURE 3. (a) Transfer characteristics of GaN/Dia and GaN/Si HEMTs at different  $V_D$  (b) Normalized  $I_{dmax}$  and  $g_{mmax}$  reduction at different  $V_D$ .

The GaN/Dia HEMT shows a much smaller percentage of drain current reduction which is 10 % compared to the 33 % in GaN/Si HEMTs (see Fig. 2(a)). Our result of I<sub>D</sub> reduction (17.7 % at  $V_D = 55$  V,  $V_g = 0$ ) was also compared with the reported value in GaN/SiC HEMTs ( $\sim 27\%$ ) [8], correlating to the much lower self-heating effect in our GaN/Dia HEMTs. Hence, it is evident that self-heating induced I<sub>Dreduc.the</sub> rate in GaN/Dia HEMTs is much lower than GaN/Si and GaN/SiC HEMTs. The dissipated DC power density (P<sub>D</sub>) in GaN/Dia was calculated as 27.56 W/mm  $(V_{\rm D}=55~{\rm V})$  as compared to the 8.7 W/mm  $(V_{\rm D}=20~{\rm V})$ in GaN/Si. The  $I_{\rm Dreduc.}$  rate in GaN/Dia is  $\sim 1~\%$  / W.mm<sup>-1</sup> as compared to 5.89% /W.mm<sup>-1</sup> in GaN/Si HEMTs, which is  $\sim$ 5.7-times lower rate of  $I_{\text{Dreduc}}$  in GaN/Dia as compared to GaN/Si (see Fig. 2(b)). It is worth to mention that GaN/Dia sustained a higher P<sub>D</sub> of 27.56 W/mm even without on-state breakdown. Whereas GaN/Si was burnt around  $\sim$ 9 W/mm of DC  $P_{\rm D}$ , could be due to intense self-heating and increased channel temperature in GaN/Si. Such inherent characteristics make GaN/Dia transistor very suitable for high power CW operation.

In addition to  $I_{\rm Dreduc}$ , maximum transconductance  $(g_{\rm mmax})$  and maximum drain current density (at  $V_{\rm G}=0$  V)  $I_{\rm Dreduc}$  were analyzed from the measured transfer characteristics. By limiting the  $V_{\rm G}$  up to 0 V, we increased the CW  $V_{\rm D}$  up to 40 V for GaN/Si and device was measured without observing catastrophic failure. The HEMTs exhibited peak extrinsic transconductance  $(g_{\rm mmax})$  of 162 and 199 mS/mm for GaN/Si

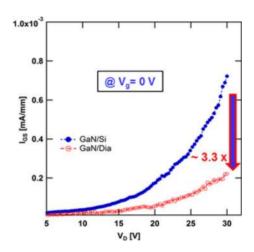

FIGURE 4. Gate current characteristics of GaN/Dia and GaN/Si HEMTs with  $V_{\rm D}$  at  $V_{\rm G}=0$  V.

and GaN Dia respectively at  $V_D = 10$  V(See Fig. 3(a)). We can clearly observe that as  $V_D$  increases, the  $g_{mmax}$  decreases. Further analysis was done for the drain bias dependent  $I_{Dmax}$ (at  $V_g = 0$  V,  $V_D = 10 - 40$  V) and  $g_{mmax}$  reduction. The percentage of  $I_D$  reduction ( $I_{Dreduc.}$ ) was calculated based on the formula:  $I_{\text{Dreduc.}} = ((I_{\text{Dmax}} - I_{\text{D-Vd}})/I_{\text{Dmax}}) \times 100$ . The  $I_{\rm Dmax}$  is the maximum  $I_{\rm D}$  value from transfer characteristics at  $V_D = 10 \text{ V}$  and  $I_{D-vd}$  is taken as maximum  $I_D$  at a particular  $V_D$  for the calculation of  $I_{Dreduc}$ . Similarly, the  $g_{mmax}$ reduction  $[g_{\text{mreduc.}} = (g_{\text{mmax}} - g_{\text{m-vd}}) \times 100/g_{\text{mmax}}]$   $(g_{\text{mmax}})$ is the maximum g<sub>m</sub> value from transfer characteristics at  $V_{\rm D}=10~{\rm V}$  and  $g_{\rm m-vd}$  is taken as maximum  $g_{\rm m}$  at a particular  $V_D$  for the calculation of  $g_{\text{mreduc.}}$ ) was also calculated. The  $g_{\text{mreduc}}$  was found to be 15 % and 35 % at  $V_{\text{D}} = 40 \text{ V}$ with the rate of 1.0 mS/mm. $V^{-1}$  and 1.9 mS/mm. $V^{-1}$  respectively for GaN/Dia and GaN/Si HEMTs (See Fig. 3(b)). Similar reduction in  $g_{\text{mmax}}$  and  $I_{\text{Dmax}}$  in GaN/Dia HEMT was observed which could be associated with mobility degradation. Lower gmmax reduction of GaN/Dia also indicates a lower reduction of effective mobility ( $\mu_{eff}$ ) which was extracted further in this work. Lower I<sub>Dreduc.</sub> and g<sub>mreduc.</sub> in GaN/Dia HEMTs confirms the low self-heating effect in the device which is due to the efficient heat dissipation through the Diamond substrate. Therefore, GaN/Dia enables the device to operate at higher  $V_D$  without much compromise of current density and transconductance, which is key requirements for devices operating at higher CW power. In addition to the  $I_D$  and  $g_m$ , gate current was also measured on the same device with increasing  $V_D$  at  $V_G = 0$  V.

Figure 4 shows the  $I_{\rm G}$  versus  $V_{\rm D}$  for both GaN/Si and GaN/Dia HEMTs. From Fig. 4, it is clear that  $I_{\rm G}$  is increasing at a higher rate in GaN/Si than GaN/Dia under similar longitudinal electric field condition. However,  $I_{\rm g}$  increase is more prominent at  $V_{\rm D} > \sim 15$  V. This increase of  $I_{\rm G}$  could be due to the increased channel temperature at higher drain bias voltage. Increased gate current with temperature was reported in the literature which is due to temperature assisted

1266 VOLUME 7, 2019

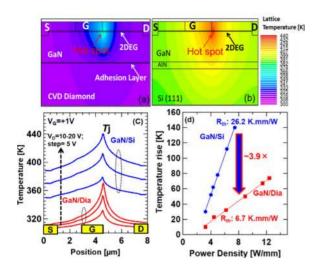

FIGURE 5. TCAD Simulated cross sectional thermal profile for (a) GaN/Dia, (b) GaN/Si at  $V_{\rm D}=20$ V,  $V_{\rm G}=+1$ V, (c) device temperature profile across source-drain region for different  $V_{\rm D}=10$ , 15 and 20 V (d)  $\Delta T_{\rm j}$  versus  $P_{\rm D}$  of GaN/Dia and GaN/Si HEMTs.

tunnelling [9], [10]. The rate of  $I_{\rm G}$  increase in GaN/Dia is obtained  $\sim$ 3-times lower than GaN/Si. Lower rise of  $I_{\rm G}$  with  $V_{\rm D}$  implies higher gate stability and reliable device performance at high voltage operation of GaN/Dia.

In order to investigate the bias dependent temperature distribution in these devices, 2D TCAD simulation (SILVACO) was also performed using the GIGA module consistently with BLAZE [11]. The thermal boundary conditions can be expressed as

$$(J_{tot}.s) = \frac{1}{R_{th}} \left( T - T_{ref} \right)$$

where  $J_{tot}$  is the total energy flux, s is the unit external normal of the boundary,  $T_{ref}$  is the reference boundary condition of the thermo-contact in the simulation environment, and Rth is the material-dependent thermal resistance. In our simulation, the bottom of the devices is used as the reference thermo-contact at 300 K.

Fig. 5(a) and 5(b) shows the lattice temperature profile of the GaN/Dia and GaN/Si HEMTs, respectively. The highest temperature in the channel (Hot spot) is referred here as junction temperature  $(T_j)$ . From the temperature scale, it is clear that GaN/Dia has much lower temperature as compared to GaN/Si HEMTs.

The obtained temperature profile across the device channel from source to drain clearly indicates (See Fig. 5(a)) that the GaN/Si HEMTs has  $T_{\rm j}$  of 440 K, whereas it is 370 K in the GaN/Dia HEMTs. The observation of lower  $T_{\rm j}$  of 70 K in GaN/Dia HEMTs means it can further operate at higher  $P_{\rm D}$ . Fig. 5(c) shows the junction temperature rise ( $\Delta T_{\rm j}$ ) of the device with  $P_{\rm D}$ . From the figure, it is clear that the junction temperature rises more rapidly in GaN/Si HEMT (140 K) than GaN/Dia HEMT (36 K) at  $P_{\rm D}$  (7 W/mm). A similar trend of temperature rise ( $\Delta T_{\rm j}$ ) in GaN/Dia HEMTs was also observed by Pomeroy *et al.* [12]. Thermal resistance ( $R_{\rm th}$ ) values were calculated from the

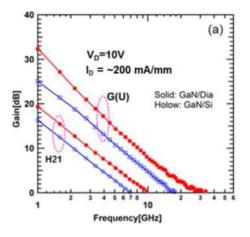

FIGURE 6. (a) Small-signal characteristics, (b) Current gain ( $H_{21}$ ) of GaN/Dia and GaN/Si HEMTs for different  $V_{\rm D}$  of a 2- $\mu$ m gate GaN/Dia and GaN/Si HEMTs.

slope of the rise of junction temperature versus  $P_{\rm D}$  for both GaN/Dia (6.7 K.mm/W) and GaN/Si (26.2 K.mm/W) HEMTs (See Fig. 5(d)). The extracted values of  $R_{\rm th}$  were closely matched the reported values ( $\sim$ 6.5 K.mm/W) for GaN/Dia HEMTs [13], and (24.6 K.mm/W) for GaN/Si HEMTs [14]. The GaN/Dia shows  $\sim$ 3.9-times lower  $R_{\rm th}$  value than GaN/Si HEMTs. This is in good agreement with the reported results by Pomeroy *et al.* [15]. The  $R_{\rm th}$  of GaN/Dia can further be minimized by optimizing the interface layer between GaN and CVD-Diamond [16].

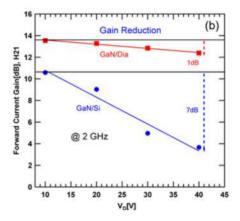

We also performed the small-signal measurements on both the HEMTs from  $V_{\rm D}=10-40$  V. Fig. 6 (a) shows the small-signal microwave characteristics of GaN/Dia and GaN/Si HEMTs. At  $V_{\rm D}=10$ V, the GaN/Dia and GaN/Si HEMTs exhibited a unity current gain cutoff frequency ( $f_{\rm T}$ ) of 10.2 GHz and 7.0 GHz and a maximum oscillation frequency ( $f_{\rm max}$ ) of 31.4 GHz and 18.2 GHz, respectively. The forward current gain ( $H_{21}$ ) was deduced from measured S-parameters at different  $V_{\rm D}$ . At 2 GHz, about 1.0 dB reduction of  $H_{21}$  was observed in GaN/Dia HEMT when compared to 7 dB reduction in GaN/Si HEMTs from  $V_{\rm D}=10-40$  V, (See Fig. 6(b)).

VOLUME 7, 2019 1267

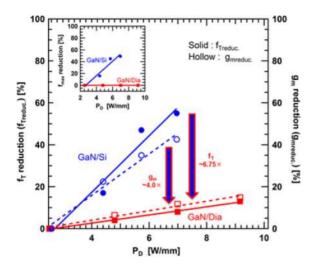

FIGURE 7. The  $f_T$  reduction ( $f_{Treduc}$ ) and  $g_{mmax}$  reduction ( $g_{mreduc}$ ) versus  $P_D$  of GaN/Dia and GaN/Si HEMTs. Inset:  $f_{max}$  reduction ( $f_{maxreduc}$ ) versus  $P_D$  for GaN/Dia and GaN/Si HEMTs.

Almost constant small signal gain for  $V_D = 10 - 40 \text{ V}$  in GaN/Dia offers a better choice for developing high-power high-frequency amplifier required for a large range of drain bias operation. The  $f_T$  and  $f_{max}$  were also evaluated for different  $V_D$  from 10 - 40V, the  $I_d$  was fixed ~200 mA/mm where both the devices exhibited maximum  $g_{\rm m}$ , for GaN/Dia and GaN/Si respectively as  $f_T$  was obtained highest at these gate bias voltage. The  $f_T$  reduction ( $f_{Treduc.}$ ) was calculated using the formula  $f_{\text{Treduc.}} = (f_{\text{Tmax}} - f_{\text{T-vd}}) \times 100 / f_{\text{Tmax}} (f_{\text{Tmax}})$ is maximum  $f_T$  value measured at  $V_D = 10 \text{ V}$  and  $f_{T-\text{vd}}$  is the  $f_{\rm T}$  obtained at different  $V_{\rm D}$ ). Fig. 7 shows the  $f_{\rm Treduc.}$ and g<sub>mreduc.</sub> versus P<sub>D</sub> for both GaN/Dia and GaN/Si HEMTs. At 7 W/mm, GaN/Dia HEMTs exhibited only 8.2 % of f<sub>Treduc.</sub> whereas GaN/Si HEMTs exhibited much higher  $f_{\text{Treduc.}}$  of 55%. This  $f_{\text{T}}$  ( $f_{\text{T}} = g_{\text{m}}/2\text{pi}(C_{\text{gs}} + C_{\text{gd}})$ ) reduction is predominantly due to the g<sub>m</sub> reduction (42%) in GaN/Si devices. The additional reduction of 13% in  $f_T$  could be attributed to the slight increase of  $C_{gs} + C_{gd}$ , as was observed for GaN on Si devices. It is also clear that the GaN/Dia HEMTs has  $\sim$ 6.75-times lower  $f_{\text{Treduc.}}$  rate with P<sub>D</sub> as compared to GaN/Si HEMTs. It is also clear that GaN/Si HEMTs has larger  $f_{Treduc.}$  than  $g_{mreduc.}$  at higher V<sub>D</sub> whereas GaN/Dia HEMTs has an almost similar rate of  $f_{\text{Treduc.}}$  and  $g_{\text{mreduc.}}$  The reduction of  $f_{\text{max}}$  with increasing  $V_D$  was also calculated using the formula;  $(f_{\text{maxreduc.}} =$  $(f_{\text{max}(\text{max})} - f_{\text{max}-\text{vd}}) \times 100/f_{\text{Tmax}})$ . Where  $f_{\text{max}(\text{max})}$  is the  $f_{\text{max}}$  obtained at  $V_{\text{D}} = 10 \text{ V}$  and  $f_{\text{max-vd}}$  is  $f_{\text{max}}$  obtained at a particular  $V_D$ . The inset of Fig. 7 shows the  $f_{\text{maxreduc}}$ for both GaN/Si and GaN/Dia HEMTs. The  $f_{\text{maxreduc.}}$  was obtained to be 49 % in the GaN/Si HEMTs while no significant reduction was observed in GaN/Dia HEMTs.

To confirm this, small-signal equivalent circuit parameters were extracted, from measured S-parameter at different  $V_{\rm D}$ , following the proposed model in the literature [17]. We observed that the intrinsic parameters, mainly  $g_{\rm m}$  intrinsic

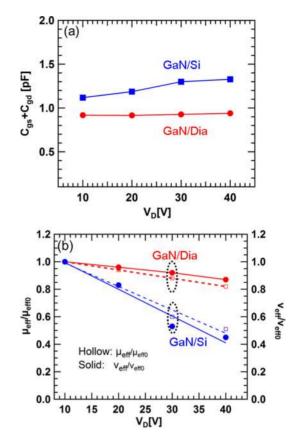

FIGURE 8. (a) Extracted gate capacitance from measured small-signal characteristics and (b) normalized effective carrier mobility and effective carrier velocity versus drain bias characteristics  $V_{\rm D}$  of a 2- $\mu$ m gate GaN/Dia and GaN/Si HEMTs.

$(g_{\text{mo}})$ ,  $C_{\text{gs}}$  and  $C_{\text{gd}}$  were affected more significantly at high  $V_{\rm D}$  which is due to increased junction temperature in the device. Extrinsic parameters have relatively less effect in small-signal performance in our device. It could be due to allower rise of temperature in the parasitic area of the device than hot spot region (See Fig. 5 (a,b)). However, a small increase in drain resistance (R<sub>d</sub>) was also observed at higher  $V_D$ . Similar behaviour of extrinsic parameters with temperature has been reported in the published work [18]. The extracted  $C_{\rm g}$  ( $C_{\rm gs} + C_{\rm gd}$ ) at different  $V_{\rm D}$  was shown in Figure 8(a). A small increase of  $C_g$  ( $\sim$ 3 %) was observed in GaN/Dia as compared to ~16 % increase in GaN/Si. Large reduction of  $f_T$  in GaN/Si is due to the reduction of  $g_m$  and increase of  $C_g$  as  $f_T$  ( $f_T\alpha(1/C_g)$ ). Higher increase of  $C_{\rm gs}$  in GaN/Si could be linked to the large junction temperature  $(T_i)$  at higher  $V_D$  (See Fig. 5(c)). The increase of  $C_{gs}$  with temperature in AlGaN/GaN HEMTs have also been reported by Cuerdo et al. [19]. Which could be related to changes occurred in SiN passivate and AlGaN permittivities [19], [20].

We observed a decreasing trend of  $C_{\rm gd}$  with  $V_{\rm D}$ . Similar trend of  $C_{\rm gd}$  was reported in other published works [21], [22]. Which could be due to the extension of the depletion region towards the drain side with an increase of

1268 VOLUME 7, 2019

$V_{\rm D}$  [22]. The reduction of  $C_{\rm gd}$  can help to improve the  $f_{\text{max}}$  at higher  $V_{\text{D}}$  [23]. Further, effective carrier mobility ( $\mu_{eff}$ ) was estimated from the extracted  $g_{mo}$  which is associated with the device channel and can be expressed as  $g_{\text{mo}} = (\mu_{\text{eff}} C_{\text{gs}} \times W/L)(V_{\text{G}} - V_{\text{TH}}))$ , where W is the gate width (200  $\mu$ m) and L is the gate length (2  $\mu$ m),  $V_{TH}$  is the threshold voltage of device. Both  $\mu_{\rm eff}$  and  $v_{\rm eff}$  (effective carrier velocity) were also calculated from the extracted small-signal equivalent circuit parameters for both GaN/Si and GaN/Dia. The normalized  $\mu_{\rm eff}$  and  $v_{\rm eff}$  versus  $V_{\rm D}$  were plotted for both the HEMTs (See Fig. 8(b)). Around 55 % reduction of  $\mu_{\rm eff}$  was observed in GaN/Si as compared to 18% in the case of GaN/Dia. Comparatively higher reduction of  $\mu_{\rm eff}$  in GaN/Si occurred due to increased  $T_{\rm i}$  at higher  $V_{\rm D}$ . Extracted effective 2-DEG mobility with temperature in GaN HEMT has shown a similar trend in the reported literature [24]. These results show that GaN/Dia HEMTs suffers  $\sim$  3-times lower rate of  $\mu_{\rm eff}$  reduction which is due to the lower rise of junction temperature at increased  $V_{\rm D}$ .

#### IV. CONCLUSION

In conclusion, we have quantitatively investigated the selfheating effect on DC and RF performances of identically fabricated AlGaN/GaN HEMTs on CVD-Diamond and Si substrates. Self-heating induced device performances were extracted at different values of dissipated DC power density  $(P_D)$  in continuous wave (CW) operating condition. The GaN/Dia HEMTs exhibited  $\sim$ 5.7-times lower rate of  $I_{\text{Dreduc.}}$ than GaN/Si HEMTs. This behaviour was also confirmed by 2D device simulation which showed  $\sim$ 3.9-times lower rate of increase in junction temperature and lowers thermal resistance ( $R_{th}$ ) in GaN/Dia HEMTs in comparison with GaN/Si HEMTs. The  $f_{\text{Treduc.}}$  rate was  $\sim$ 6.75-times lower in the case of GaN/Dia than GaN/Si HEMTs whereas no significant reduction of  $f_{\text{max}}$  was observed in GaN/Dia HEMTs. Comparatively lower reduction rate ( $\sim$ 3-times) of  $\mu_{\rm eff}$  and  $v_{\rm eff}$  in GaN/Dia made its performance less degraded (~15%) as compared to (~50%) GaN/Si. These results show that GaN/Dia HEMTs can be operated even at higher  $V_D$  as well as at higher  $P_{\rm D}$  which are paramount features for developing compact high power SSPAs for CW application.

#### **ACKNOWLEDGMENT**

Authors are grateful to the MTDC team in TL@NTU for their support.

# **REFERENCES**

- U. K. Mishra, P. Parikh, and Y.-F. Wu, "AlGaN/GaN HEMTs-an overview of device operation and applications," *Proc. IEEE*, vol. 90, no. 6, pp. 1022–1031, Jun. 2002.

- [2] S. Karmalkar and U. K. Mishra, "Enhancement of breakdown voltage in AlGaN/GaN high electron mobility transistors using a field plate," *IEEE Trans. Electron Devices*, vol. 48, no. 8, pp. 1515–1521, Aug. 2001.

- [3] V. O. Turin and A. A. Balandin, "Performance degradation of GaN field-effect transistors due to thermal boundary resistance at GaN/substrate interface," *Electron. Lett.*, vol. 40, no. 1, pp. 81–83, 2004.

- [4] J. Kuzmik, R. Javorka, A. Alam, M. Marso, M. Heuken, and P. Kordos, "Determination of channel temperature in AlGaN/GaN HEMTs grown on sapphire and silicon substrates using DC characterization method," *IEEE Trans. Electron Devices*, vol. 49, no. 8, pp. 1496–1498, Aug. 2002.

- [5] G. D. Via et al., "Wafer—scale GaN HEMT performance enhancement by diamond substrate integration," physica Status Solidi (c), vol. 11, nos. 3–4, pp. 871–874, 2014.

- [6] D. C. Dumka, T. M. Chou, F. Faili, D. Francis, and F. Ejeckam, "AlGaN/GaN HEMTs on diamond substrate with over 7W/mm output power density at 10 GHz," *Electron. Lett.*, vol. 49, no. 20, pp. 1298–1299, 2013.

- [7] P.-C. Chao et al., "Low-temperature bonded GaN-on-diamond HEMTs with 11 W/mm output power at 10 GHz," IEEE Trans. Electron Devices, vol. 62, no. 11, pp. 3658–3664, Nov. 2015.

- [8] K. Takagi et al., "Ku-band AlGaN/GaN-HEMT with over 30% of PAE," in IEEE MTT-S Int. Microw. Symp. Dig., Boston, MA, USA, 2009, pp. 457–460.

- [9] A. P. Zhang et al., "Temperature dependence and current transport mechanisms in AlGaN Schottky rectifiers," Appl. Phys. Lett., vol. 76, pp. 3816–3818, 2000.

- [10] S. Arulkumaran, T. Egawa, H. Ishikawa, and T. Jimbo, "Temperature dependence of gate-leakage current in AlGaN/GaN high-electronmobility transistors," *Appl. Phys. Lett.*, vol. 82, no. 18, pp. 3110–3112, 2003.

- [11] ATLAS User's Manual Device Simulation Software, Silvaco, Santa Clara, CA, USA, 2010.

- [12] J. W. Pomeroy, M. Bernardoni, D. C. Dumka, D. M. Fanning, and M. Kuball, "Low thermal resistance GaN-on-diamond transistors characterized by three-dimensional Raman thermography mapping," *Appl. Phys. Lett.*, vol. 104, no. 8, 2014, Art. no. 083513.

- [13] S. Martin-Horcajo, A. Wang, M.-F. Romero, M. J. Tadjer, and F. Calle, "Simple and accurate method to estimate channel temperature and thermal resistance in AlGaN/GaN HEMTs," *IEEE Trans. Electron Devices*, vol. 60, no. 12, pp. 4105–4111, Dec. 2013.

- [14] S. Arulkumaran et al., "Temperature dependent microwave performance of AlGaN/GaN high-electron-mobility transistors on high-resistivity silicon substrate," *Thin Solid Films*, vol. 515, no. 10, pp. 4517–4521, 2007.

- [15] J. Pomeroy et al., "Achieving the best thermal performance for GaN-on-diamond," in Proc. IEEE Compd. Semicond. Integr. Circuit Symp. (CSICS), Monterey, CA, USA, 2013, pp. 1–4.

- [16] H. Sun et al., "Reducing GaN-on-diamond interfacial thermal resistance for high power transistor applications," Appl. Phys. Lett., vol. 106, no. 11, 2015, Art. no. 111906.

- [17] G. Dambrine, A. Cappy, F. Heliodore, and E. Playez, "A new method for determining the FET small-signal equivalent circuit," *IEEE Trans. Microw. Theory Techn.*, vol. MTI-36, no. 7, pp. 1151–1159, Jul. 1988.

- [18] M. A. Alim, A. A. Rezazadeh, and C. Gaquiere, "Thermal characterization of DC and small-signal parameters of 150 nm and 250 nm gate-length AlGaN/GaN HEMTs grown on a SiC substrate," Semicond. Sci. Technol., vol. 30, no. 12, 2015, Art. no. 125005.

- [19] R. Cuerdo et al., "High-temperature microwave performance of submicron AlGaN/GaN HEMTs on SiC," IEEE Electron Device Lett., vol. 30, no. 8, pp. 808–810, Aug. 2009.

- [20] R. Aggarwal, A. Agrawal, M. Gupta, and R. S. Gupta, "Investigation of temperature dependent microwave performance of AlGaN/GaN MISHFETs for high power wireless applications," in *Proc. IEEE Int. Conf. Recent Adv. Microw. Theory Appl.*, Jaipur, India, 2008, pp. 66–68.

- [21] B. Green, K. Moore, D. Hill, M. C. Debaca, J. Schultz, B. Noori, M. Bokatius, "Gallium nitride RF technology advances and applications," *Edicon-China*, 2014.

- [22] Z. H. Liu et al., "Comprehensive study on the bias-dependent equivalent-circuit elements affected by PECVD SiN passivation in AlGaN/GaN HEMTs," *IEEE Trans. Electron Devices*, vol. 58, no. 2, pp. 473–479, Feb. 2011.

- [23] W. Chong, H. Yun-Long, Z. Xue-Feng, M. Xiao-Hua, Z. Jin-Cheng, and H. Yue, "AlGaN/GaN high-electron-mobility transistors with transparent gates by Al-doped ZnO," *Chinese Phys. B*, vol. 22, no. 6, 2013, Art. no. 068503.

- [24] R. Menozzi et al., "Temperature-dependent characterization of AlGaN/GaN HEMTs: Thermal and source/drain resistances," IEEE Trans. Device Mater. Rel., vol. 8, no. 2, pp. 255–264, Jun. 2008.

VOLUME 7, 2019 1269