# Investigation of Silicon Nanowire Gate-All-Around Junctionless Transistors Built on a Bulk Substrate

Dong-Il Moon, Sung-Jin Choi, Juan Pablo Duarte, and Yang-Kyu Choi

*Abstract*—A silicon nanowire (Si-NW) with a gate-all-around (GAA) structure is implemented on a bulk wafer for a junctionless (JL) field-effect transistor (FET). A suspended Si-NW from the bulk-Si is realized using a deep reactive ion etching (RIE) process. The RIE process is iteratively applied to make multiply stacked Si-NWs, which can increase the on-state current when amplified with the number of iterations or enable integration of 3-D stacked Flash memory. The fabricated JL FETs exhibit excellent electrostatic control with the aid of the GAA and junction-free structure. The influence on device characteristics according to the channel dimensions and additional doping at the source and drain extension are studied for various geometric structures of the Si-NW.

*Index Terms*—Bosch process, bulk MOSFET, corner effect, deep reactive ion etching (RIE), extension doping, gate-all-around (GAA), junctionless (JL) transistor, short-channel effects (SCEs), vertically stacked silicon nanowire (Si-NW).

## I. INTRODUCTION

SILICON nanowire (Si-NW) field-effect transistor (FET) without junctions has recently been proposed as an alternative to the conventional junction-embedded FET that contains a p-n junction at both the source and drain (S/D) [1], [2]. By virtue of its junction-free nature, the junctionless (JL) FET has potential advantages compared to the conventional FET such as reduced fabrication complexity due to a low thermal budget and elimination of the requirement of a shallow and abrupt junction, improved immunity against short-channel effects (SCEs), and less stringent demand to reduce the gate dielectric thickness [1]–[5]. Nevertheless, one of the challenging issues pertaining to the JL FET stems from contradictory demands: a narrow channel for the fully depleted (FD) body to turn off in conjunction with a high-doping concentration. The former is crucial for off-state characteristics, and the latter is important for the on-state current and reduction of the parasitic resistance to the greatest extent possible in S/D

Manuscript received August 18, 2012; revised December 18, 2012; accepted February 12, 2013. Date of publication March 7, 2013; date of current version March 20, 2013. This work was supported in part by the Center for Integrated Smart Sensors funded by the Ministry of Education, Science and Technology as Global Frontier Project under Grant CISS-2012M3A6A6054187, the IT R&D Program of MKE/KEIT under Grant 10035320 (Development of novel 3-D stacked devices and core materials for the next generation flash memory), the Samsung Electronics Company, Ltd., and SK Hynix Semiconductor Inc. The review of this paper was arranged by Editor J. Woo.

The authors are with the Department of Electrical Engineering, Korea Advanced Institute of Science and Technology, Daejeon 305-701, Korea (e-mail: dimun@nobelab.kaist.ac.kr; sjchoi@nobelab.kaist.ac.kr; jpduarte@nobelab.kaist.ac.kr; ykchoi@ee.kaist.ac.kr).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2013.2247763

extensions. Note that the aforementioned issues can result in an unwanted partially depleted region in the channel. On the one hand, the JL FET was initially demonstrated on a silicon-oninsulator (SOI) substrate, because the thickness of the channel  $(T_{ch})$  on a SOI substrate is readily scaled down. However, this adversely increases the fabrication cost and leads to noncompatibility with standard CMOS technology implemented on a bulk substrate. To overcome these issues, JL FETs have been proposed on a bulk silicon substrate [6]-[8]. Among 3-D device structures, a gate-all-around (GAA) transistor assisted by excellent electrostatic controllability is considered to be an ultimately scaled device. The GAA is especially attractive for the JL FET from a structural point of view, because it can alleviate the strict requirement of reducing  $T_{ch}$ , which is indispensable to ensure that the inherently heavily doped channel is FD. Therefore, the GAA JL FET built on a silicon bulk substrate is a timely and important development. In this aspect, a recently proposed method for the formation of a Si-NW on the bulk substrate, known as the Bosch process, can be utilized to fabricate a JL FET with a GAA structure [9]–[11]. On the other hand, in the GAA structure, a narrow Si-NW serves as a channel. Accordingly, the shape of the Si-NW is important, because the JL FET has variability issues [12]. In the JL FET, the parasitic series resistance that arises from the relatively low-doping concentration (approximately 10<sup>19</sup> cm<sup>-3</sup>) at the S/D can be problematic compared to a conventional junction-embedded transistor. Additional doping at the S/D extension can reduce the parasitic resistance and thus enhance the on-state current [4]. However, a detailed study that takes into account the Si-NW geometry and extra doping at the S/D extension has not yet been reported.

In this paper, a GAA JL FET composed of a Si-NW formed by a one-step dry etching route is demonstrated on a bulk substrate. The proposed fabrication method can also be used for multiply stacked 3-D Si-NW devices. Typical electrostatic properties of n-type JL transistors are presented. The effects that arise from various channel dimensions, the shape of the Si-NW, and extra doping at the S/D extension are also investigated.

### II. DEVICE FABRICATION

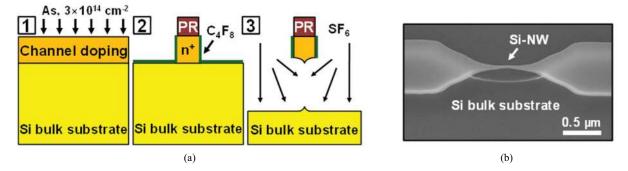

A schematic illustration of the one-step dry etching route used to form the Si-NW and an obtained result are shown in Fig. 1. In this paper, for the heavily doped S/D and channel, a bulk region was initially doped with arsenic at a dose of  $3 \times 10^{14}$  cm<sup>-2</sup>. Afterwards, the suspended Si-NW, which

Fig. 1. (a) Schematic representation of the formation of the heavily doped Si-NW on a bulk substrate by the Bosch process. The sidewall of the patterned Si-NW on a bulk substrate is passivated by the *in situ* generated  $CF_4$ -based polymer during the RIE process. (b) Tilted SEM image of the fabricated Si-NW on a bulk substrate.

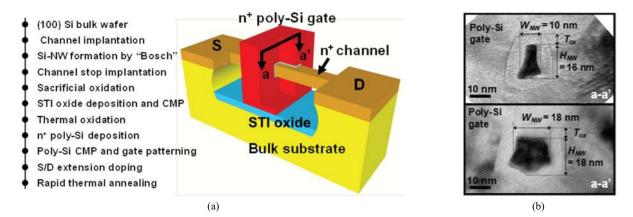

Fig. 2. (a) Process flow and a schematic of the proposed JL FET built on a bulk substrate. The JL FET has homogeneous doping polarity and a uniform doping concentration along the S/D, but the S/D extension of the control device is additionally doped by arsenic with a dose of  $5 \times 10^{15}$  cm<sup>-2</sup>. (b) Cross-sectional TEM images along the a-a' direction of the fabricated Si-NW GAA JL FET.

is separated from the bulk substrate, was formed by a deep reactive ion etching (RIE) process, i.e., the Bosch process [11]. It should be noted that the underside of the patterned bulk Si-NW was completely etched out after the one-step etching route without additional processes used in previous reports [9], [10]. Moreover, the cross-sectional geometric shape of the Si-NW can be accurately and independently controlled by anisotropic etching, which accompanies in situ sidewall passivation in the same etching chamber. Isotropic etching was subsequently applied for complete separation of the Si-NW from the bulk substrate while the in situ sidewall passivation layer protected the exposed sidewalls of the Si-NW from being etched laterally. The process flow and a schematic representation of the GAA JL FET are shown in Fig. 2(a). After the formation of the heavily doped Si-NW, the bulk substrate was doped with boron at a dose of  $10^{14}$  cm<sup>-2</sup> to block leakage paths among adjacent FETs. For proper operation of the JL FET, the diameter of the Si-NW was reduced by sacrificial oxidation. Afterward, the bottom part of the Si-NW was partially filled with an oxide for device isolation. Thermal oxidation with a thickness  $(T_{ox})$  of 5 nm was performed for the gate oxide, and  $n^+$  in situ doped polysilicon was deposited and sequentially patterned for the gate electrode. To evaluate the additional doping effect at the S/D extension, arsenic implantation at a dose of  $5 \times 10^{15}$  cm<sup>-2</sup> was carried out. Transmission electron microscopy (TEM) images

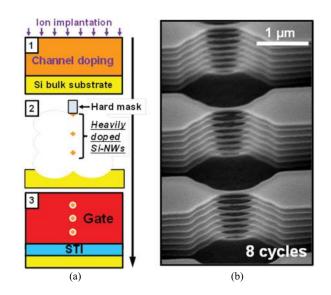

Fig. 3. (a) Schematics of the process flow for a vertically and 3-D stacked Si-NW JL FET in the cross-sectional view. (b) SEM image after 8 cycles of the deep RIE process, which enables the formation and separation of each Si-NW. The number of etching cycles is equal to that of the stacked Si-NW.

of the fabricated devices are shown in Fig. 2(b). The crosssectional area of the Si-NWs with different widths ( $W_{NW}$ ) and heights ( $H_{NW}$ ) ranges from 10 nm ( $W_{NW}$ ) by 16 nm ( $H_{NW}$ )

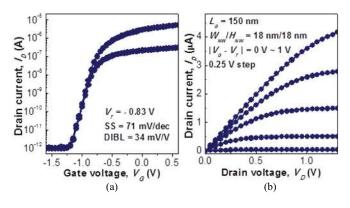

Fig. 4. Measured (a)  $I_D - V_G$  and (b)  $I_D - V_D$  characteristics of the GAA JL FET with a  $W_{\text{NW}}$  value of 18 nm, a  $H_{\text{NW}}$  value of 18 nm, a  $L_G$  value of 150 nm, and an  $n^+$  poly-silicon gate.

to 24 nm ( $W_{\text{NW}}$ ) by 20 nm ( $H_{\text{NW}}$ ), and the gate length ( $L_G$ ) ranges from 30 to 150 nm.

Interestingly, the proposed one-step etching route can be extended to a vertically and 3-D stacked Si-NW GAA JL FET using multiple cycles of the deep RIE process. Conceptual schematics of the fabrication process for a multiple stacked JL FET and a tilted scanning electron microscopy (SEM) image of vertically stacked eight-layer Si-NWs are depicted in Fig. 3(a) and (b), respectively. It should be noted that as a proof-of-concept, vertically stacked Si-NWs on a bulk substrate are realized by an iterative plasma etching route without the epitaxial growth of multiple sacrificial SiGe and structural Si layers [13], [14]. Moreover, in the conventional junction-embedded FET, the formation of the junction and its doping for the S/D become difficult when the number of stacked layers increases. However, in the JL FET, the doping process for the S/D and the channel can be applied before the formation of the vertically stacked Si-NWs; the complexity of the device fabrication process is thereby significantly reduced. The proposed JL FET with vertically stacked Si-NWs thus provides a solution for high-performance transistors and 3-D stacked Flash memory applications.

#### **III. RESULTS AND DISCUSSION**

Typical transfer and output characteristics for an n-type JL FET are shown in Fig. 4. The threshold voltages  $(V_T)$ of the fabricated devices were not optimized due to the use of  $n^+$  poly-silicon as a gate electrode. The off-state current  $(I_{off})$  does not originate from the heavily doped Si-NW but stems from the leakage paths through the bulk region [11]. The on-state current  $(I_{on})$ , however, mainly flows through the Si-NW. The normalized  $I_{on}$  by the perimeter is 50.8  $\mu$ A/ $\mu$ m at  $V_G - V_T = 1$  V and  $V_D = 1$  V. Although the leakage current flows through the bulk region, the ON/OFF current ratio within a  $V_G$  range of 1 V is larger than 10<sup>6</sup>. High mobility in a conventional junction-embedded FET composed of a GAA and an undoped Si-NW has been reported [15], but the degree of mobility in the fabricated GAA JL FET can be degraded owing to impurity scattering that arises from heavy doping concentration in the Si-NW channel. The estimated electron mobility is 70 cm<sup>2</sup>/V · s at a flatband voltage [2]. A JL FET

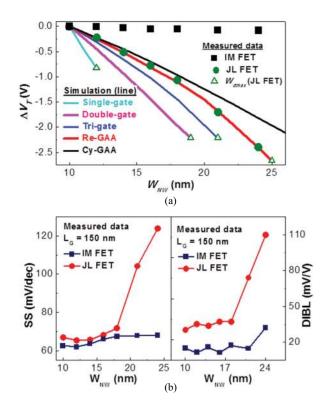

Fig. 5. (a)  $V_T$  roll-off characteristic of the JL and IM FETs according to the channel dimensions and the shape of different gate structures.  $V_T$  at a  $W_{\rm NW}$  value of 10 nm is used as a reference value in each structure. (b) SS and DIBL according to  $W_{\rm NW}$  in the fabricated GAA JL and IM FETs.

built on a bulk substrate shows feasible device characteristics with a drain-induced barrier lowering (DIBL) value of  $\sim$ 35 mV/V and a subthreshold slope (SS) of  $\sim$ 70 mV/dec due to the GAA and JL structure.

The  $W_{\rm NW}$  dependence of  $V_T$ , SS, and DIBL in the fabricated GAA JL and inversion-mode (IM) FETs are compared in Fig. 5. The IM FETs were fabricated at the same time by the same processes with the JL FETs except the channel doping concentration (N<sub>ch</sub>). It was  $2 \times 10^{15}$  cm<sup>-3</sup> by boron and  $1.5 \times 10^{19}$  cm<sup>-3</sup> by arsenic, respectively for the IM and JL FETs. Further information can be found in [11]. Fabricated devices with a  $L_G$  value of 150 nm were assessed to exclude the SCEs. In this paper,  $W_{\rm NW}$  varies more significantly than  $H_{\rm NW}$  because  $W_{\rm NW}$  is delineated by photo-lithography for various widths and  $H_{\rm NW}$  is uniformly determined by the Bosch etching time in a wafer. Therefore,  $W_{\rm NW}$  is considered as a dominant factor affecting the device characteristics. As can be clearly seen in Fig. 5, there are two distinctive trends for the  $V_T$  roll-off, SS, and DIBL according to the  $W_{\rm NW}$ . In the case of IM FETs, the aforementioned device parameters are not significantly affected by  $W_{NW}$ . In contrast, they are sensitively changed by  $W_{\rm NW}$  because their  $N_{\rm ch}$  is very high. In the JL FETs, large fluctuation of the device parameters originating from the various widths would be unavoidable; therefore, structural optimization should be required or narrow width should be sustained as long as a high  $N_{ch}$  is used for the JL FETs. For better understanding of  $\Delta V_T$  in particular, numerical simulations for n-type JL FETs were performed to

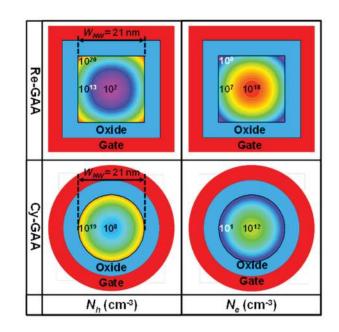

analyze the geometrical effects of the channel on  $\Delta V_T$  [16], and the results are plotted in Fig. 5(a). The parameters used in the simulation are as follows: an aspect ratio  $(H_{\rm NW}/W_{\rm NW})$  of 1 for a rectangular GAA (Re-GAA) and a tri-gate structure,  $N_{\rm ch}$  of  $1.5 \times 10^{19}$  cm<sup>-3</sup>, a  $T_{\rm ox}$  value of 5 nm, and an n<sup>+</sup> poly-silicon gate. Note that  $\Delta V_T$  with respect to  $\Delta W_{\rm NW}$  is changed according to the geometric structure of the gate. Among the different device structures, a cylindrical GAA (Cy-GAA) JL FET shows the smallest  $\Delta V_T$  due to its superior electrostatic nature. Projected from these results, the device variability originating from the process variations such as fluctuations of  $W_{\rm NW}$  and  $N_{\rm ch}$  can be minimized by the GAA structure [12]. The measured  $V_T$  roll-off is in good agreement with the simulation results in the rectangular GAA (Re-GAA) structure due to the geometric similarity, i.e., four corners in a trapezoidal shape of the fabricated Si-NW. Below a  $W_{\rm NW}$  value of 20 nm, the  $\Delta V_T$  according to  $\Delta W_{\rm NW}$  in the fabricated device was approximately 133 mV/nm. In this range, the values of SS and DIBL were not greatly affected by  $W_{\rm NW}$ . The transfer characteristic, which depends on the amount of depletion charges in the Si-NW, thus shifts in parallel. This reveals that the aforementioned Si-NW channel can be considered as a FD body. However, above a  $W_{\rm NW}$ value of 20 nm,  $V_T$  rapidly decreases, and the values of SS and DIBL also increase. Note that the maximum calculated depletion width  $(W_{dmax})$  based on the depletion approximation is approximately 25 nm for a  $N_{\rm ch}$  value of  $1.5 \times 10^{19}$  cm<sup>-3</sup> in the Re-GAA device. Although  $W_{\rm NW}$  was smaller than  $W_{\rm dmax}$ , the device characteristics were significantly degraded. These results can be explained by the concentration of the majority carriers under the FD condition. The electron and hole concentrations ( $N_e$  and  $N_h$ ) in the FD body of the n-channel JL FET are plotted in Fig. 6. In contrast to a conventional IM FET, the inversion process, i.e., the creation of holes, is enabled when the JL FET is turned off. Because inverted holes preferentially stay near the surface, they do not block the flow of electrons through the center of the body. Thus, the off-state behavior  $(V_G \leq V_T)$  of the JL FET is quite different from that of a conventional IM FET. When the body of the JL FET is partially depleted due to the heavily doped channel, the device is not properly turned off. Although the body of the JL FET is FD, the device characteristics are significantly degraded according to the pre-existing  $N_e$  in the channel. When  $W_{NW}$  becomes wider and closer to  $W_{dmax}$ , a high  $N_e$  in the channel remains even under the FD condition. That is, the body potential is not effectively controlled by  $V_G$  and becomes more sensitive to  $V_D$ . Therefore, the device characteristics, specifically the values of Ioff, DIBL, and SS, are degraded. It should be noted that the device degradation arising from the remaining  $N_e$  is more severe in the Re-GAA, which has four corners, compared to Cy-GAA [17]. Due to the corner effect, there is no significant suppression of  $N_e$  by  $V_G$ . Moreover, the corner effect tends to be severe as  $N_{ch}$  increases. Consequently, in contrast to a conventional IM transistor, the channel dimensions and the shape of the heavily doped Si-NW in a JL FET should be carefully designed.

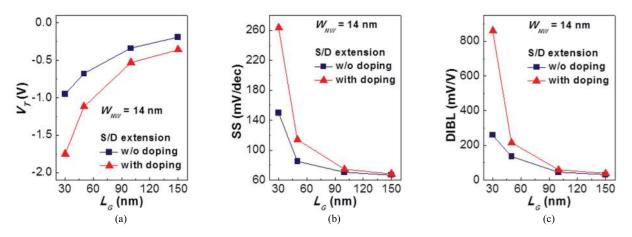

Comparisons of the  $L_G$  dependences on  $V_T$ , SS, and DIBL as extracted from the fabricated GAA JL FETs with

Fig. 6. Simulated  $N_e$  and  $N_h$  in the body of n-type JL FETs with a  $W_{NW}$  value of 21 nm and a  $V_G$  value of -2.6 V. Both channels are considered to be FD; however,  $N_e$  at the center of the body is still high in the Re-GAA. In contrast to Cy-GAA, a large buildup of electron density at the corner of the channel is observed when the center of the body begins to be depleted. Because most of the incremental charges are taken up by holes, there is no significant decrease of  $N_e$  according to  $V_G$ .

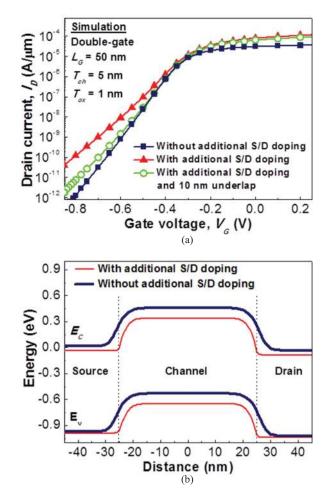

and without S/D extension doping are shown in Fig. 7. The reference JL FET has a uniform doping concentration along the source, channel, and drain, but the S/D extension of its control device was additionally doped with arsenic at a dose of  $5 \times 10^{15}$  cm<sup>-2</sup>. It should be noted that the SCEs are more severe in a device with an additionally doped S/D than in a device with no additional doping. These results are analyzed by numerical simulations with a double-gate structure, an  $N_{ch}$ value of  $1.5 \times 10^{19}$  cm<sup>-3</sup>, additional S/D doping of  $10^{20}$  cm<sup>-3</sup>, a  $T_{\rm ox}$  value of 1 nm, a  $L_G$  value of 50 nm, a  $T_{\rm ch}$  value of 5 nm, and an n<sup>+</sup> poly-silicon gate [16]. The simulation results also indicate that the additional S/D doping degrades the characteristics of the  $V_T$ -roll off, SS, and DIBL even when the on-state current is enhanced by the reduction of the series resistance in the S/D, as shown in Fig. 8(a). When the S/D extension is additionally doped and its doping concentration is therefore higher than the channel, the potential of the S/D extension cannot easily be controlled by  $V_G$ . That is, the length of the depleted S/D extension is reduced in the offstate. To verify this, a simulated energy band diagram at a  $V_G$  value of -0.8 V and a  $V_D$  value of 0.05 V is depicted in Fig. 8(b). It can clearly be seen that the effective  $L_G$ is shortened by the additional S/D doping. Accordingly, the channel potential is also not effectively controlled by  $V_G$ , and the JL device with additional S/D doping suffers more SCEs. In the same manner as done for the IM FET, the introduction of a proper length of the underlap between the gate and the additionally doped S/D extension can suppress degradation of the device characteristics with less decrement of the onstate current. There are two reasons for the aforementioned improvements. The first is that the effective  $L_G$  is modulated

Fig. 7. (a)  $V_T$ , (b) SS, and (c) DIBL versus various values of  $L_G$  of the fabricated Si-NW GAA JL FETs. The channel controllability by the gate is worsened by the additional S/D doping.

Fig. 8. (a) Simulated transfer curves of double-gate JL FETs with consideration of the additional S/D doping. The characteristics of the JL FET are degraded by the additional S/D doping; however, these are improved by the introduction of a 10-nm underlap. (b) Energy band diagram of two different JL FETs. The JL FET without additional S/D doping shows a longer effective channel length than that with additional S/D doping.

in the range of the underlap by the fringing field from the gate sidewall, i.e., the effective  $L_G$  is shortened in the on-state mode and the effective  $L_G$  is increased in the offstate mode. The second is that the parasitic resistance of the S/D extension is relatively decreased. It was also reported that high-k spacers could improve the electrostatics of the JL FETs [18]. Therefore, additional S/D doping with high-k spacers can boost the performance of the JL FET in terms of the on/off current ratio, DIBL, and SS.

## IV. CONCLUSION

A JL FET composed of a Si-NW was integrated on a bulk substrate. The Si-NW was fabricated using a one-step plasma etching route, which demands neither a silicon-oninsulator substrate nor epitaxial growth of a sacrificial SiGe and a structural Si layer. Therefore, the JL FET can be fabricated by low-cost and CMOS-compatible processes. In order to suppress the short-channel effects (SCEs), a GAA structure that completely wraps the Si-NW was employed. The proposed devices showed excellent characteristics with the aid of the GAA and junction-free nature. The variability of the threshold voltage due to fluctuation of the channel dimension was reduced by increasing the number of gate electrodes coming into contact with each channel surface in multiple-gate devices. However, it was found that a high concentration of pre-existing majority carriers in the fullydepleted Si-NW channel led to worsened SCEs even in the GAA structure owing to the corner effect. Also, the degree of channel controllability by the gate was significantly affected by additional S/D doping due to the shortened effective gate length, and an optimization strategy pertaining to this was described. Although the JL FET can have better shortchannel immunity than the IM FET, the JL FET should be carefully designed than the IM FET. Consequently, structural optimization of the JL FET is further required for the next generation technology node. As a perspective of the proposed device structure, the demonstrated fabrication process can be applicable to vertically and 3-D stacked Si-NW JL devices.

#### REFERENCES

- C.-W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, and J. P. Colinge, "Junctionless multigate field-effect transistor," *Appl. Phys. Lett.*, vol. 94, no. 5, pp. 053511-1–053511-2, Feb. 2009.

- [2] J.-P. Colinge, C.-W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. O'Neill, A. Blake, M. White, A.-M. Kelleher, B. McCarthy, and R. Murphy, "Nanowire transistors without junctions," *Nature Nanotechnol.*, vol. 5, no. 3, pp. 225–229, Mar. 2010.

- [3] A. M. Ionescu, "Nanowire transistors made easy," *Nature Nanotechnol.*, vol. 5, no. 3, pp. 178–179, 2010.

- [4] C.-W. Lee, I. Ferain, A. Afzalian, R. Yan, N. D. Akhavan, P. Razavi, and J.-P. Colinge, "Performance estimation of junctionless multigate transistors," *Solid State Electron.*, vol. 54, no. 2, pp. 97–103, Feb. 2010.

- [5] J.-P. Colinge, C.-W. Lee, I. Ferain, N. D. Akhavan, R. Yan, P. Razavi, R. Yu, A. N. Nazarov, and R. T. Doriac, "Reduced electric field in junctionless transistors," *Appl. Phys. Lett.*, vol. 96, no. 7, pp. 073510-1–073510-3, Feb. 2010.

- [6] A. Kranti, C.-W. Lee, I. Ferain, R. Yu, N. D. Akhavan, P. Razavi, and J. Colinge, "Junctionless nanowire transistor: Properties and design guidelines," in *Proc. IEEE Eur. Solid-State Device Res. Conf.*, Sep. 2010, pp. 357–360.

- [7] C.-H. Tai, J.-T. Lin, Y.-C. Eng, and P.-H. Lin, "A novel highperformance junctionless vertical MOSFET produced on bulk-Si wafer," in *Proc. IEEE Int. Conf. Solid-State Inter. Circuit Technol.*, Nov. 2010, pp. 108–110.

- [8] S. Gundapaneni, S. Ganguly, and A. Kottantharayil, "Bulk planar junctionless transistor (BPJLT): An attractive device alternative for scaling," *IEEE Electron Device Lett.*, vol. 32, no. 3, pp. 261–263, Mar. 2011.

- [9] V. Pott, K. E. Moselund, D. Bouvet, L. De Michielis, and A. M. Ionescu, "Fabrication and characterization of gate-all-around silicon nanowires on bulk silicon," *IEEE Trans. Nanotechnol.*, vol. 7, no. 6, pp. 733–744, Nov. 2008.

- [10] R. M. Y. Ng, T. Wang, F. Liu, X. Zuo, J. He, and M. Chan, "Vertically stacked silicon nanowire transistors fabricated by inductive plasma etching and stress-limited oxidation," *IEEE Electron Device Lett.*, vol. 30, no. 5, pp. 520–522, May 2009.

- [11] D.-I. Moon, S.-J. Choi, C.-J. Kim, J.-Y. Kim, J.-S. Lee, J.-S. Oh, G.-S. Lee, Y.-C. Park, D.-W. Hong, D.-W. Lee, Y.-S. Kim, J.-W. Kim, J.-W. Han, and Y.-K. Choi, "Silicon nanowire all-around gate MOSFETs built on a bulk substrate by all plasma-etching routes," *IEEE Electron Device Lett.*, vol. 32, no. 4, pp. 452–454, Apr. 2011.

[12] G. Leung and C. O. Chui, "Variability of inversion-mode and junction-

- [12] G. Leung and C. O. Chui, "Variability of inversion-mode and junctionless FinFETs due to line edge roughness," *IEEE Electron Device Lett.*, vol. 32, no. 11, pp. 1489–1491, Nov. 2011.

- [13] S.-Y. Lee, S.-M. Kim, E.-J. Yoon, C.-W. Oh, I. Chung, D. Park, and K. Kim, "A novel multibridge-channel MOSFET (MBCFET): Fabrication technologies and characterization," *IEEE Trans. Nanotechnol.*, vol. 2, no. 4, pp. 253–257, Dec. 2003.

- [14] L. K. Bera, H. S. Nguyen, N. Singh, T. Y. Liow, D. X. Huang, K. M. Hoe, C. H. Tung, W. W. Fang, S. C. Rustagi, Y. Jiang, G. Q. Lo, N. Balasubramanian, and D. L. Kwong, "Three dimensionally stacked SiGe nanowire array and gate-all-around p-MOSFETs," in *Int. Electron Devices Meeting, Tech. Dig.*, 2006, pp. 551–554.

- [15] N. Singh, A. Agarwal, L. K. Bera, T. Y. Liow, R. Yang, S. C. Rustagi, C. H. Tung, R. Kumar, G. Q. Lo, N. Balasubramanian, and D. L. Kwong, "High-performance fully depleted silicon nanowire (Diameter = 5 nm) gate-all-around CMOS devices," *IEEE Electron Device Lett.*, vol. 27, no. 5, pp. 383–385, May 2006.

- [16] Atlas User's Manual: Device Simulation Software, Silvaco International Inc., Santa Clara, CA, USA, 2010.

- [17] J. G. Fossum, J.-W. Yang, and V. P. Trivedi, "Suppression of corner effects in triple-gate MOSFETs," *IEEE Electron Device Lett.*, vol. 24, no. 12, pp. 745–747, Dec. 2003.

- [18] S. Gundapaneni, S. Ganguly, and A. Kottantharayil, "Enhanced electrostatic integrity of short-channel junctionless transistor with high-κ spacers," *IEEE Electron Device Lett.*, vol. 32, no. 10, pp. 1325–1327, Oct. 2011.

**Dong-Il Moon** received the M.S. degree from the Department of Electrical Engineering, KAIST, Daejeon, Korea, in 2010. He is currently pursuing the Ph.D. degree in electrical engineering at KAIST.

**Sung-Jin Choi** received the Ph.D. degree in electrical engineering from KAIST, Daejeon, Korea, in 2012.

He is currently a Post-Doctoral Researcher with the Electrical Engineering Department, University of California, Berkeley, CA, USA.

**Juan Pablo Duarte** received the M.S. degree from the Department of Electrical Engineering, KAIST, Daejeon, Korea, in 2012. He is currently pursuing the Ph.D. degree with the Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, CA, USA.

Yang-Kyu Choi received the Ph.D. degree from the University of California, Berkeley, CA, USA, in 2001.

He is currently a Professor with the Department of Electrical Engineering, KAIST.