# Leakage and breakdown mechanisms of GaN vertical power FinFETs

The MIT Faculty has made this article openly available. *Please share* how this access benefits you. Your story matters.

| Citation       | Xiao, Ming, Xiang Gao, Tomás Palacios and Yuhao Zhang. "Leakage<br>and breakdown mechanisms of GaN vertical power FinFETs."<br>Applied Physics Letters 114, issue 16 (April 2019) 163503 © 2019<br>Author(s) |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| As Published   | 10.1063/1.5092433                                                                                                                                                                                            |

| Publisher      | AIP Publishing                                                                                                                                                                                               |

| Version        | Author's final manuscript                                                                                                                                                                                    |

| Citable link   | https://hdl.handle.net/1721.1/121934                                                                                                                                                                         |

| Terms of Use   | Creative Commons Attribution-Noncommercial-Share Alike                                                                                                                                                       |

| Detailed Terms | http://creativecommons.org/licenses/by-nc-sa/4.0/                                                                                                                                                            |

DSpace@MIT

# Alge and Breakdown Mechanisms of Gair Vertical Power Fint ETs Publishing Ming Xiao,<sup>1</sup> Xiang Gao,<sup>2</sup> Tomás Palacios,<sup>3</sup> and Yuhao Zhang<sup>1,a)</sup>

<sup>1</sup>Center for Power Electronics Systems, The Bradley Department of Electrical and Computer Engineering, Virginia Polytechnic Institute and State University, Blacksburg, VA 24061 USA <sup>2</sup>IQE RF LLC, Somerset, NJ 08873 USA.

<sup>3</sup>Microsystems Technology Laboratories, Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology, Cambridge, Massachusetts 02139, USA

This work studies the leakage and breakdown mechanisms of 1.2 kV GaN vertical power FinFETs with edge termination. Two competing leakage and breakdown mechanisms have been identified. The first mechanism is dominated by electric field, with the leakage current dominated by electric field in the drift region and destructive breakdown voltage by peak electric field at the edge termination. The second leakage and breakdown mechanism is controlled by an energy (or potential) barrier in the fin channel. This energy barrier suffers the dram-induced barrier lowering (DIBL) effect, and is highly dependent on gate/drain biases, fin geometries and GaN/oxide interface charges. The electrons injected into the drift region due to the DIBL effect further lead to a trap-assisted space-charge-limited conduction, which results in a non-destructive early breakdown. The barrier height in the fin channel determines which mechanism is dominant; the same device could show either destructive or non-destructive breakdown at different gate biases. To enable the normally-off power switching, it is important to suppress the leakage from the second mechanism and maintain a sufficiently high energy barrier in the fin channel have been identified. The findings in this work provide critical device understanding and design guidelines for GaN vertical power FinFETs and other 'junctionless' vertical high-voltage power transistors.

a) Electronic mail: yhzhang@vt.edu.

Wide bandgap semiconductors, such as SiC, GaN, diamond and Ga<sub>2</sub>O<sub>3</sub>, are promising candidates for power electronics Publishing on s.<sup>1-7</sup> At present, GaN are becoming a mainstream power semiconductor material as a consequence of its outstanding physical properties, commercial availability of large-diameter wafers, and maturity of technological processes.<sup>1-2</sup> Lateral GaN power transistors have been commercialized up to 650 V recently.<sup>2</sup> Vertical GaN transistors have been regarded as the next-generation technologies to push GaN beyond 650 V, due to their advantages over lateral GaN transistors: 1) higher breakdown voltage (*BV*) and current for a given chip area; 2) potential superior reliability, as high electric field regions are far away from device surface, and 3) easier thermal management.<sup>8</sup> Until now, several structures have been demonstrated for vertical GaN power transistors, including current-aperture vertical electron transistors (CAVETs),<sup>9-11</sup> trench MOSFETs,<sup>12-13</sup> and power FinFETs.<sup>14-16</sup>

The vertical power FinFET was recently proposed that combines the fin-shaped channels, similar to the ones used in the FinFETs for digital applications, <sup>17-18</sup> and a thick and lightly-doped drift region which accommodates high current and high voltage needed for power switching applications. In addition, the narrow fin channels can deplete all electrons at zero gate bias due to the work function difference between the gate metal and GaN, enabling the normally-off operation. Compared to CAVETs and trench MOSFETs, GaN vertical power FinFETs (Fig. 1 (a)) only need n-GaN layers and do not require epitaxial regrowth, which greatly reduces the fabrication complexity and cost. Following the first demonstration,<sup>14</sup> GaN vertical power FinFETs have demonstrated promising performance, with a *BV* of 1.2 kV and a specific on-resistance ( $R_{on,sp}$ ) of 1 m $\Omega \cdot cm^{2.15}$  A large-area 1.2 kV, 5 A transistor was recently demonstrated with a record switching figure-of-merit (i.e. product of  $R_{on}$  and switching charges) among all 0.9-1.2 kV Si, SiC and GaN power transistors.<sup>16</sup>

Despite this excellent performance, the leakage and breakdown mechanisms of GaN vertical power FinFETs have not been fully understood. In conventional power MOSFETs, the breakdown is typically determined by the buried pn junctions. Due to the lack of p-type material in power FinFETs, the leakage and breakdown mechanisms in the vertical power FinFET, a 'junctionless' power transistor, are expected to be quite different. Prior studies have reported a destructive breakdown in vertical GaN power FinFETs with a ~200 nm fin width.<sup>14-16</sup> Although the FinFETs with larger fin widths also showed a positive threshold voltage,<sup>15</sup> their leakage and breakdown mechanisms were not clear. Understanding the dependence of these mechanisms on the fin width is key to evaluate the device design trade-offs. In addition, the leakage and breakdown mechanisms at different gate biases have not been clarified, which is important to the design of gate driver for vertical GaN power FinFETs. Two completing leakage and breakdown mechanisms are unveiled, one leading to destructive breakdown while the other leading to non-destructive breakdown. The key factors determining the dominant mechanism is also identified.

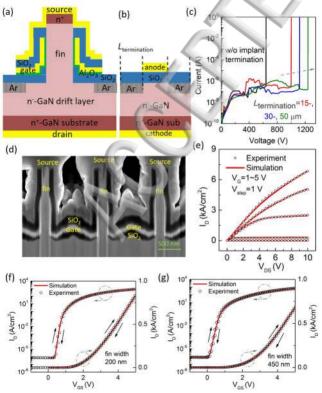

The opitaxial structure in this work consists of a 0.3  $\mu$ m-thick n<sup>+</sup>-GaN cap layer (Si: 3×10<sup>19</sup> cm<sup>-3</sup>) and ~9  $\mu$ m-thick n<sup>-</sup> **Publicanner** layer on 2-inch n<sup>+</sup>-GaN substrates. The net donor concentration and electron mobility were revealed to be ~5×10<sup>15</sup> cm<sup>-3</sup> and ~1000 cm<sup>2</sup>/V·s in the drift region, by characterizing a vertical GaN Schottky barrier diode fabricated in the wafer. FinFETs with various fin widths from 200 nm to 500 nm were fabricated in the same wafer. The fin height and gate length are 1.3  $\mu$ m and 0.75  $\mu$ m, respectively, for all devices. Device fabrication started with the fin etch and corner rounding.<sup>19</sup> Edge termination was then formed by argon (Ar) implantation (dose: 10<sup>16</sup> cm<sup>-2</sup>, energy: 150 keV) at the device periphery. This termination technique had only been used in our GaN diodes<sup>20-21</sup> but not in GaN FinFETs before. A diode structure was fabricated in the same wafer to access the effectiveness of edge termination in boosting the *BV*, as shown in Fig. 1(b). Significant *BV* improvement was observed, enabling a *BV* over 1.2 kV (Fig. 1(c)). After edge termination, the remaining fabrication steps for spacer oxides and gate, source and drain contacts were similar to our previous report.<sup>15</sup> Fig. 1(d) shows a cross-sectional scanning electron microscopy image of the fin region in the fabricated device with a 200 nm fin width.

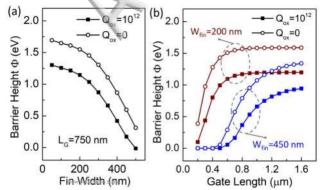

FIG 1. (a) Schematics of a unit-cell of GaN vertical power FinFETs with argon-based edge implantation and (b) a diode test structure for the evaluation of edge termination. (c) Reverse *I-V* characteristics of the diode test structure with different distances between the metal edge and termination edge. (d) Cross-sectional scanning electron microscopy image of the fin area in a fabricated GaN vertical FinFET with 200 nm fin width. (e) Representative output characteristics of GaN vertical power FinFETs from experiment (pulse measurement) and simulation. Double-sweep transfer characteristics for devices with (f) 200- and (g) 450-nm fin widths at *V*<sub>DS</sub>=1 V, with the current in both

log scale and linear scale. Simulation data are also shown, exhibiting good agreement with experimental data.

Publishings sist the device analysis, physics-based device simulation was developed for our GaN vertical power FinFETs, by using the TCAD simulator Silvaco Atlas. The physical models were based on our previous simulation for vertical GaN power transistors.<sup>8</sup> Self-heating was not accounted in the simulation model, as it has negligible impact on device leakage and breakdown. The device simulation models were calibrated to the experimental *I-V* characteristics in pulse measurements (to avoid self-heating), as shown in Fig. 1(e). Excellent agreement between simulation and experiment has been achieved.

Fig. 1 (f) and (g) show the double-sweep transfer characteristics of the fabricated GaN FinFETs with the fin width of 200 nm and 450 nm, respectively. All the current densities used in this work were normalized with respect to the total device active area, which includes fin areas and fin spacing areas but does not include edge termination areas. Both devices exhibit a positive threshold voltage ( $V_{th}$ ) with a hysteresis below 0.1 V, indicating very small interface states/traps in our devices.<sup>22</sup> As shown in Fig. 1(f) and (g), the simulations without consideration of interface traps agree well with the experiment. Further incorporation of interface traps in simulation could allow to fit this small hysteresis, <sup>23</sup> which is beyond the technical scope of this paper. The  $V_{th}$  was extracted by the constant current method at 1 mA/cm<sup>2</sup>, being ~0.5 V and ~0.3 V for FinFETs with 200-nm and 450-nm fin width. The  $V_{th}$  is slightly higher for narrower fins, due to the stronger fin depletion by the sidewall gate stacks. The extracted  $V_{th}$  is lower than the  $V_{th}$  calculated merely considering the fin depletion and the work functions of metal and GaN [see Equation (1) below], indicating the existence of fixed positive charges at the GaN/Al<sub>2</sub>O<sub>3</sub> interfaces ( $Q_{ox}$ ).

$$V_{th} \approx [W_M - \chi_{GaN} - kT ln(N_C/N_D)] - qN_D W^2/8\varepsilon_{GaN} - Q_{ox}/C_{ox}$$

(1)

where  $W_M$  is the metal work function (4.95 eV in our devices);  $\chi_{GaN}$ ,  $N_C$  and  $\varepsilon_{GaN}$  are the electron affinity, conduction band density of states and permittivity of GaN, respectively;  $N_D$  and W are the net donor concentration and width of the fin channel;  $C_{ox}$  is capacitance per unit area of the gate oxide (15 nm Al<sub>2</sub>O<sub>3</sub> in our devices). From (1), a consistent  $Q_{ox}$  of ~10<sup>12</sup> cm<sup>-2</sup> was derived for FinFETs with different fin widths. This  $Q_{ox}$  amount was further verified by our simulation.

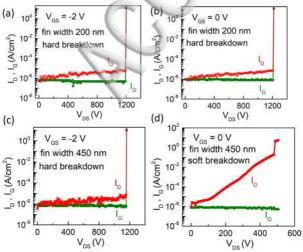

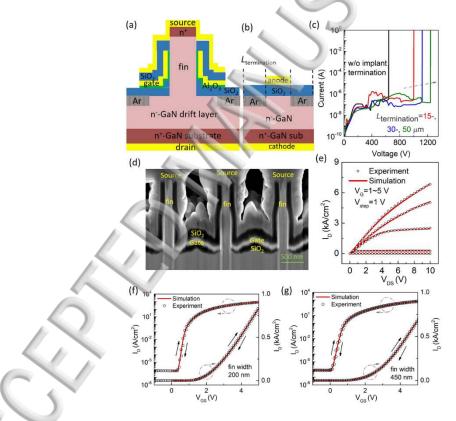

FIG. 2. Representative off-state drain and gate leakage characteristics for the FinFETs with 200- and 450-nm fin widths, measured at

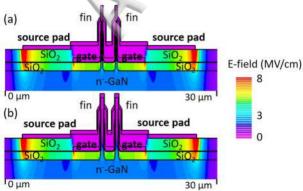

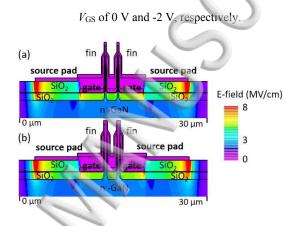

FIG. 3. Simulated E-field distribution in GaN vertical FinFETs with the fin width of (a) 200 nm and (b) 450 nm, both at  $V_{DS}$ =1200 V and  $V_{GS}$ =0 V.

Fig. 2 (a)-(d) show the representative off-state leakage curves of the FinFETs with 200 nm and 450 nm fin widths, measured at two different gate bias ( $V_{GS}$ ) conditions: 0 V and -2 V. For each of these four conditions, at least five identical devices were measured in different wafer locations, to achieve statistically significant results. As shown in Fig. 2 (a)-(c), the leakage and breakdown behaviors were found to be almost identical in the 200-nm FinFETs at  $V_{GS}$  of 0 V and -2 V and the 450-nm FinFETs at  $V_{GS}$  of -2 V. Destructive breakdown was observed occurring in the spacer oxide below the edge of gate/source pads at a drain bias ( $V_{DS}$ ) of ~1200 V. This phenomenon was validated by the fact that both gate and drain leakage suddenly shoot up at BV. Fig. 3 shows the simulated electric-field (E-field) distribution in the FinFETs at  $V_{DS}$ =1200 V and  $V_{GS}$ =0 V. As shown, the location of peak E-field is consistent with the observed breakdown location. Also, the simulation revealed that the location and magnitude of peak E-field is almost independent of the fin width and  $V_{GS}$ , which is consistent with experiment [see similar BV in Fig. 2 (a)-(c)]. In all these three conditions, the leakage current before

Publishing (VRH) through threading dislocations (TDs) under the high E-field in the drift region.<sup>25</sup> The slope between  $\ln(I)$  and  $V_{DS}$  is positively correlated to the TD density.<sup>25</sup> Based on an empirical model<sup>25</sup>, the TD density in the drift region is estimated to be  $10^6 \sim 10^7$  cm<sup>-2</sup> in our GaN-on-GaN wafer.

As shown in Fig. 2 (d), the leakage and breakdown behaviors are significantly different for the FinFET with 450-nm fins at  $V_{GS}$  of 0 V. While the gate leakage remains low, the drain leakage  $I_{DS}$  increases much faster with  $V_{DS}$ , until reaching the current compliance for *BV* measurements, exhibiting a non-destructive breakdown at  $V_{DS}$  of ~500 V. This indicates the leakage and breakdown are not dominated by the high E-field in the drift region and at the device edge termination, but are possibly controlled by the fin channel.

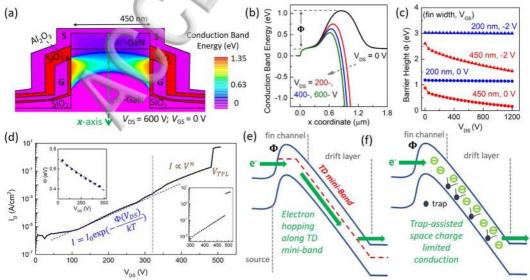

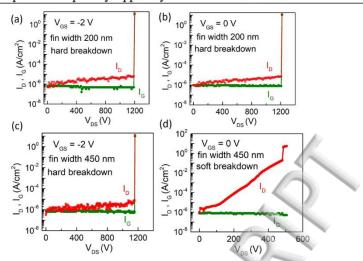

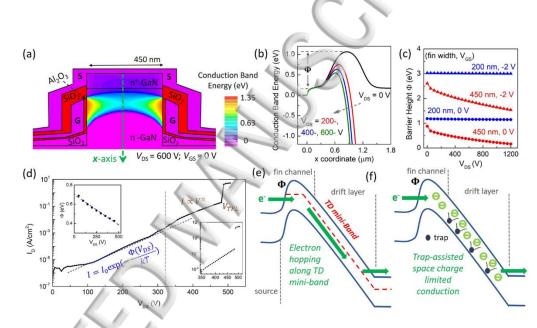

FIG. 4. (a) Simulated contour of the conduction band energy in the 450-nm fin channel, at  $V_{DS}$  of 600 V and  $V_{GS}$  of 0 V. Only positive energy with respect to the source is shown. (b) Simulated conduction band energy extracted from the cutline shown in (a), at different  $V_{DS}$ . (c) Simulated barrier heights as a function of  $V_{DS}$ , in 200- and 450-nm fin channels at  $V_{GS}$  of 0 and -2 V, respectively. (d) Off-state I-V curve for 450-nm FinFETs at  $V_{GS}=0V$ , from experimental data and theoretical models. (inset left) linear fitting of the simulated barrier height as a function of  $V_{DS}$ , (inset right) I-V data at high  $V_{DS}$  plotted in the log-log axis to illustrate the  $I \propto V^n$  relation. Physical

illustration of (e) the VRH through TDs and (f) the trap-assisted space charge limited current.

The electric potential (and band energy) within the fin channel is determined by the opposite actions of  $V_{GS}$  and  $V_{DS}$ : a zero or negative  $V_{GS}$  depletes the fin channel and lift the energy band; the high positive  $V_{DS}$  lowers the energy band towards the drift region. This is similar to the drain-induced barrier lowering (DIBL) effect in short-channel MOSFETs. To quantitatively study this effect, the band energies within the device structure were simulated at different off-state biases in

**Publiching**  $V_{\text{DS}}$  of 0 V. As shown, the lowest energy barrier in the fin channel is along the vertical axis in the middle. Fig. 4 (b) shows the extracted conduction band energy along the vertical direction in the middle of a 450-nm-wide fin channel at different  $V_{\text{DS}}$ . The barrier height decreases with the increased  $V_{\text{DS}}$ . Fig. 4 (c) shows the simulated barrier heights for 200- and 450-nm fin channels at  $V_{\text{GS}}$  of 0 V and -2 V. As shown, due to the strong gate control in 200-nm fin channels, the barrier height sees no dependence on the drain bias. In contrast, the barrier height in 450-nm fin channels is dependent on  $V_{\text{DS}}$  and approaches zero at a high  $V_{\text{DS}}$  and zero  $V_{\text{GS}}$ .

The current flowing through an energy barrier typically has an exponential dependence on the barrier height  $\Phi$ . As shown in Fig. 4 (c), the simulated  $\Phi$  for 450-nm fin channel approximately decreases linearly with  $V_{DS}$ . Based on the linearly fitted  $\Phi$  [see inset of Fig. 4 (d)], the calculated drain leakage current agrees well with the experimental data at the  $V_{DS}$  from ~100 V to ~320 V, as shown in Fig. 4 (d). This verifies that the leakage current in the 450-nm FinFETs at  $V_{GS}$  of 0 V is dominated by the energy (or potential) barrier in the fin channel.

As shown in Fig. 4 (d), the leakage current becomes higher than the exponential term when  $V_{DS}$  is above ~320 V ( $\Phi$  lower than ~0.5 eV). This is possibly due to the electron VRH through TDs, as the TD mini-band<sup>25</sup> further reduces the energy barriers for electron injection (Fig. 4 (e)). With a large amount of electrons injected into the drift region, the current then becomes limited by space charge conduction, as shown in Fig. 4 (f). This is supported by a  $I \propto V^n$  relation [see inset of Fig. 4 (d)], indicating the trap-assisted space-charge-limited conduction to be the dominant leakage mechanism.<sup>26,27</sup> A current hump is observed at the trap-filled-limited voltage ( $V_{TFL}$ ) (i.e. voltage at which all traps are filled),<sup>28,29</sup> which indicates the complete filling of traps in the drift region. Electrons further injected into the drift region will induce a large leakage current, inducing a non-destructive breakdown as the current reaches the compliance of breakdown measurement.

From the above discussion, it can be seen that the FinFET leakage current is the result of two competing mechanisms: VRH conduction in the drift region and the electron injection due to the lowered energy barrier in the fin channel. From Fig. 4 (d), the barrier-controlled leakage begins to be dominant for a  $V_{DS}$  of 100 V in the 450-nm FinFETs, corresponding to a barrier height of 0.63 eV. From Fig. 4 (c), the barrier heights for the other three measurement conditions are at least 0.5 eV higher, which corresponds to around 10<sup>8</sup>-fold lower in current. This explains why the VRH in the drift region dominates the leakage behaviors for those three conditions.

Optimal design of power transistors requires the breakdown to be determined by the drift region and edge termination. Therefore, it is important to maintain a sufficiently high energy barrier in the fin channel at  $V_{GS}$  of 0 V to prevent the punchthrough at high  $V_{DS}$ . In the discussion above, a barrier of ~0.63 eV was extracted corresponding to the onset of fin-channel

demination over the leakage current. Interestingly, as revealed by simulation, the barrier height corresponding to the onset of **Publishings** old current increase in log-scale transfer characteristics [see Fig. 1(e)] is also ~0.6 eV. This indicates that this barrier height can be considered as a critical value for normally-off GaN FinFETs, although slightly higher barriers (e.g. 0.7~0.8 eV) may be preferred in the device design to ensure the robust normally-off operation.

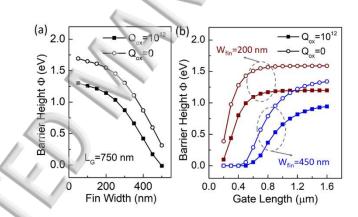

Finally, the well-calibrated simulation was used to quantify the dependence of the fin-channel barrier height on fin geometries and interface charges. Vertical GaN power FinFETs with different fin widths, gate lengths and oxide/GaN interface charges were simulated at  $V_{DS}$  of 1200 V and  $V_{GS}$  of 0 V. The fin-channel barrier height was then extracted in each simulated device, as plotted in Fig. 5(a) and (b). As shown, a smaller fin width and longer gate could increase the energy barrier as they strengthens the gate control over the electrostatics in the fin channel. The removal or reduction of  $Q_{ox}$  could also effectively lift the energy barrier, as the  $Q_{ox}$  shields the gate from the electrostatic control over the fin channel. As an example, the barrier height can be lifted to be above 0.7 eV in the FinFETs with a  $Q_{ox}$  of 10<sup>12</sup> cm<sup>-2</sup>, either by shrinking the fin width to below 300 nm (while keeping the 750 nm gate length) or increasing the gate length to beyond 1 µm (while keeping the 450 nm fin width).

FIG. 5. Simulated channel energy barrier in the FinFETs with (a) different fin widths from 50 nm to 500 nm (for 750 nm gate length) and (b) different gate lengths from 0.2  $\mu$ m to 1.6  $\mu$ m (for two fin widths 200 nm and 450 nm), with and without oxide/GaN charges  $Q_{0x}$ , all at  $V_{DS}$ =1200 V and  $V_{GS}$ =0 V.

In summary, this work unveils two distinct leakage and breakdown mechanisms in GaN vertical power FinFETs. We believe that these two competing mechanisms are also important for the understanding and design of other junctionless power transistors, such as static induction transistors, metal-semiconductor FETs, etc., based on GaN and other materials, such as Ga<sub>2</sub>O<sub>3</sub>. For example, device punch-thorough was also observed in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> power FinFETs due to the DIBL effect in the fin channel,<sup>7,30</sup> although the quantitative models may be different. Two general implications can be obtained in this work for

Vertical junctionless power transistors: (a)  $V_{th}>0$  is not a sufficient criterion for normally-off operation; the device should also blicking sustain the high  $V_{DS}$  at  $V_{GS}=0$  V; (b) it is crucial to maintain a sufficiently high energy barrier in the channel at high  $V_{DS}$ ; this should be carefully considered in the device design.

#### Acknowledgement

This work was supported in part by a faculty start-up fund at Virginia Tech, and in part by the ARPA-E SWITCHES program monitored by Dr. Isik Kizilyalli. The authors greatly acknowledge Silvaco for providing TCAD simulator licenses.

### REFERENCES

- <sup>1</sup> J. Millán, P. Godignon, X. Perpiñà, A. Pérez-Tomás, and J. Rebollo, IEEE Trans. Power Electron. 29, 2155 (2014).

- <sup>2</sup> H. Amano, Y Baines, E Beam, Matteo Borga, T Bouchet, Paul R Chalker, M Charles, Kevin J Chen, Nadim Chowdhury, Rongming Chu *et al.*, J. Phys. Appl. Phys. **51**, 163001 (2018).

- <sup>3</sup> J. Holmes, M. Dutta, F.A. Koeck, M. Benipal, J. Brown, B. Fox, R. Hathwar, H. Johnson, M. Malakoutian, M. Saremi, A. Zaniewski, R. Alarcon, S. Chowdhury, S.M. Goodnick, and R.J. Nemanich, Nucl. Instrum. Methods Phys. Res. Sect. Accel. Spectrometers Detect. Assoc. Equip. **903**, 297 (2018).

- <sup>4</sup> M. Saremi, R. Hathwar, M. Dutta, F.A.M. Koeck, R.J. Nemanich, S. Chowdhury, and S.M. Goodnick, Appl. Phys. Lett. **111**, 043507 (2017).

- <sup>5</sup> S.E. Jamali Mahabadi and H. Amini Moghadam, Phys. E Low-Dimens. Syst. Nanostructures 74, 25 (2015).

- <sup>6</sup> H.A. Moghadam, S. Dimitrijev, J. Han, D. Haasmann, and A. Aminbeidokhti, IEEE Trans. Electron Devices **62**, 2670 (2015).

- <sup>7</sup>Z. Hu, K. Nomoto, W. Li, N. Tanen, K. Sasaki, A. Kuramata, T. Nakamura, D. Jena, and H.G. Xing, IEEE Electron Device Lett. **39**, 869 (2018).

- <sup>8</sup>Y. Zhang, M. Sun, Z. Liu, D. Piedra, H.S. Lee, F. Gao, T. Fujishima, and T. Palacios, IEEE Trans. Electron Devices **60**, 2224 (2013).

- <sup>9</sup>H. Nie, Q. Diduck, B. Alvarez, A.P. Edwards, B.M. Kayes, M. Zhang, G. Ye, T. Prunty, D. Bour, and I.C. Kizilyalli, IEEE Electron Device Lett. **35**, 939 (2014).

- <sup>10</sup> D. Ji, A. Agarwal, H. Li, W. Li, S. Keller, and S. Chowdhury, IEEE Electron Device Lett. **39**, 863 (2018).

- <sup>11</sup>D. Shibata, R. Kajitani, M. Ogawa, K. Tanaka, S. Tamura, T. Hatsuda, M. Ishida, and T. Ueda, in 2016 IEEE Int. Electron Devices Meet. IEDM (2016), pp. 10.1.1-10.1.4.

<sup>2</sup> F. Oka, T. Ina, Y. Ueno, and J. Nishii, in 2016 28th Int. Symp. Power Semicond. Devices ICs ISPSD (2016), pp. 459–462.

- Publishing C. Gupta, S.H. Chan, A. Agarwal, W. Li, S. Keller, U.K. Mishra, and S. Chowdhury, in 2017 IEEE Int. Electron Devices Meet. IEDM (2017), pp. 9.4.1-9.4.4.

- <sup>14</sup> M. Sun, Y. Zhang, X. Gao, and T. Palacios, IEEE Electron Device Lett. 38, 509 (2017).

- <sup>15</sup> Y. Zhang, M. Sun, D. Piedra, J. Hu, Z. Liu, Y. Lin, X. Gao, K. Shepard, and T. Palacios, in 2017 IEEE Int. Electron Devices Meet. IEDM (2017), pp. 9.2.1-9.2.4.

- <sup>16</sup> Y. Zhang, M. Sun, J. Perozek, Z. Liu, A. Zubair, D. Piedra, N. Chowdhury, X. Gao, K. Shepard, and T. Palacios, IEEE Electron Device Lett. **40**, 75 (2019).

- <sup>17</sup> M. Saremi, A. Afzali-Kusha, and S. Mohammadi, Microelectron. Eng. 95, 74 (2012).

- <sup>18</sup> B. Yu, L. Chang, S. Ahmed, H. Wang, S. Bell, C. Yang, C. Tabery, C. Ho, Q. Xiang, T. King, J. Bokor, C. Hu, M. Lin, and D. Kyser, in *Dig. Int. Electron Devices Meet.* (2002), pp. 251–254.

- <sup>19</sup> Y. Zhang, M. Sun, Z. Liu, D. Piedra, J. Hu, X. Gao, and T. Palacios, Appl. Phys. Lett. 110, 193506 (2017).

- <sup>20</sup> Y. Zhang, M. Sun, H. Wong, Y. Lin, P. Srivastava, C. Hatem, M. Azize, D. Piedra, L. Yu, T. Sumitomo, N.A. de Braga, R.V. Mickevicius, and T. Palacios, IEEE Trans. Electron Devices **62**, 2155 (2015).

- <sup>21</sup> Y. Zhang, M. Sun, Z. Liu, D. Piedra, M. Pan, X. Gao, Y. Lin, A. Zubair, L. Yu, and T. Palacios, in 2016 IEEE Int. Electron Devices Meet. IEDM (2016), pp. 10.2.1-10.2.4.

- <sup>22</sup> Y. Zhang, M. Sun, S. J. Joglekar, T. Fujishima, and T. Palacios, Appl. Phys. Lett. 103, 033524 (2013).

- <sup>23</sup> X. Sun, Y. Zhang, K. S. Chang-Liao, T. Palacios, and T. P. Ma, in 2014 IEEE Int. Electron Devices Meet. IEDM (2016), pp. 17.3.1-17.3.4.

- <sup>24</sup> M. Sun, Vertical Gallium Nitride Power Devices on Bulk Native Substrates, Doctoral dissertation, Massachusetts Institute of Technology, Cambridge, 2017.

- <sup>25</sup> Y. Zhang, H.Y. Wong, M. Sun, S. Joglekar, L. Yu, N.A. Braga, R.V. Mickevicius, and T. Palacios, in 2015 IEEE Int. Electron Devices Meet. IEDM (2015), pp. 35.1.1-35.1.4.

- <sup>26</sup>A. Rose, Phys. Rev. **97**, 1538 (1955).

- <sup>27</sup> Y. Zhang, A. Dadgar, and T. Palacios, J. Phys. Appl. Phys. 51, 273001 (2018).

- <sup>28</sup> Y. Zhang, M. Sun, D. Piedra, M. Azize, X. Zhang, T. Fujishima, and T. Palacios, IEEE Electron Device Lett. **35**, 618 (2014).

- <sup>29</sup>C. Zhou, Q. Jiang, S. Huang, and K.J. Chen, IEEE Electron Device Lett. 33, 1132 (2012).

Z. Hu, K. Nomoto, W. Li, Z. Zhang, N. Tanen, Q.T. Thieu, K. Sasaki, A. Kuramata, T. Nakamura, D. Jena, and H.G. Xing,

Publishipper hys. Lett. 113, 122103 (2018).