# LIMITATIONS AND OPPORTUNITIES FOR WIRE LENGTH PREDICTION IN GIGASCALE INTEGRATION

A Dissertation Presented to The Academic Faculty

by

Pranav Anbalagan

In Partial Fulfillment

of the Requirements for the Degree

PhD in the

School of Electrical and Computer Engineering

Georgia Institute of Technology May 2007

**COPYRIGHT 2007 BY PRANAV ANBALAGAN**

# LIMITATIONS AND OPPORTUNITIES FOR WIRELENGTH PREDICTIOIN IN GIGASCALE INTEGRATION

# Approved by:

Dr. Jeff Davis, Advisor School of Electircal & Computer Engineering Georgia Institute of Technology

Dr. James Meindl School of Electrical & Computer Engineering Georgia Institute of Technology

Dr. Scott Wills School of Electrical & Computer Engineering Georgia Institute of Technology Dr. Sung Kyu Lim School of Electrical & Computer Engineering Georgia Institute of Technology

Dr. Paul Kohl School of Chemical & Biomolecular Engineering Georgia Institute of Technology

Date Approved: December 7, 2006

### **ACKNOWLEDGEMENTS**

First and foremost, I would particularly like to thank Dr. Jeff Davis for giving me the opportunity to work with him and letting me pursue my other interests at the same time. This I believe has been crucial in my development as a person. I am truly grateful to Dr. James Meindl, Dr. Scott Wills, Dr. Sung Kyu Lim and Dr. Paul Kohl for their guidance in this research work. I am also truly grateful to Dr. Pat Dickson for helping me foster my entrepreneurial spirit.

Finally, I wish to thank Georgia Institute of Technology for letting me pursue my PhD while being a part of its culturally diverse community. My life here would not have been so enjoyable had it not been for the rich group of friends from all corners of the world that I made at Georgia Institute of Technology.

# TABLE OF CONTENTS

|                                         | Page |

|-----------------------------------------|------|

| ACKNOWLEDGEMENTS                        | iv   |

| LIST OF TABLES                          | vii  |

| LIST OF FIGURES                         | viii |

| SUMMARY                                 | xi   |

| <u>CHAPTER</u>                          |      |

| 1 Introduction                          | 1    |

| VLSI Design Flow                        | 2    |

| Wire Model Terminologies                | 11   |

| History of Wire Length Prediction       | 14   |

| Proposed Research                       | 19   |

| 2 Limitations of Macroscopic Prediction | 22   |

| Variability of Distributions            | 23   |

| Macroscopic Models Overview             | 31   |

| Limitations of Macroscopic Models       | 44   |

| Summary                                 | 50   |

| 3 New Macroscopic Model                 | 52   |

| Terminal-to-Block Size Relation         | 53   |

| Exponent Model                          | 57   |

| Exponent Model Parameters               | 59   |

| New Wire Length Distribution Model      | 67   |

| New Model Results                       | 71   |

| Summary                                 | 75   |

| 4    | Limitations of Microscopic Prediction | 76  |

|------|---------------------------------------|-----|

|      | Microscopic Repeatability             | 76  |

|      | Microscopic Models Overview           | 86  |

|      | Limitations of Microscopic Models     | 94  |

|      | Summary                               | 96  |

| 5    | New Microscopic Model                 | 98  |

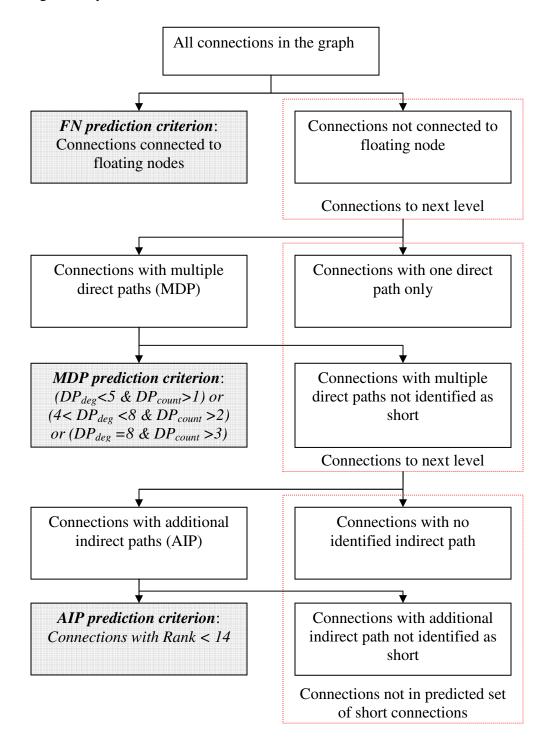

|      | New Heuristic Classification Tree     | 101 |

|      | New Model Results                     | 113 |

|      | New Model Application                 | 118 |

|      | Summary                               | 121 |

| 6    | Conclusion and Future Work            | 122 |

|      | Macroscopic Prediction Summary        | 122 |

|      | Microscopic Prediction Summary        | 125 |

|      | Key Knowledge Contributions           | 127 |

|      | Future Work                           | 128 |

| REFE | RENCES                                | 129 |

# LIST OF TABLES

|                                                                                     | Page |

|-------------------------------------------------------------------------------------|------|

| Table 1.1: Benchmarks used in the research and their attributes                     | 21   |

| Table 2.1: Average interconnect length intra-tool and inter-tool variability        | 24   |

| Table 2.2: Percent total interconnect length in non-repeatable part of distribution | 29   |

| Table 2.3: Zone attributes of DDM model length distribution                         | 43   |

| Table 3.1: Length distribution's zone attributes DDM model vs. new model            | 73   |

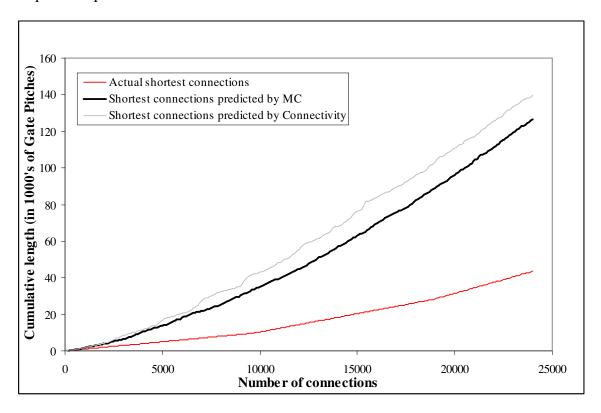

| Table 4.1: Difference in cumulative length (mutual contraction vs. actual shortest) | 96   |

| Table 5.1: Average length of connections in multiple direct paths                   | 106  |

| Table 5.2: Standard deviation of length of connections in multiple direct paths     | 106  |

| Table 5.3: Distribution of violations among the connections predicted as short      | 107  |

| Table 5.4: Statistics of length of connections for each rank                        | 110  |

| Table 5.5: Distribution of violations among the connections predicted as short      | 111  |

| Table 5.6: Heuristic classification tree vs. mutual contraction model               | 115  |

| Table 5.7: Placement application result of heuristic classification tree            | 120  |

# LIST OF FIGURES

|                                                                                    | Page |

|------------------------------------------------------------------------------------|------|

| Figure 1.1: Various design phases involved in a typical VLSI design flow           | 5    |

| Figure 1.2: Relation between design space exploration and design choice evaluation | 10   |

| Figure 1.3: Net model of a wire and corresponding length estimation models         | 12   |

| Figure 1.4: Interconnect model of a wire and corresponding length estimation model | 13   |

| Figure 1.5: Connection model of a wire and corresponding length estimation model   | 14   |

| Figure 1.6: A net and its first level neighborhood                                 | 16   |

| Figure 2.1: Intra-tool length distribution variability for IBM03                   | 25   |

| Figure 2.2: Percentile rank of length below which the distribution is repeatable   | 26   |

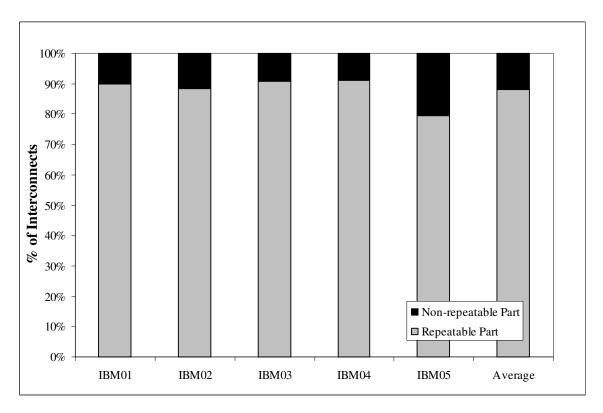

| Figure 2.3: Percent interconnects in the repeatable part of distribution           | 27   |

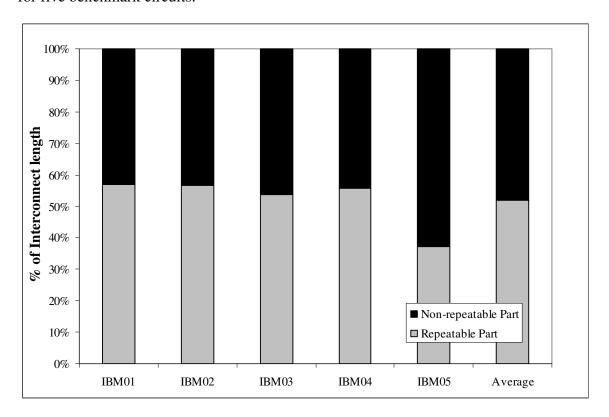

| Figure 2.4: Percent interconnect length in the repeatable part of distribution     | 28   |

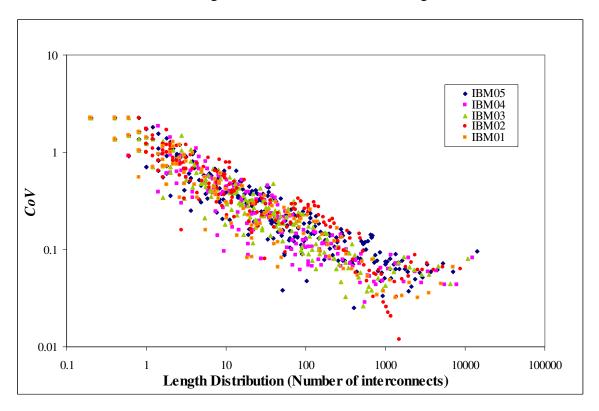

| Figure 2.5: Relation between length distribution and its coefficient of variation  | 30   |

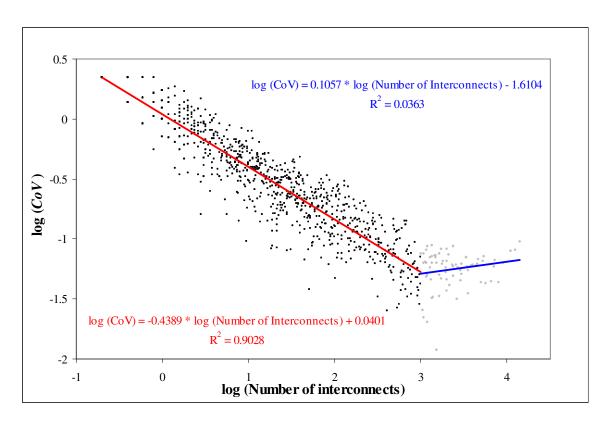

| Figure 2.6: Piecewise model of the coefficient of variation of length distribution | 31   |

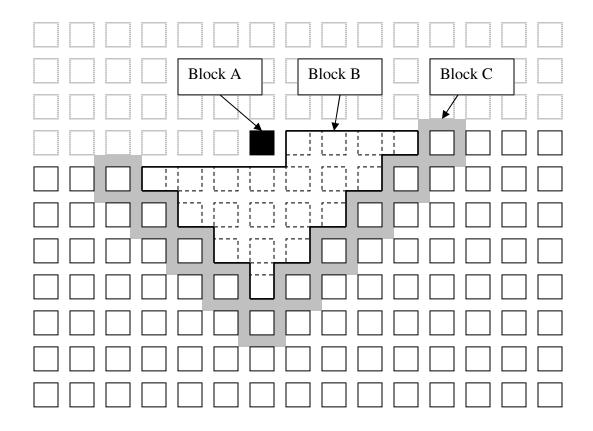

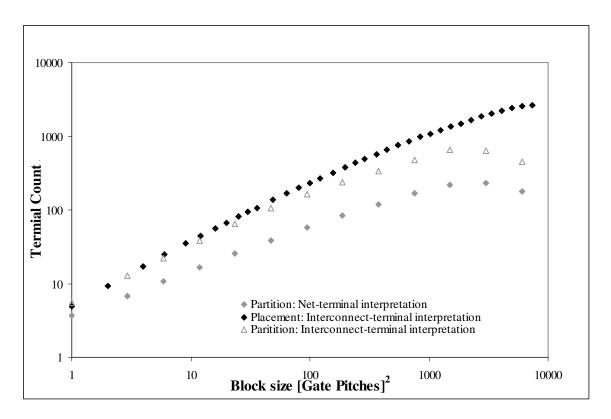

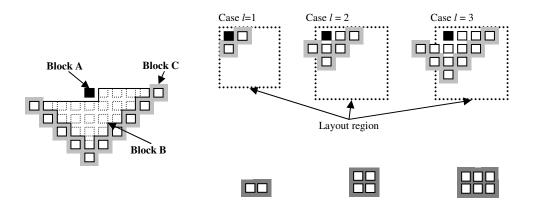

| Figure 2.7: Blocks used in interconnect length distribution model derivation       | 34   |

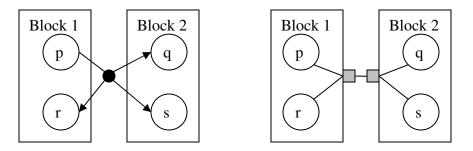

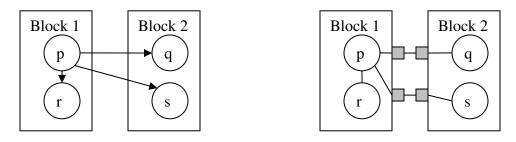

| Figure 2.8: Net model (left) and net-terminal interpretation                       | 36   |

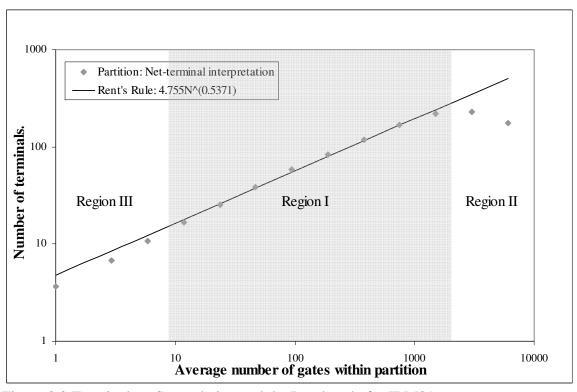

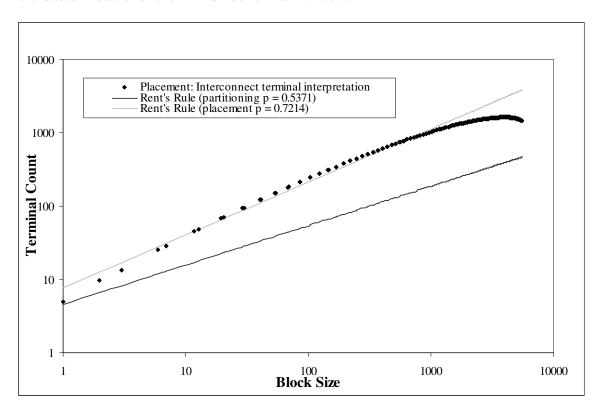

| Figure 2.9: Terminal-to-Gate relation and the Rent's rule for IBM01                | 41   |

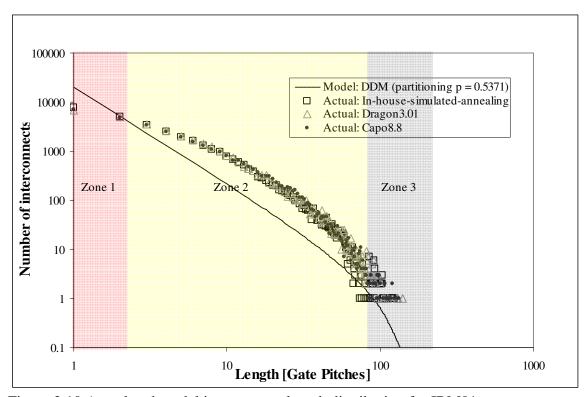

| Figure 2.10: Actual and model interconnect length distribution for IBM01           | 42   |

| Figure 2.11: Interconnect model and interconnect-terminal interpretation           | 45   |

| Figure 2.12: Validity of conservation of terminals                                 | 46   |

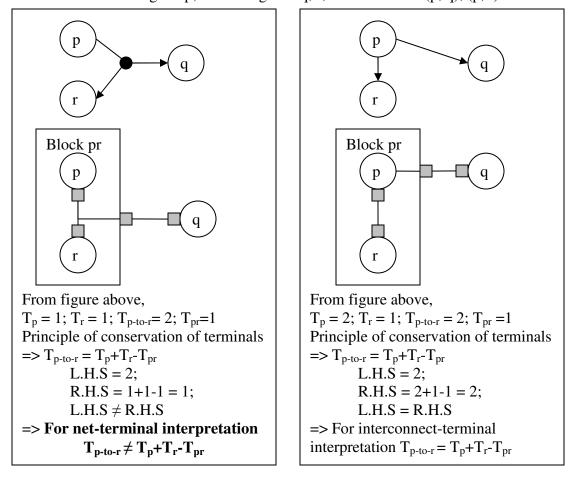

| Figure 2.13: Terminal-to-Gate and Terminal-to-Block Size relation for IBM01        | 47   |

| Figure 2.14: Terminal count extraction strategies                                  | 47   |

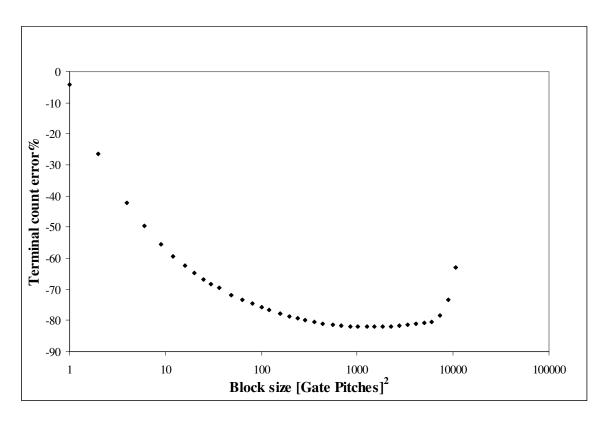

| Figure 2.15: Error in terminal count as a result of using Rent's rule for IBM01    | 49   |

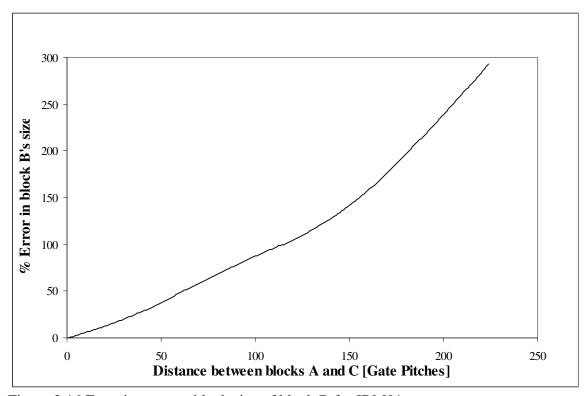

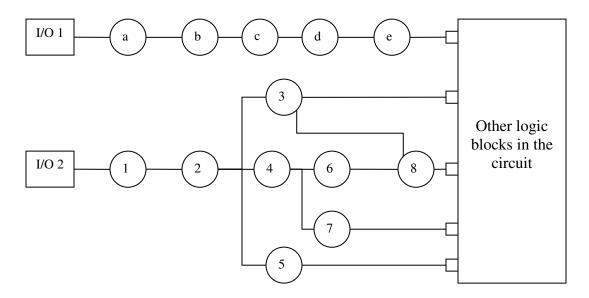

| Figure 2.16: Error in average block size of block B for IBM01                      | 50   |

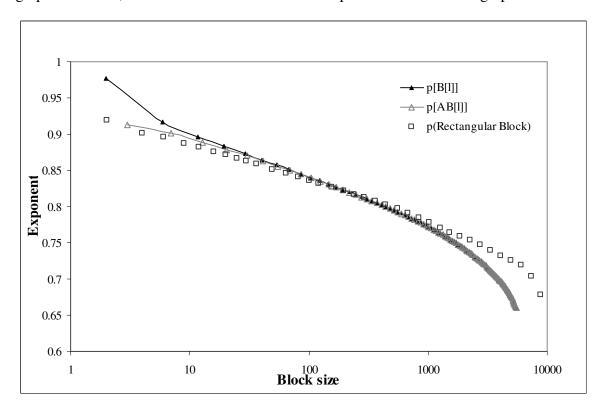

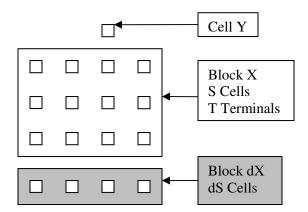

| Figure 3.1: Actual and model T-to-BS relation of IBM01                               | 53 |

|--------------------------------------------------------------------------------------|----|

| Figure 3.2: Actual exponent values for various block sizes of IBM01                  | 55 |

| Figure 3.3: Actual block shapes used by model and rectangular blocks of small sizes  | 56 |

| Figure 3.4: Blocks used to derive exponent p model                                   | 57 |

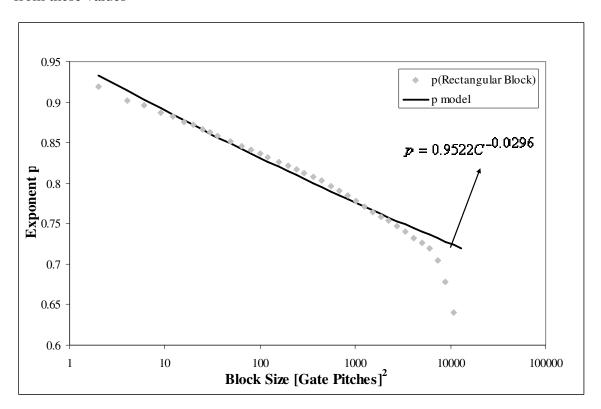

| Figure 3.5: Model of exponent p fitted to actual p values of rectangular blocks      | 59 |

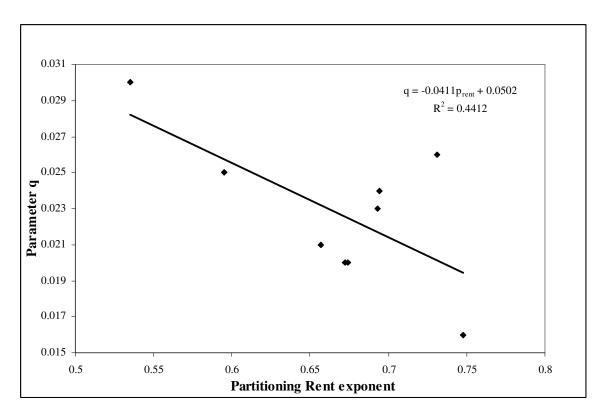

| Figure 3.6: Parameter $q$ vs. partitioning Rent exponent                             | 61 |

| Figure 3.7: Influence of layout architecture and netlist structure on interconnects  | 62 |

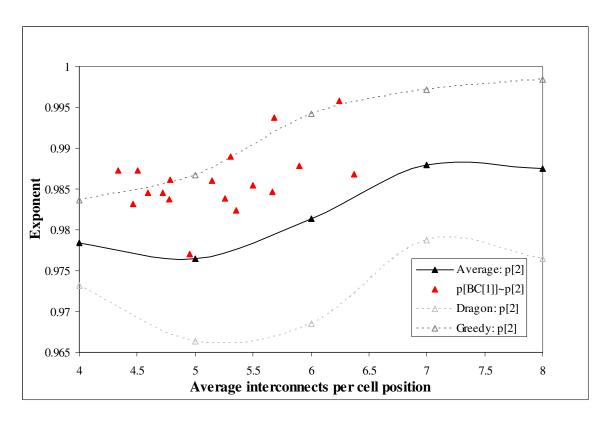

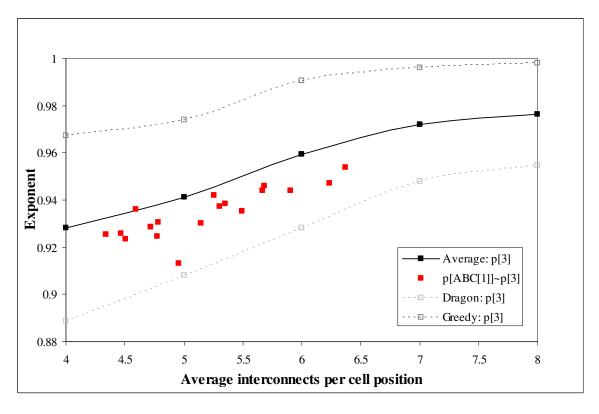

| Figure 3.8: Exponent $p[BC[l=1]]$ vs. average interconnects per cell position        | 65 |

| Figure 3.9: Exponent $p[ABC[l=1]]$ vs. average interconnects per cell position       | 65 |

| Figure 3.10: Coefficient of variation as a function interconnect length distribution | 69 |

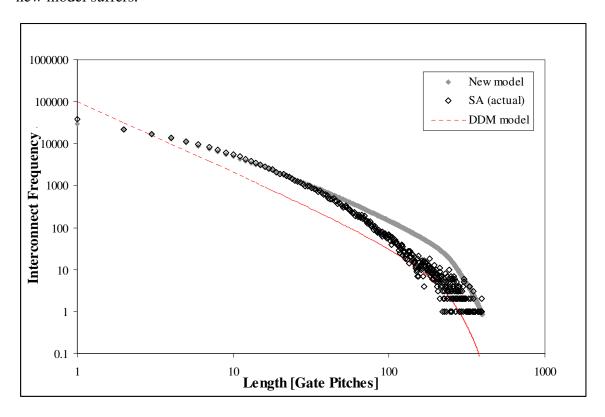

| Figure 3.11: New model results against the DDM model results for IBM10               | 71 |

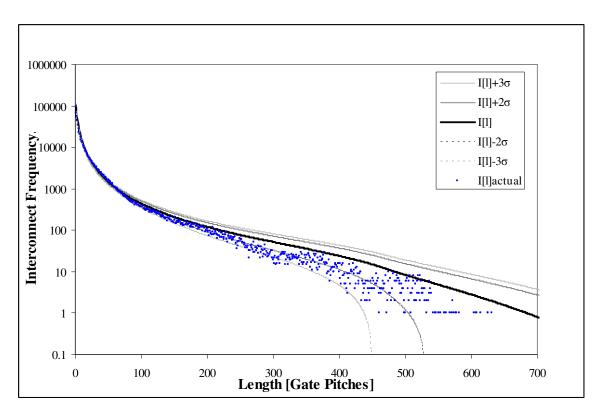

| Figure 3.12: Results of new model with variability for IBM18                         | 74 |

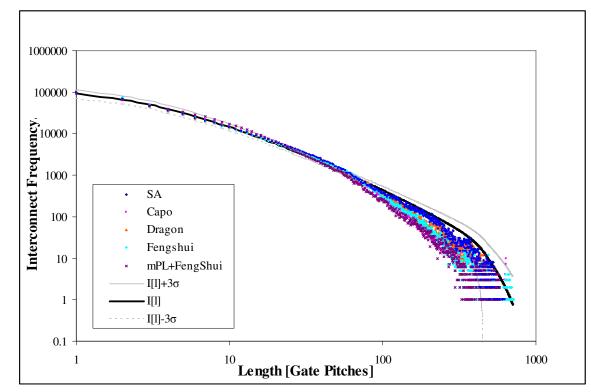

| Figure 3.13: New model against results from different placements for IBM18           | 74 |

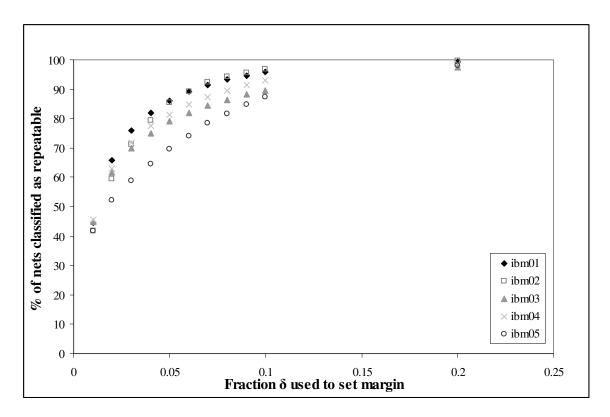

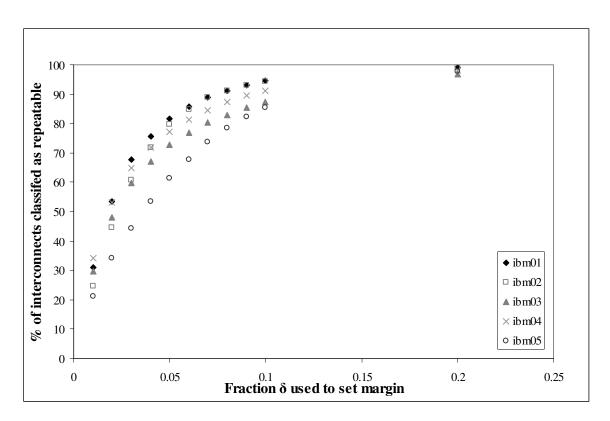

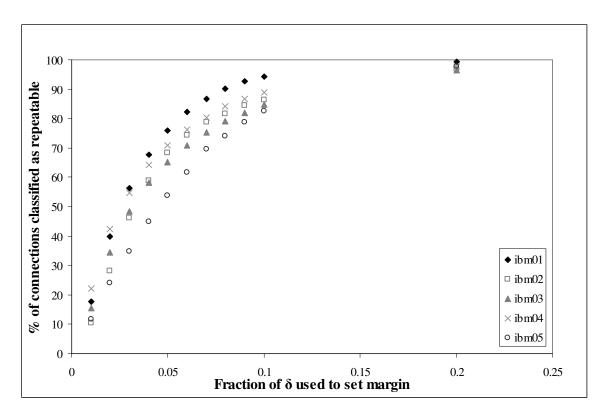

| Figure 4.1: Percent of repeatable nets vs. fraction $\delta$                         | 79 |

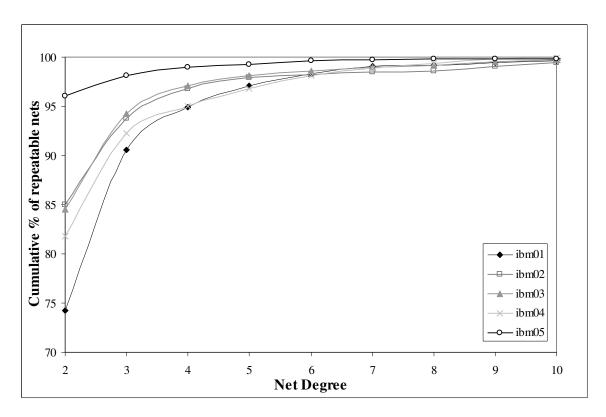

| Figure 4.2: Cumulative percent share of repeatable nets vs. net degree               | 80 |

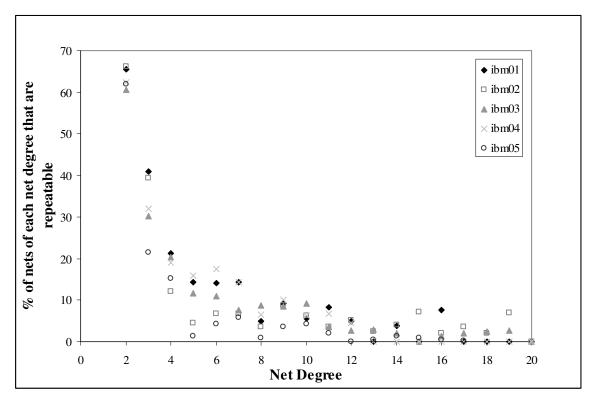

| Figure 4.3: Percent of repeatable nets among each net degree for $\delta = 0.01$     | 80 |

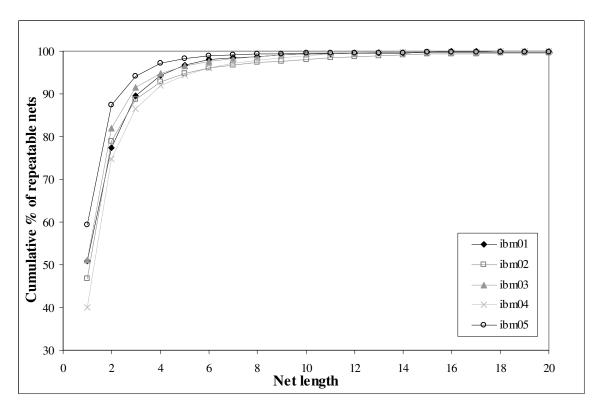

| Figure 4.4: Cumulative percent share of repeatable nets as a function of net length  | 81 |

| Figure 4.5: Percent of repeatable interconnects vs. fraction $\delta$                | 82 |

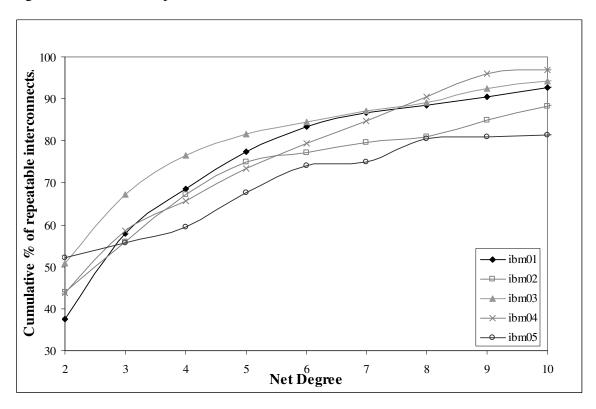

| Figure 4.6: Cumulative percent share of repeatable interconnects vs. net degree      | 82 |

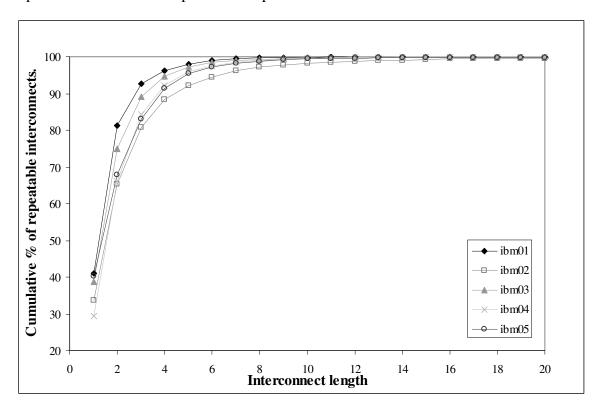

| Figure 4.7: Cumulative percent share of repeatable interconnects vs. length          | 83 |

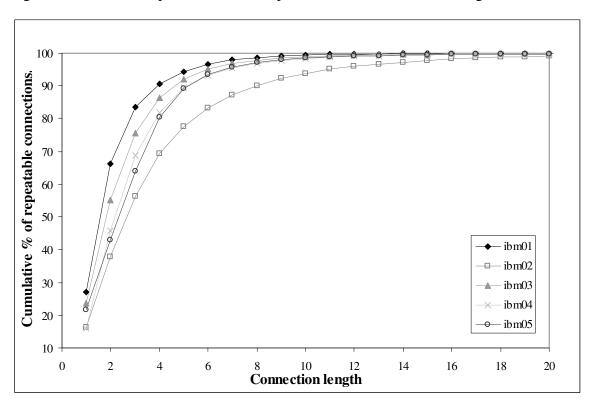

| Figure 4.8: Percent of repeatable connections vs. fraction $\delta$                  | 84 |

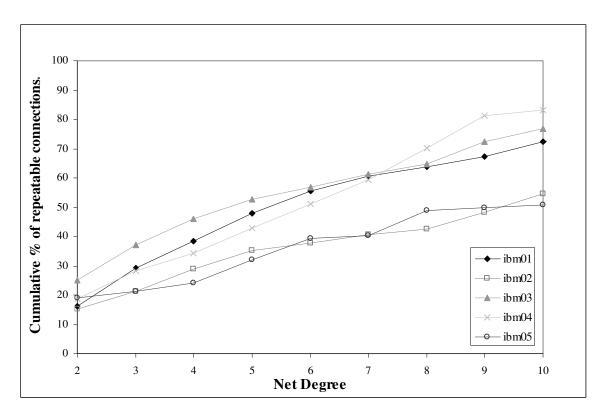

| Figure 4.9: Cumulative percent share of repeatable connections vs. net degree        | 85 |

| Figure 4.10: Cumulative percent share of repeatable connections vs. length           | 85 |

| Figure 4.11: Possible placement configurations of 2, 3 and 4 pin nets                | 88 |

| Figure 4.12: Illustration for relative weight estimation                             | 93 |

| Figure 4.13: Cumulative length of shortest connections for IBM01                  | 95  |

|-----------------------------------------------------------------------------------|-----|

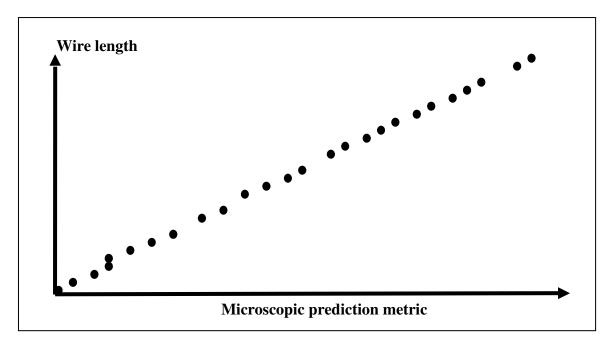

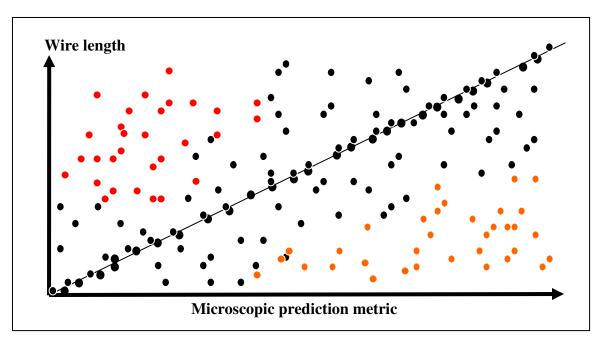

| Figure 5.1: Ideal relation between microscopic prediction metric and wire length  | 98  |

| Figure 5.2: Relation observed between prediction metrics and actual wire length   | 99  |

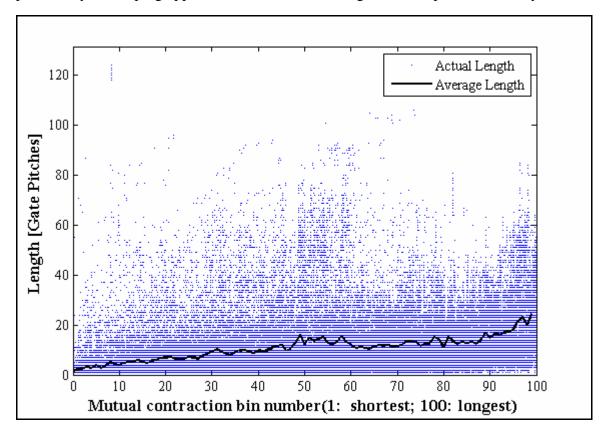

| Figure 5.3: Connections sorted based on mutual contraction and arranged in bins   | 100 |

| Figure 5.4: Direct and indirect paths                                             | 102 |

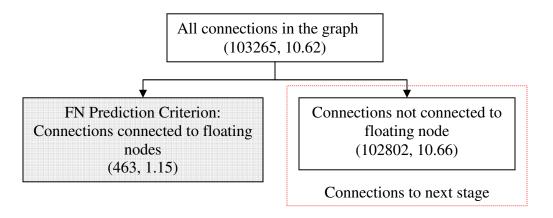

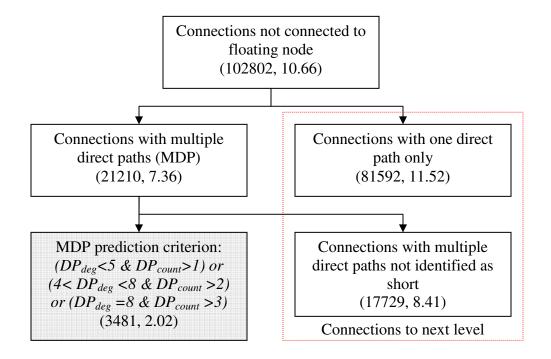

| Figure 5.5: New heuristic classification tree (stage 1)                           | 103 |

| Figure 5.6: New heuristic classification tree (stage 2)                           | 104 |

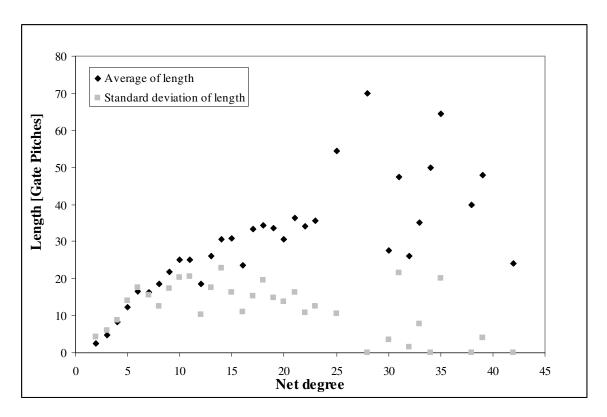

| Figure 5.7: Average length of a net for different net degrees in IBM01            | 105 |

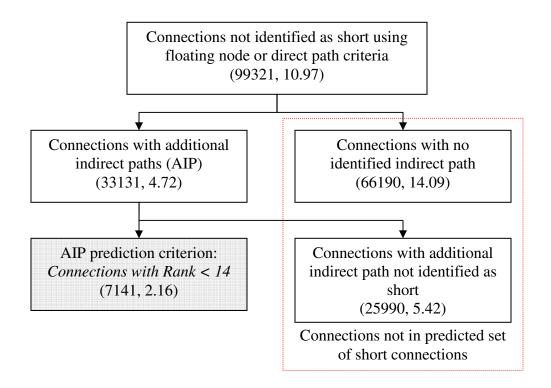

| Figure 5.8: New heuristic classification tree (stage 3)                           | 111 |

| Figure 5.9: Complete heuristic classification tree model                          | 112 |

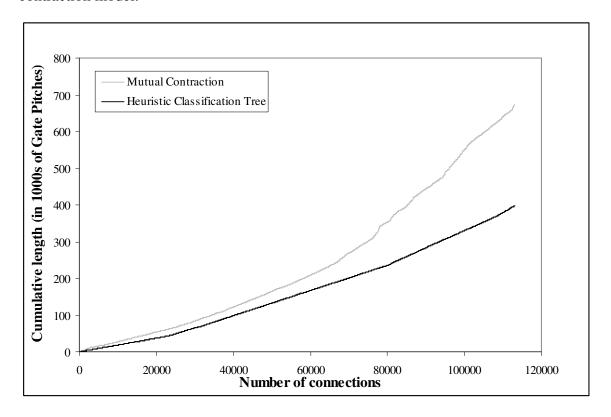

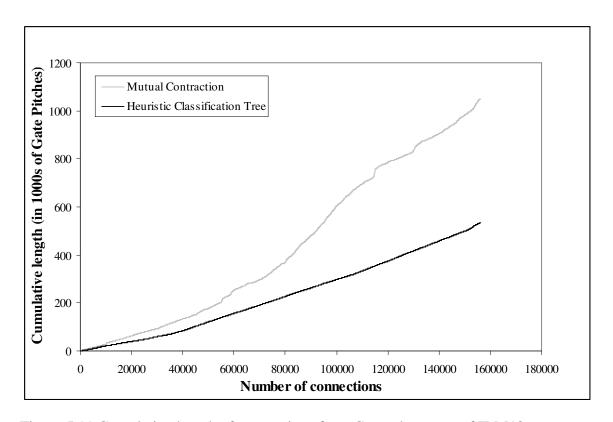

| Figure 5.10: Cumulative length of connections from Dragon placement of IBM16      | 113 |

| Figure 5.11: Cumulative length of connections from Capo placement of IBM18        | 114 |

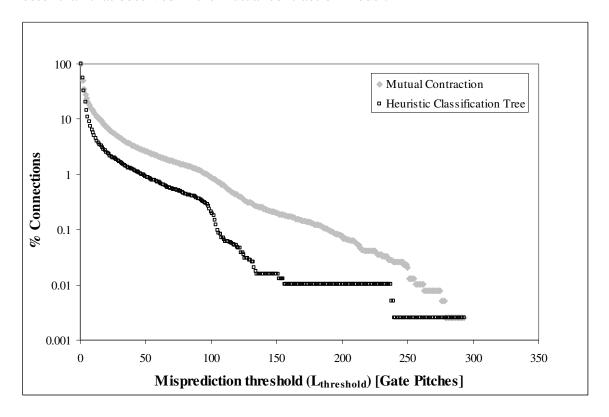

| Figure 5.12: Difference in prediction quality observed in IBM16                   | 116 |

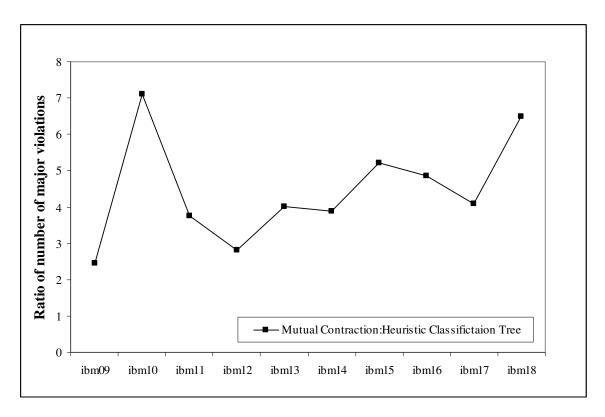

| Figure 5.13: Ratio of major violation in the prediction                           | 117 |

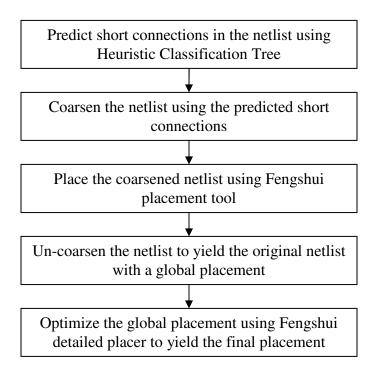

| Figure 5.14: Placement application framework of the heuristic classification tree | 118 |

# **SUMMARY**

Wires have become a major source of bottleneck in current VLSI designs, and wire length prediction is therefore essential to overcome these bottlenecks. Wire length prediction is broadly classified into two types: macroscopic prediction, which is the prediction of wire length distribution, and microscopic prediction, which is the prediction of individual wires. The objective of this thesis is to develop a clear understanding of limitations to both macroscopic and microscopic a priori post-placement pre-routing wire length predictions, and thereby develop better wire length prediction models.

Investigations carried out to understand the limitations to macroscopic prediction reveal that, in a given design (i) the variability of the wire length distribution increases with length and (ii) the use of Rent's rule with a *constant Rent's exponent p*, to calculate the terminal count of a given block size, limits the accuracy of the results from a macroscopic model. Therefore, a new model for the parameter p is developed to more accurately reflect the terminal count of a given block size in placement, and using this, a new more accurate macroscopic model is developed. In addition, a model to predict the variability is also incorporated into the macroscopic model.

Studies to understand limitations to microscopic prediction reveal that (i) only a fraction of the wires in a given design are predictable, and these are mostly from *shorter nets with smaller degrees* and (ii) the current microscopic prediction models are built based on the assumption that a single metric could be used to accurately predict the individual length of all the wires in a design. In this thesis, an alternative microscopic model is developed for the predicting the shorter wires based on a hypothesis that there

are multiple metrics that influence the length of the wires. Three different metrics are developed and fitted into a heuristic classification tree framework to provide a unified and more accurate microscopic model.

# **CHAPTER 1**

## INTRODUCTION

The size of the worldwide electronics industry is estimated to be at roughly \$1.3 trillion which has grown at roughly 7.1% for the last two decades. Practically every product of this industry is built out of the \$300 billion semiconductor industry, which grew at 24.8% in 2004 and has been growing at roughly 15.1% during the past two decades. And nearly 28% of the \$300 billion semiconductor industry is the Application Specific Integrated Circuit (ASIC) Industry. To put the economic significance of the size of these numbers in perspective the total world Gross Domestic Product (GDP) value is estimated at roughly \$46 trillion, just 39x times the size of the electronic industry, and the world GDP has grown at just 3.2% for the past two decades. However, in order to maintain this growth, one must challenge the frontiers of semiconductor chip design.

With the advancements in semiconductor technology however, a bottleneck has been developing in the design process due to the influence of the wires in the overall specifications of a design [1]. One of the primary causes of this bottleneck is the lack of a clear perspective of the influence of the wires on the design's specifications during the early stages of the design process. If the length of the wires could be predicted early on during the design process, it could help overcome some of the major bottlenecks. Therefore, in this research an attempt has been made to identify the limitations to wire length prediction, and based on the knowledge gained through the study of limitations, new wire length prediction models are developed.

The core of the semiconductor design process is the Very Large Scale Integrated (VLSI) chip design flow, and the wire length problem manifests itself during this process. Therefore, in the first section of this chapter an overview of the VLSI Design flow is provided, followed by the subsections detailing the influence of the wires on the various

design specifications and the motivation for wire length prediction. In order to predict the length of the wires, it is essential to model the length of the wires, and subsequently the second section of the chapter defines the terminology used in various wire models. The third section then provides an overview of the history of various approaches to the wire length prediction problem. Finally, the chapter is concluded with an outline of the approach used in this research along with the assumptions and the basic experimental setups used in this work.

#### **VLSI Design Flow**

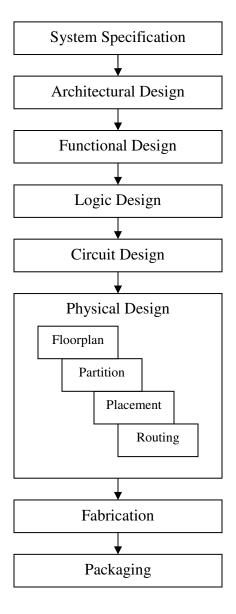

The design of a VLSI chip starts with setting target specifications for the chip and ends with a packaged chip after several design stages. Each design stage is aimed at simplifying the complexity of the design process to a manageable level. The various stages involved in this process are explained in this section along with a simplified design flow depicting the stages in Figure 1.1.

- 1. System specification: Setting the target specifications of the design is the first step of the design process. The specifications include identification of the overall functionality of the chip, its performance requirements and its target physical dimensions. These are derived based on market requirements and economic feasibility. Performance specifications will usually include the specifications of speed, power consumption, heat dissipation, etc... The physical and performance specifications are set based on the limits of the available technology.

- 2. Architectural Design: The second major step in the design process is to decide on the architectural specification of the chip. This includes decisions such as the instruction set, the number of pipeline stages, the number of ALU and or other such functional units and how they should be connected to each other.

- Various architectural possibilities are explored at this stage to choose the best architecture to meet the target specifications.

- 3. Functional Design: Functional design involves selection of the various functional units and their interrelationships in terms of timing, power, heat dissipation, noise etc... to meet the target specifications. For example, this step involves decisions about the inputs to a particular functional unit, the outputs of the unit, the connections to other functional units, the sequence in which the various functional units have to operate in order for the design to meet the targeted behavior of the design.

- 4. Logic Design: The functional blocks developed at the previous stage are decomposed into Boolean expressions and is represented using the Register Transfer Level (RTL) description. This entails making decisions about the bit-by-bit logical details of the functional blocks and the corresponding control signal details. The Boolean expressions are then optimized, using a process called synthesis, to yield the smallest logic design for the given behavioral design. The result is a gate level description of the design.

- 5. Circuit Design: The circuit design stage involves designing circuits for the gates used in the design while considering the requirements of functionality, performance and physical specifications of the design. This stage produces transistor level details from the gate level description created during the logic design stage. This stage brings into view the detailed physics of the transistors and hence the performance of the gates in the design through the circuit level simulation.

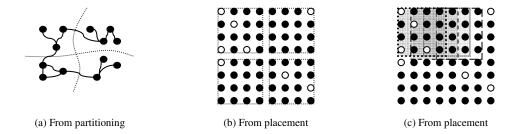

- 6. Physical Design: Physical design is the process of physically allocating space for transistors and wires in a multilevel layout in which the given design will be manufactured. Due to the complexity of this stage, it is further subdivided into various steps viz., floorplanning, partitioning, placement and routing.

Only at the end of these stages does the designer have a clear view of the layout of wires present in the design and therefore their dimensional attributes.

- a. Floorplanning is the process of planning where each of the major architectural and or functional blocks or partitions should be placed in the layout.

- b. Partitioning is the process of dividing the circuit into several groupings(i.e. partitions) to bring the cells that are highly connected closer together by including them within the same partition.

- c. Placement is the process of assigning an optimal location for each cell or gate in a design block or partition to the area allocated for that particular design block or partition in the layout.

- d. Routing is the process of assigning an optimal location for each wire in the multiple levels of metal available in the layout.

- 7. Fabrication: The layout details obtained from the previous stage is first transformed into a set of photolithographic masks. These masks are then used to guide the diffusion, deposition or removal of various chemicals in the substrate to build the multiple layers of chemicals which together form an electronic chip. Several hundred chips are manufactured on a single wafer substrate, which is then diced into individual chips. Only during testing at the end of this stage does the fabrication induced effects on chip performance come to light for the first time.

- 8. Packaging: The individual chips are then packaged using the appropriate packaging technology or used directly in Multi-Chip Modules. The final chip is then tested against the target specifications.

Figure 1.1 Various design phases involved in a typical VLSI design flow

The above step-by-step VLSI design process allows for a design to be evaluated at each stage, to check if the target specifications will be met at the end of the design process. In a case where the evaluation at the end of a design stage reveals that the targeted specifications cannot be met, additional design iteration is performed starting from an earlier stage after making some modifications to the design. However, increasing the number of iterations increases the cost of the design and its time-to-market, resulting in reduced marketability of the product.

#### **Impact of Scaling**

As the technology advances over time, the functionality of the chip is increasing with a trend that follows Moore's law [2], according to which the number of transistors in a chip doubles every 18 months. This rapid increase in the number of components within a chip is accompanied by a decrease in the feature size of the components and wires within the chip. Further, the connected gates are spread relatively farther apart in the layout as a consequence of the increased number of gates in the design. Consequently, as the size of the chips increase, so do the number of wires inside the chip and the relative length of the wires with respect to the size of the gates inside the chip. Coupled with the decreasing feature size, the resistance of the wires starts to increase dramatically since its cross-sectional area decreases and the number of longer wires increases from generation-to-generation. Further, the capacitance contribution of the wires also increases with increasing length. Meanwhile, the reduction in the feature sizes causes the transistors to switch faster. The combined interaction of these changes has allowed the wires to strongly influence every aspect of a design specification in the following ways:

1. Impact on Physical Specifications: The number of wires and their relative lengths increase from generation-to-generation and from design-to-design. To accommodate this, the number of metal levels allowed in the manufacturing technology also grows. But this growth rate is sometimes not commensurate with the amount of wire space required to accommodate the wires within the targeted physical dimensions of the chip based solely on gate occupied area. Furthermore, the increasing complexity of the designs increases the number of wires in some regions of the design, which in turn increases the wire congestion in those regions. This congestion, coupled with more wires getting longer, makes them more susceptible to noise. Therefore, increased spacing and shielding is needed between wires to alleviate possible noise problems. Consequently the wires are spread out within the available metal levels. As

- the wires are being spread out, at some point the area of the wires start to dominate over the area of the gates. Moreover, repeaters inserted to speed up the longer wires will also start pushing the layout size [3]. The result is that the wires limit the physical specification (area) of the chip.

- 2. Impact on Timing/Speed Specifications: As the resistance and capacitance of the wires increase, the time it takes for a signal to be transmitted through the wires increases. For example, wire delay degradation per scaled micron is of the order of 1.4x for every generation [3]. Further, since the time it takes for the signal to be transmitted through the transistors reduces, the propagation delay through the wires are playing a dominant role in the timing of the chip, which in turn is controlled by its length. A widely employed methodology used to reduce the propagation delay through longer wires is to insert a number of repeaters on the longer wires, where the repeaters function by allowing the signals to be accelerated through the wires. The number of repeaters that can be inserted, and hence the speed-up achieved, depends upon the length of the wires.

- 3. Impact on Power Specifications: As the number of wires and the wire length increases from technology generation-to-generation, in order to overcome the propagation delay problem, an increasing number of repeaters are employed. The number of repeaters deployed increases with the number and length of the longer wires. For example, it is predicted that 50% of the cell area at 32nm technology generation will be filled with repeaters [3]. Since each of these repeaters consume static and dynamic power, the power consumption of a design will be dominated by the number of repeaters in the design. Because the number of repeaters in the design depends upon the length of the wires in the design, the wires have started to play a major role in the power consumption specification of the chip [4].

- 4. Impact on Thermal Specifications: A large fraction of the energy is dissipated as heat during each switching event in a design. And as the wire resistance per micron doubles with every technology generation [3], more of this heat dissipation occurs through the wires. Further as the designs get more complex, some of the regions are highly congested leading to possible hot spots in the design. For example, in [5] it is argued that a non negligible amount of heat dissipation occurs through the wires. Consequently, the thermal specifications of the system are also altered by the wires present in the system.

- 5. Impact on Noise Specifications: With the increase in the length and the number of the wires, the wires are more likely to be adjacent to a number of other wires over long distances in the system. These wires are coupled with each other through a coupling capacitance and inductance and can thus induce noise on each other during switching transitions. Thus the wires are bound to influence the noise specifications of a chip design as well.

- 6. Impact on Reliability Specifications: With the increase in wire length and wire resistance, wires dissipate energy in the form of heat. As the wires get overheated this could lead to problems such as electromigration, which could affect the conductivity of the wires and thus the reliability of the design.

- 7. Impact on Functional Specification: The influence of wires as explained above in each of the performance specifications in turn influences the functionality of the overall design. For example, an unwanted time delay of the signal through the wires could change the function of clocked logic that is set up to run with a different timing specification. In addition, unwanted noise from wires could result in an undesired effect in the functionality of the design.

Thus it can be seen that the wires play a crucial role in determining the various specifications of a given design.

# **Motivation for Wire Length Prediction**

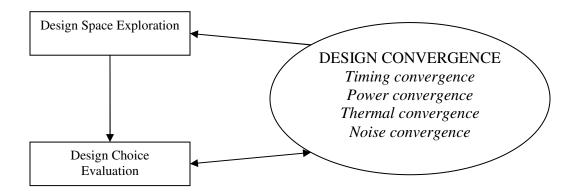

In the process of a VLSI design, the designer needs to explore the design space for each stage of the design. For example, at the architectural design phase the designer needs to evaluate the impact of the different architectural choices on the final target specifications. A highly parallel architecture choice may result in a netlist structure that is very different from a less parallel architecture choice. One architecture might result in a fewer number of gates and lesser interconnection complexity between the gates than another. Consequently, the changes in these architectural design choices could affect the final specifications of the design. Similarly, the design choices in each of the other design stages such as alternative behavioral designs, logic designs, circuit designs, partitioning strategies, floorplanning strategies, placement and routing strategies have to be explored. Each of the design choices will have their own unique attributes that will influence the final characteristics of the design.

Following the exploration of the various design choices, a decision has to be made as to which choice to use for the continued development of the design. In order to make such a decision, it is necessary to evaluate if a design choice will meet the target specifications at the end of the design process. If the design choice meets the targeted objectives, then the design is said to converge. If the evaluation stage indicates that design convergence cannot be achieved, the designer needs to go back to the previous design stages to alter the earlier design choices.

To evaluate if a design choice will meet the target specifications of the design, it is necessary to model the influence of the wires in the specifications. This is because the wires practically influence every one of the target specification metrics. And for the most part, the magnitude of this influence is dependent primarily upon the physical characteristics of the wires because its electrical attributes are dependent upon its physical characteristics. However, the physical attributes are only available at the end of the physical design stage when the gates have finally been placed in the physical layout

and the wires have been routed through the multilayer metals. Therefore, it is impossible to include the exact effect of wires on the various specification metrics at the earlier stages of the design. At the same time any evaluation of the specification metrics at the earlier stages of the design flow without an appropriate model to include the impact of wires renders them useless. This lack of information in the design specifications at the earlier stages of the design flow is one of the major bottlenecks to design convergence leading to iterations in the design flow, as shown in Figure 1.2. A prediction model of the wire attributes could, therefore, allow the designer to design by including the effect of wires from the very early stages of the design flow, and thereby could help achieve a much faster design convergence.

Figure 1.2 Relation between design space exploration and design choice evaluation

Further, the advancements in chip design and manufacturing technology will create newer design challenges. To understand and predict these newer challenges, it is necessary to develop technology extrapolation models. Such early extrapolations of future technological problems will enable the designers to be better prepared to design future systems. Due to the increasing impact of wires with scaling, it is even more important to include models that would incorporate the effect of wires on the extrapolated design problems. Since the impact of wires on a design is strongly linked to wire length, it is necessary to develop wire length prediction models.

#### **Wire Model Terminologies**

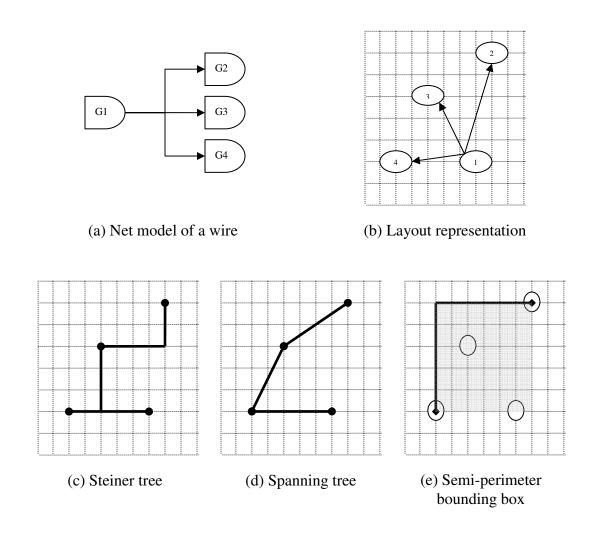

A *wire* is an equipotential connection that conducts a common electrical signal from one or more source (driver) gates to the one or more of its sink (driven) gates. During the chip design process, the design is often represented in the form of a graph with the gates or functional blocks being represented as the vertices of the graph and the edges or hyperedges between the vertices representing the wires connecting the corresponding blocks or gates. These graphical models of the wire can be classified into a *net* model, *interconnect* model and *connection* model.

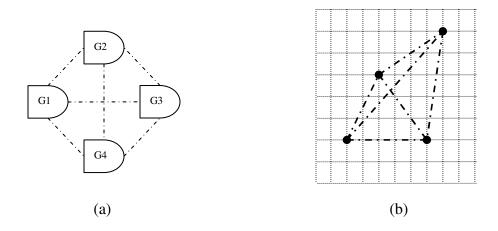

A net is the multi-terminal hyperedge model of the wire that connects all the gate nodes representing the source and sink gates of the common signal. Since the source of the common signal could be from more than one gate and since it could drive more than one gate, a net model of a given wire may have more than two terminals. This is the most accurate representation of the wire in a graph. For example, consider a signal wire with gate G1 as its source and gates G2, G3 and G4 as its sink. Such a wire can be represented as a multi-terminal hyperedge between the four gates as shown in the Figure 1.3(a). The first estimate of the length of the wire is possible only after the gates are placed on the layout. Now if the gates G1, G2, G3 and G4 are placed in a layout that is in the form of a grid, as shown in Figure 1.3(b), then the post-placement pre-routed length of the net can be computed using any of the following length estimation models shown in Figure 1.3(c), 1.3(d) and 1.3(e). Figure 1.3(c) represents the Rectilinear Steiner Tree based representation of the net. The length of the net based on the rectilinear Steiner tree is the sum of the length of the horizontal and vertical edge segments of the rectilinear Steiner tree. Figure 1.3(d) shows the spanning tree based representation of a net. The length of the net based on a spanning tree is the sum of the manhattan lengths of the edges in the spanning tree. And finally Figure 1.3(e) shows semi-perimeter bounding box based estimation of the net length. Here the length of the net is estimated as half the perimeter of the smallest rectangular box that encloses all the nodes of a given net. While

an estimation based on minimum rectilinear Steiner tree gives the minimum actual possible length between the nodes of the net, it is hard to find the actual minimal cost rectilinear Steiner tree, and the actual routed wire length may be greater than this value. However, finding a minimal rectilinear spanning tree is easier and is a close approximation to minimal rectilinear Steiner tree, but it still takes some computational power to estimate them. On the other hand, estimation of the semi-perimeter bounding box length takes significantly less computational power; but the pitfall of this method is that it could be inaccurate for nets with a large number of terminals.

Figure 1.3 Net model of a wire and corresponding length estimation models

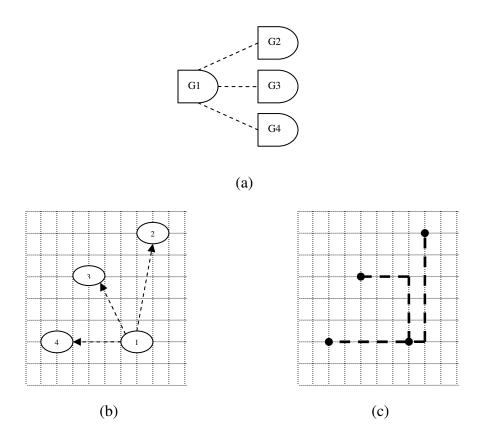

An *interconnect* model of the wire, see Figure 1.4(a) is a much simpler representation of the wire than a net. In this model, the wires with more than two terminals are decomposed into several two terminal edges. The two terminal edges run only between each pair of a source and sink gate in the net. The length estimates are then made individually for each interconnect as the manhattan distance between the two terminals of the two terminal edges as shown in figure 1.4(c). This model is similar to a spanning tree based model. The difference lies in the fact that the two terminal edges between the gates are treated individually, and also this model eliminates the computation required to find the minimal spanning tree by limiting the edges between source and sink gates of a net.

Figure 1.4 Interconnect model of a wire and corresponding length estimation model

Finally, a *connection* model of a wire is shown in Figure 1.5(a). It is a simple representation similar to interconnect model in the sense that the hyperedge is decomposed into several two terminal edges. But this model includes a two terminal edge in between every pair of terminal gates in the net. This is unlike in the interconnect model, where the two terminal edge runs solely between a source-sink gate pairs. The length of each connection is estimated separately as the manhattan distance in between the two terminal nodes of the connection placed as shown in figure 1.5(b). Based on the application requirements, all of the above models have been used in the literature to estimate wire lengths.

Figure 1.5 Connection model of a wire and corresponding length estimation model

# **History of Wire Length Prediction**

Literature research reveals wire length prediction models that provide both the microscopic and macroscopic perspectives of wires in a design. *Microscopic* perspectives are provided by models that aim to predict individual wire length, and *macroscopic* perspectives are provided by models that aim to provide a more global view of the wires by predicting statistics such as the wire length distribution. However most of these methods have their limitations and are lacking in accuracy due to the difficulty involved in prediction of wire lengths.

Early work in interconnect length prediction was carried out in 1979 by Donath to help estimate the wiring space requirements, delay values and power dissipation [6]. In this work an upper bound for average interconnection length is estimated. It is based on hierarchically applying the relationship between the number of terminal and the number of gates for a given circuit size. The interpretation of this terminal-to-gate relationship known as Rent's rule is described in [7], [8]. According to this interpretation, the number of input and output terminals of nets T leaving a block containing C cells is given by the expression in (Eq1.1), where k and p are empirical constants known as the Rent-coefficient and the Rent- exponent respectively.

$$T = kC^p (Eq1.1)$$

While [6] gives an upper bound approximation on the average length of all interconnects in the circuit, in [9] Donath develops the early model of interconnect length distribution based on the Rent's rule. According to this model the number of interconnects of length l is given by the expression in Eq1.2, where  $\alpha$  is a constant.

$$I[l] = \frac{\alpha C(1 - 4^{p-1})}{2} l^{2p-3}$$

(Eq1.2)

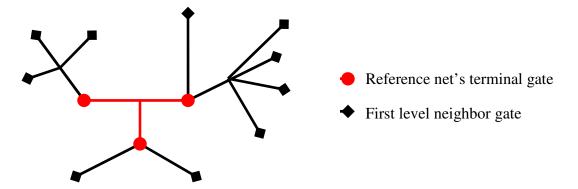

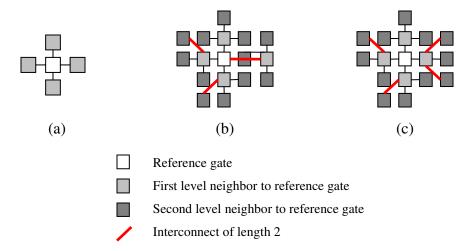

Unlike the macroscopic prediction by Donath, the method in [10], [11] increases the resolution of length prediction by predicting a different net length for each net degree. The length of a net of a given net degree is determined by considering all possible pin configurations of the net over its average neighborhood size, where the size of the neighborhood is measured as the number of gates present in the neighborhood. The neighborhood of a net refers to the cells directly connected to this net and its first-level neighbors. For example, Figure 1.6 shows a net (reference net) and its neighborhood as defined in [10], [11]. The first-level neighbors are those cells that are connected to the cells of the reference net through exactly one other net. In [12] Hamada et al., extend the neighborhood concept to include the second-level neighbors, where the second level neighbors of a net are those cells that are connected to the cells of the reference net

separated by two nets. The method in [12] predicts the connection length distribution of nets of different net degrees by assuming that the length distribution is a form of Weibull distribution and the results [12] are shown to be better than the model in [11]. However, it should be noted that the two methods use different wire length estimation models, and therefore, direct comparisons may not be accurate. In spite of the differences both the models are observed to perform poorly for the largest benchmark tested. One of the main drawbacks of these methods in [10], [11] and [12] is that they ignore the effect of those cells and nets that are outside this small neighborhood.

Figure 1.6 A net and its first level neighborhood

The authors in [13] make one more step forward in microscopic length prediction by estimating the mean and variance of an interconnect length for each interconnect separately. The interconnect lengths are calculated based on structural attributes extracted from its local neighborhood and some global parameters. The local attributes are the interconnect weight (IW) and the neighborhood population at the third-level of the neighborhood (Angh3). The interconnect weight is the sum of the number of unique nets connected to the terminals of an interconnect and degree of the interconnect's net. The global attributes are the total number of cells in the circuit C and the total number of nets in the circuit N. This method establishes a linear relationship between the interconnect weight and both the mean and variance of the interconnect length as shown in expressions (Eq1.3 and Eq1.4). It involves extracting data from known placement results

and then fitting them to a straight line to get the appropriate coefficients (am, bm, av, bv) for calculating the mean and variance for other circuits.

$$Mean = am + bm \cdot Angh3 \cdot IW$$

(Eq1.3)

$$Variance = av + \frac{bv \cdot Angh3 \cdot IW \cdot C}{N}$$

(Eq1.4)

The last decade has seen a number of research efforts targeting the prediction of interconnect length distribution of a complete design. In [14] a new interconnect length distribution model was developed by taking into account the number of possible sites available for an interconnect to occupy at a particular length. The interconnection length distribution for a circuit with C cells is given by the product of the interconnect occupational probability function (Ip[I]) and the site density function (M[I]) as given by the expression in (Eq1.5). In the expression for occupational probability (Eq1.7) the parameters k and p are the Rent-parameters and the parameter  $\alpha$  gives the fraction of terminals that are sinks (Eq1.8). This parameter  $\alpha$  is used for converting the number of net terminals between blocks into number of interconnects between blocks.

$$I[l] = M[l] \cdot Ip[l] \tag{Eq1.5}$$

$$for 1 \le l < \sqrt{C}:$$

$$M[l] = \left(\frac{l^3}{3} - 2l^2 \sqrt{C} + \frac{1}{3}l(6C - 1)\right)$$

$$for \sqrt{C} \le l < \left(2\sqrt{C} - 2\right):$$

$$M[l] = \left(-\frac{l^3}{3} + 2l^2 \sqrt{C} - \frac{1}{3}l(12C - 1) + \frac{2}{3}\sqrt{C}\left(2\sqrt{C} - 1\right)\left(2\sqrt{C} + 1\right)\right)$$

(Eq1.6)

$$Ip[l] \cong \alpha k \frac{p}{2} (2 - 2p) l^{2p-4}$$

(Eq1.7)

$$\alpha = \frac{fanout_{avg}}{1 + fanout_{avg}}$$

(Eq1.8)

The above model considered the entire system as a single block. In [15] however a model that takes into account the hierarchy of the system was developed by Stroobandt

et al. This was done to more closely approximate the multilevel partitioning and placement process which divides the system into hierarchical blocks. In spite of this difference, the model in [15] is still similar to the model in [14] both of them calculate the wire length distribution as a product of the site density function and occupational probability function. Further, the model in [15] also uses the Rent-exponent to calculate the number of interconnects at each hierarchical level and their corresponding length distribution. The overall length distribution is then obtained by the sum of the interconnect length distributions over all the hierarchical levels. This concepts from this model was then extended in [16] into a new model, also developed by Stroobandt, to predict the net length distributions. The length predicted in this model is the Steiner tree length of the nets.

Since these distribution models were heavily dependent on the accuracy of the Rent's exponent, Rent's exponent extraction methods were studied in [17], [18] and [19]. It was observed that the Rent's exponent extracted from placement was always greater than the Rent's exponent extracted from partitioning. Further, it was also shown in [18] that among the two different Rent's exponents extracted from placement, the average local Rent's exponent was greater than the placement Rent's exponent. It was also suggested that the hierarchy-unaware wire length estimation model of [14] should use the average local Rent's exponent for interconnect length distribution calculation, and the hierarchy-aware wire length estimation model in [15] should use the partitioning Rent's exponent for calculating the number of interconnects of a particular hierarchical level and the placement Rent's exponent for calculating the occupational probability of the interconnects in that hierarchical level. However, the usage of Rent's exponent is still only an approximation. Therefore, in [20] Dambre et al., improved upon the model developed by Stroobandt in [16] by eliminating the use of Rent exponent and thereby improving the accuracy in interconnect length distribution estimation.

The last decade has also seen a number of research efforts targeted at predicting the individual wire lengths. For example, the growth-limited multifold clustering methodology in [21] predicts the length of each net separately by performing a clustering based greedy local placement starting from each cell in the circuit. In [22], the post-routing net length is estimated from a polynomial function of several parameters for each net. The parameters are based on the local properties such as the number of pins in the net, number of nets of each unique pin counts in the neighborhood, and global parameters such as the number of cells and pins in the design and the place and route tool. Recently in [23] a mutual contraction (MC) metric has been developed to identify the shorter connections in the given netlist.

While the above explained methodologies were aimed at a priori interconnect length prediction, the methodology in [24] enables an online interconnect length estimation. In other words this prediction is done dynamically during the process of top-down partitioning based hierarchical placement procedure. Consequently, this method results in more accurate estimations for online estimation purposes. Each of the above methodologies explained in this section is aimed at predicting the length of connections or interconnects or nets in the circuit at different stages of the design cycle with varying inputs resulting in varying accuracies.

#### **Proposed Research**

In spite of the wide variety of length prediction models proposed and developed most of them suffer from a severe lack of accuracy. However, the ideal solution to most of the problems arising out of lack of information about the wires would be an accurate prediction of the exact individual post-routing wire lengths of all the wires in the design, during the early stages of the design flow. This would provide a good perspective on all the relevant issues at stake, such as the timing, delay, repeater planning, power dissipation, and heat dissipation attributes of a given design choice.

While predicting the individual routed wire length is ideal, it is a very difficult proposition since it will necessitate bringing into account routing level details into the prediction model. This could complicate the prediction process. Further, it will make it harder to identify possible sources of error in the prediction model. Besides, placement is the primary phase that establishes the basic lower limits on the wire length. Therefore, this research is limited to pre-routing, post-placement wire length prediction.

Most wire length prediction methods can be categorized into two types based on their objective. Microscopic models provide individual wire length prediction, while macroscopic models provide wire length distribution prediction. Another way to classify the wire length prediction models is a priori prediction and online prediction, where the former predicts the wire lengths before the physical design process, whereas the latter provides a continuously evolving wire length prediction during the hierarchical physical design procedure. The research in this work is limited to a priori prediction using both microscopic and macroscopic prediction models due to the larger scope of applicability. However, due to the large number of possible placement solutions, the lengths of the wires will vary from one solution to another. This will limit the accuracy of the prediction. Further, there are also limitations to prediction based on the modeling methodology. Consequently, these limitations to prediction are studied first, following which new models are developed.

Subsequently, this thesis is organized into six chapters. Following this introductory chapter, the first two chapters deal with macroscopic prediction, and the next two chapters deal with microscopic prediction. In each of these pairs, the first chapter deals with the study on limitations to the corresponding prediction (macroscopic or microscopic), while the second deals with the corresponding new model development. Finally, chapter six summarizes the conclusion and future work of this thesis.

The research in this thesis is carried out under the assumption that the individual cell (gate) size variations do not affect the quality of prediction by a huge margin. For the

sake of simplicity in model development and investigation of limitations, it is assumed that the cells (gates) in a given design are of unit size with unit gate pitch width and height. Therefore, IBM placement benchmarks [25] modified to have cells of unit size are used in the investigations. Further, the layout area of the benchmarks is also modified by limiting them to square shapes with approximately 5% white space. The input/output terminals are also removed from the netlists to limit the prediction to wires inside the chip. The attributes of the resulting benchmarks are shown in Table 1.1.

TABLE 1.1

BENCHMARKS USED IN THE RESEARCH AND THEIR ATTRIBUTES

| DENCHWARKS USED IN THE RESEARCH AND THEIR ATTRIBUTES |            |           |                    |

|------------------------------------------------------|------------|-----------|--------------------|

| Benchmark                                            | Gate Count | Net Count | Interconnect Count |

| IBM01                                                | 12036      | 11507     | 28672              |

| IBM02                                                | 19062      | 18429     | 52823              |

| IBM03                                                | 21924      | 21621     | 50298              |

| IBM04                                                | 26346      | 26163     | 58533              |

| IBM05                                                | 28146      | 28446     | 79985              |

| IBM06                                                | 32019      | 33354     | 85392              |

| IBM07                                                | 44848      | 44394     | 108270             |

| IBM08                                                | 50691      | 47944     | 130565             |

| IBM09                                                | 51461      | 50393     | 123024             |

| IBM10                                                | 66948      | 64227     | 176722             |

| IBM11                                                | 68119      | 67016     | 154986             |

| IBM12                                                | 69026      | 67739     | 190052             |

| IBM13                                                | 81018      | 83806     | 196967             |

| IBM14                                                | 145492     | 143202    | 339640             |

| IBM15                                                | 157861     | 161196    | 423765             |

| IBM16                                                | 181633     | 181188    | 499030             |

| IBM17                                                | 182359     | 180684    | 540059             |

| IBM18                                                | 210051     | 200565    | 539258             |

Finally, it should be noted that five different placement tools are used in this research to place these circuits. They are Dragon 3.01 [26], Capo8.8 [27], FengShui5.0 [28], mPL5.0 [29] and an In-house Simulated Annealing based Placement Tool. Partitioning is performed using hMetis [30] and the Rent exponent is extracted using the Rent exponent calculator Rentc [31].

# **CHAPTER 2**

## LIMITATIONS OF MACROSCOPIC PREDICTION

Macroscopic prediction of wire lengths have both inherent limitations and limitations arising out of the model used to make the prediction. A careful study of these limitations is necessary to understand the bounds to macroscopic prediction and to reduce the prediction error. Therefore, investigations were carried out to understand these limitations, and the results from the investigations are presented in this chapter.

The ideal solution to all wire related problems would be an accurate prediction of the length of every wire. But only a fraction of the wires have reasonably similar and therefore predictable length from one placement solution to another (see Chapter 4). Therefore, the next best solution to the wire problem is to provide an accurate macroscopic perspective by predicting the length distribution accurately. However even this could be difficult, since the length of the individual wires and subsequently their length distribution will vary from one placement solution to another. It will vary both from run-to-run within a placement tool and from tool-to-tool. For example, in [32] it was reported that nearly 30% variation in solution quality was observed in commercial placement and routing tools due to non-functional changes in the tool input such as renaming variables or permuting lines of gate level netlist. Also in [33] a similar study was performed that resulted in a difference of up to 7% between the best and the worst placement result.

Therefore, the first part of this chapter presents the results from a study of the inherent limitations to macroscopic prediction due to variability in the distributions from one placement tool to another and from one placement run to another. The second part of the chapter deals with the basics of the current wire length distribution models and the limitations to accuracy arising out of the model themselves.

# Variability of Distributions

Interconnect length distribution models dominate the current macroscopic model research due to the fact that modeling net lengths in macroscopic models is very difficult. Accurate prediction of interconnect length entails an accurate understanding of the variability associated with it. Therefore, in this section the variability in the average interconnect length is studied first, and then the variability in interconnect length distribution is studied. For each of the above cases, both intra-tool and inter-tool variability are studied. The Intra-tool variability, which is the variability in results within a placement tool, is studied using five different placement results extracted from Dragon 3.01. Although it is possible for the intra-tool variability to change form one tool to another, it is assumed that the results from Dragon3.01 are a sufficient approximation to provide a basic understanding of the intra-tool variability. Inter-tool variability, which is the variability in results from one placement tool to another, is also studied using five different placement results, but with one result each from five different placement tools viz., Dragon3.01, Capo8.8, FengShui5.0, In-house Simulated Annealing and finally mPL5.0 global placement combined with FengShui5.0 based detailed placement. The detailed placement of the mPL5.0 global placement is done using FengShui5.0 because the detailed placer of mPL5.0 crashed when used on the modified benchmarks used for our experiments.

#### **Coefficient of Variation**

The metric used in this study to analyze the variation in a given variable is called the coefficient of variation (CoV). It is defined as the ratio of the standard deviation of a given variable to the average of that given variable. CoV is used to study the variation because the metric isolates the variation from the magnitude of the average value of the data by providing the standard deviation per unit value of the average. This is especially useful in applications that compare variables with a large range of average values.

# **Average Interconnect Length**

The average interconnect length is the most basic point measure of interconnect length, and its value, which is derived from interconnect length distribution is used in a variety of applications such as area estimation and power consumption [34]. Table 2.1 gives the average and coefficient-of-variation of the average interconnect length for both inter-tool and intra-tool variability for the various benchmarks. It was observed that for the intra-tool variability, the CoV has a range of 0.025 with an average of 0.0183. The CoV of the inter-tool variability has a wider range of 0.0672 and a greater average of 0.0815 that is nearly 4.5 times the intra-tool CoV. It can also be seen from these results that the average interconnect length for a given netlist has a worst case CoV of 0.0316 for intra-tool variability and 0.1186 for inter-tool variability.

TABLE 2.1

AVERAGE INTERCONNECT LENGTH INTRA-TOOL AND INTER-TOOL VARIABILITY

| Benchmark | Intra-tool Variability |                | Inter-t | Inter-tool Variability |  |

|-----------|------------------------|----------------|---------|------------------------|--|

|           | Average                | Coefficient of | Average | Coefficient of         |  |

|           |                        | Variation      |         | Variation              |  |

| IBM01     | 7.72                   | 0.0214         | 7.59    | 0.0619                 |  |

| IBM02     | 13.96                  | 0.0188         | 13.75   | 0.0797                 |  |

| IBM03     | 12.98                  | 0.0157         | 12.85   | 0.0750                 |  |

| IBM04     | 11.91                  | 0.0092         | 11.92   | 0.0604                 |  |

| IBM05     | 22.38                  | 0.0207         | 21.86   | 0.0514                 |  |

| IBM06     | 13.81                  | 0.0316         | 13.63   | 0.1034                 |  |

| IBM07     | 12.69                  | 0.0116         | 12.54   | 0.0899                 |  |

| IBM08     | 15.69                  | 0.0241         | 16.13   | 0.0785                 |  |

| IBM09     | 10.78                  | 0.0299         | 10.83   | 0.0719                 |  |

| IBM10     | 12.20                  | 0.0163         | 12.35   | 0.0755                 |  |

| IBM11     | 11.14                  | 0.0088         | 11.41   | 0.0764                 |  |

| IBM12     | 14.62                  | 0.0219         | 14.92   | 0.0894                 |  |

| IBM13     | 12.21                  | 0.0066         | 12.25   | 0.0766                 |  |

| IBM14     | 15.49                  | 0.0151         | 15.65   | 0.0766                 |  |

| IBM15     | 15.07                  | 0.0167         | 15.47   | 0.0878                 |  |

| IBM16     | 16.17                  | 0.0300         | 16.43   | 0.0983                 |  |

| IBM17     | 18.98                  | 0.0169         | 19.24   | 0.0957                 |  |

| IBM18     | 17.73                  | 0.0142         | 18.50   | 0.1186                 |  |

| Average   |                        | 0.0183         |         | 0.0815                 |  |

### **Interconnect Length Distribution**

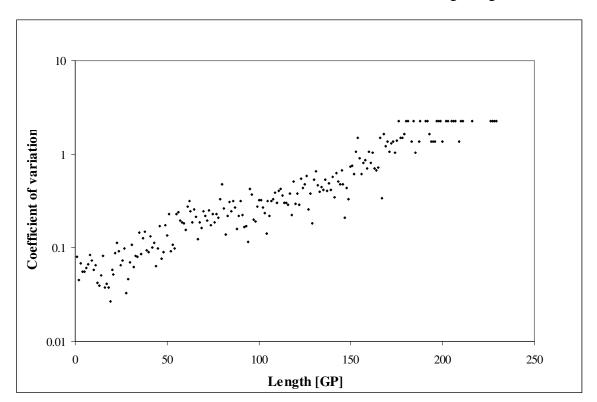

In this section, the variation in the distribution of interconnect lengths is analyzed by calculating the CoV of the distribution for each length. Figure 2.1 shows a sample relation between CoV of the length distribution and length of interconnects of IBM03 benchmark for inter-tool variation. It can be observed from this figure that the coefficient of variation generally increases with length of the interconnect. Similar CoV relations were observed for the other benchmarks in both intra-tool and inter-tool variation study. Based on these observations it is possible to hypothesize that the distribution of shorter interconnects with higher frequency are more predictable (repeatable) due to its lower CoV than the distribution of longer interconnects. Also it was observed that the CoV of the individual length distributions is much higher for most lengths than the CoV of the average interconnect length; for this reason it can be hypothesized that the prediction of the distribution of interconnects will be more difficult than the average length.

Figure 2.1 Inter-tool length distribution variability for IBM03

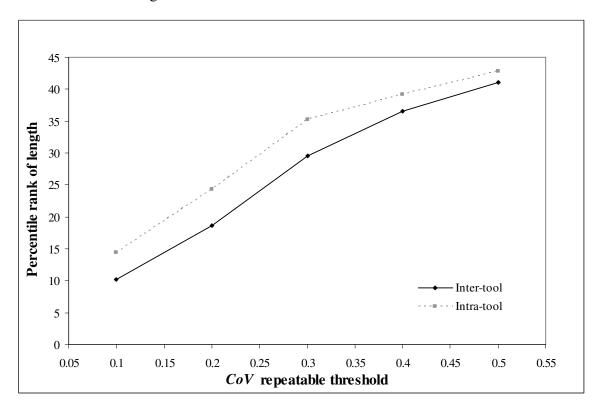

Further analysis is therefore performed to develop a better understanding of distribution variability. This is done by dividing the entire length range in the distribution into two regions, those lengths with less variation in the distribution (predictable region) and those lengths with high variation in the distribution (unpredictable region). A fixed CoV value is used as a threshold (repeatable threshold) to separate the two regions. The predictable part of the distribution is defined as that part of the distribution starting from length one and extending until the length for which the five-point moving average of the CoV of the length distribution exceeds the repeatable threshold. The five-point moving average was used to smoothen the relationship between the CoV of length distribution and the length. The value of repeatable threshold is varied from 0.1 to 0.5. This corresponds to a standard deviation that is less than 10% of its average distribution to less than 50% of its average distribution.

Figure 2.2 Percentile rank of length below which the distribution is repeatable

Figure 2.2 shows the relation between the repeatable threshold and the average of the percentile rank of length (from five different benchmarks IBM01 to IBM05) below which the distribution is repeatable for both intra-tool and inter-tool variation. Percentile rank of length is the percent value of the length with respect to the maximum possible length of an interconnect in the given design. On an average the shortest 14% of the lengths in a given design has a distribution value whose standard deviation is less than 10% of the average distribution, for the case of intra-tool variation (see Figure 2.2 for a CoV of 0.1). However for the case of inter-tool variation (see Figure 2.2) on an average only the shortest 10% of the interconnect lengths meet the same repeatable threshold criteria of 0.1.

Figure 2.3 Percent interconnects in the repeatable part of distribution

An interesting attribute of this repeatable part of the distribution in the inter-tool variation is that this shortest 10% of interconnect lengths constitute 88% of the total

number of interconnects on an average. This forms the predictable region (repeatable part) of the distribution, and the remaining 12% of interconnects constitute the part of the distribution that varies widely (non-repeatable part) from placement tool-to-tool. This result depicting the relation between the percent interconnects in the repeatable and non-repeatable part of the distribution is shown in Figure 2.3 for five benchmark circuits.

Yet another interesting aspect of this repeatable part is that the 88% of interconnects in the repeatable part constitutes only 52% of the total interconnect length, while the remaining 12% of interconnects in the non-repeatable part constitute nearly 48% of the total interconnect length. This result in terms of the percent total interconnect length in the repeatable and non-repeatable part of a distribution is shown in Figure 2.4 for five benchmark circuits.

Figure 2.4 Percent interconnect length in the repeatable part of distribution

A typical application for wire length distribution such as repeater insertion planning would need the total wire length of the longer global interconnects and therefore

the distribution of the wires in the non-repeatable part of the distribution with longer wires. Table 2.2 gives the observed relationship between the best-case and worst-case scenario (minimum and maximum) of the percentage of total interconnect length in the non-repeatable part of the distribution among the set of five different distributions studied under both intra-tool and inter-tool variation. From this table it can be seen that the maximum of total length of interconnects in the non-repeatable part of the distribution could be 13% more than the minimum in the case of intra-tool variation, and 39% more than the minimum in the case of inter-tool tool variation. Therefore if a length distribution is predicted with discrete values, even if it is accurate for one run, it could still underestimate the total length of the interconnects in the non-repeatable part of the distribution by as much as 13% for another run of the same tool or as much as 39% of for another run in a different tool. Consequently any repeater insertion planning done based on a discrete predicted interconnect length distribution without keeping these variations in consideration will suffer.

TABLE 2.2

PERCENT TOTAL INTERCONNECT LENGTH IN NON-REPEATABLE PART OF DISTRIBUTION

| Netlist | Inter-tool variation |                | Intra-tool variation |                |  |

|---------|----------------------|----------------|----------------------|----------------|--|

|         | Minimum              | <u>Maximum</u> | Minimum              | <u>Maximum</u> |  |

|         | (% Length)           | Minimum        | (% Length)           | Minimum        |  |

| IBM01   | 27.37                | 1.18           | 39.58                | 1.32           |  |

| IBM02   | 26.67                | 1.09           | 37.76                | 1.52           |  |

| IBM03   | 41.55                | 1.07           | 42.76                | 1.43           |  |

| IBM04   | 26.52                | 1.09           | 39.31                | 1.43           |  |

| IBM05   | 37.05                | 1.20           | 59.27                | 1.25           |  |

| Average | 31.83                | 1.13           | 43.73                | 1.39           |  |

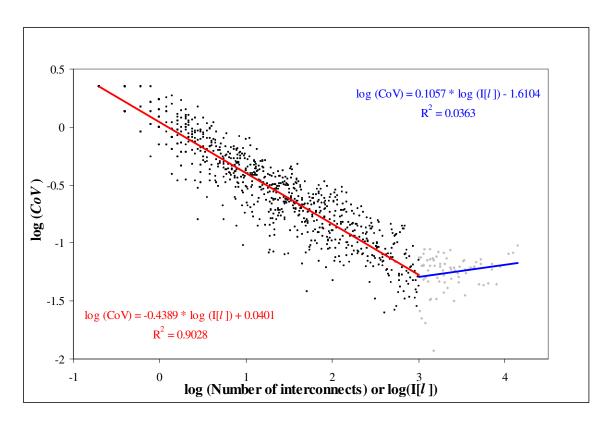

In such scenarios, a model to predict the variation would greatly aid the interconnect length distribution application development effort. Figure 2.5 shows the relationship between the average of the distribution values of interconnect length from five placement results and their corresponding CoV's observed for the five benchmark

circuits in the inter-tool variation study. A clear relationship between the CoV and distribution of interconnect lengths can be observed from this figure.

Figure 2.5 Relation between length distribution and its coefficient of variation

Consequently, a piecewise model is developed by dividing this data into two regions. Linear regression is then used to fit the logarithmic values of length distribution and its coefficient of variation. The resulting piecewise model is shown in Figure 2.6. For distribution values less than 1000, the model shows a strong negative correlation with an R<sup>2</sup> value of 0.9028, while for distribution values greater than 1000, which are observed for very short lengths, the correlation is very weak with the CoV values being almost constant. Although the model is empirical, it still depicts some basic relations between the variation of the length distribution and the distribution for a given length. Therefore, given a reasonably accurate discrete length distribution model approximate estimations on the variation of these distributions is possible.

Figure 2.6 Piecewise model of the coefficient of variation of length distribution

# **Macroscopic Models Overview**

Macroscopic models are mainly limited to interconnect length prediction due to the difficulty and time requirements involved in modeling the length of wires with more than two terminals as a net model in the prediction methodology. They generally model the length distribution of the wires. The earliest macroscopic model was developed by Donath [9]. Current state of the art macroscopic models were developed by Davis, De and Meindl (DDM model) [14], Stroobandt et al., (Stroobandt's model) [15] and an improved version of the later developed by Dambre (Dambre's model) [20]. All of the above three models are derived using a fundamentally common framework. They estimate the number of interconnects of a given length by using a combination of two functions. The first part called *interconnect site density function* calculates the number of interconnect sites of a given length available for the interconnects to occupy. The second

part called the *interconnect occupational probability function* gives the probability that an interconnect position of a given length is occupied.

The major difference between these models lies in the nature of the derivation of the solution. Stroobandt's model and Dambre's model are derived using Donath model as the basis. Since the physical design process can be viewed as a hierarchical process corresponding to the partitioning of the circuit followed by the partitioning of its corresponding layout in which the partitioned block will be placed, the models adopt a hierarchical approach, assuming the system will be placed using such a methodology. The model works by estimating the number of interconnects newly cut at each partitioning level. This is followed by an estimation of the number of interconnect sites of different lengths available for these newly cut interconnects in the correspondingly newly partitioned layout blocks at each hierarchical partitioning level. The interconnect positions are counted such that they only include those positions that have one terminal each in each of the layout partitions of the correspondingly newly partitioned layout. An interconnect occupational probability function is then used to estimate the probability that one of the newly cut wires occupy one of the available positions in each hierarchical level. Thus an interconnect length distribution is estimated for each hierarchical partitioning level and the total interconnect length distribution is obtained as the sum of the interconnect length distributions of the individual hierarchical levels. DDM model on the other hand does not make any assumptions about the placement methodology used and calculates the interconnect site density and occupational probability for the entire design in one step, in a flat manner without any hierarchical modeling. In this section of the chapter, a closer look is taken at the DDM model and Dambre's model to understand their limitations.

All of these models ignore the variation in cell sizes and assume all the cells to be of a uniform size. The DDM model and Stroobandt model assume these cells to be of unit size with a square shape. Dambre's model on the other hand includes the possibility to

model rectangular shaped cells [20]. The models assume that the cells are placed in a layout, which is in the form a grid with the sites for the cells having the same size and shape as the cells.

#### **DDM** model

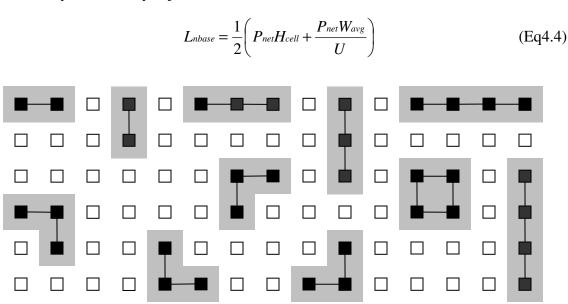

The DDM model of interconnect length distribution for a given circuit is derived by using a *principle of conservation of terminals* between three blocks constructed over the layout. The three blocks A, B and C used in the development of the model, shown in Figure 2.7, have  $N_A$ ,  $N_B$  and  $N_C$  cells in them respectively. The blocks are constructed such that a single closed path can encircle one, two or all three of the blocks and together form a semi-manhattan circle with the single celled block A at the centre, the cells of block C at the periphery, and the cells in between forming block B. Consequently the cells in block C are at a fixed distance from the cell in block A. This block based system is used to derive an expression for estimating the number of terminals between blocks A and C. This function is then used to derive the expression for interconnect occupational probability function Ip[I], where I is the distance between the block A and block C. Finally the interconnect length distribution function is obtained by the combination of interconnect site density function M[I] and interconnect occupational probability function Ip[I].

According to the conservation of terminals, the terminals coming out of a block should either be connected to one of the other block's terminals or to one of the terminals that lies outside the blocks. Applying this principle to the three block system in Figure 2.7 yields Eq2.1, where  $T_A$ ,  $T_B$ ,  $T_C$  and  $T_{ABC}$  represent the total number of terminals coming out of block A, B, C and ABC and  $T_{A-to-B}$ ,  $T_{B-to-C}$  and  $T_{A-to-C}$  represent the total number of terminals between blocks A and B, B and C and A and C respectively.

$$T_A + T_B + T_C = T_{A-to-C} + T_{B-to-C} + T_{A-to-B} + T_{ABC}$$

(Eq2.1)

Figure 2.7 Blocks used in interconnect length distribution model derivation

Upon simplification Eq2.1 yields Eq2.2, which gives the total number of terminals between blocks A and C, where the cells in block C are separated from the cell in block A by a constant distance, say *l*.

$$T_{A-to-C} = T_{AB} - T_B + T_{BC} - T_{ABC}$$

(Eq2.2)

The terminal count values used in Eq2.2 are based on the net models terminals. Assuming a single source terminal for each net, each sink terminal of the net will correspond to a single interconnect. Hence a factor  $\alpha$  (Eq1.8), which gives the fraction of net terminals that are sink terminals is used to calculate the number of interconnects between block A and C ( $I_{A-to-C}$ ), that are of length l by multiplying the number of terminals between block A and C by  $\alpha$ .

$$I_{A-to-C} = \alpha (T_{AB} - T_B + T_{BC} - T_{ABC})$$

(Eq2.3)

The probability that there is an interconnect of length l (Ip[l]) in between a pair of cell positions separated by a distance l is given by the probability that there is an interconnect between one of the cells in block C and the cell in block A.

$$I_{p}[l] = \frac{\alpha(T_{AB} - T_{B} + T_{BC} - T_{ABC})}{N_{C}}$$

(Eq2.4)

The total number of interconnects of a given length l in the system (I[l]) is then obtained by the product of the probability that there is an interconnect in between a pair of cell positions separated by length l given by Ip[l] and the total number of cell position pairs that are separated by a distance l given by M[l] (Eq2.5). The expression for number of pairs of cell positions separated by a given distance l is derived by counting the number of cell positions in Block C for all possible positions of block A in the layout, and is given by (Eq2.6)

$$I[l] = M[l] \cdot Ip[l]$$

(Eq2.5)

for

$$1 \le l < \sqrt{C}$$

:

$$M[l] = \left(\frac{l^3}{3} - 2l^2 \sqrt{C} + \frac{1}{3}l(6C - 1)\right)$$

for  $\sqrt{C} \le l < (2\sqrt{C} - 2)$ :

$$M[l] = \left(-\frac{l^3}{3} + 2l^2 \sqrt{C} - \frac{1}{3}l(12C - 1) + \frac{2}{3}\sqrt{C}(2\sqrt{C} - 1)(2\sqrt{C} + 1)\right)$$

(Eq2.6)

To calculate *I*[*I*] values, it is necessary to have a methodology to estimate the total number of terminals from blocks B, AB, BC and ABC required by Eq2.4. It is for this purpose that the Rent's rule is used to estimate the total number of terminals coming out of the blocks B, AB, BC and ABC as shown in Eq2.7.

$$T_{B} = k(N_{B})^{p}$$

$$T_{AB} = k(N_{A} + N_{B})^{p}$$

$$T_{BC} = k(N_{B} + N_{C})^{p}$$

$$T_{ABC} = k(N_{A} + N_{B} + N_{C})^{p}$$

(Eq2.7)

The original interpretation of the Rent's rule in [2] is derived using a terminal-to-gate relation (T-to-G) where the terminal count for a block with a given number of gates is counted based on the number of segments into which the net is cut among the various blocks, where each cut net segment has one terminal coming out of its block to connect to the other cut net segments. This type of interpretation of terminals will be referred to as *net-terminal interpretation* and is illustrated in Figure 2.8.

Net-terminal interpretation Net source gate: p; Net sink gates: q, r, s Block 1: p, r; Block 2: q, s; Block terminal count: 2 (shaded squares)

Figure 2.8 Net model (left) and net-terminal interpretation (right)

Given Eq2.7, values of the sizes of the blocks A, B and C are needed to estimate the required terminal count values. However the sizes of the cells will vary based on the position of block A within the layout. For example, if the block A in Figure 2.7 is placed close to the periphery of the layout and if the distance between block A and C that is considered is large enough, the semi manhattan circle forming the blocks may partially lie outside of the layout area. In order to make calculations simpler, the DDM model is derived assuming that the layout grid in which the cells are placed is infinitely large, and the block sizes can be approximated by assuming that the blocks B and C will always be entirely within the layout. Eq2.8 gives the expression for the size of the blocks based on this assumption. This approximation will be referred to as *infinite plane block size approximation*. Using Eq2.8 and Eq2.7, the expression for *Ip[I]* in Eq2.4 is simplified by binomial expansion to its final form shown in Eq2.9.

$$N_A = 1$$

$$N_B = l(l-1)$$

$$N_C = 2l$$

(Eq2.8)

$$Ip[l] \cong \alpha k \frac{p}{2} (2 - 2p) l^{2p-4}$$

(Eq2.9)

In [14], the distribution model is fitted to an actual distribution, and the corresponding Rent exponent p is extracted. This Rent exponent value is then used to predict the length distribution of other designs. The main application of this technique in [14] was to predict wire length distributions for future generic systems to understand the limits of Moore's law. However, for applications where a rapid estimation of a wire length distribution is needed for a specific netlist, a different methodology is used by researchers, which is shown below.

Step 1: Extract the net-terminal interpretation based T-to-BS relation by performing partitioning of the netlist.